| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LR38666Y | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

DESCRIPTION

The LR38666Y is a CMOS digital signal processor

for color digital still camera systems of 1 310 k/ 2 140 k/

3 300 k/3 370 k/4 200 k-pixel CCDs with primary

color mosaic filters.

FEATURES

∑ ARM7TDMI is used as the CPU core

∑ CCD signal processor modules

≠ Supported image size : 1 310 k/ 2 140 k/3 300 k/

3 370 k/4 200 k pixels

≠ R, G and B primary color mosaic filters :

Bayer matrix, 10 bits per color

≠ Built-in auto focus, auto exposure and auto

white balance functions

≠ Built-in digital clamp and gamma correction

functions

∑ Video encoder module

≠ Composite analog signal output mode :

Switchable between NTSC and PAL

≠ Built-in OSDC function

∑ JPEG encoding/decoding module :

Built-in circuits for encoding and decoding

≠ Encoding rate : Max. 66 ms per frame

(for 1/10-compression in VGA mode)

≠ Decoding rate : Max. 66 ms per frame

(for decompression in VGA mode)

(Assuming that SDRAM is used and the internal

bus is occupied by the JPEG module)

∑ SDRAM/flash memory controller module

∑ Synchronous/asynchronous SIO

∑ USB 1.0 is supported

∑ General purpose I/O ports

∑ Built-in audio I/F

∑ Built-in resizing function

∑ Built-in CompactFlash I/F

∑ Built-in SmartMedia I/F

∑ Power supplies

≠ +2.5 V for digital/analog circuits

≠ +3.3 V for digital circuits

∑ Package : 240-ball CSP (T-TFBGA240-1414)

LR38666Y

1

LR38666Y

One-chip System LSI for Digital Still

Cameras

In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP devices shown in

catalogs, data books, etc. Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.

BACK

2

LR38666Y

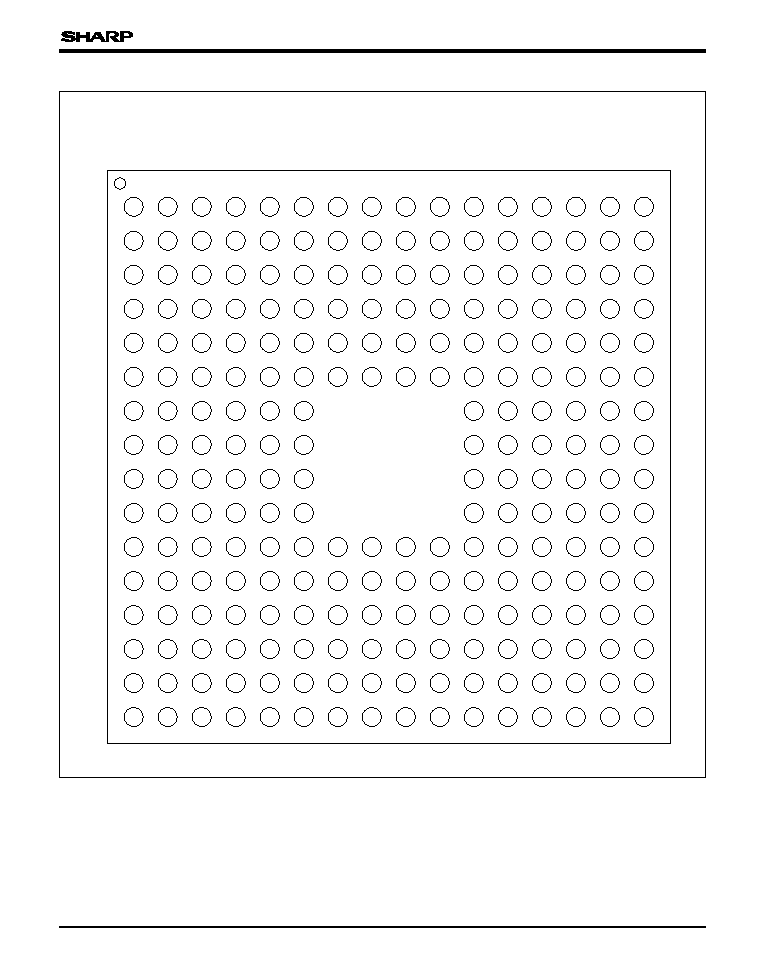

237

PLV

DD

1

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

MEMCKE

1

2

MEMCKE

2

5

MEMCS1Z

14

MEMD

3

20

MEMD

7

27

MEMD

12

32

TEST1Z

38

MEMD

18

44

DV

DD

50

DV

DD2

54

DGND

MEMD

31

236

PLGND

232

TESTCLK

2

228

DV

DD2

227

SDI

0

221

C24MI

215

ASCLK

209

TGED

1

204

CCDIN

6

198

COMI

193

DV

DD2

188

186

183

DIREF

2

DAV

DD

238

PLGND

234

DV

DD

230

C29MI

224

DV

DD

218

DV

DD

212

ASDO

206

CCDIN

8

201

DV

DD

195

CCDIN

1

190

TGCLK

185

DV

REF2

182

DAGND

181

YCOUT

239

DGND

235

PLV

DD

231

SDO

0

225

SCLK

0

219

SDI

1

213

TCLK

207

CCDIN

9

200

CCDIN

3

194

CCDIN

0

189

184

COUT

178

DI

REF1

179

DV

REF1

4

MEMCS0Z

233

ICEFIQZ C29MO

226

DGND

220

DGND

211

ASDI

208

TGED

0

202

CCDIN

4

192

VD

187

VB

2

173

GIO

14

175

RESETZ

174

GIO

15

15

DGND

12

MEMD

2

16

MEMD

4

222

C24MO AXSYNCO

COMO

162

197

CCDIN

5

203

DGND

214

216

GIO

5

163

GIO

6

167

GIO

9

164

DGND

165

GIO

7

21

DGND

18

MEMD

6

17

MEMD

5

22

MEMD

8

156

GIO

1

157

GIO

2

161

GIO

4

159

GIO

3

158

DV

DD2

26

DGND

24

MEMD

10

23

MEMD

9

28

MEMD

13

150

CFA

1

151

CFA

2

155

GIO

0

153

DGND

152

CFA

3

33

DGND

31

MEMD

15

30

MEMD

14

34

MEMD

16

CFD

11

145

CFD

13

148

CFD

15

147

CFD

14

146

DV

DD

39

MEMD

19

37

MEMD

17

40

DGND

36

TST3Z

CFD

8

DV

DD2

TEST7Z

141

DGND

140

CFD

10

46

MEMD

22

48

DGND

43

TEST5Z

42

TEST4Z

82

TEST6Z

89

DGND

94

DV

DD2

MEMA

20

96

MEMA

16

DGND

CFD

7

134

CFD

5

135

CFD

6

51

MEMD

25

49

MEMD

24

71

MEMA

0

76

MEMA

3

77

MEMA

4

83

MEMA

8

90

MEMA

12

FL_EXWEZ

100

DGND

CFD

3

CFD

2

127

CFD

0

129

DV

DD

55

MEMD

28

53

MEMD

27

70

MEMWEZ

72

MEMA

1

79

DGND

85

DGND

91

MEMA

13

FLCE0Z

97

MEMA

17

FLRP0Z EXCS1Z

124

CFRST

125

CFCE1Z

58

59

56

MEMD

30

64

MEMRASZ

67

DGND

73

DGND

80

MEMA

6

87

MEMA

10

93

DGND

DGND

99

MEMA18

EXCS0Z EXDACK1Z

118

122

126

CFCD1Z CFREGZ

TGID

DV

DD

229

9

DGND

7

DV

DD

NC

3

MEMCKE

3

6

MEMCS2Z

8

MEMCS3Z

19

DV

DD

25

MEMD

11

29

DV

DD

35

TEST2Z

41

MEMD

20

45

MEMD

21

47

MEMD

23

52

MEMD

26

DV

DD

13

DV

DD2

10

MEMD

0

MEMD

1

223

SDO

1

217

ARSYNCO

210

TGED

2

205

CCDIN

7

199

DGND

196

CCDIN

2

191

HD

169

GIO

11

171

GIO

12

170

TESTCLK

NC

177

VB

1

176

DGND

172

GIO

13

166

GIO

8

160

DV

DD

154

CFA

4

149

CFA

0

144

CFD

12

138

CFD

9

132

CFD

4

128

CFD

1

CFCE2Z

168

GIO

10

11

143

137

139

142

102

133

136

107

131

130

103

109

113

106

111

115

DGND

62

61

57

MEMLDQM

65

MEMCASZ

69

DV

DD2

75

DV

DD

81

MEMA

7

86

DV

DD

92

MEMA

14

FLCE1Z

98

DV

DD

FLRP1Z EXDACK0Z

119

121

123

CFCD2Z CFWAITZ

MEMD

29

DGND

104

110

114

MEMUDQM

66

63

DV

DD

68

MEMCLK

74

MEMA

2

78

MEMA

5

84

MEMA

9

88

MEMA

11

95

MEMA

15

FL_EXOEZ

101

MEMA

19

FLWPZ

DV

DD

116

117

EXINTZ CFRDBY

NC

NC

105

108

112

Index mark

(T-TFBGA240-1414)

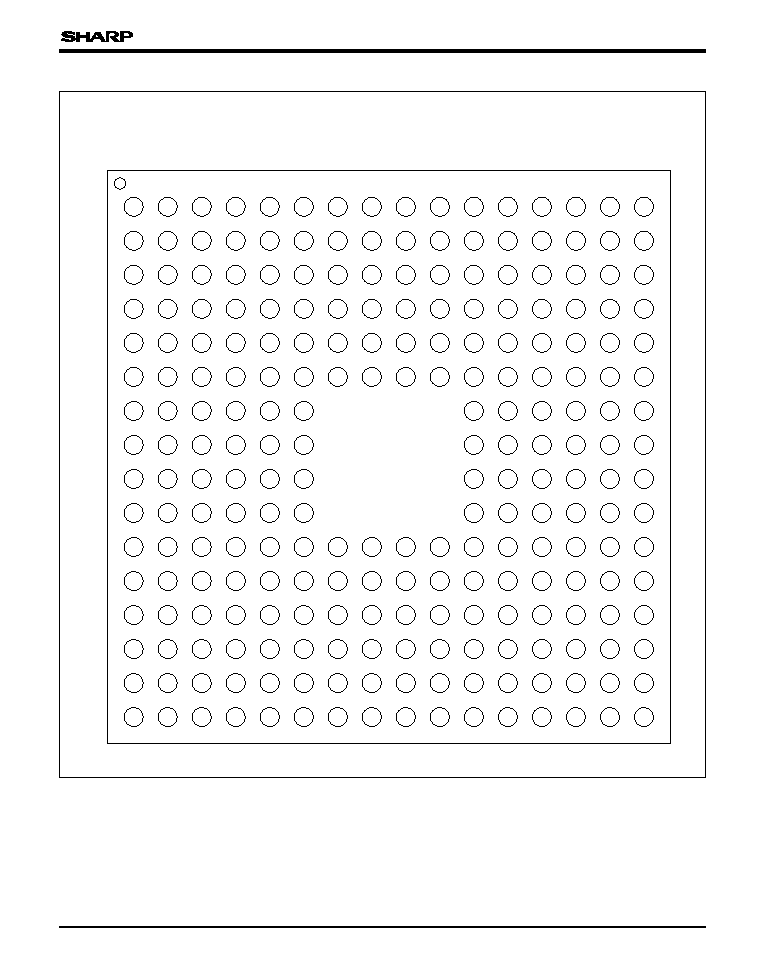

PIN CONNECTIONS

240-BALL CSP

TOP VIEW

LR38666Y

3

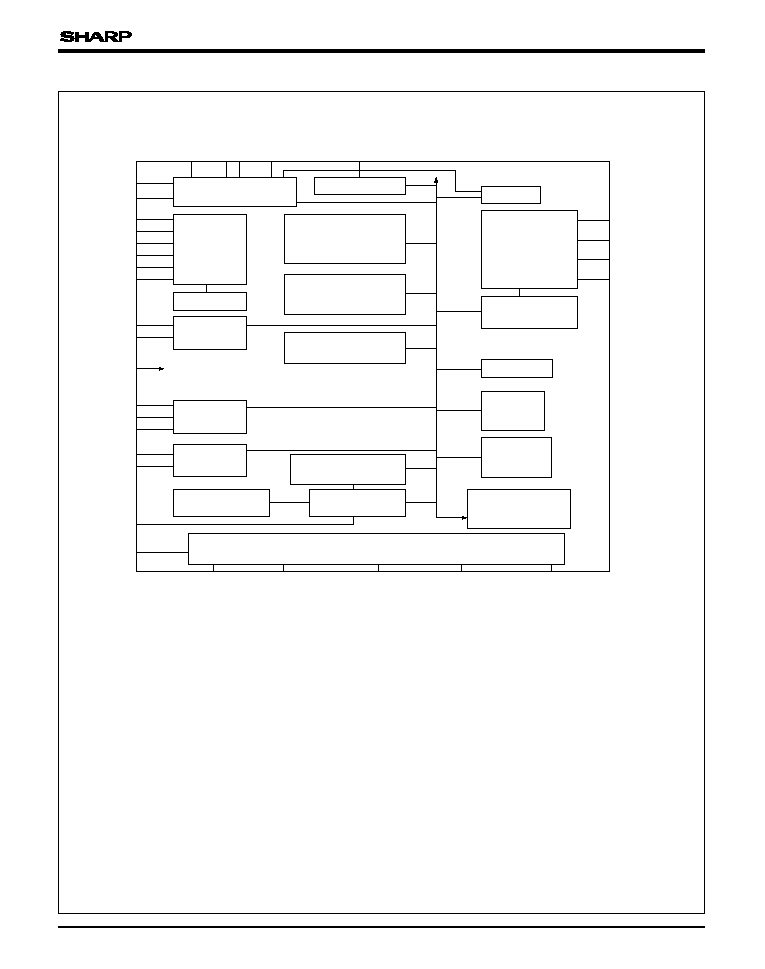

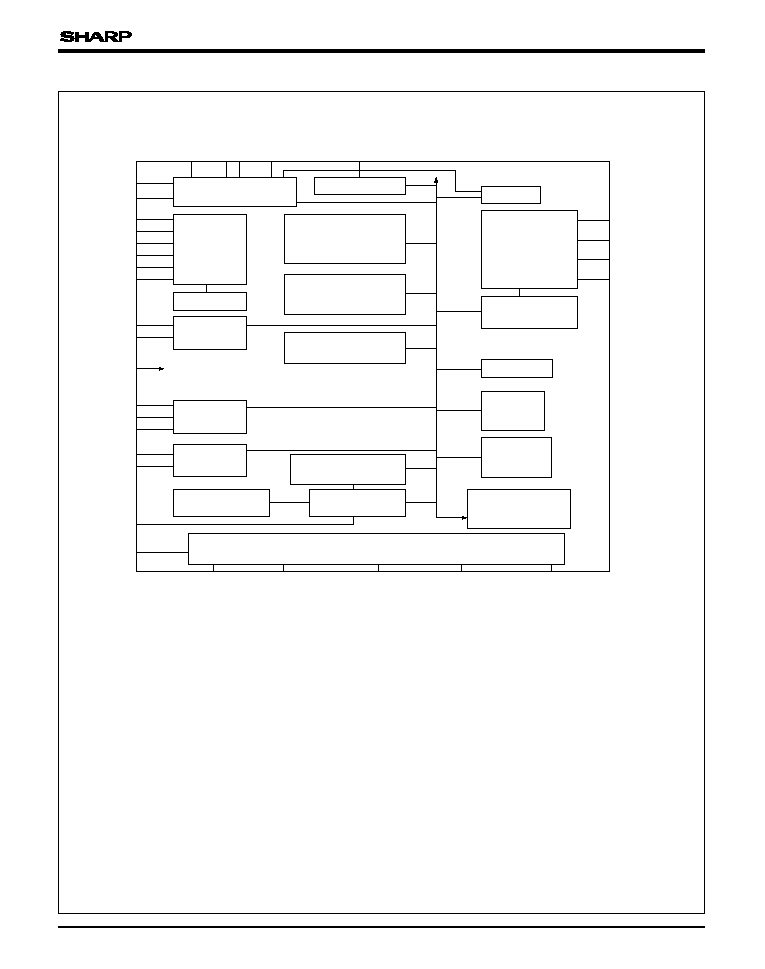

TGID

HD

VD

CCDIN

0

-

CCDIN

9

CONTROL

SIGNAL

(NOTE 3)

CONTROL

SIGNAL

(NOTE 2)

CONTROL

SIGNAL

(NOTE 1)

MEMA

0

-

MEMA

20

MEMD

0

-

MEMD

31

USB

CCD SIGNAL

PROCESSOR 2

JPEG COMPRESSOR/

DECOMPRESSOR

RESIZE

CCD SIGNAL

PROCESSOR 1

PLL

LOCAL SRAM

4 K BYTES

CPU

PERIPHERAL

ARM7TDMI

MEMORY CONTROLLER

D/A CONVERTER

NTSC/PAL

ENCODER

TIMER

DMAC

DECODER

BUS CONTROLLER

YCOUT

COUT

DV

REF1

, DV

REF2

DI

REF1

, DI

REF2

VB

1

, VB

2

GIO

0

-GIO

15

(NOTE 4)

TGCLK

TGED

0

-

TGED

2

COMI

COMO

C24MI

C24MO

C29MI

C29MO

ASDI

ASDO

ASCLK

AXSYNCO

ARSYNCO

TESTCLK

TESTCLK

2

TCLK

TEST1Z-

TEST7Z

SDI

0

SDO

0

SCLK

0

SDI

1

SDO

1

RESETZ

ICEFIQZ

CFD

0

-CFD

15

(NOTE 5)

CFA

0

-CFA

4

CLOCK

GENERATOR

AUDIO

I/F

UART

USART

GIO

BLOCK DIAGRAM

NOTES :

1. Control signal for SDRAM

MEMCLK, MEMLDQM, MEMUDQM, MEMWEZ,

MEMCASZ, MEMRASZ, MEMCKE

1

, MEMCS0Z-

MEMCS3Z

Control signal for SDRAM or general purpose I/O.

MEMCKE

2

= GIO

16

, MEMCKE

3

= GIO

17

(set by

register)

2. Control signal for flash memory and external device.

FLCE0Z, FL_EXOEZ, FL_EXWEZ, FLWPZ, FLRP0Z,

EXCS0Z, CFREGZ, CFRST, CFCE1Z to CFCE2Z

Control signal for flash memory and external device or

general purpose I/O

FLCE1Z = GIO

18

, FLRP1Z = GIO

19

, EXCS1Z =

GIO

20

(set by register)

3. Input signal from external device

EXDACK0Z, EXINTZ, CFWAITZ, CFRDBY

Input signal from external device or general purpose

I/O.

EXDACK1Z = GIO

21

, CFCD1Z = GIO

22

, CFCD2Z =

GIO

23

(set by register)

4. General purpose I/O or PWM.

GIO

0

to GIO

2

= CCDGEO

0

to CCDGEO

2

, GIO

9

=

TX_VPO, GIO

10

= TX_VMO, GIO

11

= TX_OE_N,

GIO

12

= SUSPEND_N, GIO

13

= RX_VPI, GIO

14

=

RX_VMI, GIO

15

= RX_DATA (set by register)

5. Data I/O for CompactFlash or general purpose I/O.

CFD

8

= GIO

24

, CFD

9

= GIO

25

, CFD

10

= GIO

26

,

CFD

11

= GIO

27

, CFD

12

= GIO

28

, CFD

13

= GIO

29

,

CFD

14

= GIO

30

, CFD

15

= GIO31 (set by register)

4

LR38666Y

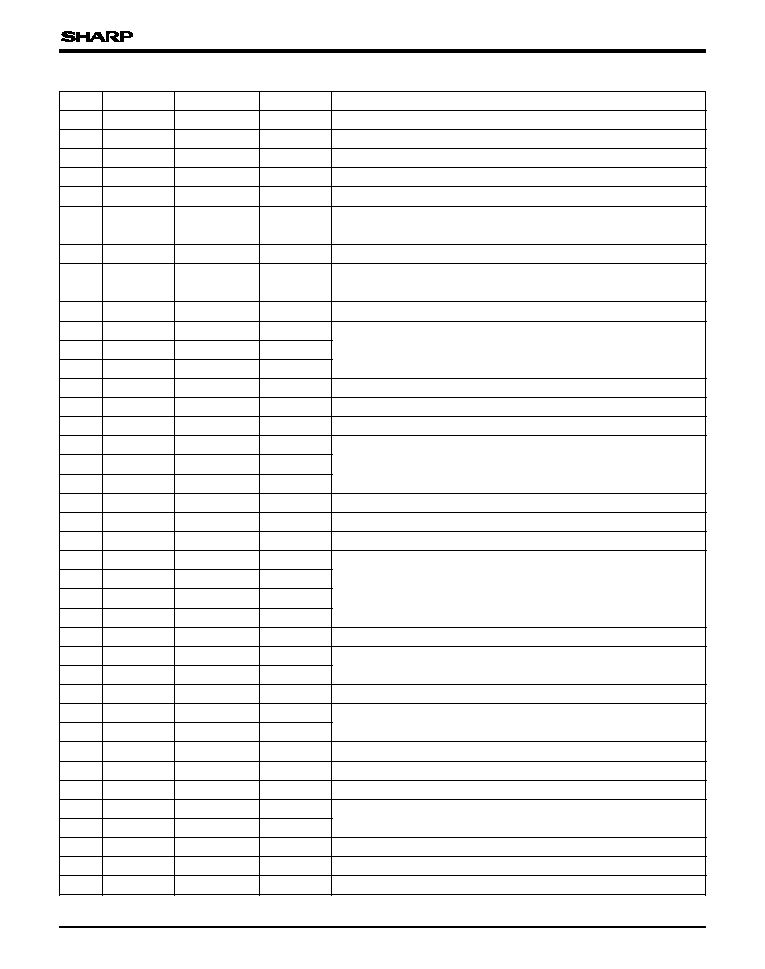

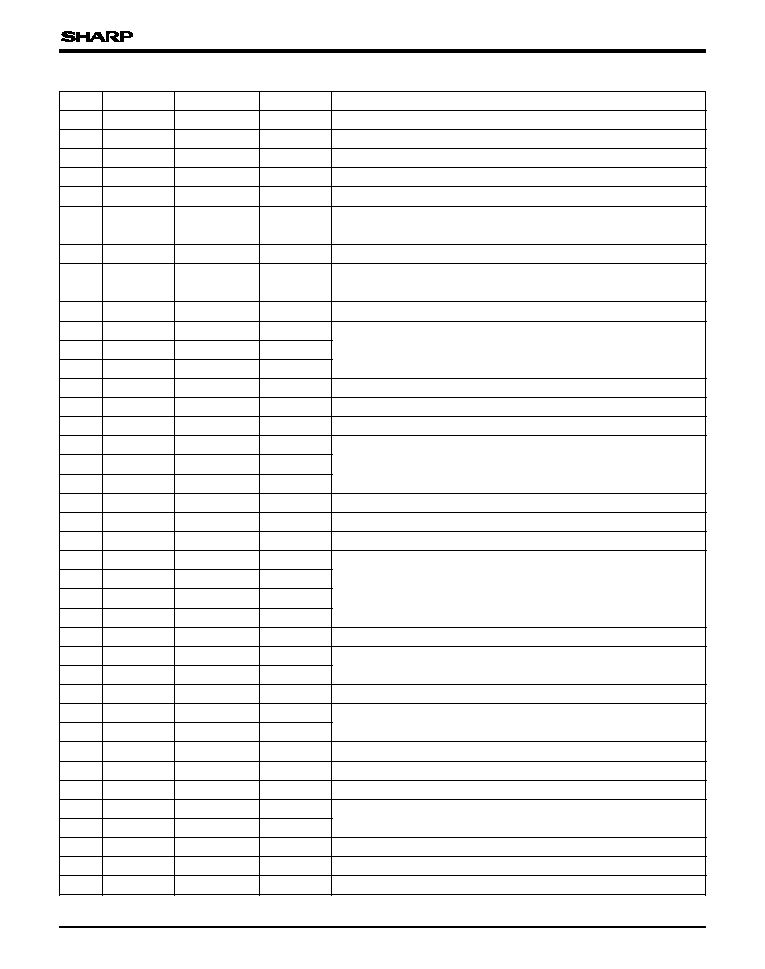

PIN DESCRIPTION

PIN NO. COORDINATE

SYMBOL

DESCRIPTION

IO SYMBOL

1

2B

MEMCKE

1

IO8

SDRAM clock enable, Block 1

2

2C

MEMCKE

2

IO8

SDRAM clock enable, Block 2/GIO

16

3

1B

MEMCKE

3

IO8

SDRAM clock enable, Block 3/GIO

17

4

3D

MEMCS0Z

IO8

SDRAM chip select, Block 0

5

2D

MEMCS1Z

IO8

SDRAM chip select, Block 1

6

1C

MEMCS2Z

IO8

16-bit data mode : SDRAM chip select, Block 2

32-bit data mode : Control MEMD

15

to MEMD

8

of SDRAM

7

3E

DV

DD

≠

Power supply (+3.3 V)

8

1D

MEMCS3Z

IO8

16-bit data mode : SDRAM chip select, Block 3

32-bit data mode : Control MEMD

7

to MEMD

0

of SDRAM

9

2E

DGND

≠

Ground

10

4E

MEMD

0

IO12U

Data I/O for SDRAM/flash memory/external device

11

5E

MEMD

1

IO12U

12

4F

MEMD

2

IO12U

13

1E

DV

DD2

≠

Internal power supply (+2.5 V)

14

2F

MEMD

3

IO12U

Data I/O for SDRAM/flash memory/external device

15

3F

DGND

≠

Ground

16

5F

MEMD

4

IO12U

Data I/O for SDRAM/flash memory/external device

17

5G

MEMD

5

IO12U

18

4G

MEMD

6

IO12U

19

1F

DV

DD

≠

Power supply (+3.3 V)

20

2G

MEMD

7

IO12U

Data I/O for SDRAM/flash memory/external device

21

3G

DGND

≠

Ground

22

6G

MEMD

8

IO12U

Data I/O for SDRAM/flash memory/external device

23

5H

MEMD

9

IO12U

24

4H

MEMD

10

IO12U

25

1G

MEMD

11

IO12U

26

3H

DGND

≠

Ground

27

2H

MEMD

12

IO12U

Data I/O for SDRAM/flash memory/external device

28

6H

MEMD

13

IO12U

29

1H

DV

DD

≠

Power supply (+3.3 V)

30

5J

MEMD

14

IO12U

Data I/O for SDRAM/flash memory/external device

31

4J

MEMD

15

IO12U

32

2J

TEST1Z

IU

Test (Must be open.)

33

3J

DGND

≠

Ground

34

6J

MEMD

16

IO12U

Data I/O for SDRAM/external device/GIO

16

35

1J

TEST2Z

IU

Test (Must be open.)

36

6K

TEST3Z

IU

37

4K

MEMD

17

IO12U

Data I/O for SDRAM/external device/GIO

17

38

2K

MEMD

18

IO12U

Data I/O for SDRAM/external device/GIO

18

39

3K

MEMD

19

IO12U

Data I/O for SDRAM/external device/GIO

19

LR38666Y

5

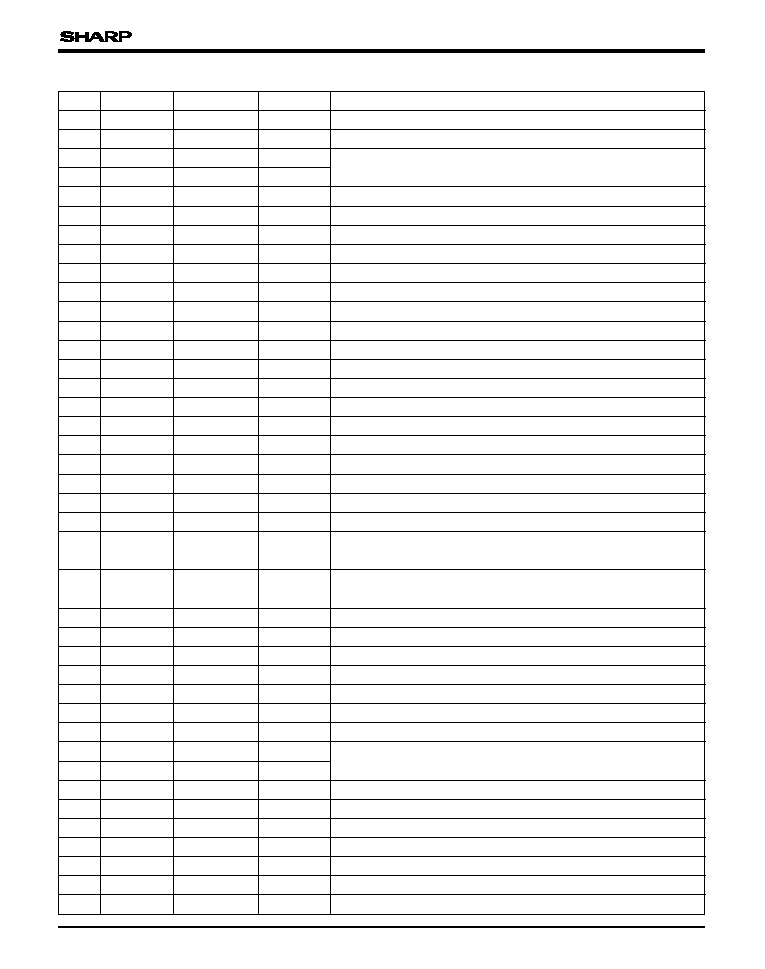

40

5K

DGND

≠

Ground

41

1K

MEMD

20

IO12U

Data I/O for SDRAM/external device/GIO

20

42

6L

TEST4Z

IU

Test (Must be open.)

43

5L

TEST5Z

IU

44

2L

DV

DD

≠

Power supply (+3.3 V)

45

1L

MEMD

21

IO12U

Data I/O for SDRAM/external device/GIO

21

46

3L

MEMD

22

IO12U

Data I/O for SDRAM/external device/GIO

22

47

1M

MEMD

23

IO12U

Data I/O for SDRAM/external device/GIO

23

48

4L

DGND

≠

Ground

49

4M

MEMD

24

IO12U

Data I/O for SDRAM/external device/GIO

24

50

2M

DV

DD2

≠

Internal power supply (+2.5 V)

51

3M

MEMD

25

IO12U

Data I/O for SDRAM/external device/GIO

25

52

1N

MEMD

26

IO12U

Data I/O for SDRAM/external device/GIO

26

53

4N

MEMD

27

IO12U

Data I/O for SDRAM/external device/GIO

27

54

2N

DGND

≠

Ground

55

3N

MEMD

28

IO12U

Data I/O for SDRAM/external device/GIO

28

56

1P

DV

DD

≠

Power supply (+3.3 V)

57

1R

MEMD

29

IO12U

Data I/O for SDRAM/external device/GIO

29

58

3P

MEMD

30

IO12U

Data I/O for SDRAM/external device/GIO

30

59

2P

MEMD

31

IO12U

Data I/O for SDRAM/external device/GIO

31

60

≠

NC

≠

Must be open.

61

2R

DGND

≠

Ground

62

3R

MEMLDQM

O12

16-bit data mode : Control MEMD

7

-MEMD

0

of SDRAM

32-bit data mode : Control MEMD

23

-MEMD

16

of SDRAM

63

2T

MEMUDQM

O12

16-bit data mode : Control MEMD

15

-MEMD

8

of SDRAM

32-bit data mode : Control MEMD

31

-MEMD

24

of SDRAM

64

4P

MEMRASZ

O12

SDRAM row address strobe

65

4R

MEMCASZ

O12

SDRAM column address strobe

66

3T

DV

DD

≠

Power supply (+3.3 V)

67

5P

DGND

≠

Ground

68

4T

MEMCLK

IO12

SDRAM clock output (49.0908 MHz : double of C24MI input)

69

5R

DV

DD2

≠

Internal power supply (+2.5 V)

70

5N

MEMWEZ

O12

SDRAM write enable

71

5M

MEMA

0

O12

Address for SDRAM/flash memory/external device

72

6N

MEMA

1

O12

73

6P

DGND

≠

Ground

74

5T

MEMA

2

O12

Address for SDRAM/flash memory/external device

75

6R

DV

DD

≠

Power supply (+3.3 V)

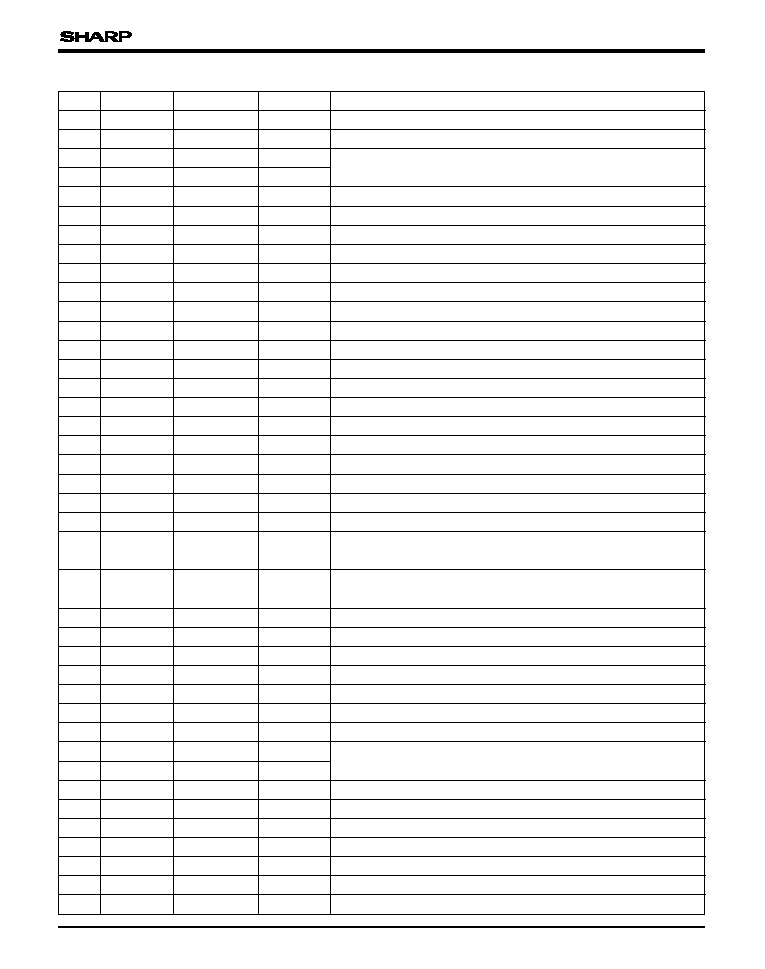

PIN NO. COORDINATE

SYMBOL

DESCRIPTION

IO SYMBOL

76

6M

MEMA

3

O12

Address for SDRAM/flash memory/external device

77

7M

MEMA

4

O12

Address for SDRAM/flash memory/external device

79

7N

DGND

≠

Ground

78

6T

MEMA

5

O12

Address for SDRAM/flash memory/external device