| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LRS1342 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Data Sheet

1

LRS1341/LRS1342

Data Sheet

Stacked Chip

16M Flash Memory and 2M SRAM

FEATURES

∑ Flash Memory and SRAM

∑ Stacked Die Chip Scale Package

∑ 72-ball CSP (FBGA072-P-0811) plastic package

∑ Power supply: 2.7 V to 3.6 V

∑ Operating temperature: -25∞C to +85∞C

∑ Flash Memory

≠ Access time (MAX.): 100 ns

≠ Operating current (MAX.):

The current for F-V

CC

pin

≠ Read: 25 mA (t

CYCLE

= 200 ns)

≠ Word write: 17 mA

≠ Block erase: 17 mA

≠ Deep power down current (the current for

F-V

CC

pin): 10 µA (MAX. F-CE

F-V

CC

- 0.2 V,

F-RP

-0.2 V, F-V

PP

0.2 V)

≠ Optimized array blocking architecture

≠ Two 4K-word boot blocks

≠ Six 4K-word parameter blocks

≠ Thirty-one 32K-word main blocks

≠ Top/Bottom boot location versions

≠ Extended cycling capability

≠ 100,000 block erase cycles

≠ Enhanced automated suspend options

≠ Word write suspend to read

≠ Block erase suspend to word write

≠ Block erase suspend to read

∑ SRAM

≠ Access time (MAX.): 85 ns

≠ Operating current (MAX.):

≠ 45 mA

≠ 8 mA (t

RC

, t

WC

= 1 µs)

≠ Standby current: 45 µA (MAX.)

≠ Data retention current: 35 µA (MAX.)

DESCRIPTION

The LRS1341/LRS1342 is a combination memory

organized as 1,048,576 ◊ 16-bit flash memory and

131,072 ◊ 16-bit static RAM in one package.

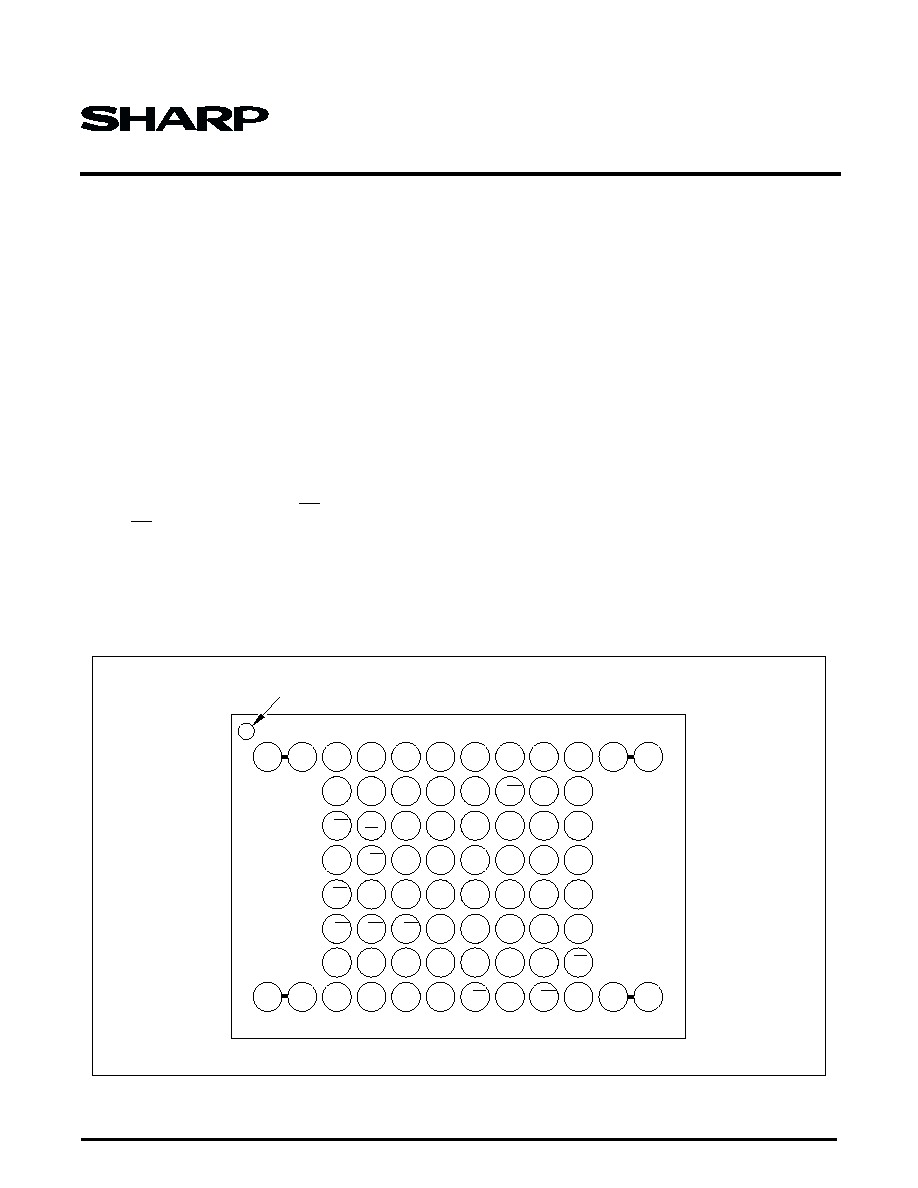

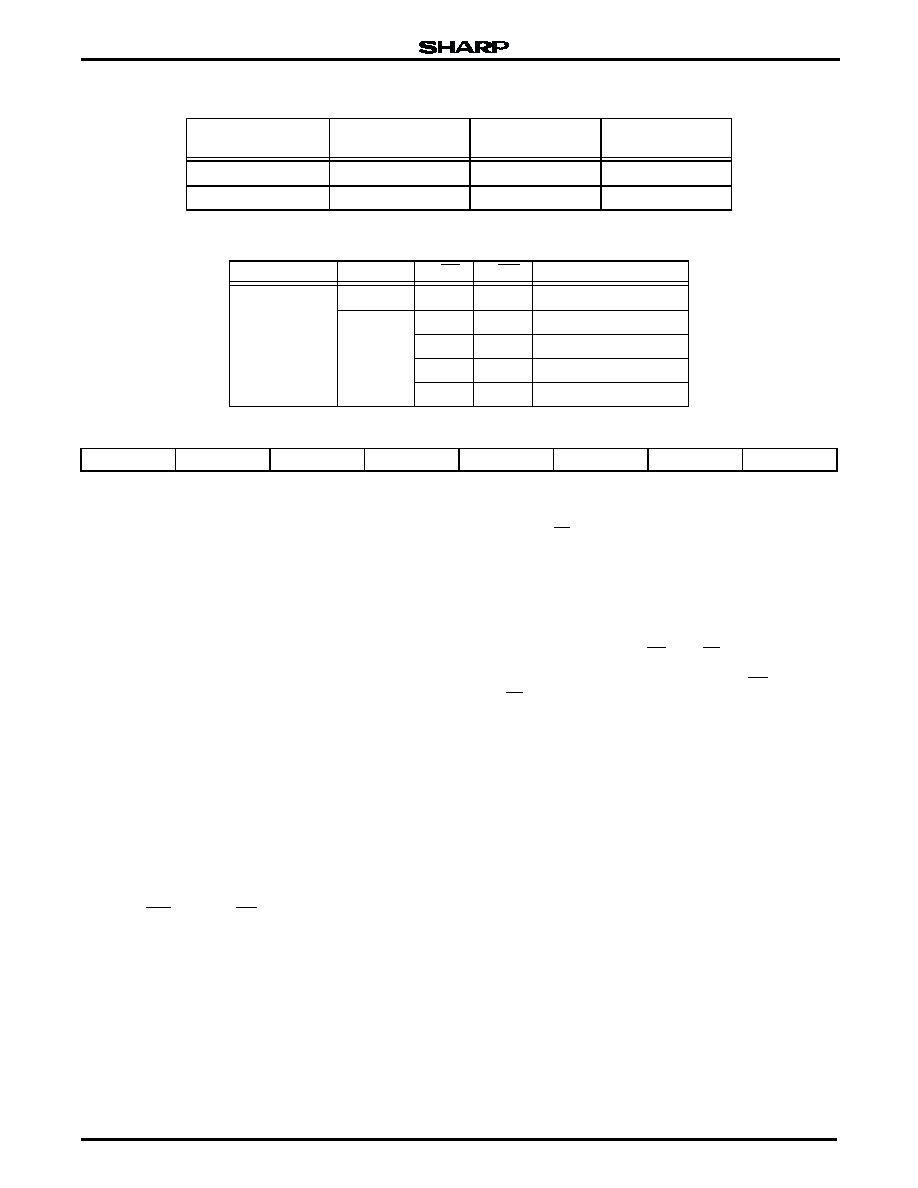

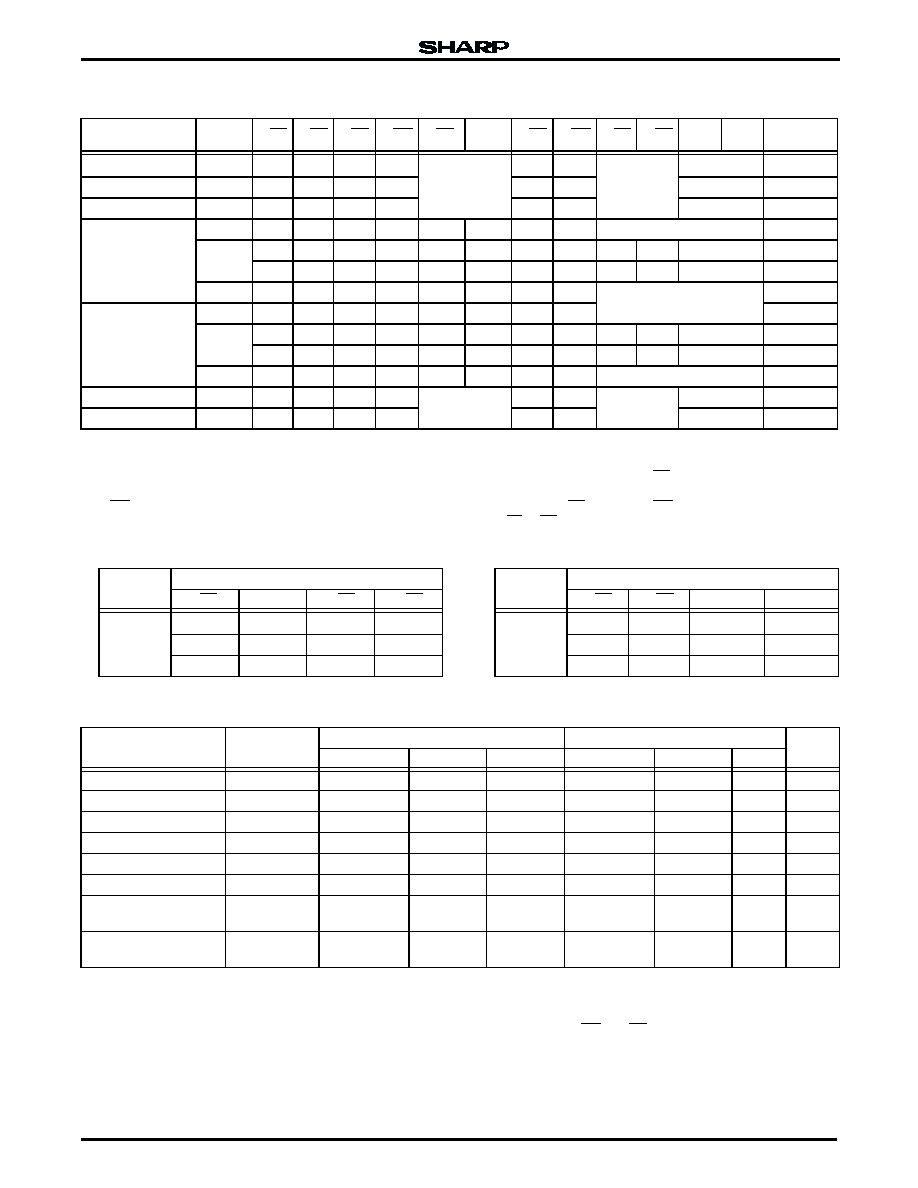

PIN CONFIGURATION

Figure 1. LRS1341/LRS1342 Pin Configuration

A

INDEX

A

11

A

15

NC

NC

NC

A

14

A

9

1

2

3

4

5

6

7

A

16

DQ

15

DQ

14

S-V

CC

A

8

A

10

T

1

T

3

DQ

13

DQ

12

GND

T

4

F-WE

F-RY/

BY

F-RP

T

2

F-WP

F-V

PP

F-A

19

DQ

11

T

5

B

C

D

E

F

S-LB S-UB S-OE

NC

DQ

9

8

DQ

6

DQ

10

DQ

8

F-A

18

F-A

17

A

7

A

6

A

3

A

2

NC

NC

G

H

NC

A

5

A

4

A

0

F-OE

F-CE

GND

NC

NC

A

12

A

13

9

10

S-WE

DQ

4

S-CE

2

DQ

2

DQ

0

11

A

1

NC

NC

NC

12

DQ

7

DQ

5

F-V

CC

DQ

3

DQ

1

S-CE

1

NC

LRS1342-1

TOP VIEW

72-BALL FBGA

NOTE: Two NC pins at the corner are connected.

GND

LRS1341/LRS1342

Stacked Chip (16M Flash & 2M SRAM)

2

Data Sheet

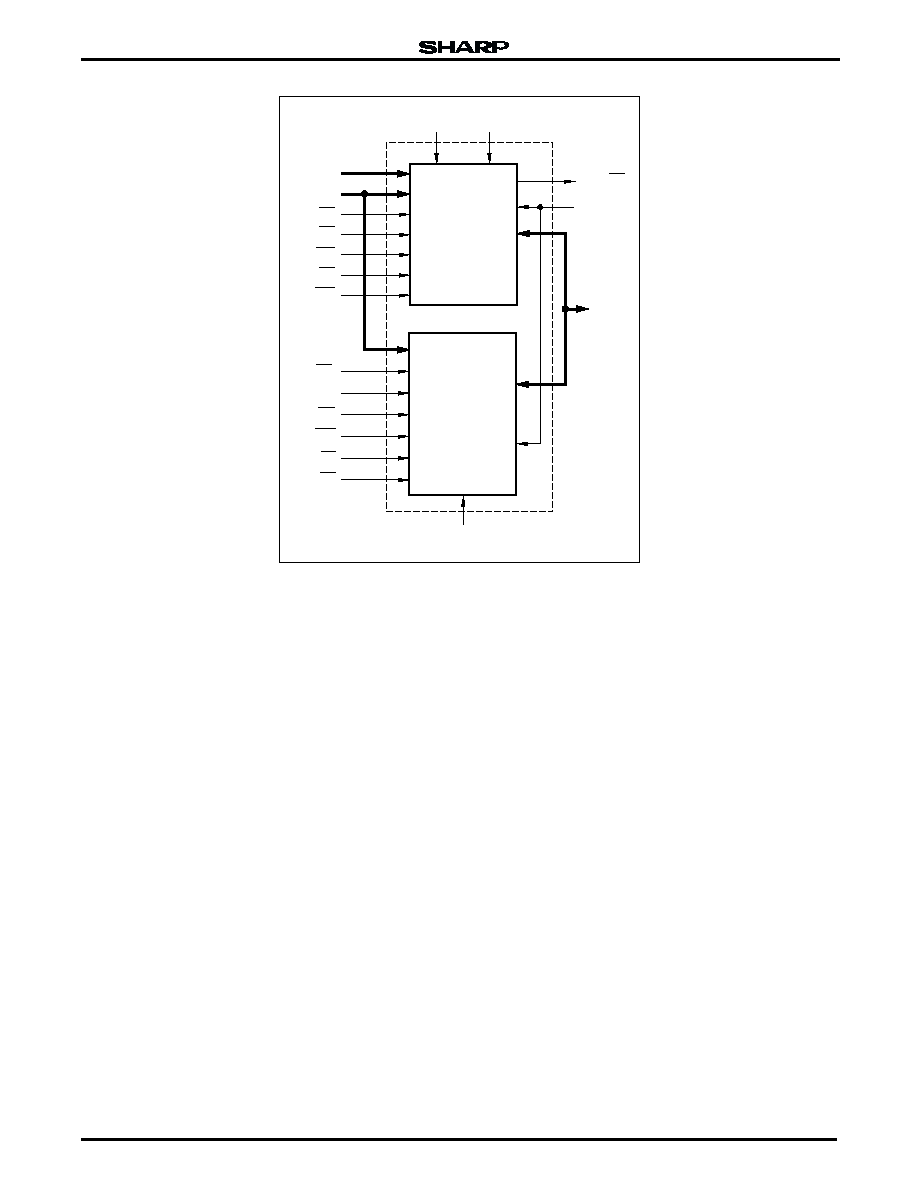

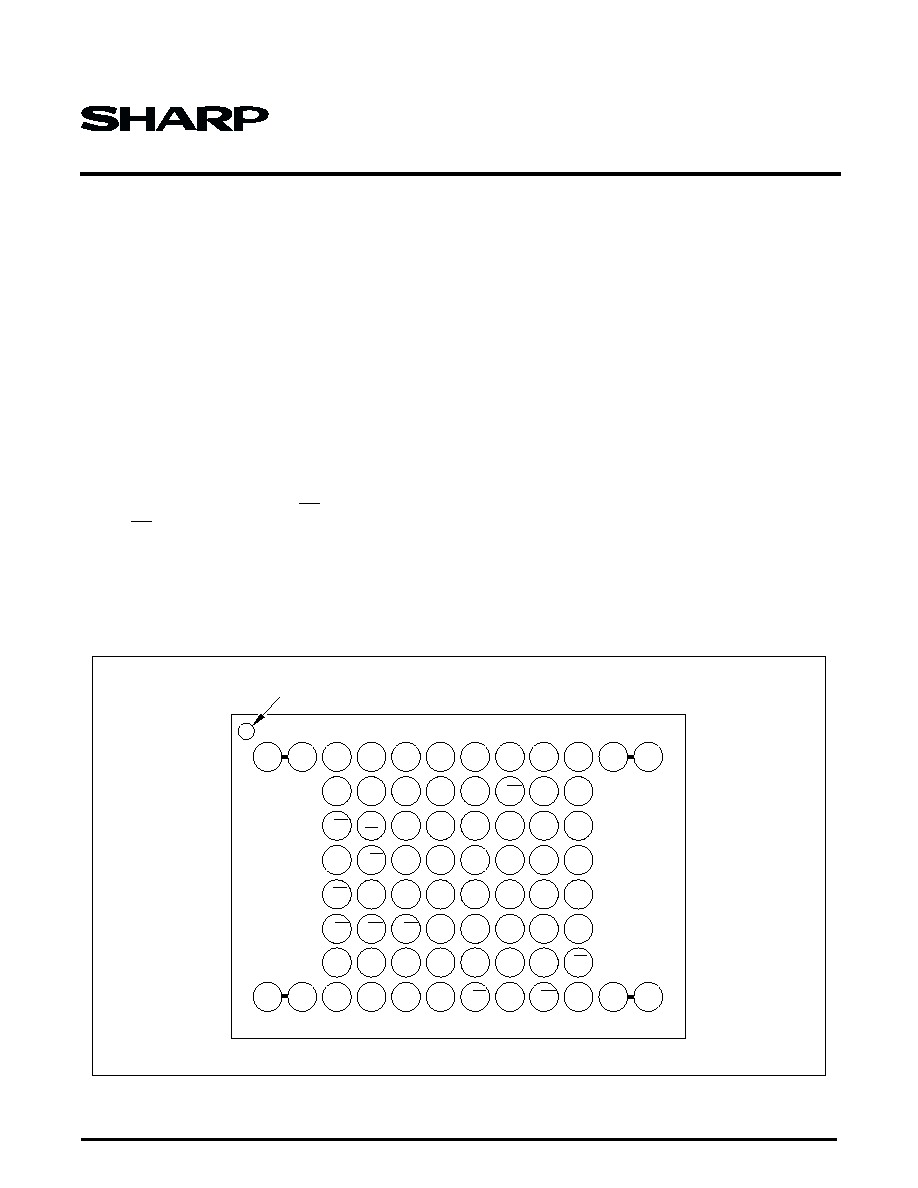

Figure 2. LRS1341/LRS1342 Block Diagram

LRS1342-2

16M (x16) BIT

FLASH MEMORY

2M (x16) BIT

SRAM

F-A

17

to

F-A

19

F-RY/BY

GND

F-V

CC

F-V

PP

S-V

CC

DQ

0

to

DQ

15

F-CE

F-OE

F-WE

F-RP

F-WP

A

0

to A

16

S-CE

1

S-CE

2

S-OE

S-WE

S-LB

S-UB

Stacked Chip (16M Flash & 2M SRAM)

LRS1341/LRS1342

Data Sheet

3

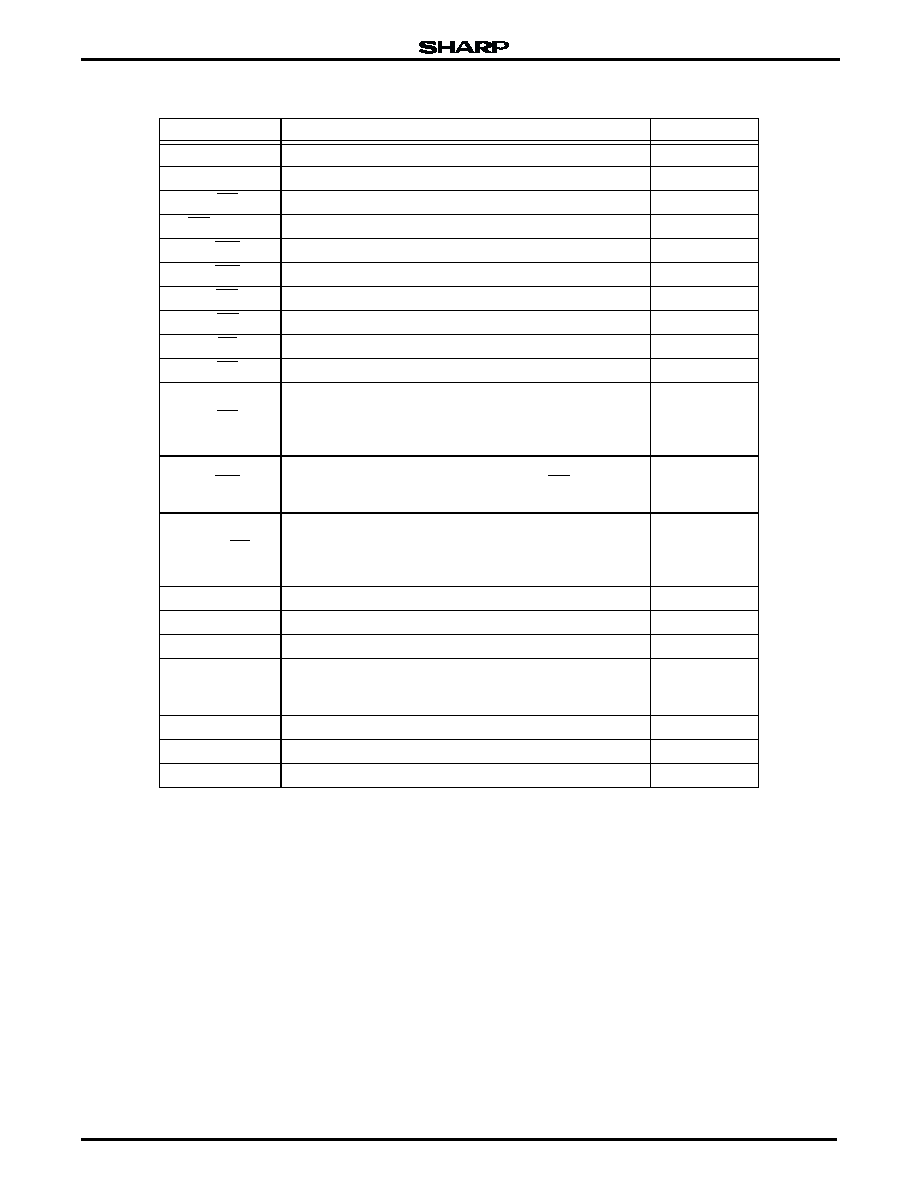

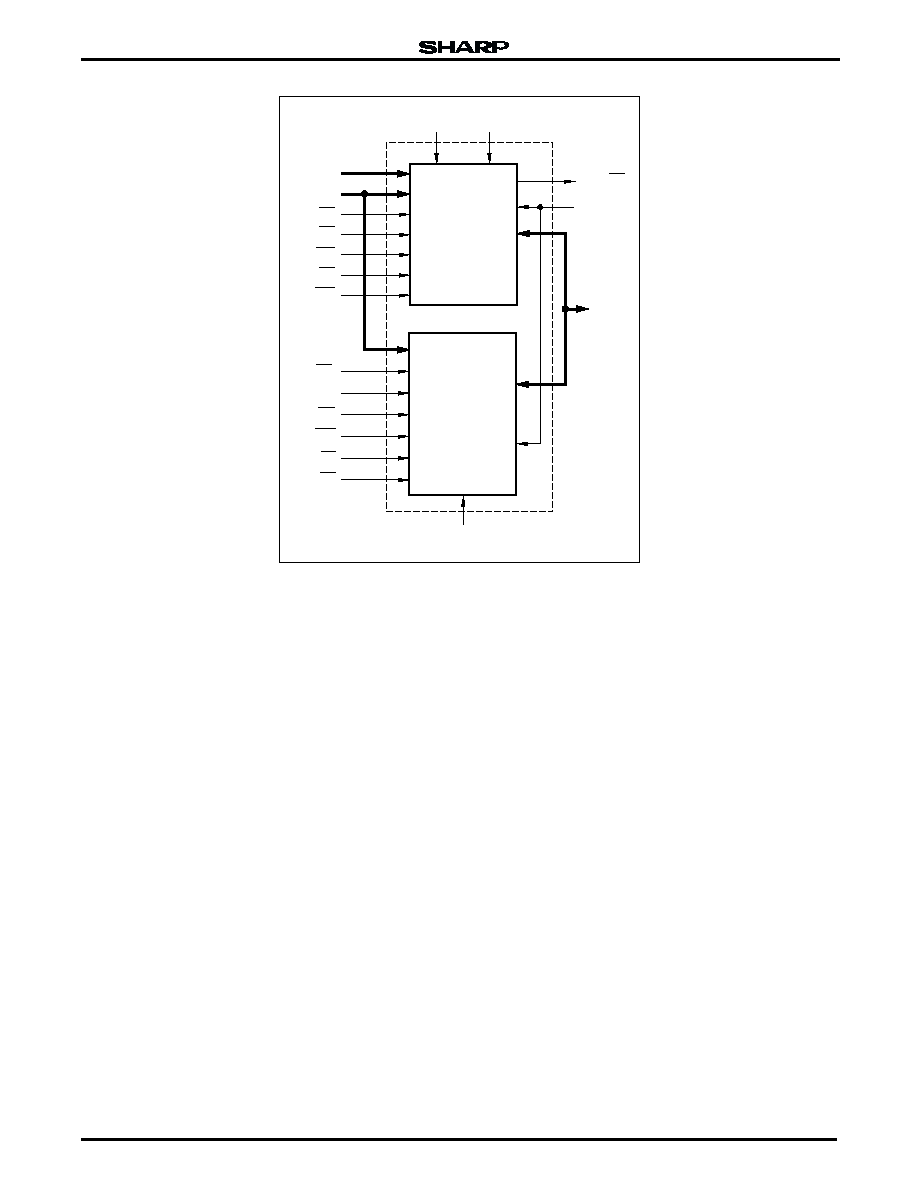

Table 1. Pin Descriptions

PIN

DESCRIPTION

TYPE

A

0

to A

16

Address Inputs (Common)

Input

F-A

17

to F-A

19

Address Inputs (Flash)

Input

F-CE

Chip Enable Input (Flash)

Input

S-CE

1

, S-CE

2

Chip Enable Inputs (SRAM)

Input

F-WE

Write Enable Input (Flash)

Input

S-WE

Write Enable Input (SRAM)

Input

F-OE

Output Enable Input (Flash)

Input

S-OE

Output Enable Input (SRAM)

Input

S-LB

SRAM Byte Enable Input (DQ

0

to DQ

7

)

Input

S-UB

SRAM Byte Enable Input (DQ

8

to DQ

15

)

Input

F-RP

Reset/Power Down (Flash)

Block erase and Word Write: V

IH

or V

HH

Read: V

IH

or V

HH

Reset/Power Down: V

IL

Input

F-WP

Write Protect (Flash)

Two Boot Blocks Locked: V

IL

(with F-RP = V

HH

Erase of Write can operate to all blocks)

Input

F-RY/BY

Ready/Busy (Flash)

During an Erase or Write operation: V

OL

Block Erase and Word Write Suspend: HIGH-Z

Deep Power Down: V

OH

Output

DQ

0

to DQ

15

Data Input/Outputs (Common)

Input/Output

F-V

CC

Power Supply (Flash)

Power

S-V

CC

Power Supply (SRAM)

Power

F-V

PP

Write, Erase Power Supply (Flash)

Block Erase and Word Write: F-V

PP

= V

PPLK

All Blocks Locked: F-V

PP

< V

PPLK

Power

GND

Ground (Common)

Power

NC

No Connection

--

T

1

to T

5

Test Pins (Should be Open)

--

LRS1341/LRS1342

Stacked Chip (16M Flash & 2M SRAM)

4

Data Sheet

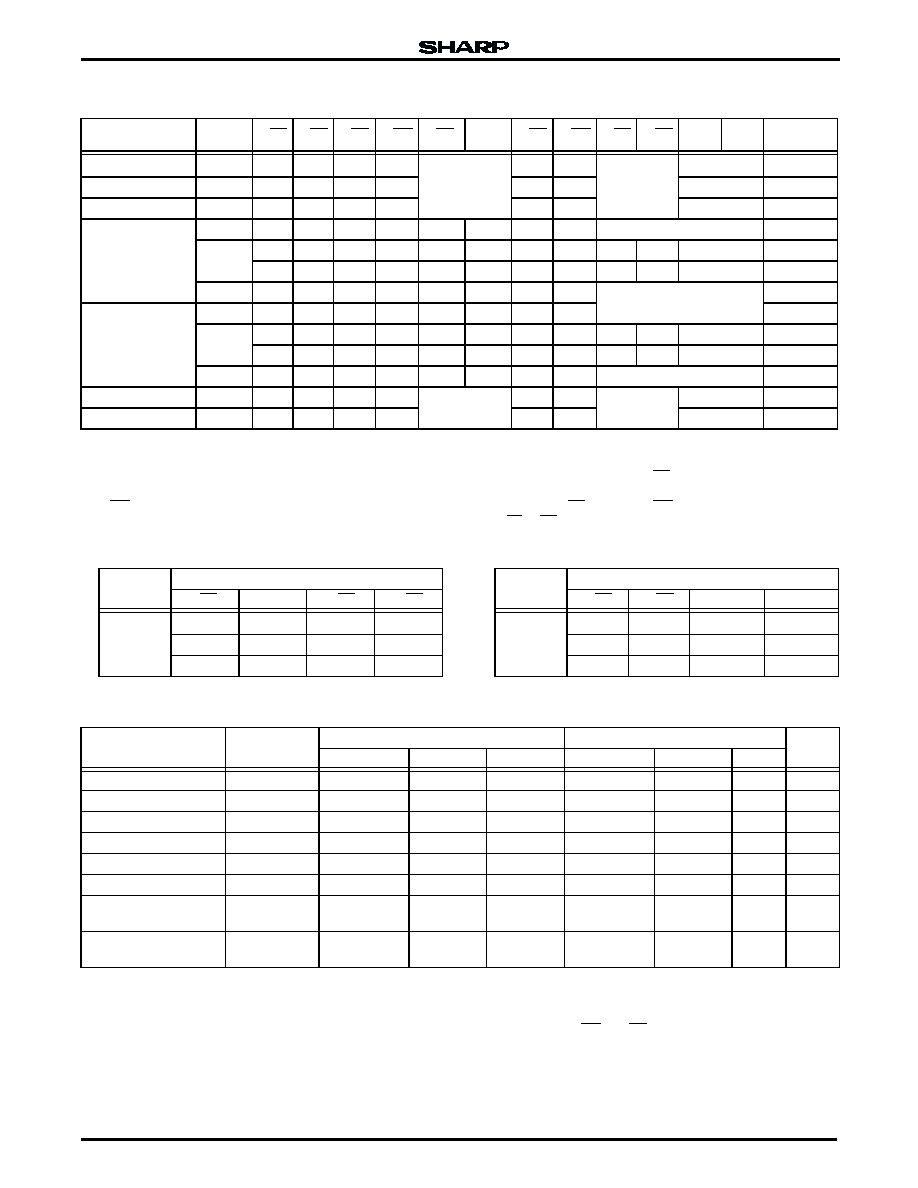

NOTES:

1. L = V

IL

, H = V

IH

, X = H or L. Refer to DC Characteristics.

2. Refer to the `Flash Memory Command Definition' section for valid

D

IN

during a write operation.

3. F-WP set to V

IL

or V

IH

.

4. SRAM standby mode. See Table 2a.

5. Command writes involving block erase or word write are reliably

executed when F-V

PP

= V

PPH

and F-V

CC

= 2.7 V to 3.6 V. Block

erase or word write with V

IH

< RP < V

HH

produce spurious results

and should not be attempted.

6. Never hold F-OE LOW and F-WE LOW at the same time.

7. S-LB, S-UB control mode. See Table 2b.

NOTES:

1. Commands other than those shown in table are reserved by

SHARP for future device implementations and should not be used.

2. BUS operations are defined in Table 2.

3. XA = Any valid address within the device;

IA = Identifier code address;

BA = Address within the block being erased;

WA = Address of memory location to be written;

SRD = Data read from status register, see Table 6;

WD = Data to be written at location WA. Data is latched on the

rising edge of F-WE or F-CE (whichever goes high first);

ID = Data read from identifier codes.

4. See Table 4 for Identifier Codes.

5. See Table 5 for Write Protection Alternatives.

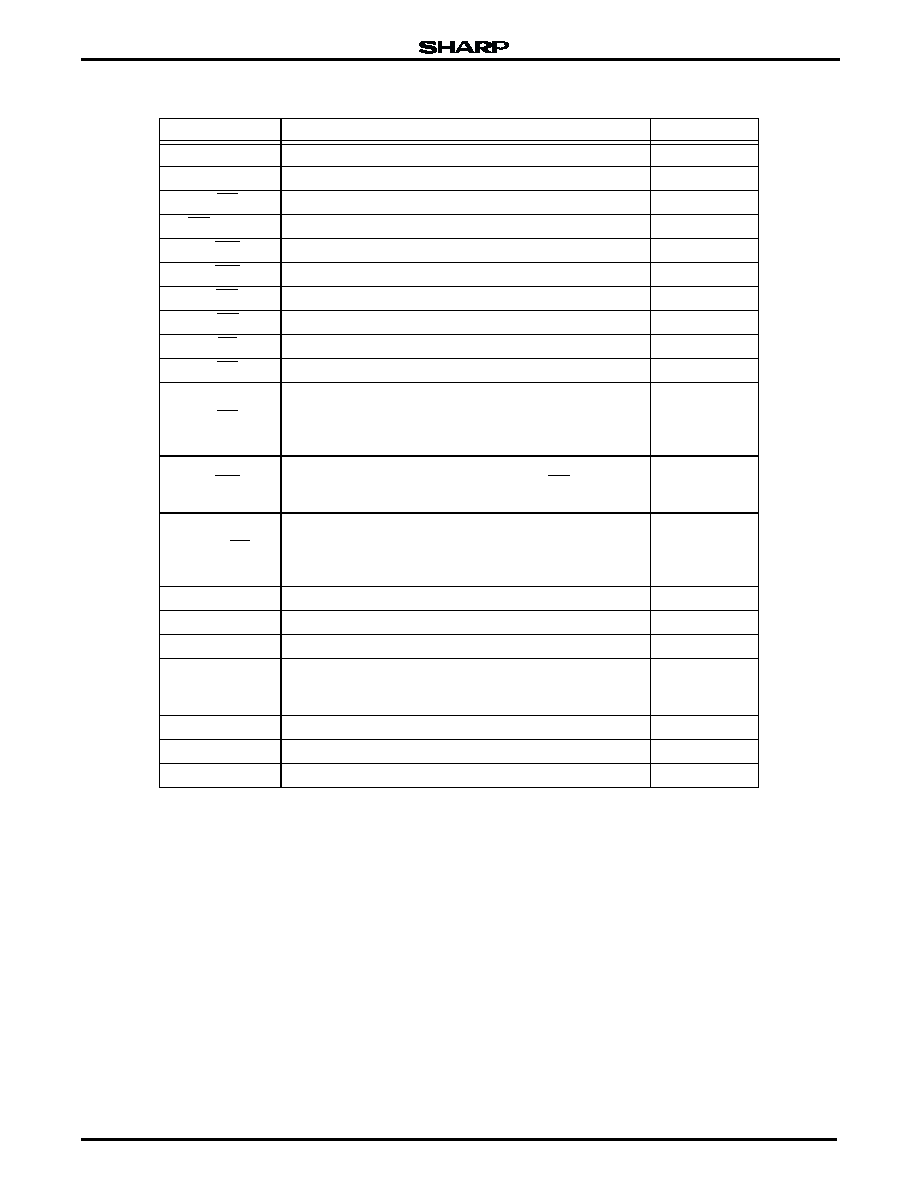

Table 2. Truth Table

1

FLASH

SRAM

F-CE

F-RP

F-OE

F-WE

S-CE

1

S-CE

2

S-OE

S-WE

S-LB

S-UB

DQ

0

-

DQ-7

DQ

8

-

DQ

15

NOTES

Read

Standby

L

H

L

H

See Note 4

X

X

See Note 4

D

OUT

2, 3

Output Disable

Standby

L

H

H

H

X

X

HIGH-Z

3

Write

Standby

L

H

H

L

X

X

D

IN

2, 3, 5, 6

Standby

Read

H

H

X

X

L

H

L

H

See Note 7

Output

Disable

H

H

X

X

L

H

H

H

X

X

HIGH-Z

H

H

X

X

L

H

X

X

H

H

HIGH-Z

Write

H

H

X

X

L

H

L

L

See Note 7

Reset/Power Down

Read

X

L

X

X

L

H

L

H

Output

Disable

X

L

X

X

L

H

H

H

X

X

HIGH-Z

X

L

X

X

L

H

X

X

H

H

HIGH-Z

Write

X

L

X

X

L

H

L

L

See Note 7

Standby

Standby

H

H

X

X

See Note 4

X

X

See Note 4

HIGH-Z

3

Reset/Power Down

Standby

X

L

X

X

X

X

HIGH-Z

3

Table 2a.

MODE

PINS

S-CE

1

S-CE

2

S-LB

S-UB

Standby

(SRAM)

H

X

X

X

X

L

X

X

X

X

H

H

Table 2b.

MODE

(SRAM)

PINS

S-LB

S-UB

DQ

0

- DQ

7

DQ

8

- DQ

15

Read/Write

L

L

D

OUT

/D

IN

D

OUT

/D

IN

L

H

D

OUT

/D

IN

HIGH-Z

H

L

HIGH-Z

D

OUT

/D

IN

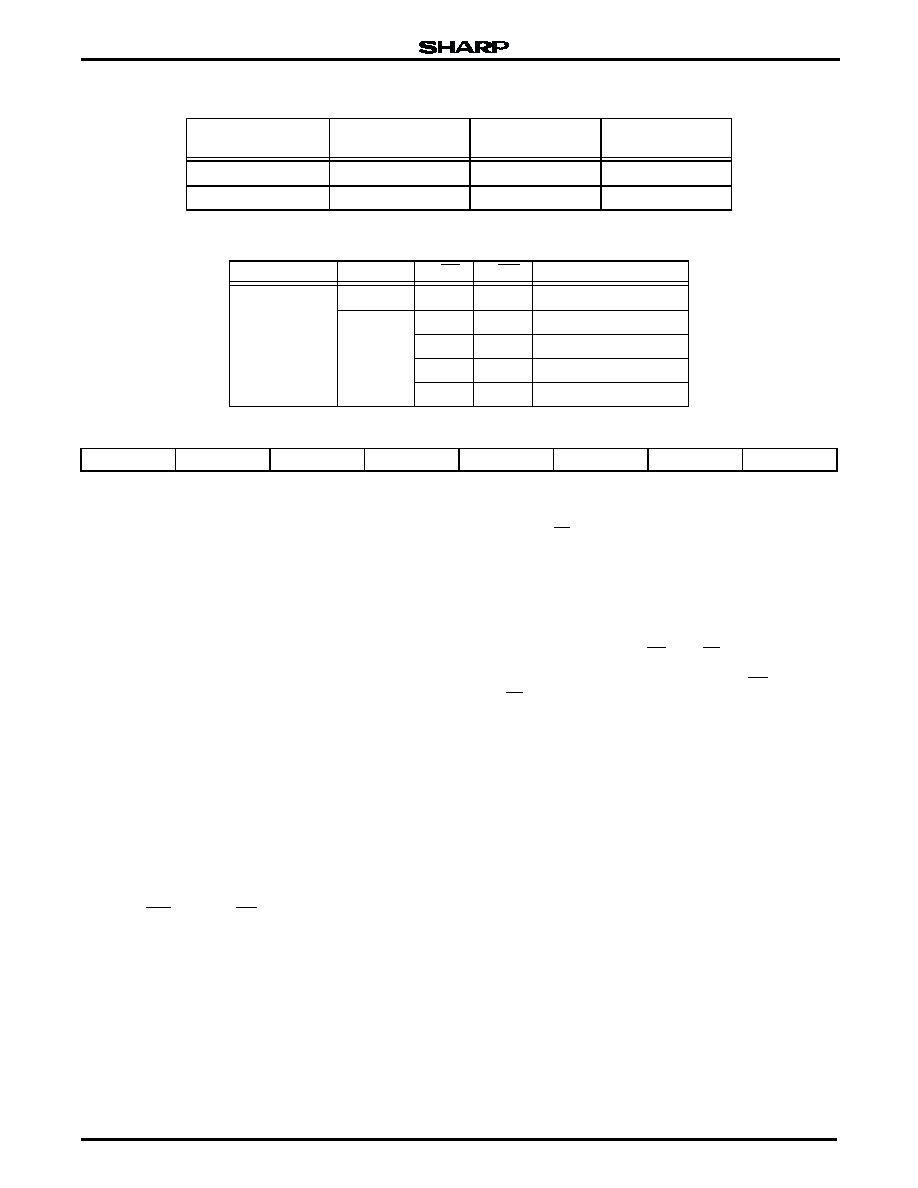

Table 3. Command Definition for Flash Memory

1

COMMAND

BUS CYCLES

REQUIRED

FIRST BUS CYCLE

SECOND BUS CYCLE

NOTES

OPERATION

2

ADDRESS

3

DATA

3

OPERATION

2

ADDRESS

3

DATA

3

Read Array/Reset

1

Write

XA

FFH

Read Identifier Codes

2

Write

XA

90H

Read

IA

ID

4

Read Status Register

2

Write

XA

70H

Read

XA

SRD

Clear Status Register

1

Write

XA

50H

Block Erase

2

Write

BA

20H

Write

BA

D0H

5

Word Write

2

Write

WA

40H or 10H

Write

WA

WD

5

Block Erase and Word

Write Suspend

1

Write

XA

B0H

5

Block Erase and Word

Write Resume

1

Write

XA

D0H

5

Stacked Chip (16M Flash & 2M SRAM)

LRS1341/LRS1342

Data Sheet

5

SR.7 = Write State Machine Status (WSMS)

1 = Ready

0 = Busy

SR.6 = Erase Suspend Status (ESS)

1 = Block Erase Suspended

0 = Block Erase in Progress/Completed

SR.5 = Erase Status (ES)

1 = Error in Block Erasure

0 = Successful Block Erase

SR.4 = Word Write Status (WWS)

1 = Error in Word Write

0 = Successful Word Write

SR.3 = V

PP

Status (VPPS)

1 = F-V

PP

LOW Detect, Operation Abort

0 = F-V

PP

Okay

SR.2 = Word Write Suspend Status (WWSS)

1 = Word Write Suspended

0 = Word Write in Progress/Completed

SR.1 = Device Protect Status (DPS)

1 = F-WP and/or F-RP Lock Detected,

Operation Abort

0 = Unlock

SR.0 = Reserved for future enhancements (R)

NOTES:

1. Check RY/BY or SR.7 to determine block erase or word write

completion. SR.6 - SR.0 are invalid while SR.7 = 0.

2. If both SR.5 and SR.4 are `1's after a block erase attempt, an

improper command sequence was entered.

3. SR.3 does not provide a continuous indication of F-V

PP

level. The

WSM interrogates and indicates the F-V

PP

level only after Block

Erase or Word Write command sequences. SR.3 is not guaranteed

to report accurate feedback only when F-V

PP

V

PPH1

, V

PPH2

.

4. The WSM interrogates the F-WP and F-RP only after Block Erase

or Word Write command sequences. It informs the system,

depending on the attempted operation, if the F-WP is not V

IH

or

F-RP is not V

HH

.

5. SR.0 is reserved for future use and should be masked out when

polling the status register.

Table 4. Identifier Codes

CODES

ADDRESS

(A

0

- A

18

)

LRS1341 DATA

(DQ

0

- DQ

7

)

LRS1342 DATA

(DQ

0

- DQ

7

)

Manufacture Code

00000H

B0H

B0H

Device Code

00001H

48H

49H

Table 5. Write Protection Alternatives

OPERATION

F-V

PP

F-RP

F-WP

EFFECT

Block Erase or

Word Write

V

IL

X

X

All blocks locked

> V

PPLK

V

IL

X

All blocks locked

V

HH

X

All blocks unlocked

V

IH

V

IL

Two boot blocks locked

V

IH

V

IH

All blocks unlocked

Table 6. Status Register Definition

WSMS

ESS

ES

WWS

VPPS

WWSS

DPS

R

7

6

5

4

3

2

1

0