In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP devices shown in

catalogs, data books, etc. Contact SHARP in order to obtain the latest device specification sheets before using any SHARP device.

1

DESCRIPTION

The LZ21N3 is a 1/2-type (8.08 mm) solid-state

image sensor that consists of PN photo-diodes

and CCDs (charge-coupled devices). With

approximately 2 140 000 pixels (1 704 horizontal x

1 255 vertical), the sensor provides a stable high-

resolution color image.

FEATURES

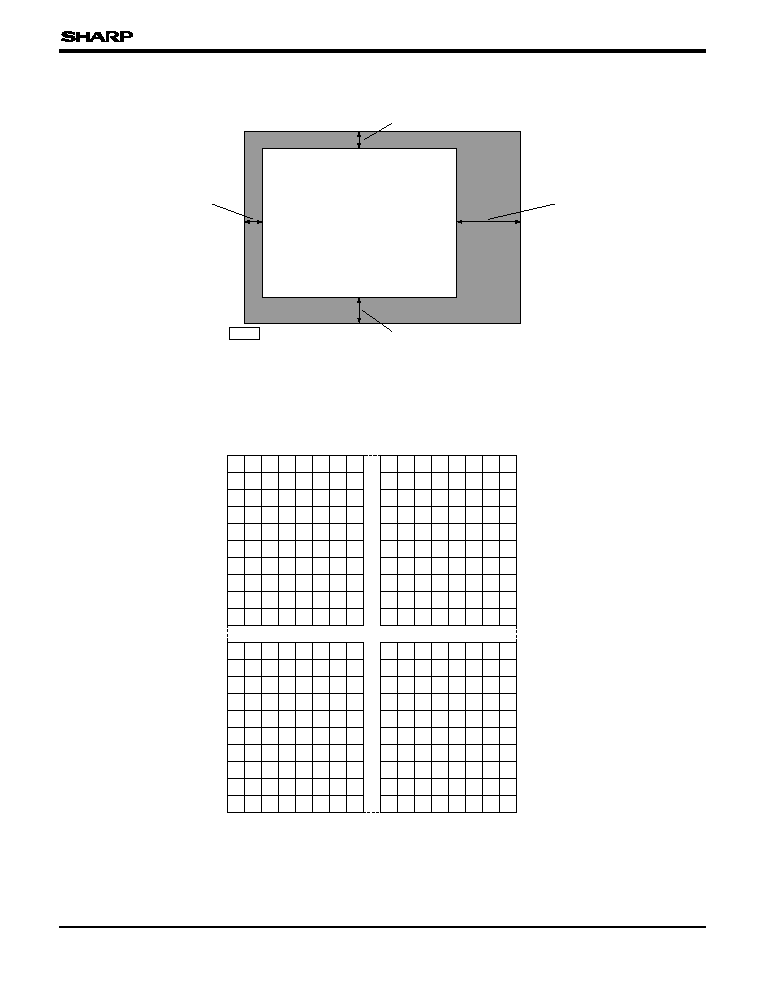

∑ Optical size : 8.08 mm (aspect ratio 4 : 3)

∑ Interline scan format

∑ Square pixel

∑ Number of effective pixels : 1 650 (H) x 1 250 (V)

∑ Number of optical black pixels

≠ Horizontal : 2 front and 52 rear

≠ Vertical : 3 front and 2 rear

∑ Number of dummy bits

≠ Horizontal : 28

≠ Vertical : 2

∑ Pixel pitch : 3.95 µm (H) x 3.95 µm (V)

∑ Mg, G, Cy, and Ye complementary color mosaic

filters

∑ Supports monitoring mode

∑ Low fixed-pattern noise and lag

∑ No burn-in and no image distortion

∑ Blooming suppression structure

∑ Built-in output amplifier

∑ Built-in overflow drain voltage circuit and reset

gate voltage circuit

∑ Variable electronic shutter

∑ Package :

20-pin half-pitch WDIP [Plastic]

(WDIP020-P-0500)

Row space : 12.20 mm

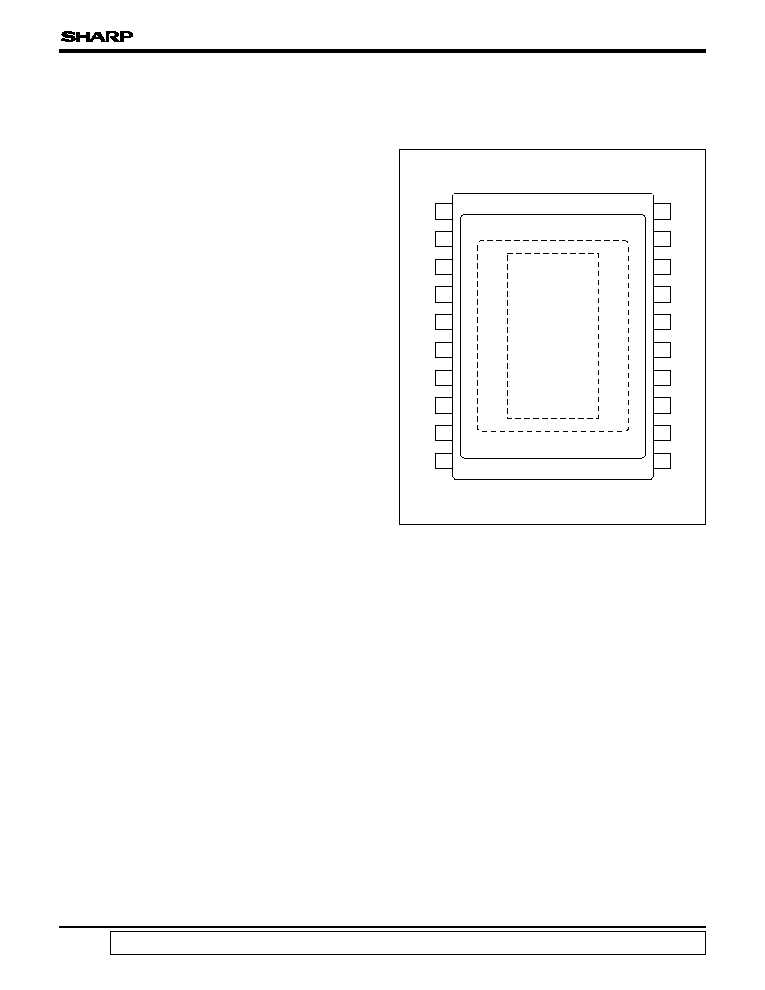

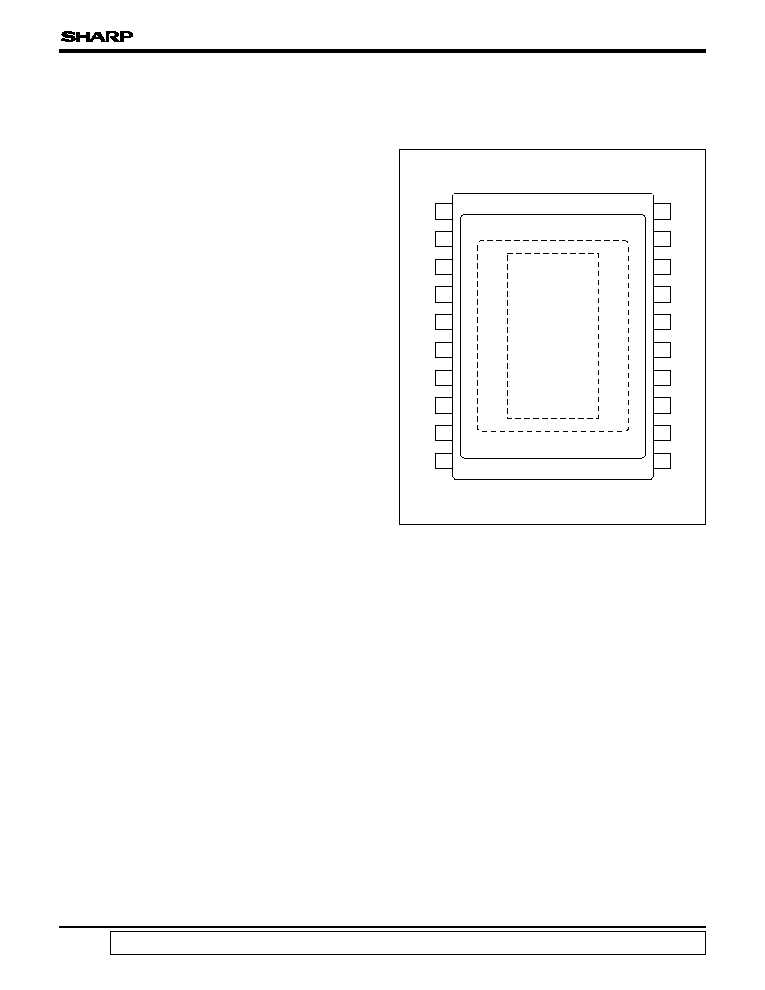

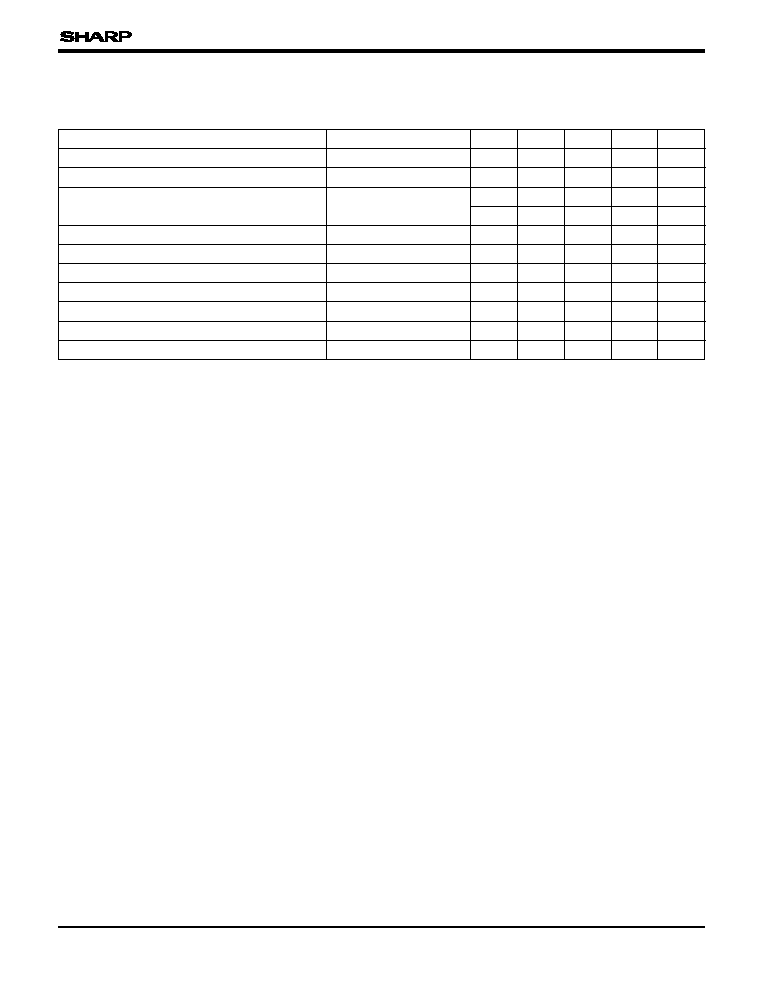

PIN CONNECTIONS

PRECAUTIONS

∑ The exit pupil position of lens should be 30 to 50

mm from the top surface of the CCD.

∑ Refer to "PRECAUTIONS FOR CCD AREA

SENSORS" for details.

LZ21N3

1/2-type Interline Color CCD Area

Sensor with 2 140 k Pixels

LZ21N3

1

OD

2

GND

3

OFD

4

PW

5

ÿ

RS

6

NC

1

7

NC

2

8

ÿ

H1

9

NC

3

10

ÿ

H2

20

19

18

17

16

15

14

OS

GND

NC

5

NC

4

ÿ

V1A

ÿ

V1B

ÿ

V2

13 ÿ

V3A

12 ÿ

V3B

11 ÿ

V4

20-PIN HALF-PITCH WDIP

TOP VIEW

(WDIP020-P-0500)

2

LZ21N3

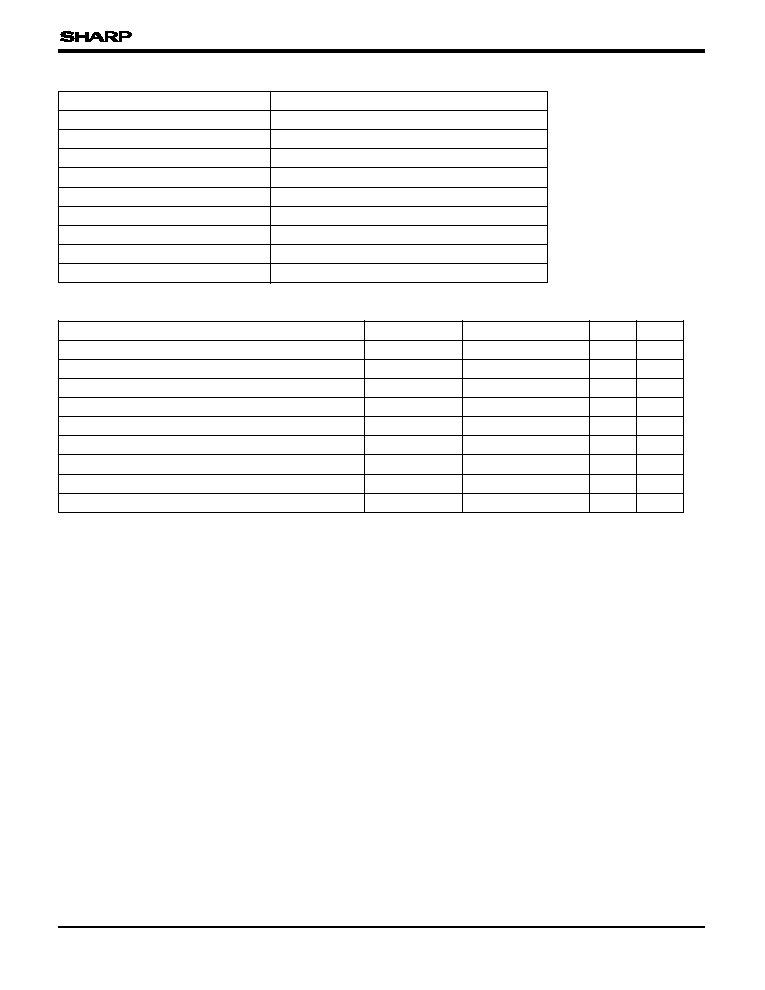

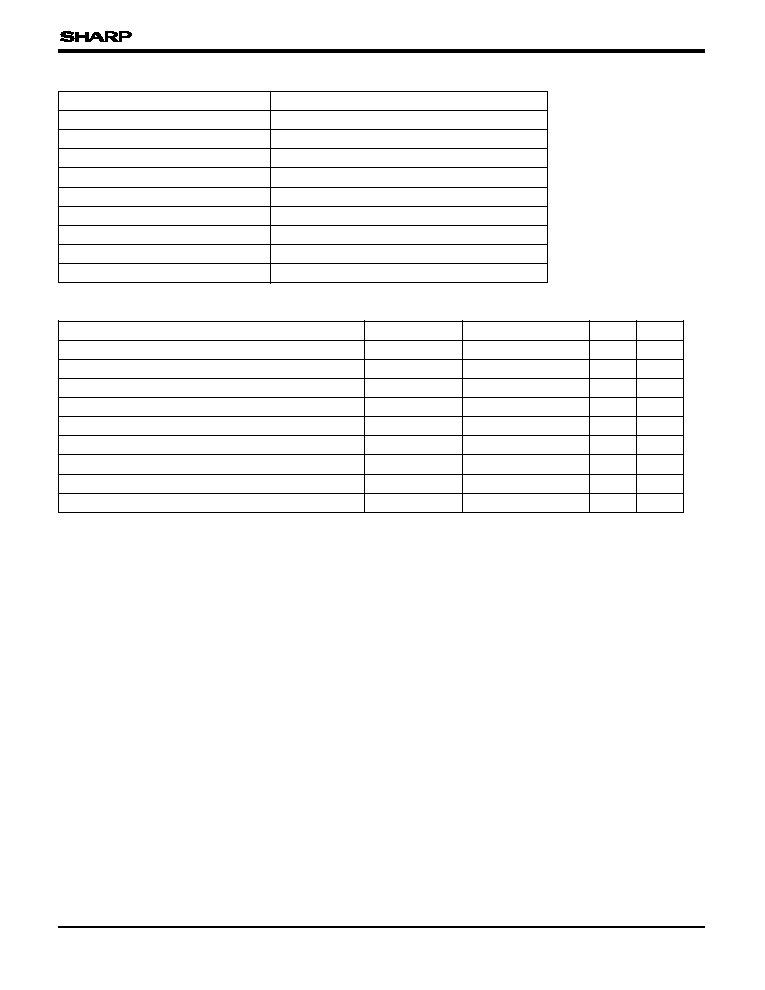

PIN DESCRIPTION

SYMBOL

PIN NAME

OD

Output transistor drain

OS

Output signals

ÿ

RS

Reset transistor clock

ÿ

V1A

, ÿ

V1B

, ÿ

V2

, ÿ

V3A

, ÿ

V3B

, ÿ

V4

Vertical shift register clock

ÿ

H1

, ÿ

H2

Horizontal shift register clock

PW

P-well

GND

Ground

NC

1

, NC

2

, NC

3

, NC

4

, NC

5

No connection

Overflow drain

OFD

ABSOLUTE MAXIMUM RATINGS

(T

A

= +25 ∞C)

PARAMETER

SYMBOL

RATING

UNIT

Output transistor drain voltage

V

OD

0 to +15

V

Reset gate clock voltage

V

ÿRS

Internal output

V

Vertical shift register clock voltage

V

ÿV

V

PW

to +15

V

Horizontal shift register clock voltage

V

ÿH

≠0.3 to +12

V

Voltage difference between P-well and vertical clock

V

PW

-V

ÿV

≠24 to 0

V

Storage temperature

T

STG

≠40 to +85

∞C

Ambient operating temperature

T

OPR

≠20 to +70

∞C

2

NOTE

NOTES :

1. Do not connect to DC voltage directly. When OFD is connected to GND, connect V

OD

to GND. Overflow drain clock is

applied below 22 Vp-p.

2. Do not connect to DC voltage directly. When ÿ

RS

is connected to GND, connect V

OD

to GND. Reset gate clock is

applied below 8 Vp-p.

3. When clock width is below 10 µs, and clock duty factor is below 0.1%, voltage difference between vertical clocks will be

below 22 V.

1

V

Internal output

V

OFD

Overflow drain voltage

3

V

0 to +15

V

ÿV

-V

ÿV

Voltage difference between vertical clocks

3

LZ21N3

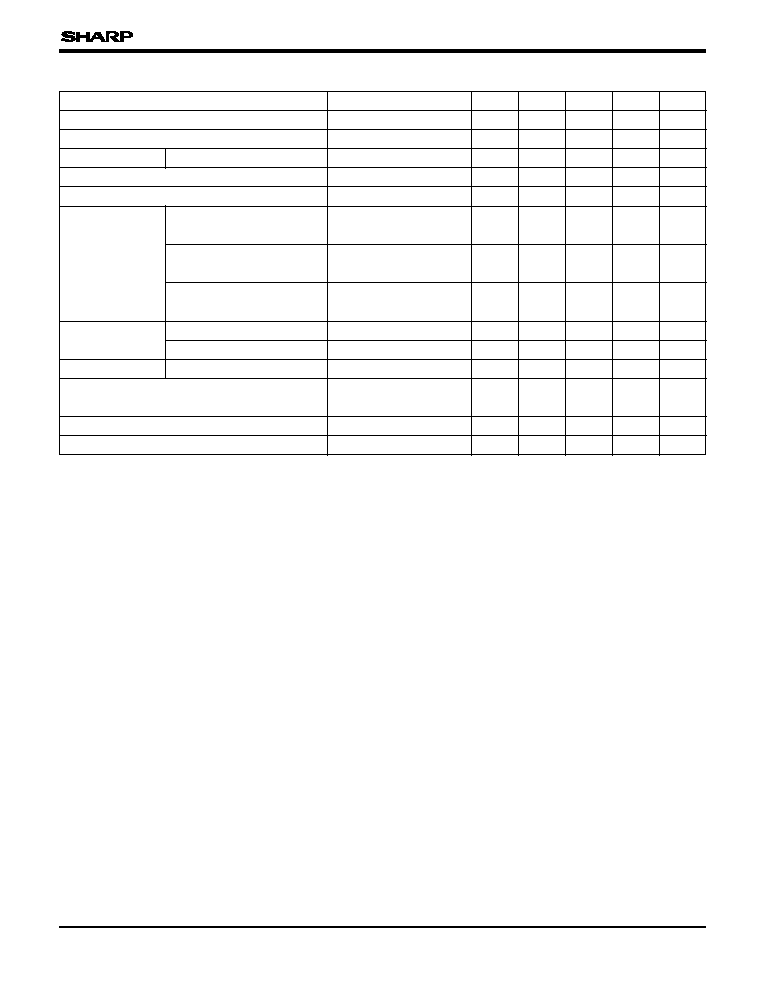

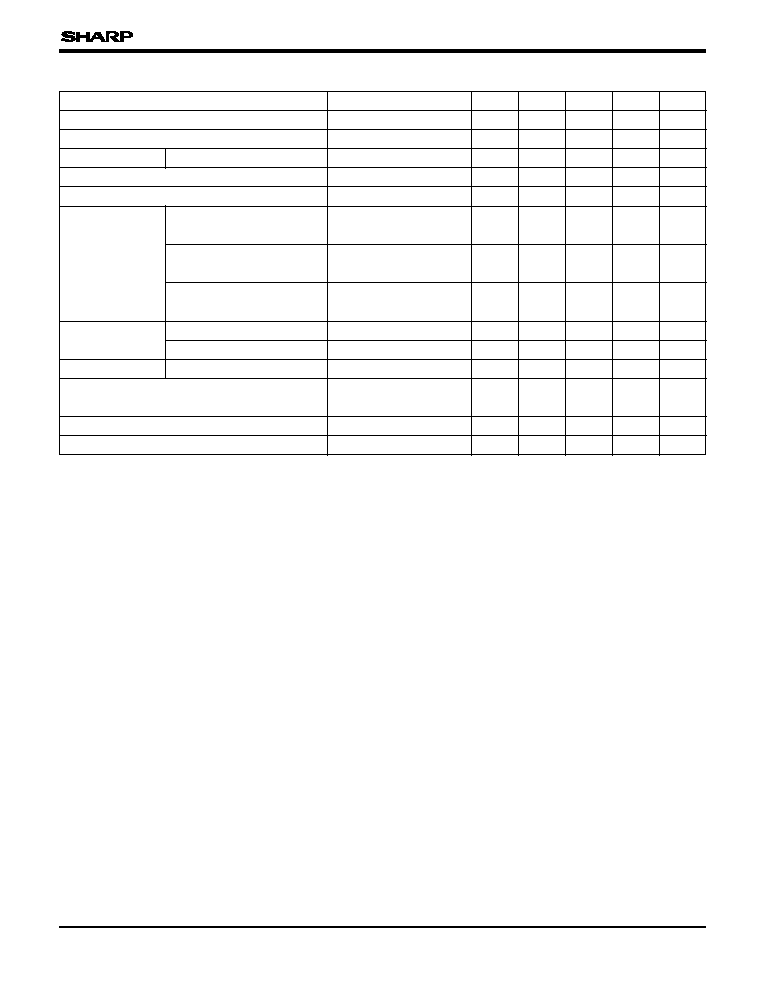

RECOMMENDED OPERATING CONDITIONS

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

NOTE

Ambient operating temperature

T

OPR

25.0

∞C

Output transistor drain voltage

V

OD

12.5

13.0

13.5

V

NOTES :

1. Use the circuit parameter indicated in "SYSTEM CONFIGURATION EXAMPLE", and do not connect to DC voltage directly.

2. V

PW

is set below V

ÿVL

that is low level of vertical shift register clock, or is used with the same power supply that is connected

to V

L

of V driver IC.

* To apply power, first connect GND and then turn on V

OD

. After turning on V

OD

, turn on PW first and then turn on other powers

and pulses. Do not connect the device to or disconnect it from the plug socket while power is being applied.

1

V

20.9

19.5

18.6

V

ÿOFD

Overflow drain clock

P-well voltage

V

PW

≠8.0

V

ÿVL

V

2

Ground

GND

0.0

V

V

≠6.65

≠7.0

≠7.35

V

ÿV1AL

, V

ÿV1BL

, V

ÿV2L

V

ÿV3AL

, V

ÿV3BL

, V

ÿV4L

Vertical shift

register clock

LOW level

INTERMEDIATE level

HIGH level

V

ÿV1AI

, V

ÿV1BI

, V

ÿV2I

V

ÿV3AI

, V

ÿV3BI

, V

ÿV4I

V

ÿV1AH

, V

ÿV1BH

V

ÿV3AH

, V

ÿV3BH

12.5

0.0

13.0

13.5

V

V

LOW level

Horizontal shift

register clock

V

ÿH1L

, V

ÿH2L

≠0.05

0.0

0.05

V

HIGH level

V

ÿH1H

, V

ÿH2H

4.5

4.8

5.5

V

1

V

5.5

4.8

4.5

V

ÿRS

Reset gate clock

p-p level

Reset gate clock frequency

f

ÿRS

17.94

MHz

Horizontal shift register clock frequency

f

ÿH1

, f

ÿH2

17.94

MHz

Vertical shift register clock frequency

f

ÿV1A

, f

ÿV1B

, f

ÿV2

f

ÿV3A

, f

ÿV3B

, f

ÿV4

7.87

kHz

p-p level

LZ21N3

4

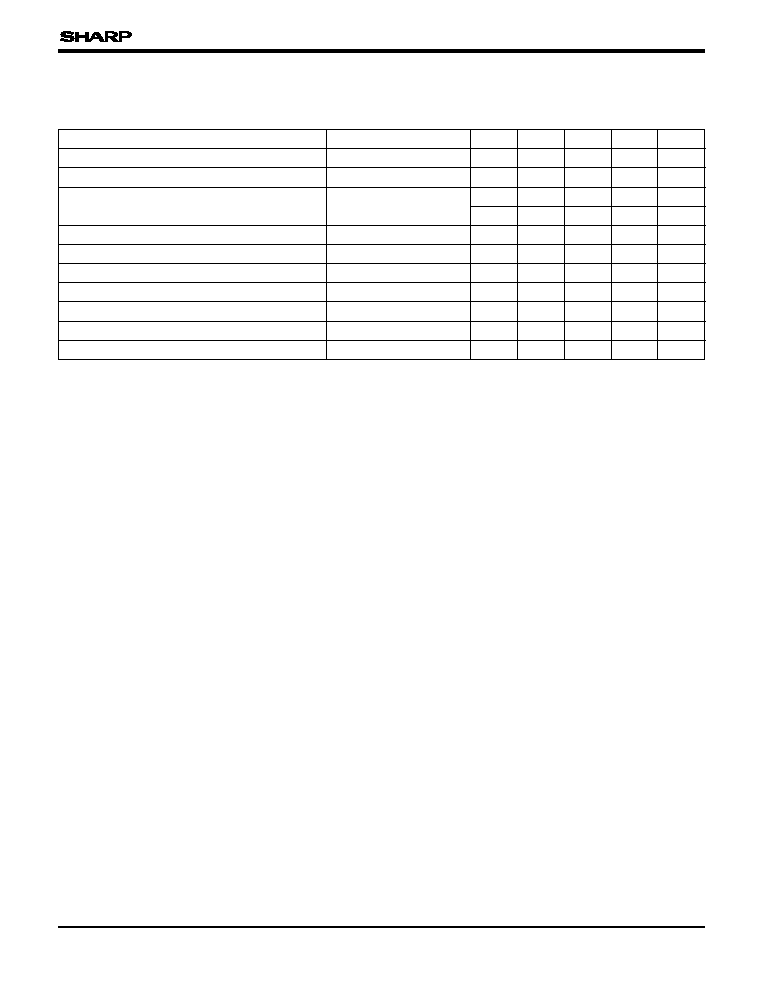

CHARACTERISTICS

(Drive method : 1/30 s frame accumulation)

(T

A

= +25 ∞C, Operating conditions : The typical values specified in "RECOMMENDED OPERATING CONDITIONS".

Color temperature of light source : 3 200 K, IR cut-off filter (CM-500, 1 mmt) is used.)

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNIT

NOTE

Standard output voltage

V

O

150

mV

2

Photo response non-uniformity

PRNU

10

%

3

Saturation output voltage

V

SAT

450

530

mV

4

Dark output voltage

V

DARK

0.5

3.0

mV

1, 6

Dark signal non-uniformity

DSNU

0.5

2.0

mV

1, 7

Sensitivity

R

140

180

mV

8

Smear ratio

SMR

≠89

≠82

dB

9

Image lag

AI

1.0

%

10

Blooming suppression ratio

ABL

1 000

11

Output transistor drain current

I

OD

4.0

8.0

mA

NOTES :

∑ Within the recommended operating conditions of V

OD

,

V

OFD

of the internal output satisfies with ABL larger than

1 000 times exposure of the standard exposure conditions,

and V

SAT

larger than 320 mV.

1. T

A

= +60 ∞C

2. The average output voltage under uniform illumination.

The standard exposure conditions are defined as when

Vo is 150 mV.

3. The image area is divided into 10 x 10 segments under

the standard exposure conditions. Each segment's

voltage is the average output voltage of all pixels within

the segment. PRNU is defined by (Vmax ≠ Vmin)/Vo,

where Vmax and Vmin are the maximum and minimum

values of each segment's voltage respectively.

4. The image area is divided into 10 x 10 segments. Each

segment's voltage is the average output voltage of all

pixels within the segment. V

SAT

is the minimum

segment's voltage under 10 times exposure of the

standard exposure conditions. The operation of OFDC is

high. (for still image capturing)

5. The image area is divided into 10 x 10 segments. Each

segment's voltage is the average output voltage of all

pixels within the segment. V

SAT

is the minimum

segment's voltage under 10 times exposure of the

standard exposure conditions. The operation of OFDC is

low.

6. The average output voltage under non-exposure

conditions.

7. The image area is divided into 10 x 10 segments under

non-exposure conditions. DSNU is defined by (Vdmax ≠

Vdmin), where Vdmax and Vdmin are the maximum and

minimum values of each segment's voltage respectively.

8. The average output voltage when a 1 000 lux light

source with a 90% reflector is imaged by a lens of F4,

f50 mm.

9. The sensor is exposed only in the central area of V/10

square with a lens at F4, where V is the vertical image

size. SMR is defined by the ratio of the output voltage

detected during the vertical blanking period to the

maximum output voltage in the V/10 square.

10. The sensor is exposed at the exposure level

corresponding to the standard conditions. AI is defined

by the ratio of the output voltage measured at the 1st

field during the non-exposure period to the standard

output voltage.

11. The sensor is exposed only in the central area of V/10

square, where V is the vertical image size. ABL is

defined by the ratio of the exposure at the standard

conditions to the exposure at a point where blooming is

observed.

5

mV

400

320