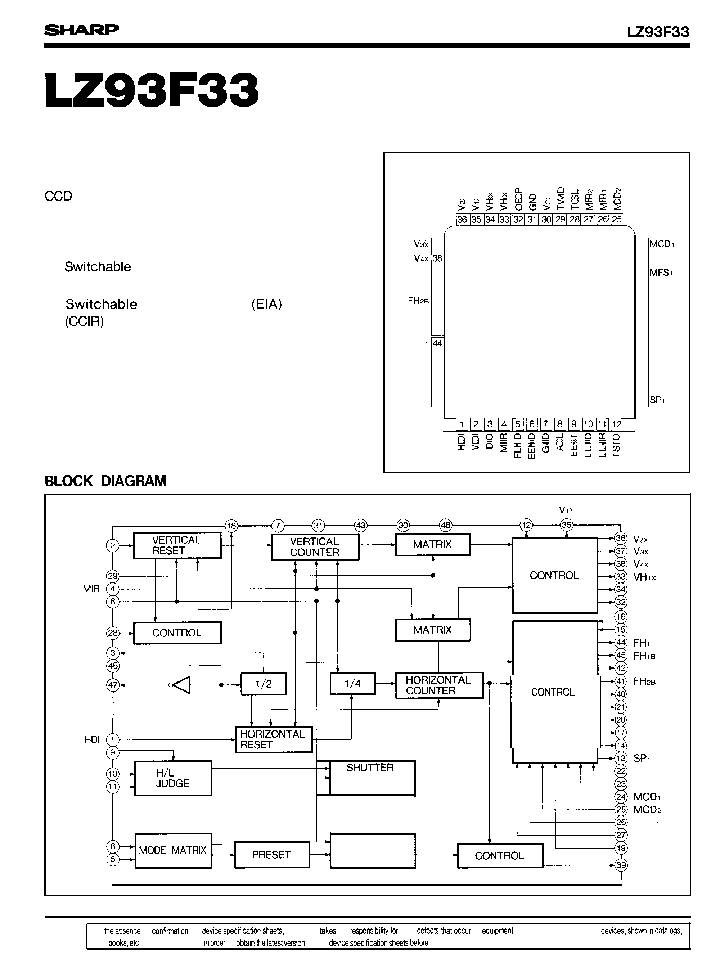

LZ93BE0

DESCRIPTION

The LZ93BE0 is a CMOS timing generator LSI

which provides horizontal transfer pulse, reset

pulse, and sample-hold pulse used for separate

camera, in combination with single-chip driver

LSI (LZ95G55, LZ95G41 ) and timing LSI

LZ93F50, LZ93N61 or

FEATURES

q

q

q

q

q

q

between 270

pixels

and

320000 pixels CCD

between NTSC

and PAL

systems

Single +5 power supply

between normal and mirror-image

Suitable for separate camera

Package : 20-pin

Timing Pulse Generator

for

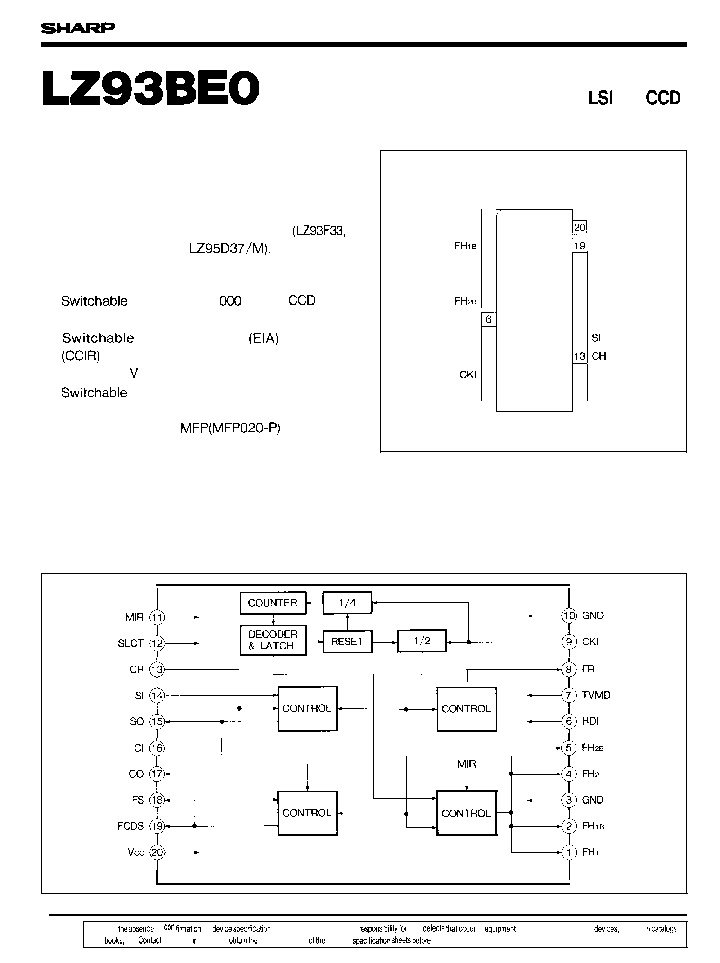

PIN CONNECTIONS

20-PIN MFP

TOP VIEW

FH

1

=

o

Vcc

2

FCDS

GND

3

1 8 F S

F H 2

4

1 7

co

5

1 6 c l

H D I

1 5 s o

T V M D

7

1 4

F R

8

9

1 2 S L C T

G N D 1 0

11

M I R

Designed for A-type and B-type CCD area sensors :

A-type CCD area sensor : LZ2314J, LZ2324J, LZ231 32, LZ23232

B-type CCD area sensor : LZ2414J, LZ2424J, LZ2313H5,

LZ2323H5, LZ2413, LZ2423

BLOCK DIAGRAM

256

"in

of

by

sheets, SHARP takes no

any

in

using any of SHARPs

shown

data

etc

SHARP order to

latest version

device

using any SHARPs device'

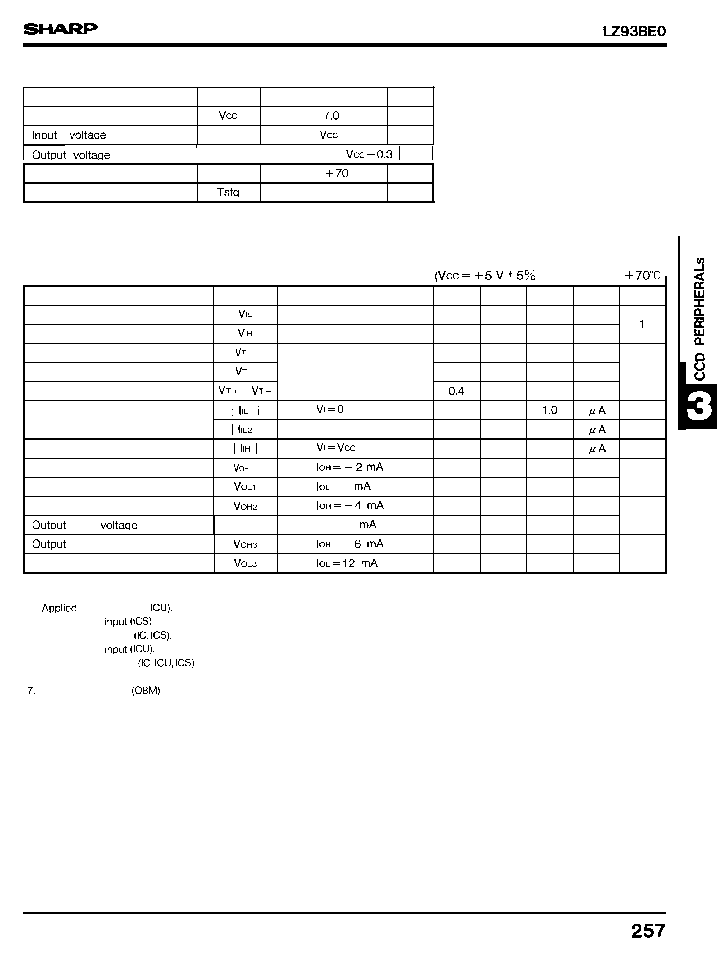

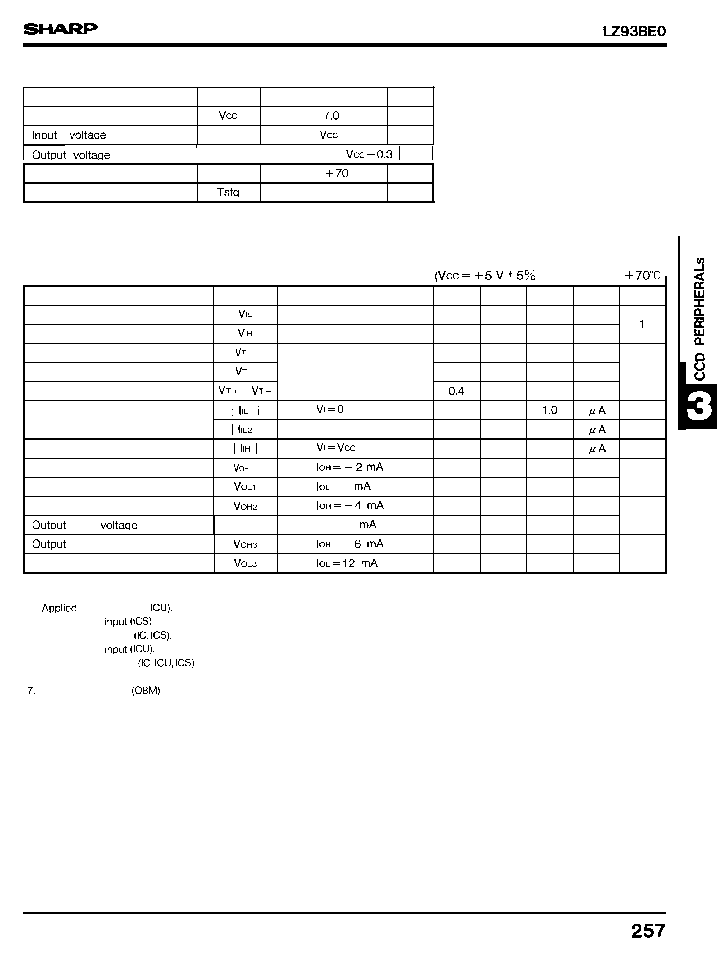

ABSOLUTE MAXIMUM RATINGS

PARAMETER

SYMBOL

RATING

UNIT

Supply voltage

� 0.3 to

v

VI

�0,3

to

+

0.3

v

Vo

-0.3

to

v

Operation temperature

Topr

� 2 0 t o

`c

Storaae temperature

�55 to +150

"c

DC CHARACTERISTICS

T a = � 2 0 t o

PRAMETER

SYMBOL

CONDITIONS

MIN.

TYP.

MAX.

UNIT

NOTE

Input Low voltage

1 . 5

v

Input High voltage

3.5

v

Input High threshold voltage

+

2.2

3.8

v

Input Low threshold voltage

Schmitt Buffer

1.0

2.4

v

2

Hysteresis voltage

v

v

3

Input Low current

Vl=o v

8.0

60

4

Input High current

1 , 0

5

Output High voltage

1

4.0

v

6

Output Low voltage

= 4

0.4

v

Output High voltage

4.0

v

7

LOW

v 0 L 2

I

OL

= 8

0.4

v

High voltage

4.0

v

8

Output Low voltage

0.4

v

NOTES :

1.

to inputs (IC,

2. Applied to

3. Applied to inputs

4. Applied to

5. Applied to inputs

6. Applied to output (0)

Applied to output

8 Applied to output (012M)

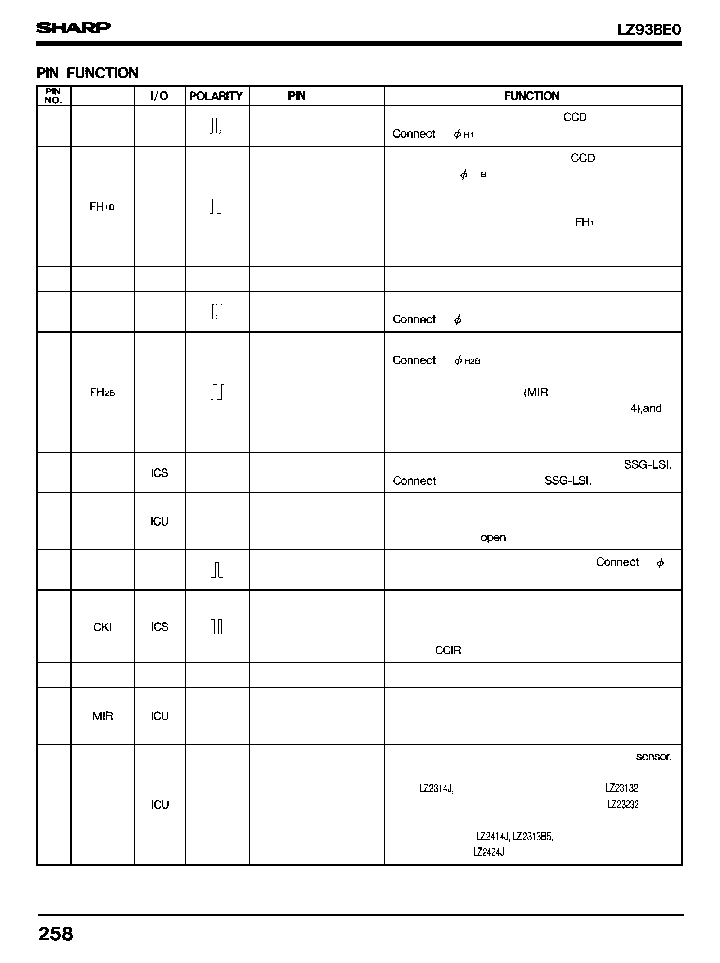

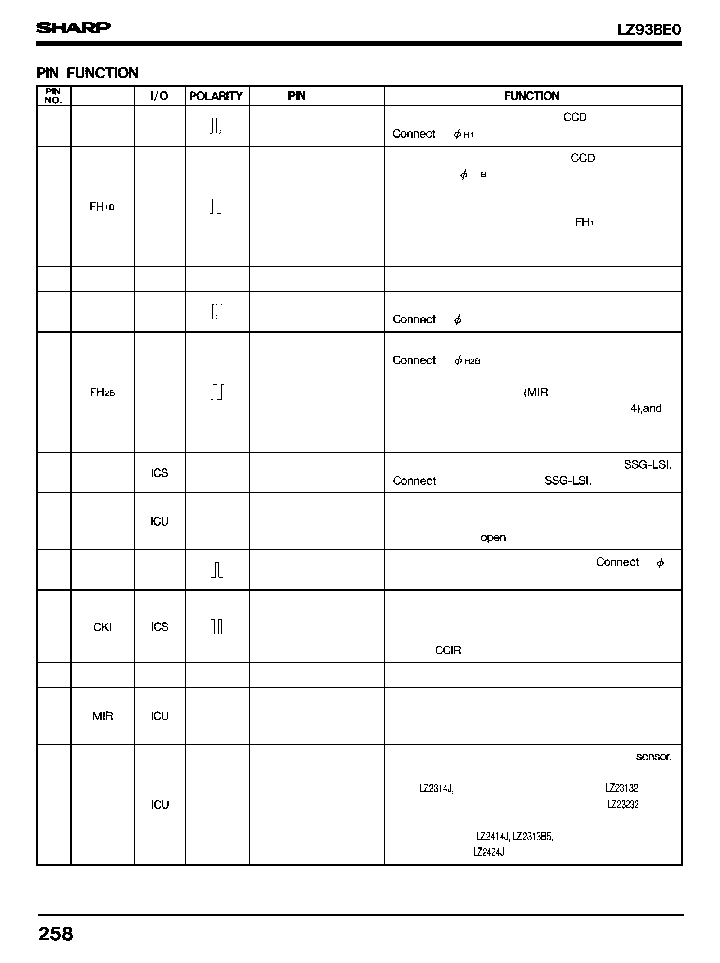

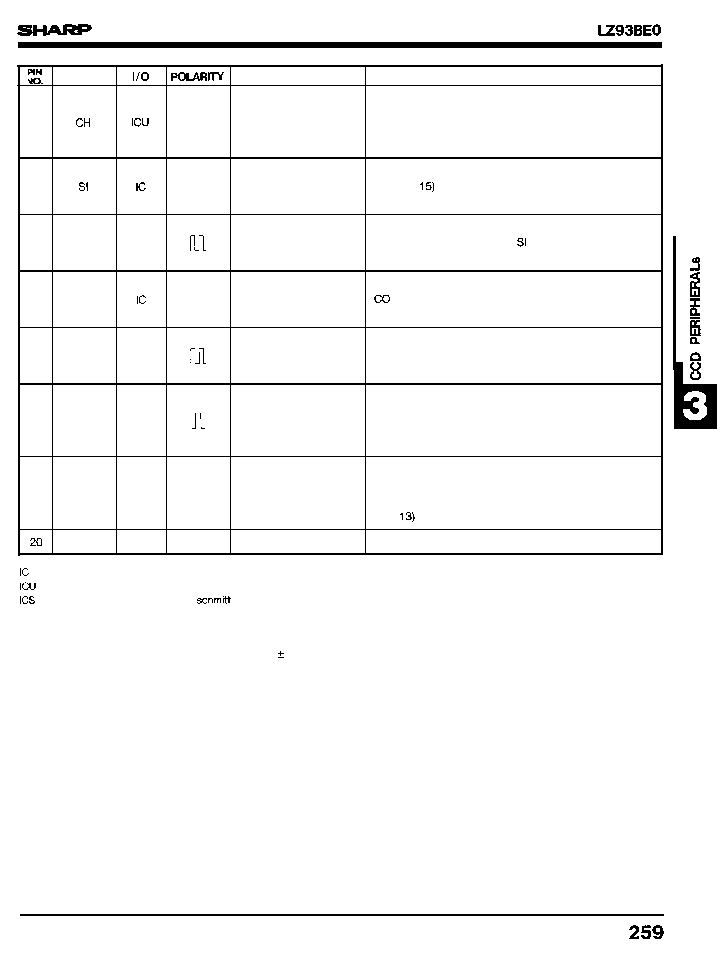

SYMBOL

NAME

1

FH

I

012M

Horizontal transfer

A horizontal transfer pulse for

area sensor.

pulse 1

to of CCD area sensor.

A horizontal transfer pulse for

area sensor,

Connect to

HI

of CCD area sensor. If the CCD

Horizontal transfer

area sensor which corresponds to Mirror mode is

2

08M

driven at Normal mode (MIR = L), its drive-pulse is

pulse 1 B

the same phase as the pulse of

(pin 1), and it

is the same phase as the pulse of FH2 (pin 4) at

Mirror mode (MIR = H).

3

GND

�

�

Ground

A grounding pin.

4

FH2

012M

Horizontal transfer

A horizontal transfer pulse for CCD area sensor.

pulse 2

to

HZ

of CCD area sensor,

A horizontal transfer pulse for CCD area sensor.

to

of CCD area sensor. If the CCD

Horizontal transfer

area sensor which corresponds to Mirror mode is

5

08M

driven at Normal mode

= L), its drive-pulse is

pulse 2B

the same phase as the pulse of FH2 (pin

it

is the same phase as the pulse of FH

I

(pin 1 ) at

Mirror mode (MIR = H).

6

HDI

�

Horizontal reference

Put in a horizontal reference pulse from

pulse

to HD terminal of

An input-pin to select TV standards,

7

TVMD

�

TV mode select

L level : NTSC mode

H level or

: PAL mode

8

FR

08M

Reset pulse

A reset pulse for CCD area sensor,

to

R

of CCD area sensor through the DC offset circuit.

An input pin for reference clock.

9

The frequencies are as follows :

Clock input

At EIA mode : 19.06993 MHz (1212 fH)

At

mode : 19.31250 MHz (1 236 fH)

10

GND

�

�

Ground

A grounding pin.

An input pin to select Mirror mode or Normal mode.

11

--

Mirror mode select

L level : Normal Drive mode

H level or open : Mirror Drive mode

An input pin to select the type of CCD area

L level (A type)

LZ2314Z, LZ23t42, LZ2313A9,

12

SLCT

--

CCD type select

LZ2324J, LZ2324Z, LZ23242, LZ2323A9,

H level or open (B type)

LZ2314BK,

LZ2313H5, LZ2413

LZ2324BK,

LZ2323B5, LZ2323H5, LZ2423

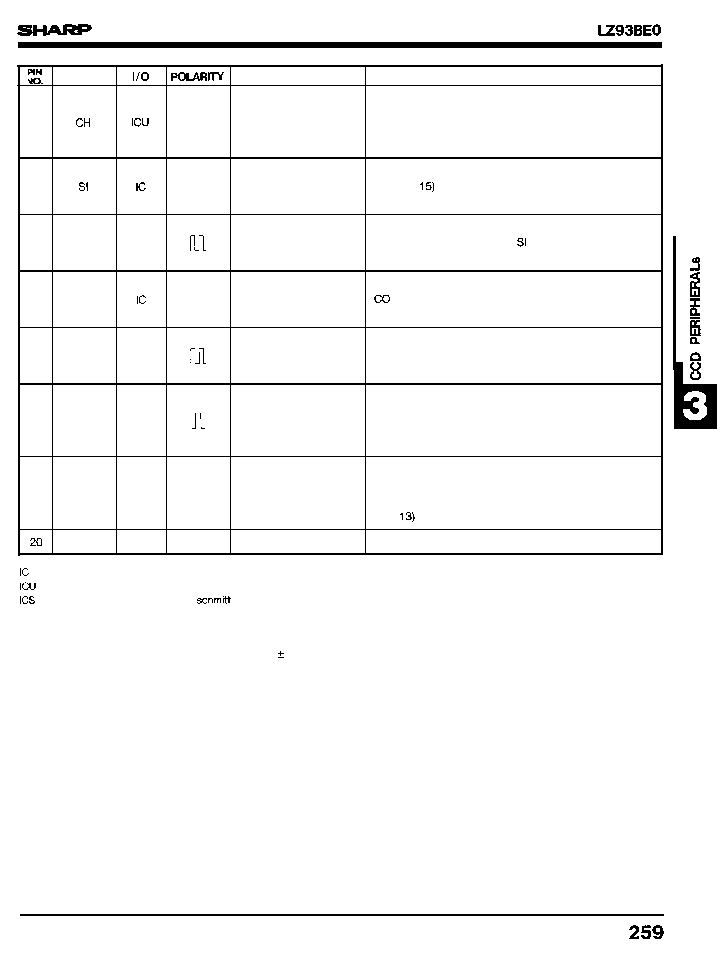

SYMBOL

PIN NAME

FUNCTION

An input pin to select the phase of FCDS (pin 19)

13

Phase control terminal

pulse and FS (pin 18) pulse.

--

for FCDS and FS

L level : adjustable

H level or open : fixed

Phase-adjust input

An input pin to control the phase of FS (pin 18).

14

�

for FS

SO (pin

pulse put in this terminal after make it

delay with resistor and capacitor.

Phase-adjust output

An output pin to control the phase of FS (pin 18).

15

s o

o

for

FS

The output pulse put in

(pin 14) after make it

delay with resistor and capacitor.

Phase-adjust input

An input pin to control the phase of FCDS (pin 19).

18

cl

--

for FCDS

(pin 17) pulse put in this terminal after make it

delay with resistor and capacitor.

Phase-adjust output

An output pin to control the phase of FCDS (pin 19).

17

c o

o

for FCDS

The output pulse put in Cl (pin 16) after make it

delay with resistor and capacitor.

A pulse to sample-hold the signal from CCD area

18

FS

o

Sample-hold pulse

sensor. The phase of FS is fixed if CH (pin 13)

output

equals H level and it can be adjustable if CH (pin

13) equals L level.

A pulse to clamp the feed-through level form CCD

19

FCDS

o

n

CDS pulse output

area sensor. The phase of FCDS is fixed if CH (pin

13) equals H level and it can be adjustable if CH

(pin

equals L level.

Vcc

�

--

Power supply

Supply +5 V power.

: Input pin (CMOS level input)

:

Input pin (CMOS level input with pull-up resistor)

:

Input pin (CMOS

input )

O, 08M, 012M : Output pin

NOTE :

At

the input pin, the rising edge of HDI (pin 6) is 20 ns shorter than that of CKI (pin 9).

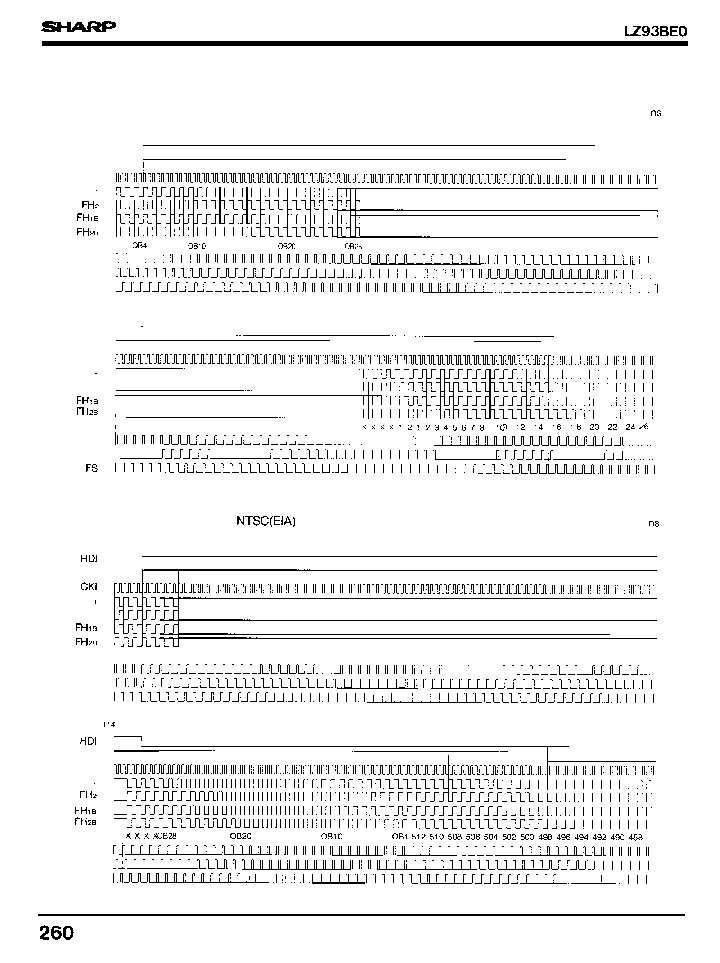

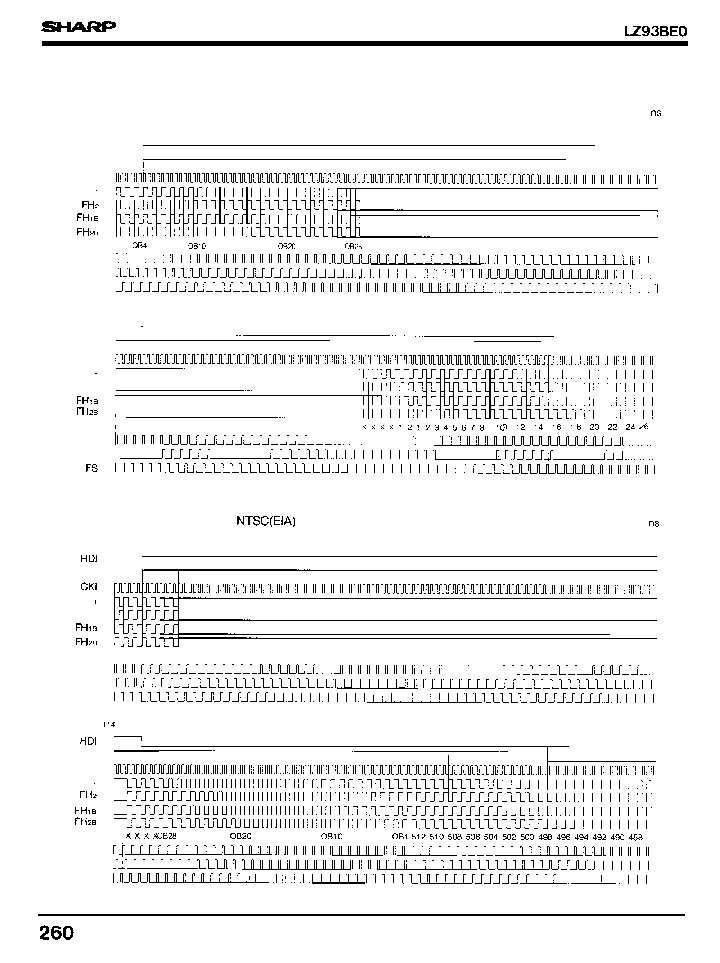

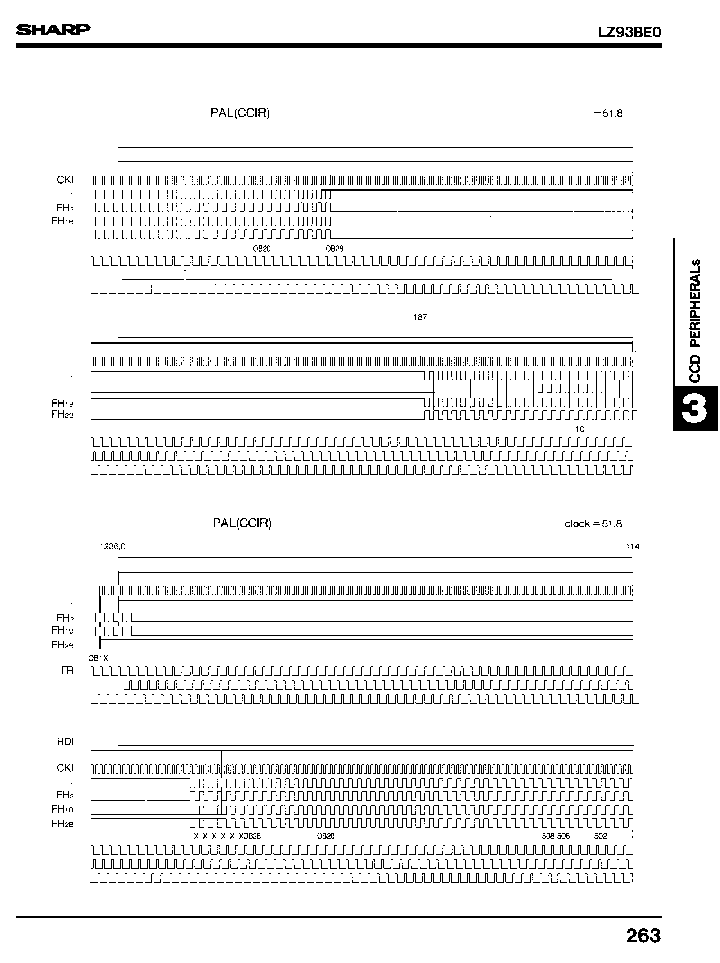

TIMING DIAGRAM

NTSC(EIA) < A-TYPE, NORMAL MODE >

1 clock = 52.4

1212,0

49

114

HDI

CBLK

CKI

FH

FR

FCDS

FS

HDI

CBLK

CKI

FH

FH2

FR

FCDS

CBLK

FH

FH2

FR

FCDS

FS

CBLK

CKI

FH

FR

FCDS

FS

114 120

166

2 1 0

X X X X 1 2 1 2 3 4 5 6 7 8

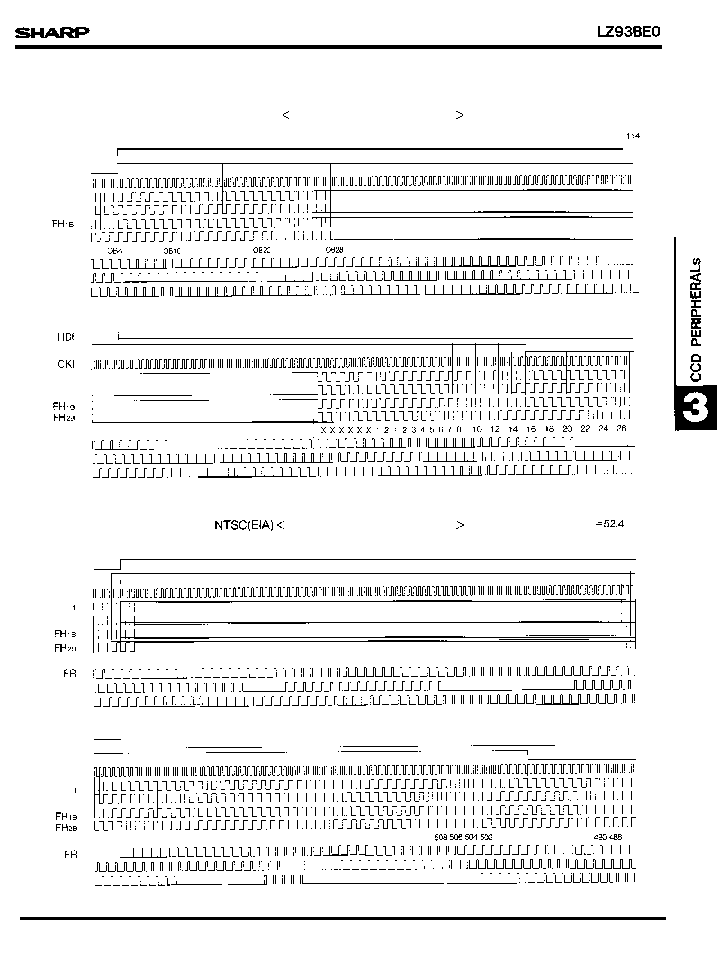

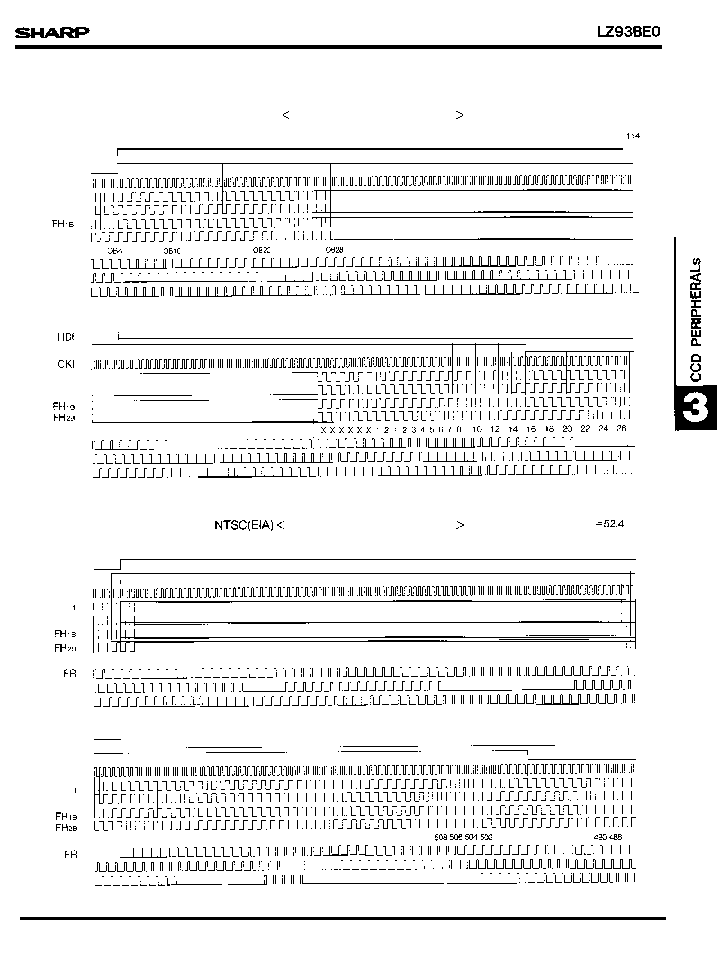

< A-TYPE, MIRROR MODE >

1

clock = 52.4

1212,0 8

114

O B I X X X X X X

n

116 120

210

HDI

CBLK

CKI

FH 1

FH2

FH2B

FR

FCDS

FS

CBLK

FH

FH2

FR

FCDS

FS

HDI

CBLK

CKI

FH

FH2

FCDS

FS

NTSC(EIA)

B-TYPE, NORMAL MODE

1

clock= 52.4 ns

1212,0

47

--

I

14

120

163

210

B-TYPE, MIRROR MODE

1 clock

ns

1212,0 3

111 114

OBIXX X X

x

114

120

210

HDI

CBLK

,

CKI

FH

FH2

XX X X XOB28

0B20

OB1O

OBI 512 510

500 498 496 494 492

FCDS

FS

261

HDI

CBLK

FH

B

FH2B

FR

FCDS

FS

HDI

CBLK

FH

I

FH2

FH2B

FR

FCDS

FS

HDI

CBLK

FH

FH2

FH2B

FR

FCDS

FS

CBLK

CKI

FH

I

F H

IB

FR

FCDS

FS

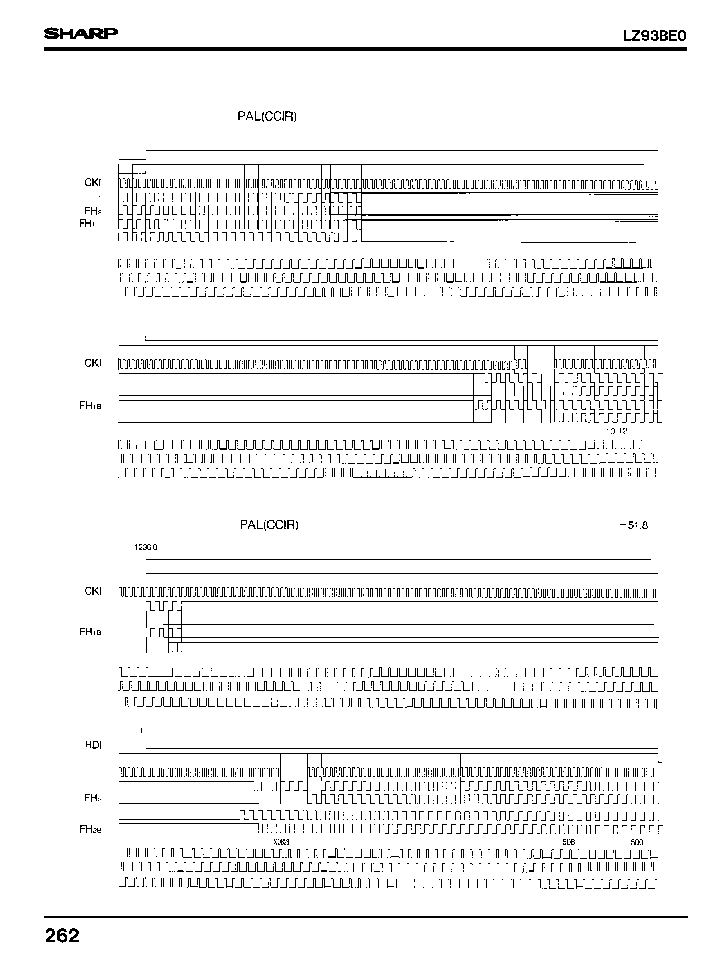

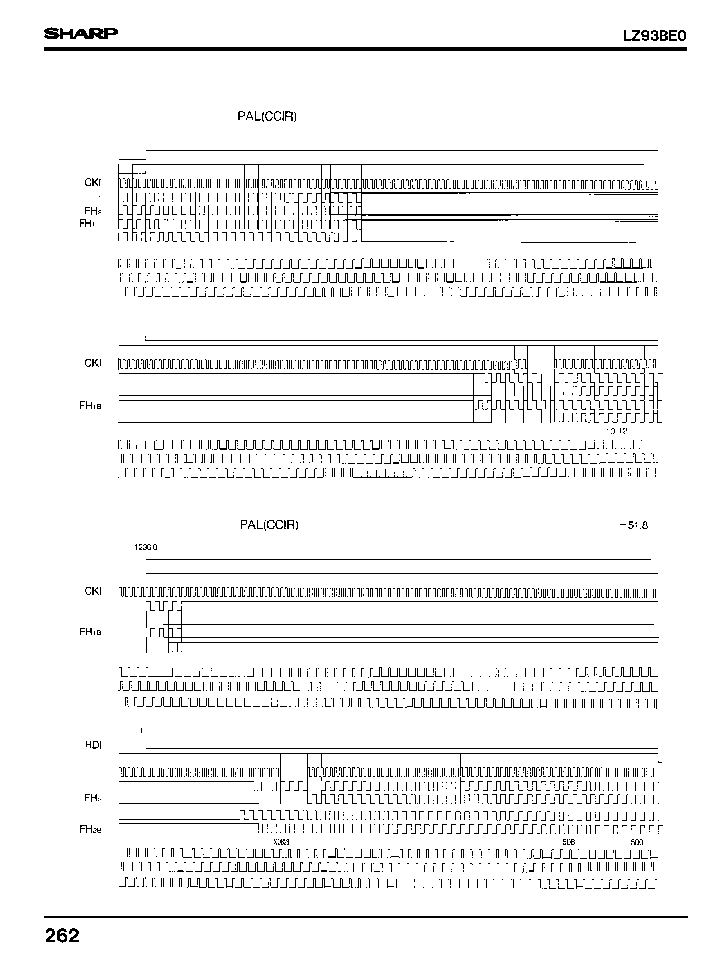

< A-TYPE, NORMAL MODE >

1 clock = 51.8 ns

1236,0

48

114

0B4

OB1O

OB20

0B28

114 120

192

234

m

J

u

X X X X 1 2 1 2 3 4 5 8 7 8

1 4

r

< A-TYPE, MIRROR MODE >

1

clock

ns

3

114

O B I X X X X X X

114

20

140

234

I

m

u

v

XX X

OB20

OB1O

OB1 512 510

506 504 502

HDI

CBLK

FH

FH2B

FR

FCDS

FS

HDI

CBLK

CKI

FH

FH2

FR

FCDS

FS

HDI

CBLK

CKI

FH

FCDS

FS

< B-TYPE, NORMAL MODE >

1 clock

ns

7236,0

47

114

OB4

OB1O

114 120

234

X X X X X X 1 2 1 2 3 4 5 6 7 8

1 2 1 4

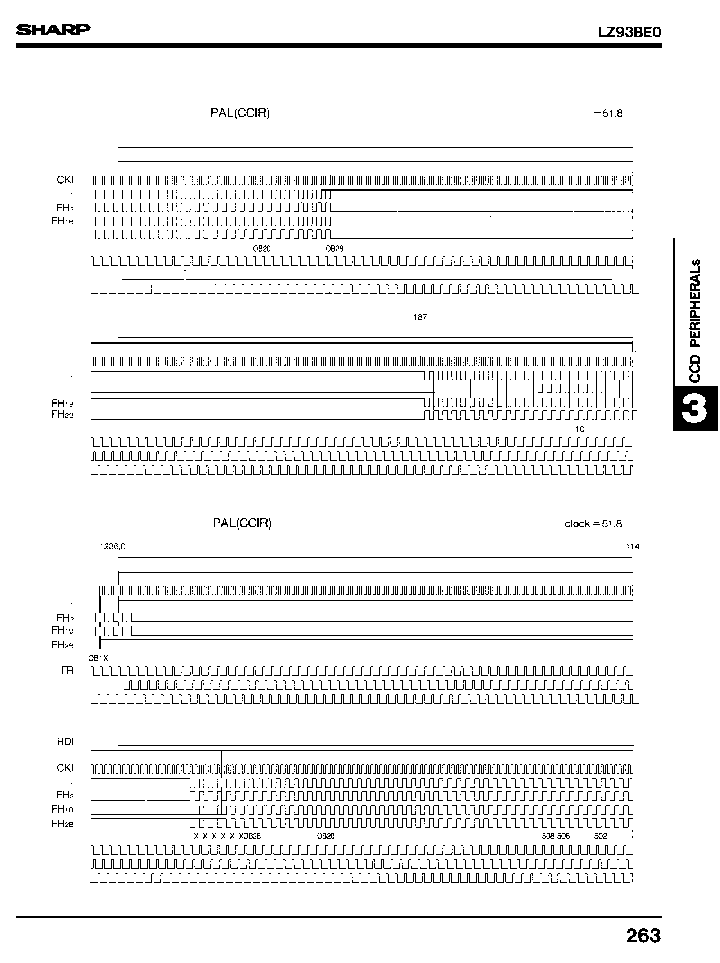

< B-TYPE, MIRROR MODE >

1

ns

3

M

X X X

114

120

135

234

CBLK

L

FH

OB1O

FR

OBI 512 510

504

500

FCDS

FS

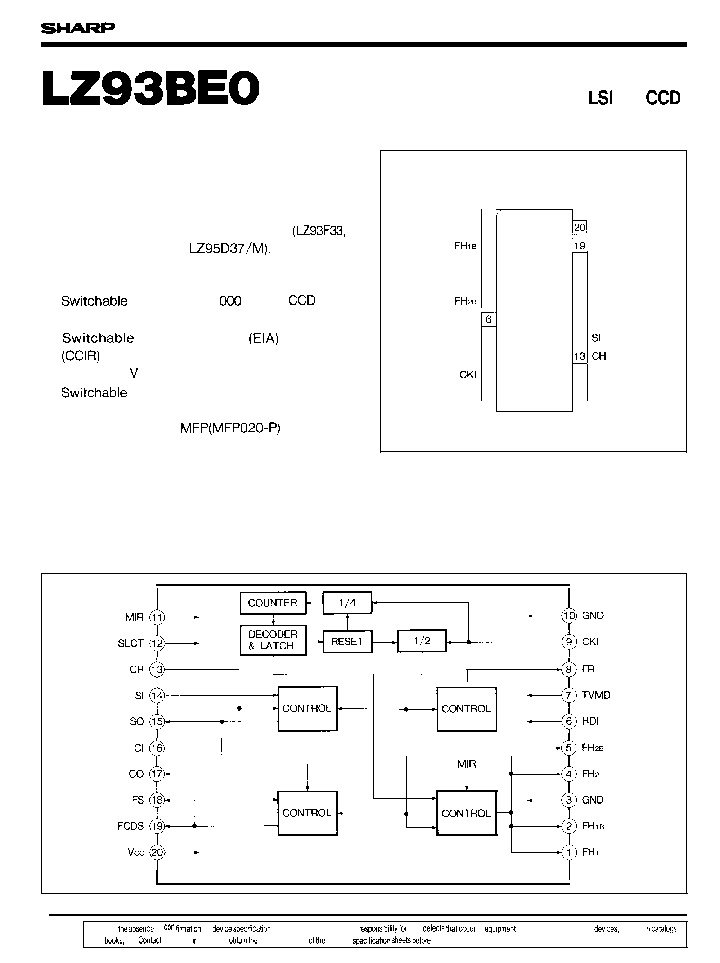

DESCRIPTION

The LZ93F33 is a CMOS timing generator LSI

which provides timing pulses used to drive a

area sensor, in combination with the SSG

LSI (LZ93N19 or LZ93B53).

FEATURES

q

q

q

q

q

q

q

between 270000 pixels CCD and

320000 pixels CCD

between NTSC

and PAL

systems

Built-in EE (Electronic Exposure) control

Flicker-less function

Switchable between normal and mirror image

Single +5 V power supply

Package : 48-pin QFP(QFP048-P-101 O)

Timing Pulse Generator LSI for CCD

PIN CONNECTIONS

48-PIN QFP

TOP VIEW

37

24

23 MFS2

OFDX 39

22

FR 40

21 FS

41

20 FCDS

FH2 42

19 INSL

GND 43

18 TO

FH

17 SE

FH

IB

45

16 SINV

CKI 46

15 SESL

CKO 47

14 SP2

TEST 48

0

13

VDI

TVMD

ACL

TOSL

DO

CKI

CKO

EEST

EEUD

EENR

EEMD

FLMD

TO

GND

GND

GND

Vcc

TEST

TSTO

UP/DOWN

CONTROL

SHUTTER

SPEED

CONTROL

VH3X

OBCP

SINV

SESL

FH2

FR

FS

FCDS

SE

SP2

MFSI

MFS2

MFR

MFR2

INS'

OFDX

264

"In

of

by

SHARP

no

any

in

using any of WARPs

data

Contact SHARP

to

of the

using any SHARPs device"