| ÐлекÑÑоннÑй компоненÑ: LZ93N61 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

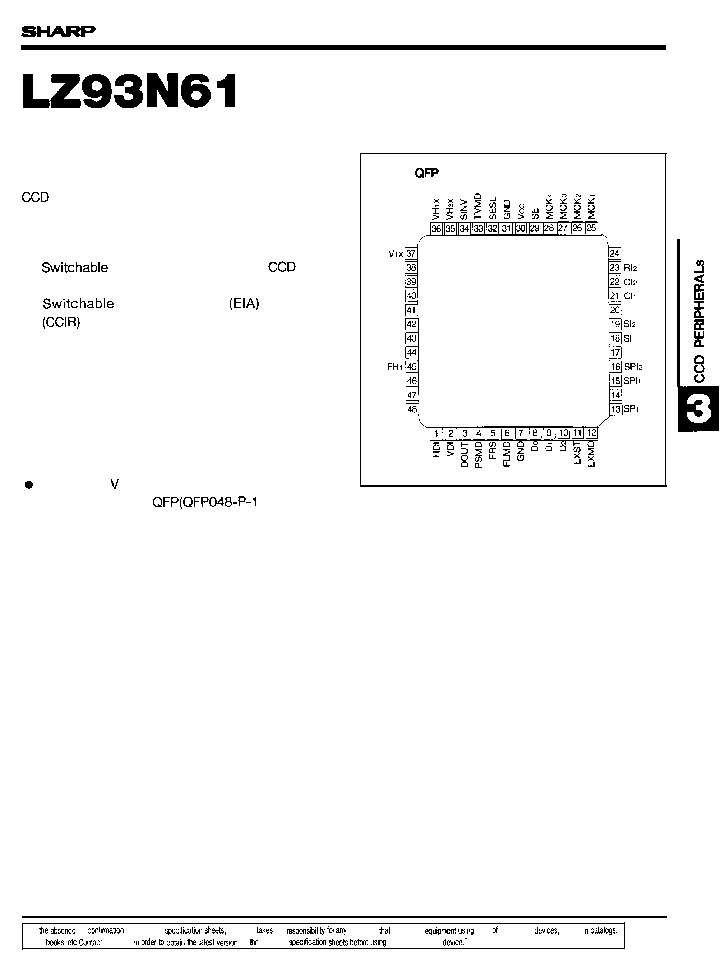

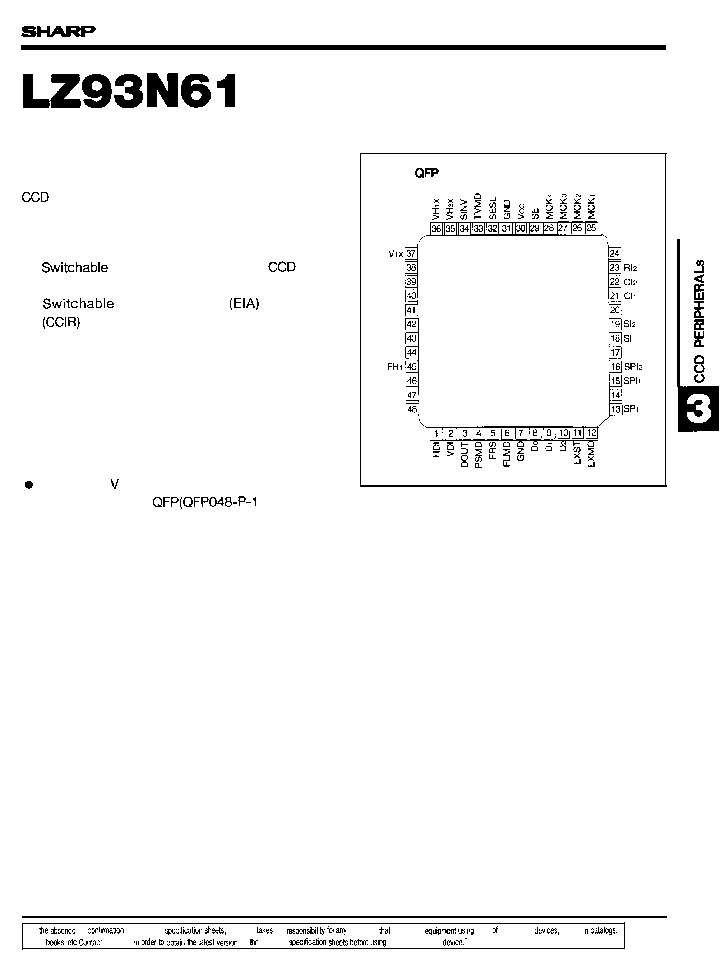

LZ93N61

DESCRIPTION

The LZ93N61 is a CMOS timing generator LSI

which provides timing pulses used to drive a

area sensor, in combination with the SSG

LSI (LZ93NI 9, LZ93B53).

FEATURES

q

q

q

q

between 270000 pixels

and

320000 pixels CCD

between NTSC

and PAL

systems

Internal electronic shutter :

Shutter speed is selectable from 1/W, 1/125,

1/250, 1/500, 1/1 000, 1/2 000, 1/4 000 and

1/10 000 s, in addition to this, 1/100 s (PAL

: 1/120 s) in Flicker-less mode using parallel

or serial code. Shutter speed can also be

controlled in 1 H period using an external

trigger to the EXST input.

Single +5 power supply

Package : 48-pin

01 O)

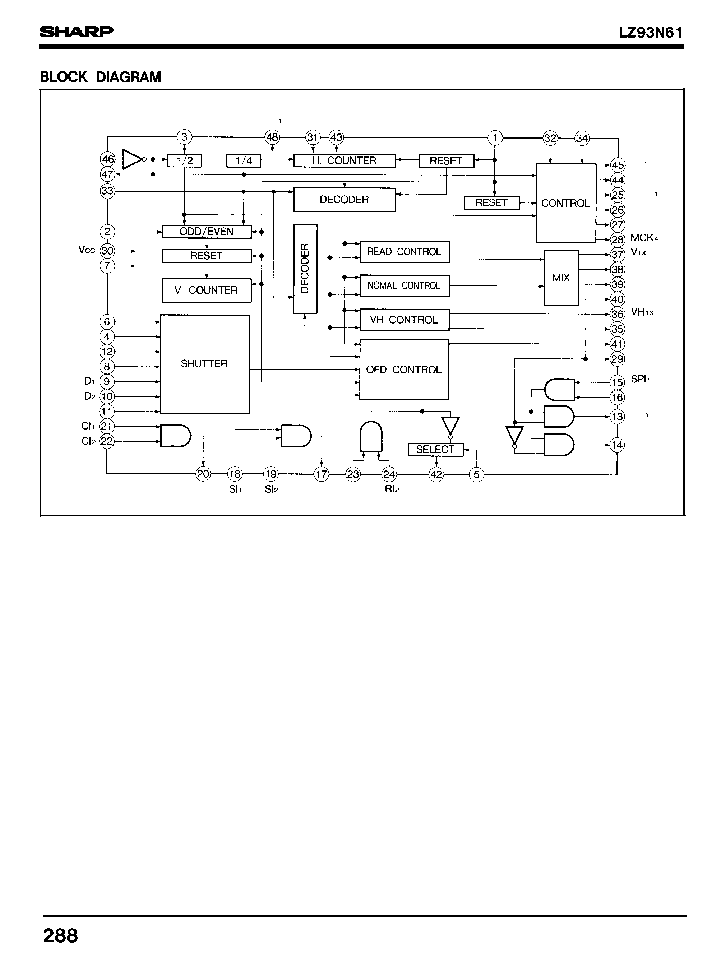

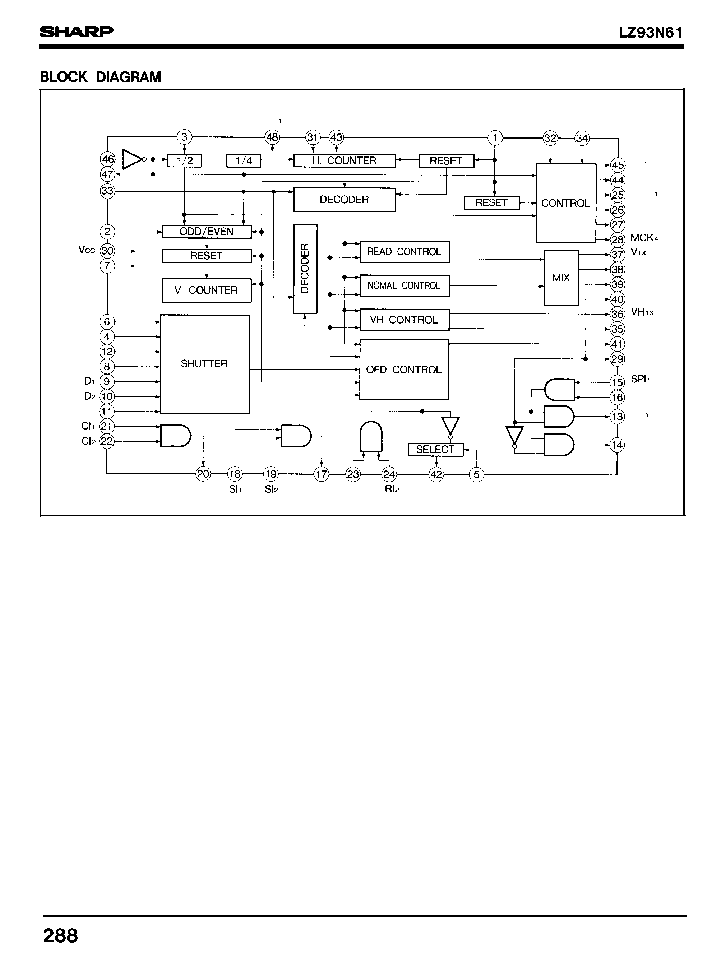

Timing Pulse Generator LSI for CCD

PIN CONNECTIONS

48-PIN

TOP VIEW

37

V 2 X 3 a

V3X

39

V 4 X 4 0

OFDX 41

FR 42

GND 43

FH2 44

45

CKI 46

CKO 47

TSTI

o

24 R12

23

22

21

20 FCDS

19

18

17 FS

16

15

14 SP2

13

"In

of

by device

WARP

no

defects

recur In

any WARPS

show

deta

WARP

of

device

any 8HARPs

287

D O U T

TST

GND GND

HDI

SESL SINV

CKI

C K O

FH

T V M D

FH2

MCK

MCK2

VDI

MCK3

G M D

V2X

V3X

V4X

FLMD

PSMD

VH3X

EXMD

OFDX

Do

SE

SPI 2

EXST

SP

SP2

F C D S

FS

RI I

FR

FRS

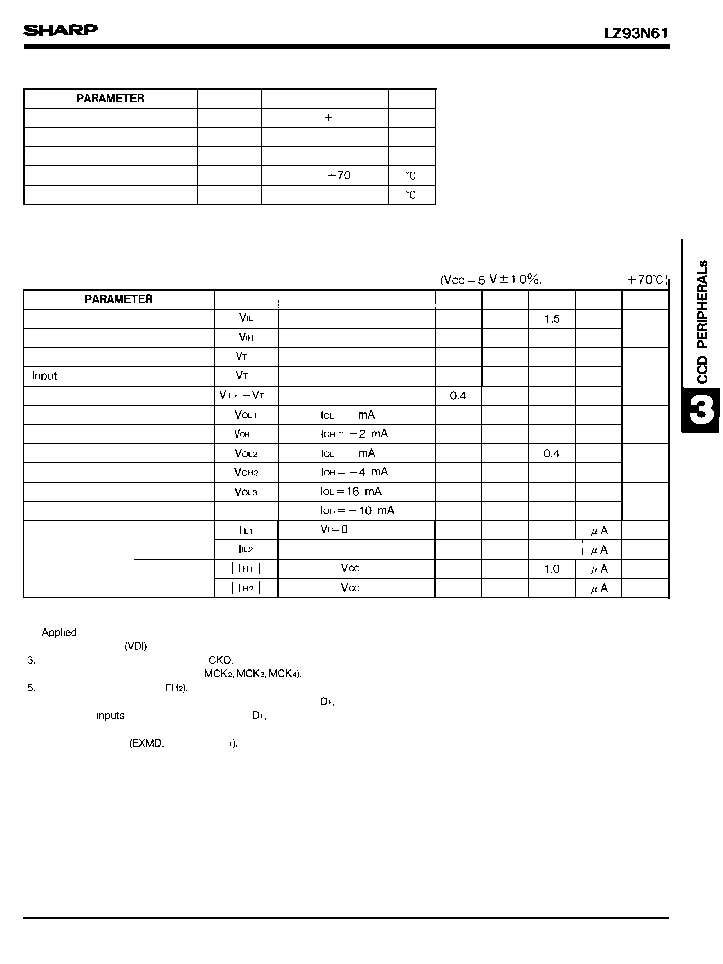

ABSOLUTE MAXIMUM RATINGS

SYMBOL

RATING

UNIT

Supply voltage

Vcc

0.3 to

7.0

v

Input voltage

VI

0.3

to

Vcc + 0.3

v

Output voltage

Vo

0.3

to Vcc +

0.3

v

Operating temperature

Topr

2 0

t o

Storage temperature

Tstg

55 to +150

DC CHARACTERISTICS

T a = 1 0 t o

S Y M B O L

CONDITIONS

MIN. TYP.

I

MAX.

UNIT NOTE

Input Low voltage

v

1

Input High voltage

3.5

v

Input High threshold voltage

+

2.2

3,8

v

Low threshold voltage

-

1,0

2.4

v

2

Hysteresis voltage

v

Output Low voltage

=

4

0.4

v

3

Output High voltage

1

4.0

v

Output Low voltage

=8

v

4

Output High voltage

4.0

v

Output Low voltage

0.4

v

Output High voltage

5

v0H3

4.0

v

Input Low current

v

1.0

6

V l = o v

8.0

60

7

VI=

8

Input High current

VI=

8.0

60

9

NOTES :

1.

to

2. Applied to

Applied to

4. Applied to

Applied to

6. Applied to

7. Applied to

8. Applied to

9. Applied to

all inputs except for VDI, CKI.

input

all outputs except for

outputs (FR, MCK

I

,

outputs (FH

1

,

all inputs except for PSMD, FRS, FLMD, Do,

D2, EXST, SESL, SINV

(PSMD, FRS, FLMD, Do,

D2, EXST, SESL, StNV).

all inputs except for EXMD, TVMD, TST

1

.

inputs

TVMD, TST

2 8 9

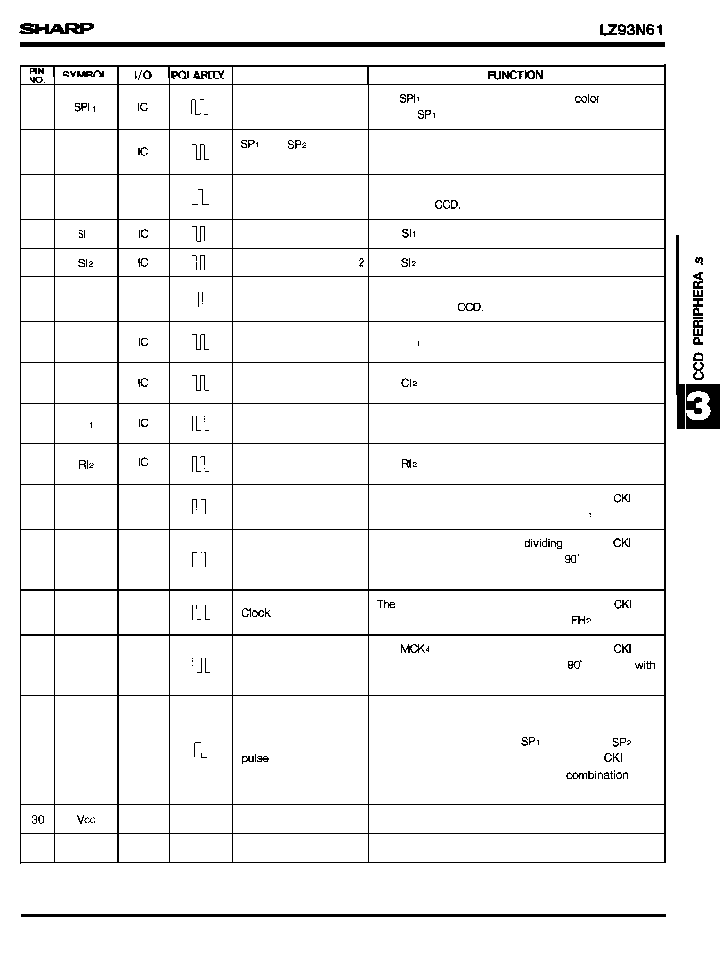

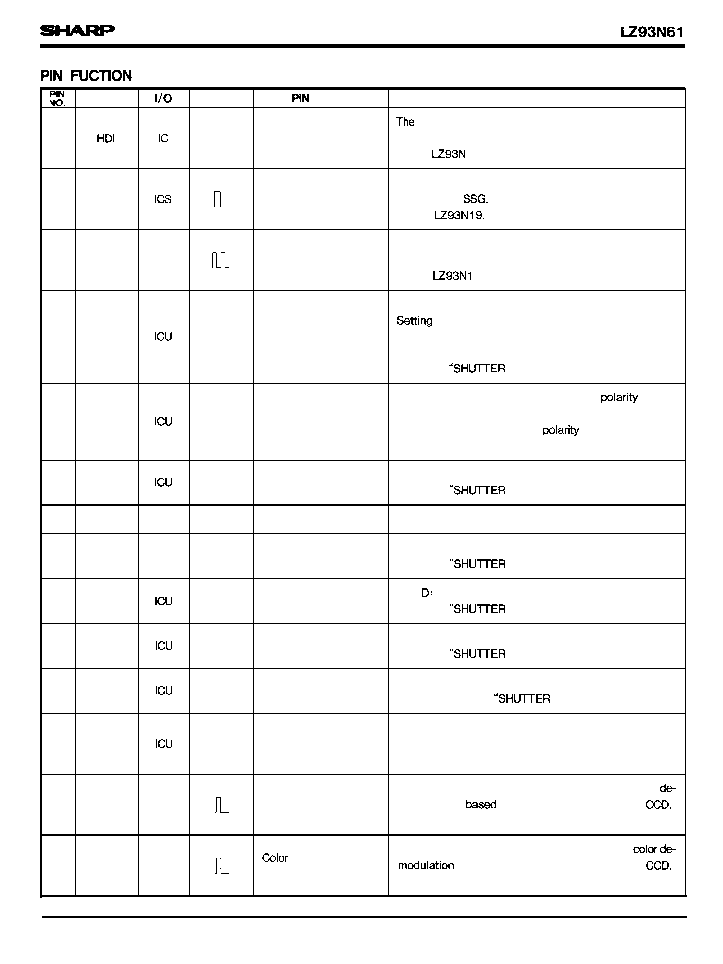

SYMBOL

POLARITY

NAME

FUNCTION

HDI pin is used to input the horizontal reference

1

MM

Horizontal drive pulse

signal from SSG. It is connected to the HD (pin 31)

of the

19.

The VDI pin is used to input the vertical reference

2

VDI

Vertical drive pulse

signal from

It is connected to the VD (pin 34)

of the

The DOUT pin output 1/2 dividing clock input to

3

DOUT

o

Delay-Line clock

the CKI (pin 46). It is connected to the CLKI (pin 27)

of the

9.

The PSMD pin is used to switch the Shutter Speed

Shutter mode select

mode.

4

PSMD

High level : Parallel Setting mode

input

Low level : Serial Setting mode

(Refer to

MODE TABLE". )

The FRS pin is used to selects the

of the

5

FRS

FR control input

FR (pin 42).

High level : negative

Low level : positive polarity

6

FLMD

Flicker-less mode

The FLMD pin is used to prevent the flicker.

select

(Refer to

MODE TABLE ".)

7

GND

--

--

Ground

The GND is a ground pin.

6

Do

Icu

Shutter speed

The Do pin is used to control the shutter speed.

--

switching input O

(Refer to

MODE TABLE". )

9

D

I

Shutter speed

The

pin is used to control the shutter speed.

--

switching input 1

(Refer to

MODE TABLE ".)

10

D2

Shutter speed

The D2 pin is used to control the shutter speed.

--

switching input 2

(Refer to

MODE TABLE ".)

11

EXST

Shutter speed

The EXST pin used to control the shutter speed 1 H

--

control 1

by 1 H. (Refer to

MODE TABLE ",)

Shutter speed

When the EXMD input pin is Low level, the EXST

12

EXMD

--

control 2

(pin 11) is prohibited. (Refer to "SHUTTER MODE

TABLE" .)

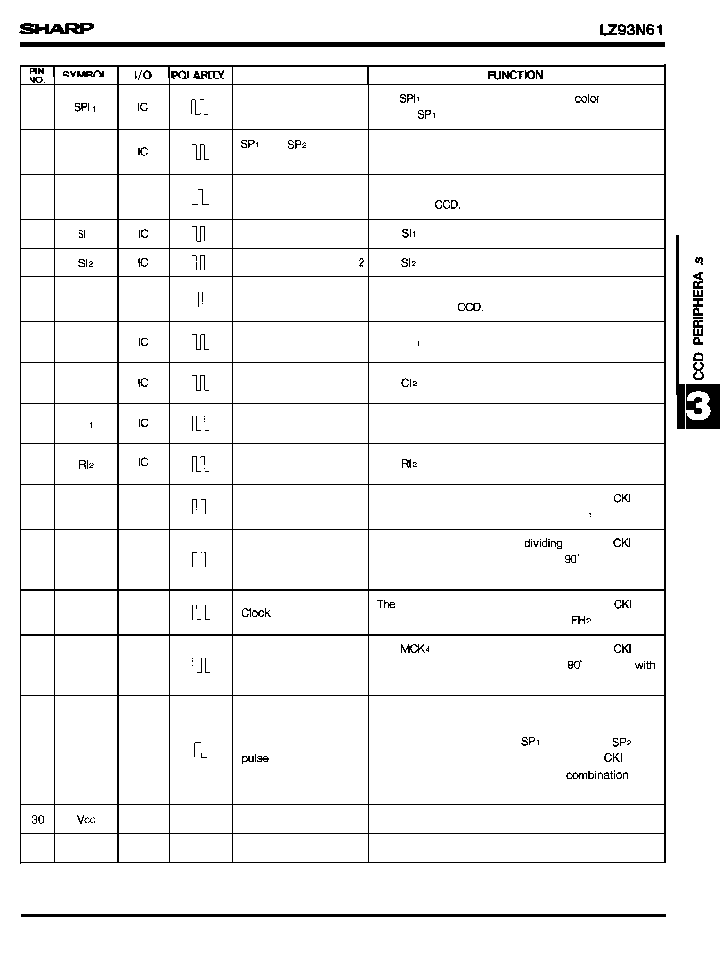

The SPI pin output the sampling pulse for color

13

SP1

o

Color sampling

pulse 1

modulation

upon the output signal of

It outputs at High level of the SE (pin 29).

sampling

The SP2 pin output the sampling pulse for

14

SP2

o

based upon the output signal of

pulse 2

It outputs at Low level of the SE (pin 29).

290

I

PIN NAME

--------

15

SPI

and SP2 phase

The

pin sets the falling edge of

sampling

control input 1

pulses

(pin 13) and SP2 (pin 14).

16

SP12

and

phase

The SP12 pin sets the rising edge of color sampling

control input 2

pulses SPI (pin 13) and SP2 (pin 14).

17

FS

o

CDS pulse 2

The FS pin outputs the pulses for sampling output

signals of

18

1

FS phase control input 1

The

pin sets the phase of the FS (pin 17).

19

FS phase control input

The

pin sets the width of the FS (pin 17).

20

FCDS

o

FCDS pulse 1

The FCDS pin outputs the pulse to clamp the out-

put signals of

21

c11

FCDS phase control

The Cl pin sets the phase of the FCDS (pin 20).

input 1

22

C12

FCDS phase control

The

pin sets the width of the FCDS (pin 20).

input 2

23

RI

FR phase control

The RI

I

pin sets the pahse of the FR (pin 42).

input 1

24

FR phase control

The

pin sets the width of the FR (pin 42).

input 2

25

MCKI

o

Clock output 1

The MCKI pin outputs 1/2 dividing pulse of

(pin

46). It is the same phase with the FH (pin 45).

The MCK2 pin outputs 1/2

pulse of

(pin

26

MCK2

o

Clink output 2

46). It is delayad by approximately

in phase with

respect to FH1 (pin 45).

27

MCK3

o

output 3

MCK3 pin outputs 1/2 dividing pulse of

(pin

46). It is the same phase with the

(pin 44).

The

pin outputs 1/2 dividing pulse of

(pin

28

MCK4

o

Clock output 4

46). It is delayed by approximately

in phase

respect to FH2 (pin 44).

The SE pin outputs the demodulation carrier of out-

put signals of CCD, and input the switching signal

29

SE

o

Color demodulation

of color sampling pulses

(pin 13) and

(pin

14). It outputs 1/4 dividing pulse of the

input

(pin 46), and selects the phase in

with

the SESL (pin 32) and the SINV (pin 34).

--

Power supply

The Vcc is a + 5 V power supply pin.

31

GND

Ground

The GND is a ground pin.

291