Semiconductor Group

1

3.3V 4M

◊

64-Bit EDO-DRAM Module

3.3V 4M x 72-Bit EDO-DRAM Module

168pin unbuffered DIMM Module

with serial presence detect

HYM64V4005GU-50/-60

HYM64V4045GU-50/-60

HYM72V4005GU-50/-60

HYM72V4045GU-50/-60

∑

168 Pin JEDEC Standard, Unbuffered 8 Byte Dual In-Line Memory Module

for PC main memory applications

∑

1 bank 4M x 64, 4M x 72 in 2k and 4k refresh organisations

∑

Optimized for byte-write non-parity or ECC applications

∑

Extended Data Out (EDO)

∑

Performance:

∑

Single +3.3 V

±

0.3 V Power Supply

∑

CAS-before-RAS refresh, RAS-only-refresh

∑

Decoupling capacitors mounted on substrate

∑

All inputs, outputs and clocks are fully LV-TTL compatible

∑

Serial presence detects (optional)

∑

Utilizes 4M x 4 -DRAMs in TSOPII packages

∑

2048 refresh cycles / 32 ms with 11 / 11 addressing ( Row / Column) for HYM64/72V4005GU

∑

4096 refresh cycles / 64 ms with 12 / 10 addressing ( Row / Column) for HYM64/72V4045GU

∑

Gold contact pads

∑

Card Size: 133,35mm x 25,40 mm x 4,00 mm

∑

This DRAM product module family is intended to be fully pin and architecture compatible

with the 168pin unbuffered SDRAM DIMM module family

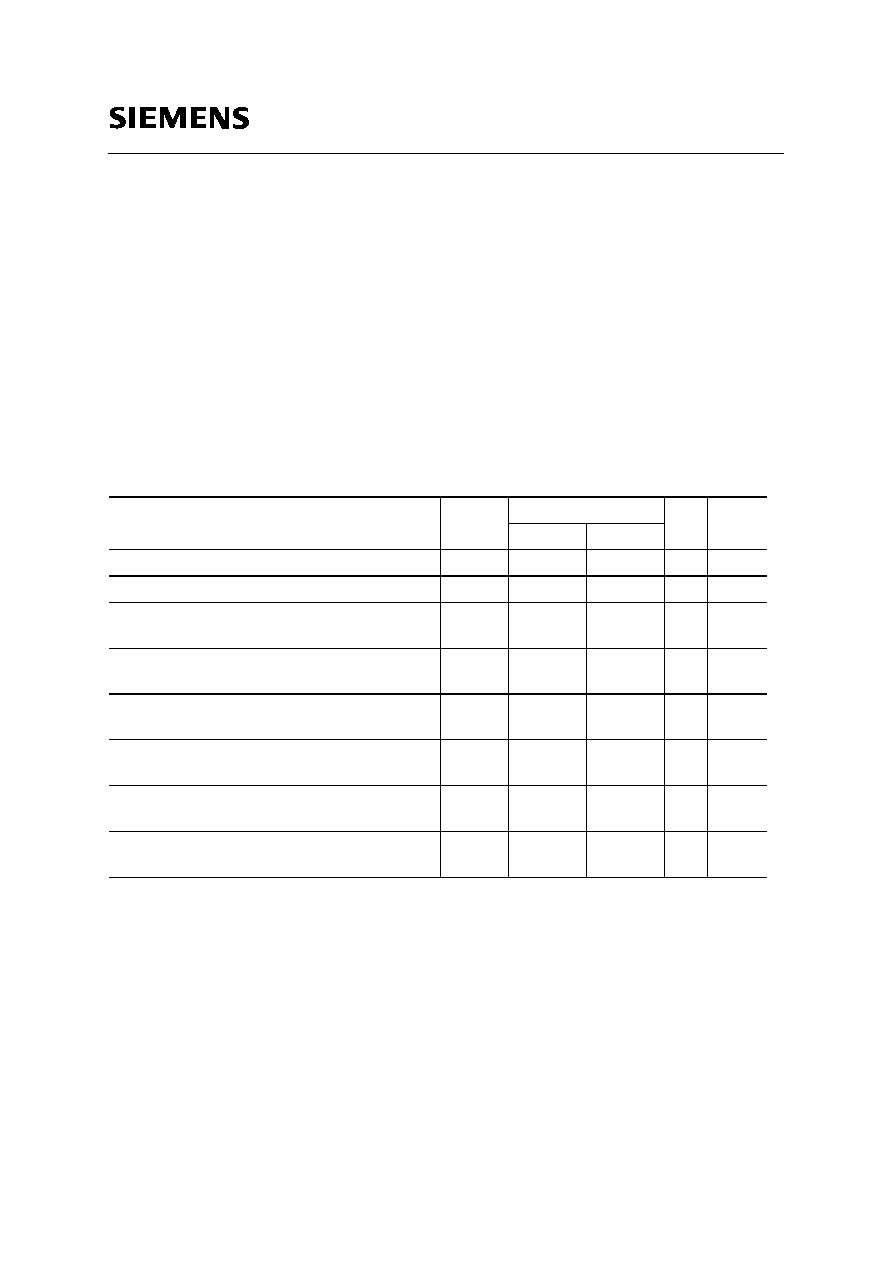

-50 -60

tRAC

RAS Access Time

50 ns

60 ns

tCAC

CAS Access Time

13 ns

15 ns

tAA

Access Time from Address

25 ns

30 ns

tRC

Cycle Time

84 ns

104 ns

tHPC

EDO Mode Cycle Time

20 ns

25 ns

1

2.97

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

2

The HYM64(72)V4005/45GU-50/-60 are industry standard 168-pin 8-byte Dual In-Line Memory

Modules (DIMMs) which are organized as 4M x 64 and 4M x 72 high speed memory arrays

designed with EDO DRAMs for non-parity and ECC applications. 2k refresh with 11 / 11 addressing

and 4k refresh modules with 12 / 10 addressing are available. The DIMMs use sixteen 4M x 4 EDO

DRAMs for the 4M x 64 organisation and eighteen 4M x 4 DRAMs for the 4M x 72 organisation, both

in TSOPII packages. Decoupling capacitors are mounted on the PC board.

The DIMMs use optional serial presence detects implemented via a serial E

2

PROM using the two

pin I

2

C protocol. The first 128 bytes are utilized by the DIMM manufacturer and the second 128

bytes of serial PD data are available to the customer.

All 168-pin DIMMs provide a high performance, flexible 8-byte interface in a 133,35 mm long space-

saving footprint.

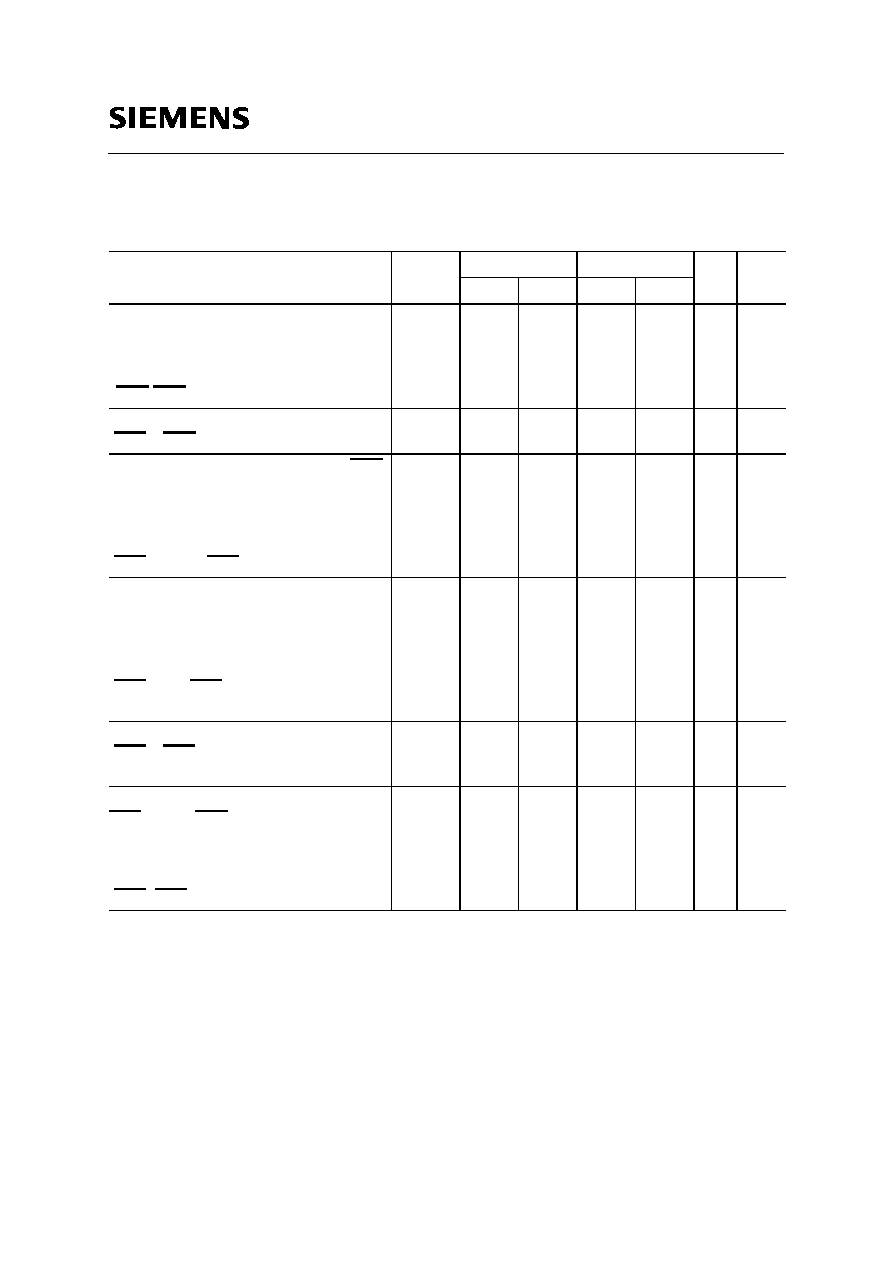

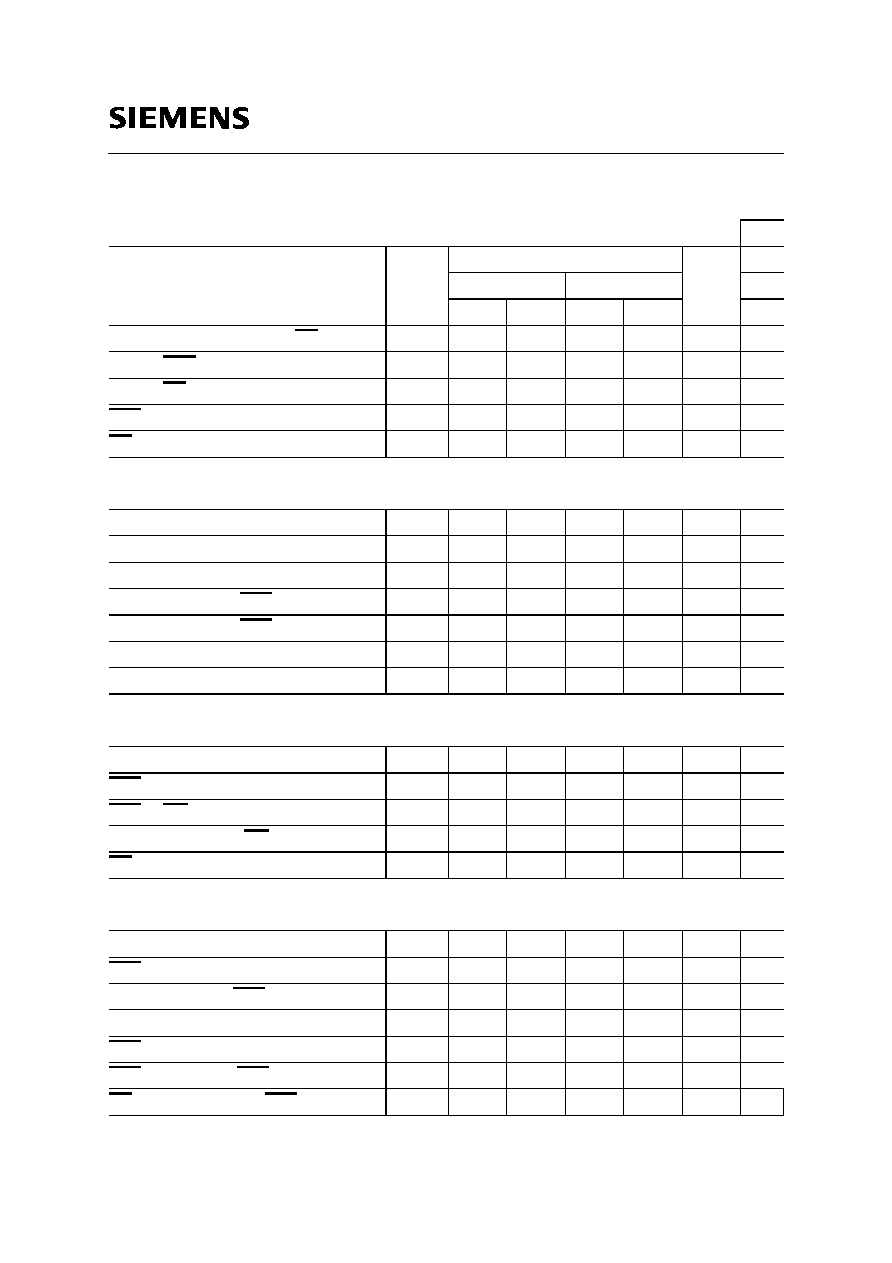

Ordering Information

Type

Ordering

Code

Package

Descriptions

2k-Refresh:

HYM 64V4005GU-50

Q67100-Q2184

L-DIM-168-12

4M x 64 DRAM module (access time 50 ns)

HYM 64V4005GU-60

Q67100-Q2185

L-DIM-168-12

4M x 64 DRAM module (access time 60 ns)

HYM 72V4005GU-50

Q67100-Q2186

L-DIM-168-12

4M x 72 DRAM module (access time 50 ns)

HYM 72V4005GU-60

Q67100-Q2187

L-DIM-168-12

4M x 72 DRAM module (access time 60 ns)

4k-Refresh:

HYM 64V4045GU-50

L-DIM-168-12

4M x 64 DRAM module (access time 50 ns)

HYM 64V4045GU-60

L-DIM-168-12

4M x 64 DRAM module (access time 60 ns)

HYM 72V4045GU-50

L-DIM-168-12

4M x 72 DRAM module (access time 50 ns)

HYM 72V4045GU-60

L-DIM-168-12

4M x 72 DRAM module (access time 60 ns)

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

3

Pin Names

A0-A10

Row Address Input for HYB64/72V4005

A0-A10

Column Address Input for HYB64/72V4005

A0-A11

Row Address Input for HYB64/72V4045

A0-A9

Column Address Input for HYB64/72V4045

DQ0 - DQ63

Data Input/Output

CB0-CB7

Check Bit Data Input/Output ( x72 only)

RAS0, RAS2

Row Address Strobe

CAS0 - CAS7

Column Address Strobe

WE0, WE2

Read / Write Input

OE0, OE2

Output Enable

Vcc

Power (+3.3 Volt)

Vss

Ground

SCL

Clock for Presence Detect

SDA

Serial Data Out for Presence Detect

SA0-SA2

Serial Presence Detect Addresses

N.C.

No Connection

DU

Don't use

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

4

Pin Configuration

PIN #

Symbol

PIN #

Symbol

PIN #

Symbol

PIN #

Symbol

1

VSS

43

VSS

85

VSS

127

VSS

2

DQ0

44

OE2

86

DQ32

128

DU

3

DQ1

45

RAS2

87

DQ33

129

NC

4

DQ2

46

CAS2

88

DQ34

130

CAS6

5

DQ3

47

CAS3

89

DQ35

131

CAS7

6

VCC

48

WE2

90

VCC

132

DU

7

DQ4

49

VCC

91

DQ36

133

VCC

8

DQ5

50

NC

92

DQ37

134

NC

9

DQ6

51

NC

93

DQ38

135

NC

10

DQ7

52

CB3

94

DQ39

136

CB6

11

DQ8

53

CB3

95

DQ40

137

CB7

12

VSS

54

VSS

96

VSS

138

VSS

13

DQ9

55

DQ16

97

DQ41

139

DQ48

14

DQ10

56

DQ17

98

DQ42

140

DQ49

15

DQ11

57

DQ18

99

DQ43

141

DQ50

16

DQ12

58

DQ19

100

DQ44

142

DQ51

17

DQ13

59

VCC

101

DQ45

143

VCC

18

VCC

60

DQ20

102

VCC

144

DQ52

19

DQ14

61

NC

103

DQ46

145

NC

20

DQ15

62

DU

104

DQ47

146

DU

21

CB0

63

NC

105

CB4

147

NC

22

CB1

64

VSS

106

CB5

148

VSS

23

VSS

65

DQ21

107

VSS

149

DQ53

24

NC

66

DQ22

108

NC

150

DQ54

25

NC

67

DQ23

109

NC

151

DQ55

26

VCC

68

VSS

110

VCC

152

VSS

27

WE0

69

DQ24

111

DU

153

DQ56

28

CAS0

70

DQ25

112

CAS4

154

DQ57

29

CAS1

71

DQ26

113

CAS5

155

DQ58

30

RAS0

72

DQ27

114

NC

156

DQ59

31

OE0

73

VCC

115

DU

157

VCC

32

VSS

74

DQ28

116

VSS

158

DQ60

33

A0

75

DQ29

117

A1

159

DQ61

34

A2

76

DQ30

118

A3

160

DQ62

35

A4

77

DQ31

119

A5

161

DQ63

36

A6

78

VSS

120

A7

162

VSS

37

A8

79

NC

121

A9

163

NC

38

A10

80

NC

122

A11

164

NC

39

NC

81

NC

123

NC

165

SA0

40

VCC

82

SDA

124

VCC

166

SA1

41

VCC

83

SCL

125

DU

167

SA2

42

DU

84

VCC

126

DU

168

VCC

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

5

4M x 64 DIMM Module Block Diagram

I/O1-I/O4

D0

I/O1-I/O4

D1

I/O1-I/O4

D2

I/O1-I/O4

D3

I/O1-I/O4

D4

I/O1-I/O4

D5

I/O1-I/O4

D6

I/O1-I/O4

D7

I/O1-I/O4

D8

I/O1-I/O4

D9

I/O1-I/O4

D10

I/O1-I/O4

D11

I/O1-I/O4

D12

I/O1-I/O4

D13

I/O1-I/O4

D14

I/O1-I/O4

D15

DQ0-DQ3

DQ4-DQ7

RAS0

WE0

OE0

DQ8-DQ11

DQ12-DQ15

DQ16-DQ19

D20-DQ23

DQ24-DQ27

DQ28-DQ31

DQ32-DQ35

D36-DQ39

RAS2

WE2

OE2

DQ40-DQ43

DQ44-DQ47

DQ48-DQ51

DQ52-DQ55

DQ56-DQ59

DQ60-DQ63

CAS0

CAS1

CAS2

CAS3

CAS4

CAS5

CAS6

CAS7

A0-A10,(A11)

VCC

VSS

D0-D15

C0-C15

SCL

SDA

SA0

SA1

SA2

E

2

PROM (256wordx8bit)

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

6

4M x 72 DIMM Module Block Diagram

I/O1-I/O4

D0

I/O1-I/O4

D1

I/O1-I/O4

D2

I/O1-I/O4

D3

I/O1-I/O4

D16

I/O1-I/O4

D4

I/O1-I/O4

D5

I/O1-I/O4

D6

I/O1-I/O4

D7

I/O1-I/O4

D8

I/O1-I/O4

D9

I/O1-I/O4

D10

I/O1-I/O4

D11

I/O1-I/O4

D17

I/O1-I/O4

D12

I/O1-I/O4

D13

I/O1-I/O4

D14

I/O1-I/O4

D15

DQ0-DQ3

DQ4-DQ7

RAS0

WE0

OE0

DQ8-DQ11

DQ12-DQ15

CB0-CB3

DQ16-DQ19

D20-DQ23

DQ24-DQ27

DQ28-DQ31

DQ32-DQ35

D36-DQ39

RAS2

WE2

OE2

DQ40-DQ43

DQ44-DQ47

CB4-CB7

DQ48-DQ51

DQ52-DQ55

DQ56-DQ59

DQ60-DQ63

CAS0

CAS1

CAS2

CAS3

CAS4

CAS5

CAS6

CAS7

A0-A10,(A11)

VCC

VSS

D0-D17

C0-C17

SCL

SDA

SA0

SA1

SA2

E

2

PROM (256wordx8bit)

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

7

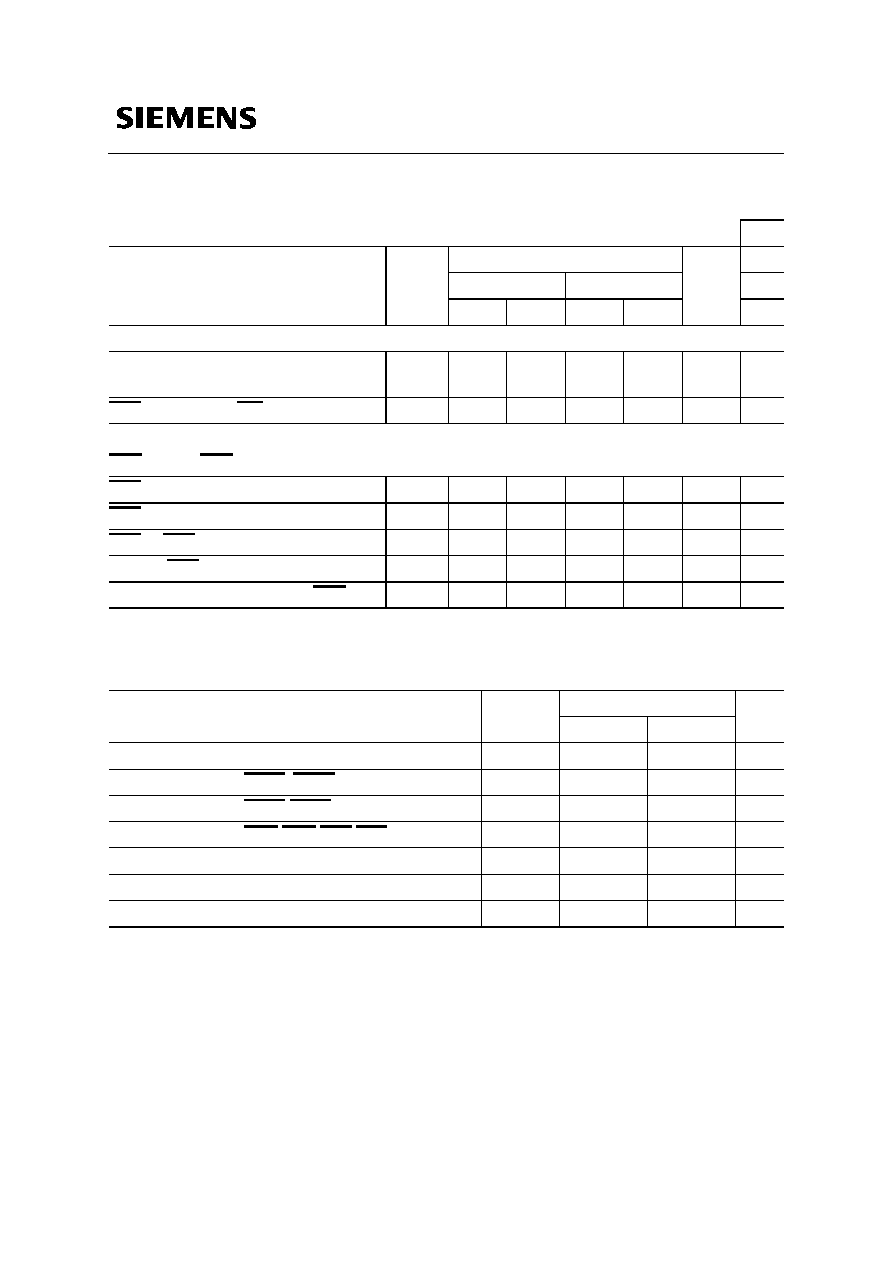

TRUTH TABLE

FUNCTION

RAS

CAS

WRITE

OE

ROW

ADDR

COL

ADDR

DQ0-DQ63

Standby

H

X

X

X

X

X

High Impedance

Read

L

L

H

L

ROW

COL

Data Out

Early-Write

L

L

L

X

ROW

COL

Data In

Late-Write

L

L

H - L

H

ROW

COL

Data In

Read-Modify-Write

(RMW)

L

L

H - L

L - H

ROW

COL

Data Out, Data In

EDO Page Mode Read

1st Cycle

L

H - L

H

L

ROW

COL

Data Out

2nd Cycle

L

H - L

H

L

n/a

COL

Data Out

EDO Page Mode Write

1st Cycle

L

H - L

L

X

ROW

COL

Data In

2nd Cycle

L

H - L

L

X

n/a

COL

Data In

EDO Page Mode RMW

1st Cycle

L

H - L

H - L

L - H

ROW

COL

Data Out, Data In

2st Cycle

L

H - L

H - L

L - H

n/a

COL

Data Out, Data In

RAS only refresh

L

H

X

X

ROW

n/a

High Impedance

CAS-before-RAS refresh

H - L

L

H

X

X

n/a

High Impedance

Hidden Refresh

READ

L-H-L

L

H

L

ROW

COL

Data Out

WRITE

L-H-L

L

L

X

ROW

COL

Data In

Self Refresh

H - L

L

H

X

X

X

High Impedance

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

8

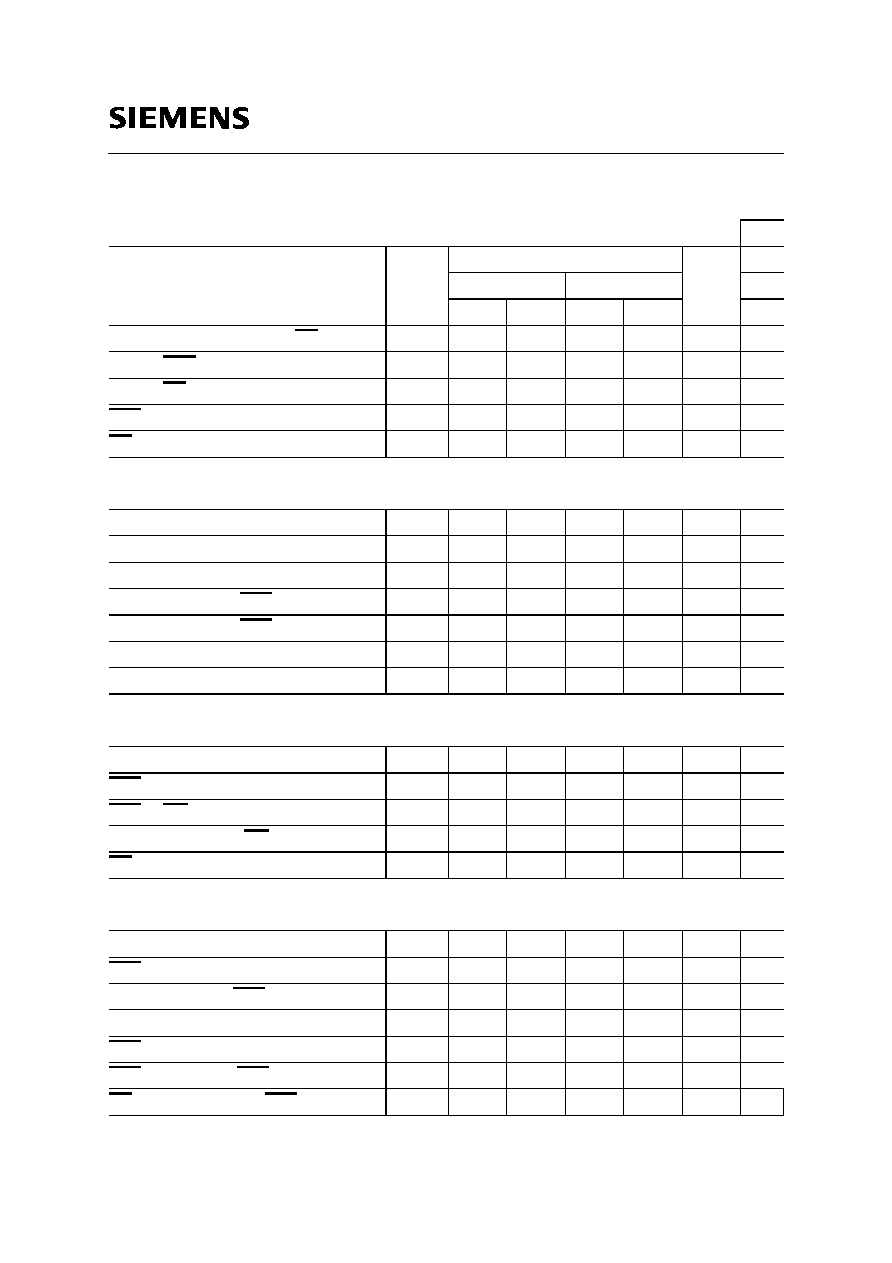

Absolute Maximum Ratings

Operating temperature range .........................................................................................

0 to + 70 ∞C

Storage temperature range......................................................................................

≠ 55 to + 125 ∞C

Input/output voltage ..............................................................................

≠0.5 to min (Vcc+0.5, 4.6) V

Power supply voltage....................................................................................................

≠0.5 to 4.6 V

Power dissipation..................................................................................................................

9.94 W

Data out current (short circuit) ................................................................................................

50 mA

Note:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent

damage to the device. Exposure to absolute maximum rating conditions for extended periods

may affect device reliability.

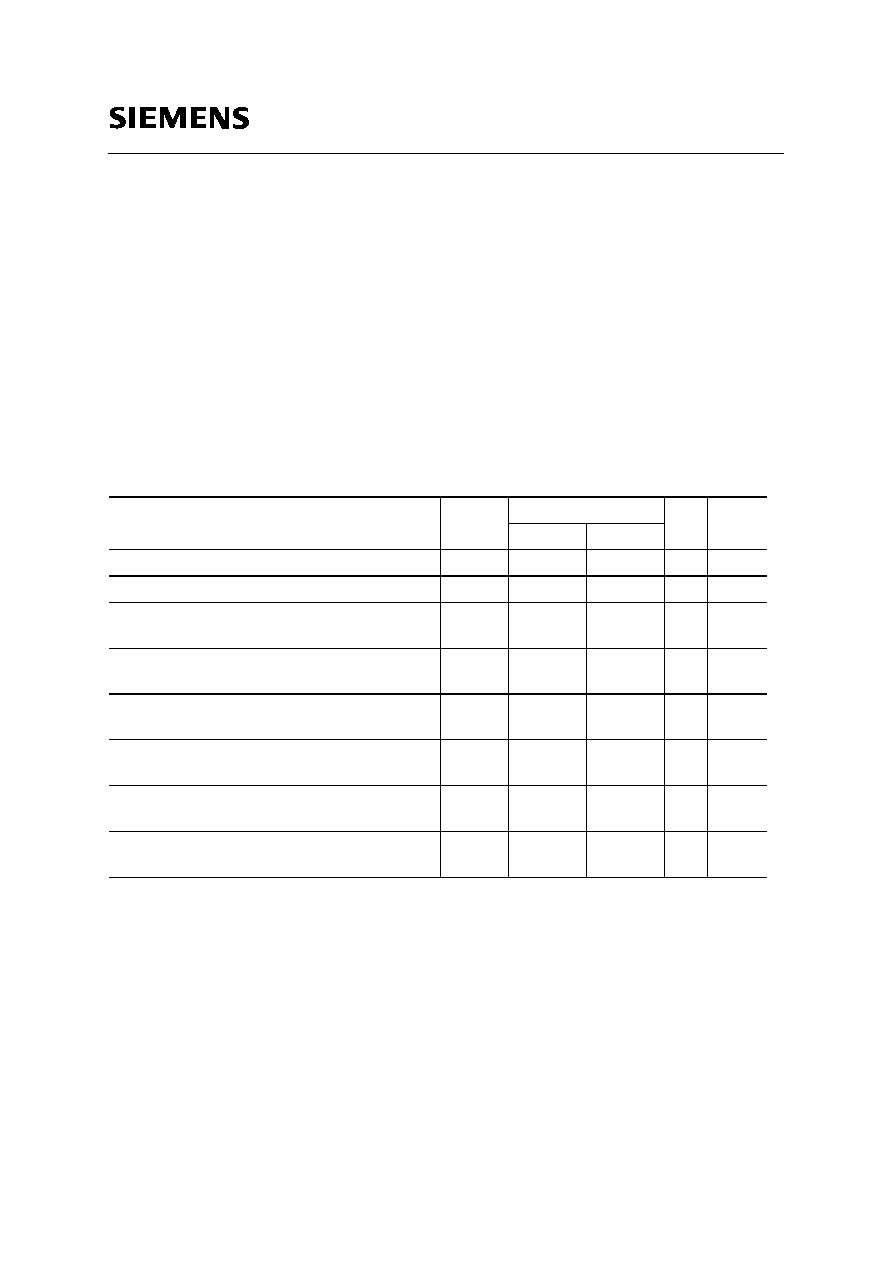

DC Characteristics

T

A

= 0 to 70 ∞C;

V

CC

= 3.3 V

±

0.3 V

Parameter

Symbol

x 64/ x72

Unit Notes

min.

max.

Input high voltage

V

IH

2.0

Vcc + 0.5 V

1)

Input low voltage

V

IL

≠ 0.5

0.8

V

1)

Output high voltage (LVTTL)

Output ,,H" level voltage (

I

OUT

= ≠ 2 mA)

V

OH

2.4

≠

V

1)

Output low voltage (LVTTL)

Output ,,L" level voltage (

I

OUT

= + 2 mA)

V

OL

≠

0.4

V

1)

Output high voltage (LVCMOS)

Output ,,H" level voltage (

I

OUT

=≠ 100

µ

A)

V

OH

Vcc-0.2

≠

V

1)

Output low voltage (LVCMOS)

Output ,,L" level voltage (

I

OUT

=+100

µ

A)

V

OL

≠

0.4

V

1)

Input leakage current

(0 V <

V

IN

< Vcc, all other pins = 0 V)

I

I(L)

≠ 10

10

µ

A

1)

Output leakage current

(DO is disabled, 0 V <

V

OUT

< Vcc)

I

O(L)

≠ 10

+10

µ

A

1)

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

9

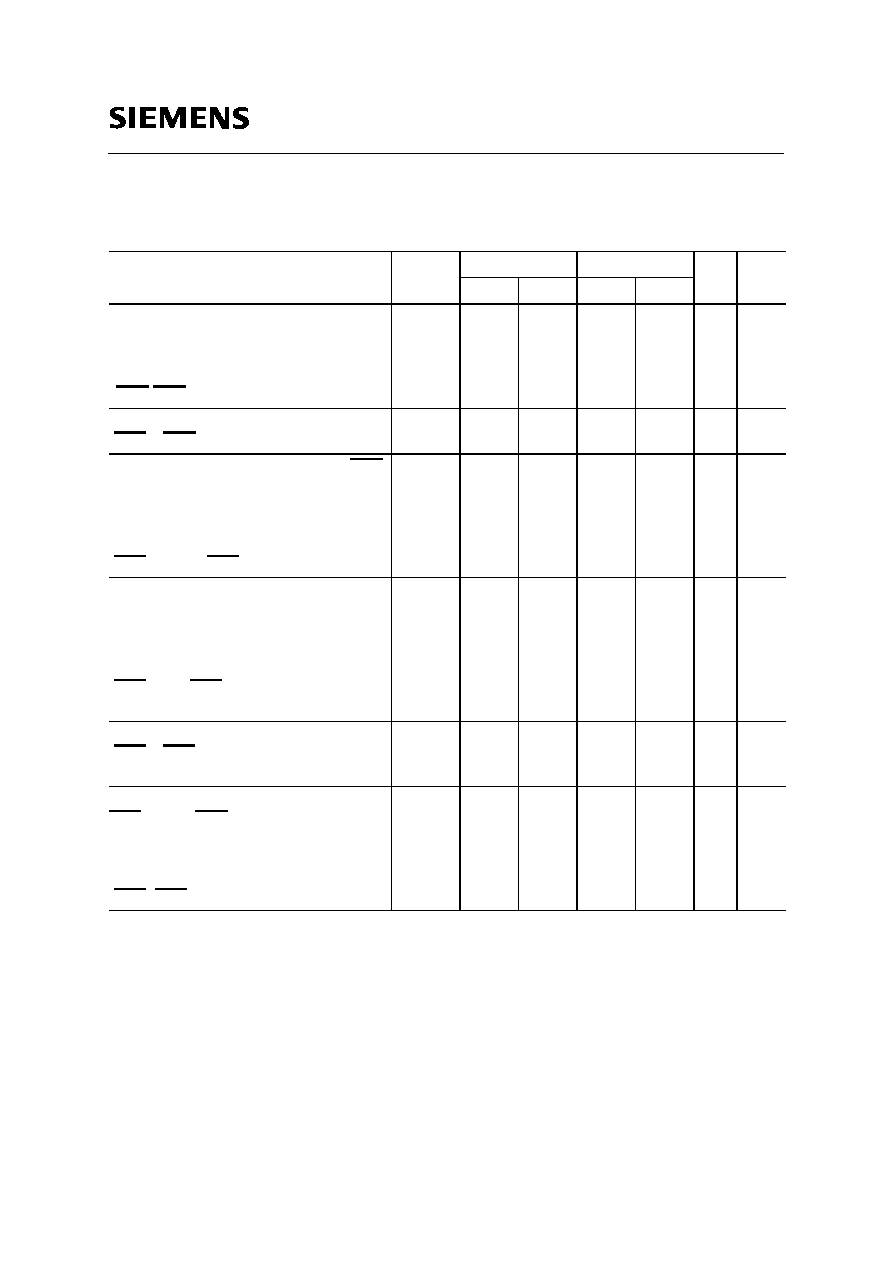

DC Characteristics for HYM64/72V4005

T

A

= 0 to 70 ∞C;

V

CC

= 3.3 V

±

0.3 V

Parameter

Symbol

x 64

x 72

Unit Note

s

min.

max.

min.

max.

Average

V

CC

supply current:

-50 version

-60 version

(RAS,CAS,address cycling,

t

RC

=

t

RC

min.)

I

CC1

≠

≠

1920

1760

≠

≠

2160

1980

mA

mA

2) 3)

4)

Standby

V

CC

supply current

(RAS = CAS =

V

IH,

one address change)

I

CC2

≠

32

≠

36

mA

≠

Average

V

CC

supply current during RAS

only refresh cycles:

-50 version

-60 version

(RAS cycling, CAS =

V

IH

, t

RC

=

t

RC

min.)

I

CC3

≠

≠

1920

1760

≠

≠

2160

1980

mA

mA

2) 4)

Average

V

CC

supply current during

hyper page mode (EDO):

-50 version

-60 version

(RAS =

V

IL,

CAS, address cycling

t

PC

=

t

PC

min.)

I

CC4

≠

≠

1120

880

≠

≠

1260

990

mA

mA

2) 3)

4)

Standby

V

CC

supply current

(RAS = CAS =

V

CC

≠ 0.2 V, one address

change)

I

CC5

≠

16

≠

18

mA

≠

Average

V

CC

supply current during

CAS-before-RAS refresh mode:

-50 version

-60 version

(RAS, CAS cycling

, t

RC

=

t

RC

min.)

I

CC6

≠

≠

1920

1760

≠

≠

2160

1980

mA

mA

2) 4)

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

10

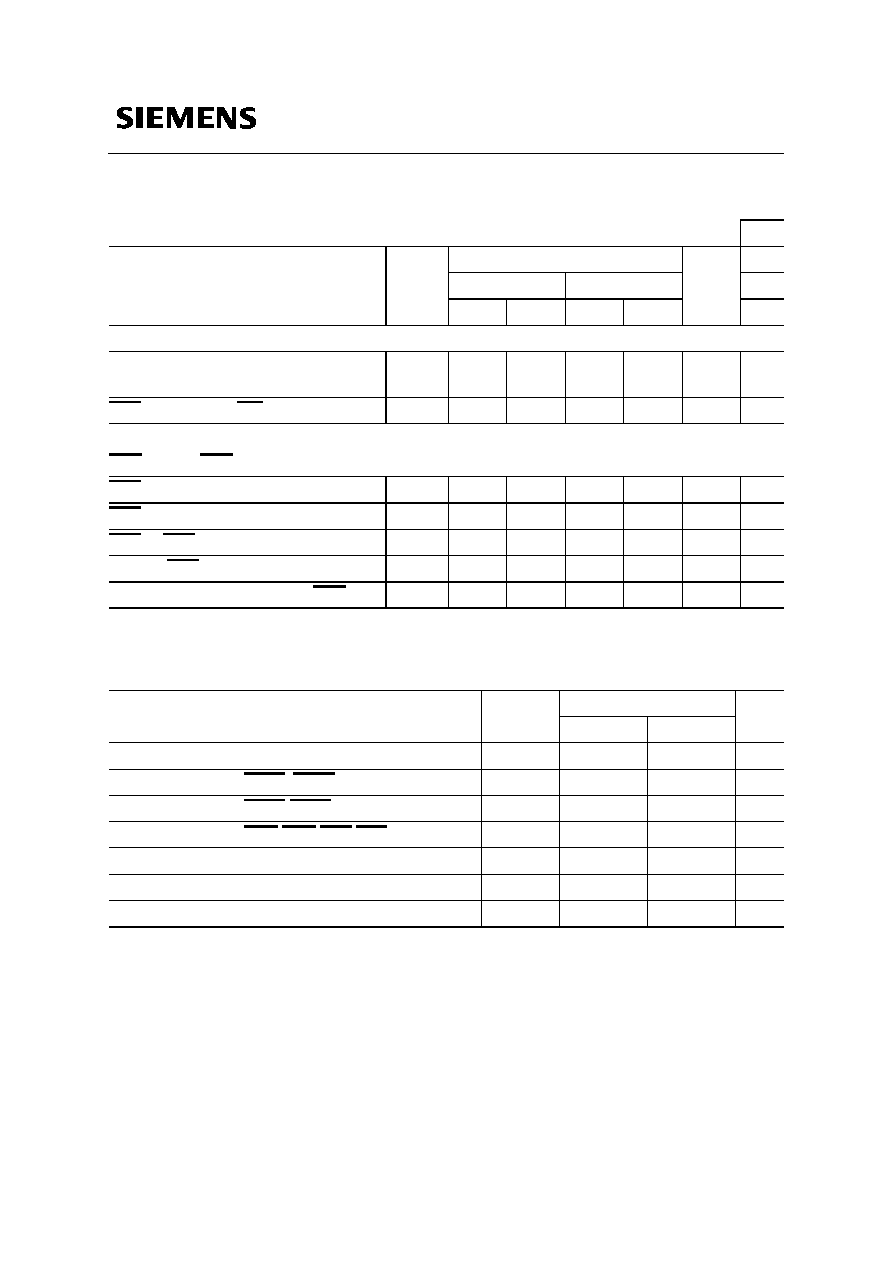

DC Characteristics for HYM64/72V4045

T

A

= 0 to 70 ∞C;

V

CC

= 3.3 V

±

0.3 V

Parameter

Symbol

x 64

x 72

Unit Note

s

min.

max.

min.

max.

Average

V

CC

supply current:

-50 version

-60 version

(RAS,CAS,address cycling,

t

RC

=

t

RC

min.)

I

CC1

≠

≠

1600

1440

≠

≠

1800

1620

mA

mA

2) 3)

4)

Standby

V

CC

supply current

(RAS = CAS =

V

IH,

one address change)

I

CC2

≠

32

≠

36

mA

≠

Average

V

CC

supply current during RAS

only refresh cycles:

-50 version

-60 version

(RAS cycling, CAS =

V

IH

, t

RC

=

t

RC

min.)

I

CC3

≠

≠

1600

1440

≠

≠

1800

1620

mA

mA

2) 4)

Average

V

CC

supply current during

hyper page mode (EDO):

-50 version

-60 version

(RAS =

V

IL,

CAS, address cycling

t

PC

=

t

PC

min.)

I

CC4

≠

≠

1120

880

≠

≠

1260

990

mA

mA

2) 3)

4)

Standby

V

CC

supply current

(RAS = CAS =

V

CC

≠ 0.2 V, one address

change)

I

CC5

≠

16

≠

18

mA

≠

Average

V

CC

supply current during

CAS-before-RAS refresh mode:

-50 version

-60 version

(RAS, CAS cycling

, t

RC

=

t

RC

min.)

I

CC6

≠

≠

1600

1440

≠

≠

1800

1620

mA

mA

2) 4)

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

11

AC Characteristics

5)6)

16E

T

A

= 0 to 70 ∞C,

V

CC

= 3.3 V

±

0.3 V,

t

T

= 2 ns

Parameter

Symbol

Limit Values

Unit

Note

-50

-60

min.

max.

min.

max.

common parameters

Random read or write cycle time

t

RC

84

≠

104

≠

ns

RAS precharge time

t

RP

30

≠

40

≠

ns

RAS pulse width

t

RAS

50

10k

60

10k

ns

CAS pulse width

t

CAS

8

10k

10

10k

ns

Row address setup time

t

ASR

0

≠

0

≠

ns

Row address hold time

t

RAH

8

≠

10

≠

ns

Column address setup time

t

ASC

0

≠

0

≠

ns

Column address hold time

t

CAH

8

≠

10

≠

ns

RAS to CAS delay time

t

RCD

12

37

14

45

ns

RAS to column address delay

t

RAD

10

25

12

30

ns

RAS hold time

t

RSH

13

15

≠

ns

CAS hold time

t

CSH

40

50

≠

ns

CAS to RAS precharge time

t

CRP

5

≠

5

≠

ns

Transition time (rise and fall)

t

T

1

50

1

50

ns

7

Refresh period for 2k-refresh

t

REF

≠

32

≠

32

ms

Refresh period for 4k-refresh

t

REF

≠

64

≠

64

ms

Read Cycle

Access time from RAS

t

RAC

≠

50

≠

60

ns

8, 9

Access time from CAS

t

CAC

≠

13

≠

15

ns

8, 9

Access time from column address

t

AA

≠

25

≠

30

ns

8,10

OE access time

t

OEA

≠

13

≠

15

ns

Column address to RAS lead time

t

RAL

25

≠

30

≠

ns

Read command setup time

t

RCS

0

≠

0

≠

ns

Read command hold time

t

RCH

0

≠

0

≠

ns

11

Read command hold time referenced to

RAS

t

RRH

0

≠

0

≠

ns

11

CAS to output in low-Z

t

CLZ

0

≠

0

≠

ns

8

Output buffer turn-off delay

t

OFF

0

13

0

15

ns

12

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

12

Output turn-off delay from OE

t

OEZ

0

13

0

15

ns

12

Data to CAS low delay

t

DZC

0

≠

0

≠

ns

13

Data to OE low delay

t

DZO

0

≠

0

≠

ns

13

CAS high to data delay

t

CDD

10

≠

13

≠

ns

14

OE high to data delay

t

ODD

10

≠

13 ≠

ns

14

Write Cycle

Write command hold time

t

WCH

8

≠

10

≠

ns

Write command pulse width

t

WP

8

≠

10

≠

ns

Write command setup time

t

WCS

0

≠

0

≠

ns

15

Write command to RAS lead time

t

RWL

13

≠

15

≠

ns

Write command to CAS lead time

t

CWL

13

≠

15

≠

ns

Data setup time

t

DS

0

≠

0

≠

ns

16

Data hold time

t

DH

8

≠

10

≠

ns

16

Read-modify-Write Cycle

Read-write cycle time

t

RWC

113

≠

138

≠

ns

RAS to WE delay time

t

RWD

64

≠

77

≠

ns

15

CAS to WE delay time

t

CWD

27

≠

32

≠

ns

15

Column address to WE delay time

t

AWD

39

≠

47

≠

ns

15

OE command hold time

t

OEH

10

≠

13

≠

ns

Hyper Page Mode (EDO) Cycle

EDO cycle time

t

HPC

20

≠

25

≠

ns

CAS precharge time

t

CP

8

≠

10

≠

ns

Access time from CAS precharge

t

CPA

≠

27

≠

32

ns

7

Output data hold time

t

COH

5

≠

5

≠

ns

RAS pulse width in EDO mode

t

RAS

50

200k

60

200k ns

CAS precharge to RAS Delay

t

RHPC

27

≠

32

≠

ns

OE setup time prior to CAS

t

OES

5

≠

5

≠

ns

AC Characteristics (cont'd)

5)6)

16E

T

A

= 0 to 70 ∞C,

V

CC

= 3.3 V

±

0.3 V,

t

T

= 2 ns

Parameter

Symbol

Limit Values

Unit

Note

-50

-60

min.

max.

min.

max.

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

13

Capacitance

T

A

= 0 to 70 ∞C;

V

CC

= 3.3 V

±

0.3 V;

f

= 1 MHz

Hyper Page Mode (EDO) Read-modify-Write Cycle

Hyper page mode (EDO) read-write

cycle time

t

PRWC

58

≠

68

≠

ns

CAS precharge to WE

t

CPWD

41

≠

49

≠

ns

CAS-before-RAS Refresh Cycle

CAS setup time

t

CSR

10

≠

10

≠

ns

CAS hold time

t

CHR

10

≠

10

≠

ns

RAS to CAS precharge time

t

RPC

5

≠

5

≠

ns

Write to RAS precharge time

t

WRP

10

≠

10

≠

ns

Write hold time referenced to RAS

t

WRH

10

≠

10

≠

ns

Parameter

Symbol

Limit Values

Unit

min.

max.

Input Capacitance (A0 to A11)

C

I1

≠

100

pF

Input Capacitance (RAS0, RAS2)

C

I2

≠

75

pF

Input Capacitance (CAS0-CAS7)

C

I3

≠

18

pF

Input Capacitance (WE0,WE2,OE0,OE2)

C

I4

≠

75

pF

I/O Capacitance (DQ0-DQ63,CB0-CB8)

C

IO1

≠

11

pF

Input Capacitance (SCL, SA0-2)

C

s

≠

8

pF

Input/Output Capacitance (SDA)

Cs

≠

10

pF

AC Characteristics (cont'd)

5)6)

16E

T

A

= 0 to 70 ∞C,

V

CC

= 3.3 V

±

0.3 V,

t

T

= 2 ns

Parameter

Symbol

Limit Values

Unit

Note

-50

-60

min.

max.

min.

max.

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

14

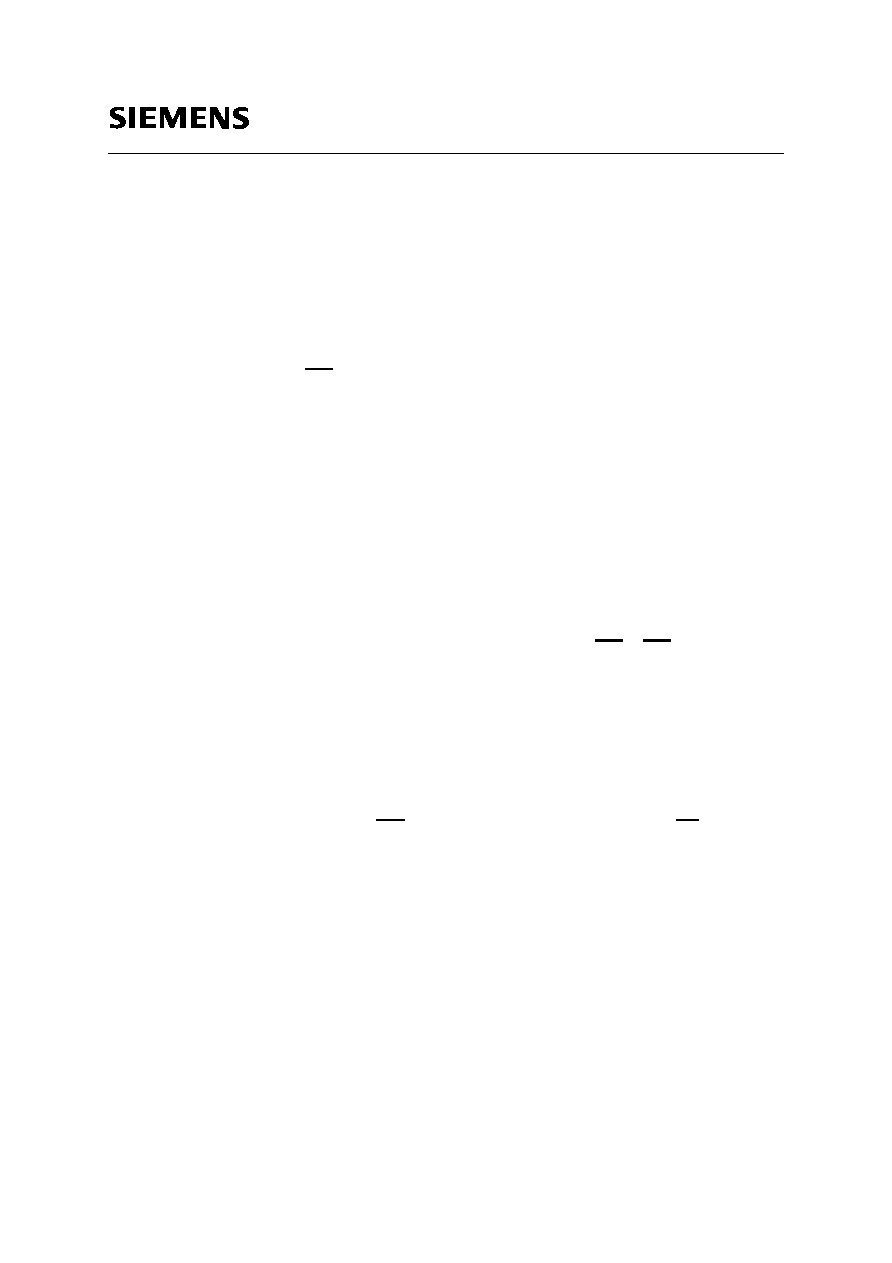

Notes:

1) All voltages are referenced to

V

SS

.

2)

I

CC1

,

I

CC3

,

I

CC4

and

I

CC6

depend on cycle rate.

3)

I

CC1

and

I

CC4

depend on output loading. Specified values are obtained with the output open.

4) Address can be changed once or less while RAS = Vil. In case of ICC4 it can be changed once or less during

a hyper page mode (EDO) cycle

5) An initial pause of 200

µ

s is required after power-up followed by 8 RAS cycles of which at least one cycle has

to be a refresh cycle, before proper device operation is achieved. In case of using the internal refresh counter,

a minimum of 8 CAS-before-RAS initialization cycles instead of 8 RAS cycles are required.

6) AC measurements assume

t

T

= 2 ns.

7)

V

I

H

(min.)

and

V

I

L (max.)

are reference levels for measuring timing of input signals. Transition times are also

measured between

V

I

H

and

V

I

L

.

8) Measured with the specified current load and 100 pF at Vol = 0.8 V and Voh = 2.0 V. Access time is determined

by the latter of t

RAC

, t

CAC

, t

AA

,t

CPA

,t

OEA

. t

CAC

is measured from tristate.

9) Operation within the

t

RCD (max.)

limit ensures that

t

RAC (max.)

can be met.

t

RCD (max.)

is specified as a reference point

only. If

t

RCD

is greater than the specified

t

RCD (max.)

limit, then access time is controlled by

t

CAC

.

10) Operation within the

t

RAD (max.

)

limit ensures that

t

RAC (max.)

can be met.

t

RAD (max.)

is specified as a reference point

only. If

t

RAD

is greater than the specified

t

RAD (max.)

limit, then access time is controlled by

t

AA

.

11) Either

t

RCH

or

t

RRH

must be satisfied for a read cycle.

12)

t

OFF (max.)

,

t

OEZ (max.)

define the time at which the output achieves the open-circuit conditions and are not

referenced to output voltage levels.

t

OFF

is referenced from the rising edge of RAS or CAS, whichever occurs

last.

13) Either

t

DZC

or

t

DZO

must be satisfied.

14) Either

t

CDD

or

t

ODD

must be satisfied.

15)

t

WCS

,

t

RWD

,

t

CWD

and

t

AWD

are not restrictive operating parameters. They are included in the data sheet as

electrical characteristics only. If

t

WCS

>

t

WCS (min.)

, the cycle is an early write cycle and data out pin will remain

open-circuit (high impedance) through the entire cycle; if

t

RWD

>

t

RWD (min.)

,

t

CWD

>

t

CWD (min.)

and

t

AWD

>

t

AWD (min.)

,

the cycle is a read-write cycle and I/O will contain data read from the selected cells. If neither of the above

sets of conditions is satisfied, the condition of I/O (at access time) is indeterminate.

16) These parameters are referenced to the CAS leading edge in early write cycles and to the WE leading edge

in read-write cycles.

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

15

Serial Presence Detects:

A serial presence detect storage device -- EEPROM 24C02 -- is assembled on to the module.

Information about the modul confuguration, speed, etc. is written into the EEPROM device during

module production using a serial presence detect protocol ( I

2

C synchronous 2-wire bus).

Byte#

Description

SPD Entry Value

Hex

HYM

64

V4005

GU-50

64

V4005

GU-60

72

V4005

GU-50

72

V4005

GU-60

0

Number of SPD bytes

128

80

80

80

80

1

Total bytes in Serial PD

256

08

08

08

08

2

Memory Type

EDO

02

02

02

02

3

Number of Row Addresses

11

0B

0B

0B

0B

4

Number of Column Addresses

11

0B

0B

0B

0B

5

Number of DIMM Banks

1

01

01

01

01

6

Module Data Width

x64 / x72

40

40

48

48

7

Module Data Width (cont'd)

0

00

00

00

00

8

Module Interface Levels

LVTTL

01

01

01

01

9

RAS access time

50 / 60 ns

32

3C

32

3C

10

CAS access time

13 / 15 ns

0D

0F

0D

0F

11

Dimm Config (Error Det/Corr.)

none / ECC

00

00

02

02

12

Refresh Rate/Type

normal

15.6

µ

s

00

00

00

00

13

Primary DRAM data width

x4

04

04

04

04

14

Error checking DRAM data width

none / x4

00

00

04

04

15-31

reserved for future offerings

FF

FF

FF

FF

32

Superset Memory Type

NA

FF

FF

FF

FF

33-61

Superset information (may be used in

future)

NA

FF

FF

FF

FF

62

SPD Revision Designator

Rev. 1.0

01

01

01

01

63

Checksum for bytes 0-62

XX

03

05

11

64-127 Manufacturer Information (optional)

FF

FF

FF

FF

128-

255

Unused Storage Locations

FF

FF

FF

FF

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

16

Serial Presence Detects (cont'd):

Byte#

Description

SPD Entry Value

Hex

HYM

64

V4045

GU-50

64

V4045

GU-60

72

V4045

GU-50

72

V4045

GU-60

0

Number of SPD bytes

128

80

80

80

80

1

Total bytes in Serial PD

256

08

08

08

08

2

Memory Type

EDO

02

02

02

02

3

Number of Row Addresses

12

0C

0C

0C

0C

4

Number of Column Addresses

10

0A

0A

0A

0A

5

Number of DIMM Banks

1

01

01

01

01

6

Module Data Width

x64 / x72

40

40

48

48

7

Module Data Width (cont'd)

0

00

00

00

00

8

Module Interface Levels

LVTTL

01

01

01

01

9

RAS access time

50 / 60 0 ns

32

3C

32

3C

10

CAS access time

13 / 150 ns

0D

0F

0D

0F

11

Dimm Config (Error Det/Corr.)

none / ECC

00

00

02

02

12

Refresh Rate/Type

normal

15.6

µ

s

00

00

00

00

13

Primary DRAM Organisation

x4

04

04

04

04

14

Secondary DRAMOrgansation

undefined

00

00

00

00

15-31

reserved for future offerings

FF

FF

FF

FF

32

Superset Memory Type

NA

FF

FF

FF

FF

33-61

Superset information (may be used in

future)

NA

FF

FF

FF

FF

62

SPD Revision Designator

Rev. 1.0

01

01

01

01

63

Checksum for bytes 0-62

XX

03

XX

0D

64-127 Manufacturer Information (optional)

FF

FF

FF

FF

128-

255

Unused Storage Locations

FF

FF

FF

FF

HYM64(72)V4005/45GU-50/-60

4M x 64/72 DRAM Module

Semiconductor Group

17

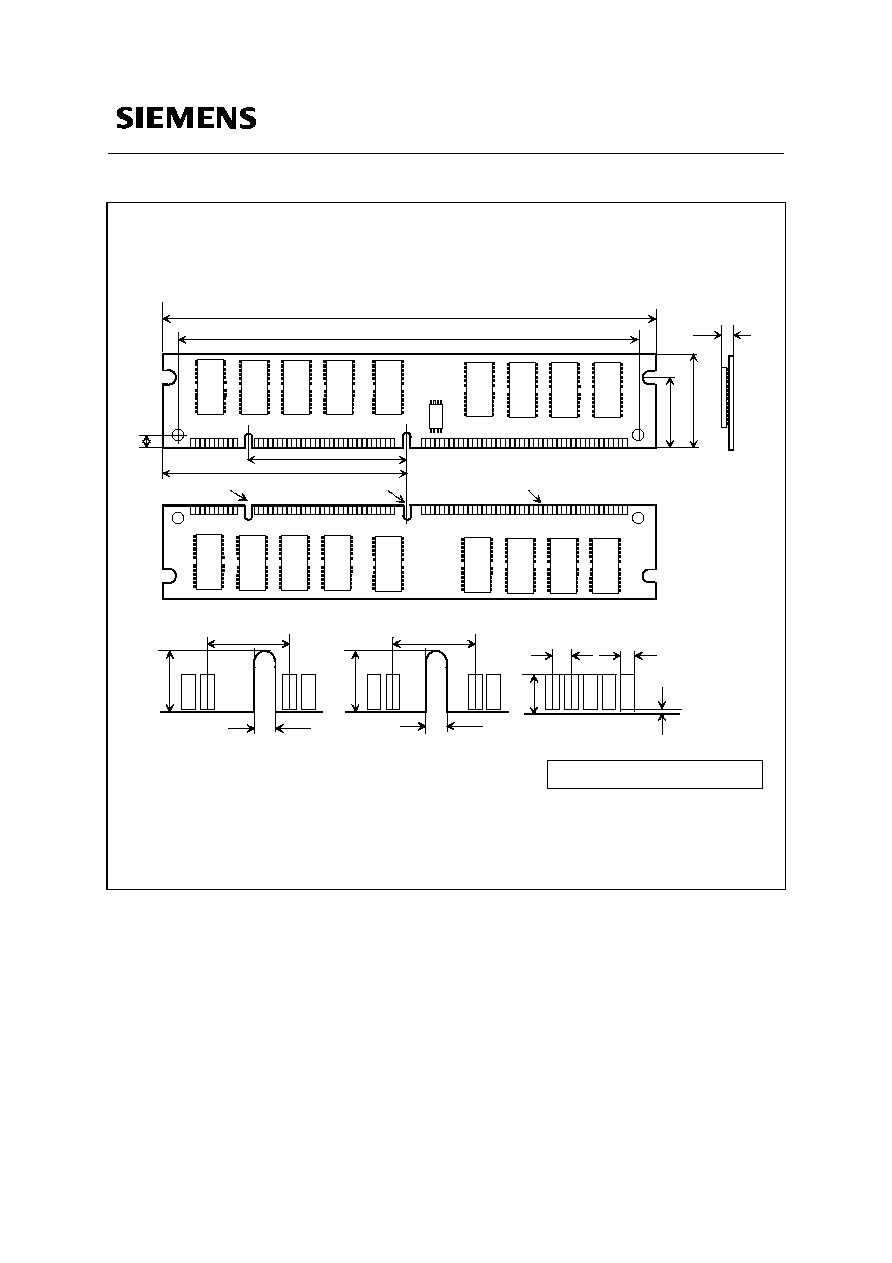

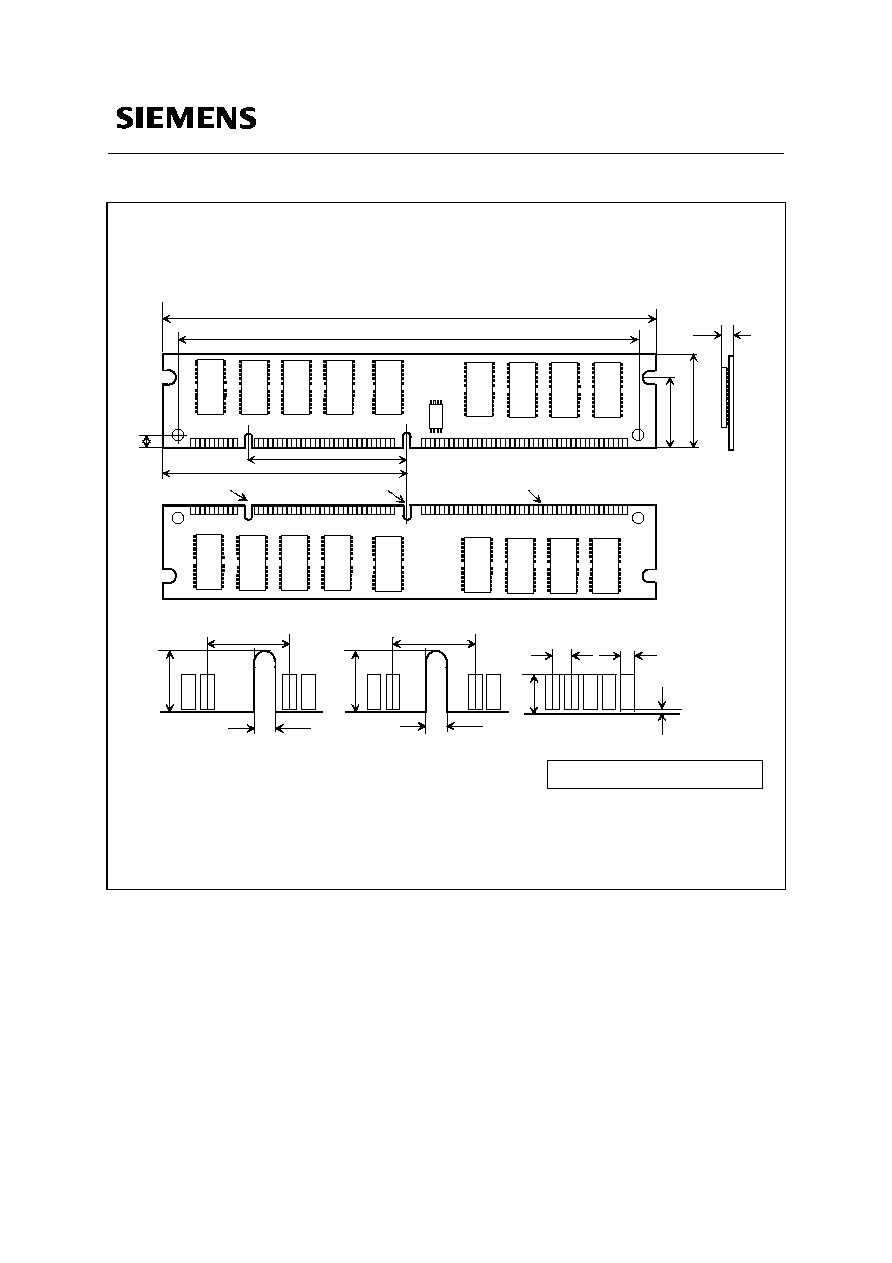

L-DIM-168-12

Module package

(168 pin, dual read-out, single in-line memory module)

133,35

1

84

17,78

25,40

10 11

40

41

85

preliminary drawing

3,0

127,35

168

124

125

66,68

42,18

* On x72 only (CB0-CB7)

5,3

*

*

DM168-12.WMF

6,35

2,0

3,125

Detail B

6,35

2,0

3,125

Detail A

Detail C

2,54 min.

1,27

1,0 + 0.5

-

A

B

C

+

-

0,2 0,15

94

95