September 2003

1

Document Control # ML0016 rev 0.1

STK15C88

32K x 8 AutoStoreTM nvSRAM

QuantumTrapTM CMOS

Nonvolatile Static RAM

FEATURES

∑ Nonvolatile Storage without Battery Problems

∑ Directly Replaces 32K x 8 Static RAM, Battery-

Backed RAM or EEPROM

∑ 25ns, 35ns and 45ns Access Times

∑ STORE to nonvolatile elements Initiated by

Software or AutoStoreTM

∑ RECALL to SRAM Initiated by Software or

Power Restore

∑ 10mA Typical I

CC

at 200ns Cycle Time

∑ Unlimited READ, WRITE and RECALL Cycles

∑ 1,000,000 STORE Cycles to nonvolatile ele-

ments

∑ 100-Year Data Retention in nonvolatile ele-

ments (Commercial/Industrial)

∑ Single 5V + 10% Operation

∑ Commercial and Industrial Temperatures

∑ 28-Pin PDIP and SOIC Packages

DESCRIPTION

The STK15C88 is a fast

SRAM

with a nonvolatile

element incorporated in each static memory cell.

The

SRAM

can be read and written an unlimited

number of times, while independent nonvolatile data

resides in nonvolatile elements. Data transfers from

the

SRAM

to the nonvolatile elements (the

STORE

operation) can take place automatically on power

down using charge stored in system capacitance.

Transfers from the nonvolatile elements to the

SRAM

(the

RECALL

operation) take place automatically on

restoration of power. Initiation of

STORE

and

RECALL

cycles can also be controlled by entering specific

read sequences. The STK15C88 is pin-compatible

with 32k x 8

SRAM

s and battery-backed

SRAM

s,

allowing direct substitution while enhancing perfor-

mance. A similar device (STK16C88) with an inter-

nally integrated capacitor is available for

applications with very fast power-down slew rates.

The STK14C88, which uses an external capacitor, is

another alternative for these applications.

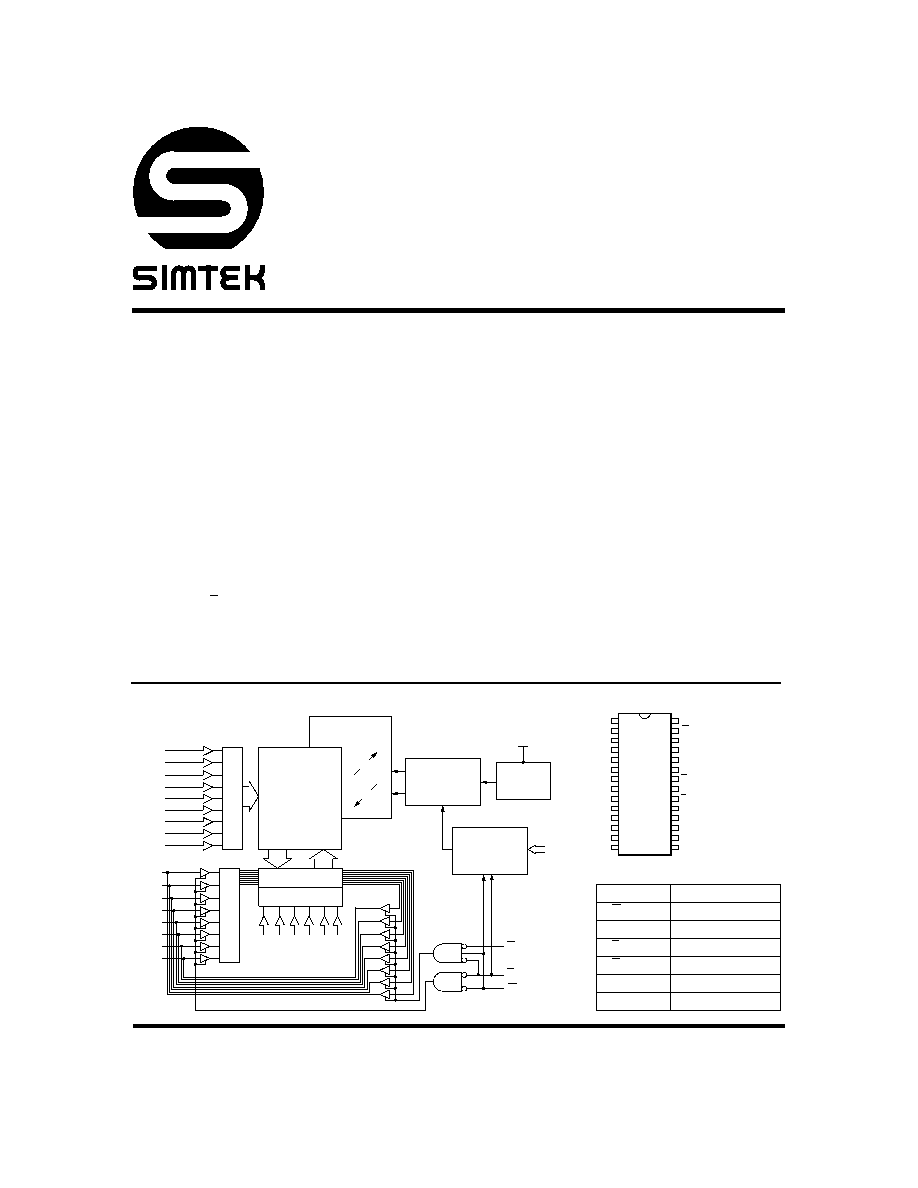

BLOCK DIAGRAM

QUANTUM TRAP

512 x 512

STORE

RECALL

COLUMN I/O

COLUMN DEC

STATIC RAM

ARRAY

512 x 512

ROW DE

CODE

R

INPU

T B

U

FFERS

STORE/

RECALL

CONTROL

POWER

CONTROL

A

6

A

7

A

11

A

12

A

13

A

14

DQ

0

DQ

1

DQ

2

DQ

3

DQ

4

DQ

5

DQ

6

DQ

7

SOFTWARE

DETECT

V

CC

A

0

-

A

13

G

E

W

A

9

A

8

A

10

A

3

A

2

A

0

A

1

A

4

A

5

PIN CONFIGURATIONS

A

14

A

12

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

DQ

0

DQ

1

DQ

2

V

SS

V

CC

A

13

A

8

A

9

A

11

G

W

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

A

10

E

DQ

7

DQ

6

DQ

5

DQ

4

DQ

3

28 - 300 PDIP

28 - 600 PDIP

28 - 300 SOIC

28 - 350 SOIC

PIN NAMES

A

0

- A

14

Address Inputs

W

Write Enable

DQ

0

- DQ

7

Data In/Out

E

Chip Enable

G

Output Enable

V

CC

Power (+ 5V)

V

SS

Ground

STK15C88

September 2003

2

Document Control # ML0016 rev 0.1

ABSOLUTE MAXIMUM RATINGS

a

Voltage on Input Relative to Ground . . . . . . . . . . . . . .≠0.5V to 7.0V

Voltage on Input Relative to V

SS

. . . . . . . . . . ≠0.6V to (V

CC

+ 0.5V)

Voltage on DQ

0-7

. . . . . . . . . . . . . . . . . . . . . . ≠0.5V to (V

CC

+ 0.5V)

Temperature under Bias . . . . . . . . . . . . . . . . . . . . . ≠55

∞

C to 125

∞

C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . ≠65

∞

C to 150

∞

C

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1W

DC Output Current (1 output at a time, 1s duration) . . . . . . . . 15mA

Note a: Stresses greater than those listed under "Absolute Maximum Rat-

ings" may cause permanent damage to the device. This is a stress

rating only, and functional operation of the device at conditions

above those indicated in the operational sections of this specifica-

tion is not implied. Exposure to absolute maximum rating condi-

tions for extended periods may affect reliability.

DC CHARACTERISTICS

(V

CC

= 5.0V

±

10%)

Note b: I

CC1

and I

CC3

are dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded.

Note c: I

CC2

and I

CC4

are the average currents required for the duration of the respective

STORE

cycles (t

STORE

) .

Note d: E

V

IH

will not produce standby current levels until any nonvolatile cycle in progress has timed out.

AC TEST CONDITIONS

CAPACITANCE

e

(T

A

= 25

∞

C, f = 1.0MHz)

Note e: These parameters are guaranteed but not tested.

SYMBOL

PARAMETER

COMMERCIAL

INDUSTRIAL

UNITS

NOTES

MIN

MAX

MIN

MAX

I

CC1

b

Average V

CC

Current

97

80

70

100

85

70

mA

mA

mA

t

AVAV

= 25ns

t

AVAV

= 35ns

t

AVAV

= 45ns

I

CC2

c

Average V

CC

Current during STORE

3

3

mA

All Inputs Don't Care, V

CC

= max

I

CC3

b

Average V

CC

Current at t

AVAV

= 200ns

5V, 25∞C, Typical

10

10

mA

W

(V

CC

≠ 0.2V)

All Others Cycling, CMOS Levels

I

CC4

c

Average V

CAP

Current during

AutoStoreTM Cycle

2

2

mA

All Inputs Don't Care

I

SB1

d

Average

V

CC

Current

(Standby, Cycling TTL Input Levels)

30

25

22

31

26

23

mA

mA

mA

t

AVAV

= 25ns, E

V

IH

t

AVAV

= 35ns, E

V

IH

t

AVAV

= 45ns, E

V

IH

I

SB2

d

V

CC

Standby Current

(Standby, Stable CMOS Input Levels)

1.5

1.5

mA

E

(V

CC

≠ 0.2V)

All Others V

IN

0.2V or

(V

CC

≠ 0.2V)

I

ILK

Input Leakage Current

±

1

±

1

µ

A

V

CC

= max

V

IN

= V

SS

to V

CC

I

OLK

Off-State Output Leakage Current

±

5

±

5

µ

A

V

CC

= max

V

IN

= V

SS

to V

CC

, E or G

V

IH

V

IH

Input Logic "1" Voltage

2.2

V

CC

+ .5

2.2

V

CC

+ .5

V

All Inputs

V

IL

Input Logic "0" Voltage

V

SS

≠ .5

0.8

V

SS

≠ .5

0.8

V

All Inputs

V

OH

Output Logic "1" Voltage

2.4

2.4

V

I

OUT

= ≠ 4mA

V

OL

Output Logic "0" Voltage

0.4

0.4

V

I

OUT

= 8mA

T

A

Operating Temperature

0

70

≠40

85

∞

C

Input Pulse Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V to 3V

Input Rise and Fall Times

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5ns

Input and Output Timing Reference Levels . . . . . . . . . . . . . . . 1.5V

Output Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Figure 1

SYMBOL

PARAMETER

MAX

UNITS

CONDITIONS

C

IN

Input Capacitance

5

pF

V = 0 to 3V

C

OUT

Output Capacitance

7

pF

V = 0 to 3V

Figure 1: AC Output Loading

480 Ohms

30 pF

255 Ohms

5.0V

INCLUDING

OUTPUT

SCOPE AND

FIXTURE

STK15C88

September 2003

3

Document Control # ML0016 rev 0.1

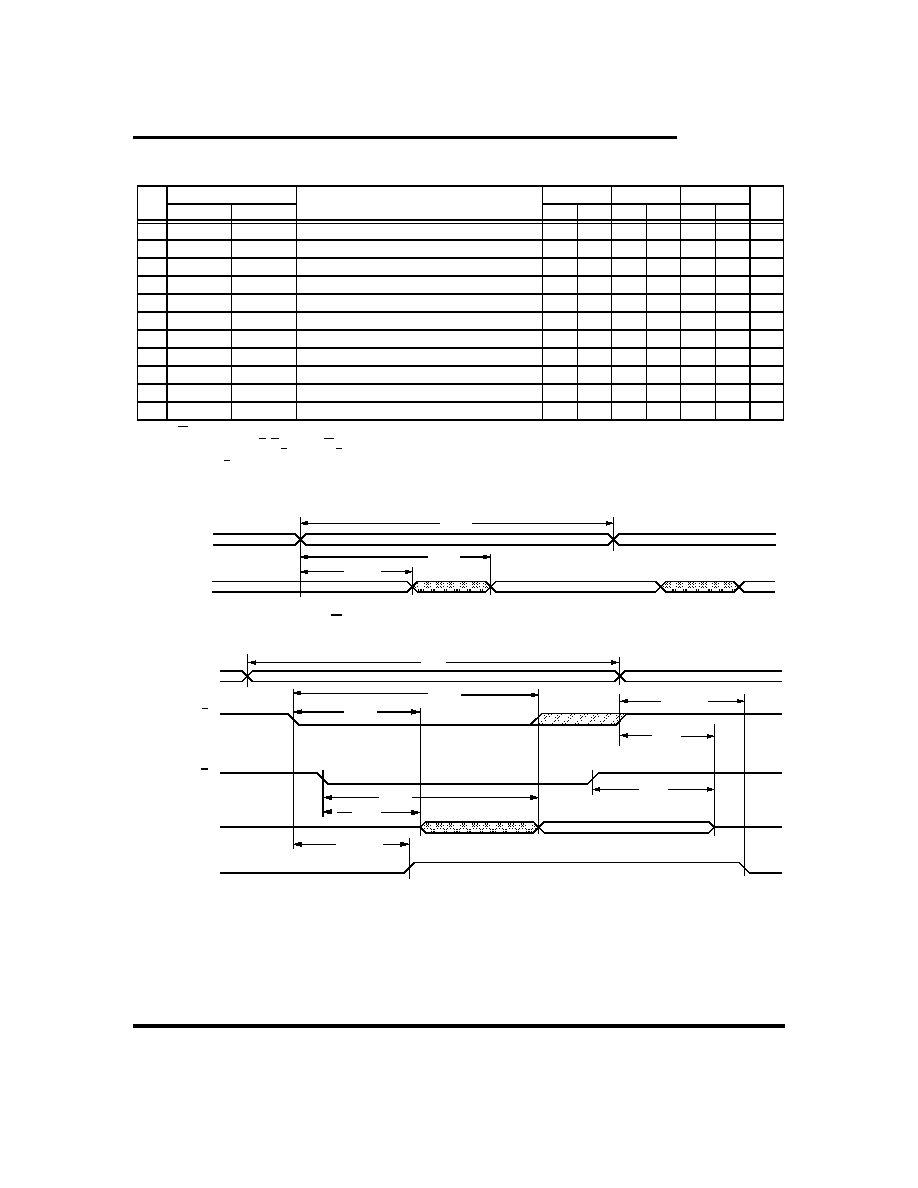

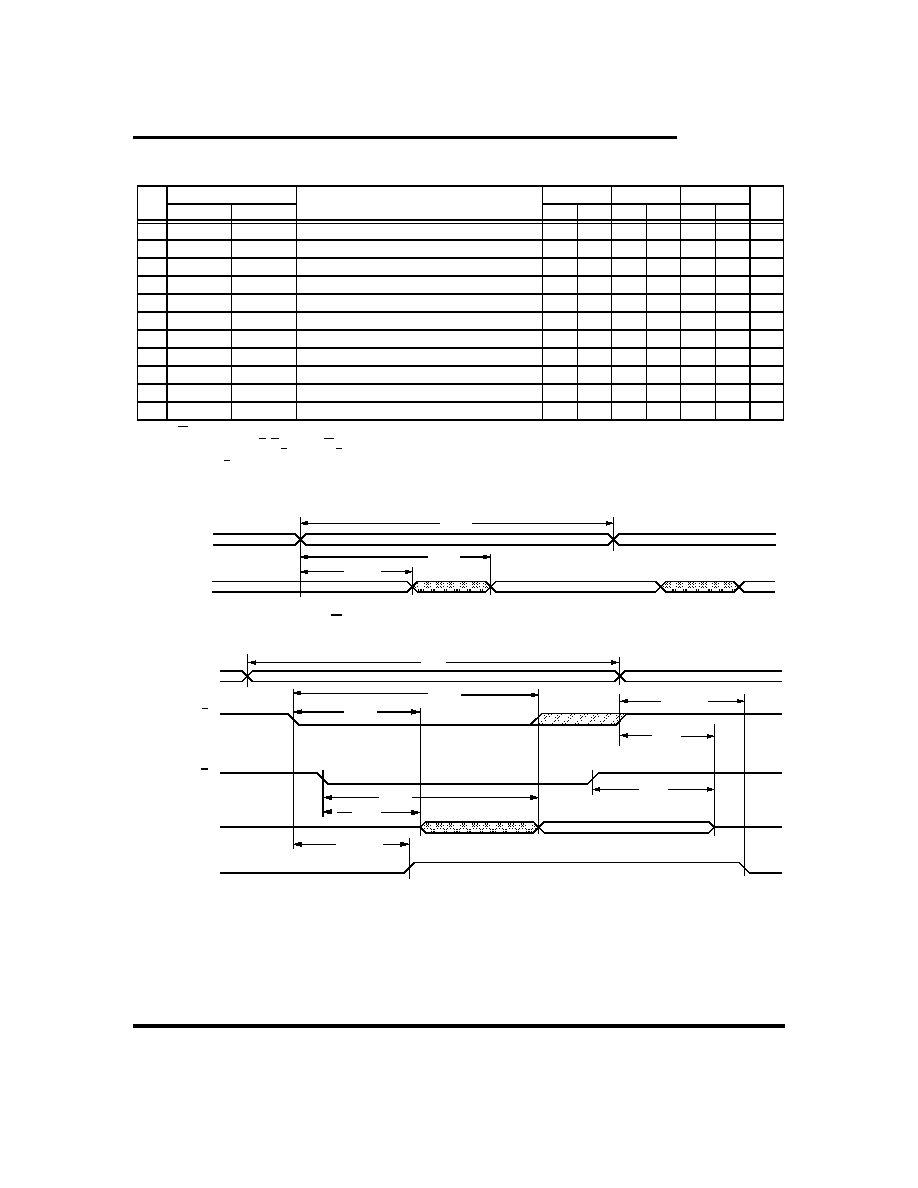

SRAM READ CYCLES #1 & #2

(V

CC

= 5.0V

±

10%)

Note f:

W must be high during SRAM READ cycles and low during SRAM WRITE cycles.

Note g: I/O state assumes E, G < V

IL

and W > V

IH

; device is continuously selected.

Note h: Measured + 200mV from steady state output voltage.

SRAM READ CYCLE #1: Address Controlled

f, g

SRAM READ CYCLE #2: E Controlled

f

NO.

SYMBOLS

PARAMETER

STK15C88-25

STK15C88-35

STK15C88-45

UNITS

#1, #2

Alt.

MIN

MAX

MIN

MAX

MIN

MAX

1

t

ELQV

t

ACS

Chip Enable Access Time

25

35

45

ns

2

t

AVAV

f

t

RC

Read Cycle Time

25

35

45

ns

3

t

AVQV

g

t

AA

Address Access Time

25

35

45

ns

4

t

GLQV

t

OE

Output Enable to Data Valid

10

15

20

ns

5

t

AXQX

g

t

OH

Output Hold after Address Change

5

5

5

ns

6

t

ELQX

t

LZ

Chip Enable to Output Active

5

5

5

ns

7

t

EHQZ

h

t

HZ

Chip Disable to Output Inactive

10

13

15

ns

8

t

GLQX

t

OLZ

Output Enable to Output Active

0

0

0

ns

9

t

GHQZ

h

t

OHZ

Output Disable to Output Inactive

10

13

15

ns

10

t

ELICCH

e

t

PA

Chip Enable to Power Active

0

0

0

ns

11

t

EHICCL

d, e

t

PS

Chip Disable to Power Standby

25

35

45

ns

DATA VALID

5

t

AXQX

3

t

AVQV

DQ (DATA OUT)

ADDRESS

2

t

AVAV

STANDBY

DATA VALID

DQ (DATA OUT)

E

ADDRESS

2

t

AVAV

G

I

CC

ACTIVE

1

t

ELQV

11

t

EHICCL

7

t

EHQZ

9

t

GHQZ

6

t

ELQX

8

t

GLQX

4

t

GLQV

10

t

ELICCH

STK15C88

September 2003

4

Document Control # ML0016 rev 0.1

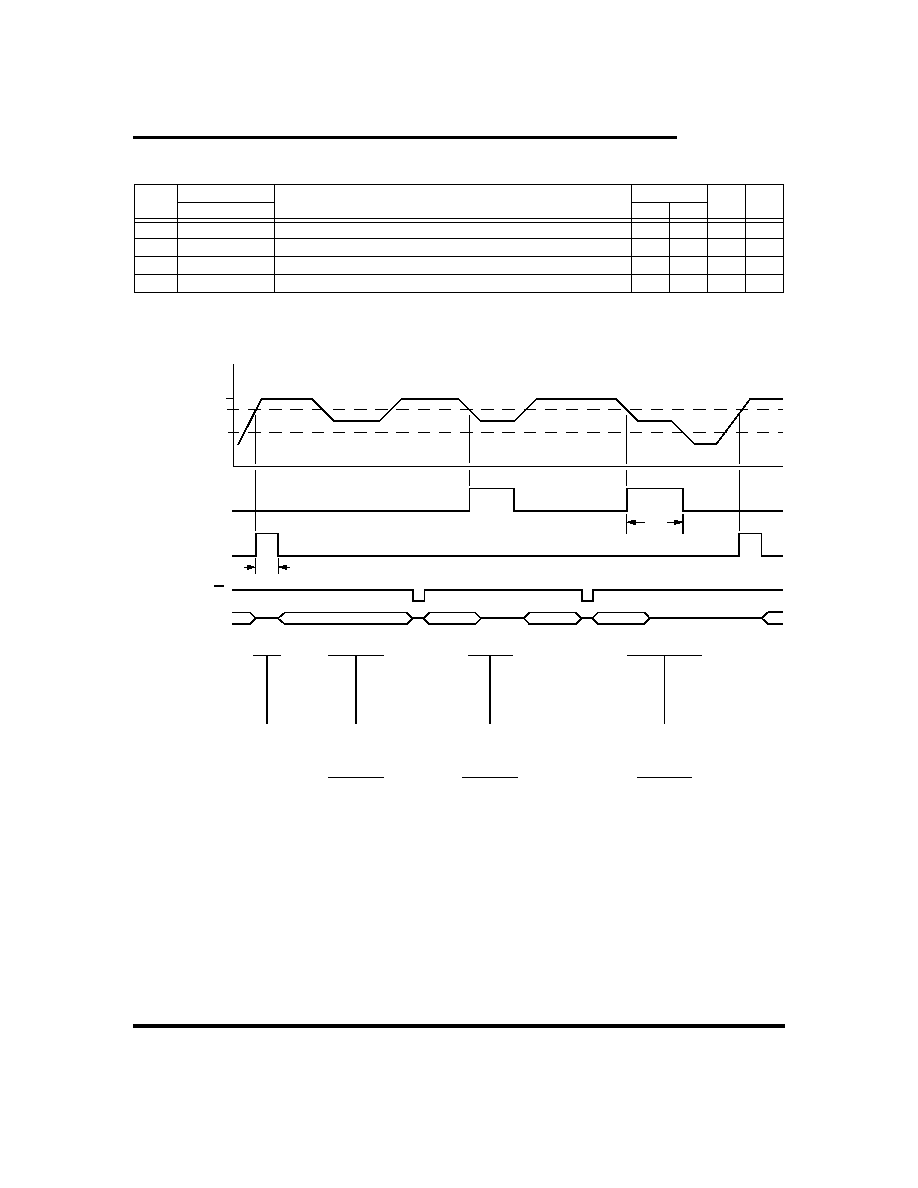

SRAM WRITE CYCLES #1 & #2

(V

CC

= 5.0V

±

10%)

Note i:

If W is low when E goes low, the outputs remain in the high-impedance state.

Note j:

E or W must be

V

IH

during address transitions.

SRAM WRITE CYCLE #1: W Controlled

j

SRAM WRITE CYCLE #2: E Controlled

j

NO.

SYMBOLS

PARAMETER

STK15C88-25

STK15C88-35

STK15C88-45

UNITS

#1

#2

Alt.

MIN

MAX

MIN

MAX

MIN

MAX

12

t

AVAV

t

AVAV

t

WC

Write Cycle Time

25

35

45

ns

13

t

WLWH

t

WLEH

t

WP

Write Pulse Width

20

25

30

ns

14

t

ELWH

t

ELEH

t

CW

Chip Enable to End of Write

20

25

30

ns

15

t

DVWH

t

DVEH

t

DW

Data Set-up to End of Write

10

12

15

ns

16

t

WHDX

t

EHDX

t

DH

Data Hold after End of Write

0

0

0

ns

17

t

AVWH

t

AVEH

t

AW

Address Set-up to End of Write

20

25

30

ns

18

t

AVWL

t

AVEL

t

AS

Address Set-up to Start of Write

0

0

0

ns

19

t

WHAX

t

EHAX

t

WR

Address Hold after End of Write

0

0

0

ns

20

t

WLQZ

h, i

t

WZ

Write Enable to Output Disable

10

13

15

ns

21

t

WHQX

t

OW

Output Active after End of Write

5

5

5

ns

PREVIOUS DATA

DATA OUT

E

ADDRESS

12

t

AVAV

W

16

t

WHDX

DATA IN

19

t

WHAX

13

t

WLWH

18

t

AVWL

17

t

AVWH

DATA VALID

20

t

WLQZ

15

t

DVWH

HIGH IMPEDANCE

21

t

WHQX

14

t

ELWH

DATA OUT

E

ADDRESS

12

t

AVAV

W

DATA IN

13

t

WLEH

DATA VALID

HIGH IMPEDANCE

14

t

ELEH

18

t

AVEL

17

t

AVEH

15

t

DVEH

19

t

EHAX

16

t

EHDX

STK15C88

September 2003

5

Document Control # ML0016 rev 0.1

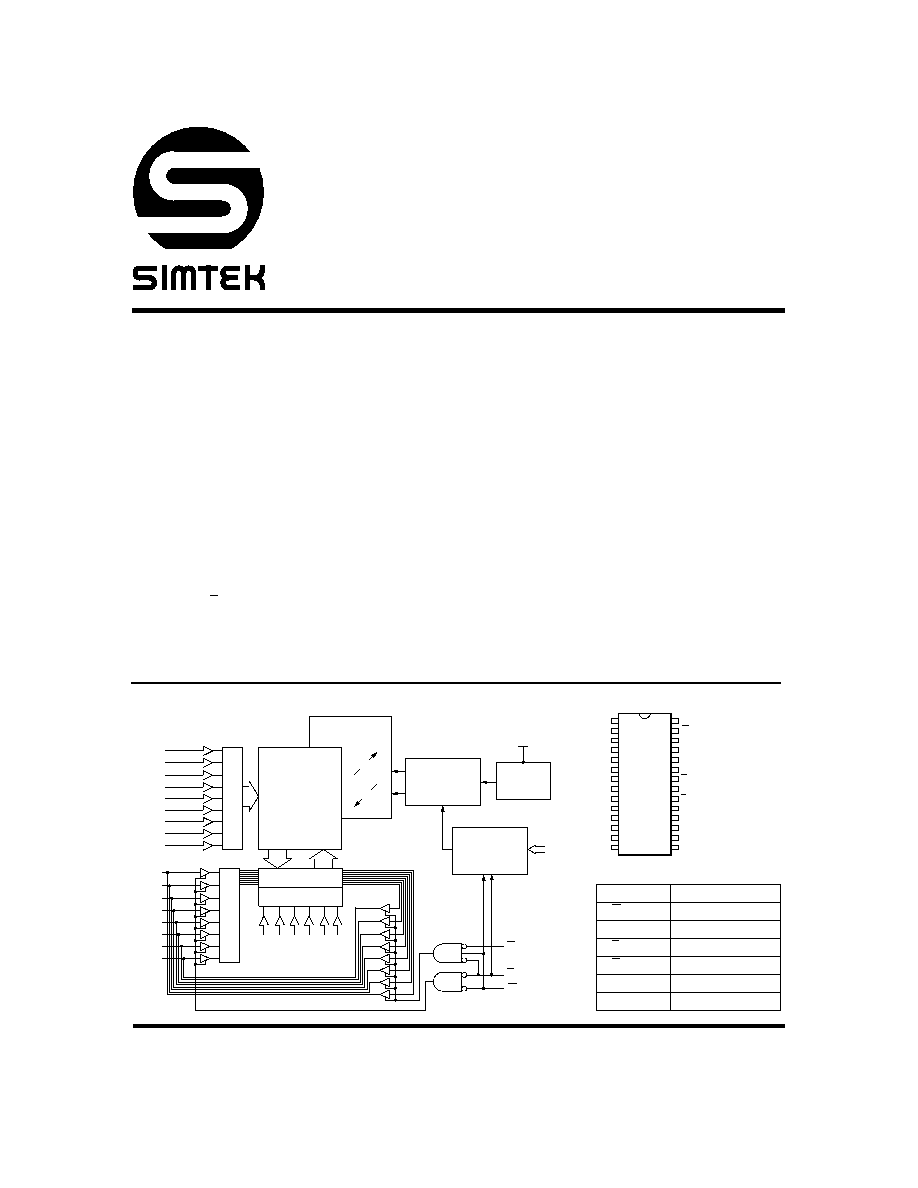

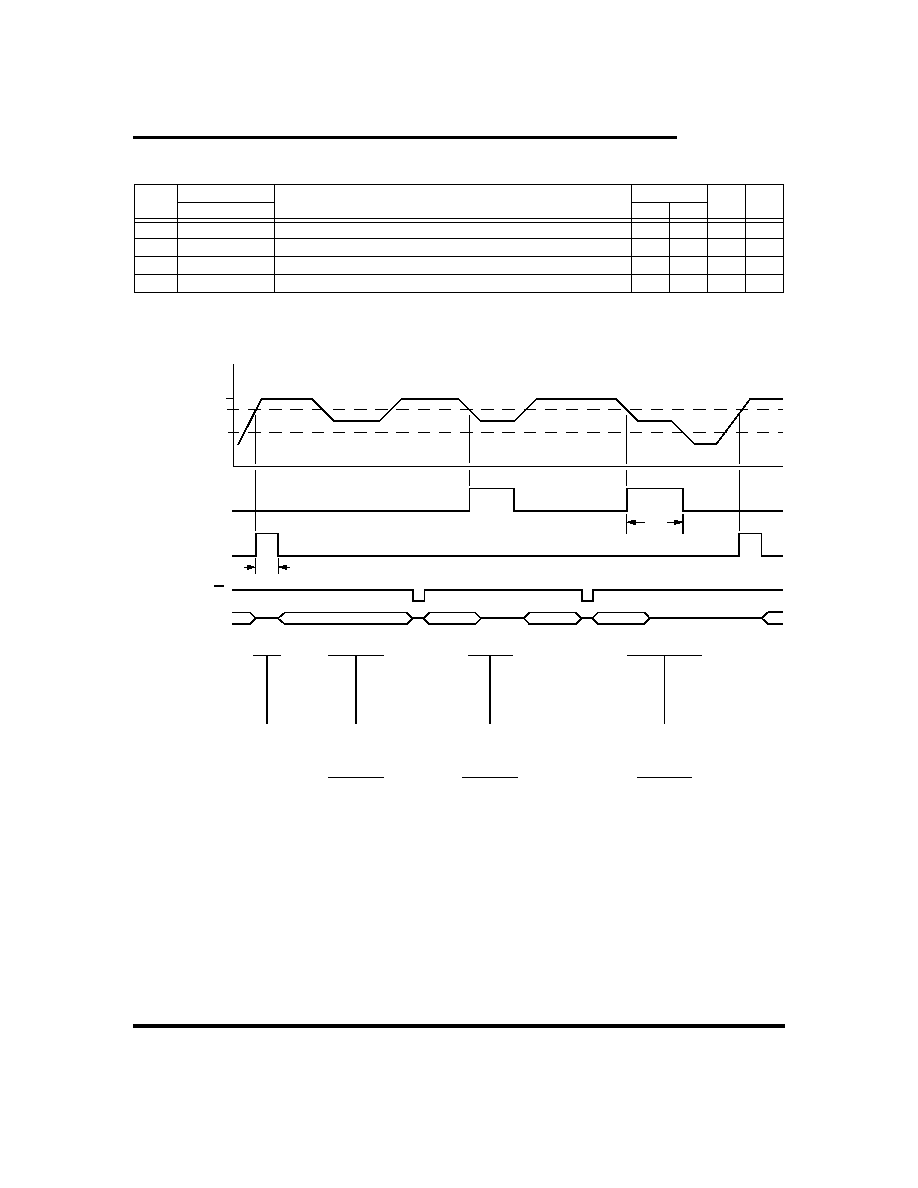

AutoStoreTM/POWER-UP RECALL

(V

CC

= 5.0V

±

10%)

Note k: t

RESTORE

starts from the time V

CC

rises above V

SWITCH

.

AutoStoreTM/POWER-UP RECALL

NO.

SYMBOLS

PARAMETER

STK15C88

UNITS NOTES

Standard

MIN

MAX

22

t

RESTORE

Power-up RECALL Duration

550

µ

s

k

23

t

STORE

STORE Cycle Duration

10

ms

g

24

V

SWITCH

Low Voltage Trigger Level

4.0

4.5

V

25

V

RESET

Low Voltage Reset Level

3.6

V

V

CC

V

SWITCH

V

RESET

POWER-UP RECALL

W

DQ (DATA OUT)

AutoStoreTM

5V

22

t

RESTORE

23

t

STORE

24

25

POWER-UP

RECALL

BROWN OUT

AutoStoreTM

NO RECALL

(V

CC

DID NOT GO

BELOW V

RESET

)

BROWN OUT

AutoStoreTM

RECALL WHEN

V

CC

RETURNS

ABOVE V

SWITCH

BROWN OUT

NO STORE DUE TO

NO SRAM WRITES

NO RECALL

(V

CC

DID NOT GO

BELOW V

RESET

)