| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: SL4066BN | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

SL4066B

System Logic

Semiconductor

SLS

Quad Bilateral Switch

High-Voltage Silicon-Gate CMOS

The SL4066B is a quad bilateral switch intended for the

transmission or multiplexing of analog or digital signals. In addition, the

on-state resistance is relatively constant over the full input-signal

range.

The SL4066B consists of four independent bilateral switches. A

single control signal is required per switch. Both the p and the n device

in a given switch are biased on or off simultaneously by the control

signal.(As show in Fig.1.)The well of the n-channel device on each

switch is either tied to the input when the switch is on or to GND when

the switch is off. This configuration eliminates the variation of the

switch-transistor threshold voltage with input signal, and thus keeps

the on-state resistance low over the full operating-signal range.

The advantages over single-channel switches include peak input-

signal voltage swings equal to the full supply voltage, and more

constant on-state impedance over the input-signal range.

∑

Operating Voltage Range: 3.0 to 18 V

∑

Maximum input current of 1

µ

A at 18 V over full package-

temperature range; 100 nA at 18 V and 25

∞

C

∑

Noise margin (over full package temperature range):

1.0 V min @ 5.0 V supply

2.0 V min @ 10.0 V supply

2.5 V min @ 15.0 V supply

ORDERING INFORMATION

SL4066BN Plastic

SL4066BD SOIC

T

A

= -55

∞

to 125

∞

C for all packages

PIN ASSIGNMENT

FUNCTION TABLE

On/Off Control

Input

State of

Analog Switch

L

Off

H

On

LOGIC DIAGRAM

PIN 14 =V

CC

PIN 7 = GND

SL4066B

System Logic

Semiconductor

SLS

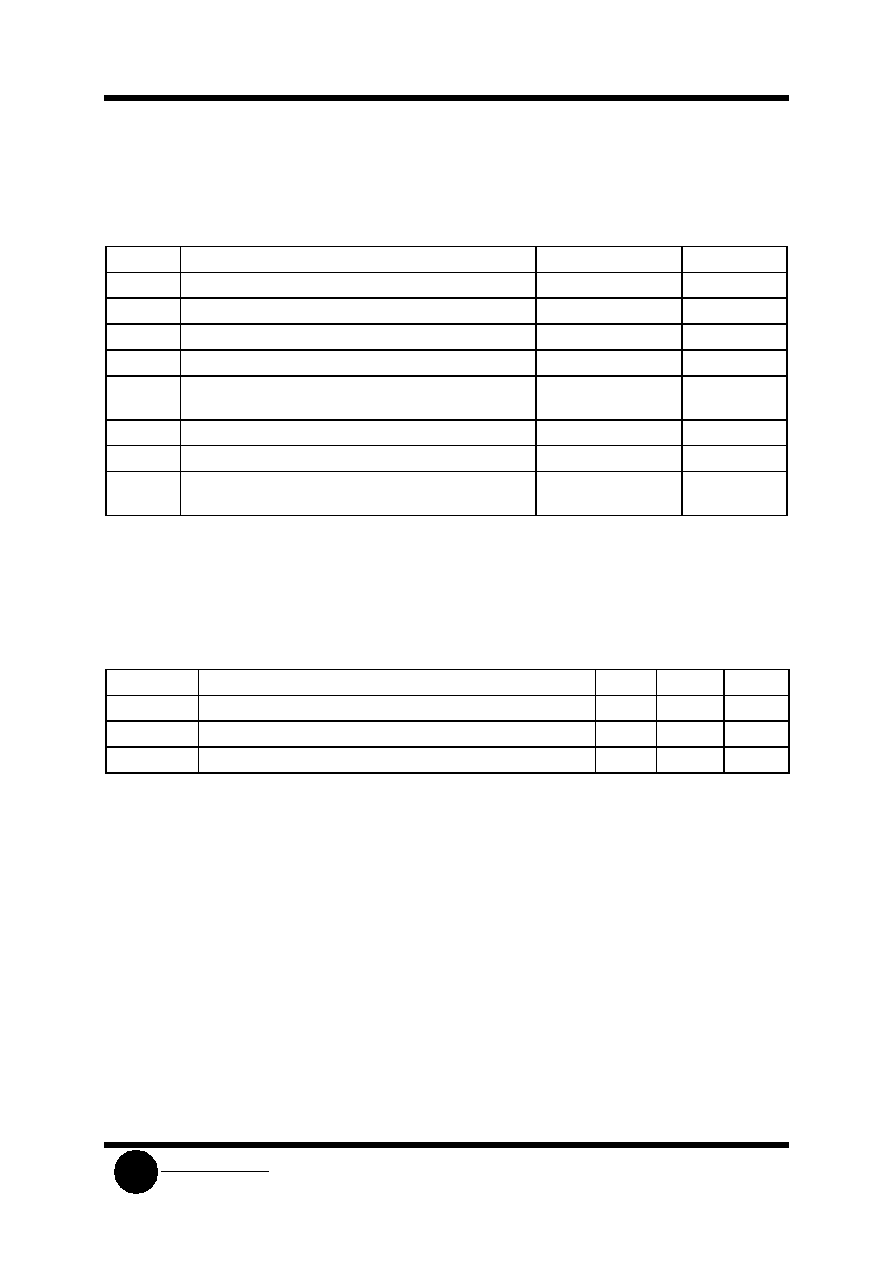

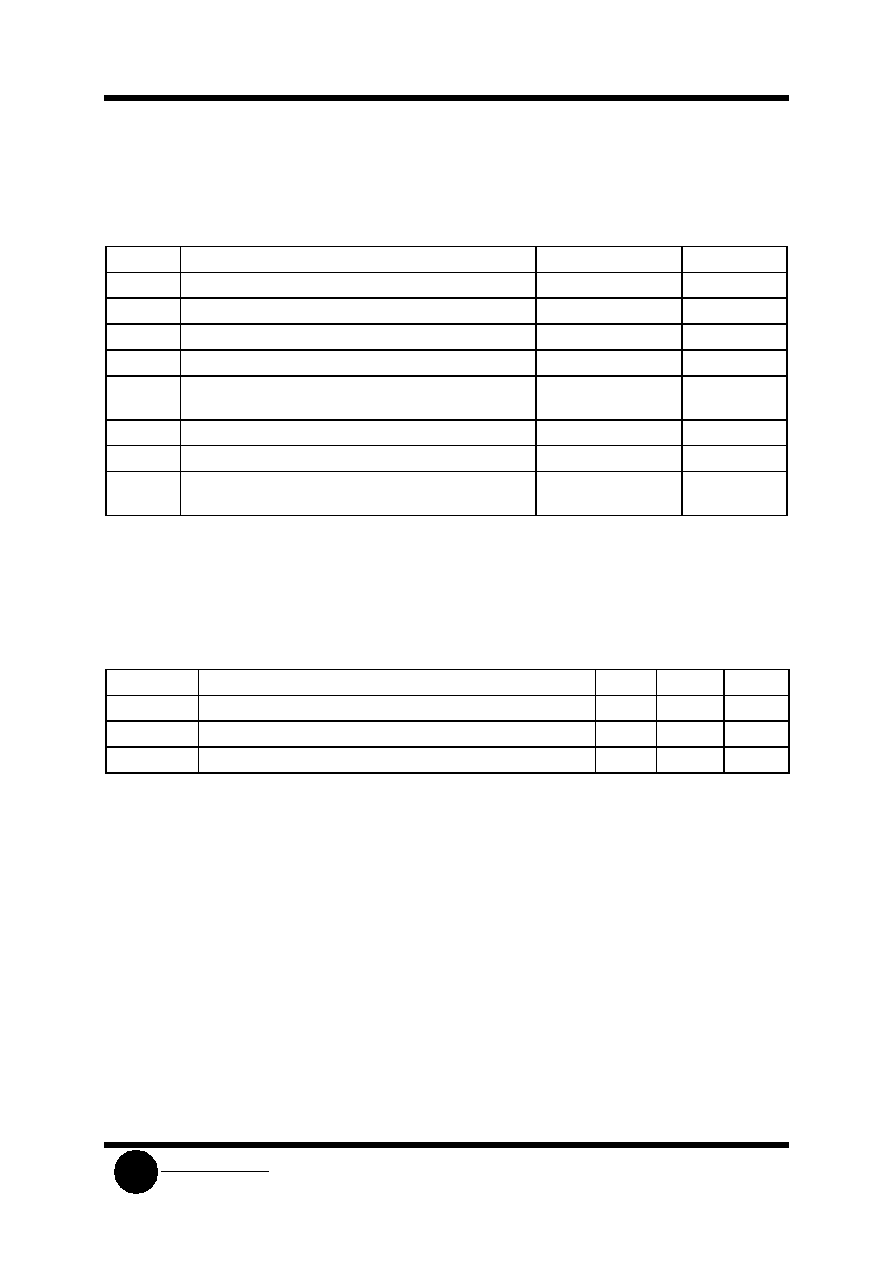

MAXIMUM RATINGS

*

Symbol

Parameter

Value

Unit

V

CC

DC Supply Voltage (Referenced to GND)

-0.5 to +20

V

V

IN

DC Input Voltage (Referenced to GND)

-0.5 to V

CC

+0.5

V

V

OUT

DC Output Voltage (Referenced to GND)

-0.5 to V

CC

+0.5

V

I

IN

DC Input Current, per Pin

±

10

mA

P

D

Power Dissipation in Still Air, Plastic DIP+

SOIC Package+

750

500

mW

P

D

Power Dissipation per Output Transistor

100

mW

Tstg

Storage Temperature

-65 to +150

∞

C

T

L

Lead Temperature, 1 mm from Case for 10 Seconds

(Plastic DIP or SOIC Package)

260

∞

C

*

Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the Recommended Operating Conditions.

+Derating - Plastic DIP: - 10 mW/

∞

C from 65

∞

to 125

∞

C

SOIC Package: : - 7 mW/

∞

C from 65

∞

to 125

∞

C

RECOMMENDED OPERATING CONDITIONS

Symbol

Parameter

Min

Max

Unit

V

CC

DC Supply Voltage (Referenced to GND)

3.0

18

V

V

IN

, V

OUT

DC Input Voltage, Output Voltage (Referenced to GND)

0

V

CC

V

T

A

Operating Temperature, All Package Types

-55

+125

∞

C

This device contains protection circuitry to guard against damage due to high static voltages or electric

fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated

voltages to this high-impedance circuit. For proper operation, V

IN

and V

OUT

should be constrained to the range

GND

(V

IN

or V

OUT

)

V

CC

.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V

CC

).

Unused outputs must be left open.

SL4066B

System Logic

Semiconductor

SLS

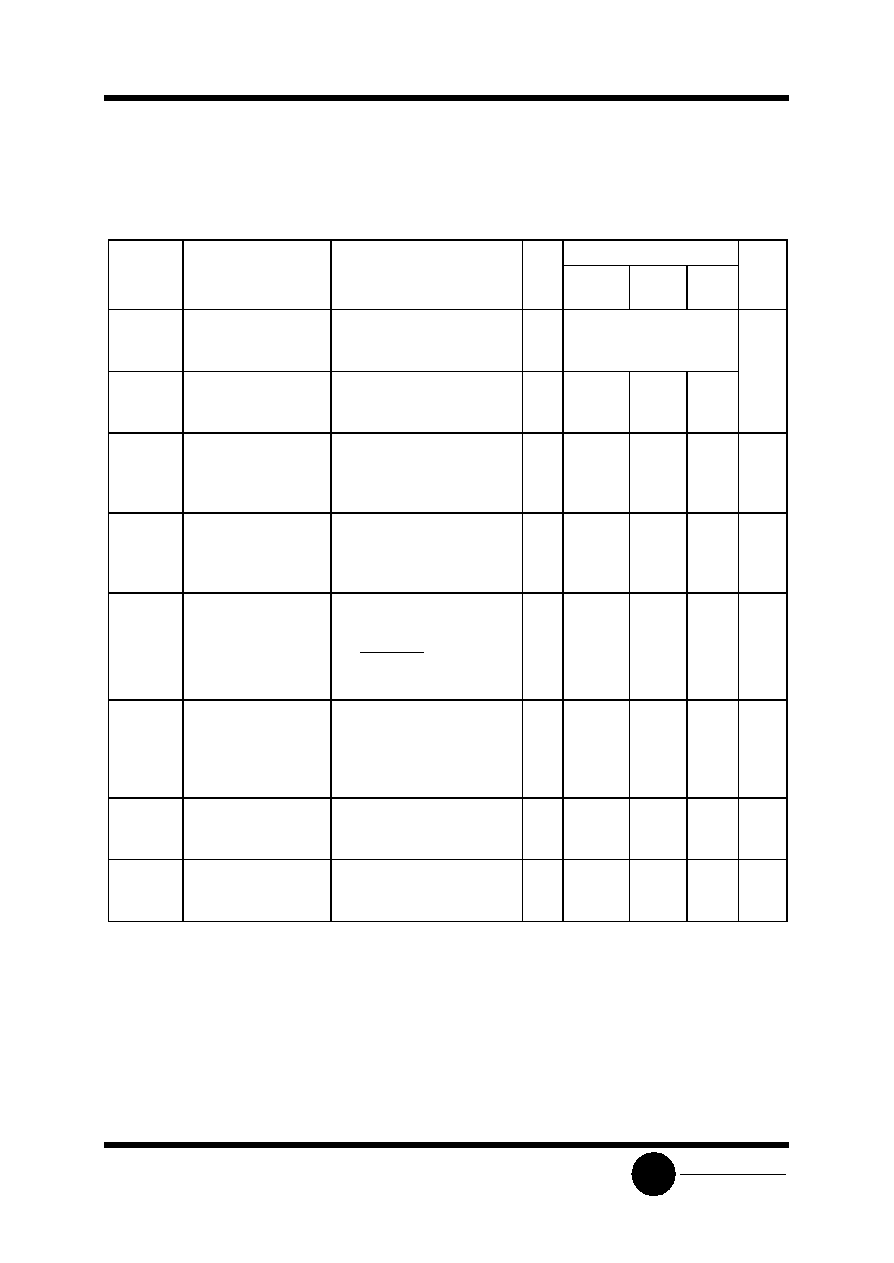

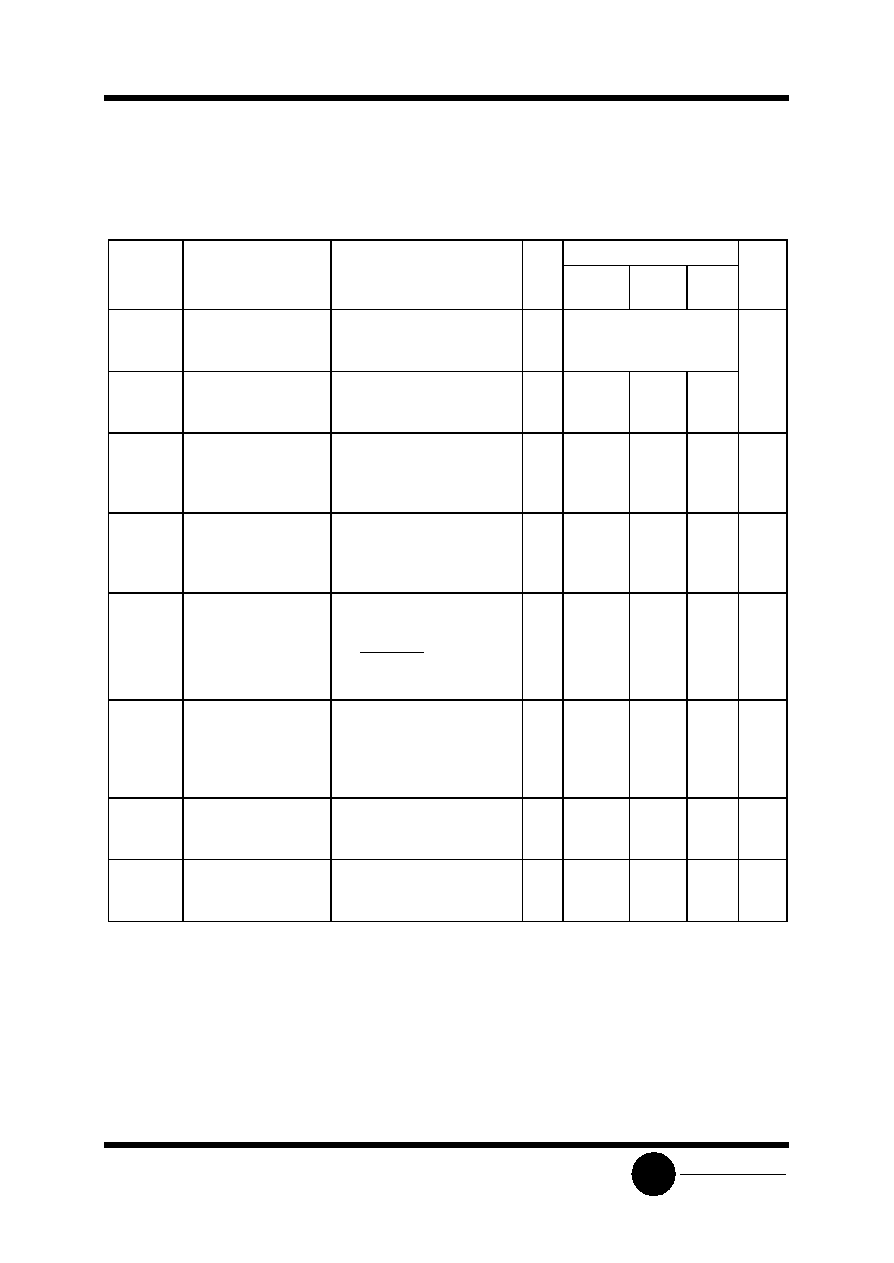

DC ELECTRICAL CHARACTERISTICS

(Voltages Referenced to GND)

V

CC

Guaranteed Limit

Symbol

Parameter

Test Conditions

V

-55

∞

C

25

∞

C

125

∞

C

Unit

V

IH

Minimum High-Level

Voltage ON/Off

Control Inputs

R

ON

= Per Spec

5.0

10

15

3.5(Min)

7(Min)

11(Min)

V

V

IL

Minimum Low-Level

Voltage ON/Off

Control Inputs

R

ON

= Per Spec

5.0

10

15

1

2

2

1

2

2

1

2

2

V

I

IN

Maximum Input

Leakage Current,

ON/OFF Control

Inputs

V

IN

= V

CC

or GND

18

±

0.1

±

0.1

±

1.0

µ

A

I

CC

Maximum Quiescent

Supply Current

(per Package)

V

IN

= V

CC

or GND

5.0

10

15

20

0.25

0.5

1

5

0.25

0.5

1

5

7.5

15

30

150

µ

A

R

ON

Maximum "ON"

Resistance

V

C

= V

CC

R

L

=10 k

returned

to

V

CC

- GND

2

V

IS

= GND to V

CC

5.0

10

15

800

310

200

1050

400

240

1300

550

320

R

ON

Maximum Difference

in "ON" Resistance

Between Any Two

Channels in the Same

Package

V

C

= V

CC

R

L

=10 k

5.0

10

15

-

-

-

15

10

5

-

-

-

I

OFF

Maximum Off-Channel

Leakage Current, Any

One Channel

V

C

= 0 V

V

IS

=18 V; V

OS

= 0 V

V

IS

=0 V; V

OS

= 18V

18

±

0.1

±

0.1

±

1.0

µ

A

I

ON

Maximum On-Channel

Leakage Current, Any

One Channel

V

C

= 0 V

V

IS

=18 V; V

OS

= 0 V

V

IS

=0 V; V

OS

= 18V

18

±

0.1

±

0.1

±

1.0

µ

A

SL4066B

System Logic

Semiconductor

SLS

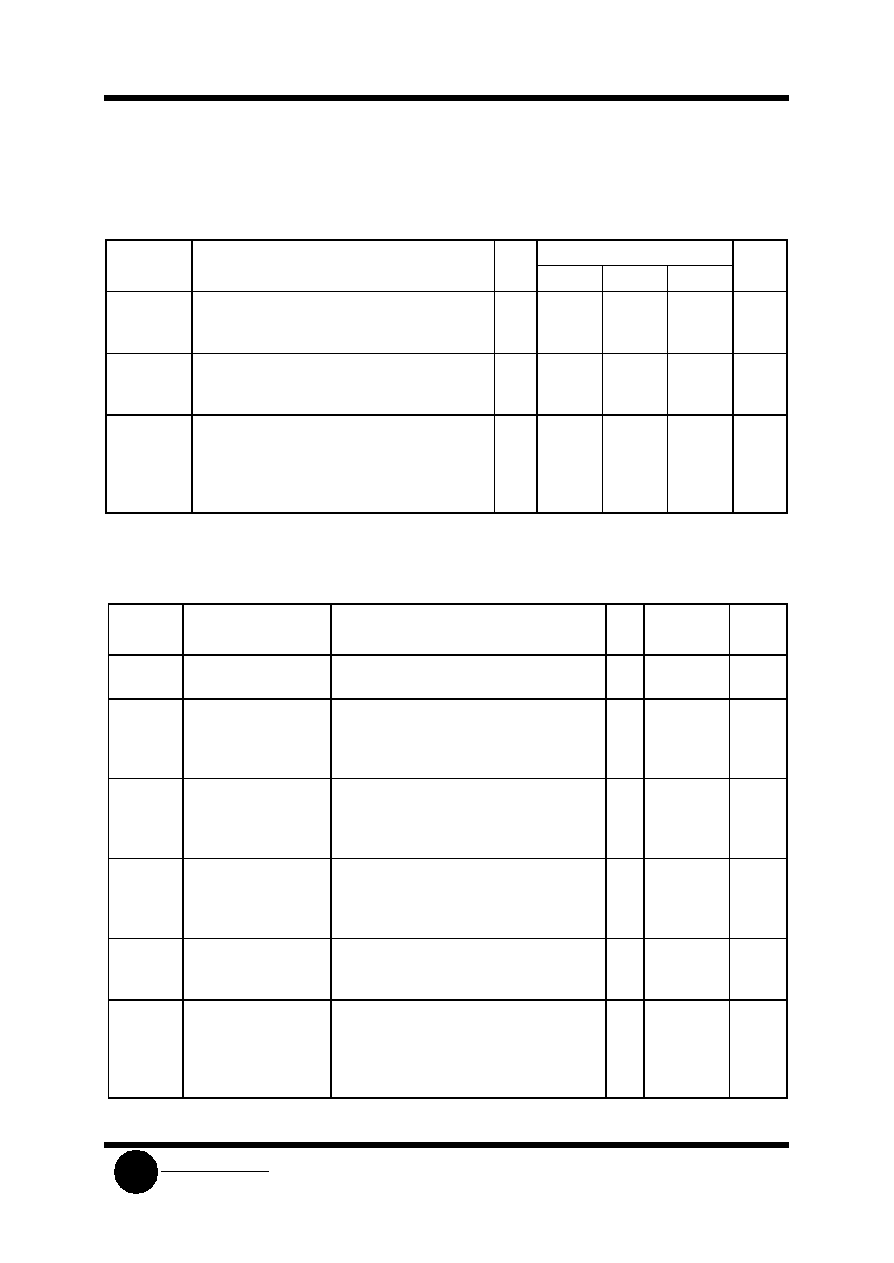

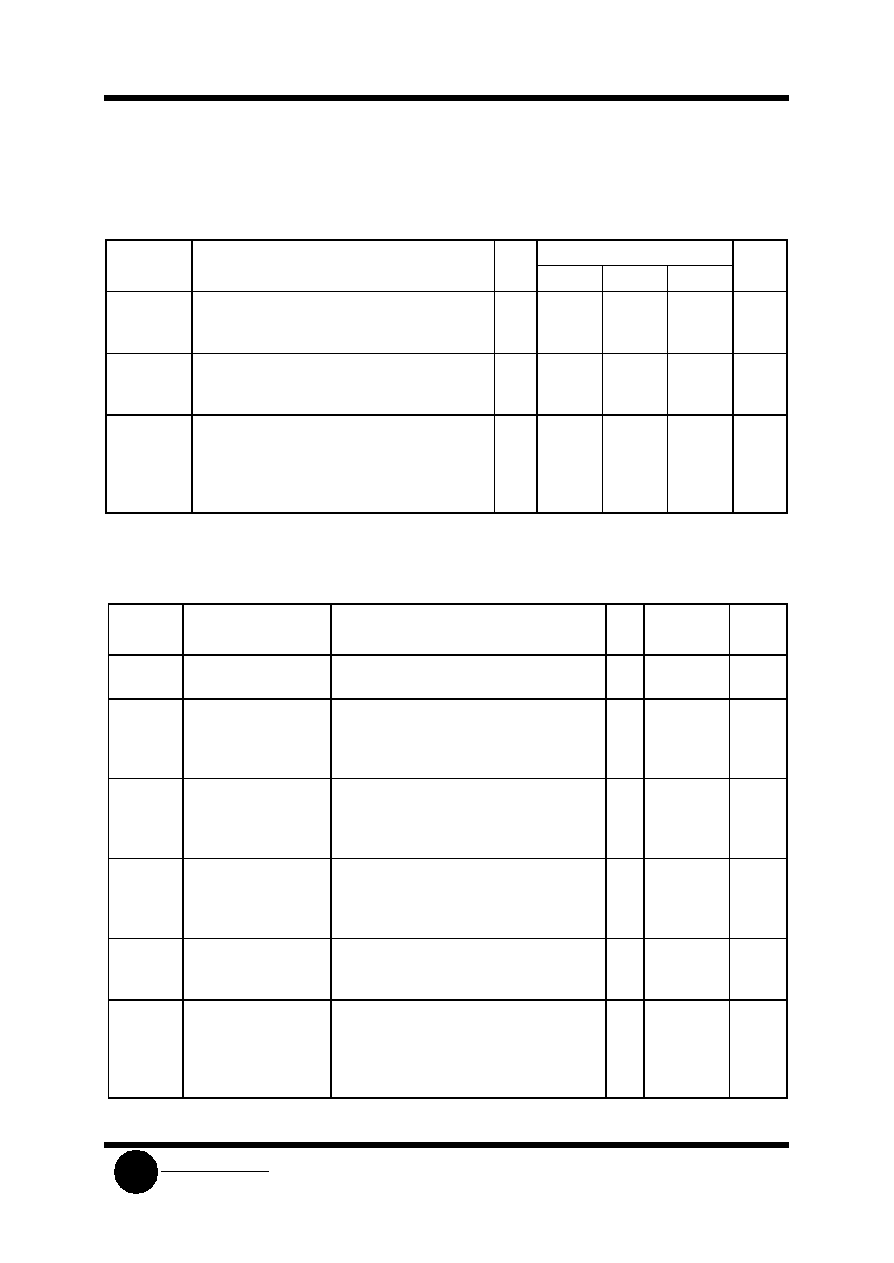

AC ELECTRICAL CHARACTERISTICS

(C

L

=50pF, R

L

=200k

, Input t

r

=t

f

=20 ns)

V

CC

Guaranteed Limit

Symbol

Parameter

V

-55

∞

C

25

∞

C

125

∞

C

Unit

t

PLH

, t

PHL

Maximum Propagation Delay, Analog Input to

Analog Output (Figure 2)

5.0

10

15

40

20

15

40

20

15

80

40

30

ns

t

PLZ

, t

PHZ

,

t

PZL

, t

PZH

Maximum Propagation Delay, ON/OFF Control

to Analog Output (Figure 3)

5.0

10

15

70

40

30

70

40

30

140

80

60

ns

C

Maximum Capacitance

ON/OFF Control Input

Control Input = GND

Analog I/O

Feedthrough

-

15

7.5

0.6

pF

ADDITIONAL APPLICATION CHARACTERISTICS

(Voltages Referenced to GND Unless Noted)

V

CC

Limit

*

Symbol

Parameter

Test Conditions

V

25

∞

C

Unit

THD

Total Harmonic

Distortion

V

C

= V

CC

, GND = -5 V

R

L

= 10 k

, f

IS

=1 kHz sine wave

5

0.4

%

BW

Maximum On-Channel

Bandwidth or

Minimum Frequency

Response

V

C

= V

CC

, GND = -5 V

R

L

= 1 k

5

40

MHz

BW

Maximum On-Channel

Bandwidth or

Minimum Frequency

Response

V

C

= GND , V

IS

= 5 V

R

L

= 1 k

10

1

MHz

BW

Maximum On-Channel

Bandwidth or

Minimum Frequency

Response

V

C

(A)

= V

CC

= 5 V

V

C

(B)

= GND = -5 V

V

IS

(A)

= 5 V

P - P

,50

source

R

L

= 1 k

5

8

MHz

-

Cross talk (Control

Input to Signal

Output)

V

C

= 10 V

t

r

, t

f

= 20 ns

R

L

= 10 k

10

50

mV

-

Maximum Control

Input Repetition Rate

V

IS

= V

CC

, R

L

= 1 k

C

L

= 50 pF

V

C

= 10 V (square wave centered on 5 V)

t

r

, t

f

= 20 ns,

V

OS

= 1/2 V

OS

@1 kHz

5

10

15

6

9

9.5

MHz

*

Guaranteed limits not tested. Determined by design and verified by qualification.

SL4066B

System Logic

Semiconductor

SLS

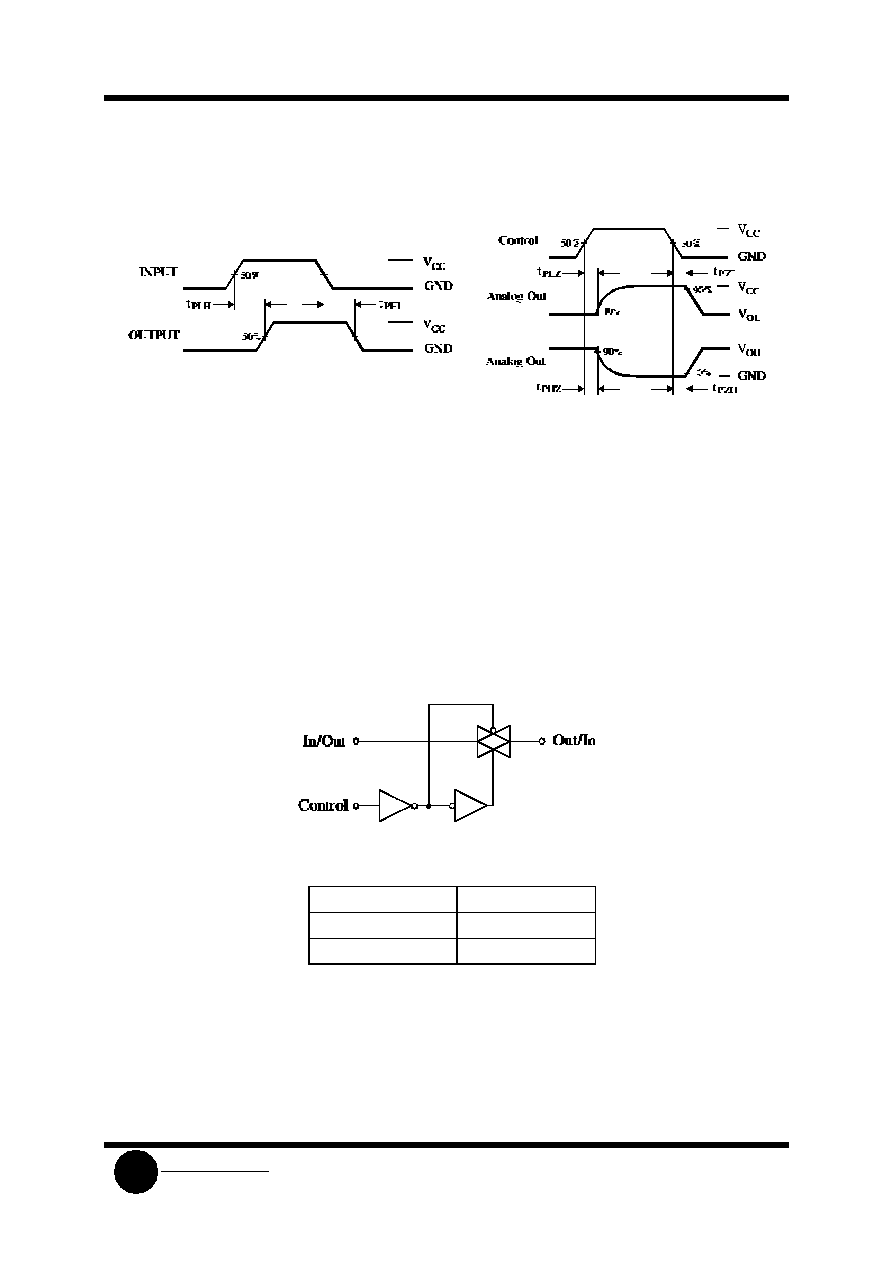

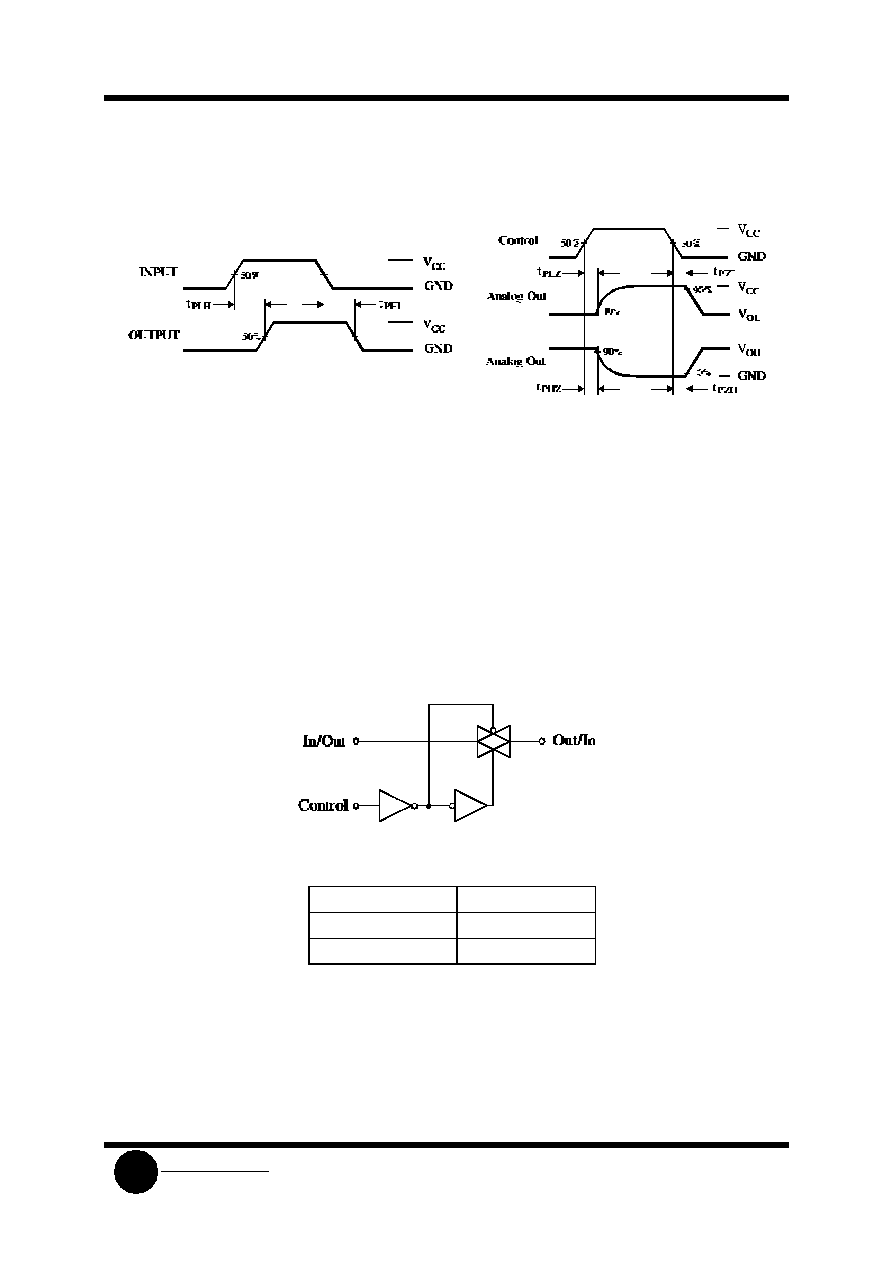

Switch Input

Switch Output,

I

IS

(mA)

V

OS

(V)

V

CC

(V)

V

IS

(V)

-55

∞

C

+25

∞

C

+125

∞

C

Min

Max

5

5

0

5

0.64

-0.64

0.51

-0.51

0.36

-0.36

-

4.6

0.4

-

10

10

0

10

1.6

-1.6

1.3

-1.3

0.9

-0.9

-

9.5

0.5

-

15

15

0

15

4.2

-4.2

3.4

-3.4

2.4

-2.4

-

13.5

1.5

-

Figure 1. Schematic diagram of 1 of 4 identical switches and its associated control circuitry.

GND

V

IS

V

CC

SL4066B

System Logic

Semiconductor

SLS

Figure 2. Switching Waveforms

Figure 3. Switching Waveforms

EXPANDED LOGIC DIAGRAM

(1/4 of the Device)

Control

Switch

GND = L

OFF

V

CC

= H

ON