SL

7101

System Logic

Semiconductor

SLS

EARTH LEAKAGE CURRENT DETECTOR

Description

The SL7101 is designed for use in earth leakage circuit

interrupters for operation directly of the AC Line in breakers.

It contains pre regulator, main regulator, after regulator,

differential amplifier, level comparator, latch circuit. The input in

the differential amplifier is connect to the secondary node of

zero current transformer. The level comparator generates high

level when earth leakage current is greater than some level.

∑ Low Power Consumption (P

D

=5mW) 100V/200V

∑ 100V/200V Common Built-in Voltage Regulator

∑ High Gain Differential Amplifier

∑ High Input Sensitivity

∑ Minimum External Parts

∑ Large Surge Margin

∑ Wide Operating Temperature Range (T

¿

=-30 to 85∞C)

∑ High Noise Immunity

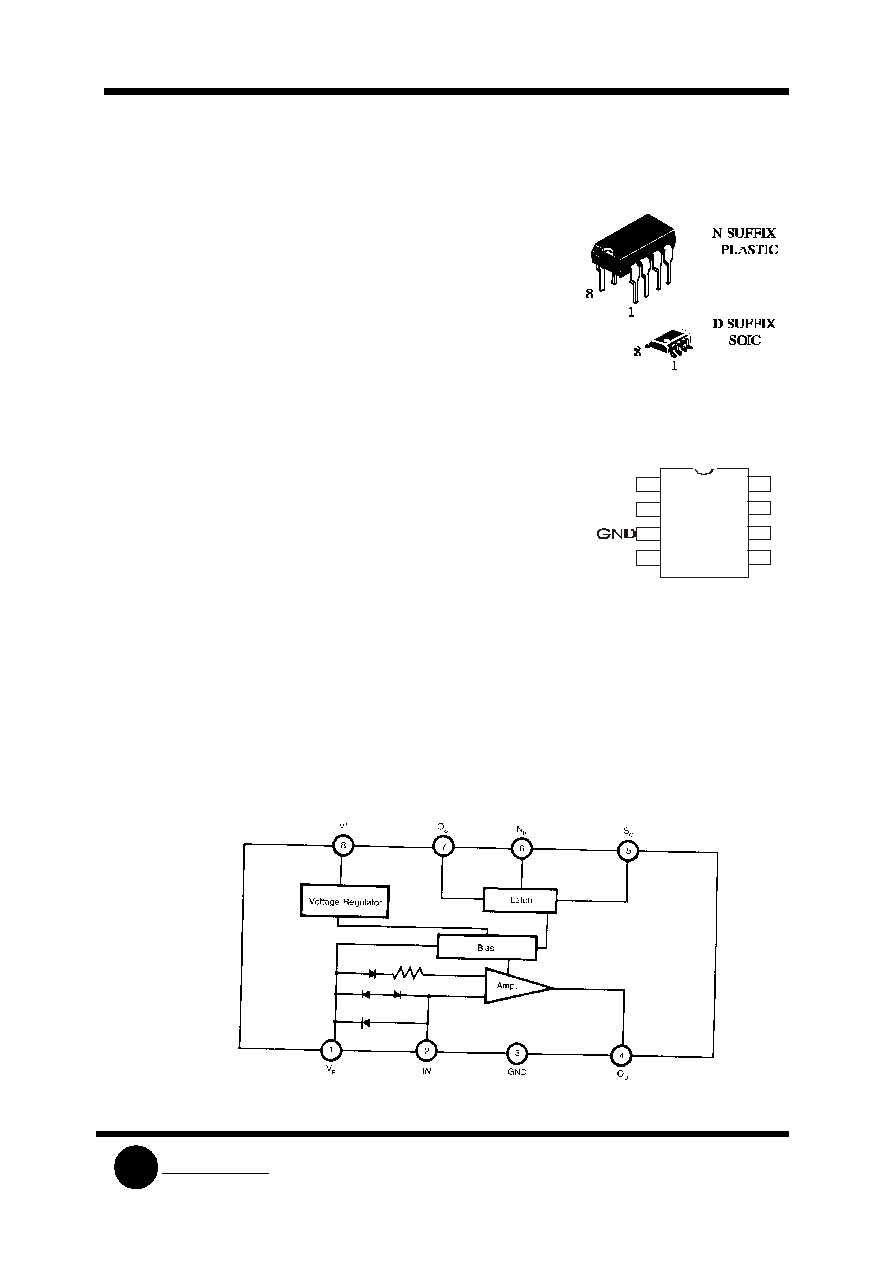

Block Diagram

Feature

Pin Configuration

(Top View)

20V

8mA

200mW

- 30 to 85∞C

- 55 to 125∞C

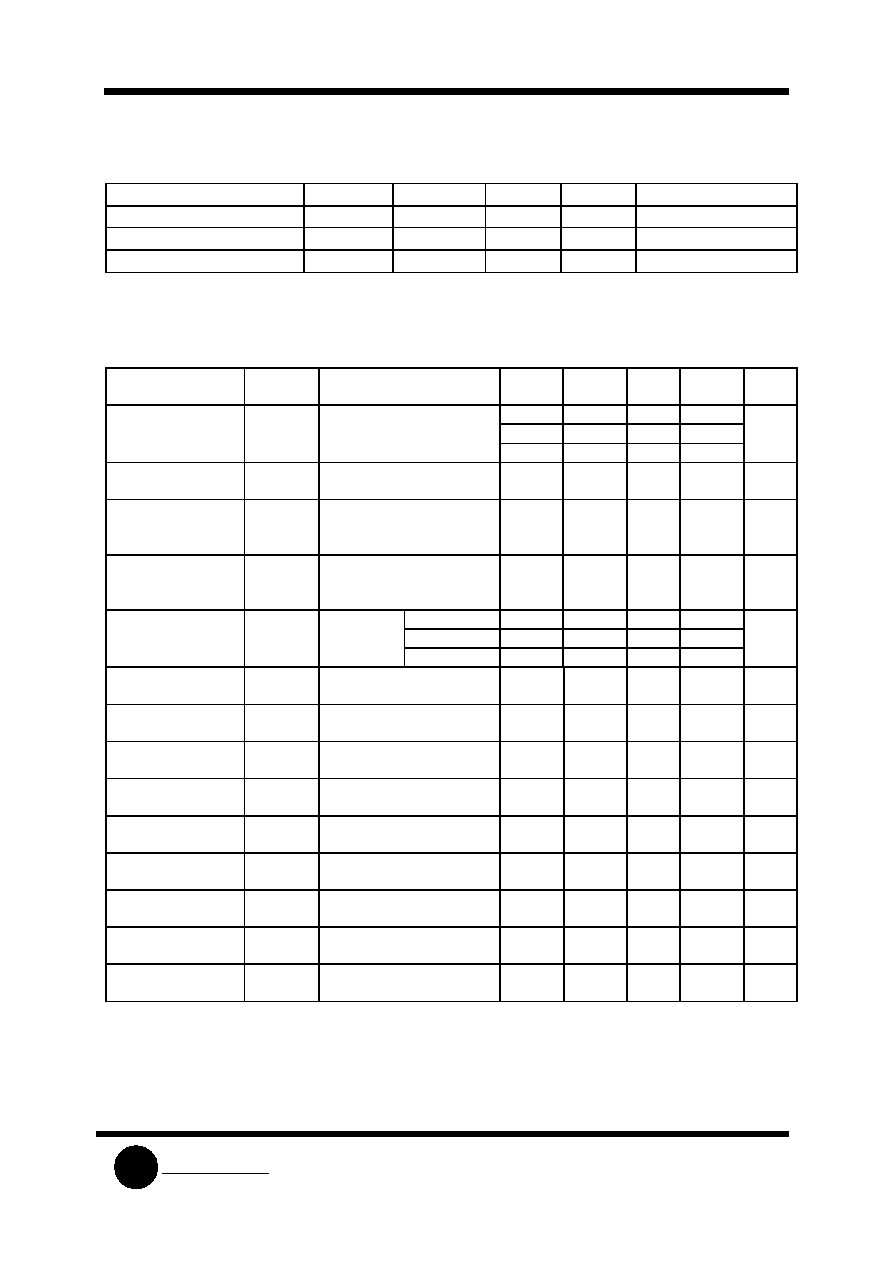

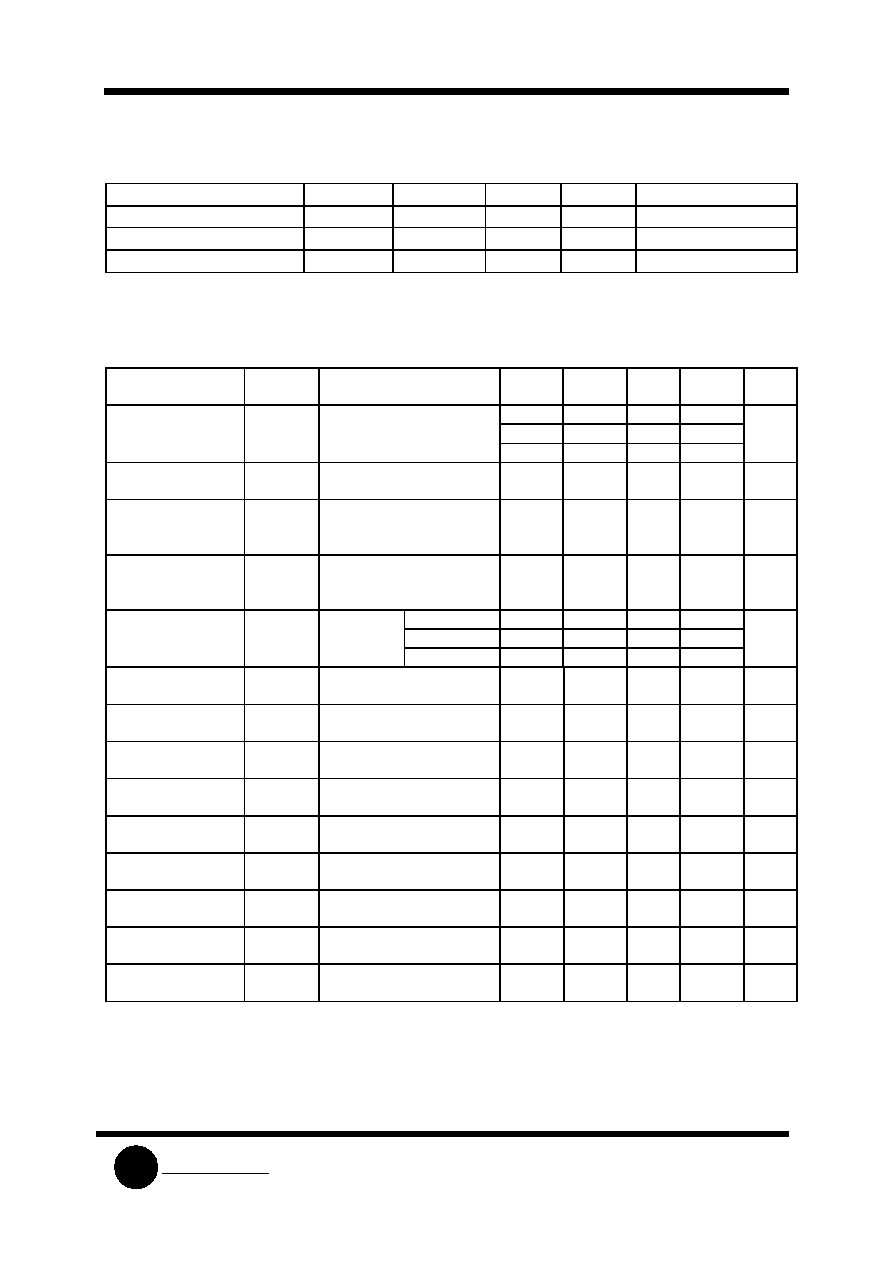

Absolute Maximum Ratings (T^=25∞c)

ß

Supply Voltage

ß

Supply Current

ß

Power Dissipation

ß

Operating Temperature

ß

Storage Temperature

4

3

2

1

5

6

7

8

V

R

O

D

IN

V

+

O

S

N

R

S

C

SL

7101

System Logic

Semiconductor

SLS

Recomended Operating Condition: T

A

=-30∞C to 80∞C

PARAMETER

SYMBOL

MIN.

TYP.

MAX

UNIT

Supply Voltage

V

+

12

V

Vs-GND Capacitor

Cvs

1

µ

F

O

S

-GND Capacitor

Cos

1

µ

F

Electrical Characteristics

PARAMETER

SYMBOL

CONDTIONS

TEMP.

(∞C)

MIN.

TYP.

MAX.

UNIT

-30

-

-

580

25

300

400

530

Supply Current 1

l

S1

V

+

=12V,

V

R

- V

I

= 30 mV

85

-

-

480

µ

A

* Trip Voltage

V

T

V

+

= 16V,

V

R

- V

I

= X

-30

85

9

13.5

18

mV

(rms)

Differential

Amplifier

Output Current 1

I

TD1

V

+

= 16 V,

V

R

- V

I

= 30 mV

V

OD

= 1.2 V

25

-12

-20

-30

µ

A

Differential

Amplifier Output

current 2

I

TD2

V

+

= 16 V,

V

R

- V

I

= short

V

OD

= 0.8 V

25

17

27

37

µ

A

l

SI

= 580

µ

A

-30

-200

-

l

SI

= 530

µ

A

25

-100

-

Output Current

I

O

V

SC

= 1.4 V

V

OS

= 0.8 V

l

SI

= 480

µ

A

85

-75

-

µ

A

S

C

O

N

Voltage

V

SC

ON V

+

= 16 V

25

0.7

1.0

1.4

V

S

C

Input Current

I

SC

ON

V

+

= l2V

25

-

-

5

µ

A

Output "L" Current

I

OSL

V

+

= 12 V,

V

OSL

= 0.2 V

-30

85

200

800

1400

µ

A

Input Clamp

Voltage

V

IC

V

+

= 12 V,

I

IC

= 20 mA

-30

85

4.3

-

6.7

V

Differential Input

Clamp Voltaqe

V

IDC

I

IDC

= 100mA

-30

85

0.4

1.2

2

V

Max. Current

Voltage

V

SM

I

SM

= 7 mA

25

20

24

28

V

Supply Current 2

I

S2

V

OS

= 0.5 V,

V

R

- V

I

= X

-30

85

-

-

1200

µ

A

Latch Circuit Off

Supply Votaqe

V+ OFF

25

0.5

V

Response Time

T

ON

V

+

= 16 V,

V

R

- V

I

= 0.3 V

25

1

3

4

ms

* A: 9 ~12.5 B: 11.5~15.5 C: 14.5~18

SL

7101

System Logic

Semiconductor

SLS

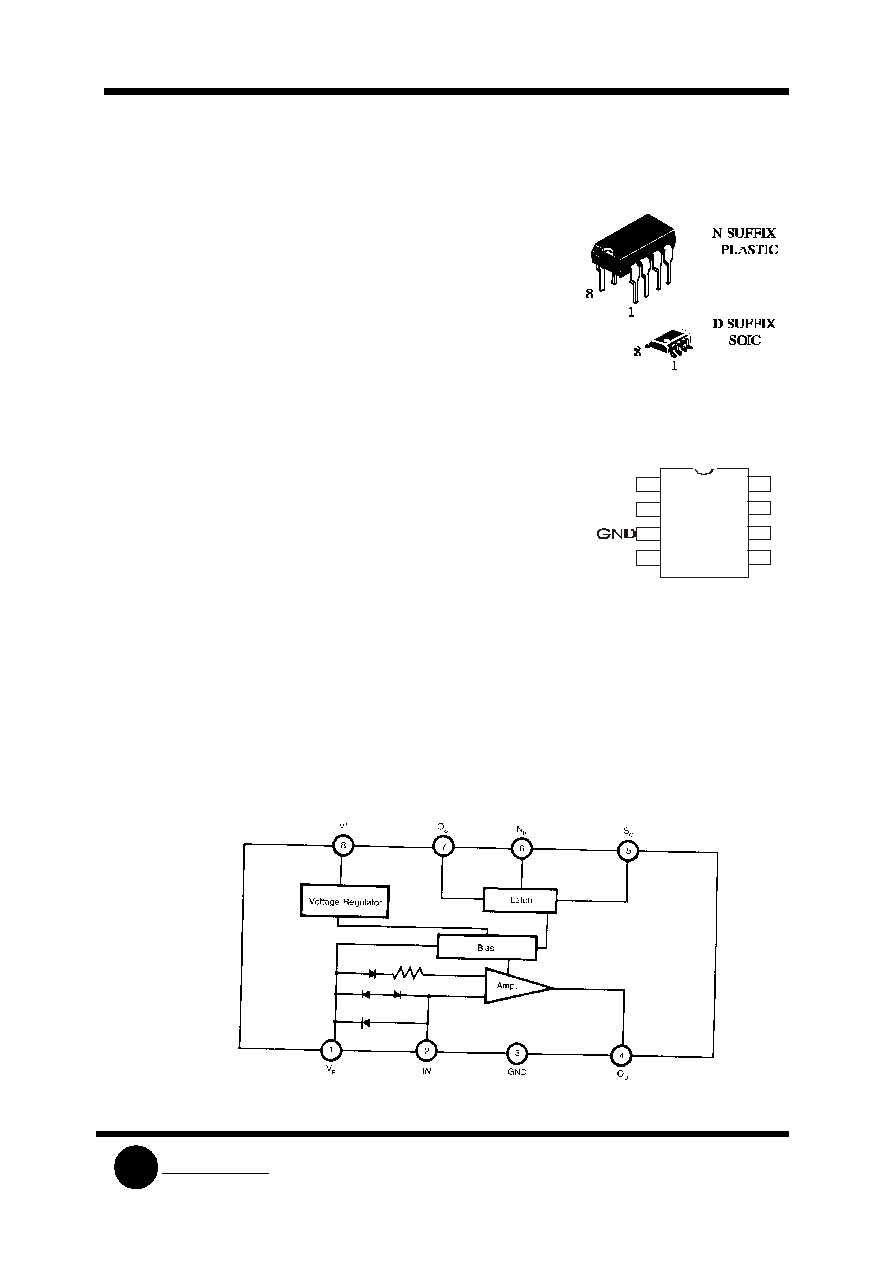

Typical Application

Description of elements of application diagram

1. The resistance of R1 resistor is chosen in such a way so that to limit IC's consumption

current (not more than 8 mA), and here the voltage drop is around 21-28V.

2. R2 resistor provides the necessary bias of the differential cascade.

3. R3 resistor is a loading one per input.

4. R4 resistor limits the charging current of C4 electrolytic capacitor are required to maintain

IC performance until the fuse is completely burn out. Its value is chosen correspondingly.

5. C1 electrolytic capacitor is a filtering one as per supply (around 1 ≠ 10

µ

F ).

6. —2 and C3 capacitors are filtering ones (not more than 1

µ

F)