SL74HC221

System Logic

Semiconductor

SLS

Dual Monostable Multivibrator

The SL74HC221 is identical in pinout to the LS/ALS221. The device

inputs are compatible with standard CMOS outputs; with pullup

resistors, they are compatible with LS/ALSTTL outputs.

There are two trigger inputs, A INPUT (negative edge) and

B INPUT (positive edge). These inputs are valid for rising/falling

signals

The device may also be triggered by using the CLR input (positive-

edge) because of the Schmitt-trigger input; after triggering the output

maintains the MONOSTABLE state for the time period determined by

the external resistor R

X

and capacitor C

X

. Taking CLR low breaks this

MONOSTABLE STATE. If the next trigger pulse occurs during the

MONOSTABLE period it makes the MONOSTABLE period longer.

∑

Outputs Directly Interface to CMOS, NMOS, and TTL

∑

Operating Voltage Range: 3.0 to 6.0 V

∑

Low Input Current: 1.0

µ

A

∑

High Noise Immunity Characteristic of CMOS Devices

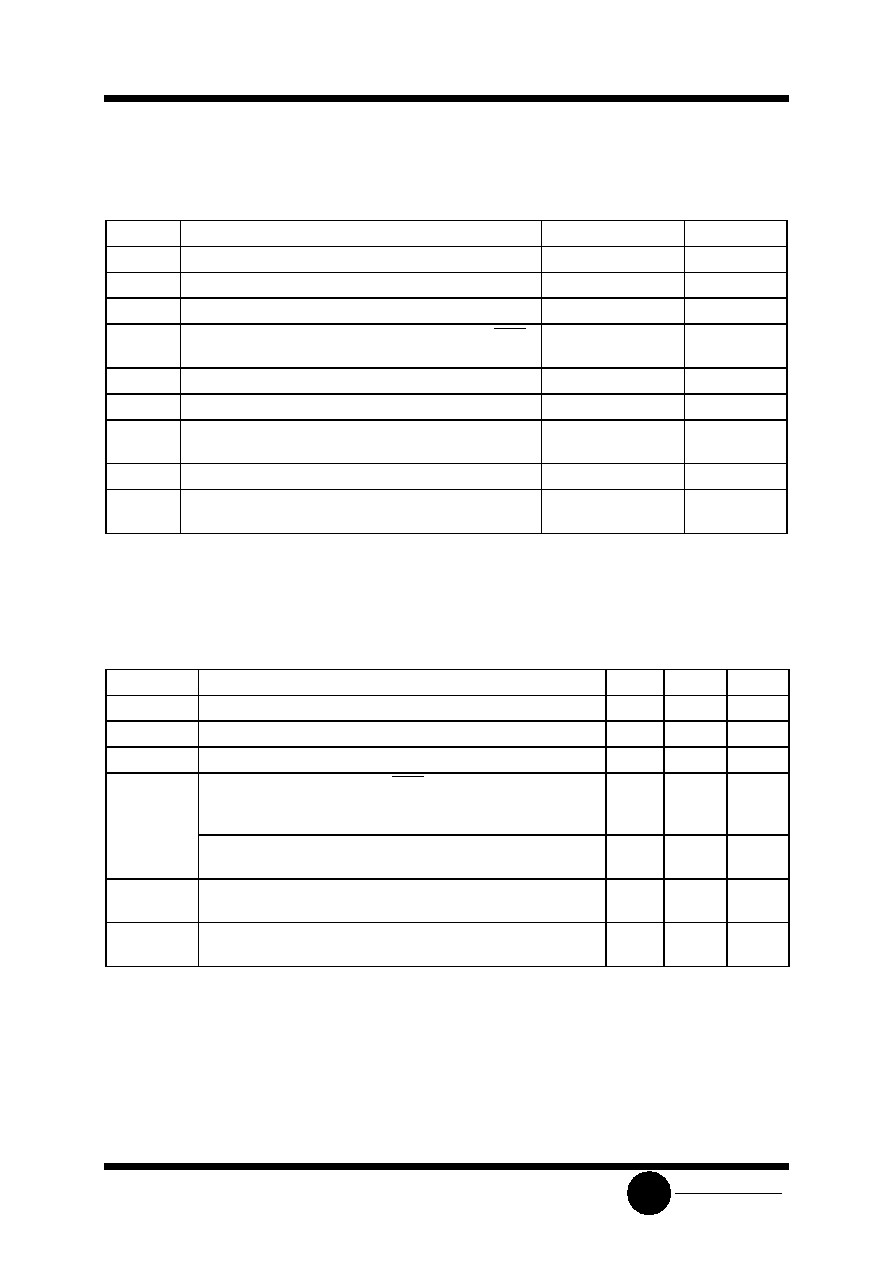

ORDERING INFORMATION

SL74HC221N Plastic

SL74HC221D SOIC

T

A

= -55

∞

to 125

∞

C for all packages

PIN ASSIGNMENT

LOGIC DIAGRAM

PIN 16 =V

CC

PIN 8 = GND

FUNCTION TABLE

Inputs

Outputs

Note

A

B

CLR

Q

Q

H

H

Output

Enable

X

L

H

L

*

H

*

Inhibit

H

X

H

L

*

H

*

Inhibit

L

H

Output

Enable

L

H

Output

Enable

X

X

L

L

H

Inhibit

X = don't care

*

- except for monostable period

Note

(1) C

X

, R

X

, D

X

are external components.

(2) D

X

is a clamping diode.

The external capacitor is charged to V

CC

in the stand-by

state, i.e. no trigger. When the supply voltage is turned off

C

X

is discharged mainly through an internal parasitic diode.

If C

X

is sufficiently large and V

CC

decreases rapidy, there will

be some possibility of damaging the I.C. with a surge

current or latch-up. If the voltage supply filter capacitor is

large enough and V

CC

decrease slowly, the surge current is

automatically limited and damage the I.C. is avoided. The

maximum forward current of the parasitic diode is

approximately 20 mA.

SL74HC221

System Logic

Semiconductor

SLS

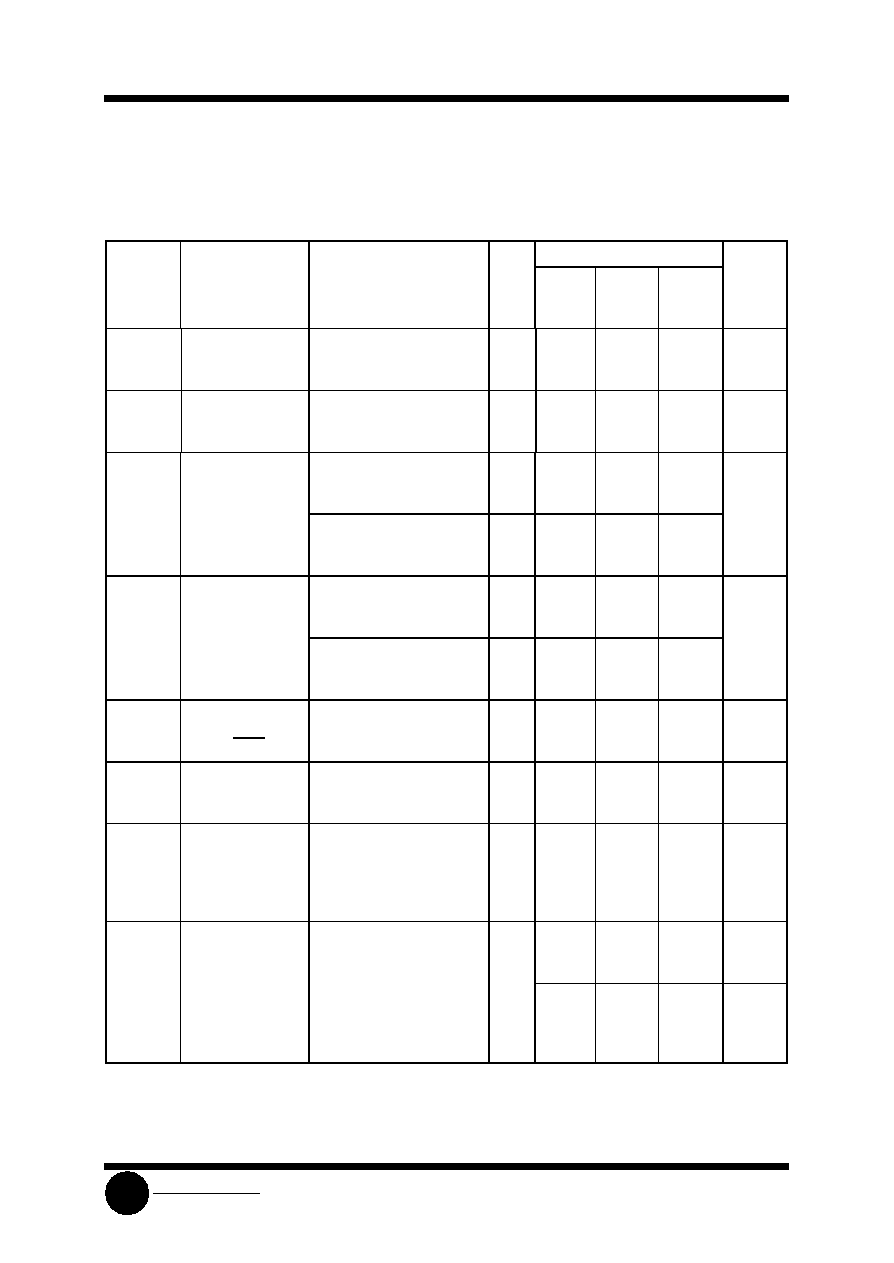

MAXIMUM RATINGS

*

Symbol

Parameter

Value

Unit

V

CC

DC Supply Voltage (Referenced to GND)

-0.5 to +7.0

V

V

IN

DC Input Voltage (Referenced to GND)

-1.5 to V

CC

+1.5

V

V

OUT

DC Output Voltage (Referenced to GND)

-0.5 to V

CC

+0.5

V

I

IN

DC Input Current, per Pin

A, B, CLR

C

X

, R

X

±

20

±

30

mA

I

OUT

DC Output Current, per Pin

±

25

mA

I

CC

DC Supply Current, V

CC

and GND Pins

±

50

mA

P

D

Power Dissipation in Still Air, Plastic DIP+

SOIC Package+

750

500

mW

Tstg

Storage Temperature

-65 to +150

∞

C

T

L

Lead Temperature, 1 mm from Case for 10 Seconds

(Plastic DIP or SOIC Package)

260

∞

C

*

Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the Recommended Operating Conditions.

+Derating - Plastic DIP: - 10 mW/

∞

C from 65

∞

to 125

∞

C

SOIC Package: : - 7 mW/

∞

C from 65

∞

to 125

∞

C

RECOMMENDED OPERATING CONDITIONS

Symbol

Parameter

Min

Max

Unit

V

CC

DC Supply Voltage (Referenced to GND)

3.0

**

6.0

V

V

IN

, V

OUT

DC Input Voltage, Output Voltage (Referenced to GND)

0

V

CC

V

T

A

Operating Temperature, All Package Types

-55

+125

∞

C

t

r

, t

f

Input Rise and Fall Time - CLR

(Figure 2)

V

CC

=2.0 V

V

CC

=4.5 V

V

CC

=6.0 V

0

0

0

1000

500

400

ns

A or B

-

No

Limit

R

X

External Timing Resistor

V

CC

<4.5 V

V

CC

4.5 V

10

2.0

1000

1000

k

C

X

External Timing Capacitor

0

No

Limit

µ

F

**

The SL74HC123 will function at 2.0 V but for optimum pulse width stability, V

CC

should be above

3.0 V.

This device contains protection circuitry to guard against damage due to high static voltages or electric

fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated

voltages to this high-impedance circuit. For proper operation, V

IN

and V

OUT

should be constrained to the range

GND

(V

IN

or V

OUT

)

V

CC

.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V

CC

).

Unused outputs must be left open.

SL74HC221

System Logic

Semiconductor

SLS

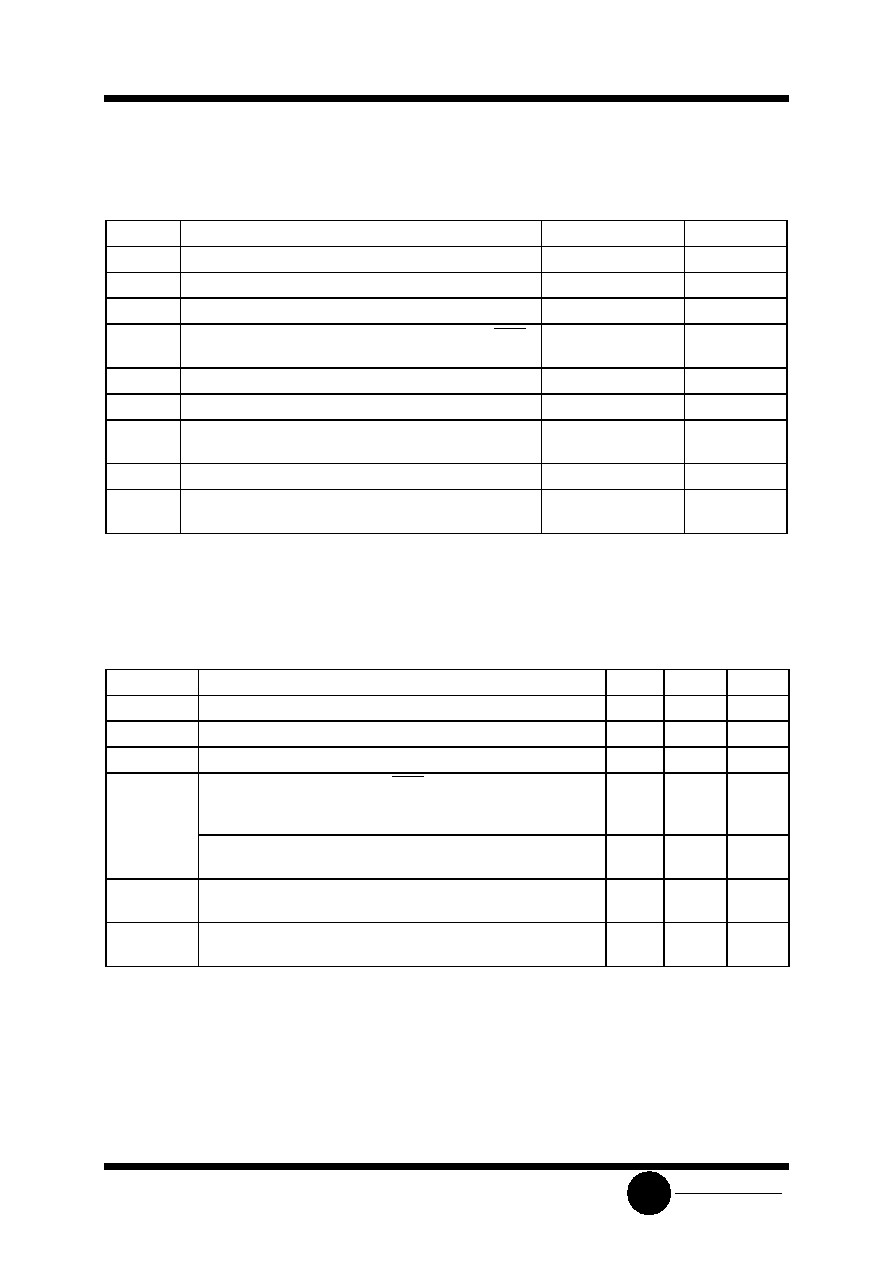

DC ELECTRICAL CHARACTERISTICS

(Voltages Referenced to GND)

V

CC

Guaranteed Limit

Symbol

Parameter

Test Conditions

V

25

∞

C

to

-55

∞

C

85

∞

C

125

∞

C

Unit

V

IH

Minimum High-

Level Input Voltage

V

OUT

=0.1 V or V

CC

-0.1 V

I

OUT

20

µ

A

2.0

4.5

6.0

1.5

3.15

4.2

1.5

3.15

4.2

1.5

3.15

4.2

V

V

IL

Maximum Low -

Level Input Voltage

V

OUT

=0.1 V or V

CC

-0.1 V

I

OUT

20

µ

A

2.0

4.5

6.0

0.5

1.35

1.8

0.5

1.35

1.8

0.5

1.35

1.8

V

V

OH

Minimum High-

Level Output

Voltage

V

IN

=V

IH

or V

IL

I

OUT

20

µ

A

2.0

4.5

6.0

1.9

4.4

5.9

1.9

4.4

5.9

1.9

4.4

5.9

V

V

IN

=V

IH

or V

IL

I

OUT

4.0 mA

I

OUT

5.2 mA

4.5

6.0

3.98

5.48

3.84

5.34

3.7

5.2

V

OL

Maximum Low-

Level Output

Voltage

V

IN

=V

IH

or V

IL

I

OUT

20

µ

A

2.0

4.5

6.0

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

V

V

IN

=V

IH

or V

IL

I

OUT

4.0 mA

I

OUT

5.2 mA

4.5

6.0

0.26

0.26

0.33

0.33

0.4

0.4

I

IN

Maximum Input

Leakage Current

(A, B, CLR)

V

IN

=V

CC

or GND

6.0

±

0.1

±

1.0

±

1.0

µ

A

I

IN

Maximum Input

Leakage Current

(R

X

, C

X

)

V

IN

=V

CC

or GND

6.0

±

50

±

500

±

500

nA

I

CC

Maximum

Quiescent Supply

Current

(per Package)

Standby State

V

IN

=V

CC

or GND

Q1 and Q2 = Low

I

OUT

=0

µ

A

6.0

130

220

350

µ

A

25

∞

C

-45

∞

C

to 85

∞

C

-55

∞

C

to

125

∞

C

I

CC

Maximum Supply

Current

(per Package)

Active State

V

IN

=V

CC

or GND

Q1 and Q2 = High

I

OUT

=0

µ

A

Pins 15 and 7 = 0.5 V

CC

6.0

400

600

800

µ

A

SL74HC221

System Logic

Semiconductor

SLS

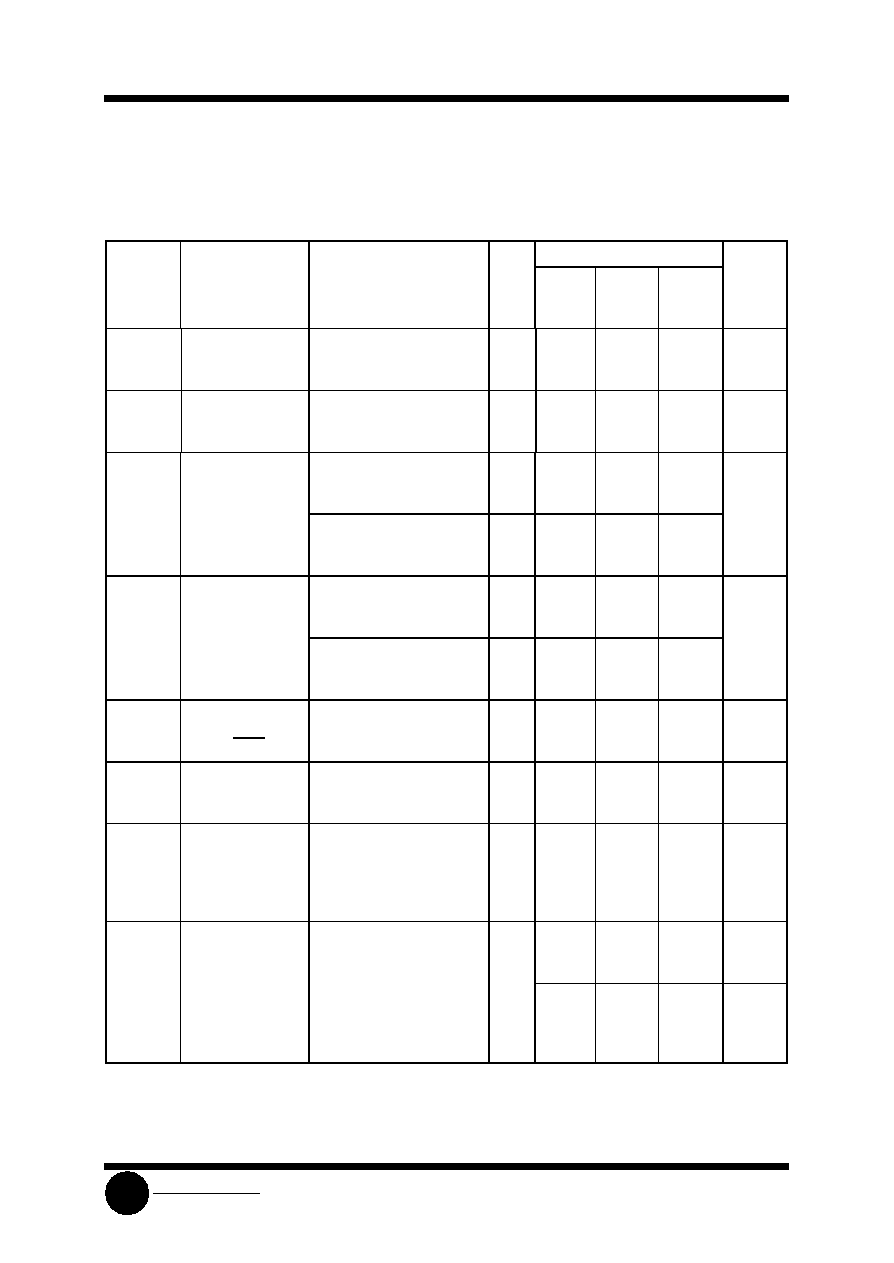

AC ELECTRICAL CHARACTERISTICS

(C

L

=50pF,Input t

r

=t

f

=6.0 ns)

V

CC

Guaranteed Limit

Symbol

Parameter

V

25

∞

C to

-55

∞

C

85

∞

C

125

∞

C

Unit

t

PLH

, t

PHL

Maximum Propagation Delay, Input A or B to Q or

Q (Figures 1 and 3)

2.0

4.5

6.0

255

50

45

320

65

55

385

75

65

ns

t

PLH

, t

PHL

Maximum Propagation Delay , CLR to Q or Q

(Figures 2 and 3)

2.0

4.5

6.0

215

45

35

270

55

45

325

65

55

ns

t

TLH

, t

THL

Maximum Output Transition Time, Any

Output(Figures 2 and 3)

2.0

4.5

6.0

75

16

14

95

20

17

110

22

20

ns

C

IN

Maximum Input Capacitance

A, B, CLR

C

X

, R

X

-

10

25

10

25

10

25

pF

Power Dissipation Capacitance

(Per Multivibrator)

Typical @25

∞

C,V

CC

=5.0 V

C

PD

Used to determine the no-load dynamic power

consumption:

P

D

=C

PD

V

CC

2

f+I

CC

V

CC

150

pF

TIMING REQUIREMENTS

(C

L

=50pF,Input t

r

=t

f

=6.0 ns)

V

CC

Guaranteed Limit

Symbol

Parameter

V

25

∞

C to

-55

∞

C

85

∞

C

125

∞

C

Unit

t

rec

Minimum Recovery Time,

Inactive to A or B

(Figure 2)

2.0

4.5

6.0

0

0

0

0

0

0

0

0

0

ns

t

w

Minimum Pulse Width,

Input A or B (Figure 1)

2.0

4.5

6.0

100

20

17

125

25

20

150

30

25

ns

t

w

Minimum Pulse Width,

CLR (Figure 2)

2.0

4.5

6.0

100

20

17

125

25

20

150

30

25

ns

t

r,

t

r

Maximum Input Rise and

Fall Times, CLR

(Figure 2)

2.0

4.5

6.0

1000

500

400

1000

500

400

1000

500

400

ns

A or B (Figure 2)

2.0

4.5

6.0

No Limit

SL74HC221

System Logic

Semiconductor

SLS

Figure 1. Switching Waveforms

Figure 2. Switching Waveforms

Figure 3. Test Circuit

SL74HC221

System Logic

Semiconductor

SLS

TIMING DIAGRAM

EXPANDED LOGIC DIAGRAM