COM81C17

Twenty Pin UART (TPUART)

FEATURES

!

Single Chip UART With Baud Rate

Generator

!

Asynchronous Operation

-

16 Selectable Baud Rate Clock

Frequencies (Internal)

-

External 16x Clock (100 KBaud)

-

Character Length: 7 or 8 Bits

-

1 or 2 Stop Bit Selection

!

Small 20 Pin DIP (300 mil) or PLCC

!

Full or Half Duplex Operation

!

Double Buffering of Data

!

Programmable Interrupt Generation

!

Programmable Modem/Terminal Signals

!

Odd or Even Parity Generate and Detect

!

Parity, Overrun and Framing Error Detection

!

TTL Compatible Inputs and Outputs

!

High Speed Host Bus Operation (with no

wait state)

!

Low Power CMOS

!

Single +5V Power Supply

GENERAL DESCRIPTION

The COM81C17 TPUART is an asynchronous

only receiver/transmitter with a built in

programmable baud rate generator housed in a

twenty pin package. The TPUART receives

serial data streams and converts them into

parallel data characters for the processor. While

receiving serial data, the TPUART will also

accept data characters from the processor in

parallel format and convert them into serial

format along with start, stop and optional parity

bus. The TPUART will signal the processor via

interrupt when it has completely transmitted or

received a character and requires service.

Complete status information is available to the

processor through the status register. The

TPUART features two general purpose control

pins that can be individually programmed to

perform as terminal or modem control

handshake signals.

2

TABLE OF CONTENTS

FEATURES ........................................................................................................................................1

GENERAL DESCRIPTION..................................................................................................................1

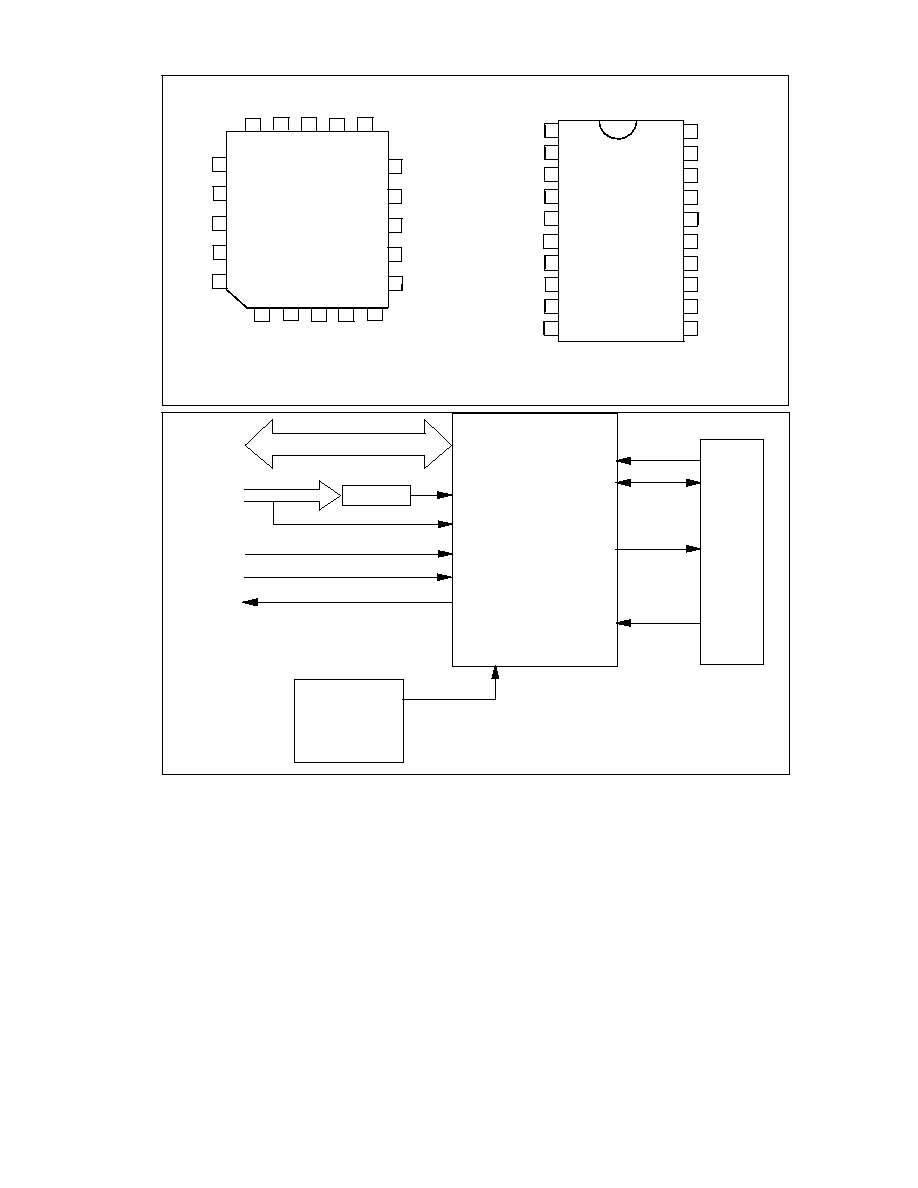

PIN CONFIGURATION/TYPICAL TPUART INTERFACE.....................................................................3

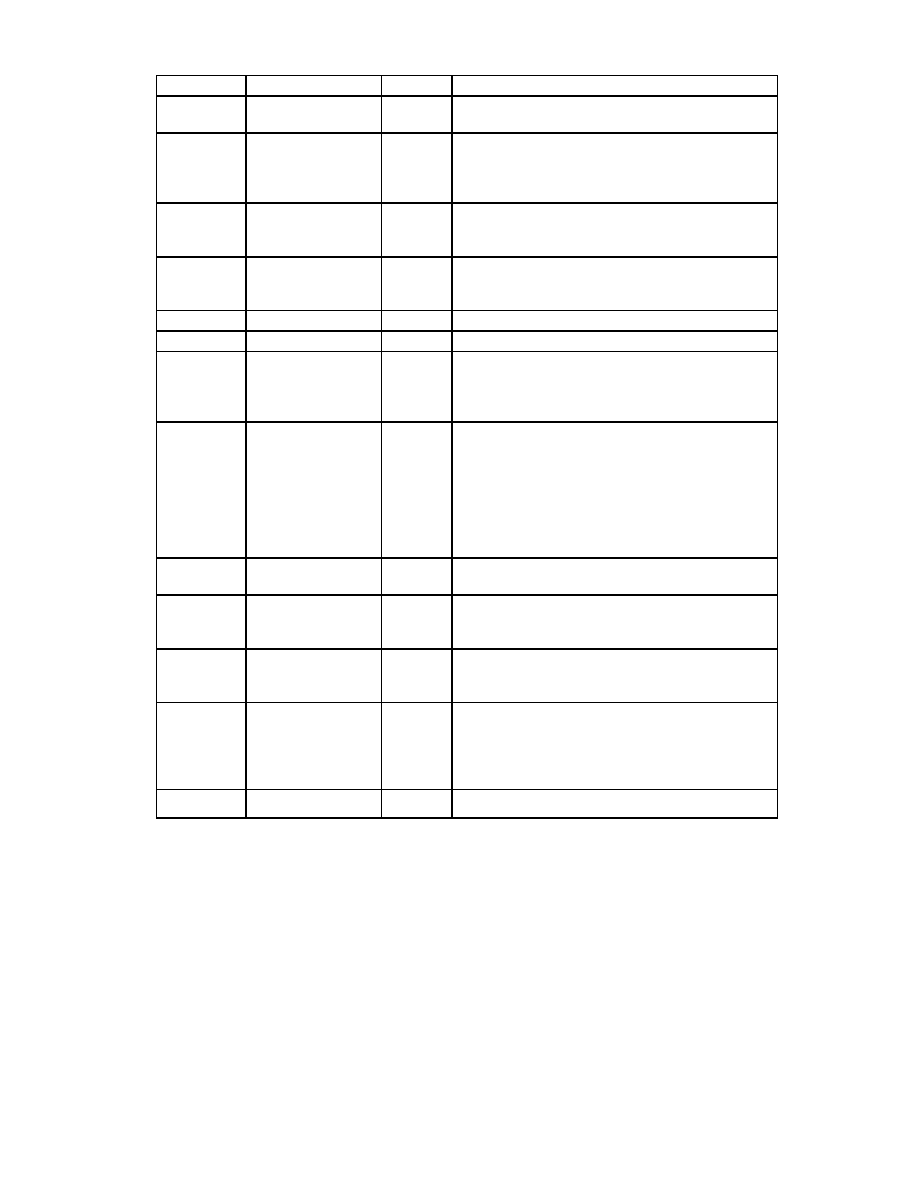

BLOCK DIAGRAM..............................................................................................................................4

DESCRIPTION OF PIN FUNCTIONS .................................................................................................5

FUNCTIONAL DESCRIPTION ............................................................................................................6

THE ON CHIP BAUD RATE GENERATOR .........................................................................................7

REGISTER DESCRIPTIONS ..............................................................................................................8

OPERATIONAL DESCRIPTION........................................................................................................12

80 Arkay Drive

Hauppauge, NY 11788

(516) 435-6000

FAX (516) 273-3123

3

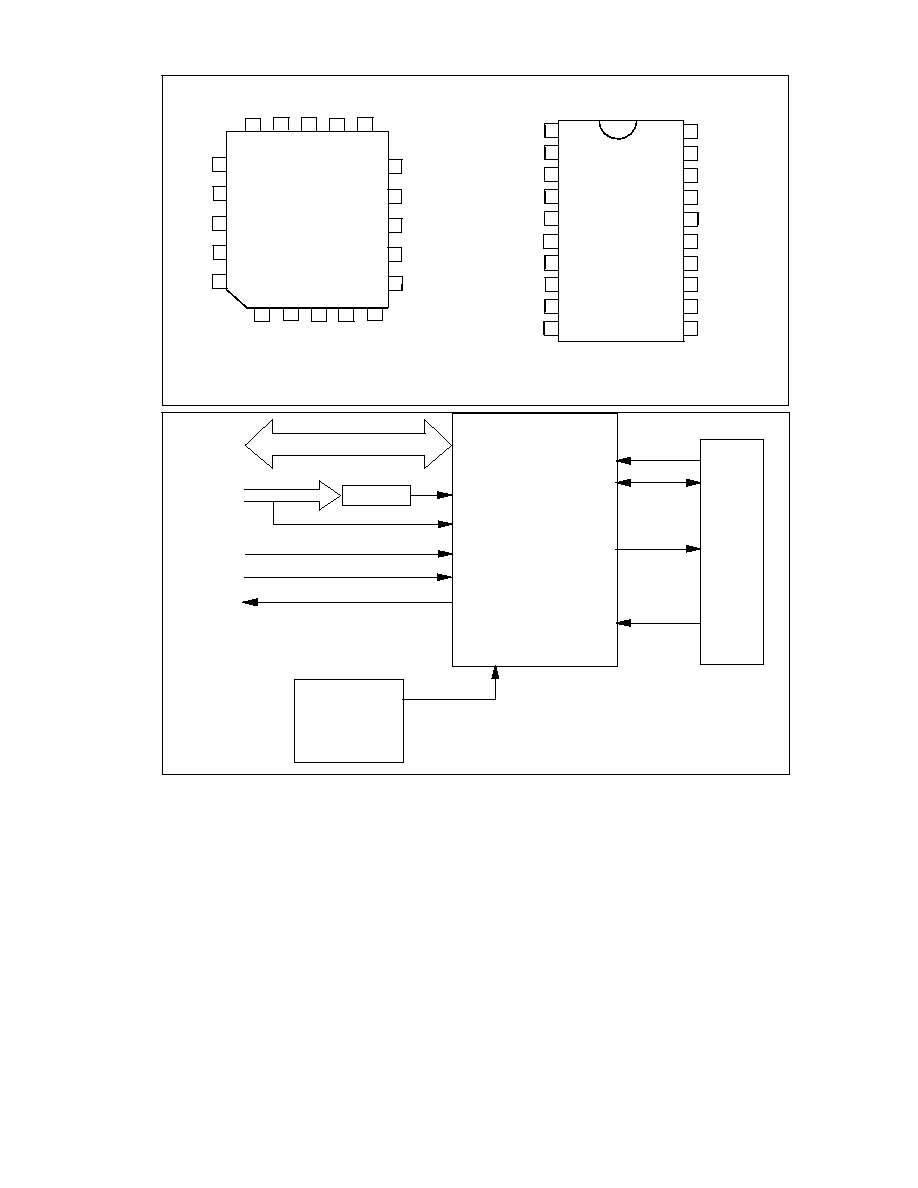

PIN CONFIGURATION

FIGURE 1 � TYPICAL TPUART INTERFACE

FIGURE 1 � TYPICAL TPUART INTERFACE

nCP

2

Vcc

D

0

D

1

nCS

CLOCK

D

7

D

6

GND

D

5

n

C

P

1

T

X

R

X

R

S

n

I

N

T

n

R

D

D

2

D

3

D

4

n

W

R

19

20

1

2

3

13

12

11

10

9

18

17 16 15

14

4

5

6

7

8

Package: 20 Pin PLCC

D

0

D

1

nCS

nRD

D

2

D

3

D

4

D

5

nWR

GND

Vcc

CP

2

CP

1

TX

RX

RS

nINT

D

7

CLOCK

D

6

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

Package 20 Pin DIP

DATA BUS

ADDRESS

BUS

nWRITE

nREAD

INTERRUPT

REQUEST

5.0688 MHZ

OSCILLATOR

OR

TTL CLOCK

D0-D7

nCS

RS

nWR

nRD

nINT

nCP1

nCP2

TX

RX

COM81C17

TWENTY

PIN

UART

DECODE

T

T

L

/

R

S

-

2

3

2

-

C

4

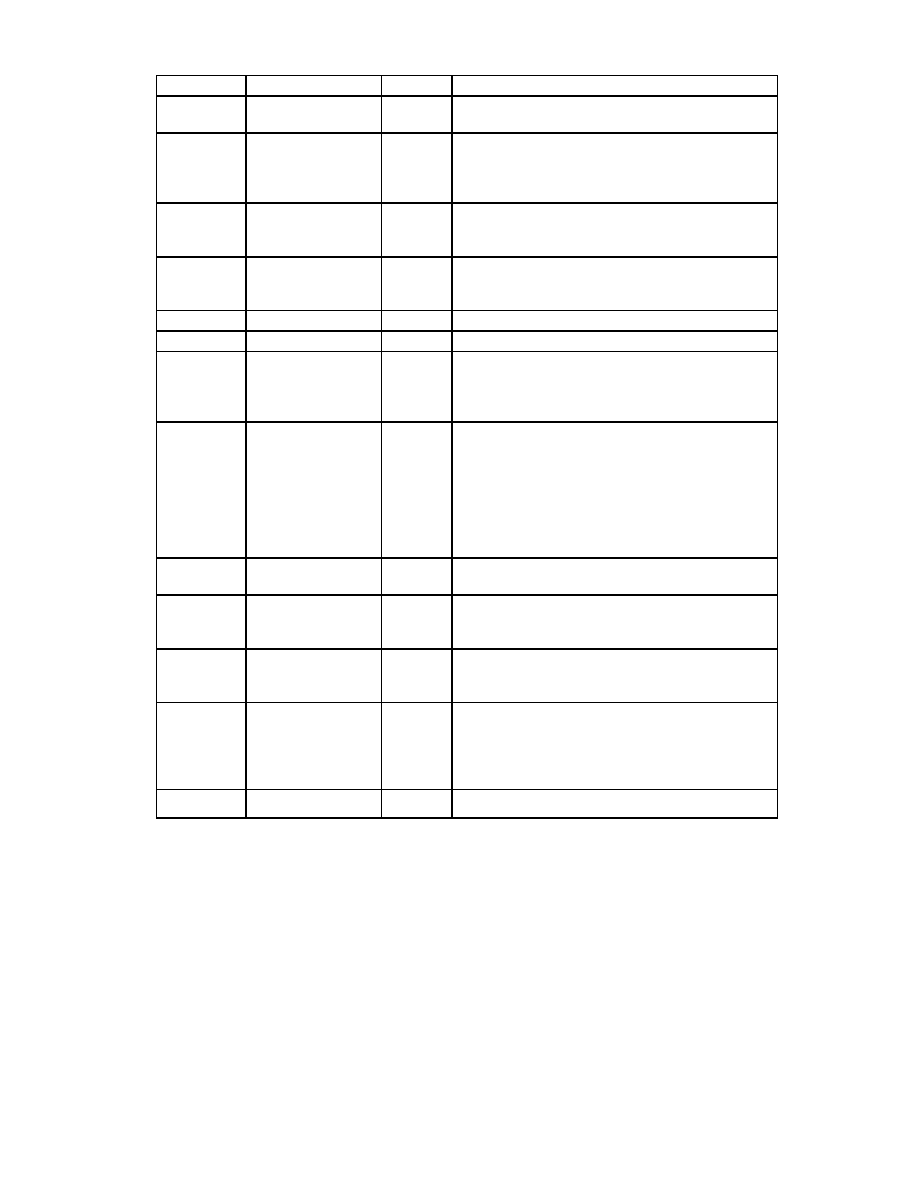

FIGURE 2 � COM81C17 BLOCK DIAGRAM

FIGURE 2A � 5.0688 MHz CRYSTAL OSCILLATOR CIRCUIT

D0-D7

nCS

nRD

nWR

RS

DATA

BUS

TRANS

nINT

VCC

GND

n

C

P

1

n

C

P

2

I

N

T

E

R

N

A

L

D

A

T

A

B

U

S

MODE

REGISTER

BAUD

RATE

SELECT

REGISTER

TRANSMIT

BUFFER

TRANSMIT

SHIFT REGISTER

TRANSMIT

CONTROL

BAUD

RATE

GENERATOR

RECEIVE

CONTROL

RECEIVE

SHIFT REGISTER

RECEIVE

BUFFER

STATUS

REGISTER

TX

CLOCK

RX

READ

WRITE

DECODE

LOGIC

MASK

REGISTER

& LOGIC

CONTROL

REGISTER

1800 OHM

560 OHM

220 OHM

7404

7404

220 OHM

30 pF

5.0688 MHz

7404

7404

5

DESCRIPTION OF PIN FUNCTIONS

DIP PIN NO.

NAME

SYMBOL

DESCRIPTION

1, 2, 5-7,

9,11-12

DATA BUS

D

0

-D

7

An 8-bit bi-driectional DATA BUS is used to

interface the TPUART to the processor Data Bus.

3

CHIP SELECT

nCS

A low level on this input enables the TPUART for

reading and writing to the processor. When nCS is

high, the DATA BUS is in high impedance and the

nWR and nRD will have no effect on the chip.

4

READ DATA

STROBE

nRD

A low pulse on this input (when nCS is low) enables

the TPUART to place the data or the status

information on the DATA BUS.

8

WRITE DATA

STROBE

nWR

A low pulse on this input (when nCS is low) enables

the TPUART to accept the data or control word

from the DATA BUS into the TPUART.

10

GROUND

GND

Power Supply Return.

13

CLOCK

CLK

External TTL Clock Input (See Table 2)

14

INTERRUPT

REQUEST

nINT

An interrupt request is asserted by the TPUART

when an enabled condition has occurred in the

Status Register. This is an active low, open drain

output. This pin has an internal pullup register.

15

REGISTER

SELECT

RS

During processor to TPUART communications, this

input is used to indicate which internal register will

be selected for access by the processor. When this

input is low, data can be written to the TX Holding

Buffer or data can be read from the RX Holding

Register. When this input is high control words can

be written to the Control Register or status

information can be read from the Status Register.

16

RECEIVER DATA

RX

This input is the receiver serial data. A high to low

transition is required to initiate data reception.

17

TRANSMITTER

DATA

TX

This output is the transmitted serial data from the

TPUART. When a transmission is concluded, the

TX line will always return to the mark (High) state.

18

CONTROL PIN 1

nCP1

This control pin is an input only pin. It can be

programmed to perform the functions of CTS or

DSR/DCD.

19

CONTROL PIN 2

nCP2

This control pin can be programmed to be either an

input or an output. When in input mode, this pin

can perform the functions of DSR/DCD. When in

output mode, this pin can perform the functions of

DTR or RTS.

20

POWER SUPPLY

V

CC

+5V Supply Voltage