| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: IRCC2.0 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

IrCC 2.0

PRELIMINARY

Infrared Communications Controller

FEATURES

∑

Multi-Protocol Serial Communications

Controller

∑

Full IrDA v1.1 Implementation: 2.4 kbps -

115.2 kbps, 0.576 Mbps, 1.152 Mbps and 4

Mbps

∑

Consumer Infrared (Remote Control)

Interface

∑

SHARP Amplitude Shift Keyed Infrared

(ASK IR) Interface

∑

Direct Rx/Tx Infrared Diode Control (Raw)

and General Purpose Data Pins

∑

Programmable High-Speed Synchronous

Communications Engine (SCE) with a 128-

Byte FIFO and Programmable Threshold

∑

Programmable DMA Refresh Counter

∑

High-Speed NS16C550A-Compatible

Universal Asynchronous Receiver/

Transmitter Interface (ACE UART) with 16-

Byte Send and Receive FIFOs

∑

ISA Single-Byte and Burst-Mode DMA and

Interrupt-Driven Programmed I/O with Zero

Wait State and String Move Timing

∑

16 Bit CRC-CCITT and 32 Bit IEEE 802

CRC32 Hardware CRC Generators

∑

Automatic Transceiver Control

∑

Transmit Pulse Width Limiter

∑

SCE Transmit Delay Timer

∑

IR Media Busy Indicator

GENERAL DESCRIPTION

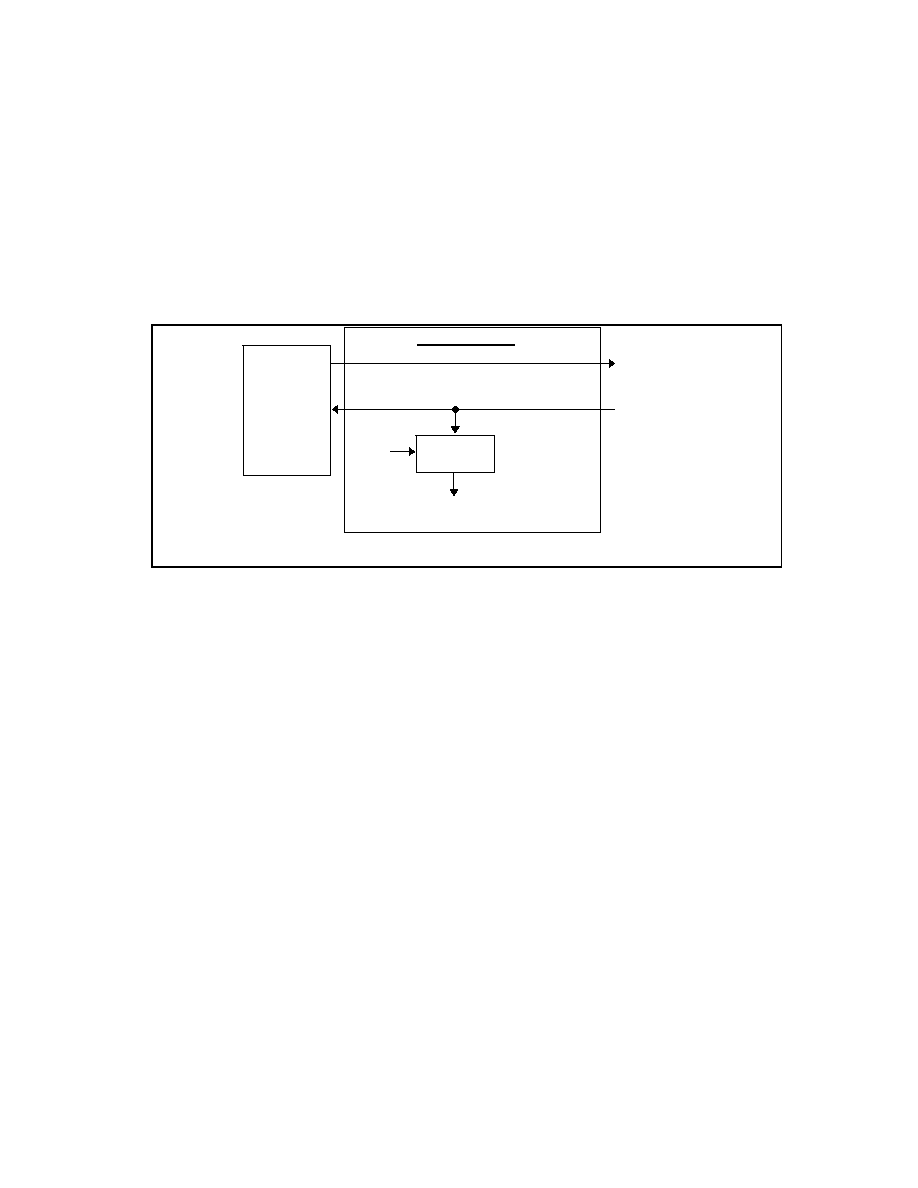

This document describes the Infrared

Communications Controller (IrCC 2.0) function,

which is common to a number of SMSC

products. The IrCC 2.0 consists of two main

architectural blocks: the ACE 16C550A UART

and a Synchronous Communications Engine

(SCE) (Figure 2). It's own unique register set

supports each block.

The IrCC 2.0 UART-driven IrDA SIR and

SHARP ASK modes are backward compatible

with current SMSC Super I/O and Ultra I/O

infrared implementations. The IrCC 2.0 SCE

supports IrDA v1.1 0.576 Mbps, 1.152 Mbps, 4

Mbps, and Consumer IR modes. All of the

SCE-driven modes can use DMA. The IrCC 2.0

offers flexible signal routing and programmable

output control through the Raw mode interface,

General Purpose Data pins and Output

Multiplexer. Chip-level address decoding is

required to access the IrCC 2.0 register sets.

2

TABLE OF CONTENTS

FEATURES ........................................................................................................................................1

GENERAL DESCRIPTION..................................................................................................................1

INTERFACE DESCRIPTION...............................................................................................................4

PORTS ...........................................................................................................................................4

CHIP-LEVEL CONFIGURATION CONTROLS .................................................................................6

OPERATION MODES.........................................................................................................................9

RAW IR ..........................................................................................................................................9

CONSUMER IR (REMOTE CONTROL)...........................................................................................9

IrDA SIR AND SHARP ASK IR INTERFACE..................................................................................14

INFRARED DATA ASSOCIATION .................................................................................................19

REGISTERS.....................................................................................................................................23

ACE UART CONTROLS................................................................................................................23

SCE CONTROLS ..........................................................................................................................23

ACE UART....................................................................................................................................44

SCE .................................................................................................................................................59

FRAMING .....................................................................................................................................59

ACTIVE FRAME INDICATOR........................................................................................................59

IRDA ENCODER...........................................................................................................................60

CONSUMER IR ENCODER TIMING .............................................................................................65

MULTI-FRAME WINDOW SUPPORT............................................................................................67

LOOPBACK MODE.......................................................................................................................68

AUTOMATIC TRANSCEIVER CONTROL......................................................................................69

BUS INTERFACE I/O .......................................................................................................................71

FIFO MULTIPLEXER ....................................................................................................................71

128-BYTE SCE FIFO ....................................................................................................................71

DMA .............................................................................................................................................73

PROGRAMMED I/O ......................................................................................................................77

OUTPUT MULTIPLEXER..................................................................................................................82

TRANSMIT PULSE WIDTH LIMIT .................................................................................................83

CHIP-LEVEL IrCC 2.0 ADDRESSING SUPPORT .............................................................................84

AC TIMING.......................................................................................................................................85

IR RX PULSE REJECTION ...........................................................................................................85

IRDA 4PPM...................................................................................................................................85

IRDA HDLC...................................................................................................................................86

80 Arkay Drive

Hauppauge, NY 11788

(516) 435-6000

FAX (516) 273-3123

3

Raw

IR

IR

Transducer

Module

REGISTERS

ACE

UART

Bus Interface

I/O

Clock Generator

COMM

Port

IrDA

IR

ASK

IR

Consumer

IR

SMSC Infrared Communications Controller

Output

Mux

COM

AUX

SCE

Encoders

System Controls

FIGURE 1 - SMSC IrCC 2.0 FUNCTIONAL COMPONENTS

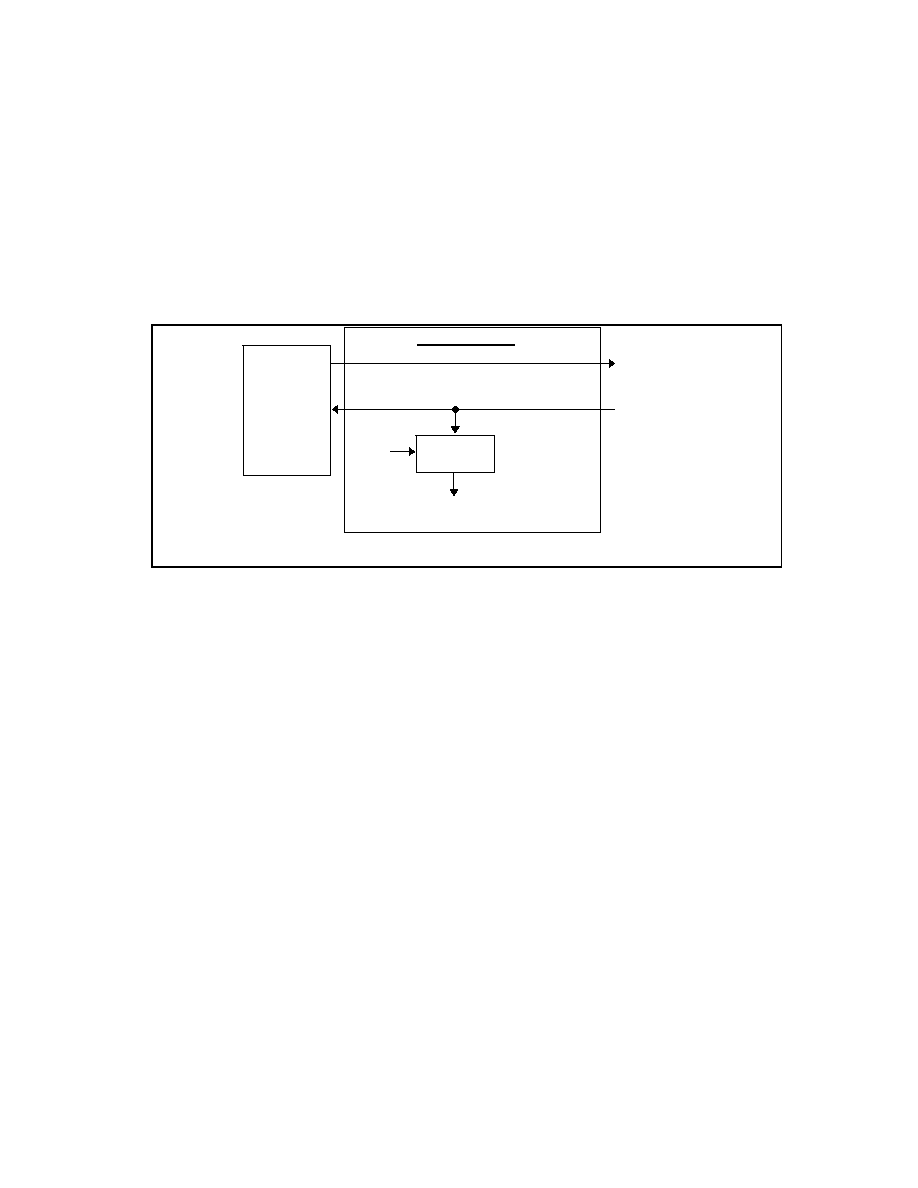

ACE UART

SCE

IrDA SIR

Sharp ASK

COM

IrDA FIR

Consumer

SCE

Registers

ACE

Registers

Output

MUX

FIFO,

DMA, I/O,

Interrupts

Databus

MUX

Bus Interface

nACE

ISA Controls

Data (0-7)

Address (0-2)

IR

COM

AUX

G.P.

nSCE

GP/Raw/Fast

FIGURE 2 - IrCC 2.0 ARCHITECTURAL BLOCK DIAGRAM

4

INTERFACE DESCRIPTION

The Interface Description lists the signals that

are required to place the IrCC 2.0 in a larger

chip-level context.

There are four groups of signals in this section:

PORT signals, HOST BUS controls, SYSTEM

controls, and CHIP-LEVEL CONFIGURATION

controls.

PORTS

The four Ports (IR, COM, AUX, and General

Purpose) provide external access for serial data

and controls. The active IrCC 2.0 encoder is

routed through the Output Multiplexer to either

the IR, COM, or AUX port. The General

Purpose port provides external access for

controls that are independent of the IrCC 2.0

Block Control bits or the Output Multiplexer.

Table 1 - IR Port Signals

NAME

SIZE (BITS)

TYPE

DESCRIPTION

IRRx

1

Input

Infrared Receive Data

IRTx

1

Output

Infrared Transmit Data

Table 2 - COM Port Signals

NAME

SIZE (BITS)

TYPE

DESCRIPTION

CRx

1

Input

COM Receive Data

CTx

1

Output

COM Transmit Data

nRTS

1

Output

Request to Send

nDTR

1

Output

Data Terminal Ready

nCTS

1

Input

Clear To Send

nDSR

1

Input

Data Set Ready

nDCD

1

Input

Data Carrier Detect

nRI

1

Input

Ring Indicator

Table 3 - AUX Port Signals

(E.g., can be used for high-current drivers for Consumer IR)

NAME

SIZE (BITS)

TYPE

DESCRIPTION

ARx

1

Input

Aux. Receive Data

ATx

1

Output

Aux. Transmit Data

5

Table 4 - G. P. Port Signals

NAME

SIZE (BITS)

TYPE

DESCRIPTION

Fast

1

Output

General Purpose Data

GP Data

1

Output

General Purpose Data

Fast

The Fast pin always reflects the state of Fast, bit

6 of SCE Line Control Register A. The state of

Fast is independent of the IrCC 2.0 Block

Controls or the Output Multiplexer. The Fast pin

can be used at the chip level for IR Transceiver

configuration.

GP Data

The G.P. Data pin typically reflects the state of

General Purpose Data, bit 5 of SCE Line Control

Register A. The state of G.P. Data is

independent of the IrCC 2.0 Block Controls or

the Output Multiplexer but will depend on the

ATC during transceiver programming cycles

(see the Automatic Transceiver Control section

on page 69).

Table 5 - HOST Signals

NAME

SIZE (BITS)

TYPE

DESCRIPTION

D0-D7

8

Bi-directional

Host Data Bus

A0-A2

3

Input

IrCC 2.0 Register Address Bus

nIOR

1

Input

ISA I/O Read

nIOW

1

Input

ISA I/O Write

AEN

1

Input

ISA Address Enable

DRQ

1

Output

DMA Request

nDACK

1

Input

ISA DMA Acknowledge

TC

1

Input

ISA DMA Terminal Count

IRQ

1

Output

Interrupt Request

IOCHRDY

1

Output

ISA I/O Channel Ready

nSRDY

1

Output

ISA Synchronous Ready (Zero Wait State)

6

Table 6 - SYSTEM Signals

NAME

SIZE (BITS)

TYPE

DESCRIPTION

CLK

1

Input

System Clock

RESET

1

Input

IrCC 2.0 System Reset

Power Down

1

Input

Low Power Control

DMAEN

1

Output

DRQ Tristate Control

IRQEN

1

Output

IRQ Tristate Control

nACE

1

Input

ACE 550 Register Bank Select

nSCE

1

Input

SCE Register Bank Select

VCC

Power

System Supply

GND

Power

System Ground

DMAEN

DMAEN is used by the chip-level interface to

tristate the IrCC 2.0 DRQ output when the DMA

Enable bit is inactive. The DMA Enable bit is

located in SCE Configuration Register B, bit 0.

IRQEN

IRQEN is used by the chip-level interface to

tristate the IrCC 2.0 IRQ output when the OUT2

bit is inactive. The OUT2 bit is located in

16C550A MODEM Control Register.

Power Down

The Power Down pin is used by the chip-level

interface to put the SCE into low power mode.

Note: Power Down only forces the SCE into low

power mode. The ACE power down function is

not a part of this specification.

CHIP-LEVEL CONFIGURATION CONTROLS

The following signals come from chip-level

configuration registers. There are two types of

Chip-Level Configuration Controls: IrCC 2.0 -

Specific controls, and Legacy Controls. Both

types have equivalent controls in either the IrCC

2.0 ACE or SCE Registers.

The IrCC 2.0-Specific controls have been newly

added primarily to support the IrCC 2.0 block.

Provisions have been made in new chip-level

configuration contexts to accommodate these

signals.

The Legacy controls already exist in other

contexts. Provisions have been made in legacy

devices to accommodate these controls from

either the Chip-Level Configuration Registers or

the IrCC 2.0 Registers; i.e., the last updated

value from either source determines the current

control state and is visible in both registers.

7

Table 7 - IrCC 2.0-Specific Chip-Level Controls

NAME

SIZE (BITS)

TYPE

DESCRIPTION

DMA Channel

4

Input

ISA DMA Channel Number

IRQ Level

4

Input

ISA Interrupt Level

Software Select A

8

Input

Software Programmable Register A

Software Select B

8

Input

Software Programmable Register B

DMA Channel

4 bit bus from a chip-level configuration register,

used to identify the current IrCC 2.0 DMA

channel number. The value appears in the

upper nibble of IrCC 2.0 Register Block Three,

Address Four.

IRQ Level

4 bit bus from a chip-level configuration register,

used to identify the current IrCC 2.0 IRQ level.

The value appears in the lower nibble of IrCC

2.0 Register Block Three, Address Four.

Software Select A/B

The 8 bit Software Select A and Software Select

B inputs come from software-only

programmable chip-level configuration controls.

The values on these buses appear in IrCC 2.0

Register Block Three, Addresses Five and Six.

8

Table 8 - Legacy Chip-Level Controls

NAME

SIZE (BITS)

TYPE

DESCRIPTION

Tx Polarity

1

Input

Output Mux. Transmit Polarity

Rx Polarity

1

Input

Output Mux. Receive Polarity

Half Duplex

1

Input

16C550A UART Half Duplex

Control

IR Half Duplex Timeout

8

Input

IR Transceiver Turnaround Time

IR Mode

3

Input

IR Mode Register Bits

IR Location

2

Input

IR Option Register Location Bits

Tx Polarity

Typically part of a 16C550A Serial Port Option

Register. The value also appears in IrCC 2.0

Register Block One, Address Zero.

Rx Polarity

Typically part of a 16C550A Serial Port Option

Register. The value also appears in IrCC 2.0

Register Block One, Address Zero.

Half Duplex

Typically part of a 16C550A Serial Port Option

Register. The value also appears in IrCC 2.0

Register Block One, Address Zero.

IR Half Duplex Timeout

Typically part of a 16C550A Serial Port 2

Configuration Register. The value also appears

in IrCC 2.0 Register Block One, Address Zero

(see the IR Half Duplex Timeout Register

(Address 1) on page 42).

IR Mode

Typically part of a 16C550A Serial Port Option

Register. These values are also part of the IrCC

2.0 Block Control bits 3-5, Register Block One,

Address Zero.

IR Location

Typically part of a 16C550A Serial Port IR

Option Register. These values are the IrCC 2.0

Output Mux bits, Register Block One, Address

One. Note:

These legacy controls are

uniformly updated in the IrCC 2.0 and the Top-

Level Device Configuration Registers only when

either set of registers is explicitly written using

IOW or following a device-level POR. IrCC 2.0

software resets will not affect the legacy bits.

9

OPERATION MODES

RAW IR

In Raw mode the state of the IR emitter and

detector can be directly accessed through the

host interface (Figure 3).

The IR emitter tracks the Raw Tx Control bit in

SCE Line Control Register A. For example,

depending on the state of the Tx Polarity control

a logic '1' may turn the LED on and a logic '0'

may turn the LED off. Care must be taken in

software to ensure that the LED is not on

continuously.

The Raw Rx Control bit in SCE Line Control

Register A represents the state of the PIN diode.

For example, depending on the state of the Rx

Polarity control a logic '1' may mean no IR is

detected, a logic '0' may mean IR is being

detected. If an IR carrier is present, the Raw Rx

Control bit will oscillate at the carrier frequency.

If enabled, a Raw Mode Interrupt will occur

when the Raw Rx Control bit transitions to the

active state, depending on the state of the Rx

Polarity control. Raw Mode is enabled with the

Block Control Bits in SCE Configuration

Register A (see page 32).

CONSUMER IR (REMOTE CONTROL)

The IrCC 2.0 Consumer IR (Remote Control)

block is a general-purpose programmable

Synchronous Amplitude Shift Keyed serial

communications interface that includes a Carrier

Frequency Divider, a Programmable Receive

Carrier Range Sensitivity Register, and Receive

and Transmit Modulators (Figure 4).

The Consumer IR block transfers data LSB first

between the SCE and Output Multiplexer without

framing as a fixed bit-cell serial NRZ data

stream. The components of this block can also

modulate and demodulate serial data at

programmable bit rates and carrier frequencies.

Variable length encoding and all packet framing

are handled by system software. Consequently,

many encoding methods, modulation

frequencies and bit rates can be supported,

including 38KHz PPM, PWM and RC-5 Remote

Control formats.

Register controls for this block can be found in

Register Block Two. They are the Consumer IR

Control Register, the Consumer IR Carrier Rate

Register, and the Consumer IR Bit Rate

Register.

RAW Tx

Registers

Transition

Detect

Enable

Interrupt

Encoder/Decoder

RAW Rx

FIGURE 3 - RAW IR BLOCK DIAGRAM

10

Consumer IR mode is enabled with the Block

Control Bits in SCE Configuration Register A

(see page 32).

Carrier Frequency Divider

The Carrier Frequency Divider register is used

to program the ASK carrier frequency for the

transmit modulator and receive detector (Figure

5). The divider is eight bits wide.

The input clock to the Carrier Frequency Divider

is 1.6MHz (48MHz

˜

30). The relationship

between the divider value (CFD) and the carrier

frequency (Fc) is as follows:

CFD = (1.6MHz/Fc) - 1

For example, program the Carrier Frequency

Divider register with 41 ('29'Hex) for a 38kHz TV

Remote: Fc = 38.095kHz. This is ~.25%

accuracy. Table 9 contains representative CFD

vs. Carrier Frequency relationships.

The Carrier Frequency range is 1.6MHz to

6.25kHz.

The carrier frequency encoder/decoder can be

defeated using the Carrier Off bit. When Carrier

Off is one, the transmitter outputs a non-

modulated SCE serial NRZ data stream at the

programmed bit rate; the receiver does not

attempt to demodulate a carrier from the

incoming serial data stream.

SCE

Transmit Bit-Rate

Divider

Carrier Frequency

Divider

Clock

Programmable

Receive Carrier

Sense

Receive Bit-Rate

Divider

TV Tx

Tx Enable

Range

Sync

Rx Enable

Encoder/Decoder

Carrier Off

TV Rx

FIGURE 4 - IrCC 2.0 CONSUMER IR (REMOTE CONTROL) BLOCK

11

Table 9 - Representative Carrier Frequencies

CFD

Fc (kHz)

CFD

Fc (kHz)

CFD

Fc (kHz)

CFD

Fc (kHz)

001

800.000

065

24.242

129

12.308

193

8.247

005

266.667

069

22.857

133

11.940

197

8.081

009

160.000

073

21.622

137

11.594

201

7.921

013

114.286

077

20.513

141

11.268

205

7.767

017

88.889

081

19.512

145

10.959

209

7.619

021

72.727

085

18.605

149

10.667

213

7.477

025

61.538

089

17.778

153

10.390

217

7.339

029

53.333

093

17.021

157

10.127

221

7.207

033

47.059

097

16.327

161

9.877

225

7.080

037

42.105

101

15.686

165

9.639

229

6.957

041

38.095

105

15.094

169

9.412

233

6.838

045

34.783

109

14.545

173

9.195

237

6.723

049

32.000

113

14.035

177

8.989

241

6.612

053

29.630

117

13.559

181

8.791

245

6.504

057

27.586

121

13.115

185

8.602

249

6.400

061

25.806

125

12.698

189

8.421

253

6.299

Bit Rate Divider

The Transmit and Receive Bit Rate Divider

register is used to extract a serial NRZ data

stream for the IrCC 2.0 SCE. The divider is eight

bits wide.

The input clock to the Bit Rate Divider is 100kHz

(Carrier Frequency Divider input clock

˜

16).

The relationship between the Bit Rate

Divider (BRD) and the Bit Rate (Fb) is as

follows:

BRD = (.1MHz/Fb) - 1

For example, program the Bit Rate Divider with

55 ('37'Hex) for a .562ms Remote Control bit

cell: Fb = 1.786kHz. This is ~.5% accuracy.

Table 10 contains representative BRD vs. Bit

Rate relationships. The Bit Rate range is

100kHz to 390.625Hz.

12

Table 10 - Representative Bit Rates

BRD

Fb (kHz)

BRD

Fb (kHz)

BRD

Fb (kHz)

BRD

Fb (kHz)

003

25.000

067

1.471

131

0.758

195

0.510

007

12.500

071

1.389

135

0.735

199

0.500

011

8.333

075

1.316

139

0.714

203

0.490

015

6.250

079

1.250

143

0.694

207

0.481

019

5.000

083

1.190

147

0.676

211

0.472

023

4.167

087

1.136

151

0.658

215

0.463

027

3.571

091

1.087

155

0.641

219

0.455

031

3.125

095

1.042

159

0.625

223

0.446

035

2.778

099

1.000

163

0.610

227

0.439

039

2.500

103

0.962

167

0.595

231

0.431

043

2.273

107

0.926

171

0.581

235

0.424

047

2.083

111

0.893

175

0.568

239

0.417

051

1.923

115

0.862

179

0.556

243

0.410

055

1.786

119

0.833

183

0.543

247

0.403

059

1.667

123

0.806

187

0.532

251

0.397

063

1.563

127

0.781

191

0.521

255

0.391

Receive Carrier Sense

The Programmable Receive Carrier Sense

register is used to program the Consumer IR

decoder to detect the presence of IR energy in

a wide-to-narrow range of carrier frequencies.

The register is two bits wide.

The range values are shown in Table 11.

Carriers that fall outside of the programmed

range "abort" the message; i.e., the Abort bit is

set, an EOM Interrupt is generated, and the

receiver is disabled. If the "Carrier Off" bit is

active, the Receive Carrier range sensitivity

function is disabled.

Table 11 - Receive Carrier Sense Range

D1

D0

RANGE

0

0

±

10%

0

1

±

20%

1

0

±

40%

1

1

Reserved

13

Receiver Bit Cell Synchronization

The Consumer IR Receiver demodulates

incoming ASK waveforms into NRZ data for the

SCE. The IrCC 2.0 uses the edges of the

demodulated incoming infrared data to indicate

changes in bit state.

For continuous periods of high or low data

without transitions, the IrCC 2.0 samples the

signal level in the center of each incoming bit

period. Using the Receiver Bit Cell

Synchronization mechanism, any transition

resets the timer that is used in the sampling

process to eliminate errors due to timing

differences between the receive decoder and the

incoming bit period (Figure 6).

Receiver synchronization can be disabled to

allow direct sampling of the demodulated

incoming infrared data stream at some preset

receive bit rate. This is useful in situations

where the speed of the receive data is not

strictly known. In such cases, the receive bit

rate is set as high as possible, the Receiver Bit

Cell Synchronization is disabled, and the system

software is used to measure the bit-cell period

from the oversampled data. The learned

parameters can then be used to switch to the

synchronized, fixed bit-cell mode to reduce

processing overhead in the host CPU for all

future transactions.

1

0

1

SCE Tx Data

TV Tx Output

Transmitter

TV Rx Input

SCE Rx Data

Driver

Receiver

1/Carrier

1/Bit Rate

No Light

Light

Light

No Light

Tx Polarity bit = 1 (default)

Rx Polarity bit = 0 (default)

FIGURE 5 - REMOTE CONTROL ASK ENCODE/DECODE

14

IrDA SIR AND SHARP ASK IR INTERFACE

This interface uses the ACE UART to provide a

two-way wireless communications port using

infrared as a transmission medium. Two

distinct implementations have been provided in

this block of the IrCC 2.0, IrDA SIR and Sharp

ASK IR.

IrDA SIR allows serial communication at baud

rates up to 115k Baud. Each word is sent

serially beginning with a zero value start bit.

Sending a single infrared pulse at the beginning

of the serial bit time signals a zero. Sending no

infrared pulse during the bit time signals a one.

Please refer to Figure 7 through Figure 10 for

the parameters of these pulses and the IrDA

waveform.

The SHARP ASK interface allows asynchronous

amplitude shift keyed serial communication at

baud rates up to 19.2k Baud. Each word is sent

serially beginning with a zero value start bit.

Sending a 500kHz waveform for the duration of

the serial bit time signals a zero.

Sending no transmission during the bit time

signals a one. Please refer to the AC timing for

the parameters of the ASKIR waveform.

If the Half Duplex option is chosen, there is a

time-out when the direction of the transmission

is changed. This time-out starts at the last bit

transferred during a transmission and blocks the

receiver input until the time-out expires. If the

transmit buffer is loaded with more data before

the time-out expires, the timer is restarted after

the new byte is transmitted. If data is loaded

into the transmit buffer while a character is

being received, the transmission will not start

until the time-out expires after the last receive

bit has been received. If the start bit of another

character is received during this time-out, the

timer is restarted after the new character is

received. The time-out is programmable up to a

maximum of 10ms through the IR Half-Duplex

Time-Out Configuration Register.

1

1

0

0

0

0

1

1

1

Sync

Sync

1

1

0

0

0

1

1

1

1

IR Rx Data

IR Rx Data

NRZ Rx Data

(SYNC)

NRZ Rx Data

(No SYNC)

1

2

3

4

5

6

7

8

9

10

Clock

1

2

3

4

5

6

7

8

9

10

11

Clock

0

FIGURE 6 - REMOTE CONTROL RECEIVER: SYNC VS. NO SYNC

15

PARAMETER

MIN

TYP

MAX

UNITS

t1

Pulse Width at 115kbaud

1.4

1.6

2.71

µ

s

t1

Pulse Width at 57.6kbaud

1.4

3.22

3.69

µ

s

t1

Pulse Width at 38.4kbaud

1.4

4.8

5.53

µ

s

t1

Pulse Width at 19.2kbaud

1.4

9.7

11.07

µ

s

t1

Pulse Width at 9.6kbaud

1.4

19.5

22.13

µ

s

t1

Pulse Width at 4.8kbaud

1.4

39

44.27

µ

s

t1

Pulse Width at 2.4kbaud

1.4

78

88.5

µ

s

t2

Bit Time at 115kbaud

8.68

µ

s

t2

Bit Time at 57.6kbaud

17.4

µ

s

t2

Bit Time at 38.4kbaud

26

µ

s

t2

Bit Time at 19.2kbaud

52

µ

s

t2

Bit Time at 9.6kbaud

104

µ

s

t2

Bit Time at 4.8kbaud

208

µ

s

t2

Bit Time at 2.4kbaud

416

µ

s

Notes:

1. IrDA @ 115k is HPSIR compatible. IrDA @ 2400 will allow compatibility with HP95LX and 48SX.

2. IRRX: RX Polarity = 1

nIRRX: RX Polarity = 0 (default)

t1

t2

t2

t1

0

1

0

1

0

0

1

1

0

1

1

DATA

IRRX

nIRRX

FIGURE 7 - IrDA SIR RECEIVE TIMING

16

PARAMETER

MIN

TYP

MAX

UNITS

t1

Pulse Width at 115kbaud

1.41

1.6

2.71

µ

s

t1

Pulse Width at 57.6kbaud

1.41

3.22

3.69

µ

s

t1

Pulse Width at 38.4kbaud

1.41

4.8

5.53

µ

s

t1

Pulse Width at 19.2kbaud

1.41

9.7

11.07

µ

s

t1

Pulse Width at 9.6kbaud

1.41

19.5

22.13

µ

s

t1

Pulse Width at 4.8kbaud

1.41

39

44.27

µ

s

t1

Pulse Width at 2.4kbaud

1.41

78

88.55

µ

s

t2

Bit Time at 115kbaud

8.68

µ

s

t2

Bit Time at 57.6kbaud

17.4

µ

s

t2

Bit Time at 38.4kbaud

26

µ

s

t2

Bit Time at 19.2kbaud

52

µ

s

t2

Bit Time at 9.6kbaud

104

µ

s

t2

Bit Time at 4.8kbaud

208

µ

s

t2

Bit Time at 2.4kbaud

416

µ

s

Notes:

1. Receive Pulse Detection Criteria: A received pulse is considered detected if the received pulse is

a minimum of 1.41

µ

s

2. IRTX: TX Polarity = 1 (default)

nIRTX: TX Polarity = 0

t1

t2

t2

t1

0

1

0

1

0

0

1

1

0

1

1

DATA

IRTX

nIRTX

FIGURE 8 - IrDA SIR TRANSMIT TIMING

17

PARAMETER

MIN

TYP

MAX

UNITS

t1

Modulated Output Bit Time

µ

s

t2

Off Bit Time

µ

s

t3

Modulated Output "On"

0.8

1

1.2

µ

s

t4

Modulated Output "Off"

0.8

1

1.2

µ

s

t5

Modulated Output "On"

0.8

1

1.2

µ

s

t6

Modulated Output "Off"

0.8

1

1.2

µ

s

Notes:

1. IRTX: TX Polarity = 1 (default)

nIRTX: TX Polarity = 0

MIRTX, nMIRTX are the modulated outputs.

t1

t2

t3

t4

t5

t6

0

1

0

1

0

0

1

1

0

1

1

DATA

IRTX

nIRTX

MIRTX

nMIRTX

FIGURE 9 - AMPLITUDE SHIFT KEYED IR TRANSMIT TIMING

18

PARAMETER

MIN

TYP

MAX

UNITS

t1

Modulated Output Bit Time

µ

s

t2

Off Bit Time

µ

s

t3

Modulated Output "On"

0.8

1

1.2

µ

s

t4

Modulated Output "Off"

0.8

1

1.2

µ

s

t5

Modulated Output "On"

0.8

1

1.2

µ

s

t6

Modulated Output "Off"

0.8

1

1.2

µ

s

Notes:

1. IRRX: RX Polarity = 1

nIRRX: RX Polarity = 0 (default)

MIRRX, nMIRRX are the modulated outputs.

t1

t2

t3

t4

t5

t6

0

1

0

1

0

0

1

1

0

1

1

DATA

IRRX

nIRRX

MIRTX

nMIRTX

FIGURE 10 - AMPLITUDE SHIFT KEYED IR RECEIVE TIMING

19

INFRARED DATA ASSOCIATION

The guidelines established by the Infrared Data

Association (IrDA) are intended to facilitate the

interconnection of computers and peripherals

using directed half-duplex serial infrared

communications. Relevant IrDA documents

include the Serial Infrared Physical Layer Link

Specification, Version 1.1, October 17, 1995,

the Serial Infrared Link Access Protocol (IrLAP),

Version 1.1, June 16, 1996, and the Serial

Infrared Link Management Protocol (IrLMP),

Version 1.1, January 23, 1996.

The Fast extensions (FIR) to the original IrDA

physical layer specification (SIR) appear as

alternate modulation/demodulation paths for

data from IrLAP bound for the IR medium and

are fundamentally transparent to IrLAP as it is

defined for SIR. IR hardware and software must

comply as a system with the entire family of

IrDA specifications, including the Physical Layer

Link Specifications, IrLAP, and IrLMP.

A block diagram of one end of an IrDA link that

includes the SIR and FIR physical

implementations is shown in Figure 11.

SIR Interaction Pulse

The SIR Interaction Pulse (SIP) is intended to

guarantee non-disruptive coexistence with SIR-

only systems, which might otherwise interfere

with Fast IR links.

A SIP is defined as a 1.6 microsecond

transmitter on pulse followed by 7.1

microseconds of off time (Figure 12). Once a

Fast connection has been established the

station must generate one SIP every 500ms.

1.152 Mbps

4 Mbps

SIR Encoder

SCE

IR

Transceiver

Module

IR Out

IR In

FIR Encoders

UART

SIP

ATC

GP DATA IRMODE

FIGURE 11 - IrCC 2.0 IrDA BLOCK DIAGRAM

20

The IrCC 2.0 configuration register SIP ENABLE

bit and a timer control the SIR Interaction Pulse.

The IrCC 2.0 transmits a SIR Interaction Pulse

every 500ms when the SIP enable is active, an

IrDA FIR mode has been selected, and the

transmitter or receiver is not otherwise engaged.

The timer that controls the SIP pulse is reset

whenever 1) the SIP enable is inactive, 2) an

active FIR frame is being transmitted or

received or, 3) during an active SIP pulse. The

timer is decrementing whenever the SIP enable

bit is active and the SIP pulse generator, the

transmitter, and the receiver are inactive. When

the timer reaches zero, the SIP pulse generator

is activated (Figure 13).

1.6us

8.7us

SIP

Active SIP

Time

FIGURE 12 - SIR INTERACTION PULSE

nActive Frame

SIP Enable

Reset SIP

Timer

SIP Timer

Countdown

Active SIP

Time

SIP Timer

Zero

FIGURE 13 - SIP CONTROL TIMING

21

BOF Counting

The IrCC 2.0 can account for system-dependent

limitations such as long interrupt latencies and

transceiver stabilization times by increasing the

number of STA flags at the beginning of every

HDLC frame (Figure 14).

The BOF COUNT register contains the number

additional start flags that are to be appended to

the standard BOF characters. Note: The BOF

COUNT extensions only apply to messages that

start from an idle line state; i.e., BOF counting

does not apply to brick walled messages.

Back-to-Back Frame Transmission

Back-to-back, or brick walled frames are

allowed with two or more flags, '7E'hex, in

between. If two consecutive frames are not

back-to-back, the gap between the last STO flag

of the first frame and the first STA field of the

second frame are separated by at least seven

bit times (abort sequence).

The IrDA FIR 1.152 Mbps and 0.576 Mbps

physical layer specification allows back-to-back

message packets with three flag characters,

which act as the closing flag of the first frame

and the opening flags of the brick, walled

packet. Additional flags can be added by

programming the Brick Wall Count register

(Figure 15). Note: The BOF COUNT extensions

do not apply to brick walled messages.

ADDR

8-bit Address

Field

STA

'01111110'

binary

DATA

8-bit Control field plus up to 2K - 3 bytes

Information Field

STA

'01111110'

binary

BOF COUNT register

Appends 0 - 4095 Flags to

Beginning of Frame

FIGURE 14 - EXTENDED BEGINNING-OF-FRAME

ADDR

8-bit Address

Field

STO

'01111110'

binary

FCS

CCITT 16-bit

CRC

DATA

8-bit Control field plus up to 2K - 3 bytes

Information Field

Brick Walled Frame

Previous

Frame

STA

'01111110'

binary

BW COUNT register

Inserts 0 - 4095 Flags between

Brick Walled Frames

STA

'01111110'

binary

FIGURE 15 - BRICK WALLED HDLC FRAMES

22

4PPM BOF Counting

The IrCC 2.0 can account for system-dependent

limitations such as long interrupt latencies and

transceiver stabilization times by increasing the

number of PA flags at the beginning of every

4PPM frame (Figure 16).

The BOF COUNT register contains the number

of additional PA bytes that are to be appended

to the standard 4PPM BOF characters. Note:

The BOF COUNT extensions only apply to

messages that start from an idle line state; i.e.,

BOF counting does not apply to brick walled

messages.

4PPM Back-to-Back Frame Transmission

Back-to-back, or brick walled frames are

allowed with 32 or more PA flag bytes between

the STO field of the first frame and the STA field

of the second frame. Additional flags can be

added by programming the Brick Wall Count

register. Note: The BOF COUNT extensions do

not apply to brick walled messages.

ADDR

8-bit Address

Field

DATA

8-bit Control field plus up to 2K - 3 bytes

Information Field

BOF COUNT register

Appends 0 - 4095 PA Bytes

to Beginning of Frame

...

PA (#16)

PA (#1)

STA

8-bit Start

Field

FIGURE 16 - 4PPM EXTENDED BOF

ADDR

8-bit Address

Field

16-byte

PA

Sequence

DATA

8-bit Control field plus up to

2K - 3 bytes Information Field

Brick Walled Frame

Previous

Frame

STA

BW COUNT register

Inserts 0 - 4095 PA Bytes

between Brick Walled Frames

STO

16-byte

PA

Sequence

FIGURE 17 - BRICK WALLED 4 MBPS FRAMES

23

REGISTERS

The IrCC 2.0 is partially enabled through binary

controls found in two 8-byte register banks. The

banks, the ACE550 UART Controls and the SCE

Controls, are selected with the nACE and nSCE

register-bank selector inputs found in the

Interface Description.

If nACE is zero, the three least significant bits of

the Host Address Bus decode the 16C550A

UART control registers. If nSCE is zero, the

SCE control bank is addressed. All of the IrCC

2.0 registers are 8 bits wide.

ACE UART CONTROLS

The table below (Table 12) lists the ACE UART

Control Registers. See the current SMSC

16C550A implementation for a complete

description.

Table 12 - 16C550A UART Addressing

DLAB

A2

A1

A0

DIRECTION

REGISTER NAME

0

0

0

0

Read

Receive Buffer

0

0

0

0

Write

Transmit Buffer

0

0

0

1

Read/Write

Interrupt Enable

X

0

1

0

Read

Interrupt Identification

X

0

1

0

Write

FIFO Control

X

0

1

1

Read/Write

Line Control

X

1

0

0

Read/Write

Modem Control

X

1

0

1

Read/Write

Line Status

X

1

1

0

Read/Write

Modem Status

X

1

1

1

Read/Write

Scratchpad

1

0

0

0

Read/Write

Divisor (LSB)

1

0

0

1

Read/Write

Divisor (MSB)

SCE CONTROLS

The IrCC 2.0 SCE Registers are arranged in 7-

byte blocks. Of the eight possible register

blocks, six are used in this implementation.

The Master Block Control Register controls

access to the register blocks. Table 13 lists all

of the SCE registers in all blocks.

Table 13 - SCE Register Addressing

BLOCK

ADDRESS

DIRECTION

REGISTER NAME

X

7

R/W

Master Block Control

0

0

R/W

Data Register

0

1

RO

Interrupt Identification

0

2

R/W

Interrupt Enable

0

3

RO

Line Status (read)

24

Table 13 - SCE Register Addressing

BLOCK

ADDRESS

DIRECTION

REGISTER NAME

0

3

WO

Line Status Address (write)

0

4

R/W

Line Control A

0

5

R/W

Line Control B

0

6

R/W

Bus Status

1

0

R/W

SCE Configuration A

1

1

R/W

SCE Configuration B

1

2

R/W

FIFO Threshold

1

3

RO

FIFO COUNT

1

4

R/W

Message Byte-Count (low)

1

5

R/W

Message Byte-Count (high)

1

6

R/W

SCE Configuration C

2

0

R/W

Consumer IR Control

2

1

R/W

Consumer IR Carrier Rate

2

2

R/W

Consumer IR Bit Rate

3

0

RO

SMSC ID (high)

3

1

RO

SMSC ID (low)

3

2

RO

CHIP ID

3

3

RO

VERSION Number

3

4

RO

IRQ Level

DMA Channel

3

5

RO

Software Select A

3

6

RO

Software Select B

4

0

R/W

IrDA Control

BOF Count (high)

4

1

R/W

BOF Count (low)

4

2

R/W

Brick Wall Count (low)

4

3

R/W

BW Count (high)

Tx Data Size (high)

4

4

R/W

Tx Data Size (low)

4

5

R/W

Rx Data Size (high)

4

6

R/W

Rx Data Size (low)

5

0

R/W

ATC Register

5

1

R/W

IR Half Duplex Timeout

5

2

R/W

SCE Transmit Delay Timer

25

MASTER BLOCK CONTROL REGISTER

The Master Block Control Register contains the

IrCC 2.0 Power Down bit, two reset bits, the

Master Interrupt Enable bit, and the Register

Block Select lines (Table 14).

Address 7 is solely reserved for the Master

Block Control register. If the nSCE input is 0,

the MBC is always visible, regardless of the

state of the Register Block Select lines.

Table 14 - SCE Master Block Control Register

ADDRESS

DIRECTION

DESCRIPTION

DEFAULT

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

1

1

1

R/W

Master Block Control Register

'00'hex

power

down

master

reset

master

int en.

error

reset

register block

select

Register Block Select, bits 0-2

The Register Block Select bits enable access to

each of the eight possible register blocks. To

access a register block other than the default

(0), write a 3 bit register block number to the

least significant bits of the Master Block Control

Register. All subsequent reads and writes to

addresses 0 through 6 will access the registers

in the new block. To return to register block 0,

rewrite zeros to the register block select bits.

Error Reset, bit 4

Writing a one to the Error Reset bit will return all

of the SCE Line Status Register bits (Register

Block Zero) to their inactive states and reset the

Message Count bits, the Memory Count bits,

and the Message Byte Count registers to zero.

Master Interrupt Enable, bit 5

Setting the Master Interrupt Enable to one

enable the SCE interrupts onto the Interrupt

Request bus (IRQ) only if their individual

enables are active. Setting this bit to a zero

disables all SCE interrupts regardless of the

state of their individual enables.

Master Reset, bit 6

Setting the Master Reset bit to one forces data

in the SCE registers and SCE logical blocks into

the Power-On-Reset state. The Master Reset

bit is reset to zero following the reset operation.

Note: The Legacy bits (Register Block One,

Address Zero, Bits D0-D6) and the IR Half

Duplex Timeout are unaffected by Master Reset.

Power Down, bit 7

Setting this bit to a one causes only the SCE to

enter the low-power state. Power down mode

does not preclude access to the Master Block

Control register so that this mode can be

maintained entirely under software control. The

SCE can also be powered-down by the Power

Down input described in the Interface

Description.

26

REGISTER BLOCK ZERO

Register Block Zero contains the SCE Data

Register, the Interrupt Control/Status registers,

the Line Control/Status registers, and the Bus

Status register (Table 15). Typically, the

controls in Register Block Zero are used during

IrDA FIR and Consumer IR message

transactions. Bits and registers marked

"reserved" in the table below cannot be written

and return 0s when read. Programmers must

set reserved bits to 0 when writing to registers

that contain reserved bits.

Table 15 - Register Block Zero

ADDRESS

DIRECTION

DESCRIPTION

DEFAULT

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

0

0

0

R/W

Data Register

0

0

1

RO

Interrupt Identification Register

`00'hex

active

frame

eom

raw

mode

fifo

IR

busy

reserved

0

1

0

R/W

Interrupt Enable Register

'00'hex

active

frame

eom

raw

mode

fifo

IR

busy

reserved

0

1

1

RO

Line Status Register (read)

'00'hex

under-

run

over-

run

frame

error

size

error

crc

error

frame

abort

reserved

0

1

1

WO

Line Status Address Register (write)

reserved

status register

address

1

0

0

R/W

Line Control Register A

'00'hex

fifo

reset

fast

g. p.

data

raw

tx

raw

rx

abort

data

done

rsrvd

1

0

1

R/W

Line Control Register B

'00'hex

sce modes

bits

sip

enable

brick

wall

message

count

1

1

0

RO

Bus Status Register

'00'hex

not

empty

fifo

full

time-

out

memory count

valid

frame

Data Register (Address 0)

The Data Register is the FIFO access port.

Typically, the user will only write to the FIFO

when transmitting and read from the FIFO when

receiving. The host always has read access to

the FIFO regardless of the state of the SCE

Modes bits or the Loopback bit. Host read

access to the FIFO is blocked when the FIFO is

empty. The host has write access to the FIFO

only when the Loopback bit is inactive and the

SCE Modes bits are zero or Transmit mode is

enabled. Host write access to the FIFO is

blocked when the FIFO is full.

Interrupt Identification Register (Address 1)

When an interrupt is active the associated

interrupt identifier bit in the IID register is also

active regardless of the state of its individual

interrupt enable or the Master Interrupt Enable,

except for the FIFO Interrupt. The Master

Interrupt Enable and the individual Interrupt

Enables serve only to enable the IID register

interrupts onto the Interrupt Request bus IRQ

shown in the Interface Description.

27

Active Frame Interrupt, bit 7

When this bit is one, an Active Frame has

occurred (see the Active Frame Indicator section

on page 59). The Active Frame interrupt

typically indicates that the SCE receiver has

detected a valid incoming IrDA FIR or Remote

Control start-of-frame sequence. Reading the

Interrupt Identification register resets the Active

Frame Interrupt bit.

EOM Interrupt, bit 6

When this bit is one, an End of Message has

occurred. The EOM Interrupt indicates the end

of an IrDA FIR EOF or Abort. During Consumer

IR messages EOM Interrupt indicates FIFO

underruns/overruns and DMA Terminal Counts.

Reading the Interrupt Identification register

resets the EOM Interrupt bit.

Raw Mode Interrupt, bit 5

When this bit is one, a Raw Mode interrupt has

occurred. The Raw Mode Interrupt indicates

that the Raw Rx Control bit has gone active.

Reading the Interrupt Identification register

resets the Raw Mode Interrupt bit.

FIFO Interrupt, bit 4

When this bit is one, a FIFO Interrupt has

occurred. The FIFO Interrupt indicates that the

FIFO Interrupt Enable is active and either a

TxServReq or a RxServReq has occurred. The

FIFO Interrupt bit is cleared when the interrupt is

disabled; i.e., reading the Interrupt Identification

register does not reset the FIFO Interrupt bit

(see the FIFO Interrupt section on page 72).

IR Busy, bit 3

The IR Media Busy hardware sets the IR Busy

bit in the IID high if an infrared pulse that is

greater than T

PW_MIN

has occurred at the

receiver input, except during message transmit

or during the IR Half Duplex Timeout following

message transmit.

T

PW_MIN

can be defined as 20ns

#

T

PW_MIN

#

30ns

The IR Media Busy hardware operates

independently of the IR Rx Pulse Rejection

filters, the programmed receive data rate, or the

state of the ACE or SCE Rx Enables (see Figure

51). Reading the IID register will reset the IR

Busy bit. The IR Busy bit is also reset following

Master Reset and POR. If the IR Busy Enable

bit is high, the IR Busy Interrupt is enabled onto

the Interrupt Request bus IRQ if the master

Interrupt Enable is also active. The IR Busy

Enable bit does not affect the IR Busy bit in the

IID. PROGRAMMER'S NOTE: The IR Busy bit

may be unintentionally activated during IR Mode

changes.

Interrupt Enable Register (Address 2)

Setting any of the bits in this register to one

enables the associated interrupt (see the

Interrupt Identification Register). Interrupts will

only occur if both the interrupt enable bit and the

Master Interrupt Enable bit (see the Master

Block Control Register) are active.

The interrupt enables do not affect the state of

the interrupts, except for the FIFO Interrupt. For

example, a Raw Mode interrupt that occurs

while the Raw Mode Interrupt Enable is inactive

will be visible in the IID register but will not

affect IRQ.

Line Status Register(s) (Address 3)

Error Indicators (read-only)

There are eight Line Status Registers at address

3. Each register is read-only and is accessed

using the three Status Register Address bits,

also located at this address. The FIFO

Underrun, FIFO Overrun, Frame Error, Size

Error, Frame Abort, and CRC Error flags

indicate the status of any one of eight IrDA FIR

message frames. The Error Indicators, in all

registers, are reset following a Master Reset,

Power-On-Reset, and Error Reset (see the

Master Block Control Register). The error

indicators for the current status register only

(see the Message Count bits) are reset following

a valid IrDA BOF sequence.

FIFO Underrun, bit 7

The FIFO Underrun bit gets set to one when the

IrDA FIR transmitter runs out of FIFO data and

the Data Done bit is not active.

28

FIFO Overrun, bit 6

The FIFO Overrun bit gets set to one when the

IrDA FIR receiver tries to write data to the FIFO

when the FIFO Full flag is active.

Frame Error, bit 5

The Frame Error bit gets set to one when IrDA

framing errors are detected; for example, HDLC

pulse-widths greater than one bit-cell, and

invalid framing fields (see the Framing Errors

section on page 65).

Size Error, bit 4

The Size Error bit is set to one whenever the

IrDA FIR receiver decrements the Rx Data Size

count to zero before the End-Of-Frame, or

whenever the the Brick Wall bit is inactive and

the IrDA FIR transmitter decrements the Tx Data

Size count to zero before FIFO Empty goes

active.

CRC Error, bit 3

The CRC Error bit is set to one following Frame-

Check-Sequence errors in IrDA FIR receive

message frames.

Frame Abort, bit 2

The Frame Abort bit is set to one following; 1) a

forced abort, i.e. after setting the Abort bit to

one in Line Control Register A; 2) an IrDA FIR

FIFO underrun with the Data Done bit inactive

during transmit; 3) an IrDA FIR FIFO Overrun

during receive; 4) framing errors in IrDA FIR

payload data during receive. NOTE: The Frame

Abort bit will not go active during transmit if the

Tx Data Size register decrements to zero when

the last byte is read from the FIFO with the Data

Done bit not set.

Status Register Address, bits 0 - 2 (write-

only)

Three Status Register Address bits control

software access to, and reside at the same

address as, the Line Status Registers. The

Status Register Address bits are write-only and

occupy bits D0 to D2. To access any one of the

eight Line Status Registers or the Message Byte

Counters (SCE Register Block One, addresses 4

and 5), first write the address of the appropriate

register (0 - 7), then read the register contents.

Line Control Register A (Address 4)

FIFO Reset, bit 7

When set to one, the FIFO Reset bit clears the

FIFO Full and Not Empty flags in the 128-byte

SCE FIFO. The FIFO Reset bit is automatically

set to zero following the re-initialization.

Fast, bit 6

The Fast bit controls the state of an

uncommitted IrCC 2.0 output, Fast. The bit is

read/write.

General Purpose Data, bit 5

The General Purpose Data bit controls the state

of an uncommitted IrCC 2.0 output, GP Data.

The bit is read/write.

Raw Tx, bit 4

The Raw Tx bit controls the state of the infrared

emitter in Raw IR mode. The bit is read/write.

Raw Rx, bit 3

The Raw Rx bit represents the state of the

infrared detector in Raw IR mode. The bit is

read-only.

29

Abort, bit 2

The Abort bit is used to cancel messages in

progress. When the Abort bit is set to one, an

IrDA Abort sequence is sent, the EOM flag is

activated, and the SCE FIFO is cleared. The

Abort bit is reset to zero following EOM. Abort

can be used during IrDA FIR transmit mode

only.

Data Done, bit 1

When set to one, the Data Done bit is used

during transmit to distinguish an end-of-valid-

message-data condition from a FIFO Underrun

that indicates incomplete message data.

Terminal Count automatically activates the Data

Done bit during DMA operations. Note:

The Data Done bit is not activated by TC during

receive operations. Data Done is automatically

reset to zero following the end of a message

only if the FIFO is empty.

Line Control Register B (Address 5)

SCE Modes, bits 6 - 7

The SCE Modes bits enable the SCE transmitter

and receiver (Table 16). These bits are R/W

and must be manually reset by the host

following IrDA message transactions. The SCE

Modes bits are automatically reset by the

hardware following Consumer IR messages.

Note: the SCE Modes bits must be zero for

loopback tests.

Table 16 - SCE Modes

D7

D6

MODE DESCRIPTION

0

0

Receive/Transmit Disabled (default)

0

1

Transmit Mode

1

0

Receive Mode

1

1

Undefined

Transmit Mode

Transmit mode enables the SCE IrDA FIR and

Consumer IR transmitters whenever TC goes

active, or the FIFO THRESHOLD has been

exceeded (see the Transmit Timing section on

page 61). In Transmit mode, the SCE FIFO

input is connected to the Host System Data Bus

and the FIFO output is connected to the SCE

transmitter input. Transmit mode is strictly

software controlled when the IrDA FIR encoders

are active. The Consumer IR encoder will reset

Transmit mode in hardware following the rising

edge of nActive Frame following a FIFO

underrun.

Receive Mode

Receive mode enables the SCE IrDA FIR and

Consumer IR receivers (see the Receive Timing

section on page 66). In Receive mode, the SCE

FIFO output is connected to the Host System

Data Bus, the FIFO input is connected to the

SCE receiver output. Receive mode is strictly

software controlled when the IrDA FIR encoders

are active. The Consumer IR encoder will reset

Receive mode in hardware following the rising

edge of nActive Frame following a FIFO

underrun or TC.

SIP Enable, bit 5

If the SIP Enable is one, an SIR Interaction

Pulse occurs every 500ms if an IrDA FIR mode

has been selected and the transmitter or

receiver is not otherwise engaged (see the SIR

Interaction Pulse section on page 19).

Brick Wall, bit 4

When the Brick Wall bit is active the IrCC 2.0

sends back-to-back IrDA FIR frames separated

by the number of additional flags specified in the

brick wall count register (see the Multi-Frame

Window Support section on page 67). The Data

Size register or the Message Byte Counters can

be used when the Brick Wall bit is active to send

back-to-back IrDA FIR frames when the DMA

30

data block is larger than the IrDA message

length. In this case, if the maximum number of

data bytes according to the Tx Data Size

register or a Message Byte Counter have been

transferred and the DMA terminal count or the

FIFO Empty flags have not been activated the

next message is brick walled to the previous

message (Table 17). The Brick Wall bit is

software controlled only. Note: BOF counts do

not apply during brick walled messages.

Table 17 - Message Flow Control

BRICK

WALL

ENABLE

DATA

DONE

BIT

FIFO

EMPTY

STATE

AFTER

EOF

DESCRIPTION

1

1

0

BOF

Brick Wall Next Message

1

1

1

Idle

Multi-Frame Window Complete, Reset Data Done bit

1

0

0

BOF

Brick Wall Next Message

1

0

1

BOF

Brick Wall Next Message (possible underrun)

0

1

0

Idle

Re-enable Transmitter for Next Message

0

1

1

Idle

Single Message Complete, Reset Data Done bit

0

0

0

Idle

Single Message Complete, Datasize Counter = 0

0

0

1

Idle

Single Message Complete, Datasize Counter = 0

Message Count, bits 0 - 3

The four Message Count bits control (internal)

hardware access to the Line Status Registers

and are unaffected by the Status Register

Address bits (see the Multi-Frame Window

Support section on page 67). The Message

Count bits also indicate the system message-

state. For example, if the Message Count bits

are zero, i.e. the power-up default, Line Status

Register zero is active, although undefined

because no messages have been sent or

received. The Message Count bits are

incremented after every active frame. At point A

in Figure 18, for example, the rising edge of

nActive Frame increments Message Count by

one indicating that the first message has been

received. This means that Line Status Register

#1 (status register address 0) is valid, and Line

Status Register #2 is currently active, although

undefined. Hardware prevents the Message

Count register from exceeding eight

('1000'Binary). Note: IrDA messages beyond

eight frames are ignored.

31

Bus Status Register (Address 6)

FIFO Indicators (read-only)

The FIFO Indicators reflect the current status of

the SCE FIFO.

FIFO Not Empty, bit 7

The FIFO Not Empty bit when set to one

indicates that there is data in the SCE FIFO.

FIFO Full, bit 6

The FIFO Full bit when set to one indicates that

there is no room for data in the SCE FIFO.

Time-Out, bit 5

The Time-Out bit is the IOCHRDY time-out error

bit. The Time-Out bit when set to one indicates

that an IOCHRDY time-out error has occurred

(see the IOCHRDY Time-Out section on page

79). Time-Out is reset by the IrCC 2.0 System

Reset, following a read of the Bus Status

register, and following a Master Reset.

Memory Count, bits 1-4

Memory Count indicates the status of received

IrDA messages in memory. Memory Count is

incremented whenever the first byte of a

message is read from the SCE FIFO. For

example, if Memory Count=3, there are currently

two complete messages in memory. Legal

Memory counts are 0-8; i.e., there can be a

maximum of eight contiguous received IrDA

messages. Memory Count is only valid during

receive. Memory Count is reset to zero during

POR, Master Reset, and Error Reset (see the

Master Block Control register). Note: Memory

Count is closely related to the Message Count in

SCE Line Control Register B. Memory Count

will typically fall behind the Message Count

depending on the size of the received messages

and the speed of the host bus interface.

Valid Frame, bit 0

The Valid Frame bit reflects the state of the

internal state variable nActive Frame. When

nActive Frame=0 (active) Valid Frame=1

(active). When nActive Frame=1 (inactive)

Valid Frame=0 (inactive). Valid Frame is only

defined for the SCE IrDA FIR and Consumer IR

Encoder/Decoders during Transmit and

Receive.

nActive Frame

Message Count (0000)

0001

A

0010

0011

FIGURE 18 - MESSAGE COUNT EXAMPLE

32

REGISTER BLOCK ONE

Register Block One contains the SCE control

registers (Table 18). Typically, the controls in

Register Block One are needed to configure the

SCE before message transactions can occur.

Bits and registers marked "reserved" in the table

below cannot be written and return 0s when

read. Programmers must set reserved bits to 0

(zero) when writing to registers that contain

reserved bits.

Table 18 - Register Block One

Address

Direction

Description

Default

A2

A1

A0

D7

D6

D5

D4

D3

D2

D1

D0

0

0

0

R/W

SCE Configuration Register A

'02'hex

aux

ir

block control

bits

half

duplx

tx po-

larity

rx po-

larity

0

0

1

R/W

SCE Configuration Register B

'00'hex

output mux

bits

loop-

back

lpbck

tx crc

no

wait

string

move

dma

burst

dma

enable

0

1

0

R/W

FIFO Threshold Register

'00'hex

0

1

1

RO

FIFO COUNT

'00'hex

FC7

FC6

FC5

FC4

FC3

FC3

FC1

FC0

1

0

0

R/W

Message Byte-Count (low byte)

'00'hex

MBC

7

MBC

6

MBC

5

MBC

4

MBC

3

MBC

2

MBC

1

MBC

0

1

0

1

R/W

Message Byte-Count (high byte)

'00'hex

reserved

MBC

11

MBC

10

MBC

9

MBC

8

1

1

0

R/W

SCE Configuration Register C

'03'hex

MFW

tx pw

limit

rx pw

reject

reserved

DMA Refresh

Count

SCE Configuration Register A (Address 0)

Auxiliary IR, bit 7

When the Auxiliary IR bit is one and the active

device is routed through the Output Multiplexer

to the IR Port or the COM Port, the transmit

signal also appears at the Auxiliary Port.

Block Control, bits 3 - 6

The Block Control bits select one of the eight

IrCC 2.0 operational modes (Table 19). The

three low-order Block Control bits are equivalent

to the IR Mode bits in the chip-level

configuration space of earlier devices; e.g., the

FDC37C93x IR Option Register, Serial Port 2,

Logical Device 5, Register 0xF1. Provisions

have been made in legacy devices to

accommodate IR Mode selection through either

the chip-level configuration registers or the IrCC

2.0 Block Control bits; i.e., the last write from

either source determines the current mode

selection and is visible in both registers.

33

Table 19 - IrCC 2.0 Logical Block Controls

D6

D5

D4

D3

MODE

DESCRIPTION

0

0

0

0

COM

16C550A UART COM Port (default)

0

0

0

1

IrDA SIR - A

Up to 115.2 Kbps, Variable 3/16 Pulse

0

0

1

0

ASK IR

Amplitude Shift Keyed Ir Interface

0

0

1

1

IrDA SIR - B

Up to 115.2 Kbps, Fixed 1.6

F

s Pulse

0

1

0

0

IrDA HDLC

Includes 0.576 Mbps & 1.152 Mbps

0

1

0

1

IrDA4PPM

Includes 4 Mbps

0

1

1

0

CONSUMER

TV Remote

0

1

1

1

RAW IR

Direct IR Diode Control

1

X

X

X

OTHER

Reserved

Half Duplex, bit 2

When Half Duplex is zero (default), the

16C550A is in full duplex mode. The Half Duplex

bit only supports the 16C550A UART; i.e., this

bit has no effect on the IrCC 2.0 SCE. The Half

Duplex bit is analogous to the chip-level

configuration register Half Duplex bit and has

the same effect on the UART. Provisions have

been made in legacy devices to accommodate

Half Duplex selection through either the chip-

level configuration registers or the IrCC 2.0 Half

Duplex bit; i.e., the last write from either source

determines the current mode selection and is

visible in both registers.

Tx/Rx Polarity Bits, 0 - 1

The Tx and Rx Polarity bits define the active

states for signals entering and exiting the Output

Multiplexer ports. Internal IrCC 2.0 Active states

are typically decoded as zero. The Tx Polarity

bit default is one; the Rx Polarity bit default is

zero.

For backward compatibility, the Tx and Rx

Polarity bits do not apply to COM mode; i.e.,

when the Block Control bits are zero. The

relationship between the Output Multiplexer port

signals and the Polarity bits is an exclusive-or

(Table 20). For example, if the IRRx pin in the

Output Multiplexer is one and the Rx Polarity bit

is zero, the signal is inactive and therefore

decoded as a one. The IrCC 2.0 Tx Polarity bit

(bit 1) is equivalent to the Transmit Polarity bit

in the chip-level configuration space of earlier

devices; e.g., the FDC37C93x IR Option

Register, Serial Port 2, Logical Device 5,

Register 0xF1. The Rx Polarity bit (bit 0) is

equivalent to the Receive Polarity bit in the

same register. Provisions have been made in

legacy devices to accommodate Polarity bit

selection through either the chip-level

configuration registers or the SCE registers; i.e.,

the last write from either source determines the

current Polarity bit value and is visible in both

registers.

Table 20 - Tx/Rx Polarity Bit Effects

SIGNAL

POLARITY BIT

DECODED SIGNAL

0

0

0

0

1

1

1

0

1

1

1

0

34

SCE Configuration Register B (Address 1)

Output Mux, bits 7 - 6

The Output Mux bits select the Output

Multiplexer port for the active encoder/decoder

(Table 21). When D[7:6]=1,1 in Table 21

inactive outputs depend on the state of the Tx

Polarity bit, otherwise inactive outputs are zero.

The Output Mux bits are equivalent to the

FDC37C93x IR Option Register bits 6-7. The IR

Location Mux, bit 6, in the FDC37C93x IR

Option Register is equivalent to Output Mux bit,

D6; bit 7 (Reserved) in the FDC37C93x IR

Option Register is equivalent to Output Mux bit,

D7. Provisions have been made in legacy

devices to accommodate Output Multiplexer port

selection through either the chip-level

configuration registers or the Output Mux bits;

i.e., the last write from either source determines

the current port selection and is visible in both

registers.

Table 21 - IrCC 2.0 Output Multiplexer

D7

D6

MUX. MODE

0

0

Active Device to COM Port (default)

0

1

Active Device to IR Port

1

0

Active Device to AUX Port

1

1

Outputs Inactive

Loopback, bit 5

The Loopback bit configures the FIFO and

enables the transmitter/receiver for loopback

testing (see the Loopback Mode section on page

68). The SCE MODES bits must be set to zero

before activating the Loopback bit. When the

Loopback bit is one, the SCE enters a full-

duplex mode with internal loopback capability

for testing. The CRC generator can be

selectively reconfigured for either transmit or

receive. The 128-byte FIFO input is connected

to the SCE receiver output, the FIFO output is

connected to the SCE transmit input. For IrDA

FIR loopback tests the Loopback bit must be set

to zero to exit loopback mode. Consumer IR

loopback tests reset the Loopback bit

automatically when the Rx Data Size register

reaches zero. Provisions must be made

following loopback tests in all modes to verify

the Rx message data in the FIFO.

Loopback Transmit CRC, bit 4

When the Loopback Transmit CRC bit is set to

one, the CRC generator is used by the

transmitter during loopback testing regardless of

the state of the CRC Select bit. Otherwise, the

CRC generator is connected to the receiver

(Table 22).

Table 22 - Hardware CRC Programming

LOOPBACK

BIT

CRC

SELECT

LOOPBACK TX

CRC BIT

HARDWARE DESCRIPTION

0

0

X

No CRC Generation, No CRC Checking

0

1

X

CRC Generation, CRC Checking

1

0

0

No CRC Generation, No CRC Checking

1

0

1

CRC Generation, No CRC Checking

1

1

0

CRC Checking, No CRC Generation

1

1

1

CRC Generation, No CRC Checking

35

No Wait, bit 3

When the No Wait bit is one, the ISA Bus

nSRDY signal goes active following the trailing

edge of the ISA I/O command and inactive

following the rising edge (see the Zero Wait

State Support section on page 80).

String Move, Bit 2

When the String Move bit is one, the

programmed I/O host interface is qualified by

IOCHRDY (Table 23). See the IOCHRDY Time-

Out section on page 79.

DMA Burst Mode, bit 1

When the DMA Burst Mode bit is one, DMA

Burst (Demand) mode is enabled. When the

DMA Burst Mode bit is zero, Single Byte DMA

mode is enabled (Table 23). See the DMA

section on page 73.

DMA Enable, bit 0

DMA Enable is connected to a signal in the

Interface Description called DMAEN that is used

by the chip-level interface to tristate the IrCC 2.0

DMA controls when the DMA interface is

inactive. When the DMA Enable bit is one, the

DMA host interface is active (Table 23). See the

DMA section on page 73. When the DMA

Enable bit is zero (default), the nDACK and TC

inputs are disabled and DRQ output is gated off.

Table 23 - I/O Interface Modes

STRING

MOVE

DMA

BURST

DMA

ENABLE

FUNCTION

0

X

0

Programmed I/O, no IOCHRDY

1

X

0

Programmed I/O, uses IOCHRDY

X

0

1

Single Byte DMA Mode

X

1

1

Demand Mode DMA

FIFO Threshold Register (Address 2)

The FIFO Threshold Register contains the

programmable FIFO threshold count (see the

FIFO Threshold section on page 72). The FIFO

Threshold is programmable from 0 to 127. Bit 7

in the FIFO Threshold register is read-only and

will always return zero. FIFO Threshold values