| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXA1166 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

≠ 1 ≠

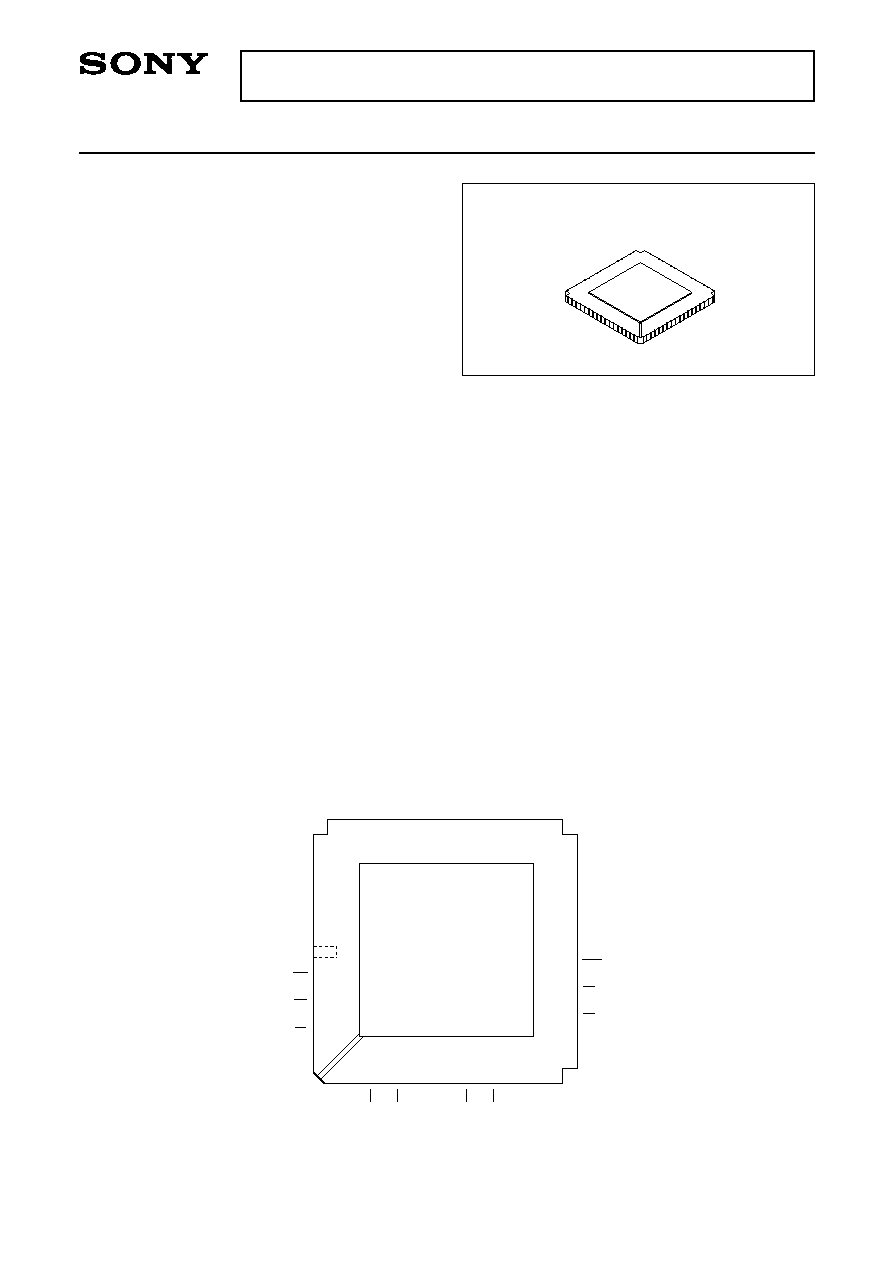

CXA1166K

E90406-ST

8-bit 250 MSPS Flash A/D Converter

Description

The CXA1166K is an 8-bit ultrahigh-speed flash

A/D converter IC capable of digitizing analog signals

at a maximum rate of 250 MSPS. The digital I/O

level of this A/D converter is compatible with the

ECL 100K/10KH/10K.

This IC is pin-compatible with the conventional

CXA1076AK/CXA1176K/CXA1176AK, and can

replace the conventional models easily. Compared

with the conventional models, the CXA1166K has a

greatly improved performance because of the new

circuit design and carefully considered layout.

Features

∑ Differential linearity error: ±0.5 LSB or less

∑ Integral linearity error: ±0.5 LSB or less

∑ Built-in integral linearity compensation circuit

∑ Ultrahigh-speed operation with maximum conver-

sion rate of 250 MSPS

∑ Low input capacitance: 18pF

∑ Wide analog input bandwidth: 250MHz (full-scale

input, standard)

∑ Single power supply: ≠5.2V

∑ Low power consumption: 1.4W (Typ.)

∑ Low error rate

∑ Good temperature characteristics

∑ Capable of driving 50

loads

Structure

Bipolar silicon monolithic IC

Applications

∑ Digital oscilloscopes

∑ Other apparatus requiring ultrahigh-speed A/D

conversion

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

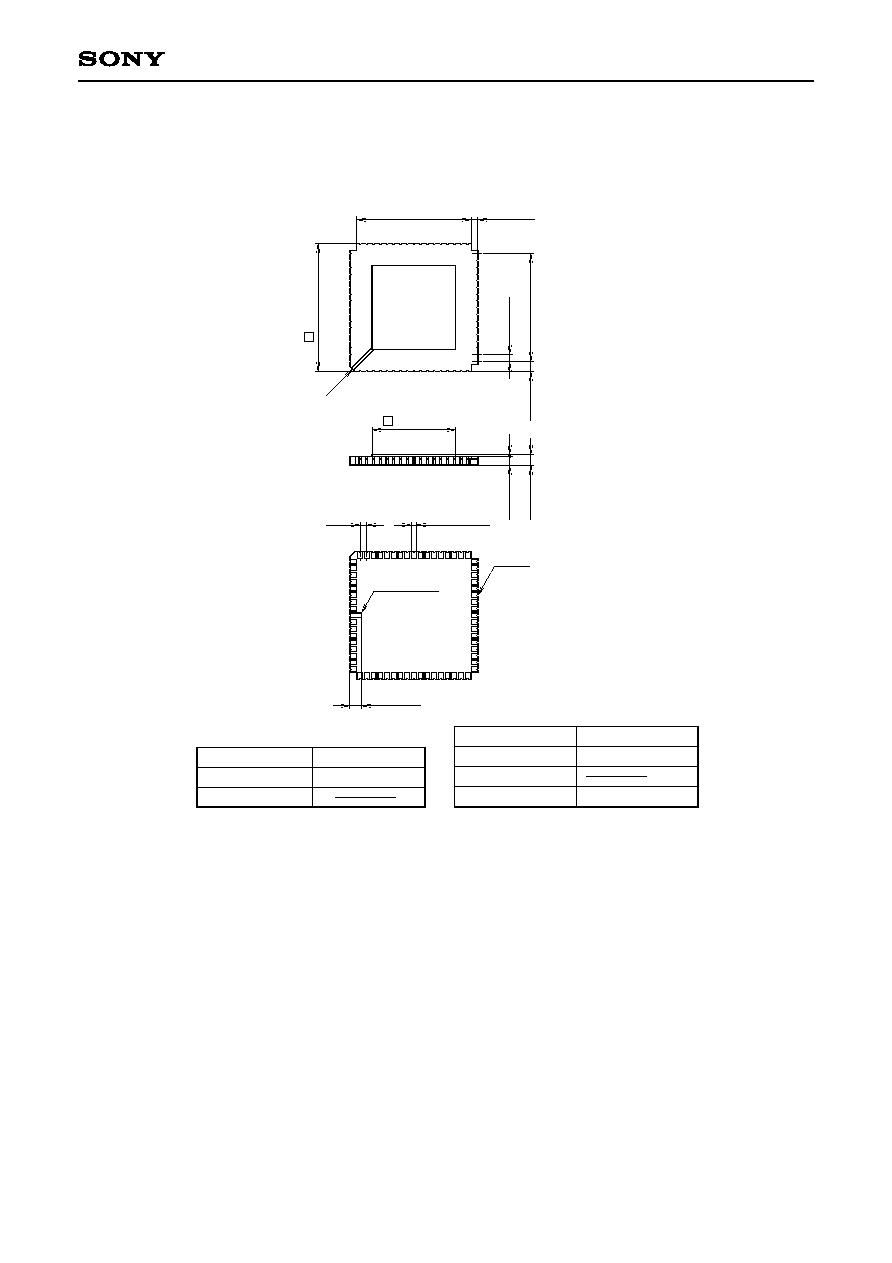

68 pin LCC (Ceramic)

61

62

63

64

65

66

67

68

1

2

3

4

5

6

7

8

9

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

AV

EE

AGND

V

IN1

V

IN1

AGND

V

RM

AGND

V

IN2

V

IN2

AGND

D2

D2

D3

D3

DGND2

DGND2

DGND1

D4

D4

D5

D5

AGND

AV

EE

V

RB

V

RBS

AV

EE

AV

EE

CLK

CLK

MINV

D7

D7

D6

D6

DV

EE

AGND

AV

EE

V

RT

V

RTS

AV

EE

AV

EE

LINV

OR

OR

D0

D0

D1

D1

DV

EE

Pin Configuration (Top View)

Pins without name are NC pins (not connected internally).

≠ 2 ≠

CXA1166K

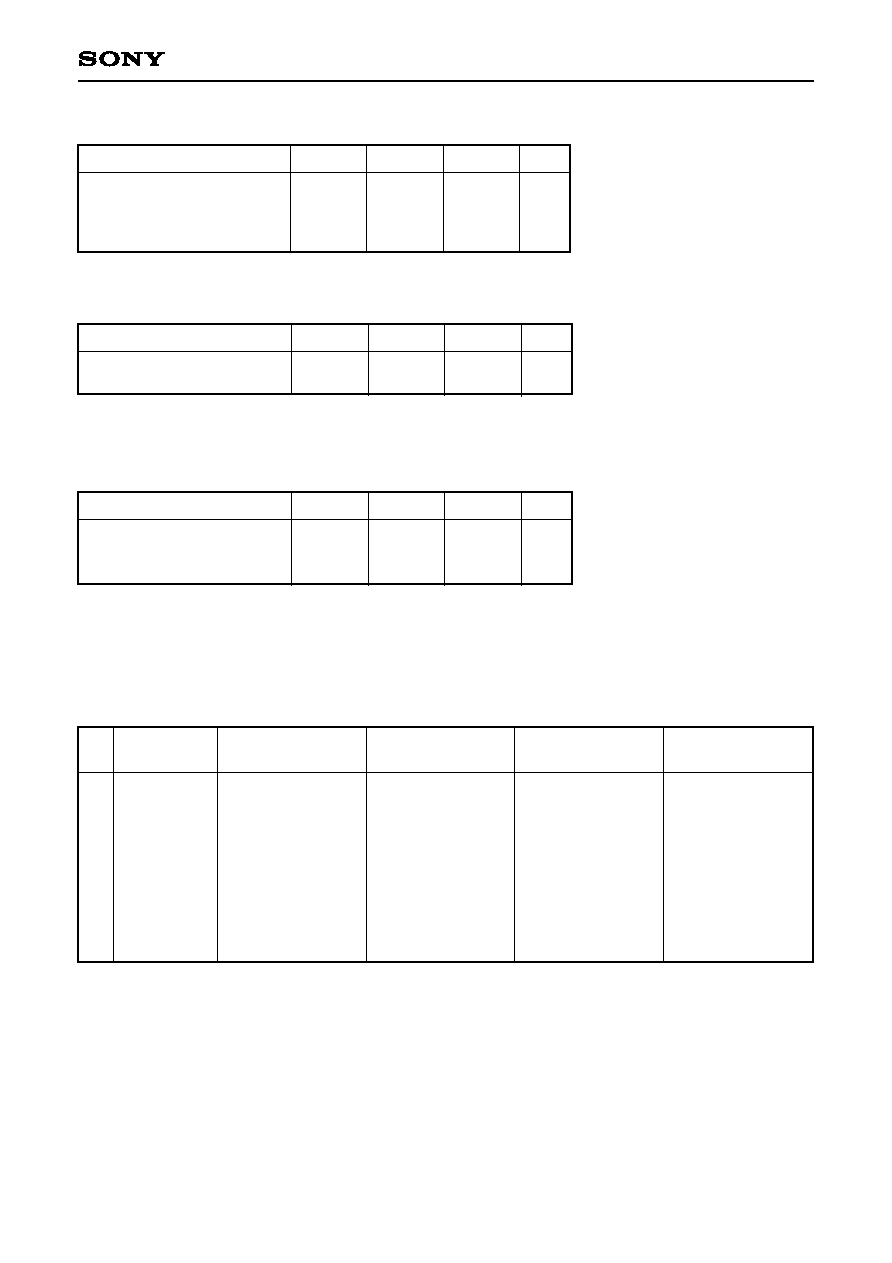

Absolute Maximum Ratings (Ta = 25∞C)

∑ Supply voltage

AV

EE

, DV

EE

≠7 to +0.5

V

∑ Analog input voltage

V

IN

≠2.7 to +0.5

V

∑ Reference input voltage

V

RT

, V

RB

, V

RM

≠2.7 to +0.5

V

| V

RT

≠ V

RB

|

2.5

V

∑ Digital input voltage

MINV, LINV, CLK, CLK

≠4 to +0.5

V

| CLK ≠ CLK |

2.7

V

∑ V

RM

pin input current

I

VRM

≠3 to +3

mA

∑ Digital output current

ID

0

to ID

7

, IOR, ID

0

to ID

7

, IOR

≠30 to 0

mA

∑ Storage temperature

Tstg

≠65 to +150

∞C

Operating Conditions

Min.

Typ.

Max.

Unit

∑ Supply voltage

AV

EE

, DV

EE

≠5.5

≠5.2

≠4.95

V

AV

EE

≠ DV

EE

≠0.05

0

0.05

V

AGND ≠ DGND

≠0.05

0

0.05

V

∑ Reference input voltage

V

RT

≠0.1

0

0.1

V

V

RB

≠2.2

≠2.0

≠1.8

V

∑ Analog input voltage

V

IN

V

RB

V

RT

∑ Operating temperature

Tc

≠20

100

∞C

≠ 3 ≠

CXA1166K

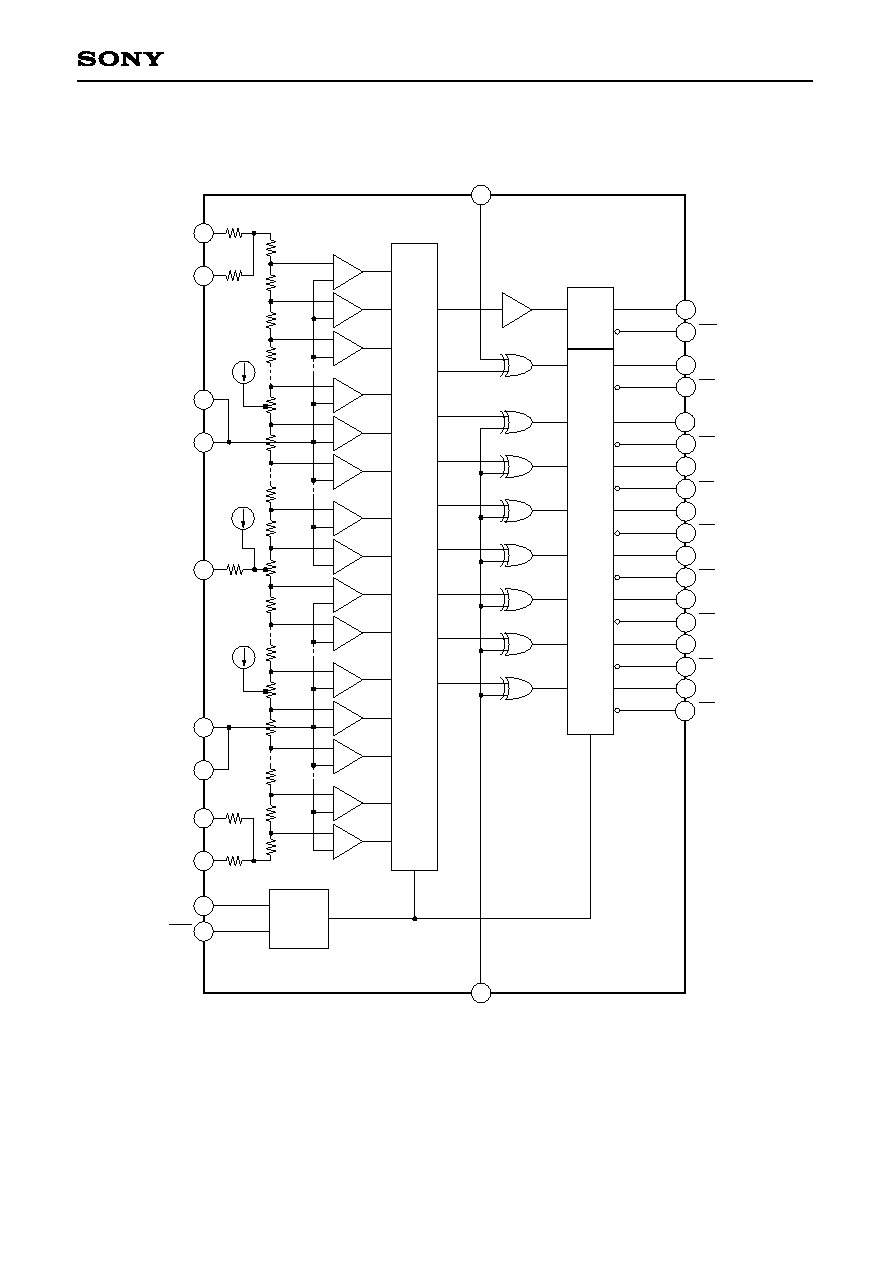

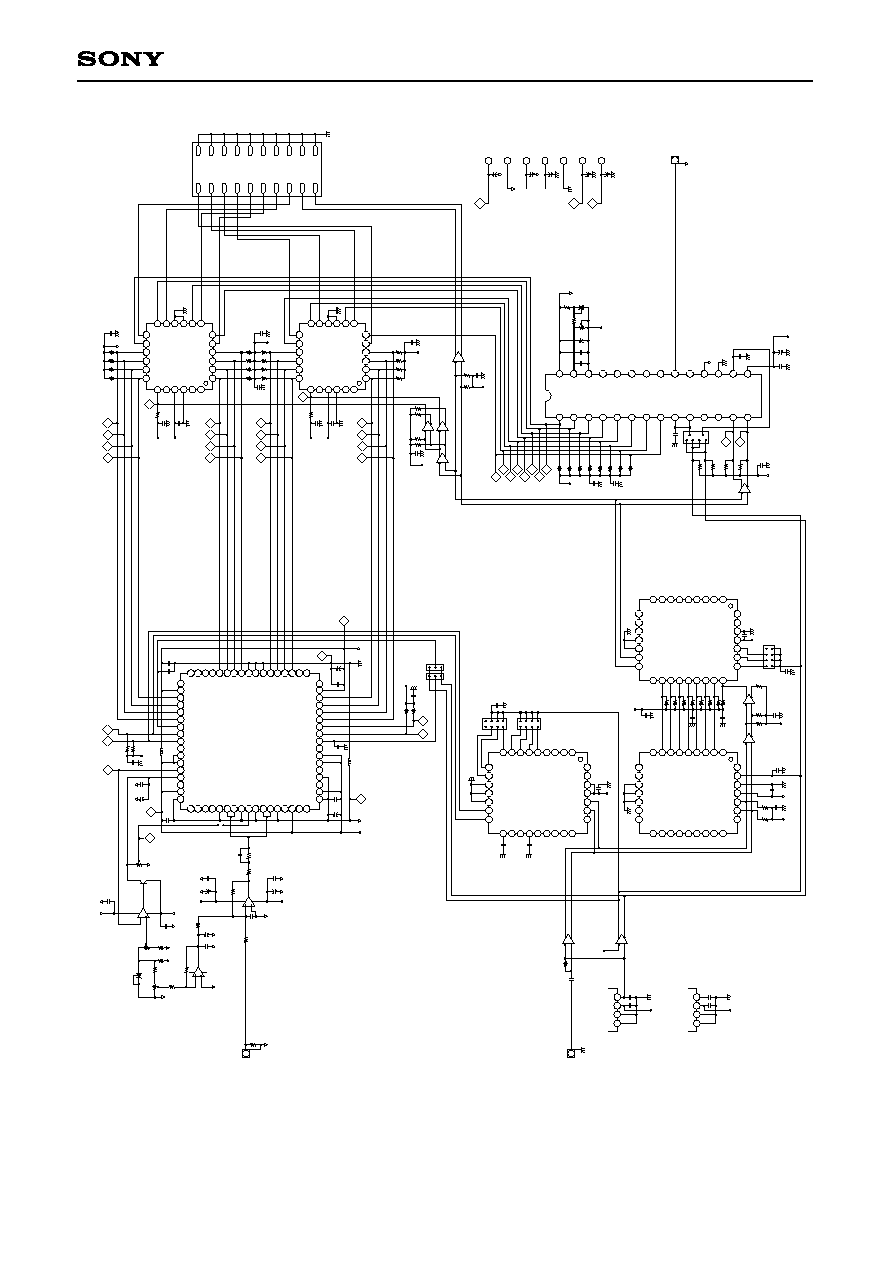

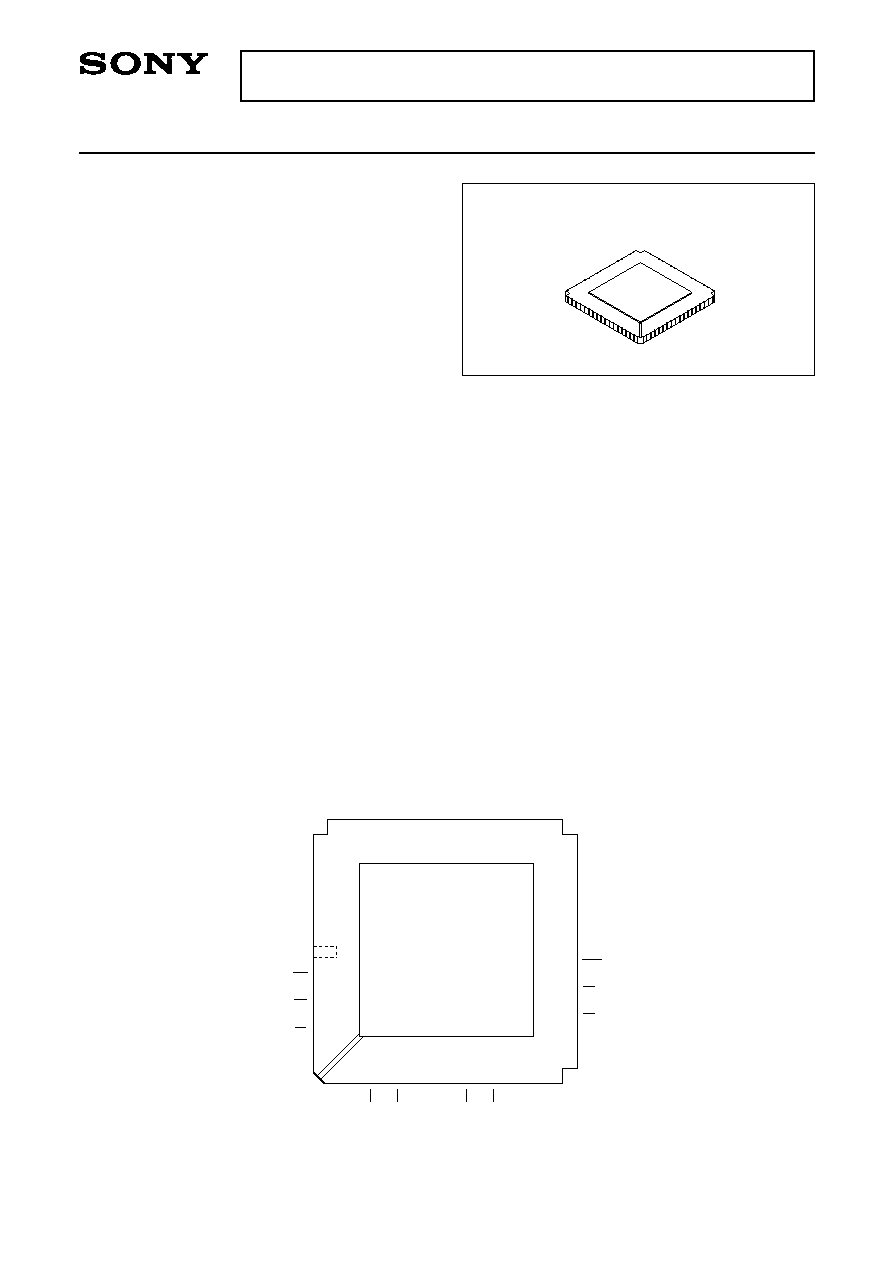

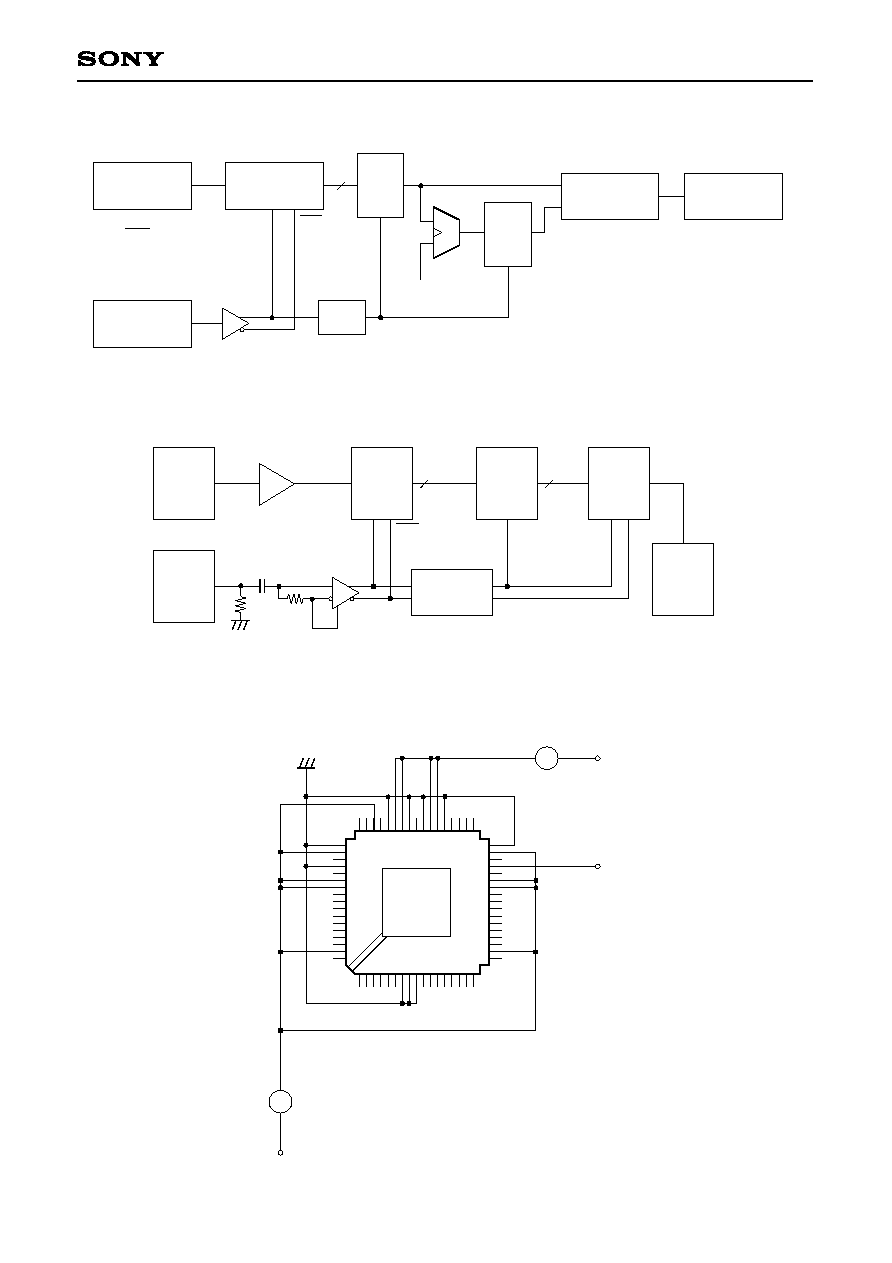

Block Diagram

255

126

127

128

129

191

192

193

254

63

64

65

1

2

CLOCK

DRIVER

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

r

5

r

1

r

3

r/2

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r/2

D7 (MSB)

D6

D4

D3

D5

D2

D1

D0 (LSB)

OUTPUT

ENCODE LOGIC

MINV

V

RT

V

RM

V

RB

CLK

CLK

LINV

Comparator

r

4

V

RBS

r

2

V

RTS

V

IN1

V

IN2

0

D7

D6

D4

D3

D5

D2

D1

OR

OR

1

D0

64

65

54

55

52

49

50

39

40

35

34

33

2

3

31

32

29

30

21

22

19

20

14

15

12

13

6

7

4

5

≠ 4 ≠

CXA1166K

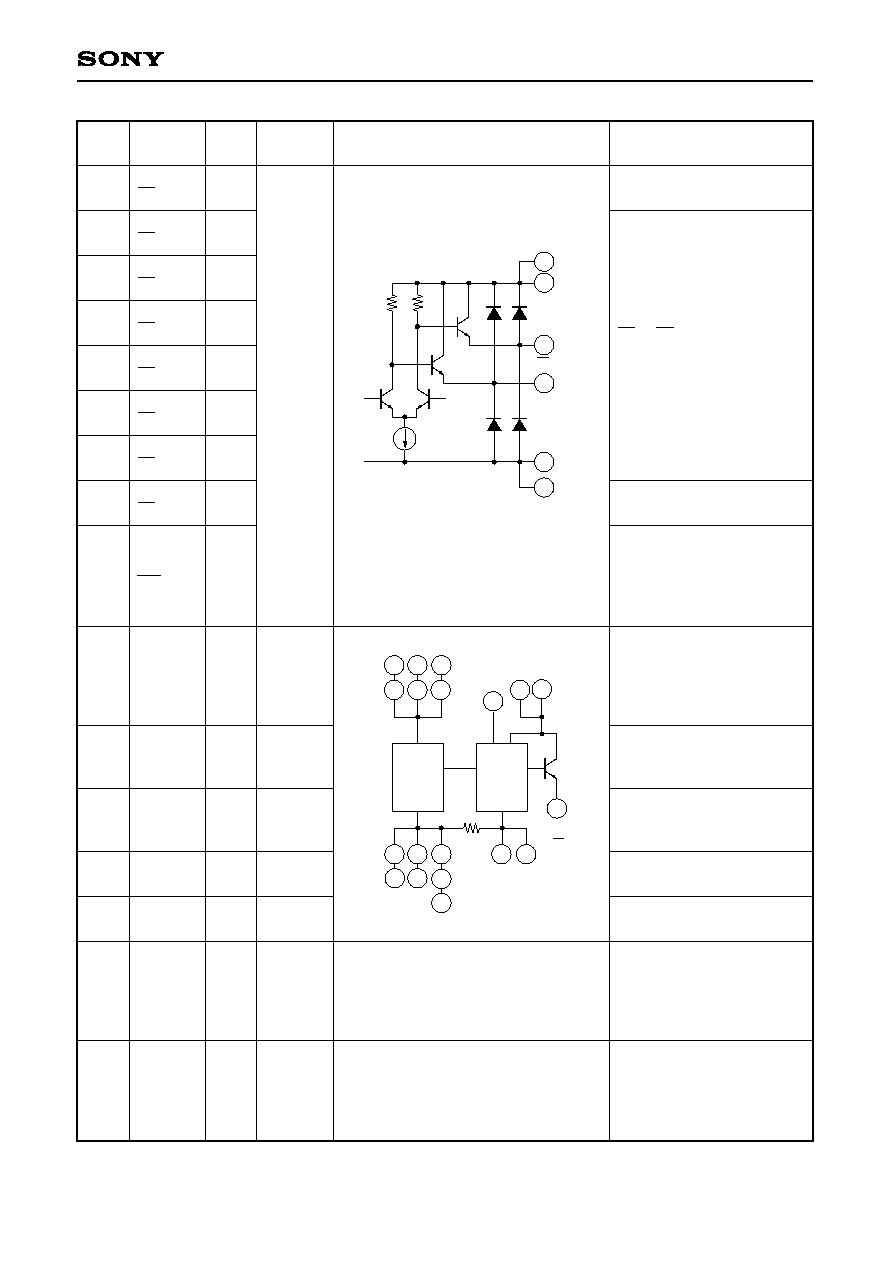

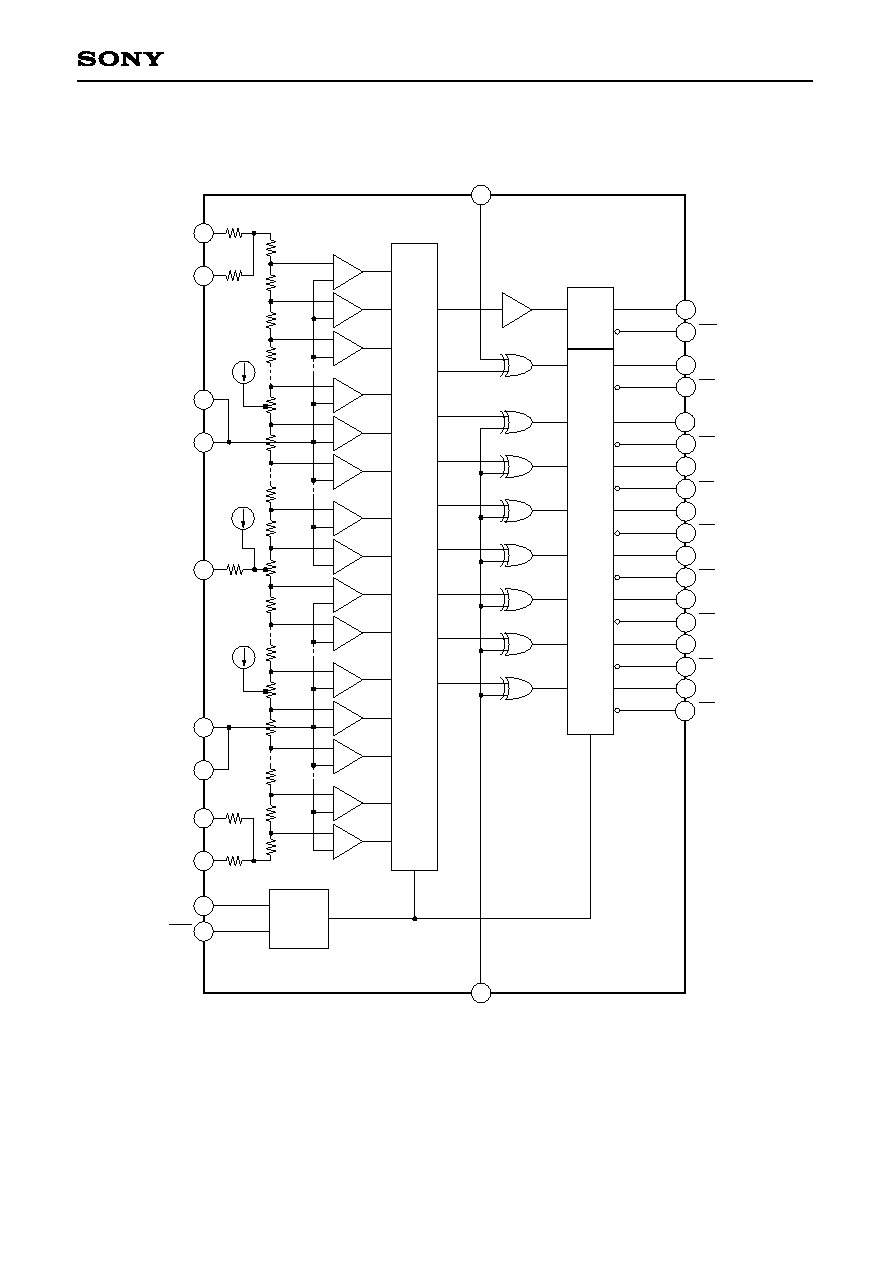

Pin Description

Pin

No.

Symbol

I/O

Standard

voltage level

Equivalent circuit

Description

1

LINV

I

ECL

Polarity selection other than

MSB and overrange.

(Refer to the table of input

voltage vs. Digital output)

Low level is maintained with

left open.

33

MINV

I

ECL

Polarity selection for MSB

(Refer to the table of input

voltage vs. Digital output)

Low level is maintained with

left open.

64

V

RT

I

0V

Reference voltage

(Top) (0V typ.)

65

V

RTS

O

0V

Reference voltage sense

(Top)

52

V

RM

I

V

RB

/2

Reference voltage mid-point.

Can be used for linearity

compensation.

39

V

RBS

O

≠2V

Reference voltage sense

(Bottom)

40

V

RB

I

≠2V

Reference voltage (Bottom)

54

55

V

IN1

49

50

V

IN2

I

V

RTS

to

V

RBS

Analog input.

Pins 49, 50 and Pins 54, 55

should be connected

externally.

35

CLK

I

ECL

34

CLK

I

ECL

CLK input

Complementary CLK input.

ECL threshold potential

(≠1.3V) is maintained with

left open.

The complementary input is

recommended for stable

operation at high speed

though the operation only

with the CLK input is

possible when the CLK

input is left open.

r

r

r

r

LINV

DGND1

DV

EE

≠1.3V

MINV

or

18

1

33

28

8

To

Comparator

r/2

r

1

r

r

r

r /2

r

4

r

3

r

2

V

RT

V

RM

V

RB

r

5

V

RTS

V

RBS

64

65

25

39

40

AGND

V

IN1

V

IN2

43, 48, 51, 53, 56, 61

128 to 255

To Comp

0 to 127

54

55

49

50

r

r

r

r

r

r

DGND1

CLK

CLK

DV

EE

18

35

34

8

28

≠ 5 ≠

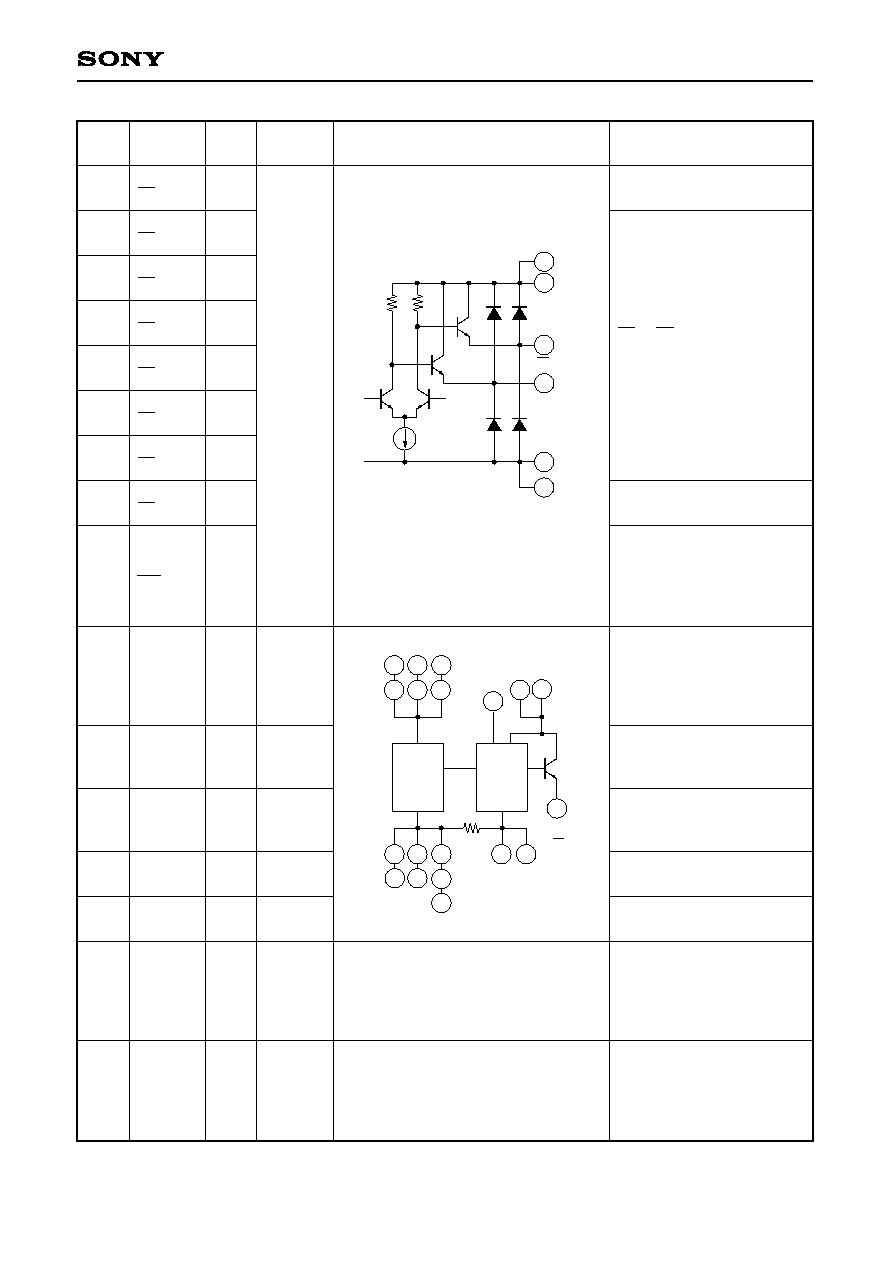

CXA1166K

31

32

29

30

21

22

19

20

14

15

12

13

6

7

4

5

2

3

D

7

D

7

D

6

D

6

D

5

D

5

D

4

D

4

D

3

D

3

D

2

D

2

D

1

D

1

D

0

D

0

OR

OR

O

O

O

O

O

O

O

O

O

ECL

MSB and complementary

MSB output

D

1

to D

6

: Output

D

1

to D

6

: Complementary

output

LSB and complementary

LSB output

Overrange output;

Low level for overrange.

Overrange complementary

output;

High level for overrange.

37, 38,

42, 58,

62, 66,

67

AV

EE

≠5.2V

Analog supply.

Internally connected with

DV

EE

(resistance: 4 to 6

).

43, 48,

51, 53,

56, 61

AGND

0V

Analog ground.

Separated from DGND.

8

28

DV

EE

≠5.2V

Digital supply.

Internally connected with

AV

EE

(resistance: 4 to 6

).

18

DGND1

0V

Digital ground

16

17

DGND2

0V

Digital ground for output

drive

41, 44,

45, 46,

47, 57,

59, 60,

63

NC

--

No connected.

It is recommended to connect

these pins to AGND.

9, 10,

11, 23,

24, 25,

26, 27,

36, 68

NC

--

No connected.

It is recommended to connect

these pins to DGND.

DGND2

DV

EE

Di

Di

16

17

8

28

DGND2

Internal

Analog

Circuit

Internal

Digital

Circuit

DGND1

AGND

Di

Di

DV

EE

AV

EE

4 to 6

61

43

48

51

53

56

18

16 17

42

62

37

38

58

66

67

8

28

For stable operation, all of these pins must be connected on the corresponding PCB pattern.

Pin

No.

Symbol

I/O

Standard

voltage level

Equivalent circuit

Description

≠ 6 ≠

CXA1166K

Electrical Characteristics

(AV

EE

= DV

EE

= ≠5.2V, V

RT

, V

RTS

= 0V, V

RB

, V

RBS

= ≠2V, Ta = 25∞C)

Item

Resolution

DC characteristics

Integral linearity error

Differential linearity error

Analog input

Analog input capacitance

Analog input resistance

Input bias current

Reference inputs

Reference resistance

Residual resistance

1

r

1

r

2

r

3

r

4

r

5

Digital inputs

Logic High level

Logic Low level

Logic High current

Logic Low current

Input capacitance

Switching characteristics

Maximum conversion rate

Aperture jitter

Sampling delay

Output delay

Clock High pulse width

Clock Low pulse width

Digital output

Logic High level

Logic Low level

Output rise time

Output fall time

Dynamic characteristics

Input bandwidth

SNR

Error rate

Differential gain error

Differential phase error

Power supply

Supply current

Power consumption

3

E

IL

E

DL

C

IN

R

IN

I

IN

R

REF

r

1

r

2

r

3

r

4

r

5

V

IH

V

IL

I

IH

I

IL

Fc

Taj

Tds

Tdo

T

PW1

T

PW0

V

OH

V

OL

Tr

Tf

SNR

DG

DP

I

EE

Pd

V

IN

= ≠1V + 0.07Vrms

V

IN

= ≠1V

V

IN

= ≠1V

V

IH

= ≠0.8V

V

IL

= ≠1.6V

R

L

= 50

to ≠2V

T

PW1

+ T

PW0

= 4.0ns

R

L

= 50

to ≠2V

R

L

= 50

to ≠2V

R

L

= 50

to ≠2V

R

L

= 50

to ≠2V

V

IN

=2Vp-p

Input = 1kHz, FS

Clock = 250MHz

Input = 62.499MHz, FS

Clock = 250MHz

Input = 49.999MHz, FS

Error > 16LSB

Clock = 200MHz

Input = 62.499MHz, FS

Error > 16LSB

Clock = 250MHz

NTSC 40IRE mod.

ramp, Fc = 250MSPS

50

20

83

0.1

300

0.5

300

0.1

≠1.13

0

≠50

250

0.4

1.8

1.8

1.8

≠1.00

200

44

30

≠360

8

18

120

125

0.6

500

2.0

500

0.6

4

9

1.4

2.5

0.6

0.6

46

35

10

≠8

1.0

0.5

≠270

1.4

±0.5

±0.5

450

182

2.0

700

5.0

700

2.0

≠1.50

70

50

2.4

3.2

≠1.60

1.5

1.5

10

≠9

10

≠6

1.9

bits

LSB

LSB

pF

k

µA

V

V

µA

µA

pF

MSPS

ps

ns

ns

ns

ns

V

V

ns

ns

MHz

dB

dB

TPS

2

TPS

2

%

deg

mA

W

Symbol

Condition

Min.

Typ.

Max.

Unit

{

{

}

{

{

1 See Block Diagram.

2 TPS: Times Per Sample

3 Pd = I

EE

∑ V

EE

+

R

REF

(V

RT

≠ V

RB

)

2

}

≠ 7 ≠

CXA1166K

Input Voltage vs. Digital Output

V

IN

0V

≠1V

≠2V

0

1

127

128

254

255

0 0 0 ...... 0 0

0 0 0 ...... 0 0

0 0 0 ...... 0 1

:

:

0 1 1 ...... 1 1

1 0 0 ...... 0 0

:

:

1 1 1 ...... 1 0

1 1 1 ...... 1 1

1 1 1 ...... 1 1

0

1

1

1

1

:

:

1

1

1

1 0 0 ...... 0 0

1 0 0 ...... 0 0

1 0 0 ...... 0 1

:

:

1 1 1 ...... 1 1

0 0 0 ...... 0 0

:

:

0 1 1 ...... 1 0

0 1 1 ...... 1 1

0 1 1 ...... 1 1

0 1 1 ...... 1 1

0 1 1 ...... 1 1

0 1 1 ...... 1 0

:

:

0 0 0 ...... 0 0

1 1 1 ...... 1 1

:

:

1 0 0 ...... 0 1

1 0 0 ...... 0 0

1 0 0 ...... 0 0

1 1 1 ...... 1 1

1 1 1 ...... 1 1

1 1 1 ...... 1 0

:

:

1 0 0 ...... 0 0

0 1 1 ...... 1 1

:

:

0 0 0 ...... 0 1

0 0 0 ...... 0 0

0 0 0 ...... 0 0

Step

MINV 1

LINV 1

D7 D0

D7 D0

D7 D0

D7 D0

0

1

1

0

0

0

V

RT

= V

RTS

= 0V, V

RM

= ≠1V or Open, V

RB

= V

RBS

= ≠2V

Timing Diagram

Tr

Tf

80%

20%

80%

N + 1

20%

N

N ≠ 1

Td

Tpw0

Tpw1

N

N + 1

Analog input

CLK

CLK

Digital output

Tds

N + 2

OR

0

1

1

1

1

:

:

1

1

1

OR

0

1

1

1

1

:

:

1

1

1

OR

0

1

1

1

1

:

:

1

1

1

OR

≠ 8 ≠

CXA1166K

Electrical Characteristics Measurement Circuit

Integral Linearity Error Measurement Circuit

Differential Linearity Error Measurement Circuit

DUT

CXA1166K

A<B A>B

Comparator

Buffer

Controller

DVM

8

8

"1 "

"0"

000∑∑∑00

to

111∑∑∑10

V

IN

+ V

≠ V

S2

S1

S1:ON when A<B

S2: ON when A>B

A8

to

A1

A0

B8

to

B1

B0

Sampling Delay Measurement circuit

Aperture Jitter Measurement circuit

Aperture Jitter Measurement Method

CXA1166K

OSC1

:Variable

OSC2

Logic

Analizer

60MHz

60MHz

Amp

ECL

Buffer

CLK

V

IN

8

fr

1024

samples

V

IN

(LSB)

CLK

V

IN

CLK

t

t

0V

≠1V

≠2V

129

128

127

126

125

Sampling timing fluctuation

( = aperture jitter)

When the distribution of the output codes is

(unit: LSB) If

the maximum slew rate point is sampled with the clock signal

having the same frequency as that of the analog input signal,

Aperture jitter (Taj) is defined as follows:

Taj =

/ =

/ ( )

t

2

256

◊

2

f

≠ 9 ≠

CXA1166K

Error Rate Measurement Circuit

Comparator

A<B

Pulse

Counter

CXA1166K

Signal

Source

ECL

Latch

ECL

Latch

1/16

+

Signal

Source

2Vp ≠ p Sine Wave

f

CLK

V

in

CLK

CLK

8

DATA 16

A

B

f

CLK

4

≠ 1kHz

Differential Gain Error Measurement Circuit

Differential Phase Error Measurement Circuit

ECL

Latch

10bit

D/A

Vector

Scope

Amp

NTSC

Signal

Source

SG (CW)

50

CLK

CLK

8

8

V

BB

Decimator

(CX20202A ≠ 1)

DUT

CXA1166K

Power Supply Current Measurement Circuit

Analog Input Bias Current Measurement Circuit

I

IN

A

A

≠ 1V

I

EE

≠ 2V

≠ 5.2V

61

60

10

43

27

44

26

1

9

CXA1166K

≠ 10 ≠

CXA1166K

Notes on Operation

∑ The CXA1166K is an ultra-high speed A/D converter featuring ECL level of input/output for the logic block. In

order to derive the most from its high-speed performance, the characteristic impedance should be matched

properly.

∑ The outputs are designed to drive a load terminated to ≠2V at 50

. An excellent transmission characteristic

can be yielded by designing the printed circuit board with a 50

characteristic impedance.

Yielding its top performance is difficult on the printed circuit board with a characteristic impedance of 100

or

more.

∑ The power supply and ground pattern greatly affect the characteristics of the converter. The higher the

frequency, the more important these connections become. The general precautions are as follows.

≠ Make the pattern of the power supply and ground as wide as possible. Using a ground plane inner layer by

using a multilayer printed circuit board is recommended.

≠ lsolate the AGND, DGND pins and the AV

EE,

DV

EE

from one another on the pattern in order to safeguard

against interaction. Connect the AGND and DGND pins at one place using a ferrite-bead filter to prevent

DC offset. The same processing is requited for the AV

EE

and DV

EE

pins.

∑ When mounting the A/D converter on the socket, use the one of shortest leads. The QFP socket, the type

name IC61-0684-048, manufactured by YAMAICHI ELECTRONICS CO., LTD. is recommended.

∑ The V

IN

analog input pins have somewhat large input capacitance (approximately 18pF) for high-frequency

circuits. In order to drive them with an excellent frequency response, it is necessary to safeguard against any

deterioration in performance resulting from parasitic capacitance and parasitic inductance by using a high-

capacity drive circuit, keeping the wiring as short as possible, and using chip parts as resistors and

capacitors, for instance. The drive circuit shown in the Application Circuit has a virtually flat frequency

response up to approximately 170MHz. C89, R11 and C15 have been inserted mainly to expand the

bandwidth, while R10 has been inserted mainly to suppress operational amplifier oscillation and block

peaking of the frequency response. Since the optimal values of these elements differ depending on the

printed circuit board pattern and mounting condition of the A/D converter socket used, they must be

determined on the basis of experimentation.

∑ Connect all four V

IN

pins directly and as short as possible. Unlike the CXA1176, it is not necessary to insert

resistance of several ohms for each pin.

∑ The voltage at the V

RT

and V

RB

reference voltage pins and the reference voltage inside these pins differ

slightly due to residual resistance. V

RTS

and V

RBS

are provided to detect the reference voltage inside the pins.

The overrange reference voltage is 1/2 LSB down from V

RTS

; the lowest input voltage at which the output

code changes is 1/2 LSB up from V

RBS

.

∑ Provide adequate by-pass capacitors for V

RT

and V

RB

to protect them from high-frequency noise. Normally,

V

RT

is connected to AGND of an inner layer of the printed circuit board. Using a chip capacitor (approximately

0.1µF), make the by-pass from V

RB

to AGND as short as possible. C22 (1µF), in the Application Circuit is for

suppressing the oscillation of the reference voltage generation circuit.

≠ 11 ≠

CXA1166K

∑ Unlike the CXA1176, V

RTS

and V

RBS

are connected to the reference resistors via resistors of approximately

500

. Since these resistors may be eliminated in the future improved versions of this converter, use a

reference voltage generation circuit which is adaptable to their elimination. The reference voltage generation

circuit (the section composed of IC12_2, etc.) in the Application Circuit is recommended.

∑ Although V

RM

is provided to compensate for the integral linearity error, there is no need for such

compensation. It is recommended that it is kept open.

∑ OR and OR are output pins for indicating that the input is over range. They are not inverted by MINV or LINV.

∑ Noise in MINV and LINV results in misoperation, the cause of which is extremely difficult to track down. Keep

these pins open in cases where low level setting voltage alone is sufficient. When high level voltage input is

required, provide the shortest possible by-pass from them to DGND using chip capacitors (approximately

0.1µF). Input voltages of ≠0.5V to ≠1.0V for high level and ≠1.6V to ≠2.5V for low level are recommend. Do

not make the direct connection to DGND when high level voltage is input.

∑ Inputting differential signals is recommended for the CLK and CLK clock input pins. Although operation is

possible by driving only the CLK pin, doing so involves the risk that the characteristics may become unstable

near the maximum speed. This is because the internal operation of the A/D converter depends on both clock

rise and fall.

∑ When the CLK pin is not used, by-pass it to DGND using a capacitor (approximately 0.1µF). At this time,

approximately ≠1.3V voltage will be generated at this pin. However, the driving capacity is too weak for this to

be used as the V

BB

threshold voltage. It cannot drive even one ECL input load.

∑ This converter is designed to be used at the clock duty cycle of 50%. The deviation from this condition will

subtly affect the performance of the A/D converter but the degree of the affection is not so great as to require

adjustment. The "Error rate vs. Clock duty cycle characteristics" graph shows an example of these changes

in the converter's performance.

∑ Increasing chip temperature will cause the supply current and also the error rate to rise. Adding to these

reasons, in order to prolong the converter's service life, provide an adequate means of cooling. See the

"Maximum conversion frequency vs. Temperature characteristics" and "Supply current vs. Temperature

characteristics" graphs. The reference data for thermal resistance is shown in the "Thermal resistance of the

converter mounted on a board" graph. Note that the actual thermal resistance will differ greatly depending on

the mounting conditions.

∑ Since the CXA1166K is a high-speed IC, take adequate measures to prevent electrostatic breakdown. For

further details on these measures, refer to "Precautions for IC Application" in Sony's Data book.

∑ Sony's SPECL series is used as the logic ICs in the Application Circuit to investigate the maximum

performance of the CXA1166K. For normal applications, lower speed logic ICs can be used according to the

applied frequency.

≠ 12 ≠

CXA1166K

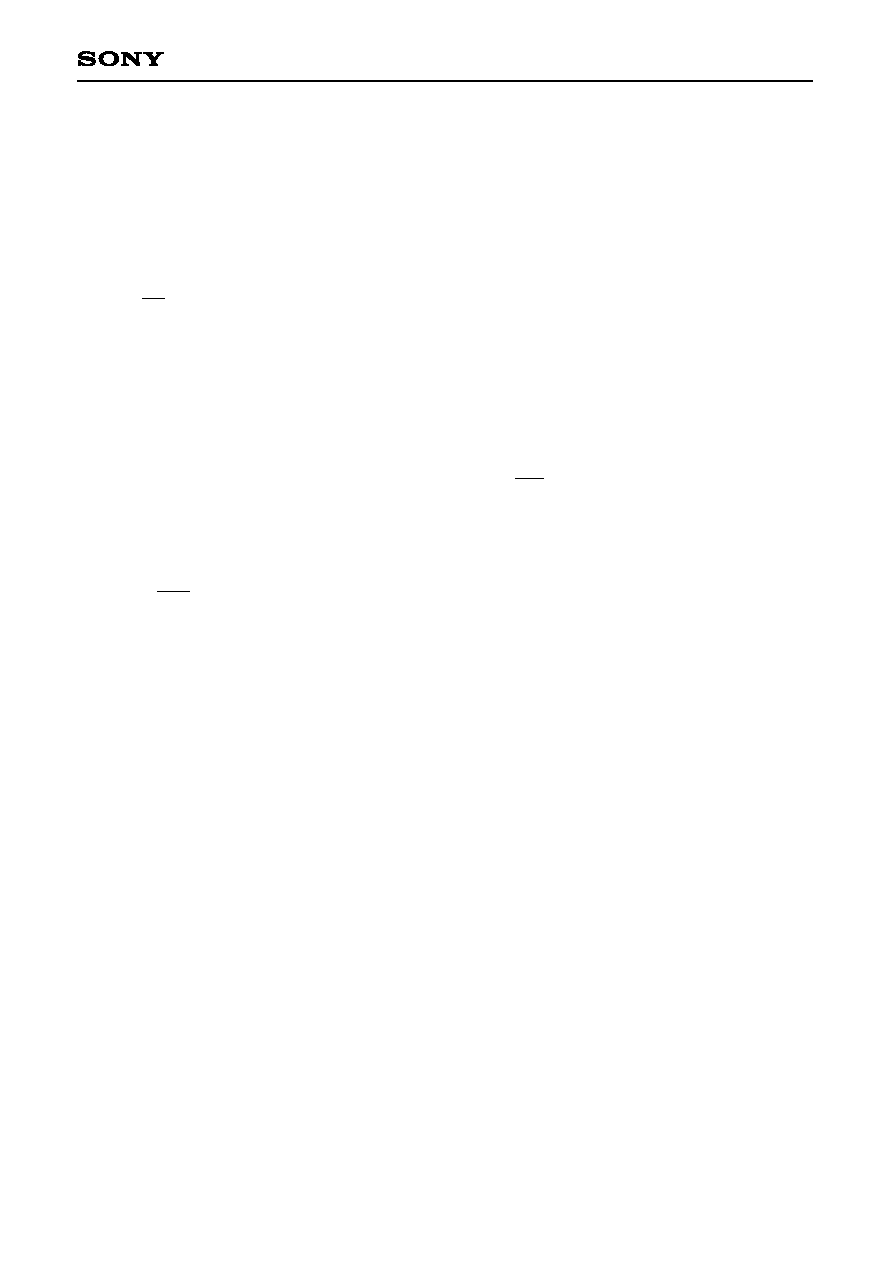

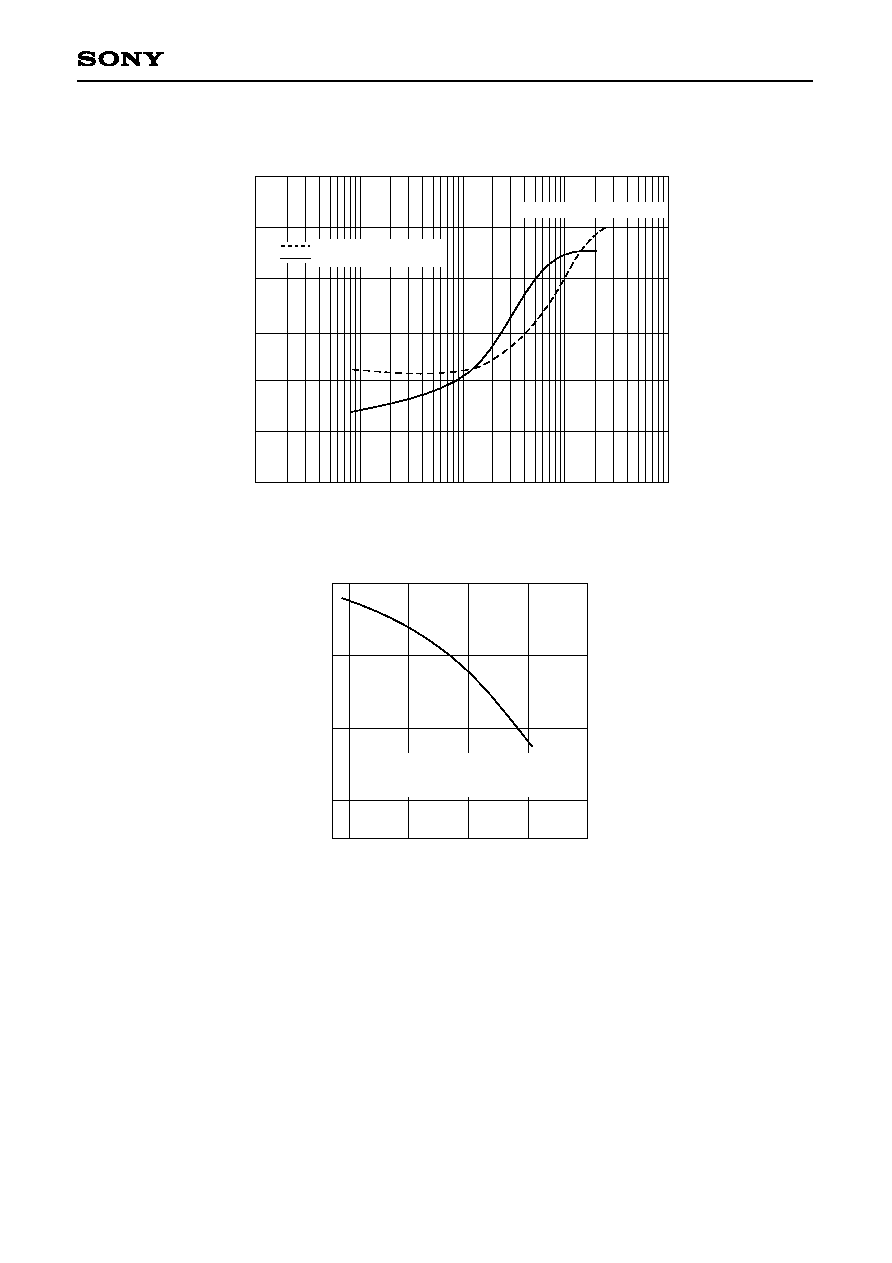

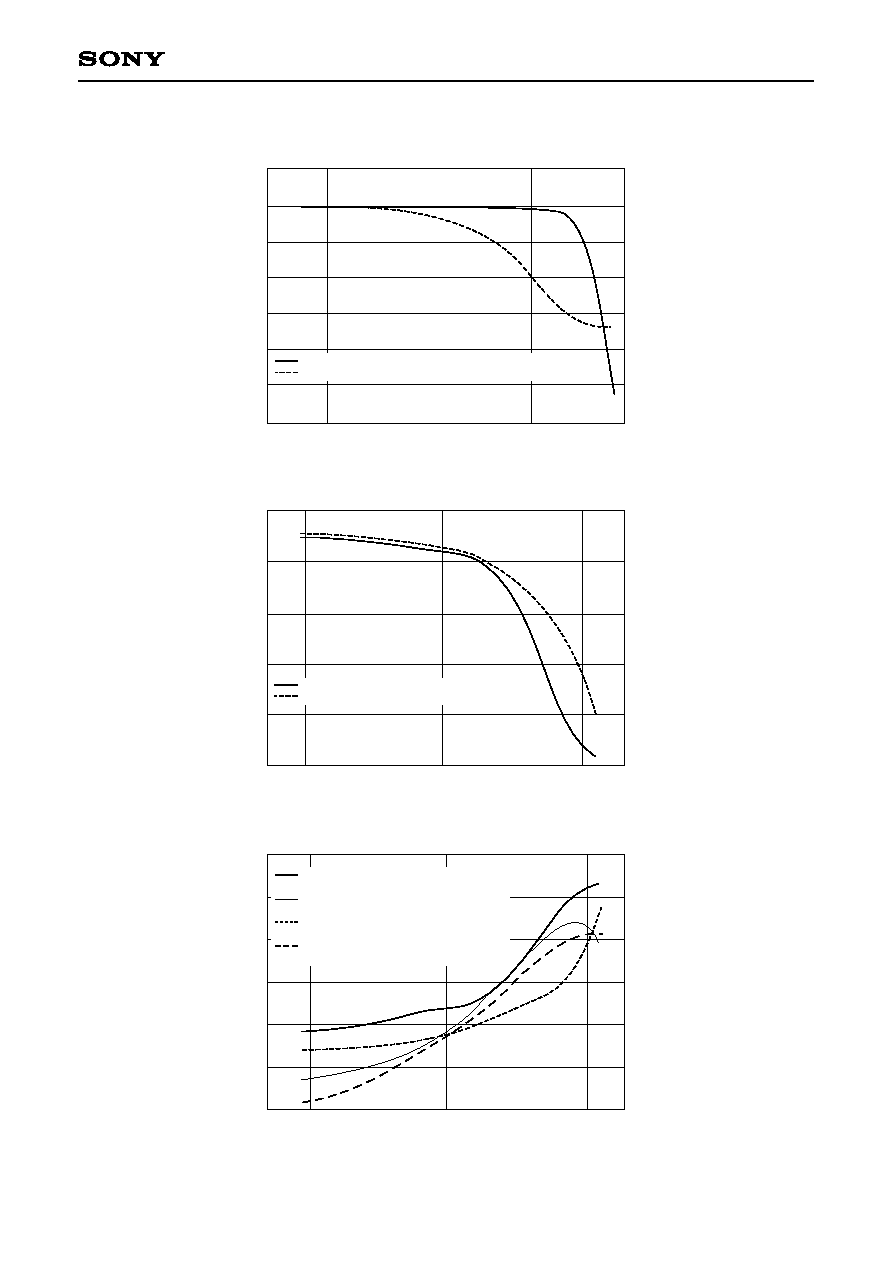

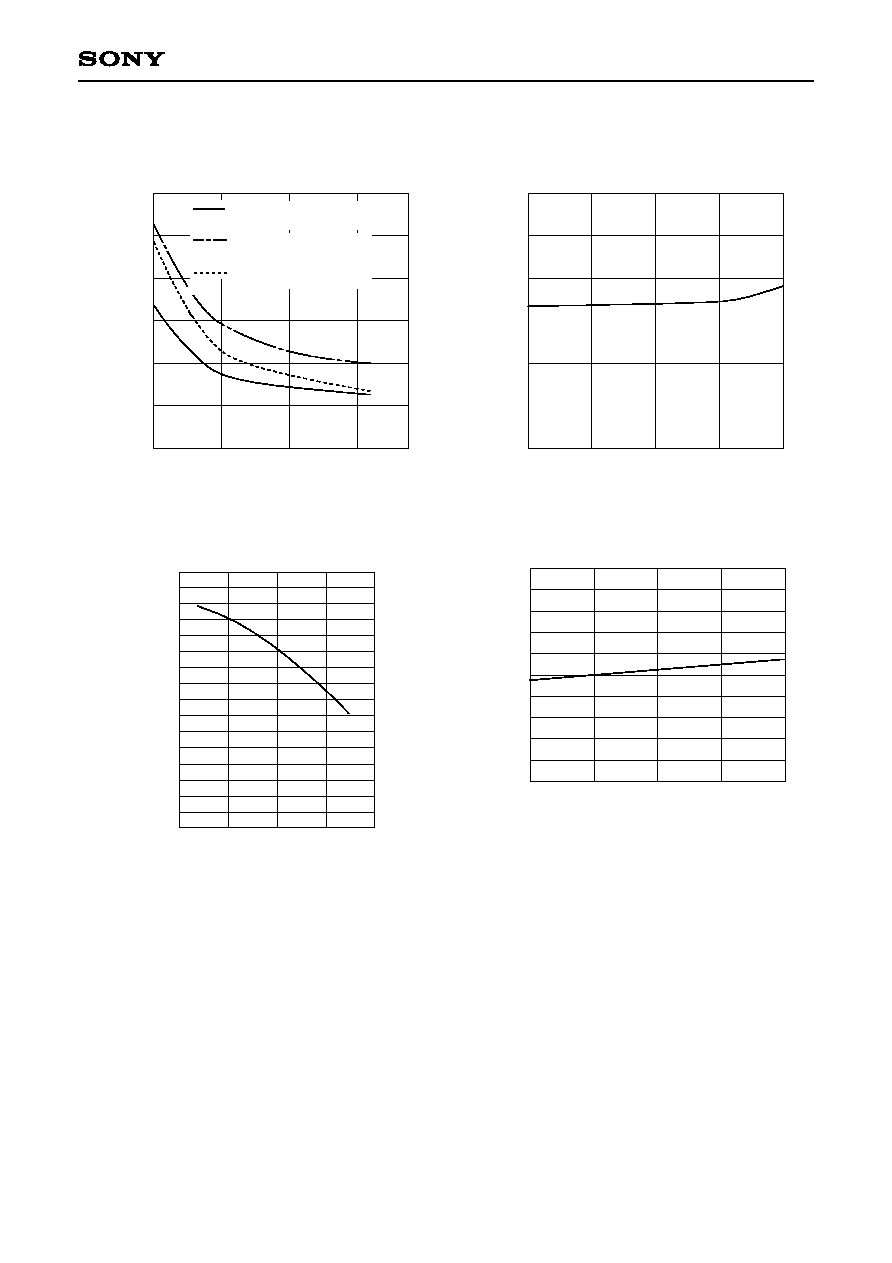

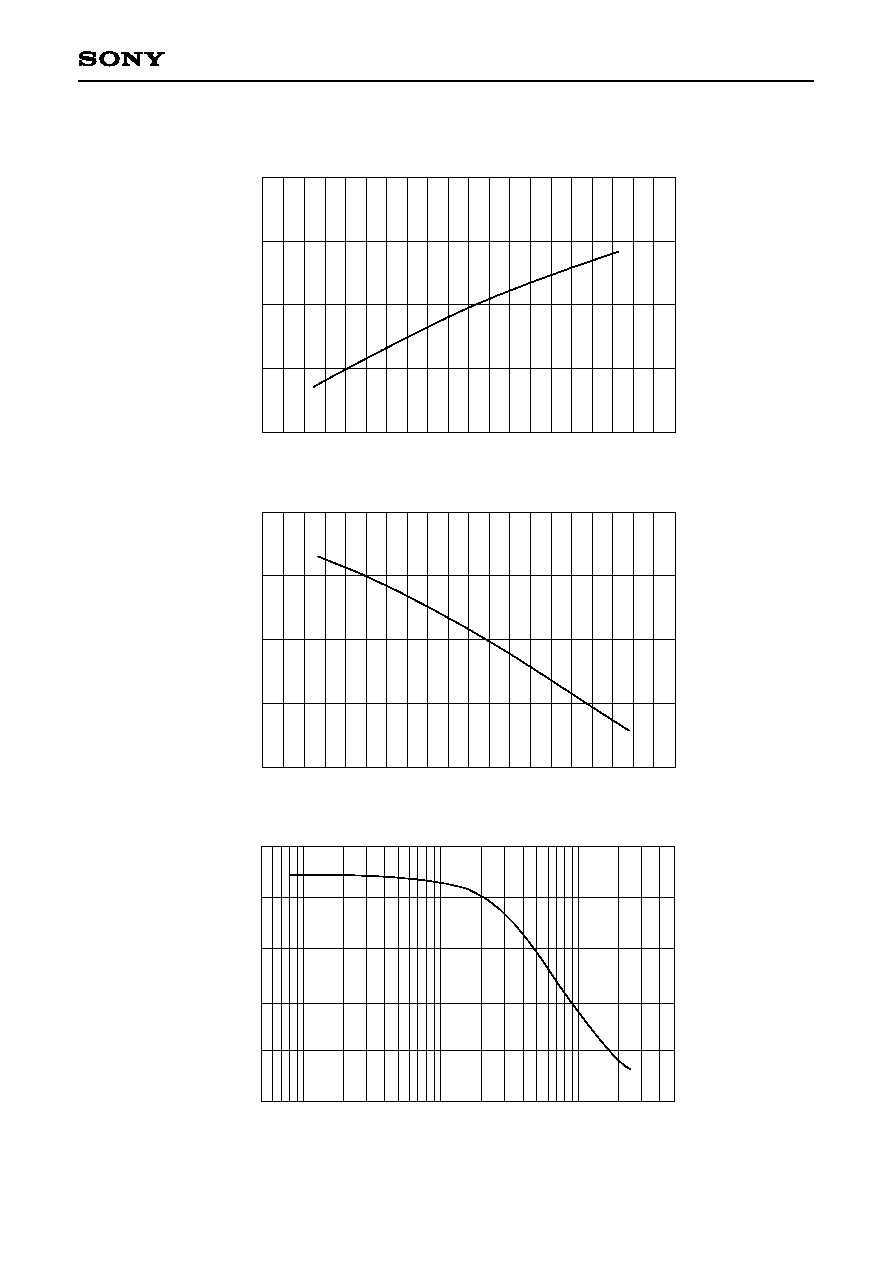

Example of Representative Characteristics

V

IN

pin input capacitance vs.

Voltage characteristics

C

IN

-- Input capacitance [pF]

25

20

15

10

≠

2

0

≠1.5

≠0.5

V

IN

-- Input voltage [V]

I

IN [

µA

]

200

100

0

≠2.0

≠

1.0

0

≠

1.5

≠

0.5

V

IN

-- Input voltage [V]

V

IN

pin input resistance vs.

Voltage characteristics

Analog input resistance [k

]

150

100

≠

2.0

≠

1.0

0

≠

1.5

≠

0.5

125

V

IN

--

Input voltage [V]

Thermal resistance at on-board condition

ja -- Thermal resistance [∞C/W]

50

40

30

0

1.0

2.0

3.0

Air velocity [m/s]

Socket for AMP173061-5

(without heat sink)

Socket for AMP173257-3

(with heat sink)

Socket for YAMAICHI

ELECTRONICS IC61-0684-048

≠1

V

IN

pin input current vs.

Voltage characteristics

≠ 13 ≠

CXA1166K

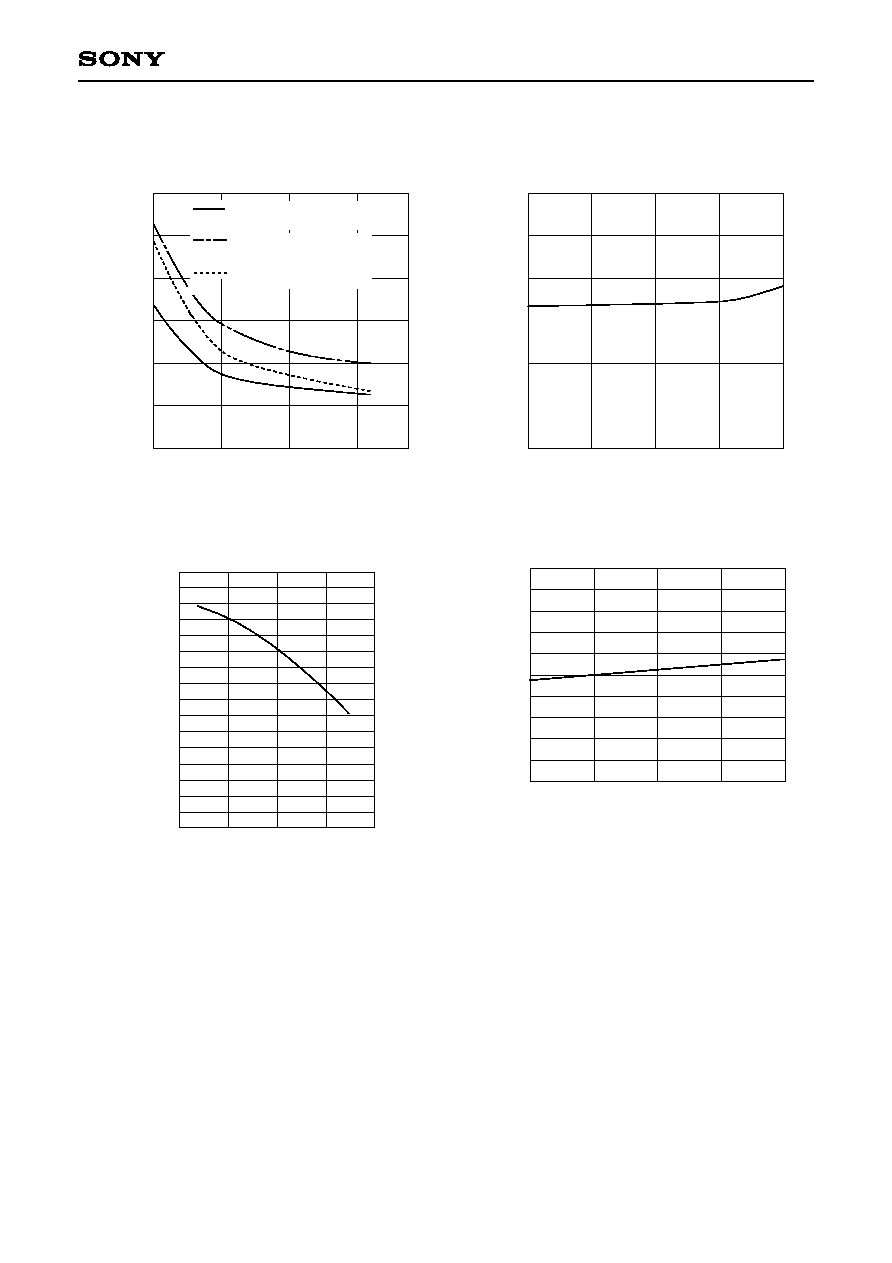

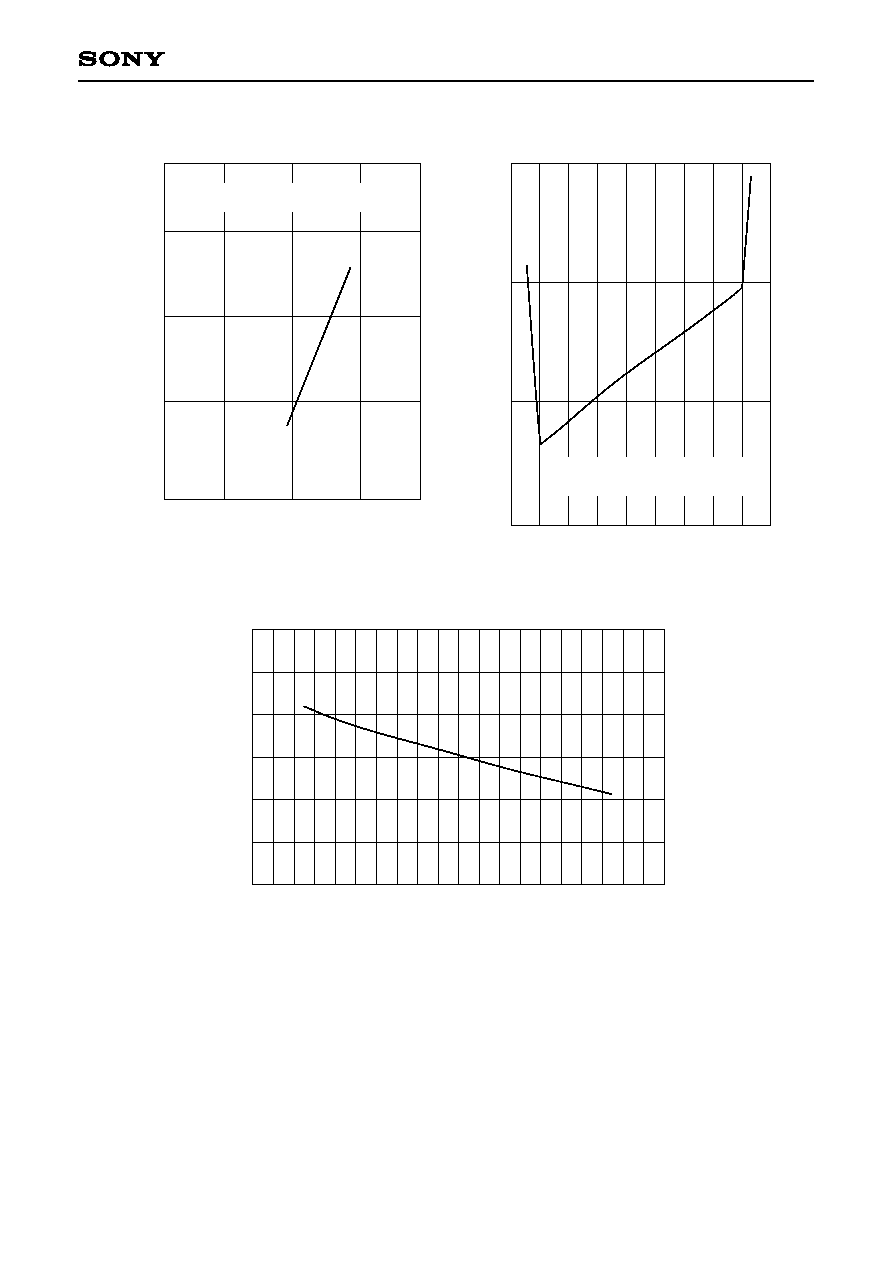

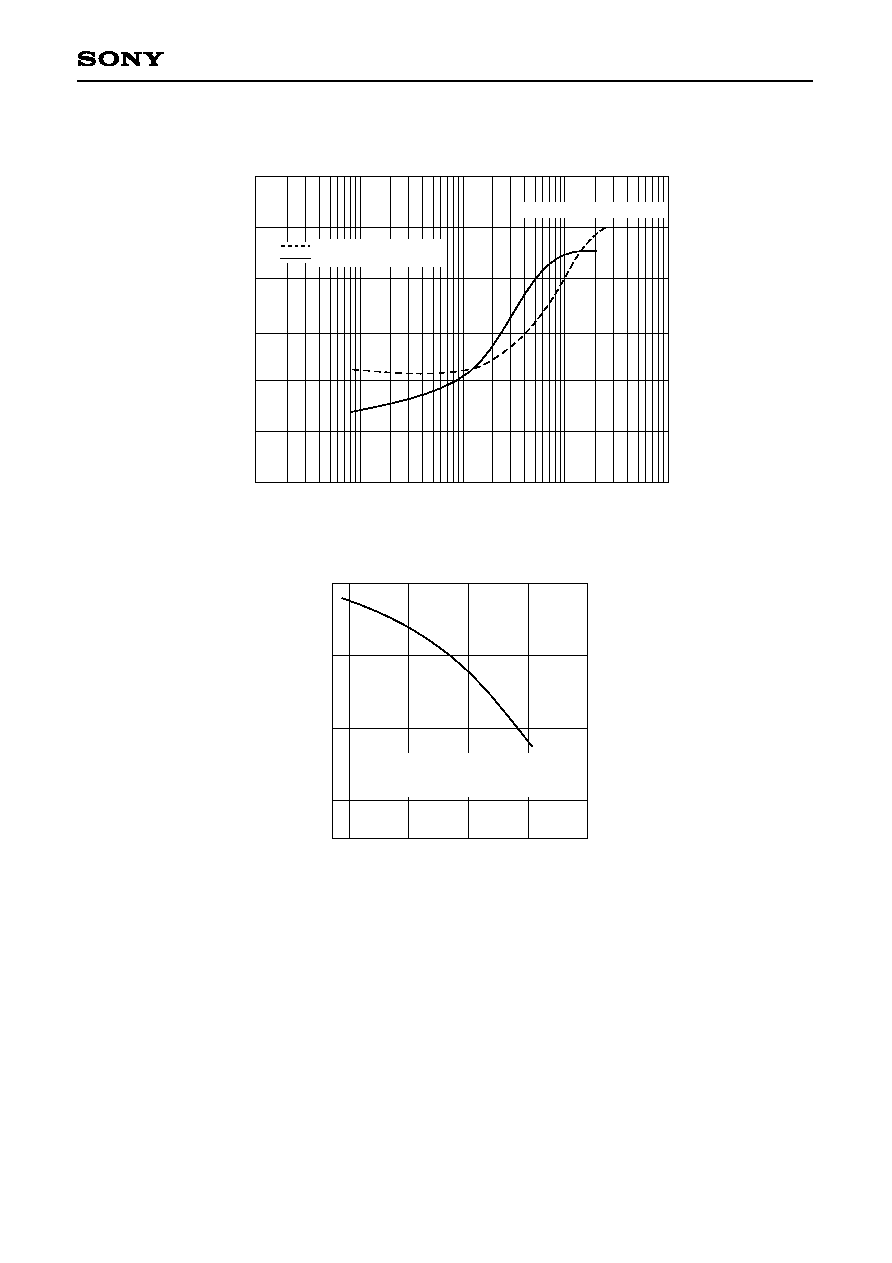

V

IN

pin input current vs. Temperature characteristics

Tc -- Case temperature [∞C]

V

IN

-- Input current [µ

A]

200

150

100

50

0

≠50

0

50

100

150

Resistor string current vs. Temperature characteristics

Tc -- Case temperature [∞C]

Resistor string current [mA]

≠50

0

50

100

150

≠12

≠14

≠16

≠18

≠20

≠22

≠24

CLK open voltage vs. Temperature characteristics

Tc -- Case temperature [∞C]

CLK open voltage [V]

≠50

0

50

100

150

≠1.25

≠1.3

≠1.35

≠1.4

≠1.45

≠ 14 ≠

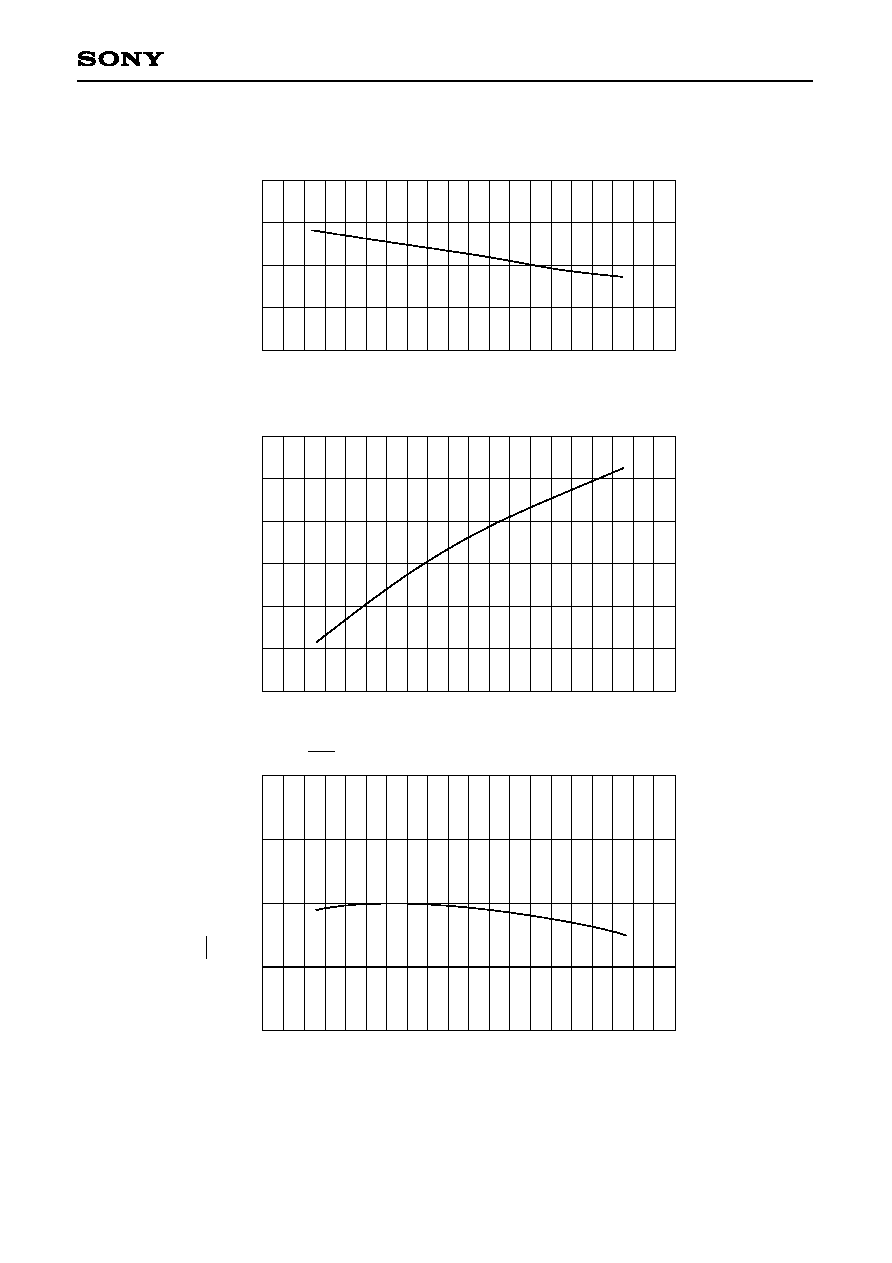

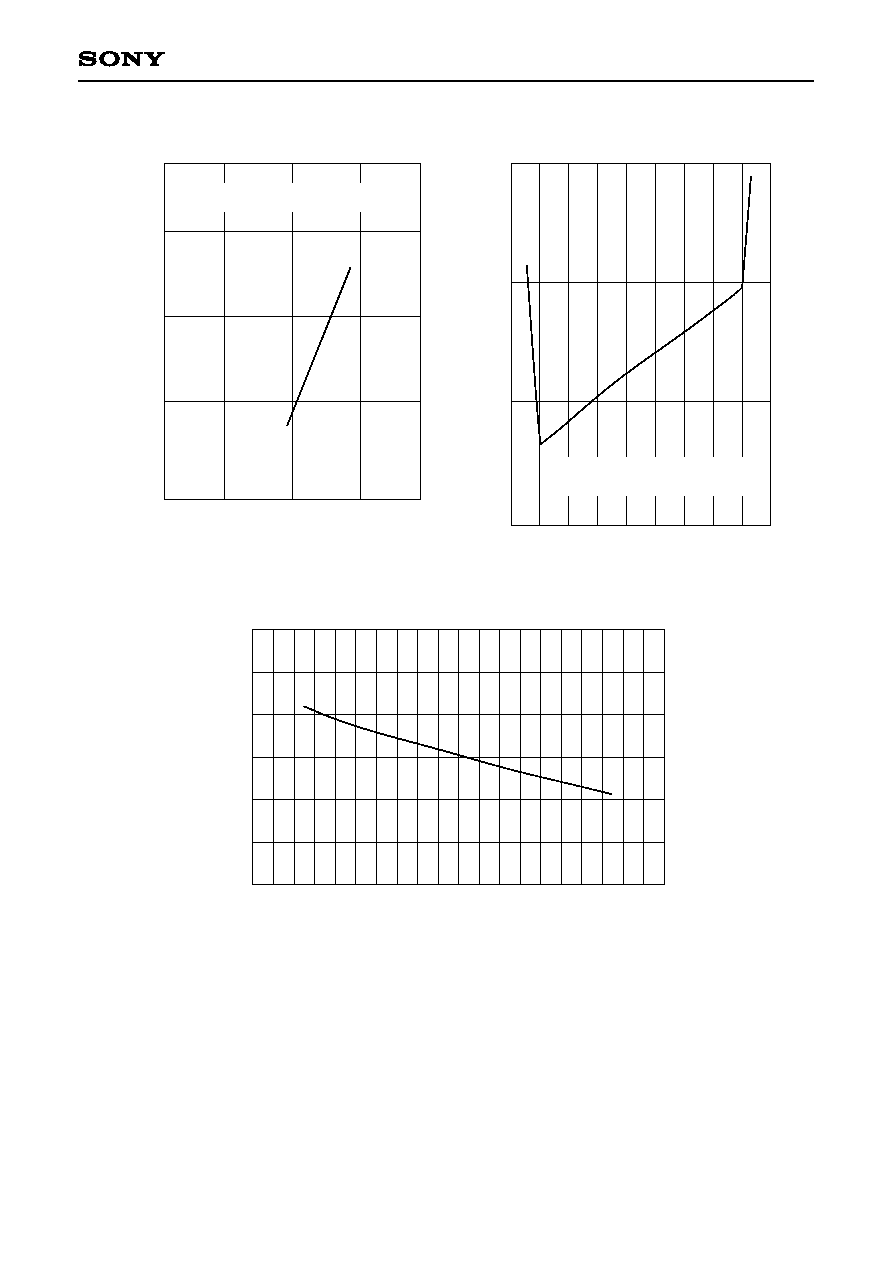

CXA1166K

V

OH

vs. Temperature characteristics

Tc -- Case temperature [∞C]

V

OH

[V]

≠50

0

50

100

150

≠0.7

≠0.8

≠0.9

≠1.0

≠1.1

V

OL

vs. Temperature characteristics

Tc -- Case temperature [∞C]

V

OL

[V]

≠50

0

50

100

150

≠1.7

≠1.8

≠1.9

≠2.0

≠2.1

SNR vs. Input frequency response characteristics

Input frequency [MHz]

SNR [dB]

1

10

100

50

45

40

35

25

30

≠ 15 ≠

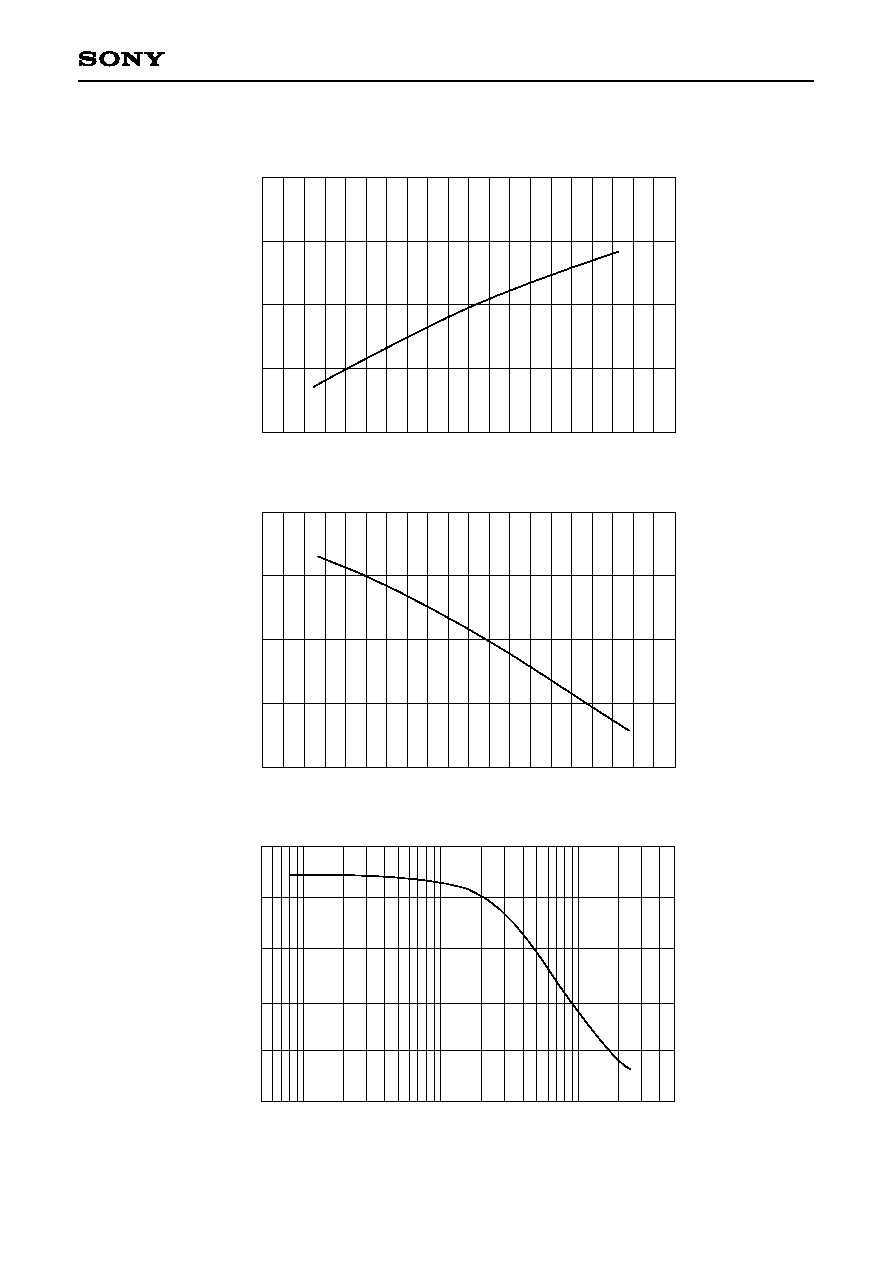

CXA1166K

Harmonic distortion vs. Input frequency response characteristics

Input frequency [MHz]

Harmonic distortion [dB]

0.1

1

10

100

1000

≠30

≠40

≠50

≠60

≠80

≠70

2nd harmonic distortion

3rd harmonic distortion

Clock frequency : 250MHz

Maximum conversion rate vs.

Temperature characteristics

CLK [MHz]

300

250

200

150

Ta -- Ambient temperature [∞C]

Error rate = 10

≠8

TPS

Input frequency = CLK frequency/4 ≠ 1kHz

16LSB or more error

75

125

25

≠

25

≠ 16 ≠

CXA1166K

Supply current vs. Temperature characteristics

Tc -- Case temperature [∞C]

Supply current [mA]

≠50

0

50

100

150

≠200

≠250

≠300

≠350

Error rate vs. Clock duty cycle

Error rate [TPS]

10≠

7

10≠

8

10≠

9

CLK duty cycle [%]

30

40

50

25

35

45

60

55

65

70

Input frequency = 125MHz, full-scale

Clock frequency = 250MHz

16LSB or more error

CLK frequency [MHz]

200

250

300

10≠

7

10≠

8

10≠

9

10≠

10

Error rate vs. Conversion rate

Error rate [TPS]

Input frequency = CLK frequency/4≠1kHz

16LSB or more error

≠ 17 ≠

CXA1166K

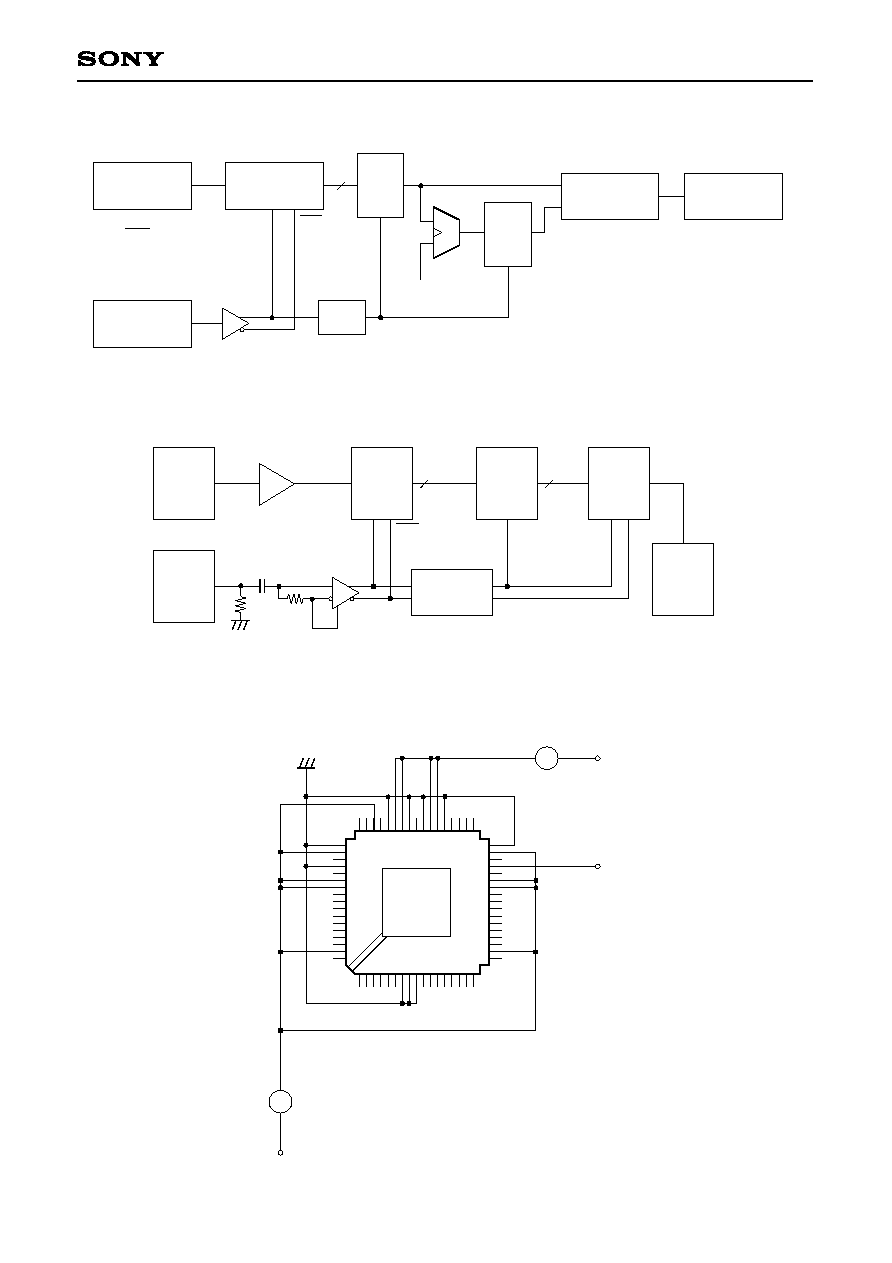

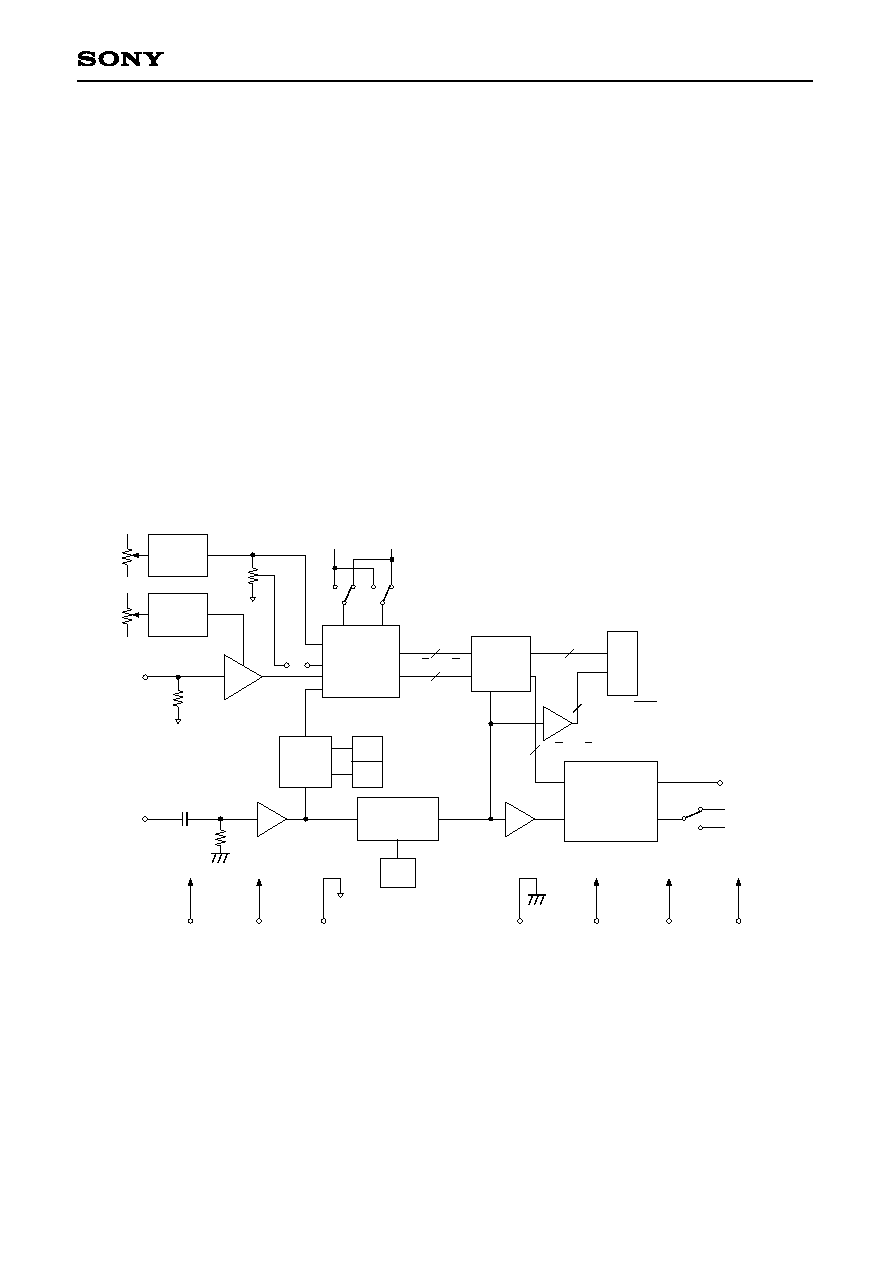

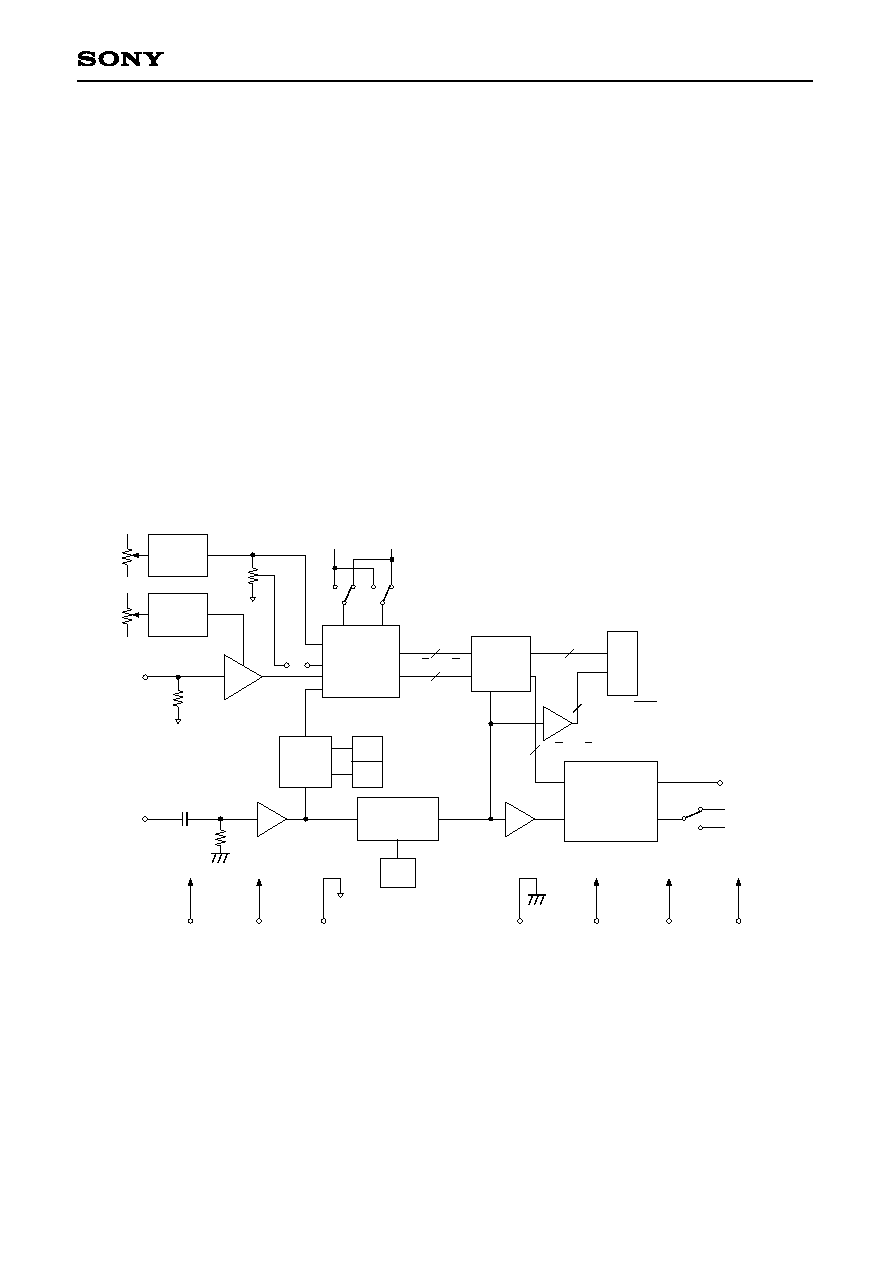

8-bit, 250 MSPS ADC Evaluation Board

The CXA1166K PCB is a tool for customers to evaluate the performance of the CXA1166K (8-bit, 250MHz,

high-speed A/D converter). In addition to indispensable features such as the reference voltage generator, this

tool equips the input voltage offset generator, clock decimator, output date latches, 10-bit high-speed DAC,

and 20-pin cable connector for digital outputs. This evaluation board is designed to facilitate evaluation.

Features

∑ Resolution: 8 bits

∑ Maximum conversion rate: 250 MSPS

∑ Supply voltage: ≠5.2V, ≠4.5V, ≠2.0V, +5.0V

∑ Clock level converter: Sine wave to ECL level signal

∑ Reference voltage adjustment circuit for A/D converter

∑ Built-in clock frequency decimation circuit: 1/1 to 1/128

Fig. 1. Block Diagram

DATA

LATCH

LINV MINV

V

RB

V

IN

CLK

CXA1166K

Vin

OFFSET

DECIMATOR

D/A

CONVERTER

SW3

CLK

SW4

SW5

L

H

AMP.IN

53

J1

DIGITAL OUT

(CONNECTOR)

2 (CLK.CLK)

CLK

D/A OUT

1/1 to 1/128

AGND

X

(≠ 2)

DELAY

SW2

SW1

CLK

51

H

L

INV

8 (D

7

to D

0

)

8 (D

7

to D

0

)

8 (D

7

to D

0

)

8 (D

7

to D

0

)

+ 5V (A)

≠ 5.2V (A)

≠ 5.2V (D)

≠ 2V (D)

DGND

0.1µ

≠ 4.5V (D)

SW6

V

R2

(2k)

V

R1

(2k)

V

R3

(2k)

V

RB

≠ 2V

≠ 18 ≠

CXA1166K

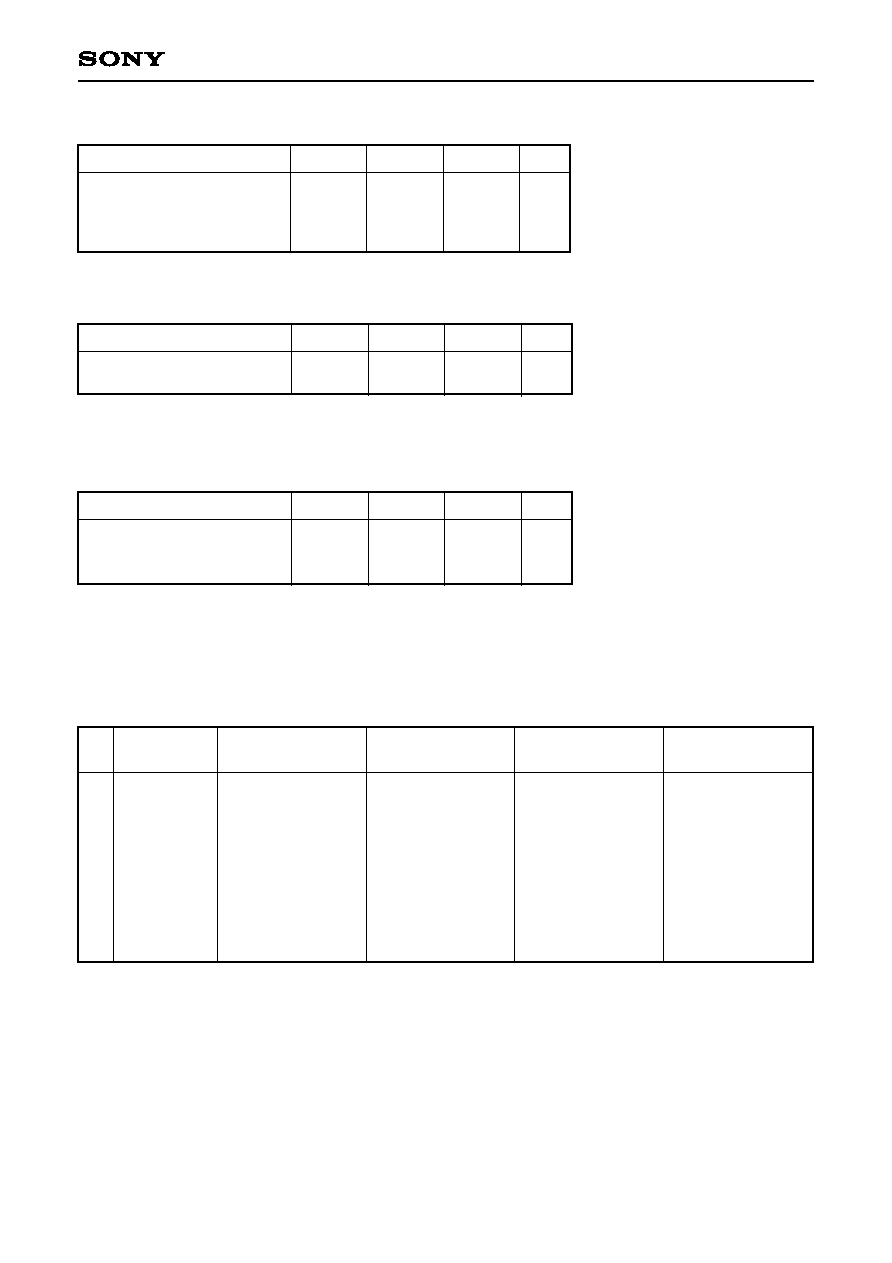

Supply Current

Item

Min.

Typ.

Max.

Unit

≠5.2V

+5.0V

≠4.5V

≠2.0

0.65

17

0.9

0.7

0.9

40

1.1

0.9

A

mA

A

A

Analog Input (AMP. IN)

Item

Min.

Typ.

Max.

Unit

Input voltage

(AMP.IN)

Input impedance

≠2.0

50

0

V

(

Adjustable with VR1)

Clock input (CLK)

Item

Min.

Typ.

Max.

Unit

Input voltage

(Peak to Peak)

Input impedance

2.0

50

Vp-p

Digital output (Digital OUT)

ECL level

Output Code Table

1: ECL High level, 0: ECL Low level

V

IN

1 1 1 ...... 1 1

1 1 1 ...... 1 0

:

:

1 0 0 ...... 0 0

0 1 1 ...... 1 1

:

:

0 0 0 ...... 0 1

0 0 0 ...... 0 0

0V

:

:

:

:

:

:

:

:

≠2V

1 0 0 ...... 0 0

1 0 0 ...... 0 1

:

:

1 1 1 ...... 1 1

0 0 0 ...... 0 0

:

:

0 1 1 ...... 1 0

0 1 1 ...... 1 1

0 1 1 ...... 1 1

0 1 1 ...... 1 0

:

:

0 0 0 ...... 0 0

1 1 1 ...... 1 1

:

:

1 0 0 ...... 0 1

1 0 0 ...... 0 0

0 0 0 ...... 0 0

0 0 0 ...... 0 1

:

:

0 1 1 ...... 1 1

1 0 0 ...... 0 0

:

:

1 1 1 ...... 1 0

1 1 1 ...... 1 1

MINV (SW5)

LINV (SW4)

0

1

0

0

1

0

1

1

≠ 19 ≠

CXA1166K

Fig. 2. Timing Diagram

N ≠ 1

N

N ≠ 2

N ≠ 1

N

Tdh

1.8ns

(Typ)

Tdh

1.8ns

(Typ)

N

N ≠ 2

N ≠ 4

N + 1

A/D input pin

(AMP. IN)

PCB input pin

A/D clock

A/D output

PCB output pin

(For 1/1 decimation)

PCB output pin

(For 1/1 decimation)

PCB output pin

(For 1/2 decimation)

PCB output pin

(For 1/2 decimation)

Vin

CLK

CLK

CLK

D7 to D0

CLKN

CLK

D7 to D0

D7 to D0

CLKN

CLK

D7 to D0

N + 2

N

Adjustment Methods and Notes on Operation

1) V

IN

Offset (VR1)

The volume to adjust the AMP. IN signal range (0V center assumed) with the A/D converter input range.

2) A/D Full Scale (VR2)

The volume to adjust A/D converter V

RB

voltage (≠2V typ.).

3) Linearity (VR3)

The volume to adjust the VRM (linearity) voltage by shorting the J1.

≠ 20 ≠

CXA1166K

4) D/A Full Scale (VR4)

The volume to adjust the bottom of D/A output full scale voltage (≠1V typ.)

5) SW1 and SW2

Selection switches to adjust the clock delay. These switches enable clock delay to be stepped to any one of

128 settings (binary code of "0000000" to "1111111") through binary input. Approximately 163ps is delayed

per one step. Normal evaluation requires the binary code of "0000000" (all of OFF), so that these switches

are not mounted for shipment.

6) SW3 (Decimation)

The switch to select clock frequency decimation. Selection settings are as follows.

H = ECL High level ; L = ECL Low level

7) SW4

The switch for LINV High/Low.

8) SW5

The switch for MINV High/Low.

9) SW6 (D/A INV)

The switch for D/A converter output inversion.

SW3

3

2

Decimation

ratio

L

L

L

L

H

H

H

H

L

L

H

H

L

L

H

H

L

H

L

H

L

H

L

H

1/1

1/2

1/4

1/8

1/16

1/32

1/64

1/128

1

≠ 21 ≠

CXA1166K

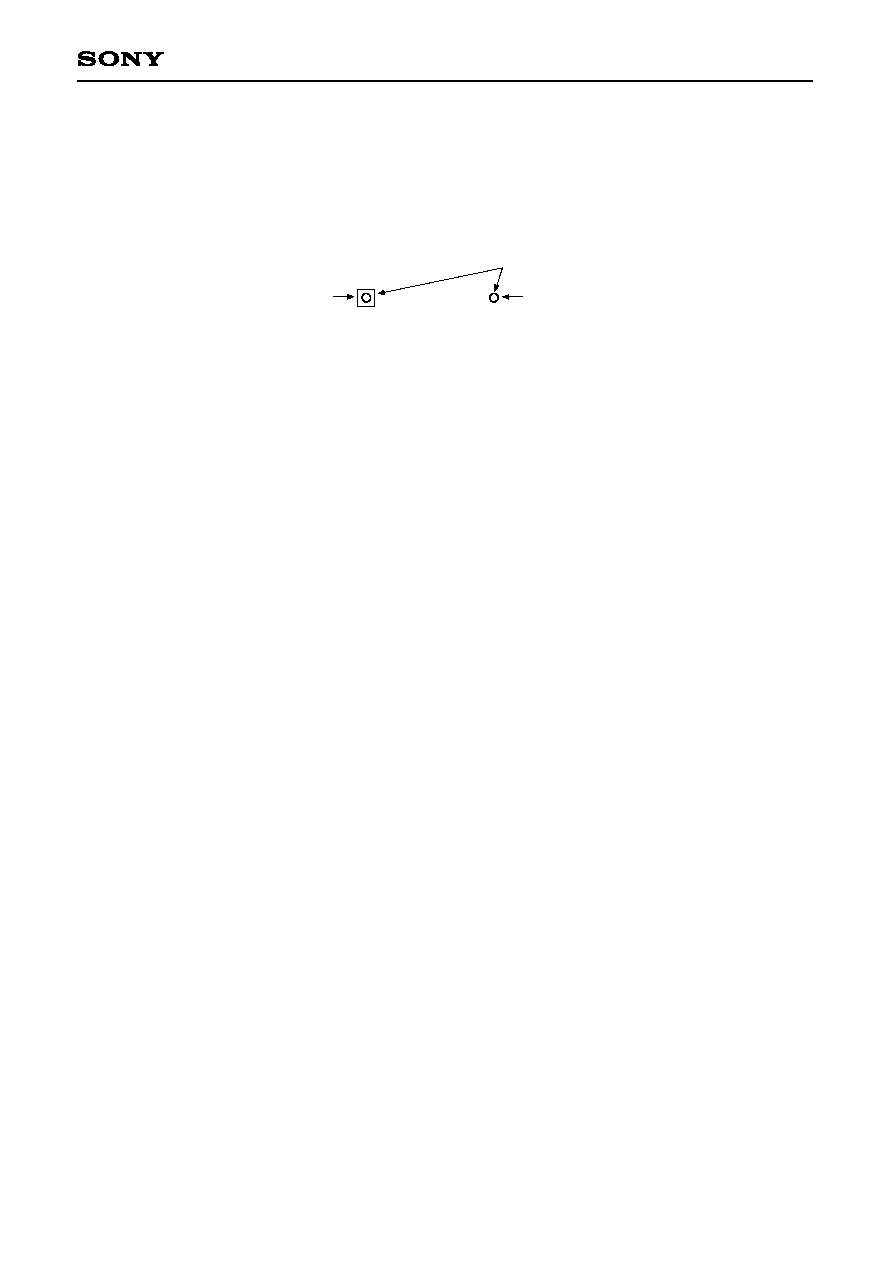

10) The waveform monitoring pins P6 through P39 are designed to make connection to GND easily in order to

reduce distortion when monitoring the waveform with an oscilloscope. As shown in the diagram below, the

distance between the measuring point and GND is 300mil, and each is equipped with a through hole of

1.2mm. When a Tektronix ground chip (part No. 013-1185-00) is mounted on the tip of a probe, the

signal ≠ GND positions match.

11) D/A converter (IC9) input data (waveform monitoring pins P28 to P35) are the negative logic signals of the

decimated A/D converter outputs. Those are inverted again in the D/A converter so that the direction

(rise/fall) of reproduced waveform can agree with the A/D input signal's.

12) In order to maintain the accuracy of the reproduced waveform (waveform from A/D to D/A), set the

decimator such that the clock frequency of the D/A converter (IC9: CX20201A-1) is less than 100MHz.

13) The input bandwidth weighs with the design of this PCB analog input circuit. Therefore, the SNR (signal-to-

noise ratio) should be less significant. The input circuit example to improve the SNR is shown in Fig.4. See

the measured data in Fig.s 6 to 8 for the SNR and the input circuit characteristics.

14) The part number of the digital output connector mounted on the PCB is KEL 8830E-020-170S. A

corresponding connector and cable assembly is JUNKOSHA KB0020MCG50B1.

1.2mm

Monitoring point

GND

Fig. 3.

≠ 22 ≠

CXA1166K

From offset circuit

V

IN2

V

IN2

V

IN1

V

IN1

560

240

68

30

120

CLC409

2

3

6

3pF

5pF

AGND

AGND

V

RB

(≠ 2V)

AMP. IN

Fig. 4. Example of SNR Improvement Circuit

≠ 23 ≠

CXA1166K

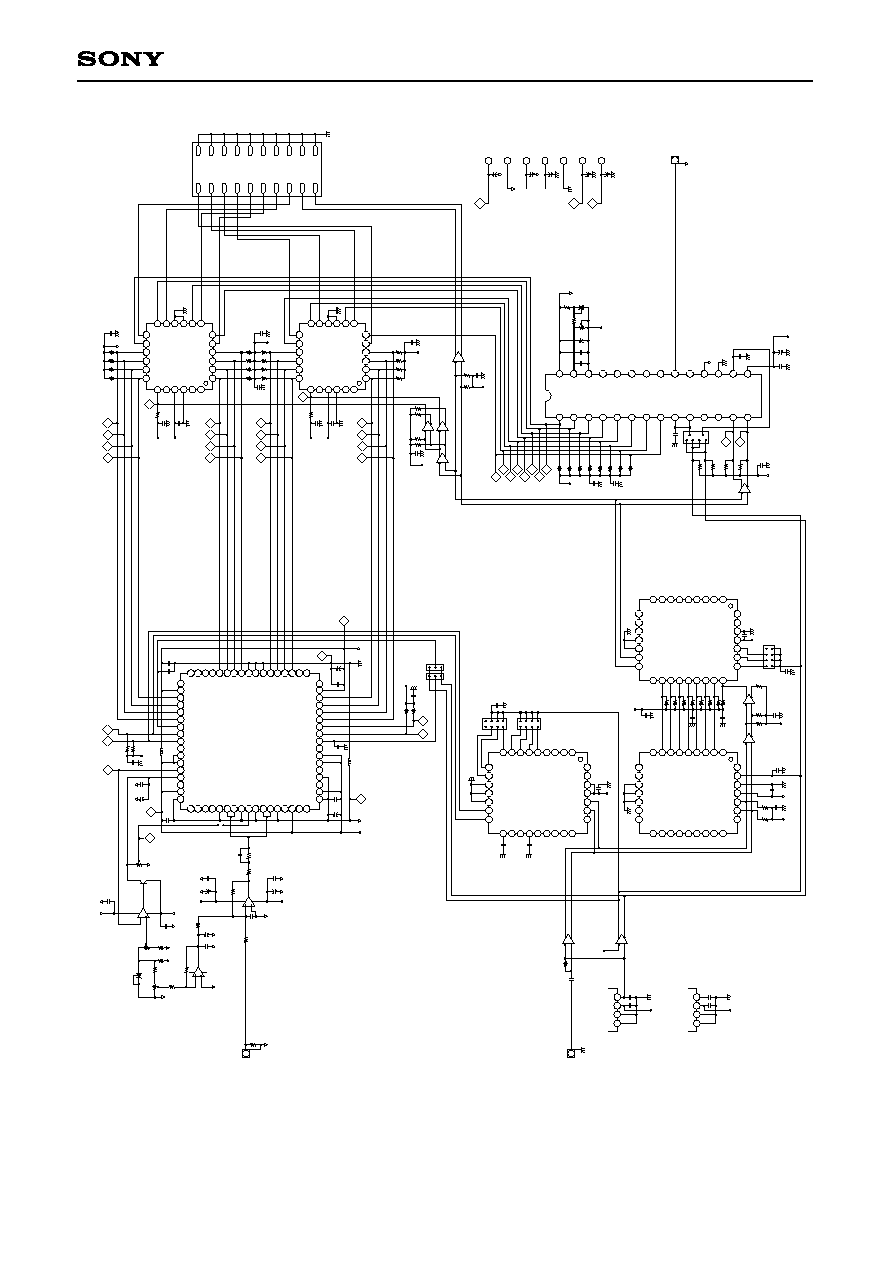

Fig. 5. Schematic Diagram

: CHIP CAPACITOR

R3

510

VR1

2k

R5

240

R6

1.3k

≠ 5.2V

(A)

AGND

6

5

8

7

4

2

3

7

6

4

AGND

AGND

AGND

≠ 5.2V

(A)

R9

560

R10

24

R11

10

C15

10p

C14

0.1µ

C13

1µ

C12

0.1µ

C11

1µ

AGND

AGND

+ 5.2V

(A)

C89

3P

R7

240

AGND

AGND

C8

3.3µ

C7

0.1µ

2

3

8

1

4

AGND

R4

22k

R2

11k

AGND

R8

1k

AGND

≠ 5.2V

(A)

C9

0.1µ

AGND

C10

0.1µ

AGND

≠ 5V

(A)

P5

P6

P7

P4

C22

1µ

AGND

AGND

C23

0.1µ

C21

0.1µ

L2

R13

51

R12

51

C39

0.1µ

GND

≠ 2V

(D)

FERRITE

BEAD

CLKN

CLK

V

RBS

J1

P1

VRT

Q1

2SA970

TL4558

IC12_2

Linearity

VR2

2k

IC13

TL431CP

TL4558

IC12_1

CLC404AJP

IC11

C18

1µ

C19

0.1µ

AGND

P2

AGND

≠ 5.2V

(A)

L1

FERRITE

BEAD

C34

0.1µ

P9

DGND

C37

1µ

C36

0.1µ

DGND

≠ 5.2V

(D)

P8

DV

EE

≠ 5.2V

(D)

R28

51

R27

51

P10

C35

0.1µ

DGND

≠ 2V (D)

P11

OR

ORN

DGND

C26

0.1µ

DGND

DGND

SW1

DELAY ADJ.

C17

0.01µ

C16

1000p

GND

GND

C24

0.1µ

≠ 5.2V

(D)

DGND

18

16

DGND

C2

0.1µ

≠ 4.5V

(D)

C3

0.1µ

9

21

22

10

IC1

CXB1103Q

V

CC

V

CC

A

V

EE

V

BB

≠ 2V

(D)

28

R8

51

C1

0.1µ

DGND

C5

0.1µ

≠ 4.5V

(D)

C4

0.1µ

9

21

22

10

IC5

CXB1103Q

V

CC

V

CC

A

V

EE

V

BB

IC1_2

IC1_1

GND

C26

0.1µ

DGND

R23

51

C25

0.1µ

GND

C27

0.1µ

R22

51

≠ 4.5V

(D)

≠ 2V

(D)

24

23

12

11

IC1_4

35

IC1_3

R24

51

R25

51

GND

C28

0.1µ

≠ 2V

(D)

GND

R14

51

C31

0.1µ

DGND

C33

0.1µ

≠ 2V

(D)

R15

51

R20

51

R19

51

R18

51

R17

51

R16

51

R21

51

DGND

C32

0.1µ

DGND

C30

0.1µ

R26

51

DGND

≠ 4.5V

(D)

DGND

C29

0.1µ

SW3

DECIMATION

IC4

CXB1144Q

26

27

28

29

30

31

32

S0

S1

S2

V

EE

V

CC

A

NC

NC

2

3

4

5

6

7

8

9

1

DIA

DIB

DIC

DID

DIE

DIF

DIG

DIH

LEN1

17

18

19

20

21

22

23

24

25

DOA

DOB

DOC

DOD

DOE

DOF

DOG

DOH

MR

10

11

12

13

14

15

16

QON

QO

V

CC

A

V

CC

QI

LEN2

IC2

CXB1136Q

26

27

28

29

30

31

32

V

BB

C

V

EE

V

CC

A

S1

S2

2

3

4

5

6

7

8

9

1

CIMN

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

17

18

19

20

21

22

23

24

25

D0

D1

D2

D3

D4

D5

D6

D7

NC

10

11

12

13

14

15

16

MR

NC

V

CC

A

V

CC

V

CC

A

COUT

IC3

CXB1159Q

26

27

28

29

30

31

32

V

REF

DINB

DIN

V

EE

V

EE

F0

F1

2

3

4

5

6

7

8

9

1

F2

F3

F4

F5

C0

C1

C2

C3

C4

17

18

19

20

21

22

23

24

25

DINPB

DINP

SW

MR

RBIAS

CBIAS

DOUTP

DOUTPB

CAP

10

11

12

13

14

15

16

DOUTB

DOUT

DGND

GND

GND

C6

C5

SW4

SW5

LINV

MINV

INV

NORM

C38

0.1µ

C70

0.1µ

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

40

39

38

37

36

35

34

31

32

33

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

2

3

4

5

6

7

8

9

68

67

63

64

65

66

61

62

1

AV

EE

NC

AGND

V

RT

V

RTS

AV

EE

AV

EE

NC

LINV

OR

D0

D1

DV

EE

NC

AV

EE

NC

V

RB

V

RBS

AV

EE

AV

EE

NC

CLK

CLKN

MINV

D7

D6

DV

EE

NC

NC

NC

NC

NC

D5

D4

DGND1

DGND2

DGND2

D3

D2

NC

NC

NC

NC

NC

NC

AGND

V

IN2

V

IN2

AGND

V

RM

AGND

V

IN1

V

IN1

AGND

NC

AV

EE

NC

NC

IC6

CXA1166K

C41

0.1µ

DGND

≠ 2V

(D)

R33

51

DGND

C42

0.1µ

R34

51

R35

51

R36

51

R37

51

R38

51

R39

51

R40

51

≠ 2V

(D)

≠ 4.5V

(D)

C44

0.1µ

DGND

R62

51

C45

0.1µ

DGND

P38

CLKA

P27

D7N

P26

D7

P25

D6N

P24

D6

P23

D5N

P22

D5

P21

D4N

P20

D4

P19

D3N

P18

D3

P17

D2N

P16

D2

≠ 2V

(D)

DGND

C40

0.1µ

≠ 2V

(D)

≠ 4.5V

(D)

C46

0.1µ

DGND

R61

51

C47

0.1µ

DGND

P39

CLKB

P15

D1N

P14

D1

P13

D0N

P12

D0

R29

51

R30

51

R31

51

R32

51

R41

51

≠ 2V

(D)

DGND

C43

0.1µ

R44

51

R42

51

R43

51

2

1

8

IC5_4

18

17

16

IC5_2

DGND

C48

0.1µ

15

20

19

14

13

≠ 2V

(D)

R55

51

R56

51

R58

51

R57

51

IC5_3

23

24

11

12

IC5_1

≠ 2V

(D)

DGND

C49

0.1µ

R60

51

R59

51

7

≠ 2V

(D)

DGND

C50

0.1µ

R46

51

R47

51

R48

51

R49

51

R50

51

R51

51

R52

51

DGND

C51

0.1µ

D1

D3

D5

D7

D0

D2

D4

D6

P35

P33

P31

P29

P34

P32

P30

P28

R45

51

DGND

DGND

36

IC5_5

DGND

C60

0.1µ

SW6

INV

R66

51

INV

NORM

CLKN

R65

51

P37

CLK

P36

R54

51

R53

51

DGND

R63

1k

R64

270

≠ 5.2V

(A)

AGND

C57

0.1µ

TL431CP

IC10

DGND

20

DGND

19

18

DGND

17

CLK

16

DGND

15

D7

14

DGND

13

D6

12

DGND

11

D5

10

DGND

9D

4

8

DGND

7D

3

6

DGND

5D

2

4

DGND

3D

1

2

DGND

1D

0

(LSB)

Digital OUT

C58

0.1µ

C59

1µ

VR4

2k

AGND

DGND

DGND

C55

0.1µ

DGND

C53

0.1µ

DGND

≠ 5.2V

(D)

C54

1µ

IC7

CXB1109Q

2

3

4

5

6

1

19

20

21

22

23

24

7

8

9

10

11

12

17

18

13

14

15

16

IC8

CXB1109Q

D3

D4

Q4

2

3

4

5

6

1

19

20

21

22

23

24

MR

V

BB

V

CC

A

V

EE

CB

CA

Q3

V

CC

V

CC

A

Q2

7

8

9

10

11

12

P42

+ 5V

P41

DV

EE

( ≠ 4.5)

P40

VTT

AGND

DGND

DGND

C63

33µ

C64

33µ

AGND

C65

33µ

AGND

DGND

C62

33µ

DGND

C61

33µ

+ 5V (A)

AGND

≠ 5.2V (A)

≠ 5.2V (D)

DGND

≠ 4.5V (D)

≠ 2V (D)

IC9

CXA20201

2

3

4

5

6

7

8

9

1

10

11

12

13

14

D1

D2

D3

D4

D5

D6

D7

D8

D9

LSB

NC

NC

CLK

AGND

V

REF

AV

EE

NC

NC

NC

NC

NC

OUT

NC

AGND

DGND

INV

DV

EE

26

27

28

17

18

19

20

21

22

23

24

25

15

16

AGND

D/A OUT

AGND

AMP. IN

R1

68

CLK

DGND

CXA1166K EVALUATION BOARD

C52

0.1µ

SW2

DELAY ADJ.

D7N

D6N

D5N

D4N

D3N

D2N

ORN

D0N

D1N

COUTN

CN

QIN

CLKN

17

18

13

14

15

16

D2

D1

Q1

D3N

D4N

Q4N

Q3M

Q2M

Q1N

D1N

D2N

D3

D4

Q4

MR

V

BB

V

CC

A

V

EE

CB

CA

Q3

V

CC

V

CC

A

Q2

D2

D1

Q1

D3N

D4N

Q4N

Q3M

Q2M

Q1N

D1N

D2N

CLKN

Full Scale

VR3

1k

45

Offset

17

17

15

46

AV

EE

≠ 5.2V

≠ 2V

(D)

≠ 24 ≠

CXA1166K

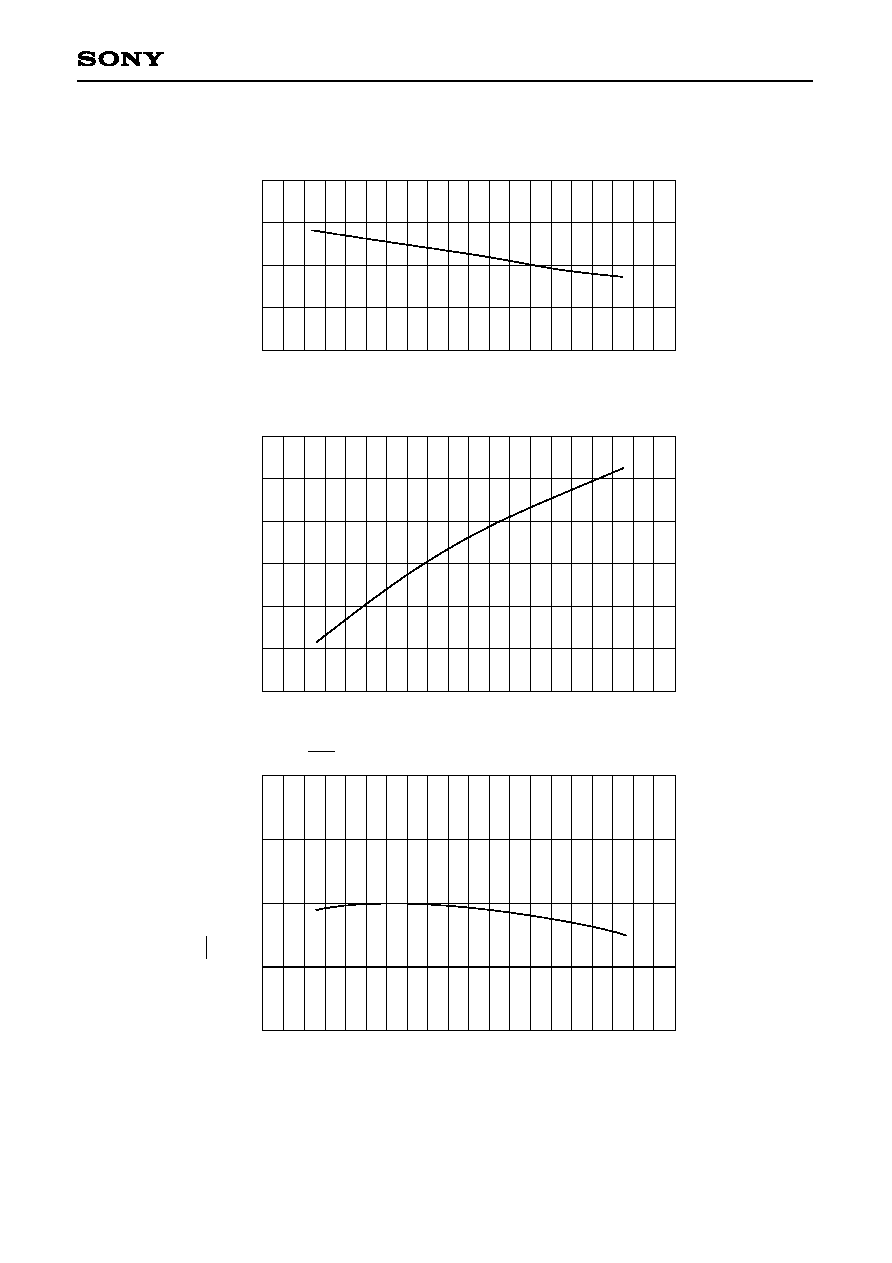

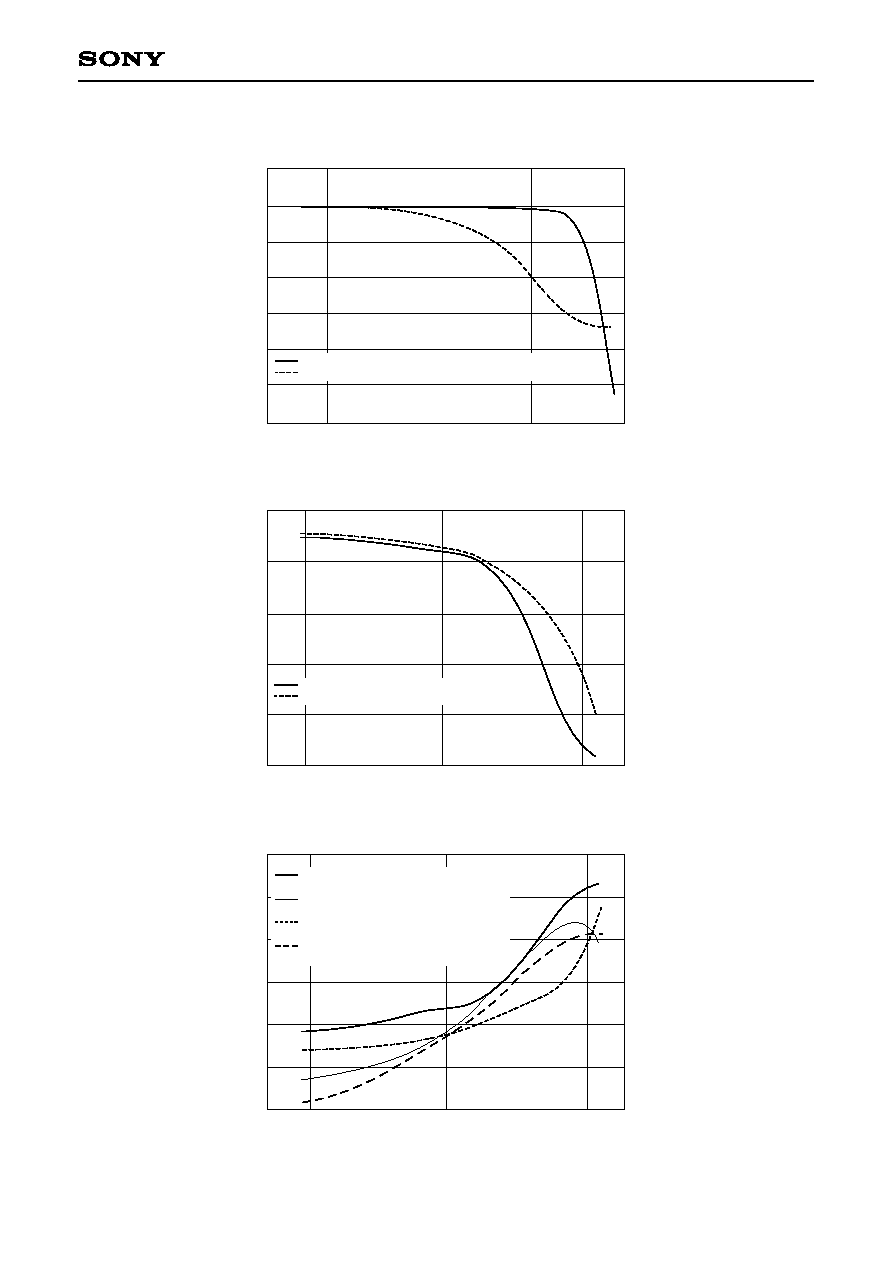

Characteristics

Fig.8. 2nd, 3rd Harmonic distortion vs. Input frequency

Fig.7. SNR vs. Input frequency

Fig.6. Gain vs. Input frequency

Input frequency [MHz]

Gain [dB]

≠ 12

≠ 10

≠ 8

≠ 6

≠ 4

≠ 2

0

2

5

10

100

300

Fig.5. CXA1166K PCB Schematic Diagram

Fig.4. Example of SNR Improvement Circuit

Input frequency [MHz]

SNR [dB]

25

30

35

40

45

50

1

10

200

100

Fig.5. CXA1166K PCB Schematic Diagram

Fig.4. Example of SNR Improvement Circuit

Input frequency [MHz]

2nd, 3rd Harmonic distortion [dB]

≠ 80

≠ 60

≠ 50

≠ 40

≠ 30

≠ 20

1

10

200

100

≠ 70

Fig.5. Schematic Diagram

(2nd Harmonic distortion)

Fig.5. Schematic Diagram

(3rd Harmonic distortion)

Fig.4. Example of SNR Improvement

Circuit (2nd Harmonic distortion)

Fig.4. Example of SNR Improvement

Circuit (3rd Harmonic distortion)

≠ 25 ≠

CXA1166K

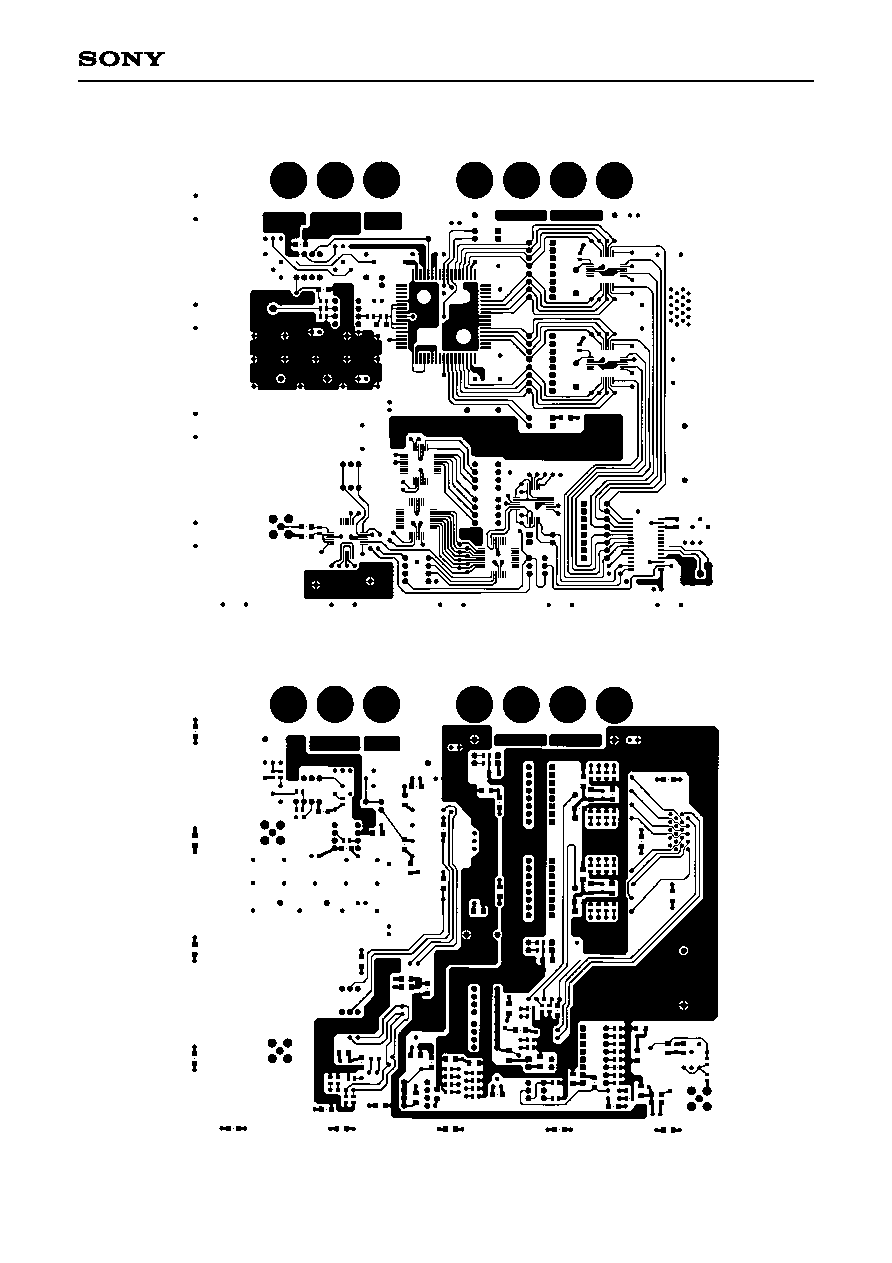

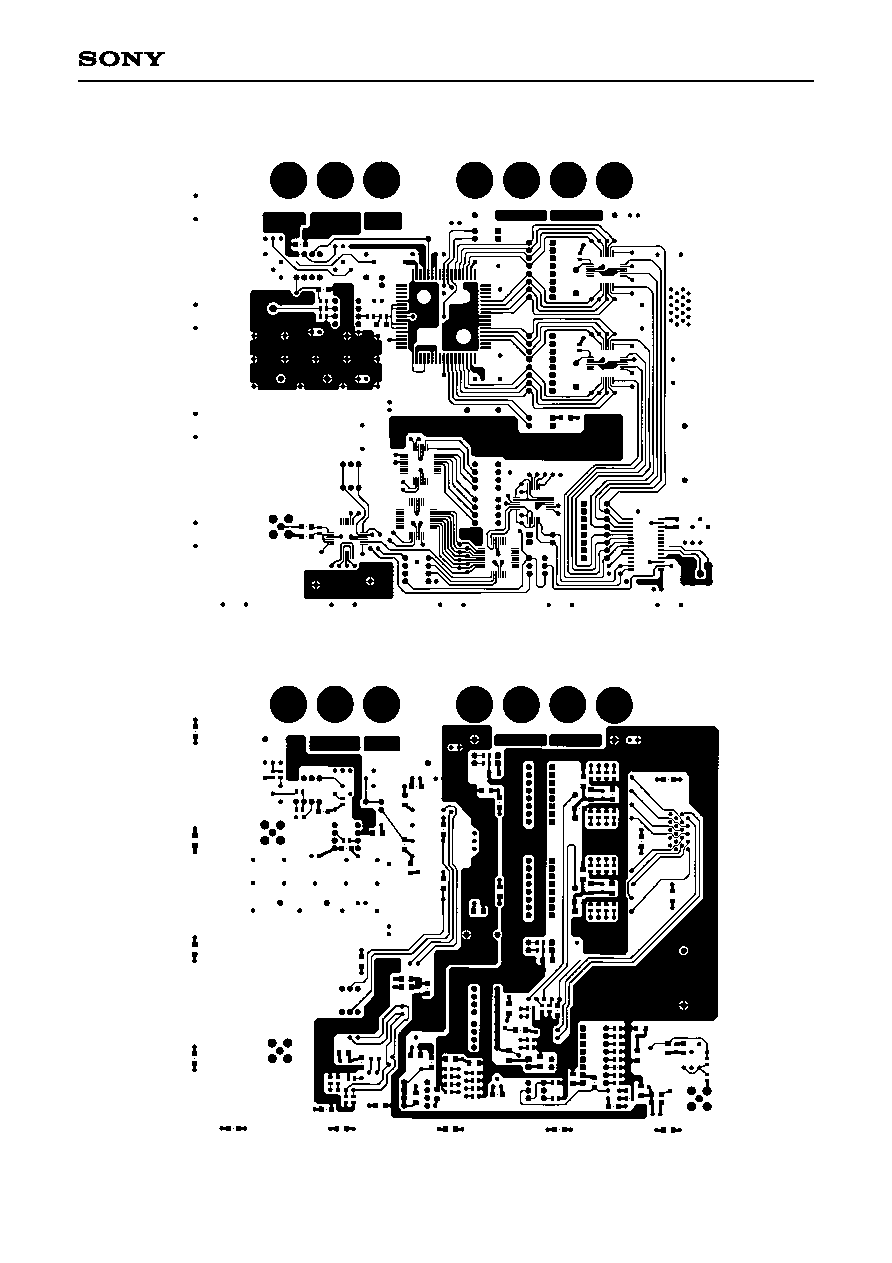

Parts Layout

Component side

Soldering side

≠ 26 ≠

CXA1166K

Component side

Soldering side

Printed Pattern

≠ 27 ≠

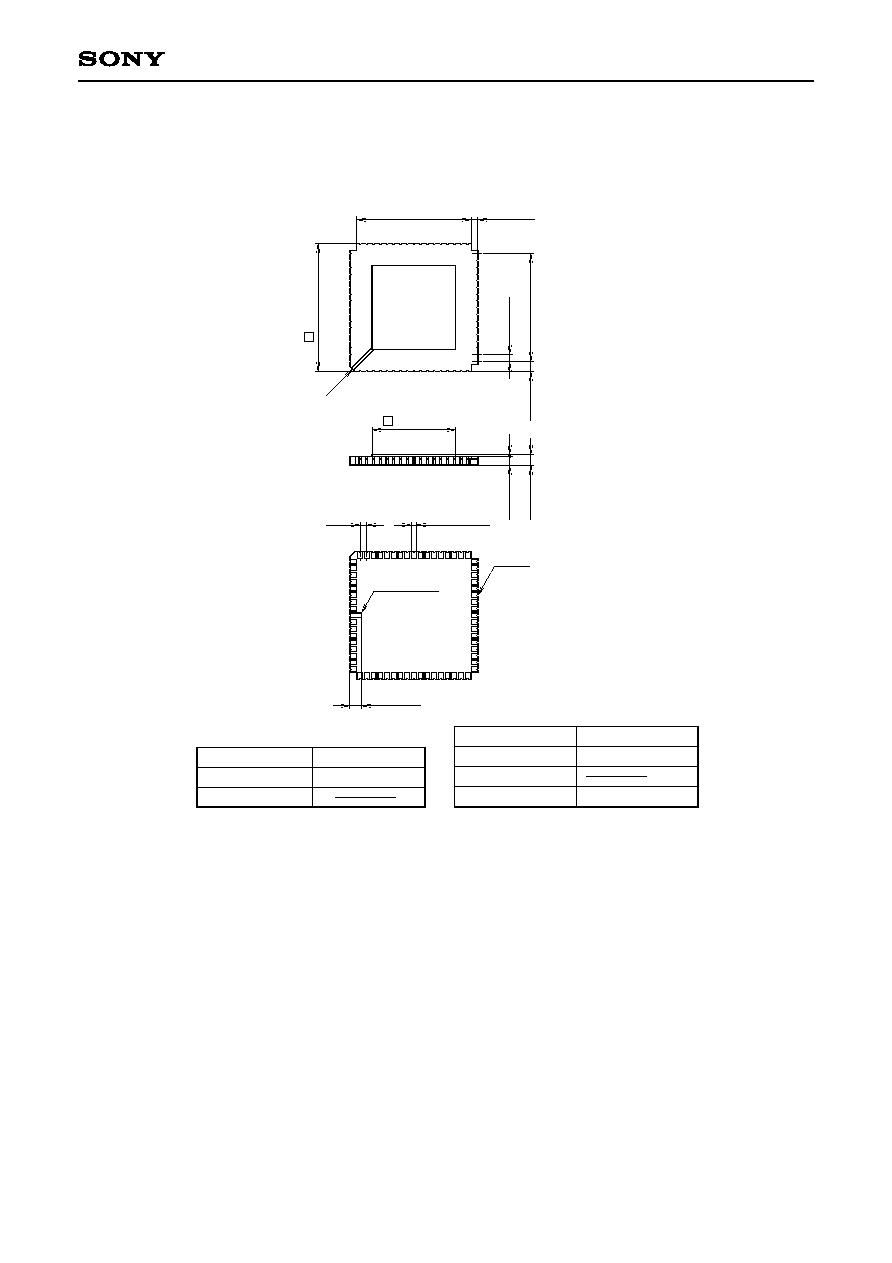

CXA1166K

GND layer (inner layer)

V

EE

layer (inner layer)

≠ 28 ≠

CXA1166K

Package Outline

Unit: mm

SONY CODE

EIAJ CODE

JEDEC CODE

68PIN LCC (CERAMIC)

21.59 ± 0.2

1.27 ± 0.2

20.32 ±

0.1

1.27 ±

0.1

1.9 ±

0.25

24.13

+ 0.38 ≠ 0.25

C1

15.85 ± 0.2

1.65 ±

0.18

1.95 ±

0.25

0.3

1.27

0.915 ± 0.07

R0.2

PIN NO.1

INDEX

2.16 ± 0.25

PACKAGE STRUCTURE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE WEIGHT

GOLD PLATING

3.7g

LCC-68C-01

QFN068-C-S950-A

CERAMIC