| –≠–Ľ–Ķ–ļ—ā—Ä–ĺ–Ĺ–Ĺ—č–Ļ –ļ–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā: CXA1372BS | –°–ļ–į—á–į—ā—Ć:  PDF PDF  ZIP ZIP |

Description

The CXA1372BQ/BS is a bipolar IC developed for

RF signal processing (focus OK, mirror, defect

detection, EFM comparator) and various servo

control.

Features

∑ Dual Ī5V and single 5V power supplies

∑ Low power consumption

∑ Fewer external parts

∑ Disc defect countermeasure circuit

∑ Fully compatible with the CXA1182 for microcomputer

software

Functions

∑ Auto asymmetry control

∑ Focus OK detection circuit

∑ Mirror detection circuit

∑ Defect detection, countermeasure circuit

∑ EFM comparator

∑ Focus servo control

∑ Tracking servo control

∑ Sled servo control

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings (Ta = 25įC)

∑ Supply voltage

V

CC

≠ V

EE

12

V

∑ Operating temperature

Topr

≠20 to +75

įC

∑ Storage temperature

Tstg

≠65 to +150

įC

∑ Allowable power dissipation

P

D

457 (CXA1372BQ)

mW

833 (CXA1372BS)

mW

Recommended Operating Conditions

V

CC

≠ V

EE

3.6 to 11

V

V

CC

≠ D

GND

3.6 to 5.5

V

≠ 1 ≠

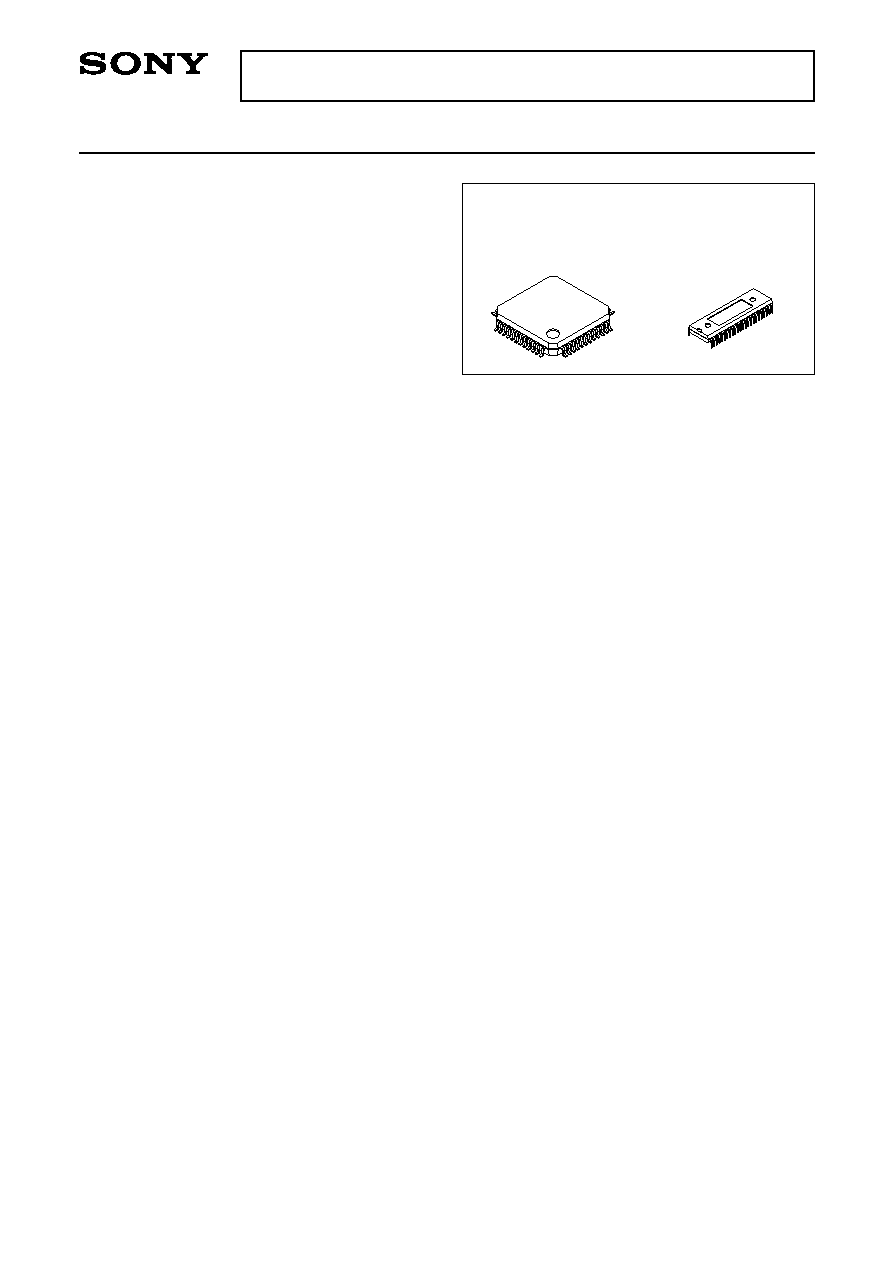

CXA1372BQ/BS

E95927A67-PS

RF Signal Processing Servo Amplifier for CD Player

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXA1372BQ

48 pin QFP (Plastic)

CXA1372BS

48 pin SDIP (Plastic)

≠ 2 ≠

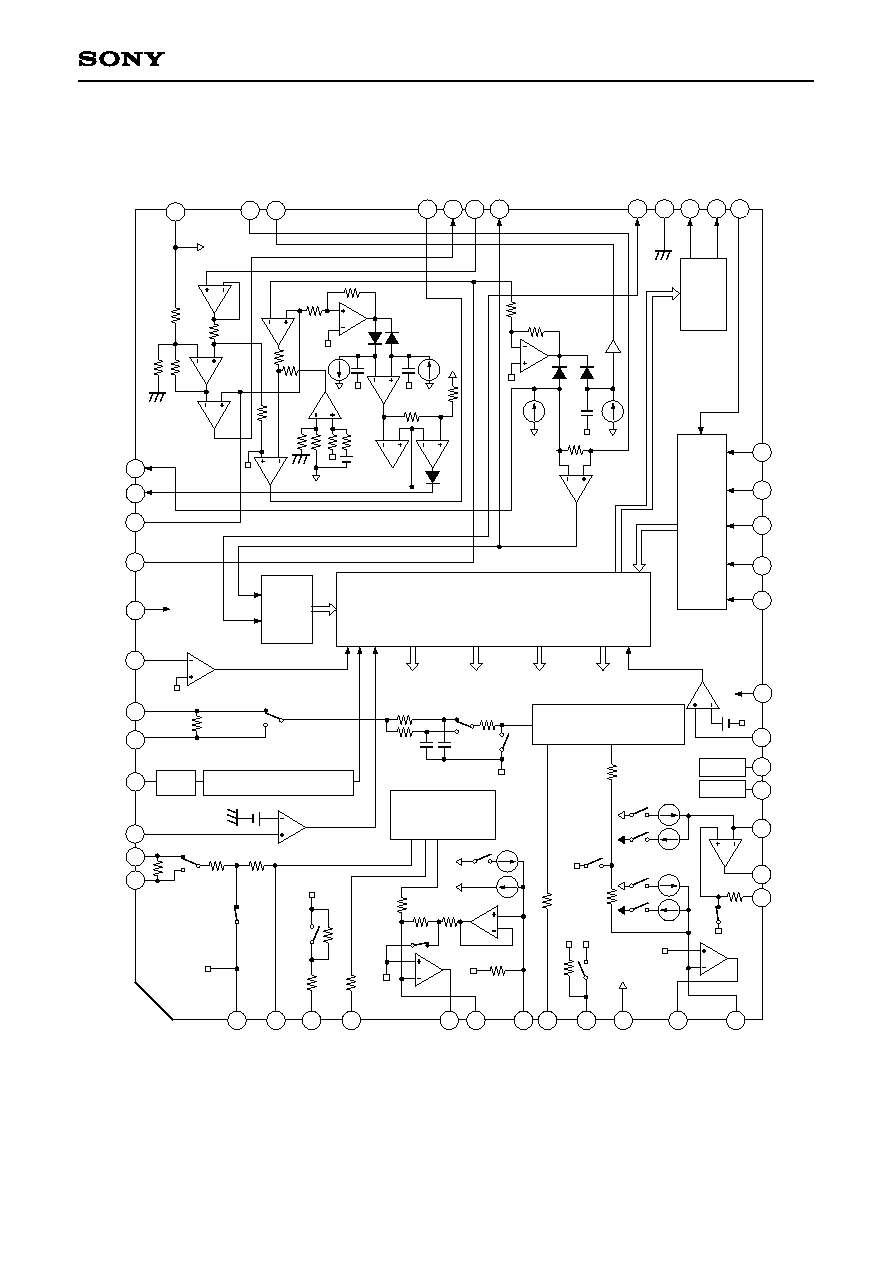

CXA1372BQ/BS

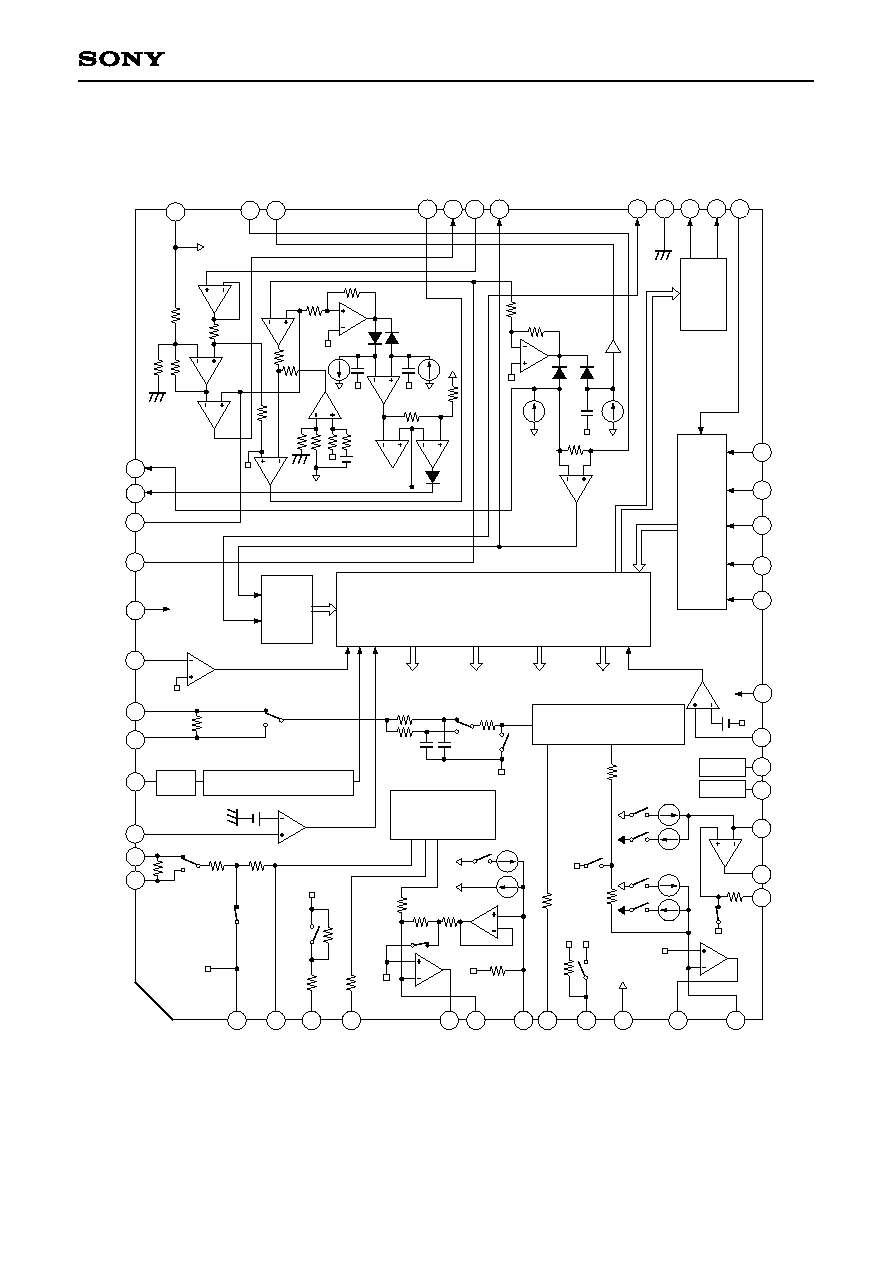

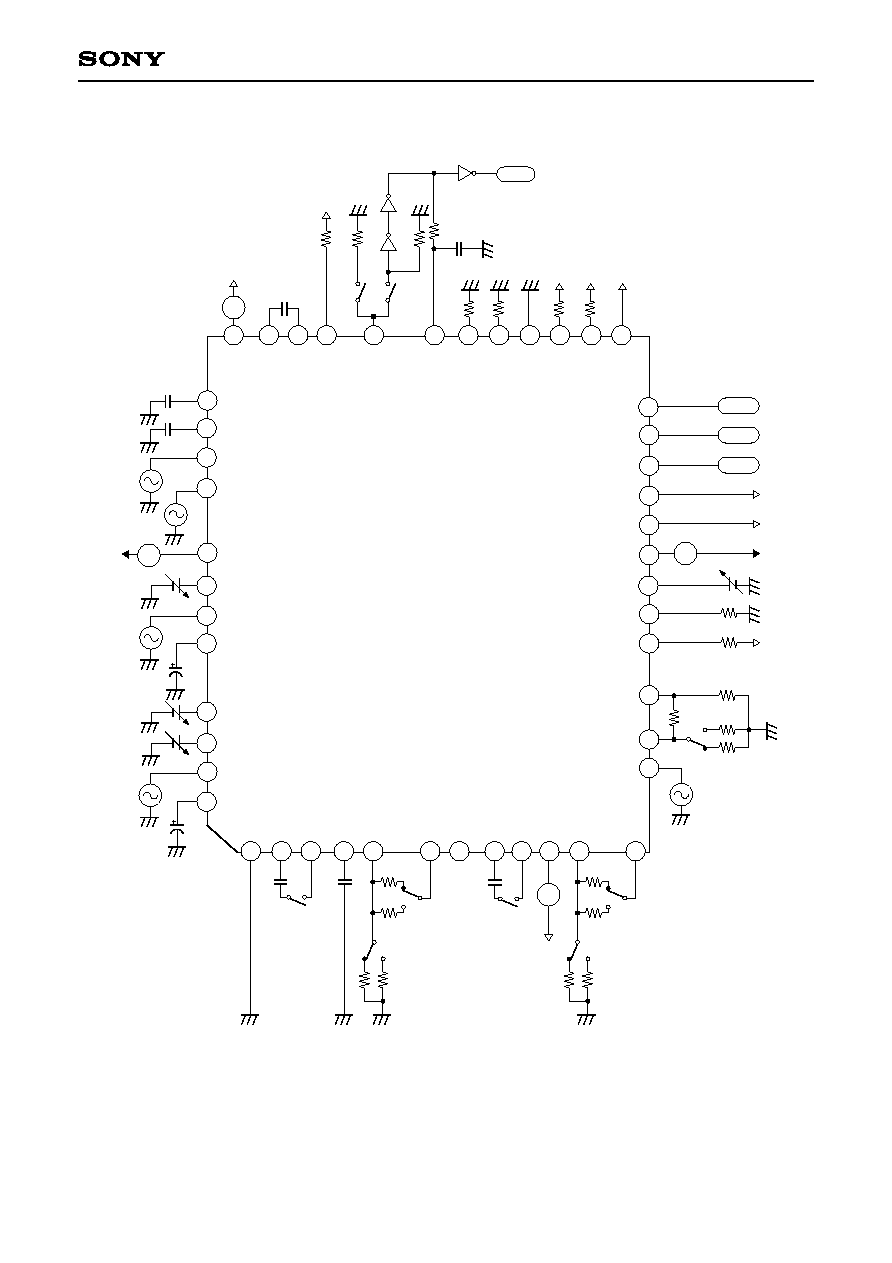

Block Diagram

35

34

30

31

32

33

25

26

27

28

29

∑ IIL

∑ TTL

20

21

22

23

24

19

13

14

15

16

17

18

∑ I SET

∑ F SET

TM6

TM5

TM4

TM3

TM7

12

11

10

9

8

7

6

5

4

3

2

1

FS3

FS2

FS1

∑ FOCUS

PHASE

COMPENSATION

48

47

46

45

44

43

42

41

40

39

37

DFCT

∑ BPF

∑ WINDOW COMPARATOR

DFCT

TG1

∑ TRACKING

PHASE COMPENSATION

∑ IIL DATA REGISTER

∑ OUTPUT DECODER

∑ INPUT SHIFT REGISTER

∑ ADDRESS DECODER

∑ FS1 to 4

∑ TG1 to 2

∑ TM1 to 7

∑ PS1 to 3

∑ TTL

∑ IIL

DVcc

CC2

CC1

FOK

EFM

ASY

DFCT

MIRR

DGND

SENS

C. OUT

XRST

DATA

XLT

CLK

LOCK

DIRC

AV

EE

SSTOP

ISET

FSET

SL≠

SLO

SL+

TA≠

TAO

AV

CC

TG2

TGU

SRCH

FE≠

FEO

FLB

FS3

FGD

VC

FDFCT

FE

FZC

ATSC

TDFCT

TE

TZC

DV

EE

RFO

RFI

CP

CB

36

TM1

FS4

TG2

TM2

∑ TTL

∑ IIL

38

≠ 3 ≠

CXA1372BQ/BS

Pin Configuration

CXA1372BQ

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

40

39

38

37

36

35

34

31

32

33

41

42

43

44

45

46

47

48

1

CB

CP

RFI

RFO

DV

EE

TZC

TE

TDFCT

ATSC

FZC

FE

FDFCT

DATA

XLT

CLK

LOCK

DIRC

AV

EE

SSTOP

ISET

FSET

SL≠

SLO

SL+

VC

FGD

FS3

FLB

FEO

FE≠

SRCH

TGU

TG2

AVcc

TAO

TA≠

DVcc

CC2

CC1

FOK

EFM

ASY

DFCT

MIRR

DGND

SENS

C. OUT

XRST

CXA1372BQ

CXA1372BS

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

40

39

38

37

36

35

34

31

32

33

41

42

43

44

45

46

47

48

1

TE

TDFCT

ATSC

TZC

FE

FDFCT

VC

FGD

FS3

FLB

FEO

FE≠

SRCH

TGU

TG2

AVcc

TAO

TA≠

SL+

SLO

SL≠

FSET

ISET

SSTOP

TZC

DV

EE

RFO

RFI

CP

CB

DVcc

CC2

CC1

FOK

EFM

ASY

DFCT

MIRR

DGND

SENS

C. OUT

XRST

DATA

XLT

CLK

LOCK

DIRC

AV

EE

CXA1372BS

≠ 4 ≠

CXA1372BQ/BS

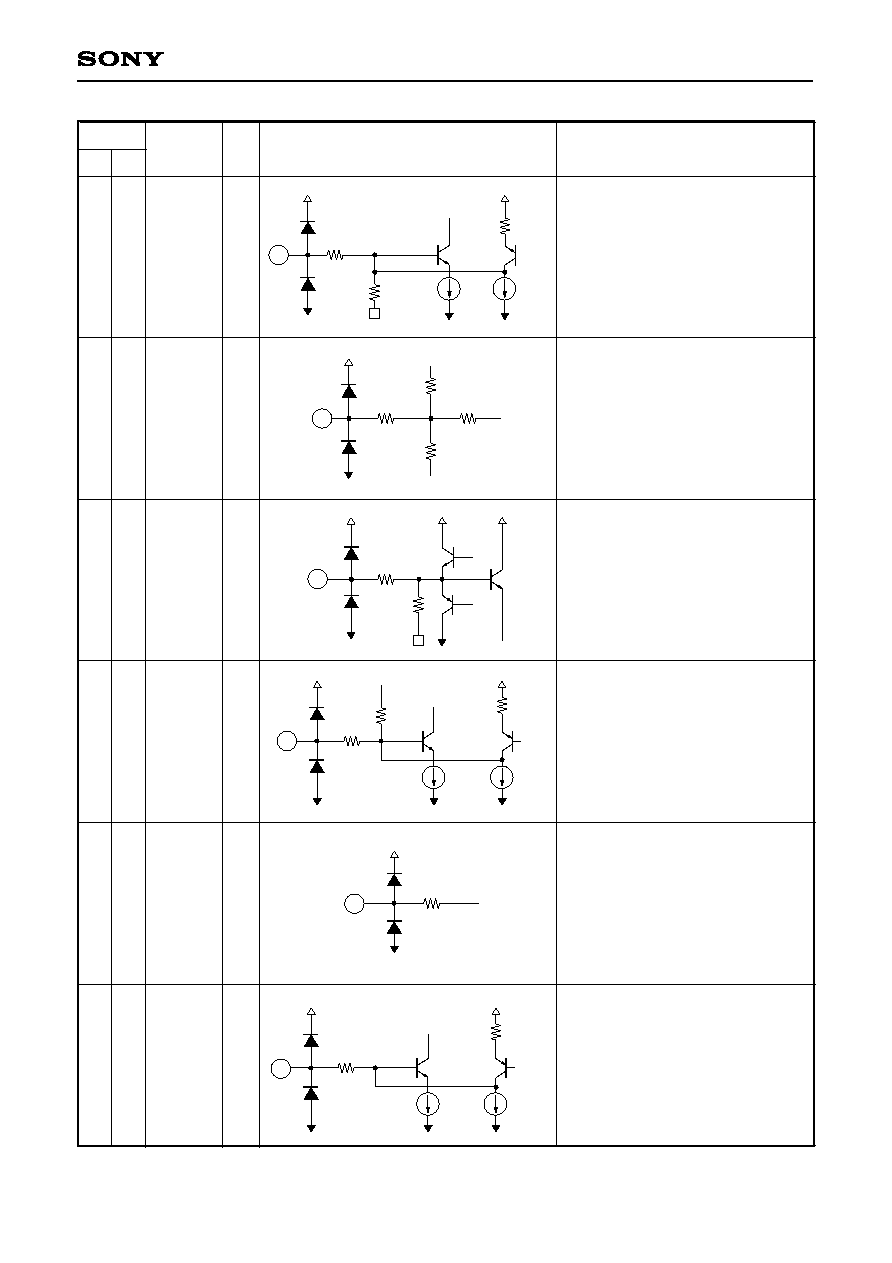

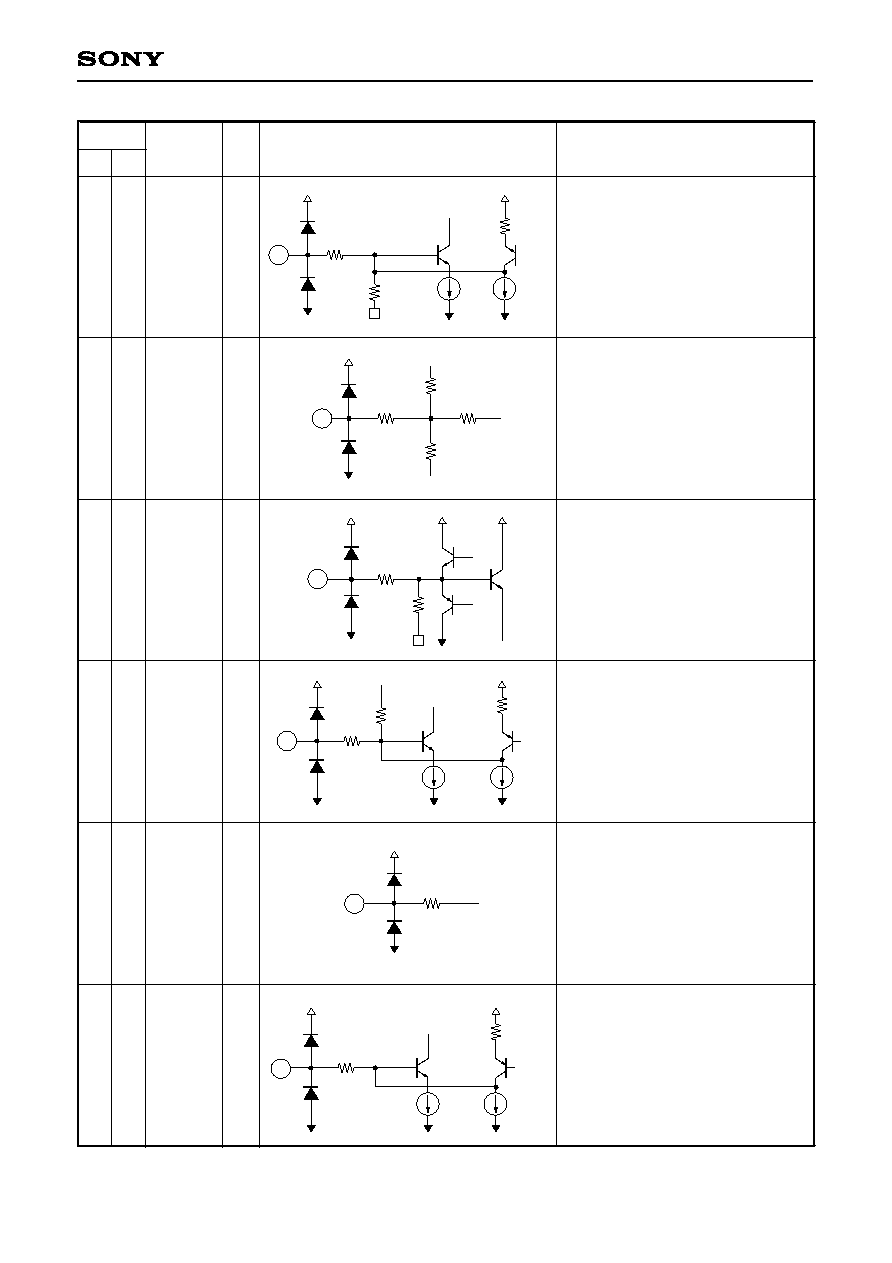

Pin Description

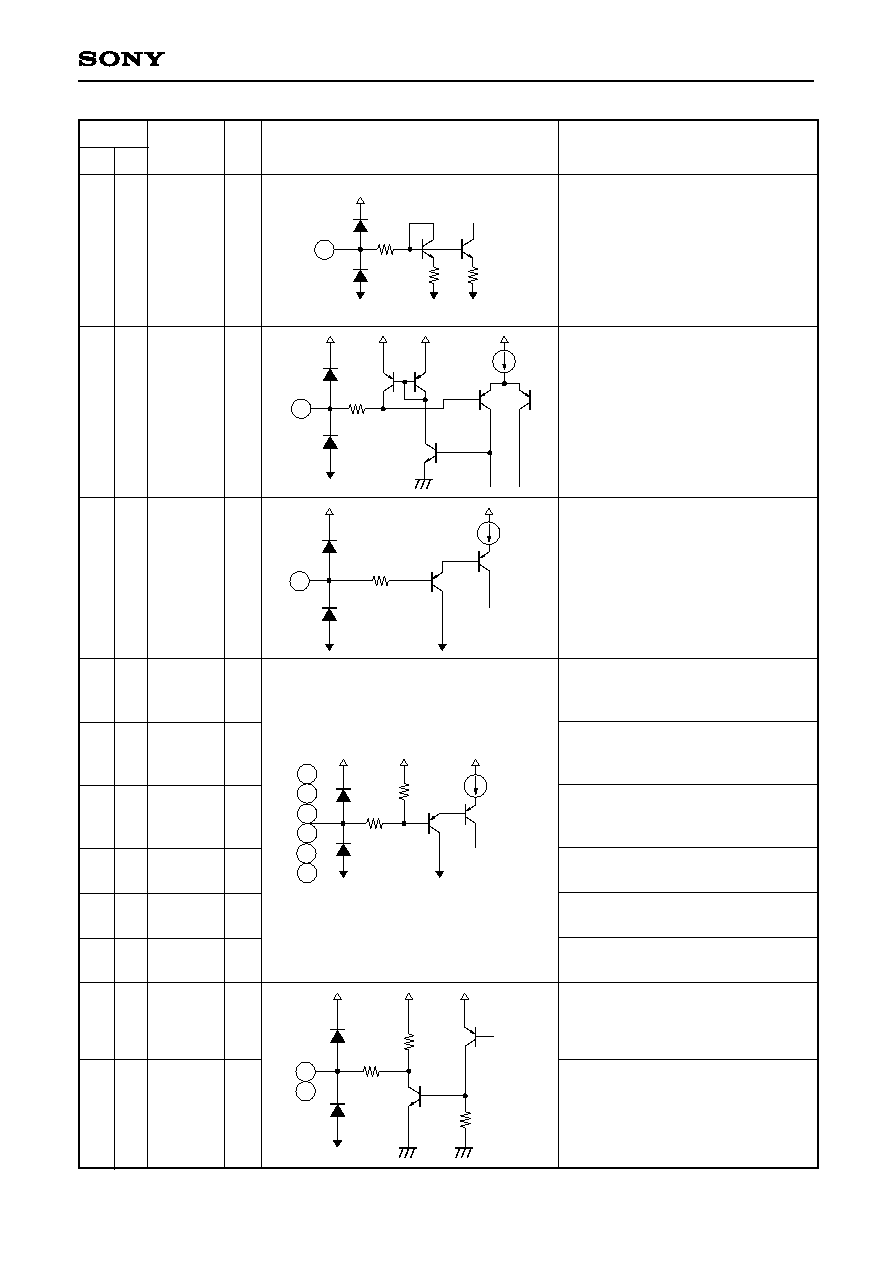

Pin No.

Symbol

I/O

Equivalent circuit

Description

VC

I

Center voltage input.

For dual power supplies: GND

For single power supply:

(V

CC

+ GND)/2

FGD

I

Connects a capacitor between this

pin and Pin 3 to cut high-frequency

gain.

FS3

I

The high-frequency gain of the

focus servo is switched through FS3

ON and OFF.

FLB

I

External time constant to boost the

low frequency of the focus servo.

FEO

O

TAO

O

SLO

O

Focus drive output.

Tracking drive output.

Sled drive output.

1

2

3

4

5

11

14

6

7

8

9

10

11

17

20

12

FE≠

I

Inverted input for focus amplifier.

147

40k

90k

2.5ĶA

6

5

11

14

250ĶA

2.5ĶA

40k

4

2

Vcc

V

EE

147

48k

130k

20ĶA

3

46k

580k

Q

S

≠ 5 ≠

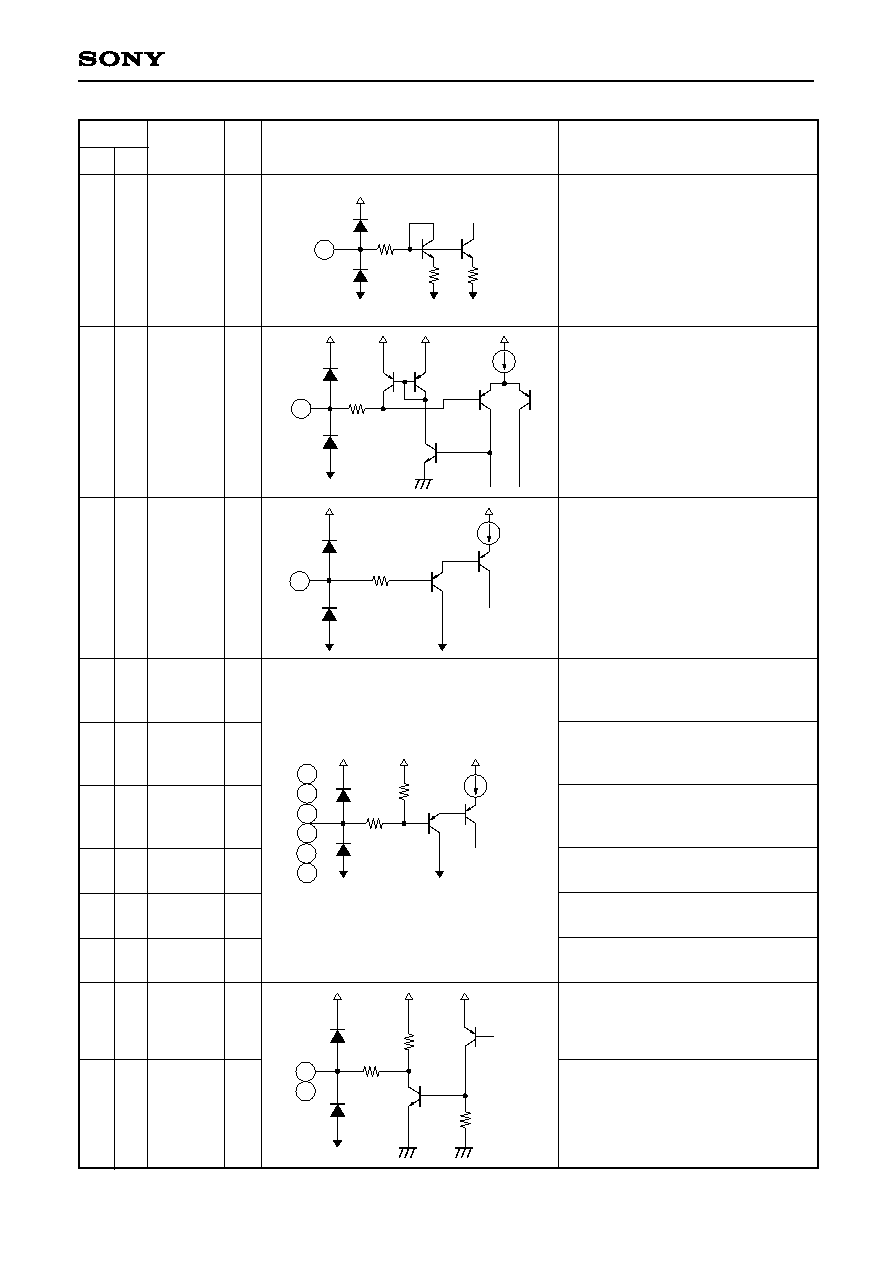

CXA1372BQ/BS

External time constant for forming

the focus search waveforms.

External time constant for selecting

the tracking high-frequency gain.

External time constant for selecting

the tracking high-frequency gain.

Inverted input for tracking amplifier.

Non-inverted input for sled amplifier.

Inverted input for sled amplifier.

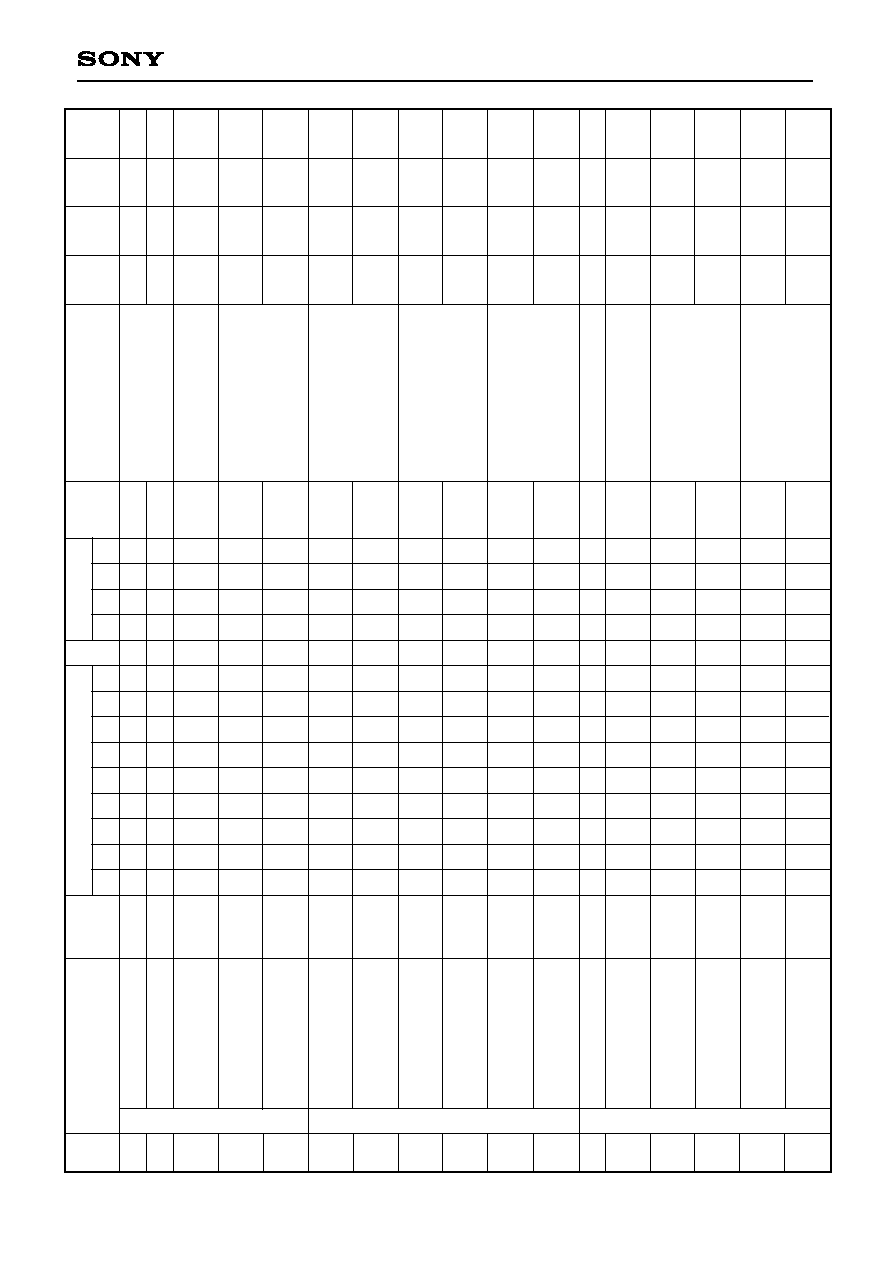

Pin No.

Symbol

I/O

Equivalent circuit

Description

SRCH

I

TGU

I

TG2

I

TA≠

I

SL+

I

13

14

15

18

19

21

7

8

9

12

13

15

SL≠

I

147

22ĶA

3ĶA

15

10k

13

147

90k

11ĶA

3ĶA

12

147

50k

11ĶA

3.5ĶA

7

20k

110k

82k

8

470k

147

9

Q

S

≠ 6 ≠

CXA1372BQ/BS

Serial data transfer clock input from

CPU. (no pull-up resistor)

Serial data input from CPU.

(no pull-up resistor)

Reset input, reset at "Low".

(no pull-up resistor)

Latch input from CPU.

(no pull-up resistor)

Track number count signal output.

Outputs FZC, AS, TZC and SSTOP

through command from CPU.

Sets the peak frequency of focus

tracking phase compensation.

Current is input to determine focus

search, track jump, and sled kick

level.

Used for 1-track jump. Contains a

47k

pull-up resistor.

At "Low" sled overrun prevention

circuit operates. Contains a 47k

pull-up resistor.

Limit SW ON/OFF signal detection

for disc innermost track detection.

Pin No.

Symbol

I/O

Equivalent circuit

Description

FSET

I

ISET

I

SSTOP

I

DIRC

I

LOCK

I

22

23

24

26

27

33

16

17

18

20

21

CLK

I

28

22

XLT

I

29

23

DATA

I

30

24

XRST

I

31

25

27

SENS

O

32

26

C. OUT

O

100k

147

20k

26

27

147

47k

15ĶA

20

21

22

23

24

25

147

15k

15k

16

147

17

147

7ĶA

18

Q

S

≠ 7 ≠

CXA1372BQ/BS

Input for DEFECT bottom hold

output with capacitance coupled.

Pin No.

Symbol

I/O

Equivalent circuit

Description

29

MIRR

O

38

CP

I

MIRR comparator output.

(DC voltage: 10k

load connected)

Connects MIRR hold capacitor.

Non-inverted input for MIRR

comparator.

34

CC1

O

35

CC2

I

30

DFCT

O

37

CB

I

31

ASY

I

Auto asymmetry control input.

32

EFM

O

EFM comparator output.

(DC voltage: 10k

load connected)

33

35

44

40

41

36

43

37

38

39

FOK

O

FOK comparator output.

(DC voltage: 10k

load connected)

147

33

20k

4.8k

Current source depending on

power supply

(V

CC

to D

GND

)

32

147

31

147

147

20k

29

38

147

37

147

35

147

34

147

30

DEFECT bottom hold output.

Connects DEFECT bottom hold

capacitor.

DEFECT comparator output.

(DC voltage: 10k

load connected)

Q

S

≠ 8 ≠

CXA1372BQ/BS

Input for RF summing amplifier

output with capacitance coupled.

Tracking zero-cross comparator

input.

Connects a capacitor for time

constant during defect.

Tracking error input.

Window comparator input for ATSC

detection.

Focus zero-cross comparator input.

Focus error input.

Connects a capacitor for time

constant during defect.

Pin No.

Symbol

I/O

Equivalent circuit

Description

RFI

I

TZC

I

TE

I

ATSC

I

FZC

I

45

48

1

3

4

5

39

RF summing amplifier output.

Check point of eye pattern.

RFO

O

46

40

42

43

TDFCT

I

2

44

45

46

47

FE

I

6

48

FDFCT

I

147

147

470k

47

48

147

46

1.2k

60k

330k

45

Vcc

V

EE

470k

47P

147

39

40

147

40k

42

147

75k

7ĶA

147

147

43

44

470k

Q

S

≠ 9 ≠

CXA1372BQ/BS

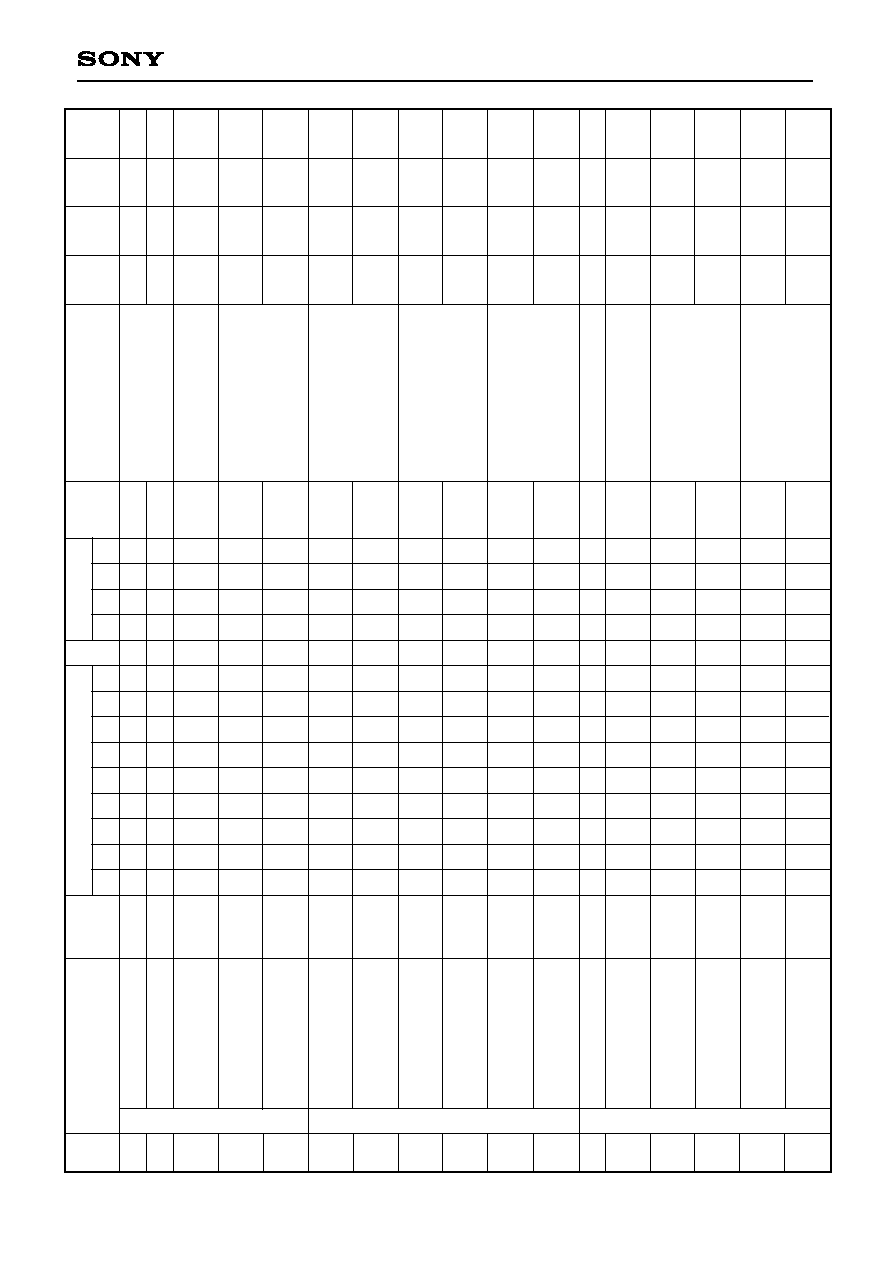

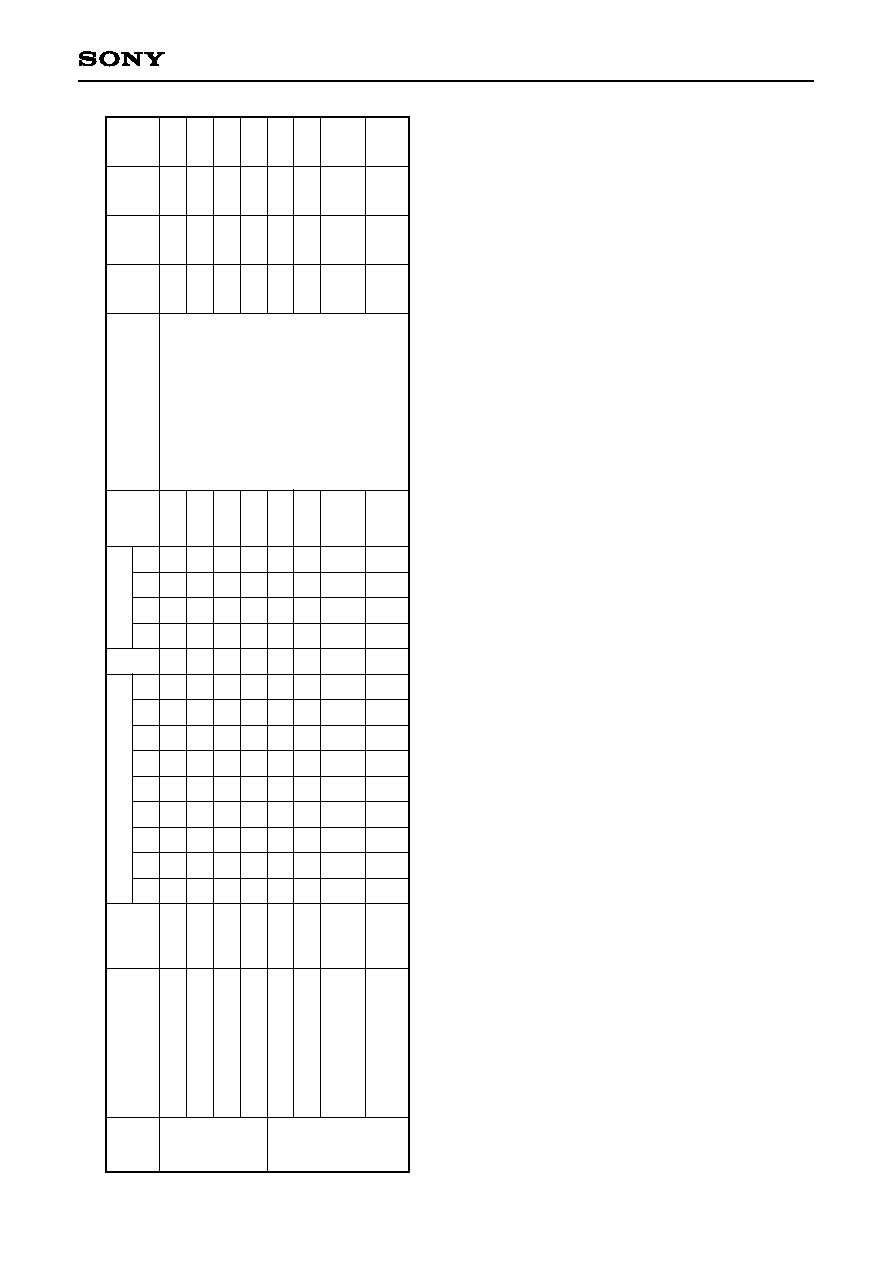

Electrical Characteristics

(Ta = 25įC, V

CC

= 2.5V, V

EE

= ≠2.5V, D. GND = ≠2.5V)

No.

Current consumption

Current consumption

O

O

O

O

O

O

S1

S2

S3

S4

S5

S6

S7

S8

S9

E1

E2

E3

E4

SD

Measure-

ment

point

Description of output

waveform and measurement

method

10, 36

19, 41

5

5

5

5

5

5

5

5

27

11

11

11

11

11

11

11

11

Unit

Max.

Typ.

Min.

Item

Symbol

Bias condition

SW condition

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

DC voltage gain

Feedthrough

Max. output voltage

Max. output voltage

Max. output voltage

Max. output voltage

Search output voltage

Search output voltage

FZC threshold value

DC voltage gain

Feedthrough

Max. output voltage

Max. output voltage

Max. output voltage

Max. output voltage

Jump output voltage

Jump output voltage

I

CC

I

EE

G

FEO

V

FEOF

V

FE01

V

FE02

V

FE03

V

FE04

V

SRCH1

V

SRCH2

V

FZC

G

TEO

V

TEOF

V

TE01

V

TE02

V

TE03

V

TE04

V

JUMP1

V

JUMP2

O

O

O

O

O

O

00

00

08

00

08

08

08

08

02

03

00

25

00

25

25

25

25

2C

28

8

≠24

18.0

2.0

1.2

≠640

360

39

11.6

2.0

1.2

≠640

360

19

≠17

21.0

50

13.3

27

≠8

24.0

≠35

≠2.0

≠1.2

≠360

640

61

17.6

≠39

≠2.0

≠1.2

≠360

640

mA

mA

dB

dB

V

V

V

V

mV

mV

mV

dB

dB

V

V

V

V

mV

mV

V

1

= 10Hz, 100mVp-p

G

FEO

= 20 log (Vout/Vin)

SG = 10kHz, 40mVp-p

Difference in gain when

SD = 00 and SD = 08

V

1

= 0.5V

DC

V

1

= ≠0.5V

DC

V

1

= 0.5V

DC

V

1

= ≠0.5V

DC

(V

CC

+ DGND)/2 = SENS

value when E4 is varied.

V

2

= 10Hz, ≠500mVp-p

G

TEO

= 20 log (Vout/Vin)

V

2

= 10kHz, 40mVp-p

Difference in gain when

SD = 00 and SD = 25

V

2

= ≠0.5V

DC

V

2

= 0.5V

DC

V

2

= ≠0.5V

DC

V

2

= 0.5V

DC

FOCUS SERVO

TRACKING SERVO

≠ 10 ≠

CXA1372BQ/BS

No.

O

O

S1

S2

S3

S4

S5

S6

S7

S8

S9

E1

E2

E3

E4

SD

Measure-

ment

point

Description of output

waveform and measurement

method

27

27

27

14

14

14

14

14

14

14

14

27

27

26

33

33

33

33

Unit

Max.

Typ.

Min.

Symbol

Bias condition

SW condition

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

10

10

20

25

00

25

25

25

25

23

22

30

≠45

7

≠20

50

2.0

2.0

≠750

450

≠40

≠400

2.2

45

≠26

26

0

≠25

≠356

≠7

45

20

≠34

≠2.0

≠2.0

≠450

750

≠10

≠2.0

≠2.0

≠330

≠1.8

mV

mV

mV

dB

dB

V

V

V

V

mV

mV

mV

V

V

mV

V

V

kHz

(V

CC

+ DGND)/2 = SENS

value when E3 is varied.

(V

CC

+ DGND)/2 = SENS

value when E2 is varied.

V

5

= 10Hz, 20mVp-p

Open loop gain

V

5

= 10kHz, 100mVp-p

Difference in gain when

SD = 00 and SD = 25

V

5

= 1.0V

DC

V

5

= ≠1.0V

DC

V

5

= 1.0V

DC

V

5

= ≠1.0V

DC

(V

CC

+ DGND)/2 = SENS

value when E1 is varied.

(V

CC

+ DGND)/2 = value

between Pins 39

and 40

when V

4

is varied.

V

4

= 1Vp-p ≠ 375mV

DC

FOK

ATSC threshold value

ATSC threshold value

TZC threshold value

DC voltage gain

Feedthrough

Max. output voltage

Max. output voltage

Max. output voltage

Max. output voltage

Kick output voltage

Kick output voltage

SSTOP threshold

value

SENS Low level

COUT Low level

FOK threshold value

High level voltage

Low level voltage

Max. operating frequency

V

ATSC1

V

ATSC2

V

TZC

G

SLO

V

SLOF

V

SL01

V

SL02

V

SL03

V

SL04

V

KICK1

V

KICK2

V

SSTOP

V

SENS

V

COUT

V

FOKT

V

FOKH

V

FOKL

F

FOK

SLED SERVO

TRACKING

SERVO

Item

≠ 11 ≠

CXA1372BQ/BS

S1

S2

S3

S4

S5

S6

S7

S8

S9

E1

E2

E3

E4

SD

Measure-

ment

point

Description of output

waveform and measurement

method

29

29

29

29

29

30

30

30

30

30

30

31

31

32

32

A

A

Unit

Max.

Typ.

Min.

Symbol

Bias condition

SW condition

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

High level voltage

Low level voltage

Max. operating

frequency

Min. input operating

voltage

Max. input operating

voltage

High level output

voltage

Low level output

voltage

Min. operating

frequency

Max. operating

frequency

Min. input operating

voltage

Max. input operating

voltage

Duty 1

Duty 2

High level output

voltage

Low level output

voltage

Min. input operating

voltage

Max. input operating

voltage

V

MIRH

V

MIRL

F

MIR

V

MIR1

V

MIR2

V

DFCTH

V

DFCTL

F

DFCT1

F

DFCT2

V

DFCT1

V

DFCT2

D

EFM1

D

EFM2

V

EFMH

V

EFML

V

EFM1

V

EFM2

O

O

O

O

O

O

1.8

30

1.8

1.8

2.5

1.8

≠50

0

1.2

1.8

0

50

≠2.0

0.3

≠2.0

1

0.5

50

100

≠1.2

0.12

V

V

kHz

Vp-p

Vp-p

V

V

kHz

kHz

Vp-p

Vp-p

mV

mV

V

V

Vp-p

Vp-p

V

4

= 10kHz

1.0Vp-p ≠ 0.4V

DC

V

4

= 800mVp-p ≠ 0.4V

DC

V

4

= 10kHz ≠ 0.4V

DC

V

4

= 0.8Vp-p + 375mV

DC

V

4

= 50Hz + 375mV

DC

(square wave)

V

4

= 750kHz, 0.7Vp-p

V

4

= 750kHz,

0.7Vp-p + 0.25V

DC

V

4

= 750kHz, 0.7Vp-p

V

4

= 750kHz

DEFECT

EFM

MIRROR

Item

No.

O

O

≠ 12 ≠

CXA1372BQ/BS

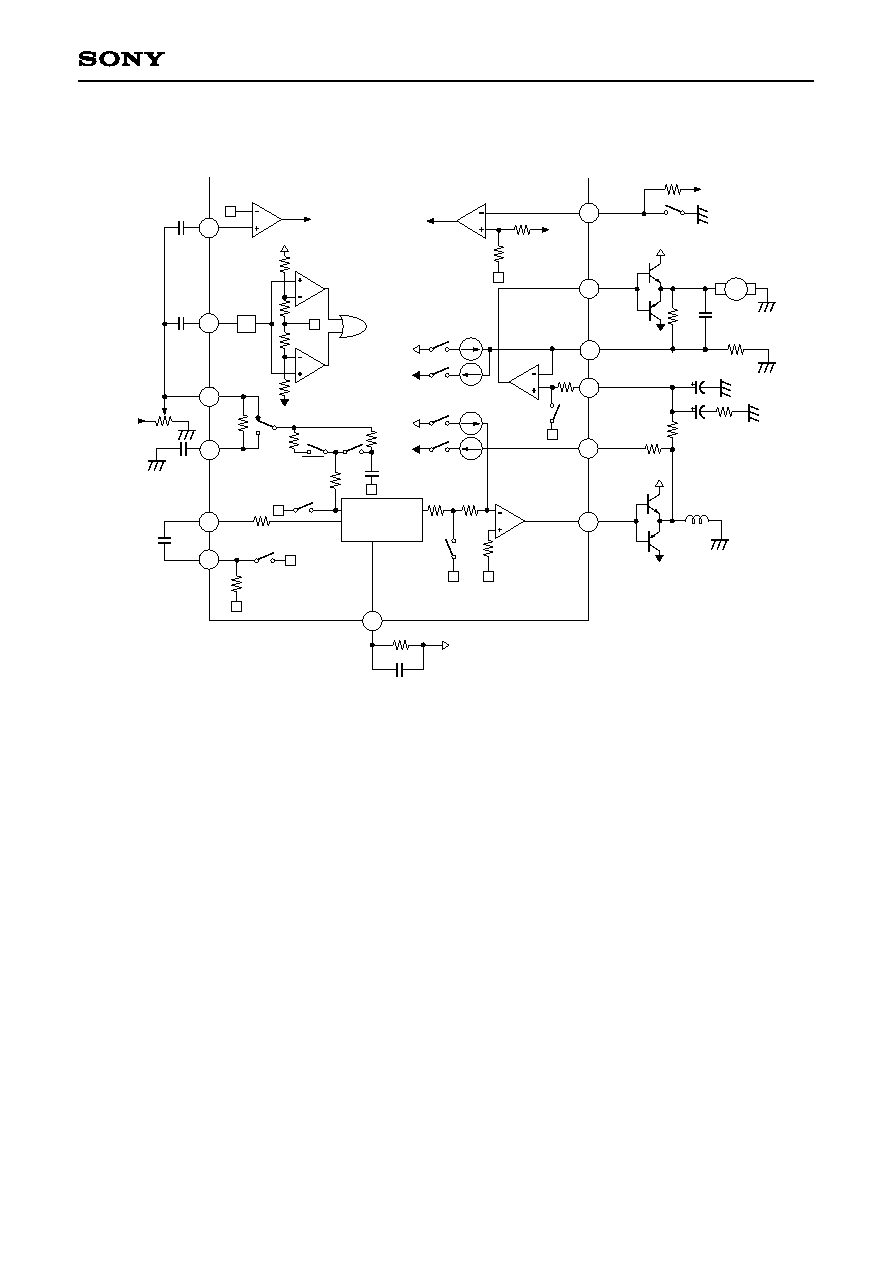

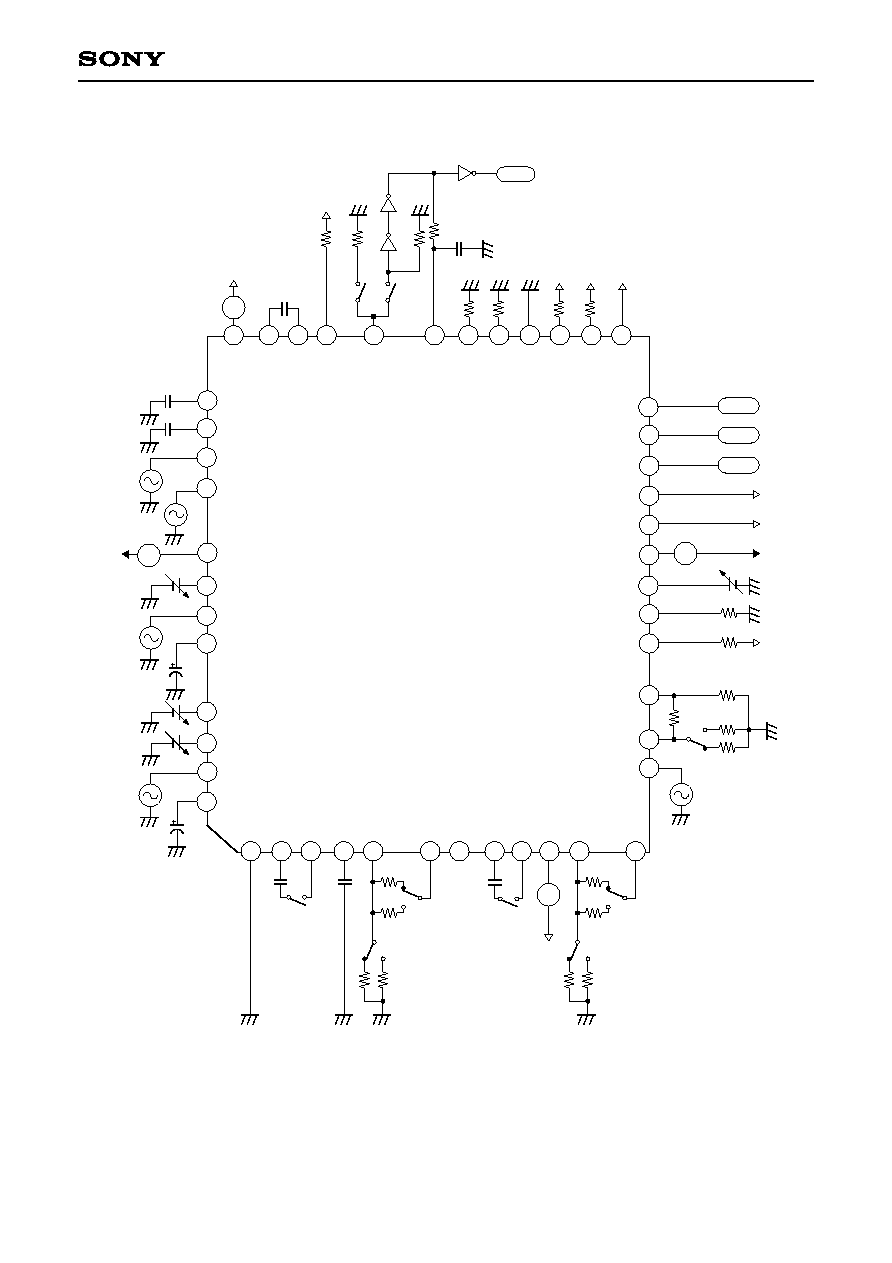

Electric Characteristics Measurement Circuit

GND

0.1Ķ

S1

GND

1000P

130

13k

S3

100k

200k

S2

S4

0.033Ķ

AVcc

GND

130

S6

100k

200k

S5

GND

13k

GND

V5

AC

130

13k

S7

60k

5.1k

GND

510k

Vcc

240k

AV

EE

Vcc

Vcc

GND

E1

CLK

XLT

DATA

10k

Vcc Vcc

10k

Vcc

10k

DGND

10k

DGND

S8

S9

0.01Ķ

1k

A

DGND

1M

DGND

10k

Vcc

10k

3300P

A

DVcc

1000P

DGND

3300P

DGND

V4

AC

GND

V3

AC

GND

DV

EE

GND

E2

V2

AC

GND

GND

0.1Ķ

GND

E3

GND

E4

V1

AC

GND

0.1Ķ

GND

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

40

39

38

37

36

35

34

31

32

33

41

42

43

44

45

46

47

48

1

CB

CP

RFI

RFO

DV

EE

TZC

TE

TDFCT

ATSC

FZC

FE

FDFCT

DATA

XLT

CLK

LOCK

DIRC

AV

EE

SSTOP

ISET

FSET

SL≠

SLO

SL+

VC

FGD

FS3

FLB

FEO

FE≠

SRCH

TGU

TG2

AVcc

TAO

TA≠

DVcc

CC2

CC1

FOK

EFM

ASY

DFCT

MIRR

DGND

SENS

C. OUT

XRST

DGND

DGND

+

GND

+

+

+

A

A

A

≠ 13 ≠

CXA1372BQ/BS

Description of Functions

Focus Servo

FZC

1.2k

56k

FE

22k

FZC

Focus Phase

Compensation

48k

510k

0.1Ķ

FSET

FLB

40k

FGD

10k

DFCT

2200p

FE

470k

0.1Ķ

FDFCT

FS3

580k

46k

100k

FOCUS COIL

FE≠

120k

11Ķ

22Ķ

ISET

FS1

50k

40k

4.7Ķ

SRCH

10k

FS2

0.01Ķ

FEO

0.1Ķ

20k

FS4

FS3

120k

46

47

48

2

3

4

16

7

17

6

5

DGND

The above figure shows a block diagram of the focus servo.

Ordinarily the FE signal is input to the focus phase compensation circuit through a 20k

and 48k

resistance;

however, when DFCT is detected, the FE signal is switched to pass through a low-pass filter formed by the

internal 470k

resistance and the capacitance connected to Pin 48. When this DFCT countermeasure circuit is

not used, leave Pin 48 open.

When FS3 is ON, the high-frequency gain can be cut by forming a low-frequency time constant through a

capacitor connected between Pins 2 and 3 and the internal resistor.

The capacitor connected between Pin 4 and GND is a time constant to boost the low frequency in the normal

playback state.

The peak frequency of the focus phase compensation is approximately 1.2kHz when a resistance of 510k

is

connected to Pin 16.

The focus search level is approximately Ī1.1Vp-p when using the constants indicated in the above figure. This

level is inversely proportional to the resistance connected between Pin 17 and GND. However, changing this

resistance also changes the level of the track jump and sled kick as well.

The FZC comparator inverted input is set to 2% of V

CC

and VC (Pin 1); (V

CC

≠ VC)

◊

2%.

510k

resistance is recommended for Pin 16.

≠ 14 ≠

CXA1372BQ/BS

Tracking Sled Servo

42

TZC

TZC

0.022Ķ

45

0.047Ķ

ATSC

BPF

100k

1k

1k

100k

ATSC

43

44

TE

22k

0.1Ķ

TE

TDFCT

470k

DFCT

680k

TG1

TG1

680K

10k

TM1

66P

Tracking

Phase

Compensation

8

9

0.033Ķ

TGU

TG2

20k

TG2

470k

10k

90k

TM7

11

12

TA≠

13

SL+

14

15

SLO

SL≠

TRACKING

COIL

100k

82k

22Ķ

3.3Ķ

15k

8.2k

0.015Ķ

M

SLED MOTOR

120k

100k

SSTOP

SSTOP

100k

1k

10k

TM2

TM6

TM5

22ĶA

22ĶA

TM4

TM3

11ĶA

11ĶA

16

510k

0.01Ķ

FSET

TAO

18

The above figure shows a block diagram of the tracking and sled servo.

The capacitor connected between Pins 8 and 9 is a time constant to cut the high-frequency gain when TG2 is

OFF. The peak frequency of the tracking phase compensation is approximately 1.2kHz when a 510k

resistance connected to Pin 16.

To jump tracks in FWD and REV directions, turn TM3 or TM4 ON. During this time, the peak voltage applied to

the tracking coil is determined by the TM3 or TM4 current and the feedback resistance from Pin 12. To be

more specific,

Track jump peak voltage = TM3 (or TM4) current

◊

feedback resistance

The FWD and REV sled kick is performed by turning TM5 or TM6 ON. During this time, the peak voltage

applied to the sled motor is determined by the TM5 or TM6 current and the feedback resistance from Pin 15;

Sled kick peak voltage = TM5 ( or TM6) current

◊

feedback resistance

The values of the current for each switch are determined by the resistance connected between Pin 17 and

GND. When this resistance is 120k

:

TM3 ( or TM4) = Ī11ĶA, and TM5 (or TM6) = Ī22ĶA.

This current value is almost inversely proportional to the resistance and the variable range is approximately 5

to 40ĶA at TM3.

SSTOP is the ON/OFF detection signal for the limit SW of the linear motor's innermost track.

As is the case with the FE signal, the TE signal is switched to pass through a low-pass filter formed by the

internal resistance (470k

) and the capacitor connected to Pin 44.

TM-1 was ON at DFCT in the CXA1082 and CXA1182, but it does not operate in the CXA1372.

≠ 15 ≠

CXA1372BQ/BS

Focus OK circuit

15k

92k

VG

54k

20k

V

CC

0.625V

RFO

RFI

FOK

◊

1

FOCUS OK AMP

FOCUS OK

COMPARATOR

RF signal

33

39

40

C5

0.01Ķ

The focus OK circuit creates the timing window okaying the focus servo from the focus search state.

The HPF output is obtained at Pin 39 from Pin 40 (RF signal), and the LPF output (opposite phase) of the

focus OK amplifier output is also obtained.

The focus OK output reverses when V

RFI

≠ V

RFO

≠0.37V.

Note that, C5 determines the time constants of the HPF for the EFM comparator and mirror circuit and the LPF

of the focus OK amplifier. Ordinarily, with a C5 equal to 0.01ĶF selected, the fc is equal to 1kHz, and block

error rate degradation brought about by RF envelope defects caused by scratched discs can be prevented.

EFM comparator

EFM comparator changes RF signal to a binary value. The asymmetry generated due to variations in disc

manufacturing cannot be eliminated by the AC coupling alone. Therefore, the reference voltage of EFM

comparator is controlled through 1 and 0 that are in approximately equal numbers in the binary EFM signals.

As this comparator is a current SW type, each of the High and Low levels is not equal to the power supply

voltage. A feedback has to be applied through the CMOS buffer.

R8, R9, C8, and C9 form a LPF to obtain (V

CC

+ DGND)/2V. When fc (cut-off frequency) exceeds 500Hz, the

EFM low-frequency components leak badly, and the block error rate worsens.

31

C8

C9

ASY

R8

R9

CMOS

BUFFER

CXD2500

100k

20k

VC

Vcc

40k

40k

AUTO ASYMMETRY

BUFFER

AUTO ASYMMETRY

CONTROL AMP

39

RFI

EFM COMPARATOR

32

EFM

DGND = 0V

◊

6

≠ 16 ≠

CXA1372BQ/BS

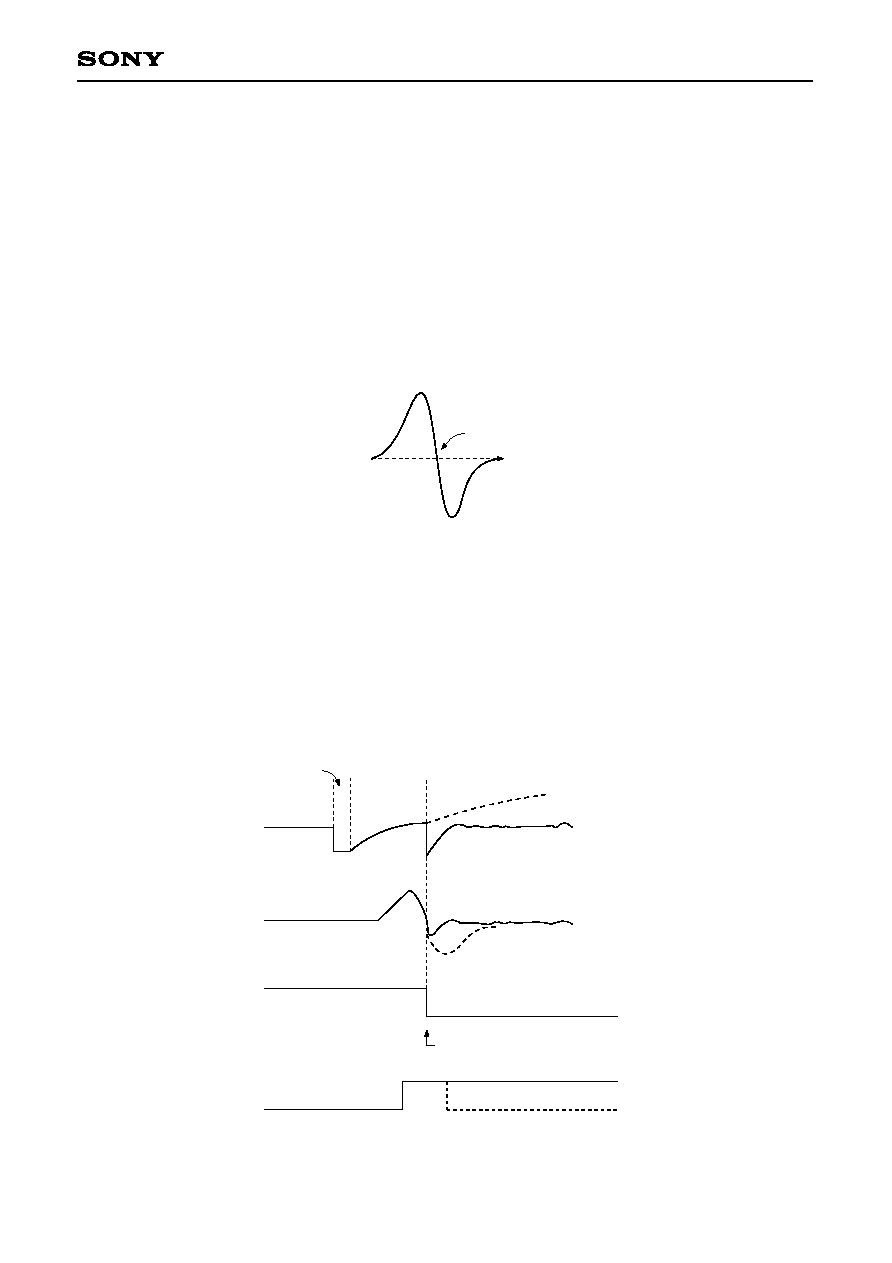

DEFECT circuit

After inversion, RFI signal is bottom held by means of the long and short time constants. The long time-

constant bottom hold keeps the mirror level prior to the defect.

The short time-constant bottom hold responds to a disc mirror defect in excess of 0.1ms, and this is

differentiated and level-shifted through the AC coupling circuit.

The long and short time-constant signals are compared to generate at mirror defect detection signal.

RFO

a

◊

2

b

DEFECT AMP

CC1

CC2

DFCT

CB

0.01Ķ

0.033Ķ

DEFECT COMPARATOR

DEFECT BOTTOM

HOLD

e

c

d

e

d

c

b

a

BOTTOM

HOLD (1);

Solid line CC1

DEFECT

AMP

RFO

DEFECT

BOTTOM

HOLD (2);

Dotted line CC2

H

L

34

35

37

40

30

≠ 17 ≠

CXA1372BQ/BS

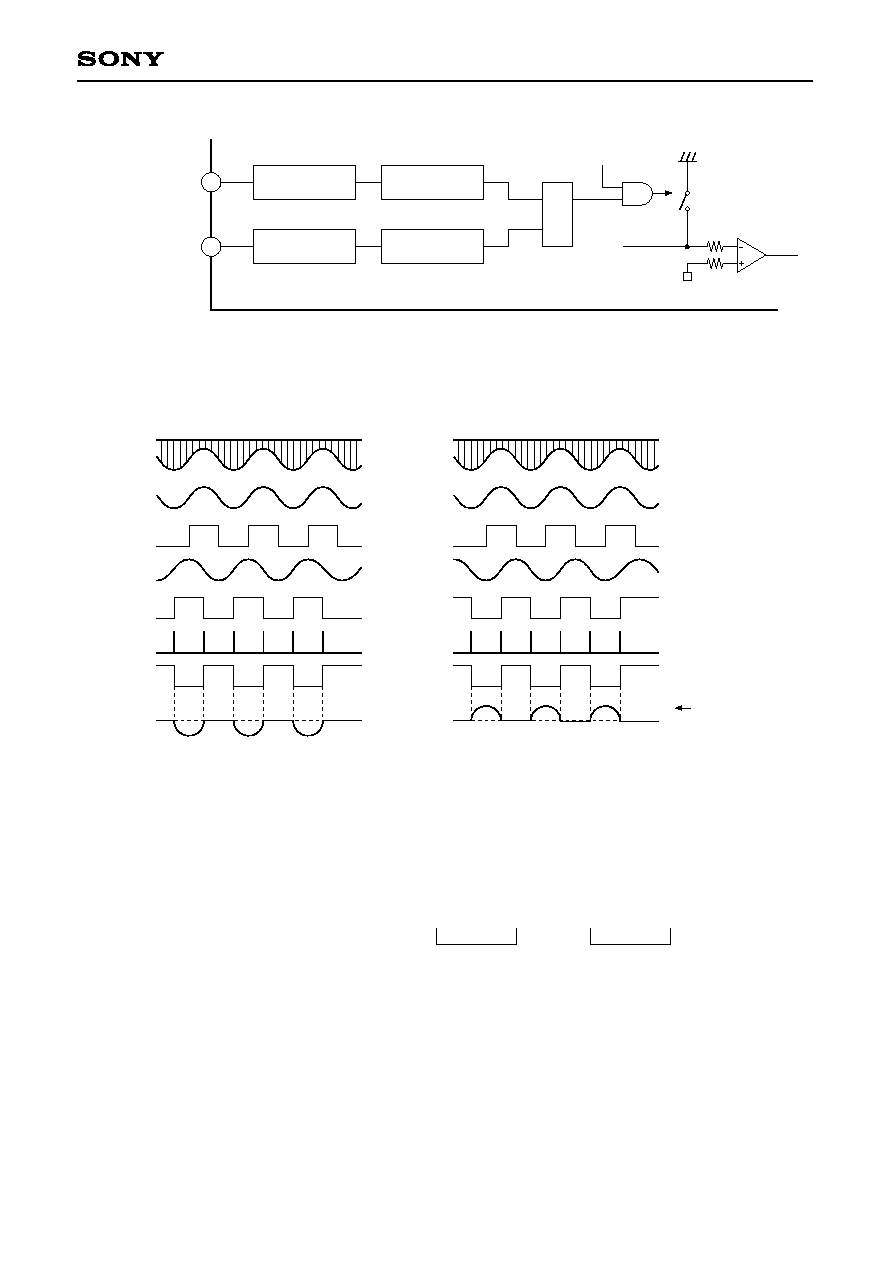

Mirror Circuit

The mirror circuit performs peak and bottom hold after the RFI signal has been amplified.

For the peak hold, a time constant can follow a 30kHz traverse, and, for the bottom hold, one can follow the

rotation cycle envelope fluctuation.

Through differential amplification of the peak and bottom hold signals H and I, mirror output can be obtained by

comparing an envelope signal J (demodulated to DC) to signal K for Which peak holding at a level 2/3 that of

the maximum was performed with a large time constant. In other words, mirror output is low for tracks on the

disc and high for the area between tracks (the MIRR areas). In addition, a high signal is output when a defect

is detected. The mirror hold time constant must be sufficiently large in comparison with the traverse signal.

20k

0.033Ķ

RFO

RFI

CP

MIRROR

COMPARATOR

PEAK &

BOTTOM

HOLD

◊

2.2

K

MIRROR HOLD AMP

J

H

I

◊

1

G

MIRROR AMP

MIRR

DGND

29

38

39

RFO

H

L

0V

0V

0V

0V

G

(RFI)

H

(PEAK HOLD)

I

(BOTTOM HOLD)

(MIRROR HOLD)

J

K

MIRR

≠ 18 ≠

CXA1372BQ/BS

Commands

The input data to operate this IC is configured as 8-bit data; however, below, this input data is represented by

2-digit hexadecimal numerals in the form $XX, where X is a hexadecimal numeral between 0 and F.

Commands for the CXA1372 can be broadly divided into four groups ranging in value from $0X to $3X.

1. $0X ("FZC" at SENS (Pin 27))

These commands are related to focus servo control.

The bit configuration is as shown below.

D7

D6

D5

D4

D3

D2

D1

D0

0

0

0

0

FS4

FS3

FS2

FS1

Four focus-servo related switches exist: FS1 to FS4 corresponding to D0 to D3, respectively.

$00

When FS1 = 0, Pin 7 is charged to (22ĶA ≠ 11ĶA)

◊

50k

= 0.55V.

If FS2 = 0, this voltage is no longer transferred, and the output at Pin 5 becomes 0V.

$02

From the state described above, the only FS2 becomes 1. When this occurs, a negative signal is output

to Pin 5. This voltage level is obtained by equation 1 below.

(22ĶA ≠ 11ĶA)

◊

50k

◊

.

.

.

.

Equation 1

$03

From the state described above, FS1 becomes 1, and a current source of +22ĶA is split off.

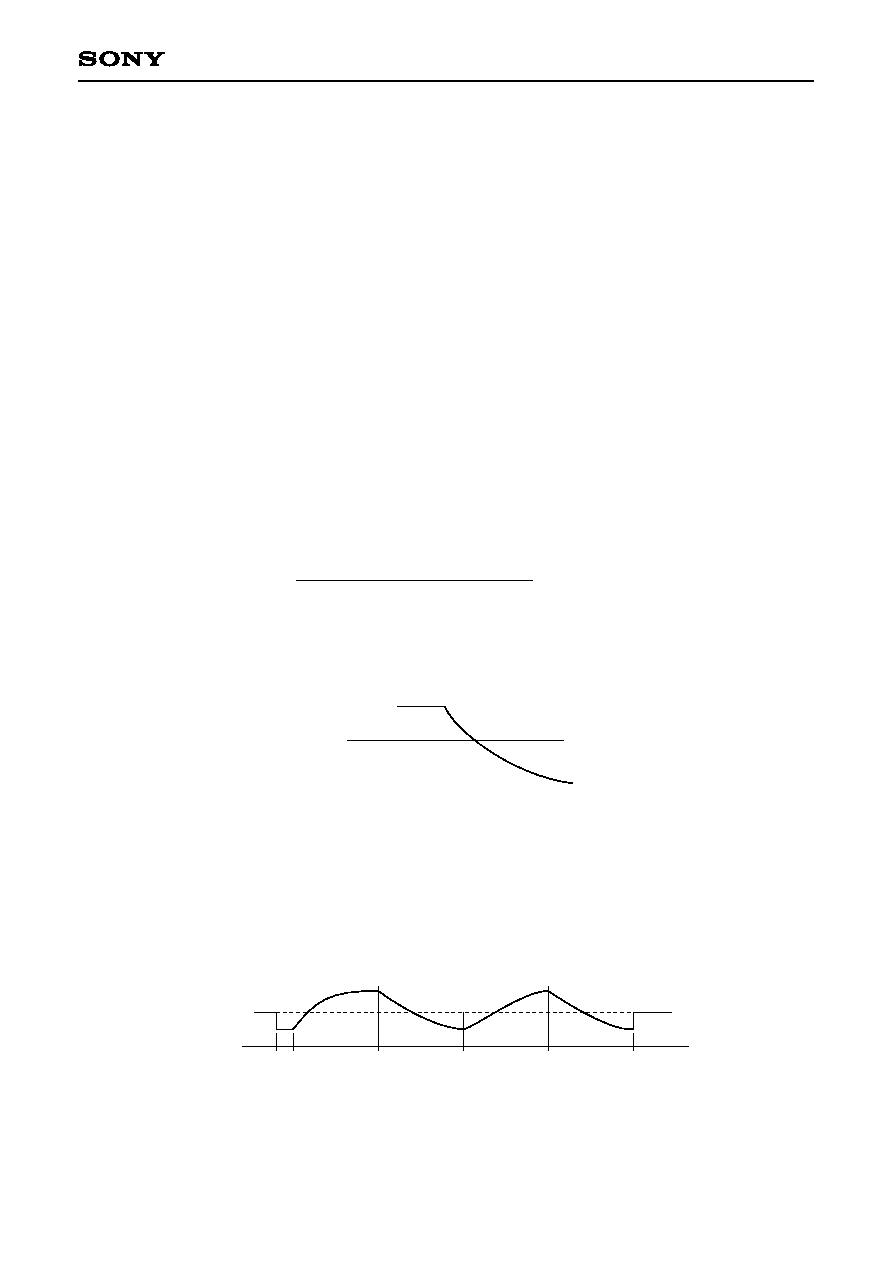

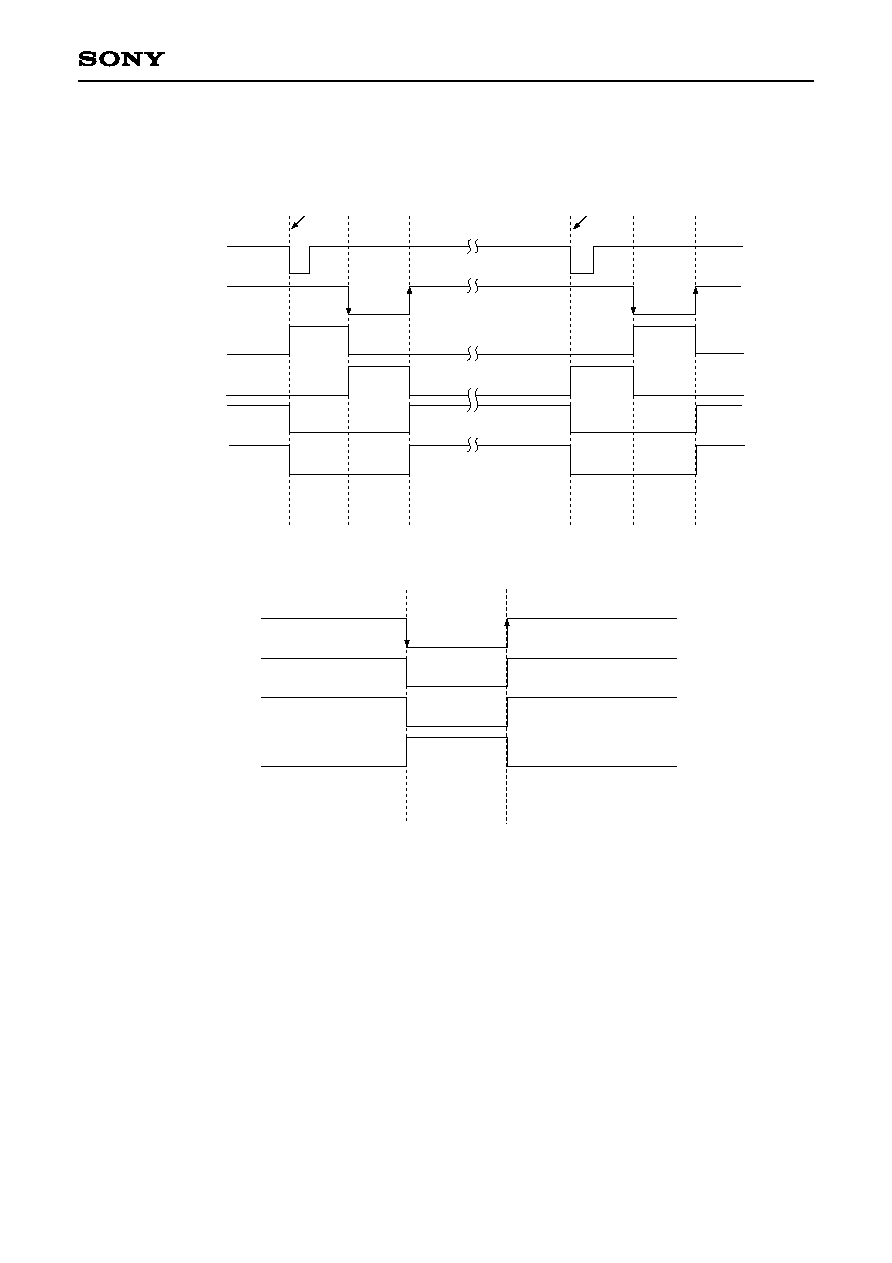

Then, a CR charge/discharge circuit is formed, and the voltage at Pin 7 decreases with the time as

shown in Fig. 1 below.

This time constant is obtained with the 50k

resistance and an external capacitor.

By alternating the commands between $02 and $03, the focus search voltage can be constructed. (Fig. 2)

0V

0V

$

00 02

03

02

03

02

00

Fig. 1. Voltage at Pin 7 when FS1 gose from 0

1

Fig. 2. Constructing the search voltage by alternating between $02 and $03 (Voltage at Pin 5)

resistance between Pins 5 and 6

50k

≠ 19 ≠

CXA1372BQ/BS

The instant the signal is brought into focus.

$08

$03

($00)

$02

(20ms) (200ms)

Drive voltage

Focus error

SENS pin

(FZC)

Focus OK

1-1. FS4

This switch is provided between the focus error input (Pin 47) and the focus phase compensation, and is in

charge of turning the focus servo ON and OFF.

$00

$08

Focus OFF

Focus ON

1-2. Procedure of focus activation

For description, suppose that the polarity is as described below.

a) The lens is searching the disc from far to near;

b) The output voltage (Pin 5) is changing from negative to positive; and

c) The focus S-curve is varying as shown below.

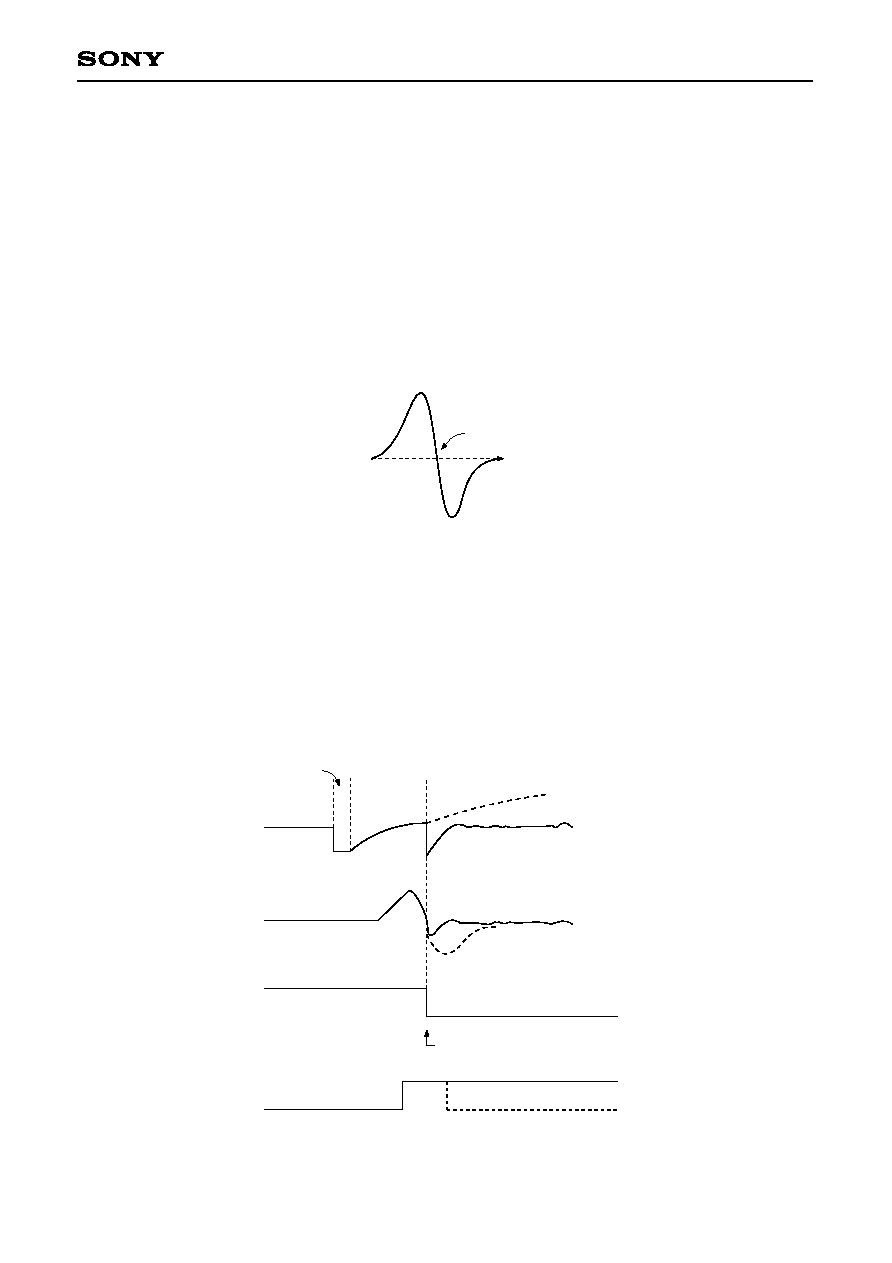

The focus servo is activated at the operating point indicated by A in Fig. 3. Ordinarily, focus searching and

turning the focus servo switch ON are performed when the focus S-curve transits the point A indicated in Fig. 3.

To prevent misoperation, this signal is ANDed with the focus OK signal.

In this IC, FZC (Focus Zero Cross) signal is output from the SENS pin (Pin 27) as the point A transit signal.

Focus OK is output as a signal indicating that the signal is in focus (can be in focus in this case).

Following the line of the above description, focusing can be well obtained by observing the following timing

chart.

The broken lines in the figure

indicate the voltage assuming

the signal is not in focus.

t

A

Fig. 3. S-curve

Fig. 4. Focus ON timing chart

≠ 20 ≠

CXA1372BQ/BS

1-3. SENS (Pin 27)

The output of the SENS pin differs depending on the input data as shown below.

$0X: FZC

$1X: AS

$2X: TZC

$3X: SSTOP

$4X to 7X: HIGH-Z

2. $1X ("AS" at SENS (Pin 27))

These commands deal with switching TG1 and TG2 ON/OFF.

The bit configuration is as follows

D7

D6

D5

D4

D3

D2

D1

D0

0

0

0

1

ANTI

Break

TG2

TG1

SHOCK

circuit

ON/OFF ON/OFF

TG1, TG2

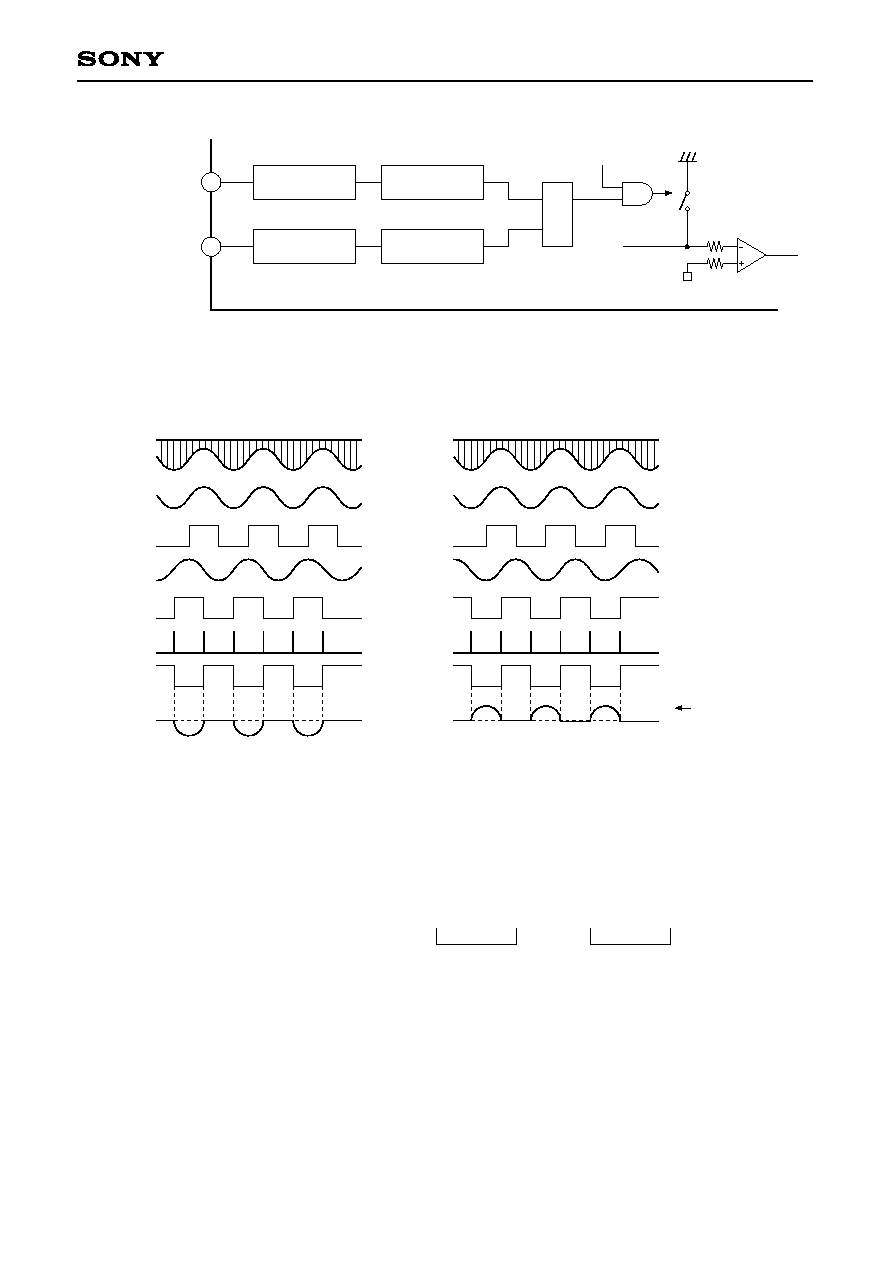

The purpose of these switches is to switch the tracking servo gain Up/Normal. The brake circuit (TM7) is to

prevent the frequently occurred phenomena where the merely 10-track jump has been performed actually

though a 100-track jump was intended to be done due to the extremely degraded actuator settling caused by

the servo motor exceeding the linear range after a 100 or 10-track jump.

When the actuator travels radially; that is, when it traverses from the inner track to the outer track of the disc

and vice versa, the brake circuit utilizes the fact that the phase relationship between the RF envelope and the

tracking error is 180įout-of-phase to cut the unneeded portion of the tracking error and apply braking.

Note that the time from the High to Low transition of FZC to the time command $08 is asserted must be

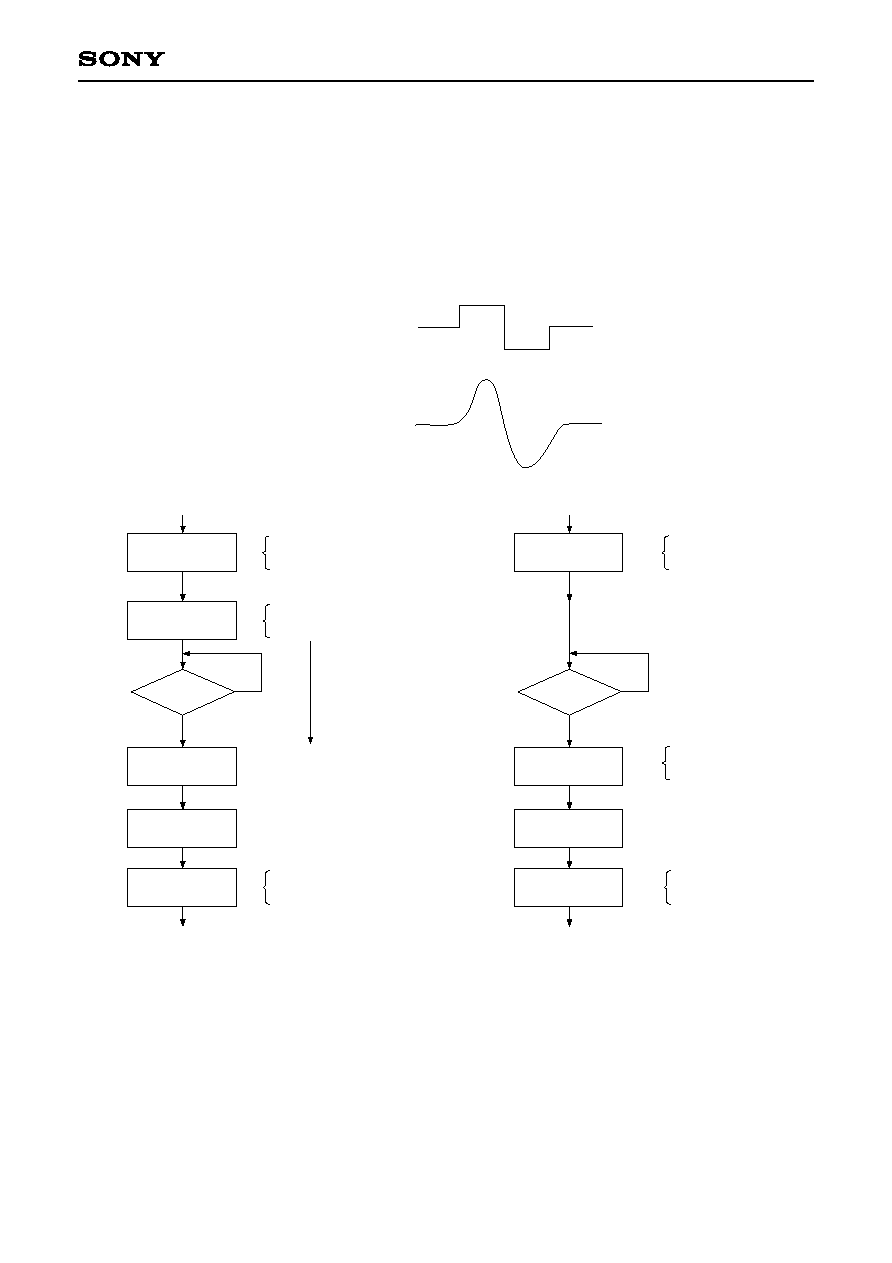

minimized. To do this, the software sequence shown in B is better than the sequence shown in A.

FZC

?

NO

YES

F. OK ?

NO

Transfer $08

Latch

FZC

?

NO

F. OK ?

NO

Transfer $08

Latch

(A)

(B)

YES

YES

YES

Fig. 5. Poor and good software command sequences

≠ 21 ≠

CXA1372BQ/BS

Envelope

Detection

[

B]

[

E]

RFI

(TZC)

Tracking error

(Latch)

Q

D

CK

(MIRR)

[

C]

[

F]

[

G]

BRK

D2

TM7

Low: open

High: make

[

A]

[

D]

Waveform

Shaping

Waveform

Shaping

Edge Detection

39

42

[

H]

Fig. 6. TM7 operation (brake circuit)

From inner to outer track

0V

From outer to inner track

("MIRR")

("TZC")

Braking is

applied from

here.

[

A]

[

B]

[

C]

[

D]

[

E]

[

F]

[

G]

[

H]

Fig. 7. Internal waveform

3. $2X ("TZC" at SENS (Pin 27))

These commands deal with turning the tracking servo and sled servo ON/OFF, and creating the jump pulse

and fast forward pulse during access operations.

D7

D6

D5

D4

D3

D2

D1

D0

0

0

1

0

Tracking

Sled

control

control

00: OFF

00: OFF

01: Servo ON

01: Servo ON

10: F-JUMP

10: F-FAST FORWARD

11: R-JUMP

11: R-FAST FORWARD

TM1, TM3, TM4

TM2, TM5, TM6

≠ 22 ≠

CXA1372BQ/BS

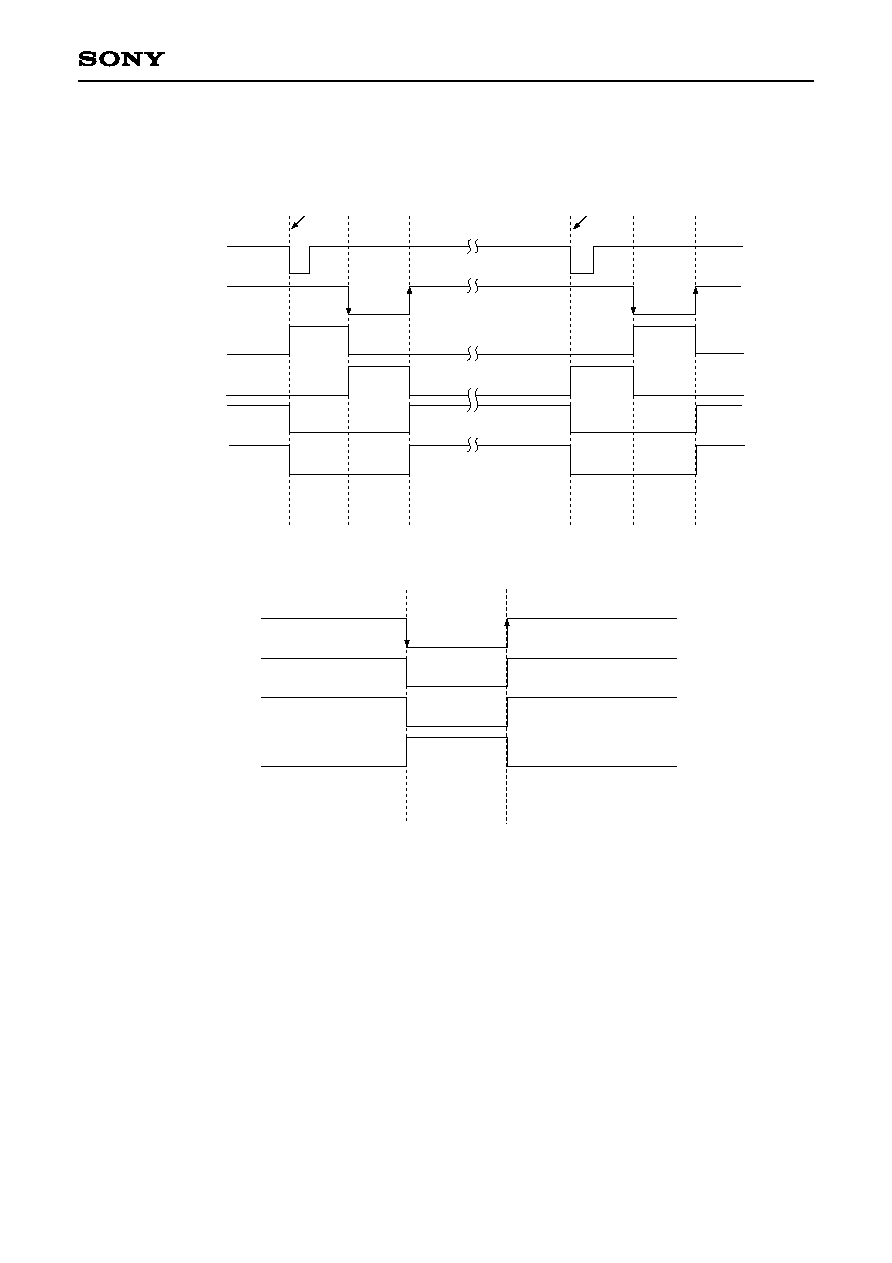

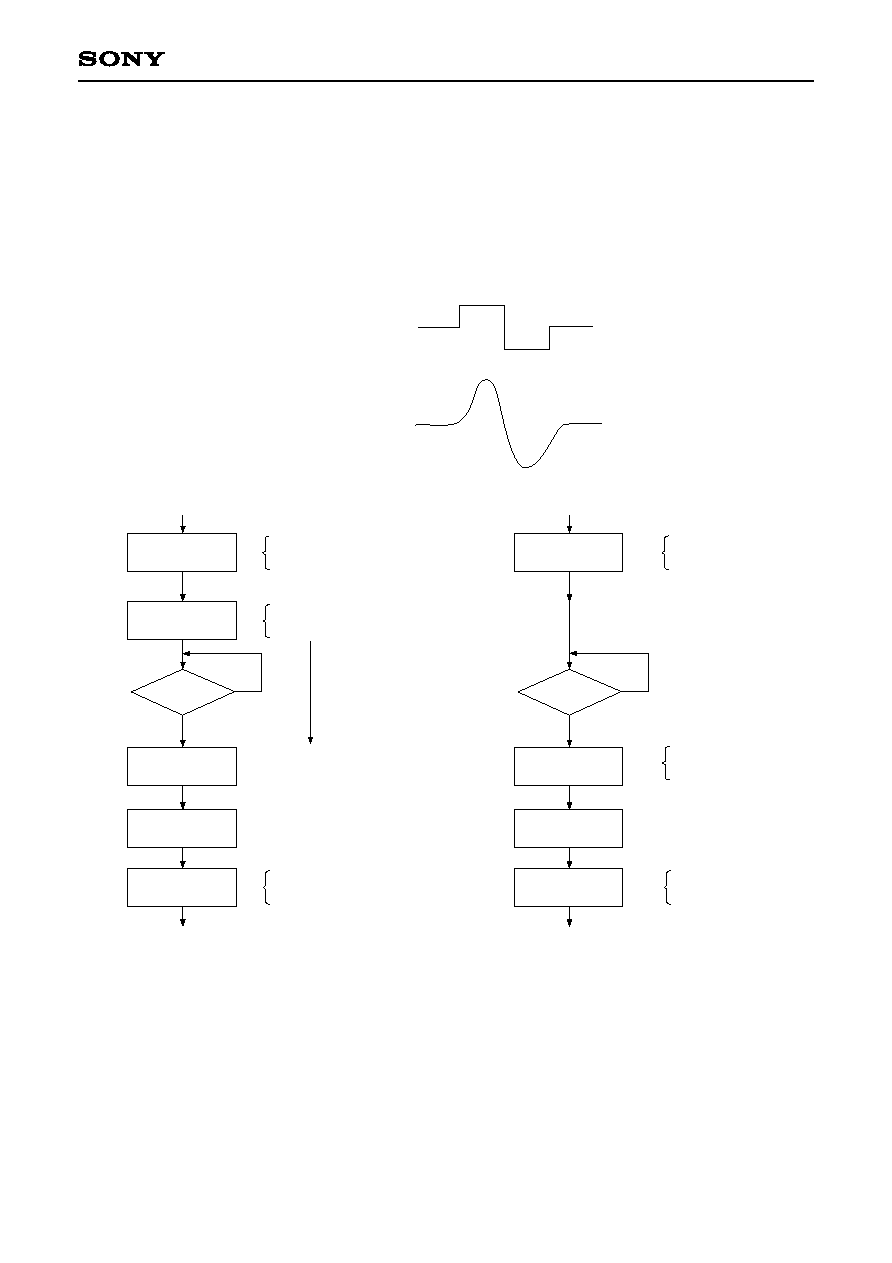

DIRC (Pin 20) and 1 Track Jump

Normally, an acceleration pulse is applied for a 1-track jump. Then a deceleration pulse is given for a specified

time observing the tracking error from the moment it passes point 0, and tracking servo is turned ON again.

For the 100-track jump to be explained in the next item, as long as the number of tracks is about 100 there is

no problem. However a 1-track jump must be performed here, which requires the above complicated

procedure. For the 1-track jump in CD players, both the acceleration and deceleration take about 300 to

400Ķs. When software is used to execute this operation, it turns out as shown in the flow chart of Fig. 9.

Actually, it takes some time to transfer data.

Acceleration

Pulse waveform

Tracking error

Deceleration

$2C transfer latch

$28 transfer only

TZC

?

NO

YES

Latch

Timer (0.3ms)

$25 transfer latch

TR: REV

SL: OFF

TR: FWD

SL: OFF

Execute

Execute

TR: ON

SL: ON

Execute

$2C transfer latch

TZC

?

NO

YES

DIRC = L

Timer (0.3ms)

DIRC = H

TR: REV

SL: OFF

TR: FWD

SL: OFF

Execute

TR: ON

SL: ON

Fig. 9. 1-track jump not using DIRC (Pin 20)

Fig. 10. 1-track jump with DIRC (Pin 20)

Fig. 8. Pulse waveform and tracking error of 1-track jump

The DIRC (Direct Control) pin was provided in this IC to facilitate the 1-track jump operation. Conduct the

following process to perform 1-track jump using DIRC (normal High).

(a) Acceleration pulse is output. ($2C for REV or $28 for FWD).

(b) With TZC

(or TZC

), set DIRC to Low. (SENS Pin 27 outputs "TZC"). As the jump pulse polarity is

inverted, deceleration is applied.

(c) Set DIRC to High after a specific time.

Both the tracking servo and sled servo are switched ON automatically.

As a result, the track jump turns out as shown in the flow chart of Fig. 10 and the two serial data transfers

can be omitted.

≠ 23 ≠

CXA1372BQ/BS

4. $3X

This command selects the focus search and sled kick levels.

D0, D1 ..... Sled, NORMAL feed, high-speed feed

D2, D3 ..... Focus search level selection

D7 D6 D5 D4

0

0

1

1

Focus search level

Sled kick level

Relative

value

D3

(PS4)

0

0

1

1

D2

(PS3)

0

1

0

1

D1

(PS2)

0

0

1

1

D0

(PS1)

0

1

0

1

Ī1

Ī2

Ī3

Ī4

≠ 24 ≠

CXA1372BQ/BS

Parallel Direct Interface

1. DIRC

$28 latch

$2C latch

ON

OFF

ON

OFF

OFF

ON

ON

OFF

XLT

DIRC

FWD JUMP

REV JUMP

TRACK SERVO

SLED SERVO

ON

OFF

ON

OFF

DOWN

UP

LOCK

SLED SERVO

TG1, TG2

TRACKING GAIN

2. LOCK (Sled overrun prevention circuit)

≠ 25 ≠

CXA1372BQ/BS

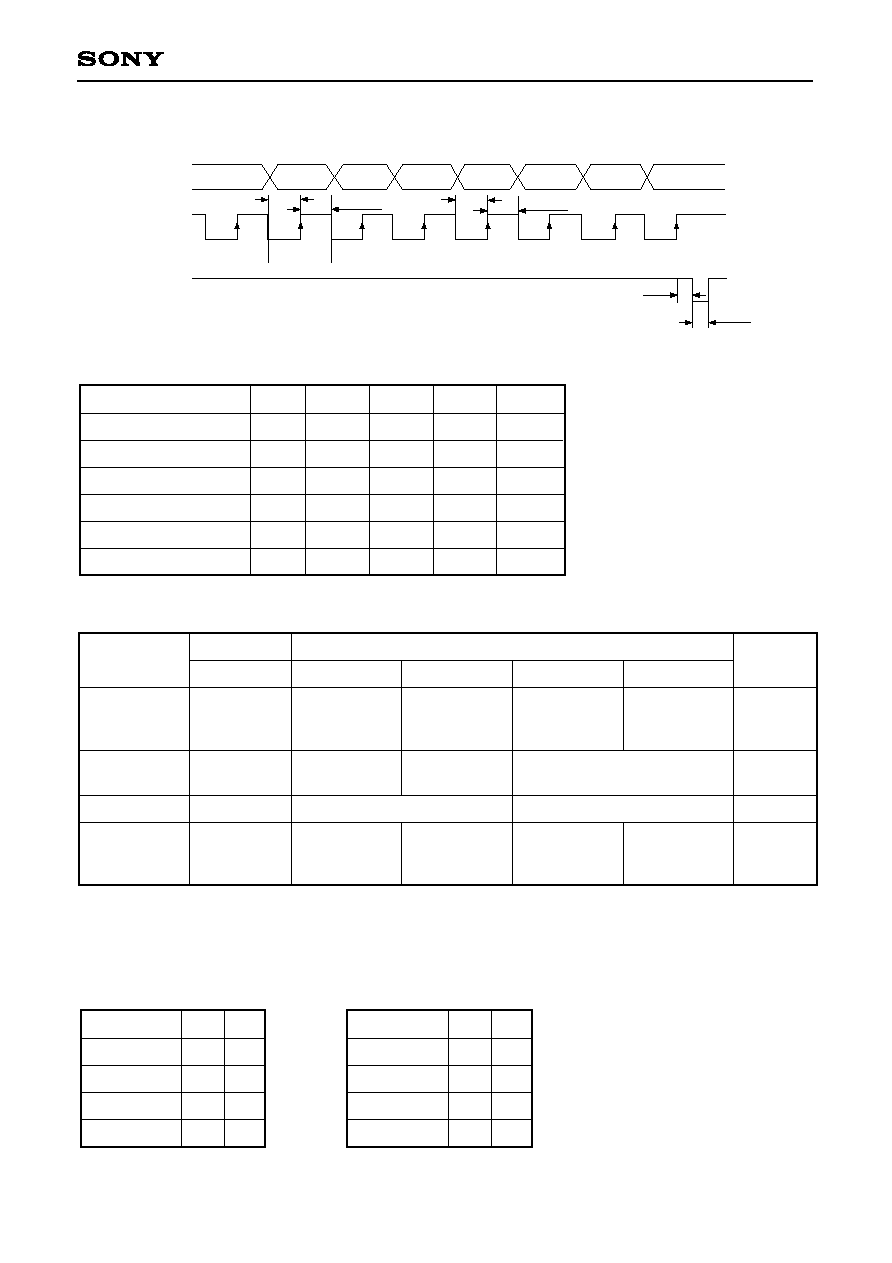

CPU Serial Interface Timing Chart

t

WCK

D0

D1

D2

D3

D4

D5

D6

D7

t

WCK

t

SU

1/fck

t

h

t

WL

t

D

DATA

CLK

XLT

Item

Clock frequency

Clock pulse width

Setup time

Hold time

Delay time

Latch pulse width

Symbol

fck

fwck

t

su

t

h

t

D

t

WL

Min.

500

500

500

1000

1000

Typ.

Max.

Unit

MHz

ns

ns

ns

ns

ns

1

(DV

CC

≠ DGND = 4.5 to 5.5V)

System Control

Focus control

Tracking

control

Tracking mode

Select

D7 D6 D5 D4

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

FS4

Focus

ON

Anti-shock

PS4

Focus

search + 2

PS3

Focus

search + 1

PS2

Sled kick + 2

PS1

Sled kick + 1

FS3

Gain

Down

Brake

ON

FS2

Search

ON

TG2

Gain set

1

FS1

Search

Up

TG1

FZC

A. S

TZC

SSTOP

Tracking mode

2

Sled mode

3

Address

D3

D2

D1

D0

Data

SENS

output

2

Tracking mode

FWD JUMP

REV JUMP

D3

0

0

1

1

D2

0

1

0

1

OFF

ON

3

Sled mode

FWD MOVE

REV MOVE

D1

0

0

1

1

D0

0

1

0

1

OFF

ON

Item

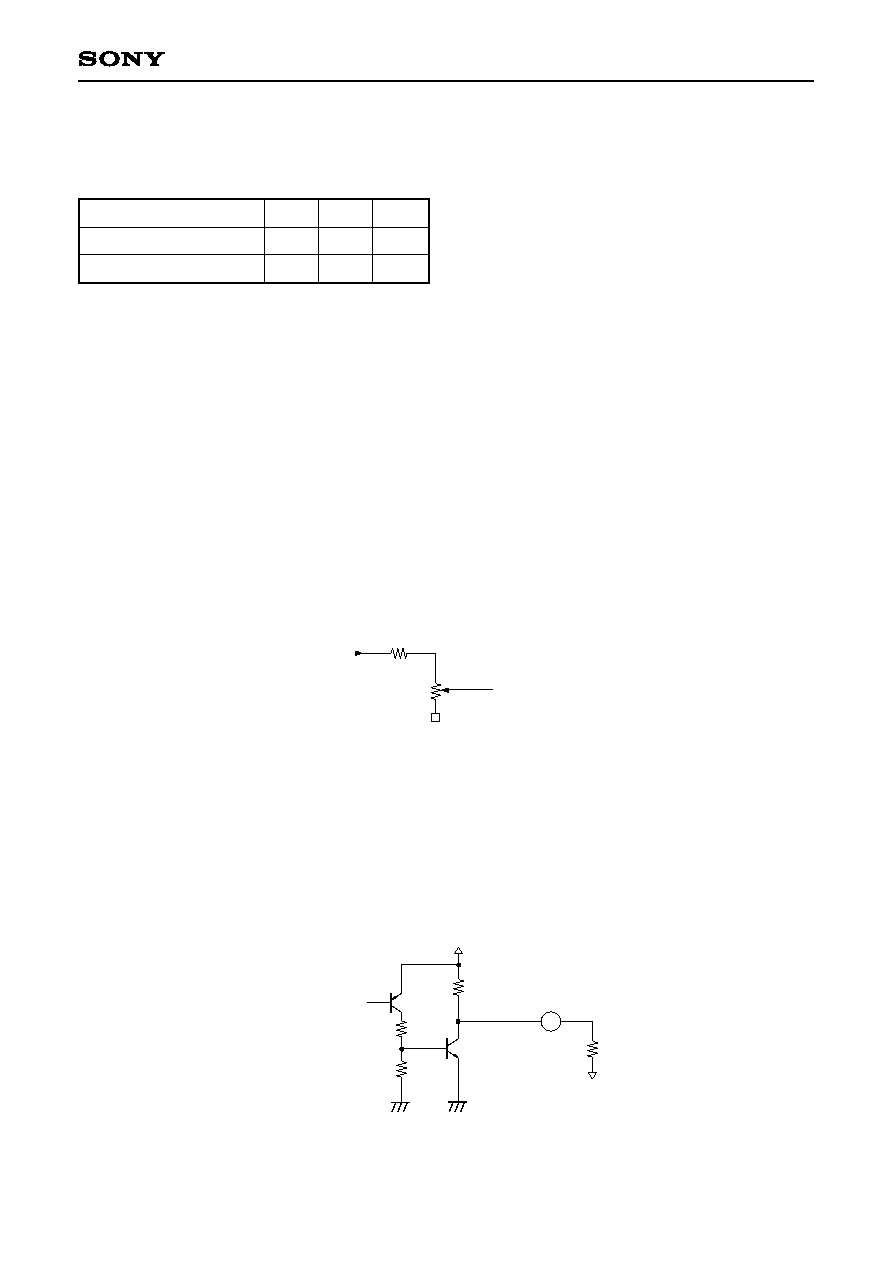

1

Gain set

TG1 and TG2 can be set independently.

When the anti-shock is at 1 (00011xxx), both TG1 and TG2 are inverted when the internal anti-shock is at High.

≠ 26 ≠

CXA1372BQ/BS

Serial Data Truth Table

FOCUS CONTROL

TRACKING CONTROL

TRACKING MODE

DIRC = 1 DIRC = 0 DIRC = 1

TM = 654321

654321

654321

AS = 0 AS = 1

TG = 2 1

TG = 2 1

Hex.

Function

FS = 4 3 2 1

$00

$01

$02

$03

$04

$05

$06

$07

$08

$09

$0A

$0B

$0C

$0D

$0E

$0F

$10

$11

$12

$13

$14

$15

$16

$17

$18

$19

$1A

$1B

$1C

$1D

$1E

$1F

Serial data

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1

0 0 0 0 0 0 1 0

0 0 0 0 0 0 1 1

0 0 0 0 0 1 0 0

0 0 0 0 0 1 0 1

0 0 0 0 0 1 1 0

0 0 0 0 0 1 1 1

0 0 0 0 1 0 0 0

0 0 0 0 1 0 0 1

0 0 0 0 1 0 1 0

0 0 0 0 1 0 1 1

0 0 0 0 1 1 0 0

0 0 0 0 1 1 0 1

0 0 0 0 1 1 1 0

0 0 0 0 1 1 1 1

0 0 0 1 0 0 0 0

0 0 0 1 0 0 0 1

0 0 0 1 0 0 1 0

0 0 0 1 0 0 1 1

0 0 0 1 0 1 0 0

0 0 0 1 0 1 0 1

0 0 0 1 0 1 1 0

0 0 0 1 0 1 1 1

0 0 0 1 1 0 0 0

0 0 0 1 1 0 0 1

0 0 0 1 1 0 1 0

0 0 0 1 1 0 1 1

0 0 0 1 1 1 0 0

0 0 0 1 1 1 0 1

0 0 0 1 1 1 1 0

0 0 0 1 1 1 1 1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

0 0

0 0

0 1

0 1

1 0

1 0

1 1

1 1

0 0

0 0

0 1

0 1

1 0

1 0

1 1

1 1

0 0

1 1

0 1

1 0

1 0

0 1

1 1

0 0

0 0

1 1

0 1

1 0

1 0

0 0

1 1

0 1

000000

001000

000011

000010

001010

000011

010000

011000

100001

100000

101000

100001

000001

000100

000011

000011

000110

000011

010001

010100

100001

100001

100100

100001

000100

001000

000011

000110

001010

000011

010100

011000

100001

100100

101000

100001

001000

000100

000011

001010

000110

000011

011000

010100

100001

101000

100100

100001

$20

$21

$22

$23

$24

$25

$26

$27

$28

$29

$2A

$2B

$2C

$2D

$2E

$2F

0 0 1 0 0 0 0 0

0 0 1 0 0 0 0 1

0 0 1 0 0 0 1 0

0 0 1 0 0 0 1 1

0 0 1 0 0 1 0 0

0 0 1 0 0 1 0 1

0 0 1 0 0 1 1 0

0 0 1 0 0 1 1 1

0 0 1 0 1 0 0 0

0 0 1 0 1 0 0 1

0 0 1 0 1 0 1 0

0 0 1 0 1 0 1 1

0 0 1 0 1 1 0 0

0 0 1 0 1 1 0 1

0 0 1 0 1 1 1 0

0 0 1 0 1 1 1 1

≠ 27 ≠

CXA1372BQ/BS

GND

C26

GND

GND

WFCK

XRAOF

GND

FOK

FSW

MON

MDP

MDS

LOCK

NC

VCOO

VCOI

TEST

PDO

V

SS

NC

NC

NC

VPCO

VCKI

FILO

FILI

PCO

AV

SS

CLTV

AV

DD

RF

2

5

6

7

8

9

10

11

12

13

14

15

16

18

19

20

21

22

23

1

SBSO

SCOR

WFCK

EMPH

DOUT

MD2

C16M

C4M

FSTT

XTSL

XTAO

XTAI

V

SS

APTL

APTR

MNT0

MNT1

MNT2

MNT3

XRAOF

C2PO

RFCK

GFS

XPLCK

25

26

27

28

29

30

40

39

38

37

36

35

34

31

32

33

BIAS

ASYI

ASYO

ASYE

NC

PSSL

WDCK (48)

LRCK (48)

V

DD

DATA (48)

BCLK (48)

DATA (64)

BCLK (64)

LRCK (64)

GTOP

XUGF

13

14

15

16

17

18

19

20

21

23

SL+

SL0

SL≠

FSET

ISET

SSTOP

AV

EE

DIRC

LOCK

CLK

XLT

DATA

28

29

30

36

35

34

31

32

33

DV

CC

CC2

CC1

FOK

EFM

ASY

DFCT

MIRR

DGND

SENS

C.OUT

XRST

FDFCT

FE

FZC

ATSC

TDFCT

TE

TZC

DV

EE

RFO

RFI

CP

CB

40

39

38

37

41

42

43

44

45

46

47

48

GND

GND

GND

GND

200p

1M

AV

DD

GND

GND

V

SS

GND

V

CC

C2PO

MUTE

BCLK

DATA

WDCK

LRCK

DEMP

GND

MNT0

MNT1

MNT2

MNT3

GND

GTOP

UGFS

GFS

RFCK

XPLCK

DOUT

GND

GND

GND

V

DD

MUTE

SCOR

SQCK

SUBQ

GFS

CLK

XLT

DATA

XRST

SENS

FOK

LDON

DFCT

MIRR

FE

TE

RF

LDON

V

CC

V

O

V

CC

C17

GND

GND

C15

C16

GND

C14

C13

C11

C12

GND

GND

RV2

RV1

RF

TE

FE

GND

C9

GND

C10

GND

C23

TRACK-D

GND

FOCUS-D

GND

SLED-D

GND

SPIND-D

GND

SSTOP

GND

R1

GND

C28

GND

C27

R6

R7

GND

R3

R4

SPD

SLD

FD

TD

GND

GND

R10

GND

R12

CXD2500AQ

VC

FGD

FS3

FLB

FEO

FE≠

SRCH

TGU

TG2

AV

CC

TA0

TA≠

2

3

4

5

6

7

8

9

10

11

12

1

CXA1372BQ

R1

R1

70

69

68

67

65

66

71

72

73

74

75

76

77

78

79

80

MIRR

CLKO

XLTO

DATO

CNIN

SEIN

CLOK

V

DD

XLAT

DATA

XRST

SENS

MUTE

SQCK

SQSO

EXCK

22

24

4

3

17

GND

GND

41

42

43

44

45

46

47

48

49

50

51

53

54

55

56

57

58

59

60

63

64

61

62

27

25

26

24

GND

R14

R13

GND

GND

52

PCM

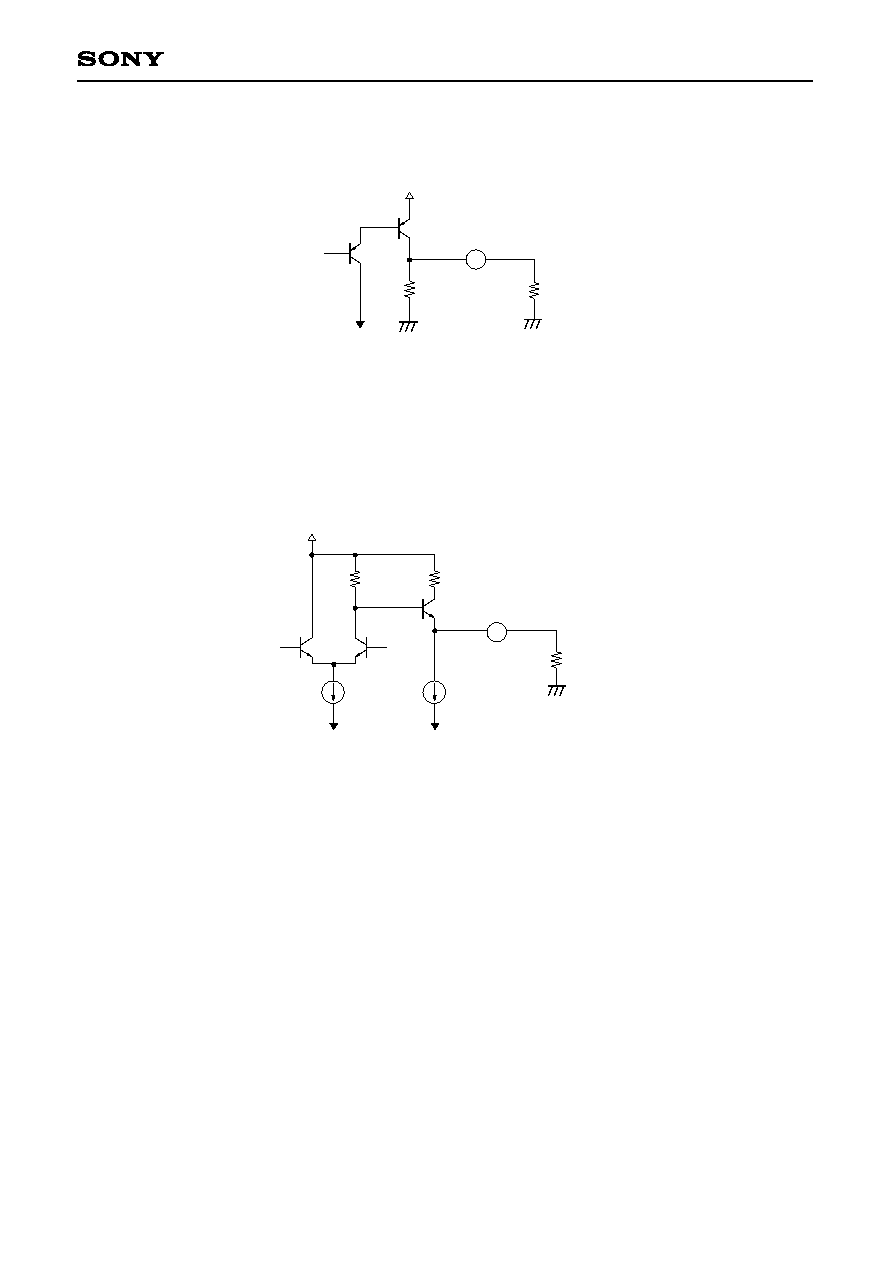

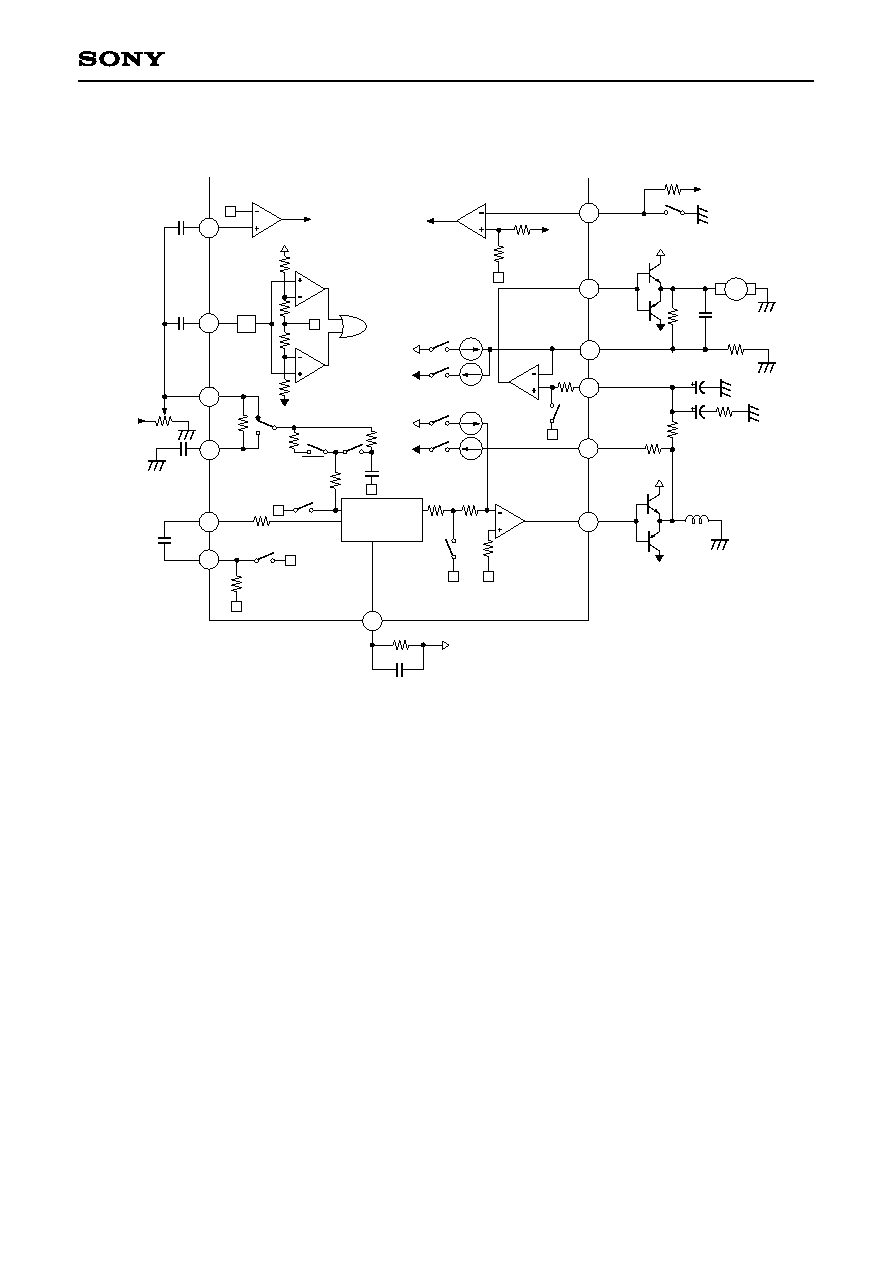

Application Circuit

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

≠ 28 ≠

CXA1372BQ/BS

Notes on Operation

1. Connection of the power supply pin

2. FSET pin

The FSET pin determines the cut-off frequency fc for the focus and tracking high-frequency phase compensation.

3. ISET pin

ISET current = 1.27V/R

= Focus search current

= Tracking jump current

= 1/2 sled kick current

4. The tracking amplifier input is clamped at 1V

BE

to prevent overinput.

5. FE (focus error) and TE (tracking error) gain changing method

(1) High gain: Resistance between FE pins (Pins 5 and 6) 100k

Large

Resistance between TA pins (Pins 11 and 12) 100k

Large

(2) Low gain: A signal, whose resistance is divided, is input to FE and TE.

6. Input voltage of microcomputer interface Pins 20 to 25, should be set as follows.

V

IH

V

CC

◊

90% or more

V

IL

V

CC

◊

10% or less

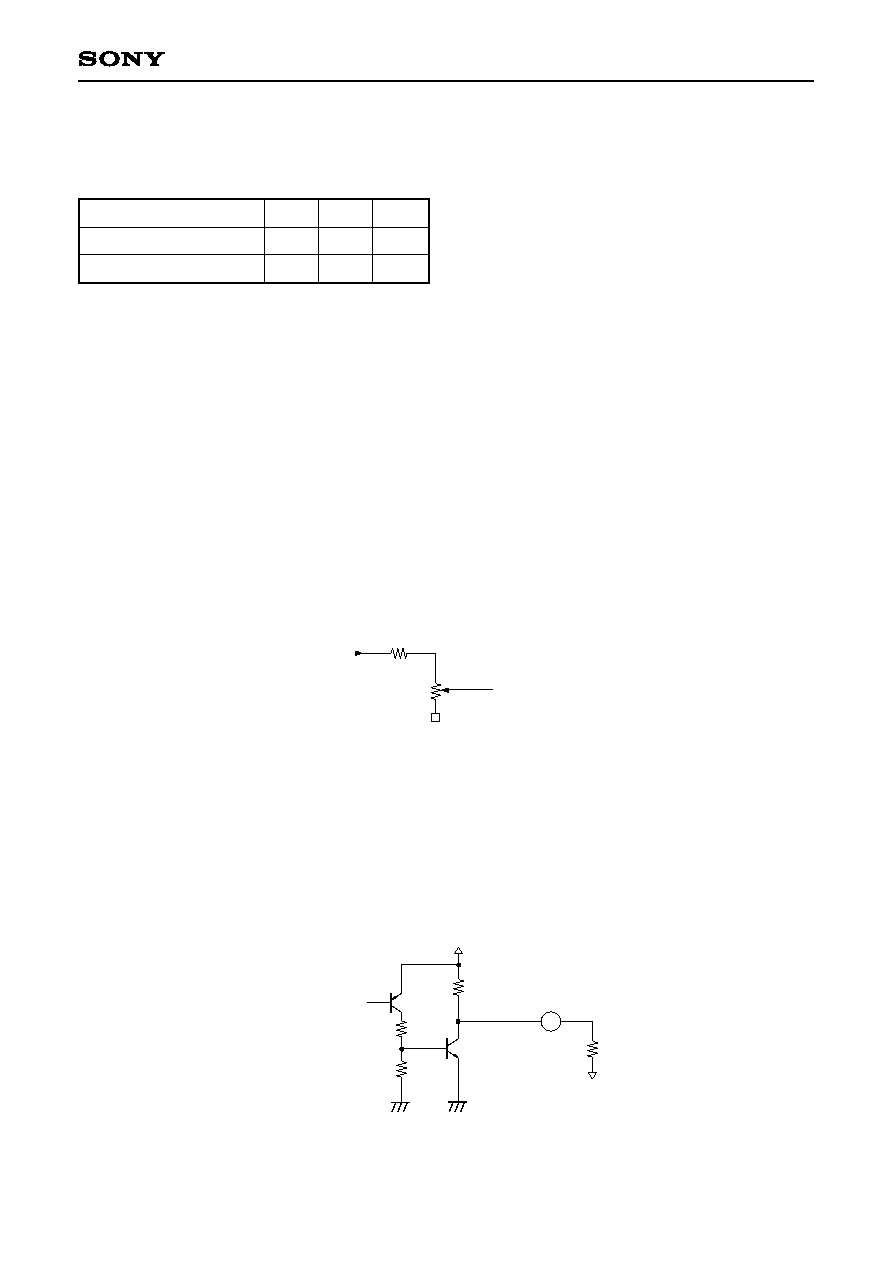

7. Focus OK circuit

(1) Refer to the "Description of Operation" for the time constant setting of the focus OK amplifier LPF and the

mirror amplifier HPF.

(2) The equivalent circuit of FOK output pin is as follows.

V

CC

20k

50k

100k

DGND

R

L

FOK

V

CC

DGND

33

FOK comparator output is:

Output voltage High: V

FOKH

near Vcc

Output voltage Low: V

FOKL

Vsat

(NPN)

+ DGND

dual Ī5V power supplies

+5V

0V

VC

+5V

≠5V

0V

single 5V power supplies

Vcc

V

EE

VC

FE

TE

≠ 29 ≠

CXA1372BQ/BS

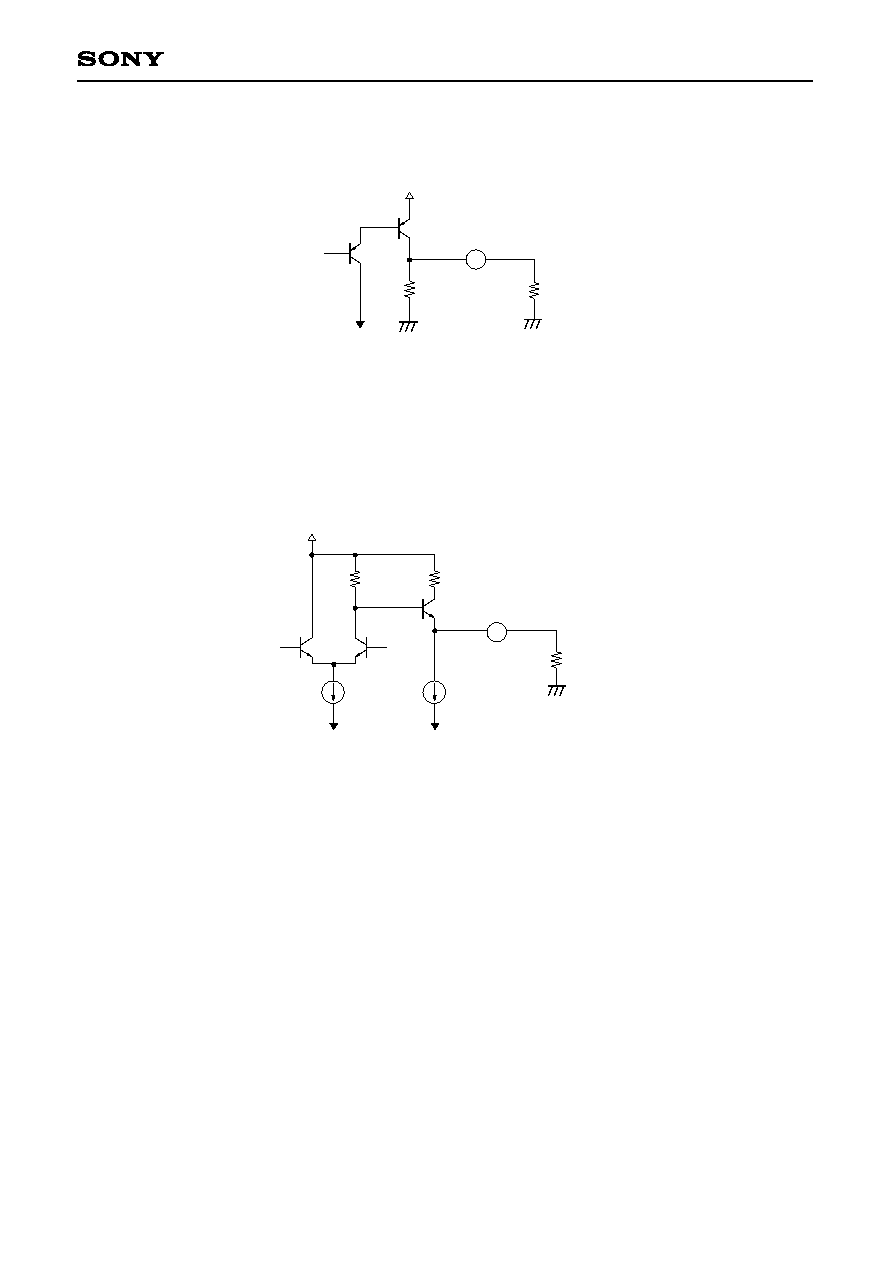

8. Mirror Circuit

(1) The equivalent circuit of MIRR output pin is as follows.

MIRR comparator output is:

Output voltage High: V

MIRH

V

CC

≠ Vsat

(LPNP)

Output voltage Low: V

MIRL

near DGND

9. EFM Comparator

(1) Note that EFM duty varies when the CXA1372 Vcc differs from that of DSP IC (such as the CXD2500).

(2) The equivalent circuit of the EFM output pin is as follows.

When the power supply current between Vcc and DGND is 5V.

EFM comparator output is:

Output voltage High: V

EFMH

V

CC

≠ V

BE (NPN)

Output voltage Low: V

EFML

V

CC

≠ 4.8 (k

)

◊

700 (ĶA) ≠ V

BE (NPN)

700ĶA

4.8k

50

2mA

32

EFM

R

L

DGND

Vcc

V

EE

DGND

20k

MIRR

R

L

DGND

29

≠ 30 ≠

CXA1372BQ/BS

Standard Circuit Design Data for Focus/Tracking Internal Phase Compensation

S1

S2

S3

S4

S5

S6

S7

S8

S9

E1

E2

E3

E4

SD

Measure-

ment

point

Description of output

waveform and measurement

method

5

5

5

5

11

11

11

11

08

08

0C

0C

25

25

25

13

25

13

Unit

Max.

Typ.

Min.

Symbol

Bias condition

SW condition

1.2kHz gain

1.2kHz phase

1.2kHz gain

1.2kHz phase

1.2kHz gain

1.2kHz phase

2.7kHz gain

2.7kHz phase

O

O

O

O

21.5

63

16

63

13

≠125

26.5

≠130

dB

deg

dB

deg

dB

deg

dB

deg

When C

FLB

= 0.1Ķ

F

TRACKING

FOCUS

Item

Mode

O

O

O

O

≠ 31 ≠

CXA1372BQ/BS

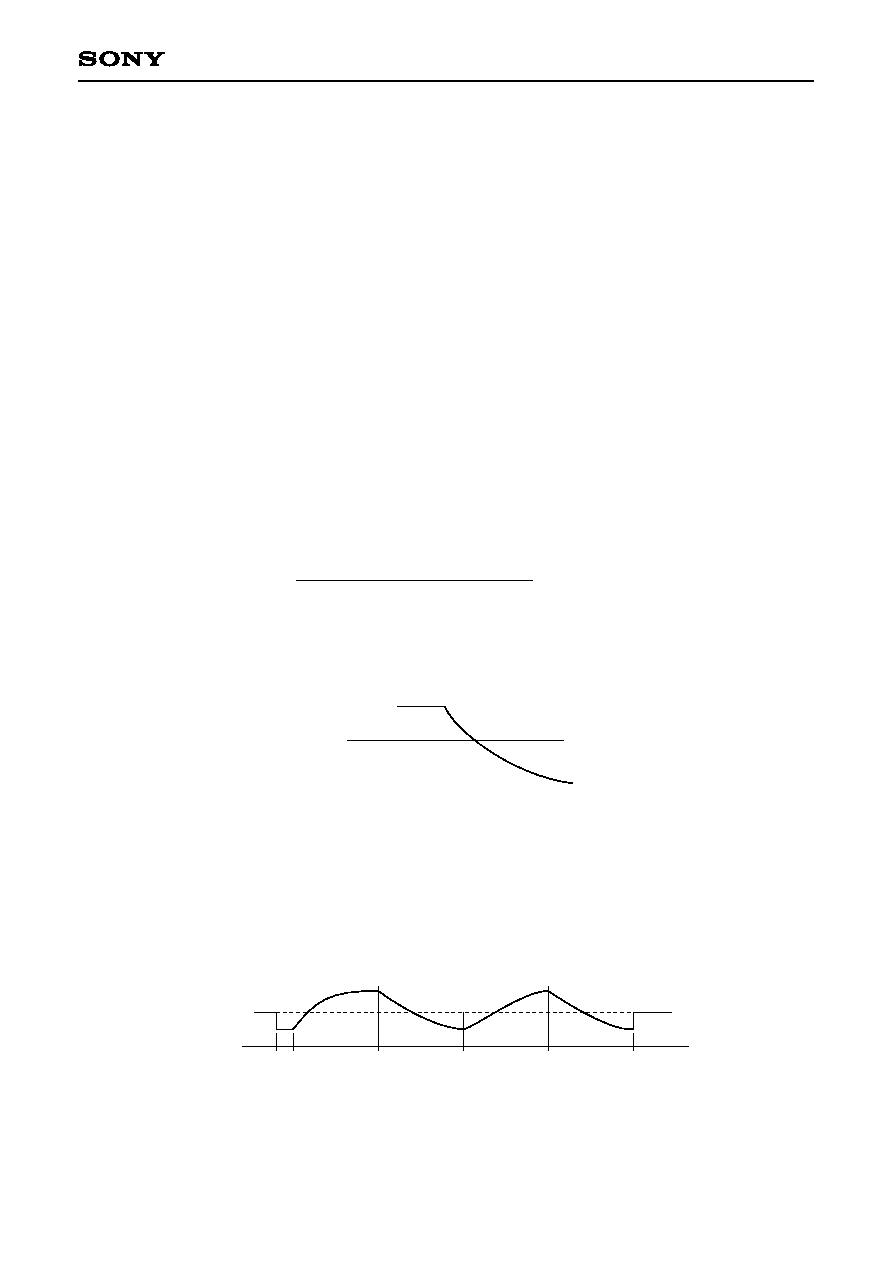

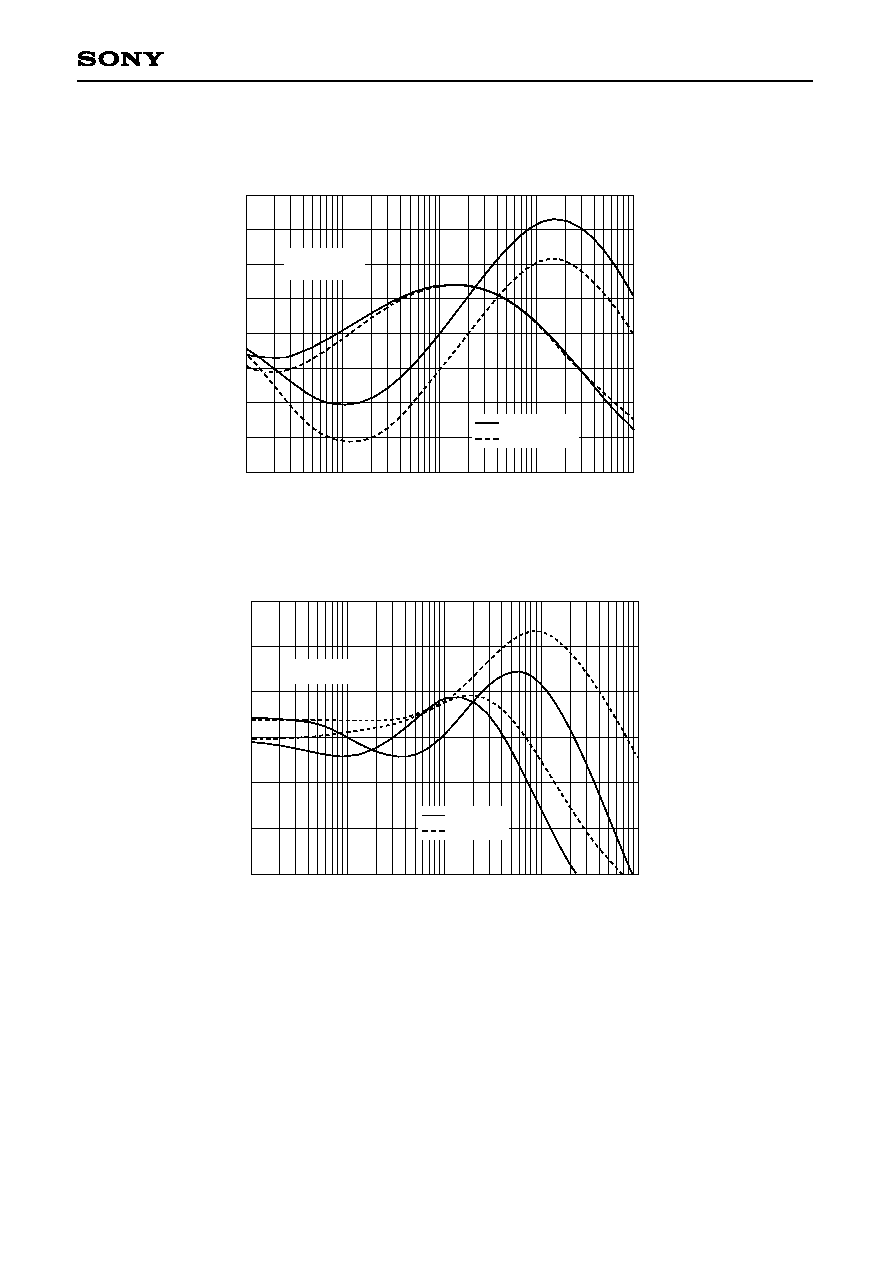

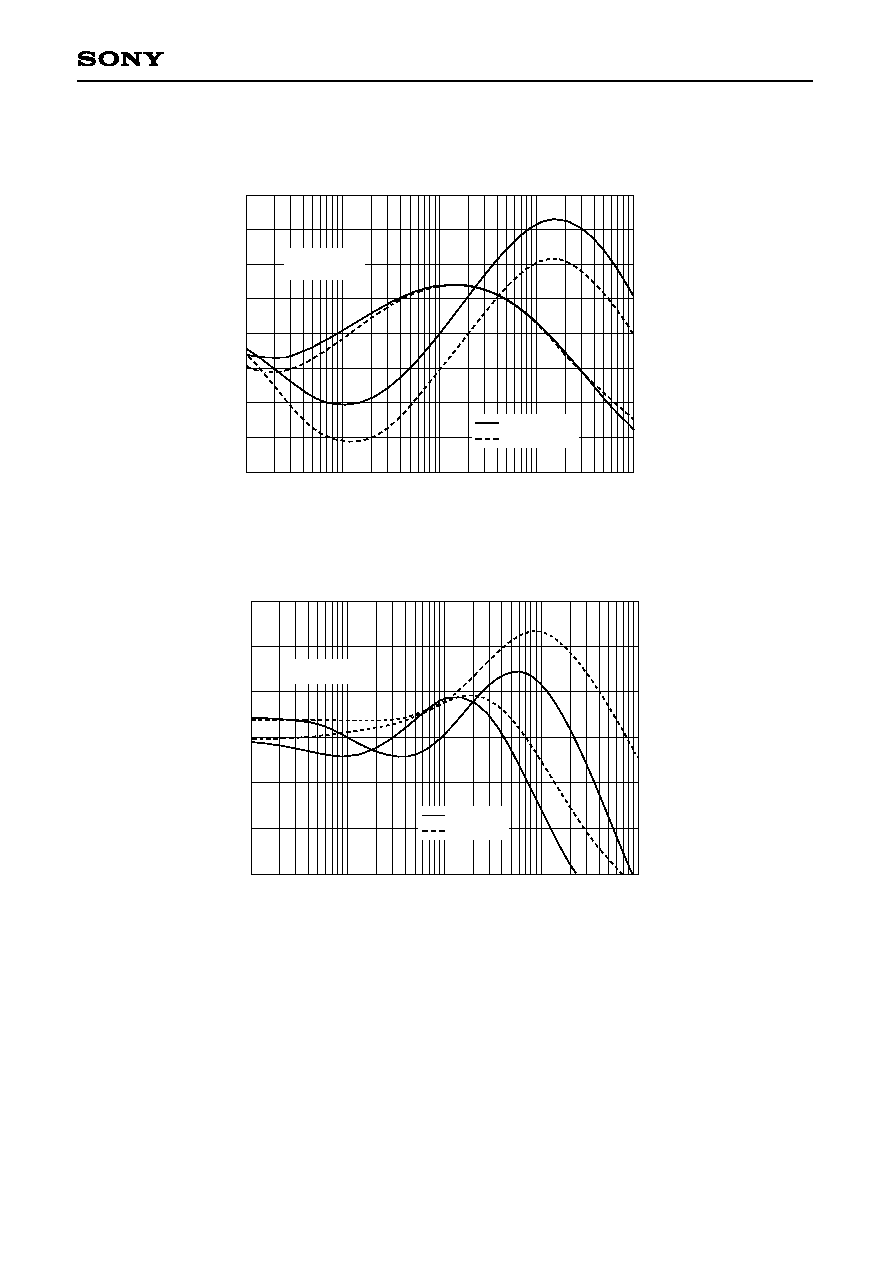

Example of Representative Characteristics

40

35

30

25

20

15

10

5

10

1

10

2

10

3

10

4

10

5

≠180

≠135

≠90

≠45

0

45

90

135

180

f ≠ Frequency [Hz]

G ≠ Gain [dB]

≠ Phase [degree]

FOCUS frequency characteristics

40

30

20

10

0

≠10

≠20

10

1

10

2

10

3

10

4

10

5

f ≠ Frequency [Hz]

G ≠ Gain [dB]

≠ Phase [degree]

Tracking frequency characteristics

G

G

0

180

120

60

0

≠60

≠120

≠180

C

TGU

= 0.033Ķ

GAIN UP

NORMAL

C

FGD

= 0.1Ķ

C

FLB

= 0.1Ķ

GAIN DOWN

NORMAL

≠ 32 ≠

CXA1372BQ/BS

Package Outline

Unit: mm

CXA1372BQ

CXA1372BS

SONY CODE

EIAJ CODE

JEDEC CODE

M

PACKAGE STRUCTURE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE WEIGHT

EPOXY RESIN

SOLDER / PALLADIUM

PLATING

COPPER / 42 ALLOY

48PIN QFP (PLASTIC)

15.3 Ī 0.4

12.0 ≠ 0.1

+ 0.4

0.8

0.3 ≠ 0.1

+ 0.15

Ī 0.12

13

24

25

36

37

48

1

12

2.2 ≠ 0.15

+ 0.35

0.9 Ī

0.2

0.1 ≠ 0.1

+ 0.2

13.5

0.15

0.15 ≠ 0.05

+ 0.1

QFP-48P-L04

QFP048-P-1212-B

0.7g

48PIN SDIP (PLASTIC) 600mil

13.0

+ 0.3 ≠ 0.1

4.6

+ 0.4 ≠ 0.1

0.25

+ 0.1

≠ 0.05

48

25

1

24

1.778

15.24

0į to 15į

0.5 Ī 0.1

0.9 Ī 0.15

3.0 MIN

0.5 MIN

SONY CODE

EIAJ CODE

JEDEC CODE

PACKAGE STRUCTURE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE WEIGHT

EPOXY RESIN

SOLDER PLATING

COPPER / 42 ALLOY

5.1g

SDIP-48P-02

SDIP048-P-0600-A

43.2

+ 0.4

≠ 0.1