| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXA1396D | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

≠ 1 ≠

CXA1396D

E94521A79-PS

8-bit 125 MSPS Flash A/D Converter

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

AV

EE

LINV

DV

EE

DGND1

DGND2

(LSB) D0

D1

D2

D3

D4

D5

D6

(MSB) D7

DGND2

DGND1

DV

EE

MINV

CLK

CLK

22

23

24

25

26

27

28

29

30

40

39

38

37

36

35

34

31

32

33

41

42

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

1

V

RT

AV

EE

AV

EE

AGND

V

IN

AGND

V

RM

AGND

V

IN

AGND

AV

EE

AV

EE

V

RB

(Top View)

Description

The CXA1396D are 8-bit ultrahigh-speed flash A/D

converter ICs capable of digitizing analog signals at

the maximum rate of 125 MSPS. The digital I/O

levels of these A/D converters are compatible with

the ECL 100K/10KH/10K.

The CXA1396D is pin-compatible with the earlier

model CX20116. They can replace the earlier models

respectively, without any design changes, in most

cases. Compared with the earlier models, these new

models have been greatly improved in performance,

by incorporating advanced process, new circuit

design and carefully considered layout.

Features

∑ Ultrahigh-speed operation with maximum

conversion rate of 125 MSPS (Min.)

∑ Wide analog input bandwidth: 200MHz (Min. for

full-scale input)

∑ Low power consumption: 870mW (Typ.)

∑ Single power supply: ≠5.2V

∑ Low input capacitance

∑ Built-in integral linearity compensation circuit

∑ Low error rate

∑ Operable at 50% clock duty cycle

∑ Good temperature charactcristics

∑ Capable of driving 50

loads

Structure

Bipolar silicon monolithic IC

Applications

∑ Digital oscilloscopes

∑ HDTV (high-definition TVs)

∑ Other apparatus requiring ultrahigh-speed A/D

conversion

Pin Configuration

Pins without name are NC pins (not connected).

42 pin DIP (Ceramic)

≠ 2 ≠

CXA1396D

Absolute Maximum Ratings (Ta = 25∞C)

∑ Supply voltage

AV

EE

, DV

EE

≠7 to +0.5

V

∑ Analog input voltage

V

IN

≠2.7 to +0.5

V

∑ Reference input voltage

V

RT

, V

RB

, V

RM

≠2.7 to +0.5

V

V

RT

≠ V

RB

2.5

V

∑ Digital input voltage

CLK, CLK, MINV, LINV

≠4 to +0.5

V

CLK ≠ CLK

2.7

V

∑ V

RM

pin input curent

I

VRM

≠3 to +3

mA

∑ Digital output current

ID

0

to ID

7

≠30 to 0

mA

∑ Storage temperature

Tstg

≠65 to +150

∞C

Recommended Operating Conditions

Min.

Typ.

Max.

unit

∑ Supply voltage

AV

EE

, DV

EE

≠5.5

≠5.2

≠4.95

V

AV

EE

≠ DV

EE

≠0.05

0

+0.05

V

AGND ≠ DGND

≠0.05

0

+0.05

V

∑ Reference input voltage

V

RT

≠0.1

0

+0.1

V

V

RB

≠2.2

≠2.0

≠1.8

V

∑ Analog input voltage

V

IN

V

RB

V

RT

∑ Pulse width of clock

T

PW1

4.0

ns

T

PW0

4.0

ns

∑ Operating temperature

Ta

≠20

+75

∞C

≠ 3 ≠

CXA1396D

Block Diagram

255

126

127

128

129

191

192

193

254

63

64

65

1

2

CLOCK

DRIVER

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

r

3

r

1

r

2

r/2

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r/2

D7 (MSB)

D6

D4

D3

D5

D2

D1

D0 (LSB)

O

U

T

P

U

T

E

N

C

O

D

E

L

O

G

I

C

MINV

V

RT

V

IN

V

RM

V

IN

V

RB

CLK

CLK

LINV

Comparator

≠ 4 ≠

CXA1396D

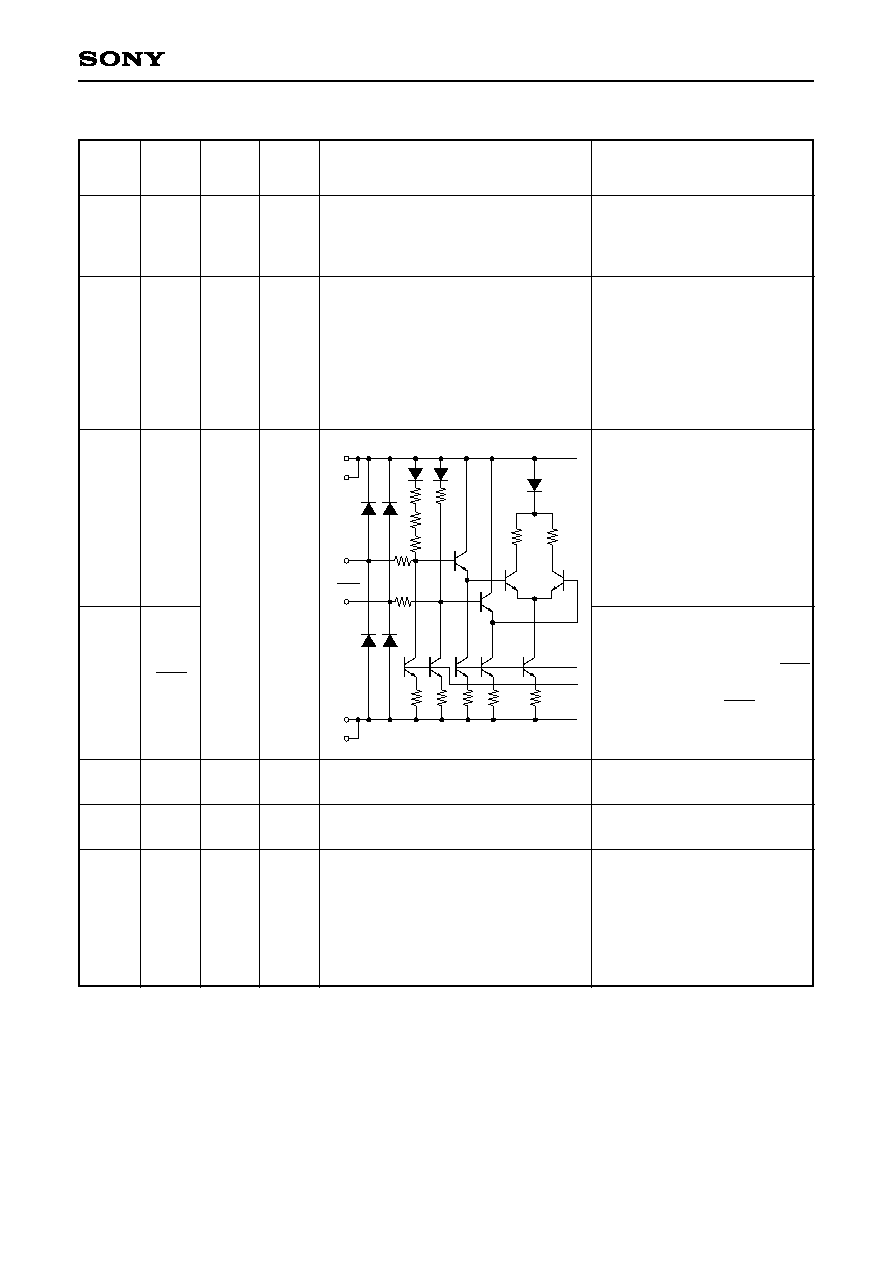

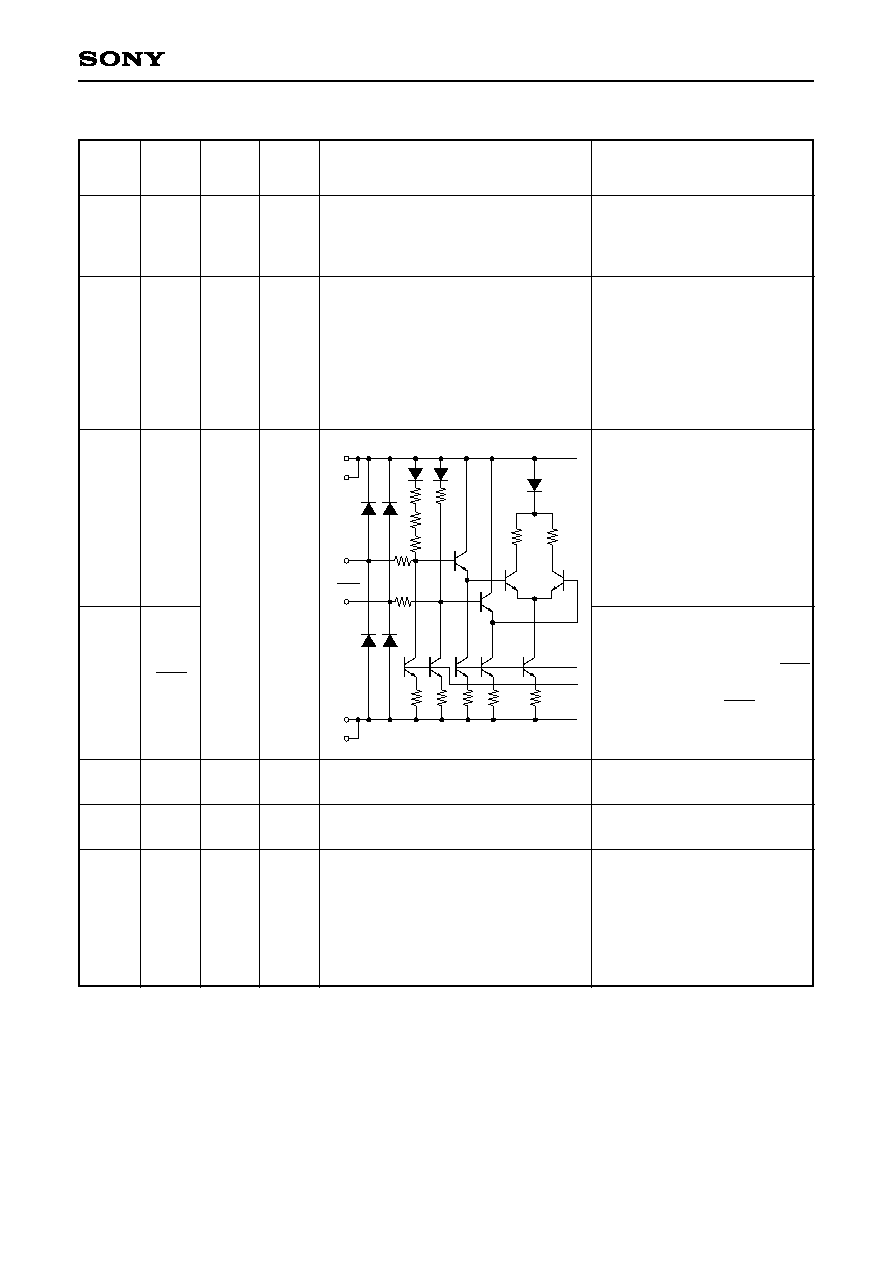

Pin Description and I/O Pin Equivalent Circuit

Analog GND.

Used as GND for input buffers

and latches of comparators.

Isolated from DGND1, DGND2.

29, 31,

33, 35

AGND

--

0V

1, 25,

26, 38,

39

21

20

5, 16

6, 15

DGND2

--

0V

4, 17

DV

EE

--

≠5.2V

DGND1

--

0V

CLK

CLK

I

ECL

AV

EE

--

≠5.2V

Analog V

EE

.

≠5.2V (Typ.).

Internally connected with DV

EE

(resistance: 4 to 6

).

A ceramic chip capacitor of at

least 0.1µF should be used to

connect to AGND and be

placed near the pins.

CLK input

Complementary input to CLK.

With open connection, kept at

threshold voltage (≠1.3V).

Device is operable without CLK

input, but use of omplementary

inputs of CLK and CLK is

recommended to obtain the

stable high-speed operation.

Digital GND for internal

circuits.

Digital GND for output

transistors.

Digital V

EE

.

Internally connected with AV

EE

(resistance: 4 to 6

).

A ceramic chip capacitor of at

least 0.1µF should be used to

connect to DGND near the

pins.

Pin No. Symbol

I/O

Standard

voltage

level

Equivalent circuit

Description

r

r

r

r

r

r

DGND1

CLK

CLK

DV

EE

≠ 5 ≠

CXA1396D

LSB of data outputs.

External pull-down resistor is

required.

Data outputs.

External pull-down resistors

are required.

MSB of data outputs.

External pull-down resistor is

required.

Input pin for D0 (LSB) to D6

output polarity inversion (see

output code table).

With open connection, kept at

"L" level.

Input pin for D7(MSB) output

polarity inversion (see output

code table).

With open connection, kept at

"L" level.

Analog input pins.

These two pins must be

connected externally, since

they are not internally

connected.

See Application Note for

precautions.

7

14

3

18

30, 34

V

IN

I

V

RT

to

V

RB

MINV

I

ECL

LINV

I

ECL

D7

8

9

10

11

12

13

D1

D2

D3

D4

D5

D6

D0

O

ECL

Pin No. Symbol

I/O

Standard

voltage

level

Equivalent circuit

Description

DGND2

DV

EE

Di

r

r

r

r

LINV

or

MINV

DGND1

DV

EE

≠1.3V

AGND

AV

EE

V

IN

V

IN

≠ 6 ≠

CXA1396D

Reference voltage (bottom).

Typically ≠2V.

A ceramic capacitor of at least

0.1µF and a tantalum capacitor

of at least 10µF should be

used to connect to AGND near

the pins.

Reference voltage mid point.

Can be used as a pin for

integral linearity compensation.

Reference voltage (top).

Typically 0V.

When a voltage except for

AGND is applied to this pin, a

ceramic capacitor of at least

0.1µF and a tantalum capacitor

of at least 10µF should be used

to connect to AGND near the

pins.

Unused pins.

No internal connections have

been made to these pins.

Connecting them to AGND or

DGND on PC board is

recommended.

23

32

41

2, 19,

22, 24,

27, 28,

36, 37,

40, 42

NC

--

--

V

RT

I

0V

V

RM

I

V

RB

/2

V

RB

I

≠2V

Pin No. Symbol

I/O

Standard

voltage

level

Equivalent circuit

Description

.

.

.

Comparator

1

Comparator

2

Comparator

127

Comparator

128

Comparator

129

Comparator

130

Comparator

255

.

.

.

.

.

.

.

r/2

r

r

r

r

r

r

r

r/2

r

3

r

2

r

1

V

RT

V

RM

V

RB

≠ 7 ≠

CXA1396D

Electrical Characteristics

(Ta = 25∞C, AV

EE

= DV

EE

= ≠5.2V, V

RT

= 0V, V

RB

= ≠2V)

Item

Resolution

DC characteristics

Integral linearity error

Differential linearity error

Analog input

Analog input capacitance

Analog input resistance

Input bias current

Reference inputs

Reference resistance

Offset voltage

V

RT

V

RB

Digital inputs

Logic H level

Logic L level

Logic H current

Logic L current

Input capacitance

Switching characteristics

Maximum conversion rate

Aperture jitter

Sampling delay

Output delay

H pulse width of clock

L pulse width of clock

Digital outputs

Logic H level

Logic L level

Output rising time

Output falling time

Dynamic characteristics

Input bandwidth

S/N ratio

Error rate

Differential gain error

Differential phase error

Power supply

Supply current

Power consumption

2

n

E

IL

E

DL

C

IN

R

IN

I

IN

R

REF

E

OT

E

OB

V

IH

V

IL

I

IH

I

IL

Fc

Taj

Tds

Tdo

T

PW1

T

PW0

V

OH

V

OL

Tr

Tf

DG

DP

I

EE

Pd

Fc = 125MSPS

Fc = 125MSPS

V

IN

= ≠1V + 0.07Vrms

V

IN

= ≠1V

Input connected to ≠0.8V

Input connected to ≠1.6V

Error rate 10

≠9

TPS

1

R

L

= 50

to ≠2V

R

L

= 50

to ≠2V

R

L

= 50

to ≠2V, 20% to 80%

R

L

= 50

to ≠2V, 80% to 20%

V

IN

= 2Vp-p, 3dB down

Input = 1MHz, FS

Clock = 125MHz

Input = 31.5MHz, FS

Clock = 125MHz

Input = 31.249MHz, FS

Error > 16LSB

Clock = 125MHz

NTSC 40IRE mod.ramp,

Fc = 125MSPS

75

8

0

≠1.13

0

≠50

125

3.0

4.0

4.0

≠1.10

200

≠230

8

±0.3

±0.3

17

190

130

110

19

15

7

10

1.5

3.6

0.8

1.0

46

40

1.0

0.5

≠160

870

±0.5

±0.5

320

155

32

24

≠1.50

50

50

4.2

≠1.62

10

≠9

bits

LSB

LSB

pF

k

µA

mV

mV

V

V

µA

µA

pF

MSPS

ps

ns

ns

ns

ns

V

V

ns

ns

MHz

dB

dB

TPS

1

%

deg

mA

mW

Symbol

Condition

Min.

Typ.

Max.

Unit

{

{

}

{

1

TPS: times Per Sample

2

Pd = I

EE

∑

V

EE

+

R

REF

(V

RT

≠ V

RB

)

2

≠ 8 ≠

CXA1396D

Output Code Table

V

IN

0V

≠1V

≠2V

0

1

127

128

254

255

0 0 0 ...... 0 0

0 0 0 ...... 0 0

0 0 0 ...... 0 1

:

:

0 1 1 ...... 1 1

1 0 0 ...... 0 0

:

:

1 1 1 ...... 1 0

1 1 1 ...... 1 1

1 1 1 ...... 1 1

1 0 0 ...... 0 0

1 0 0 ...... 0 0

1 0 0 ...... 0 1

:

:

1 1 1 ...... 1 1

0 0 0 ...... 0 0

:

:

0 1 1 ...... 1 0

0 1 1 ...... 1 1

0 1 1 ...... 1 1

0 1 1 ...... 1 1

0 1 1 ...... 1 1

0 1 1 ...... 1 0

:

:

0 0 0 ...... 0 0

1 1 1 ...... 1 1

:

:

1 0 0 ...... 0 1

1 0 0 ...... 0 0

1 0 0 ...... 0 0

1 1 1 ...... 1 1

1 1 1 ...... 1 1

1 1 1 ...... 1 0

:

:

1 0 0 ...... 0 0

0 1 1 ...... 1 1

:

:

0 0 0 ...... 0 1

0 0 0 ...... 0 0

0 0 0 ...... 0 0

Step

MINV 1

LINV 1

D7 D0

D7 D0

D7 D0

D7 D0

0

1

1

0

0

0

V

RT

= 0V, V

RB

= ≠2V

Timing diagram

Tds

Tr

Tf

80%

20%

80%

N + 1

20%

N

N ≠ 1

Tdo

Tpw0

Tpw1

N + 1

N + 2

N

Analog in

CLK

CLK

Digital out

≠ 9 ≠

CXA1396D

Electrical Characteristics Test Circuit

Maximum conversion rate test circuit

Comparator

A

>

B

Pulse

Counter

CXA1396D

Signal

Source

ECL

Latch

ECL

Latch

1/4

+

Signal

Source

f

CLK

4

≠ 1kHz

2Vp-p Sine Wave

f

CLK

V

in

CLK

CLK

8

DATA 16

A

B

Differential gain error test circuit

Differential phase error test circuit

DUT

CXA1396D

ECL

Latch

10bit

D/A

Vector

Scope

Delay

Amp

NTSC

Signal

Source

SG (CW)

50

CLK

CLK

10

V

IN

8

8

V

BB

DG.DP

(CX20202A-1)

DUT

CXA1396D

A < B A > B

Comparator

A8

A1

A0

B8

B1

B0

to

to

Buffer

Controller

DVM

8

8

8

"1"

"0"

00000000

to

11111110

CLK (125MHz)

V

IN

+V

≠V

S2

S1

S1: A

<

B: ON

S2: A

>

B: ON

Integral linearity error test circuit

Differential linearity error test circuit

≠ 10 ≠

CXA1396D

Power Supply Current Test Circuit

Analog input bias current test circuit

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

1

CXA1396D

A

A

≠1V

I

IN

≠2V

I

EE

≠5.2V

22

23

24

25

26

27

28

29

30

40

39

38

37

36

35

34

31

32

33

41

42

Sampling delay test circuit

Aperture jitter test circuit

Aperture jitter test method

CXA1396D

OSC1

: Variable

OSC2

Logic

Analizer

67.5MHz

67.5MHz

Amp

ECL

Buffer

CLK

V

IN

8

fr

1024

samples

V

IN

(LSB)

CLK

V

IN

CLK

t

v

t

0V

≠1V

≠2V

129

128

127

126

125

Aperture jitter

Apeature jitter is defined as follows:

Taj =

/ =

/( ),

Where

(unit : LSB) is the deviation of the output codes when the input

frequency is exactly the same as the clock and is sampled at the

largest slew rate point.

t

v

2

256

◊

2

f

≠ 11 ≠

CXA1396D

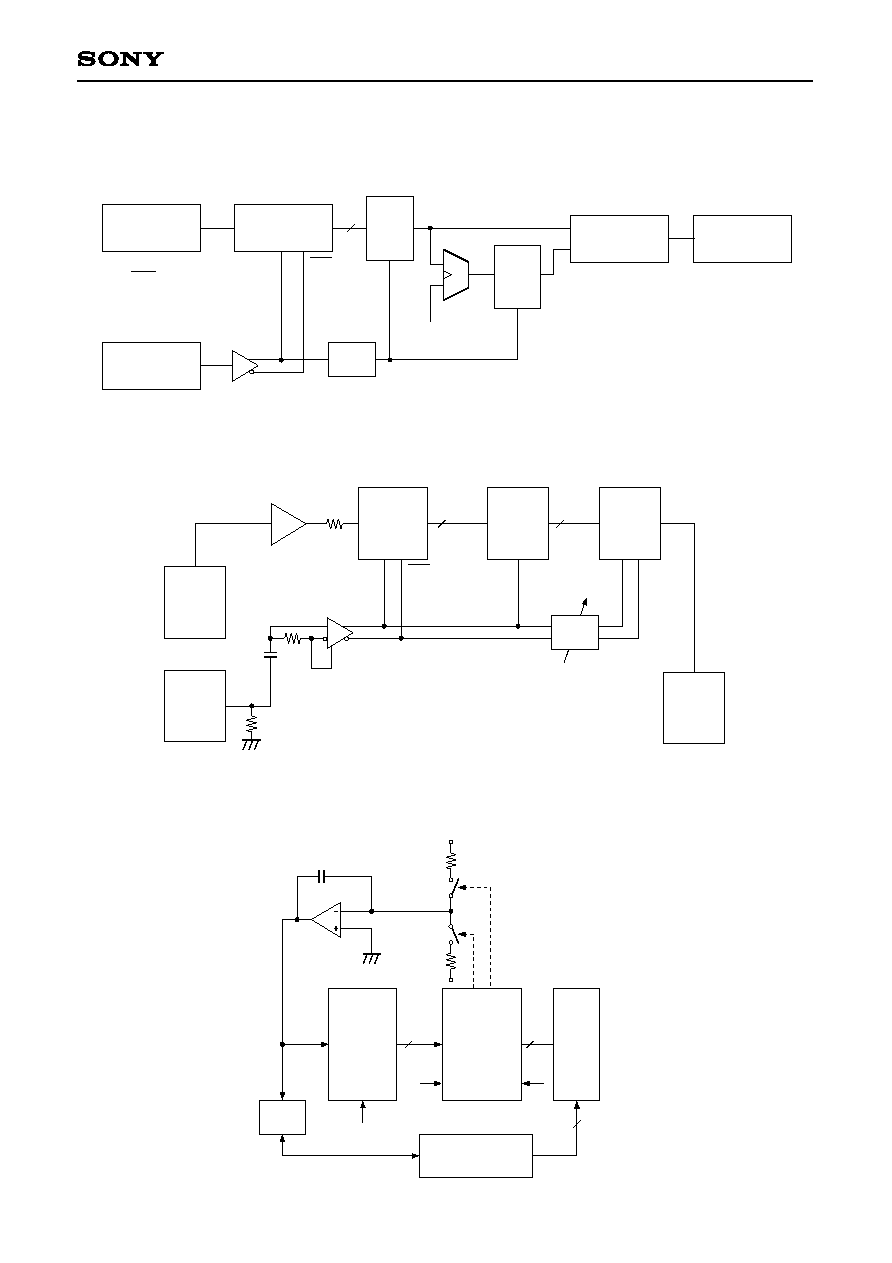

8-bit, 125MSPS ADC Evaluation board

Description

The CXA1396D EVALUATION BOARD WITH DAC is a tool for customers to evaluate the performance of the

CXA1396D (8-bit, 125MSPS, high-speed A/D converter). In addition to indispensable features such as the

reference voltage generator, this tool equips two sets of analog inputs (the direct input and the buffer amplifier

input), the input voltage offset generator, the clock decimator, the output data latches, the 10-bit high-speed

DAC, and the 20-pin cable connector for digital outputs.

This evaluation board provides full performance of the CXA1396D and it is designed to facilitate evaluation.

Features

∑ Resolution: 8bits

∑ Maximum conversion rate: 125MSPS

∑ Supply voltage: +5.0V, ≠5.2V, ≠2.0V

∑ Two analog inputs (Direct input, buffer amplifier input)

∑ Clock level converter: Sine wave to ECL level signal

∑ Reference voltage adjustment circuit for the A/D converter

∑ Built-in clock frequency decimation circuit: (1/1 to 1/16)

Fig. 1. Block Diagram

BUFFER

DATA

LATCH

LINV MINV

V

RB

V

RM

Vin

CLK

CXA1396D

Vin

OFFSET

DECIMATOR

D/A

CONVERTER

VRB

≠2V

SW3

CLK

SW1

SW2

L

H

≠5.2V (A)

≠5.2V (A)

V

R2

(2k)

V

R1

(2k)

AMP.IN

DIR.IN

CLK

240

51

51

0.1µ

J1

A

B

C

D

V

R3

(1k)

1k

8

8

8

(D

7

to D

0

)

DIGITAL OUT

(CONNECTOR)

8

(D

7

to D

0

)

2 (CLK.CLK)

CLK

D/A OUT

1/1 to 1/16

X (≠2)

≠5.2V (D)

DGND

≠2V (D)

≠5.2V (A)

AGND

+5V

≠ 12 ≠

CXA1396D

Supply Current

Item

Min.

Typ.

Max.

Unit

≠5.2V

+5.0V

≠2.0V

0.85

15

0.45

1.0

30

0.6

A

mA

A

(Note: Supply current ≠2.0V is the value when Rn10, Rn11 and Rn12 are not mounted.)

Analog Input (DIR. IN, AMP. IN)

Item

Min.

Typ.

Max.

Unit

Input voltage (DIR. IN)

(AMP. IN)

1

Input impedance

≠2.0

≠0.5

50

0

+0.5

V

V

(

1

: Adjustable by VR1)

Clock Input (CLK)

Item

Min.

Typ.

Max.

Unit

Input voltage

(Peak to Peak)

Input impedance

1.0

50

Vp-p

Digital Output (D0 to D7)

ECL 10KH level

Clock Output

ECL 10KH level, complementary output

Output Code Table

V

IN

1 1 1 ...... 1 1

1 1 1 ...... 1 0

:

:

1 0 0 ...... 0 0

0 1 1 ...... 1 1

:

:

0 0 0 ...... 0 1

0 0 0 ...... 0 0

0V

:

:

:

:

:

:

:

:

≠2V

1 0 0 ...... 0 0

1 0 0 ...... 0 1

:

:

1 1 1 ...... 1 1

0 0 0 ...... 0 0

:

:

0 1 1 ...... 1 0

0 1 1 ...... 1 1

0 1 1 ...... 1 1

0 1 1 ...... 1 0

:

:

0 0 0 ...... 0 0

1 1 1 ...... 1 1

:

:

1 0 0 ...... 0 1

1 0 0 ...... 0 0

0 0 0 ...... 0 0

0 0 0 ...... 0 1

:

:

0 1 1 ...... 1 1

1 0 0 ...... 0 0

:

:

1 1 1 ...... 1 0

1 1 1 ...... 1 1

MINV

LINV

0

1

0

0

1

0

1

1

≠ 13 ≠

CXA1396D

Fig. 2. Timing Chart

N ≠ 1

N

N ≠ 2

N ≠ 1

N

Tdh

1.8ns

(Typ)

N

N ≠ 2

N ≠ 4

N + 1

N

A/D input pin

PCB input pin

A/D clock

A/D output

PCB output pin

PCB output pin

PCB output pin

PCB output pin

Vin

(DIR. IN, AMP. IN)

CLK

CLK

CLK

D7 to D0

(For 1/1 frequency division)

CLKN

CLK

(For 1/1 frequency division)

D7 to D0

DATA OUT

(For 1/2 frequency division)

CLKN

CLK

(For 1/2 frequency division)

Tdh

1.8ns

(Typ)

≠ 14 ≠

CXA1396D

Adjustment Methods and Notes on Operation

1)

Vin Offset (VR1)

The volume to adjust the signal range (0V center assumed) with the A/D converter input range when a

waveform is input through AMP. IN.

2)

A/D Full Scale (VR2)

The volume to adjust A/D converter VRB voltage.

3)

Linearity (VR3)

The volume to adjust VRM (linearity) voltage. When DIR. IN input selected and it is supplied through the

capacitor, VR3 can be used to adjust the input offset voltage.

4)

D/A Full Scale (VR4)

The volume to adjust D/A output full scale (≠1V).

5)

J1 (Input selection)

A: Shorts to adjust VRM voltage.

B: Shorts to supply DC voltage to Vin.

C: Shorts to select AMP.IN input.

D: Shorts to select DIR.IN input.

[Jumper Position at Shipment]

J1

J1

J1

A

A

A

B

B

B

C

C

C

D

D

D

6)

SW1

The switch for LINV High/Low.

7)

SW2

The switch for MINV High/Low.

8)

SW3 (Decimation)

The switch to select clock frequency decimation.

Switch position: decimation ratio

0: 1/1

1: 1/2

2: 1/4

3: 1/8

4: 1/16

9)

SW4 (D/A INV)

The switch for D/A converter output inversion.

0.1µF

Input through the

buffer amplifier

Input through the

buffer amplifier

(When the linearity

is adjusted)

Input through the capacitor

(When the offset is adjusted using the

DIR IN. at the evaluation board)

≠ 15 ≠

CXA1396D

10) Rn10, Rn11 and Rn12 are not mounted at shipment. They are not required during evaluation.

11) Waveform probe pins P5 and P8 through P28 are devised to facilitate GND connection in order to reduce

the distortion. As shown in the diagram below, the distance between the probe point and the GND is 300

mil, and there is

1.2mm through hole at each. The signal and GND locations are suit for a Tektronix GND

tip (part number 013-1185-00).

Fig. 3

12) D/A converter (IC13) input data (waveform probe pins P21 through P28) are the complementary signals of

the decimated A/D converter outputs. Those are inverted again in the D/A converter so that the direction

of reproduced waveform can agree with the A/D input signal converter.

13) The part unmber of the digital output connector is KEL 8830E-020-170S. A corresponding connector and

cable assembly is JUNKOSMA KBO020MCG50BI.

1.2mm

Probe point

GND

300mil

≠ 16 ≠

CXA1396D

PCB Circuit Schematic

IC4

CLC404AJP

≠2V

(D)

P6

SW1

LINV

AGND

FERRITE

BEAD

AGND

R9

1.3k

VR2

2k

C8

0.1µ

AGND

≠5.2V (A)

IC1-2

TL4558

Q1

2SA970

7

6

8

5

4

C9

0.1µ

AGND

+5V (A)

A/D Full Scale

R6

240

IC3

TL431CP

R8

510

VR1

2K

1

2

6

3

4

AGND

AGND

IC1-1

TL4558

AGND AGND

R7

1k

2

7

3

4

AGND

6

DIR.IN

AMP.IN

AGND AGND

AGND

AGND

AGND AGND

AGND AGND

C12

0.1µ

C11

0.1µ

C3

0.1µ

C6

1µ

C7

1µ

C4

3.3µ

R4

22k

R5/11k

Vin Offset

R2

240

R1

51

R12

51

R11

43

R10

510

+5V (A)

≠5.2V (A)

≠5.2V (A)

P2

DGND

J1

B

Rn1

51

Rn1

51

Rn1

51

Rn1

51

V

CC

1

Aout_

Aout

Ain_

Ain

Bout_

Bout

V

EE

V

CC

2

Cout

Cout_

Cin

Cin_

V

BB

Bin

Bin_

I

C

8

:

1

0

H

1

1

6

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

V

CC

1

Q2

Q3

Cout_

D3

D2

S2

V

EE

V

CC

2

Q1

Q0

CLK

D0

D1

Cin_

S1

I

C

5

:

1

0

H

1

3

6

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

V

CC

2

Enable_

X3

X2

X1

X0

A

V

EE

V

CC

1

Z

X7

X6

X5

X4

C

B

I

C

7

:

1

0

H

1

6

4

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

C5

0.1µ

C2

0.1µ

C10

0.1µ

C14

0.1µ

C13

0.1µ

Rn1

DGND

DGND

R3

51

DGND

≠5.2V (D)

DGND

DGND

DGND

≠5.2V (D)

DGND

DGND

DGND

C22

0.1µ

DGND

≠5.2V (D)

DGND

C21

0.1µ

C37

0.1µ

DGND

C23

0.1µ

R14

51

≠2V (D)

DGND

≠2V (D)

DGND

Rn2

51

Rn2

51

Rn2

51

Rn2

51

Rn2

DGND

DGND

≠2V (D) DGND

C31

0.1µ

R18

51

SW3

Decimation

C30

0.1µ

C29

0.1µ

DGND

C1

0.1µ

≠5.2V (D)

DGND

D3

D2

D1

L

H

P11

P12

D1

CLK

DGND

P13

D2

R15

330

28

31

32

NC

VRB

NC

AV

EE

AV

EE

NC

NC

AGND

VIN

AGND

VRM

AGND

VIN

AGND

NC

NC

AV

EE

AV

EE

NC

VRT

NC

I

C

6

:

C

X

A

1

3

9

6

D

40

39

38

37

36

33

41

42

CLK

CLKN

NC

MINV

DV

EE

DGND1

DGND2

D7

D6

D5

D4

D3

D2

D1

D0

DGND2

DGND1

DV

EE

LINV

NC

AV

EE

P10

SW2

MINV

C24

0.1µ

C26

1µ

C25

0.1µ

FERRITE BEAD

D3

D0

C22

0.1µ

DGND

≠2V (D)

R17

51

R16

51

≠5.2V (D)

9

10

11

12

13

14

15

16

17

18

19

20

21

2

3

4

5

6

7

8

1

P17

P16

P15

P14

D6

D7

D4

D5

P9

CLK

P8

CLKN

C19

0.1µ

C20

10

AGND

C18

0.1µ

≠5.2V (A)

22

23

24

25

26

27

AGND

29

30

C17

0.1µ

AGND

P5

P4

AGND

AGND

VIN

P3

AV

EE

≠5.2V (A)

AGND

C15

1µ

C16

0.1µ

A

D

C

R13

1k

AGND

P1

VRB

VRM

VR3

1k

35

34

≠5.2V (D)

≠5.2V (A)

C25

0.1µ

C27

0.1µ

DGND

DGND

P17

DV

EE

Linearity

#1

#2

#3

#4

#5

#6

#7

#8

#9

#10

#11

#12

#13

#14

≠ 17 ≠

CXA1396D

MSB

D2

D3

D4

D5

D6

D7

D8

D9

LSB

NC

NC

CLKN

CLK

AGND2

V

REF

AV

EE

NC

NC

NC

NC

NC

OUT

NC

AGND1

DGND

INV

DV

EE

Rn11

51

DGND

DGND

D0

DGND

D1

DGND

D2

DGND

D3

DGND

D4

DGND

D5

DGND

D6

DGND

D7

DGND

CLK

DGND

DIGITAL OUT

CONNECTOR

KEL: 8830E-020-170S

(TOP VIEW)

Rn10

75

Rn10

75

Rn10

75

Rn10

75

Rn10

Rn11

51

Rn11

51

Rn11

51

Rn11

Rn12

51

Rn12

Rn12

51

Rn12

51

Rn12

51

C52

0.1µ

DGND

≠2V (D)

C53

0.1µ

≠2V (D)

DGND

≠2V (D)

DGND

C51

0.1µ

20

16

12

8

4

6

10

13

14

18

P29

C54

33µ

DGND

≠2V (D)

≠2V (D)

P30

DGND

DGND

DGND

P31

C55

33µ

DGND

≠5.2V (D)

≠5.2V (D)

P32

C56

33µ

AGND

≠5.2V (A)

≠5.2V (A)

P33 AGND

AGND

P34

C57

33µ

AGND

+5V (A)

+5V (A)

AGND

I

C

1

3

:

C

X

2

0

2

0

2

A

-

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

1

Rn9

75

Rn9

75

Rn9

75

Rn9

75

Rn8

75

Rn8

75

Rn8

75

Rn8

75

Rn8

C44

0.1µ

DGND ≠2V (D)

≠2V (D)

C46

0.1µ

C47

0.1µ

≠5.2V (D)

DGND

DGND

DGND

D/A OUT

SW4

D/A INV

D4

D6

D5

R23

3.2k

≠5.2V (D)

P23

P24

P25

P26

P27

P28

C45

0.1µ

DGND

≠2V (D)

≠5.2V (A)

AGND

R22

240

C50

33µ

C49

0.1µ

D/A Full Scale

C48

0.1µ

R21

1k

VR4

2k

IC14

TL431CP

D7

D6

D5

D4

D3

D2

D1

D0

Rn7

51

Rn7

51

Rn7

51

Rn7

51

C43

0.1µ

DGND

Rn7

P19

P20

CLKN

CLK

AGND

DGND

AGND

Rn9

DGND

L

H

V

CC

1

Q0

Q1

Q2

D0

D1

D2

V

EE

V

CC

2

Q5

Q4

Q3

D5

D4

D3

CLK

2

3

4

8

9

11

12

13

14

15

16

1

V

CC

1

Q0

Q1

Q2

D0

D1

D2

V

EE

V

CC

2

Q5

Q4

Q3

D5

D4

D3

CLK

I

C

9

:

1

0

H

1

7

6

2

3

4

8

9

11

12

14

15

16

1

DGND

DGND

DGND

C24

0.1µ

DGND

≠5.2V (D)

C26

0.1µ

DGND

≠5.2V (D)

V

CC

2

Dout_

Cout_

Din

COM

IN

Cout

Cin

Dout

V

CC

1

Aout_

Bout_

Ain

Aout

Bout

Bin

V

EE

I

C

1

2

:

1

0

H

1

0

1

2

3

4

5

7

8

10

12

13

14

15

16

1

V

CC

1

Aout_

Bout_

Ain

Aout

Bout

Bin

V

EE

V

CC

2

Dout_

Cout_

Din

COM

IN

Cout

Cin

Dout

I

C

1

1

:

1

0

H

1

0

1

2

3

4

12

14

15

16

1

C39

0.1µ

DGND

≠5.2V (D)

DGND

DGND

DGND

C41

0.1µ

DGND

≠5.2V (D)

DGND

DGND

Rn4

75

Rn4

75

Rn4

75

DGND

C36

0.1µ

≠2V (D)

Rn4

75

Rn4

Rn6

75

Rn6

75

Rn6

75

DGND

C42

0.1µ

≠2V (D)

Rn6

75

Rn6

Rn5

75

Rn5

75

Rn5

75

DGND

C40

0.1µ

≠2V (D)

Rn5

Rn3

75

Rn3

75

Rn3

75

DGND

C35

0.1µ

≠2V (D)

Rn3

75

Rn3

V

CC

1

Aout_

Aout

Ain_

Ain

Bout_

Bout

V

EE

V

CC

2

Cout

Cout_

Cin

Cin_

V

BB

Bin

Bin_

I

C

8

:

1

0

H

1

1

6

2

3

4

5

8

9

10

11

12

13

16

1

DGND ≠5.2V (D)

C34

0.1µ

DGND

≠2V (D)

C38

0.1µ

DGND

DGND

R20

51

DGND

C37

0.1µ

17

19

CLKN

14

15

P18

R19

51

≠2V (D)

CLK

9

1

2

7

3

5

15

11

11

6

9

11

10

9

13

5

6

7

8

I

C

1

0

:

1

0

H

1

7

6

5

6

7

10

P21

P22

6

7

5

6

7

10

Rn5

75

#1

#2

#3

#4

#5

#6

#7

#8

#9

#10

#11

#12

#13

#14

13

≠ 18 ≠

CXA1396D

Characteristic Graph

Fig. 5. Gain vs. Input frequency

(CLK = 125MHz)

G

a

i

n

[

d

B

]

2

0

≠2

≠4

≠6

≠8

≠10

10

100

Input frequency [MHz]

Fig. 6. SNR vs. Input frequency

(CLK = 125MHz)

S

N

R

[

d

B

]

50

45

40

35

30

25

20

10

100

Input frequency [MHz]

DIR. IN

AMP. IN

1

Fig. 7. 2nd, 3rd harmonic distortion vs. Input frequency

(CLK = 125MHz)

2

n

d

,

3

r

d

h

a

r

m

o

n

i

c

d

i

s

t

o

r

t

i

o

n

[

d

B

]

≠20

≠30

≠40

≠50

≠60

≠70

≠80

10

100

Input frequency [MHz]

2nd DIR. IN

2nd AMP. IN

3rd DIR. IN

3rd AMP. IN

1

Measurement data

Figs. 5, 6 and 7 show the characteristic graphs.

DIR. IN is the characteristic where the signal is directry input to the ADC and AMP. IN is the characteristic

where the signal is input to ADC through the amplifier.

≠ 19 ≠

CXA1396D

Parts Layout

≠ 20 ≠

CXA1396D

1st layer

Component plane (Top View)

4th layer

Solder plane (Top View)

Printed Pattern

≠ 21 ≠

CXA1396D

2nd layer

GND plane (Top View)

3rd layer

Power supply plane (Top View)

≠ 22 ≠

CXA1396D

Package Outline

Unit: mm

SONY CODE

EIAJ CODE

JEDEC CODE

PACKAGE STRUCTURE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE WEIGHT

GOLD PLATING

42 ALLOY

42PIN DIP (CERAMIC) 600mil

53.4 ± 0.5

13.2 ± 0.2

2.54

21

22

42

1

0.46 ± 0.1

1.0 ± 0.1

3

.

3

M

I

N

1

.

0

M

I

N

6

.

6

M

I

N

6

.

9

1

M

I

N

1

5

.

2

4

±

0

.

2

5

0

.

2

5

+

0

.

0

5

≠

0

.

0

2

0∞ to 15∞

6.7g

DIP-42C-01

DIP042-C-0600-A

CERAMIC