| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXA2174S | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

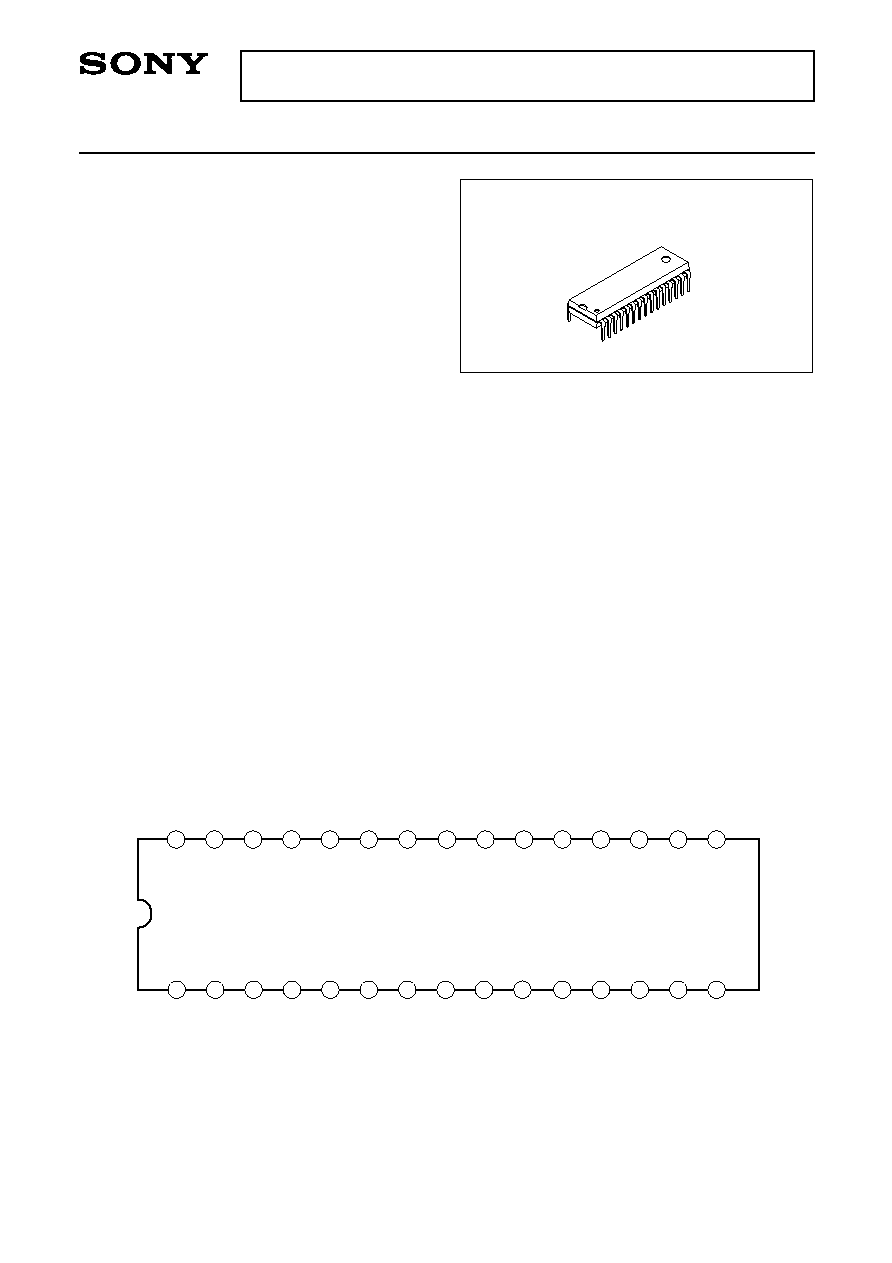

CXA2174S

US Audio Multiplexing Decoder

Description

The CXA2174S is an IC designed as a decoder for

the Zenith TV Multi-channel System and also

corresponds with I

2

C BUS. Functions include stereo

demodulation, SAP (Separate Audio Program)

demodulation,

dbx noise reduction and sound

processor. Various kinds of filters are built-in this IC.

Adjustment, mode control and sound processor

control are all executed through I

2

C BUS.

Features

∑ Alignment-free VCO and filter

∑ Audio multiplexing decoder

dbx noise reduction decoder

sound processor

-- One external input

-- Volume control

are all included in a single chip. Almost any sort of

signal processing is possible through this IC.

∑ Input level, separation adjustments and each mode

control are possible through I

2

C bus.

Applications

TV, VCR and other decoding systems for US audio

multiplexing TV broadcasting

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings (Ta = 25∞C)

∑ Supply voltage

V

CC

11

V

∑ Operating temperature

Topr

≠20 to +75

∞C

∑ Storage temperature

Tstg

≠65 to +150 ∞C

∑ Allowable power dissipation

P

D

1.35

W

Range of Operating Supply Voltage

9 ± 0.5

V

A license of the dbx-TV noise reduction system is

required for the use of this device.

≠ 1 ≠

E00815-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

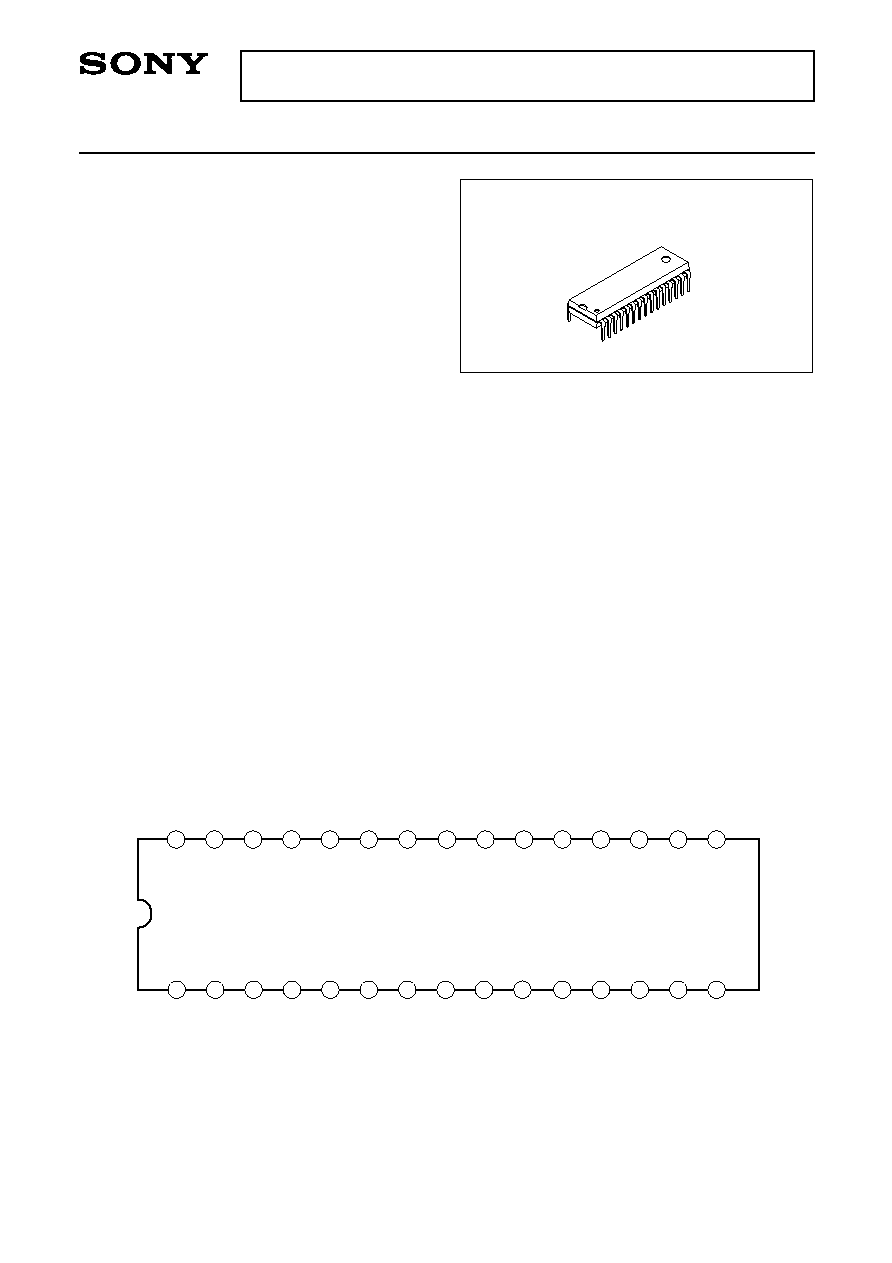

30 pin SDIP (Plastic)

LSOUT-R

2

3

4

5

6

7

8

9

10

11

12

13

14

15

1

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

LSOUT-L

SDA

SCL

DGND

MAININ

MAINOUT

PCINT1

PCINT2

PLINT

COMPIN

VGR

IREF

GND

SAPTC

AUX-L

AUX-R

VCAWGT

VCATC

VCAIN

VEOUT

VETC

VEWGT

VE

SAPIN

SAPOUT

NOISETC

STIN

SUBOUT

V

CC

Pin Configuration (Top View)

≠ 2 ≠

CXA2174S

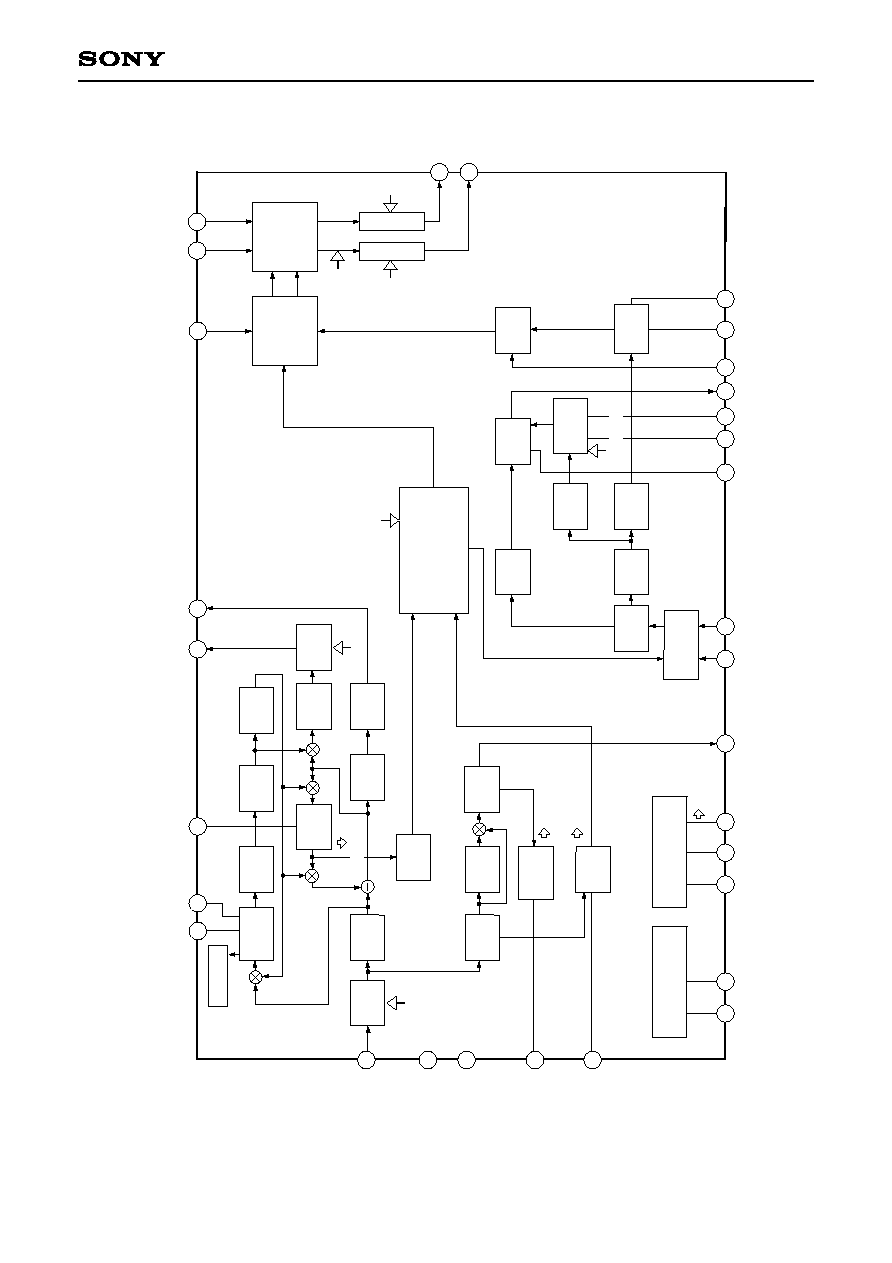

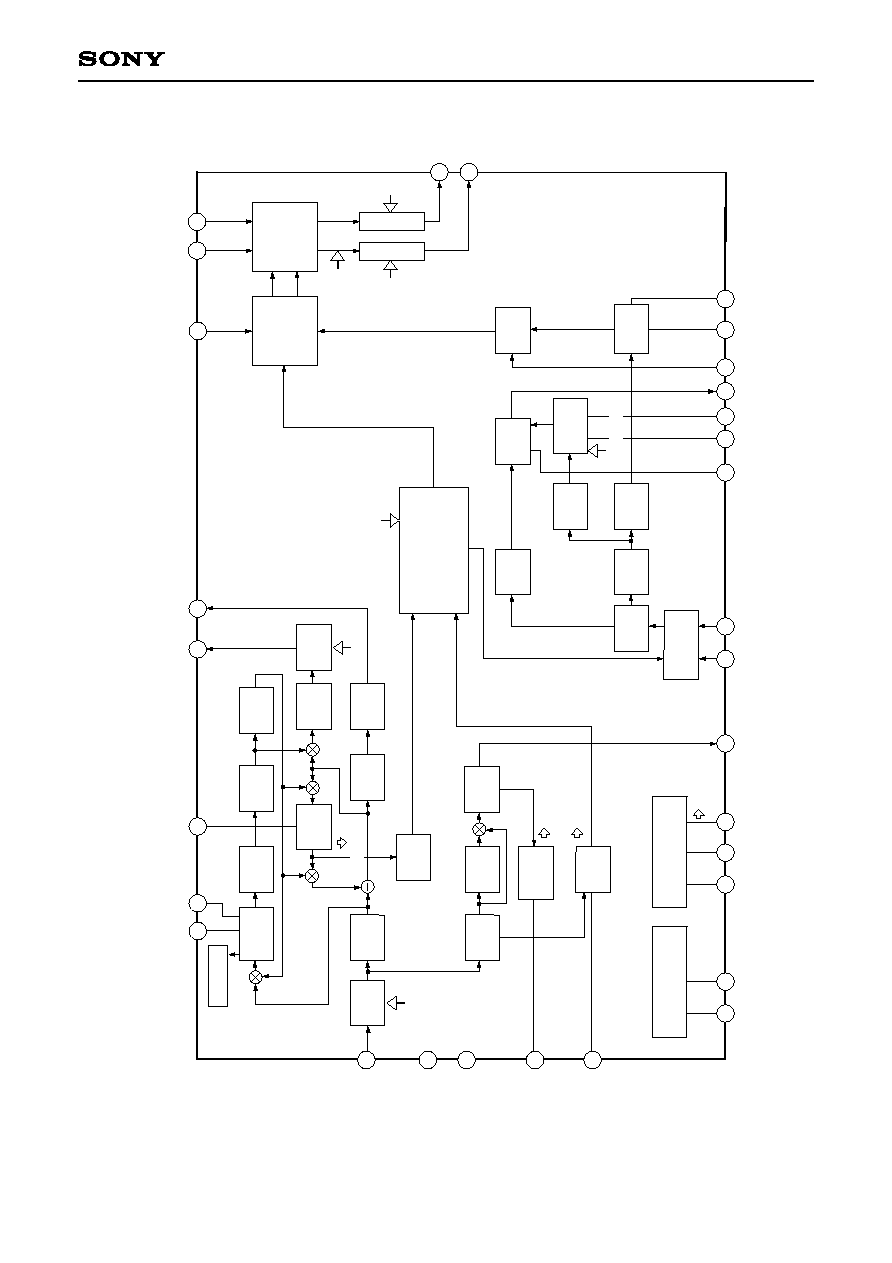

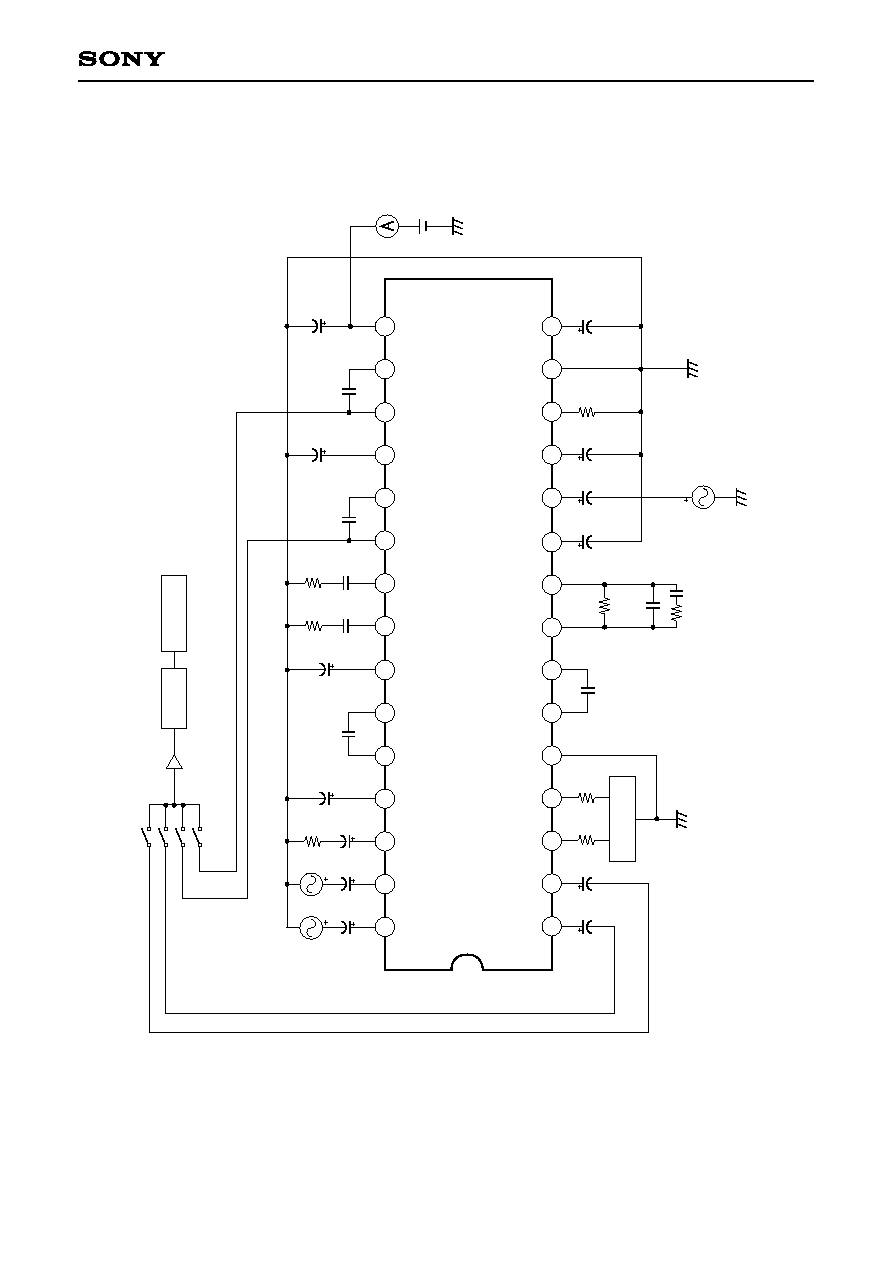

Block Diagram

VGR

IREF

DGND

SCL

SDA

SAPOUT

SAPIN

STIN

VE

VEWGT

VETC

VEOUT

VCAIN

VCAWGT

VCATC

MAININ

MAINOUT

SUBOUT

PLINT

PCINT1

COMPIN

V

CC

GND

NOISETC

SAPTC

IREF

SW

LPF

L

PF

HPF

RMSDET

RMSDET

VCA

VE

DeEm

LOGIC

VCA

LPF

LPF

1/2

1/4

VCO

LFLT

STLPF

VCA

LPF

BPF

SAPVCO

LPF

NOISE

DET

SAPIND

"PONRES"

STIND

"SAP"

"NOISE"

NRSW/FOMO/SAPC

WIDEBAND

SPECTRAL

"STEREO"

DeEm

FLT

AMP

(+4dB)

I

2

C BUS I/F

(+6dB)

PCINT2

ATT

6

7

17

10

9

8

11

16

14

19

15

12

13

5

4

3

20

21

18

22

23

24

25

26

28

27

TVSW

MATRIX

VOL-R

VOL-L

LSOUT-L

LSOUT-R

1

2

AUX-L

AUX-R

29

30

EXTI/MI

VOL-R

VOL-L

≠ 3 ≠

CXA2174S

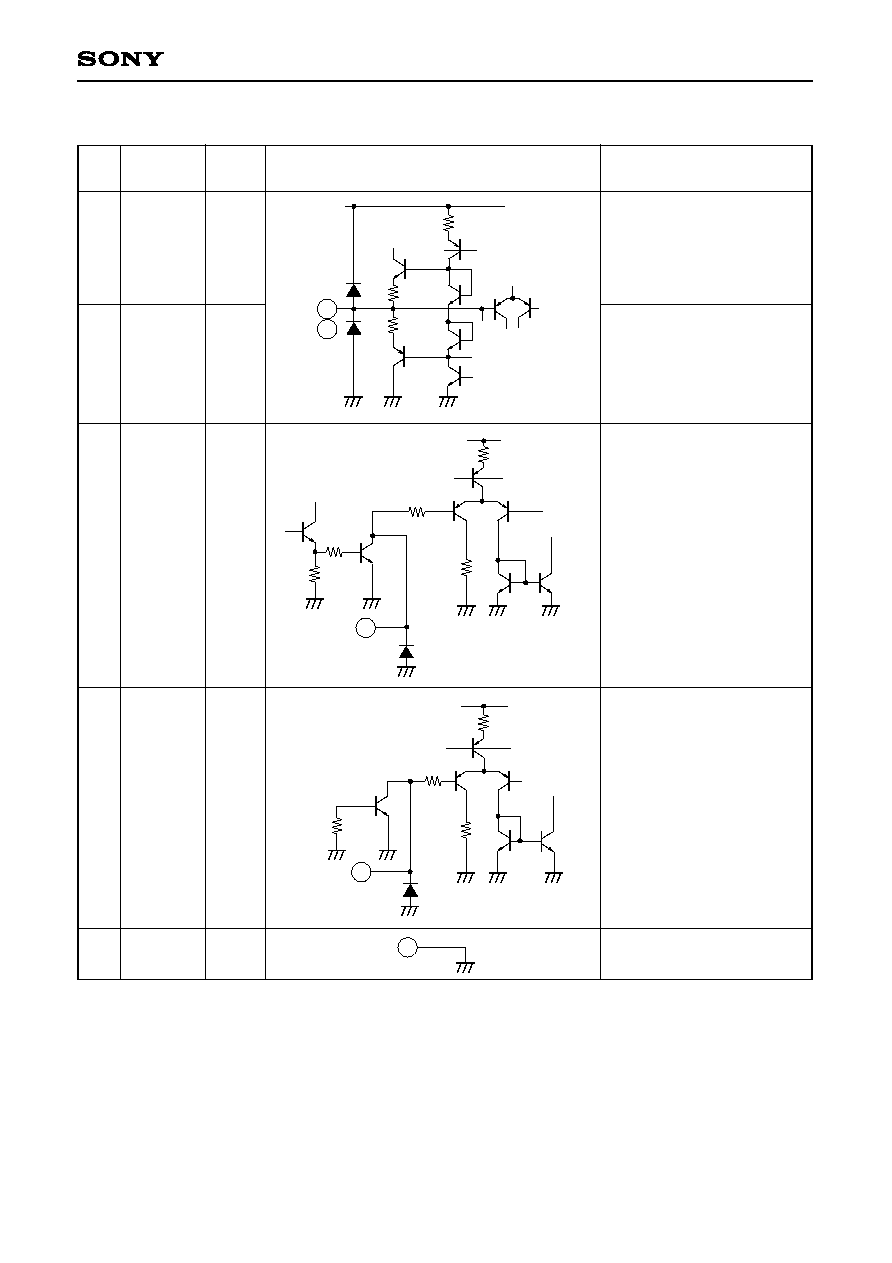

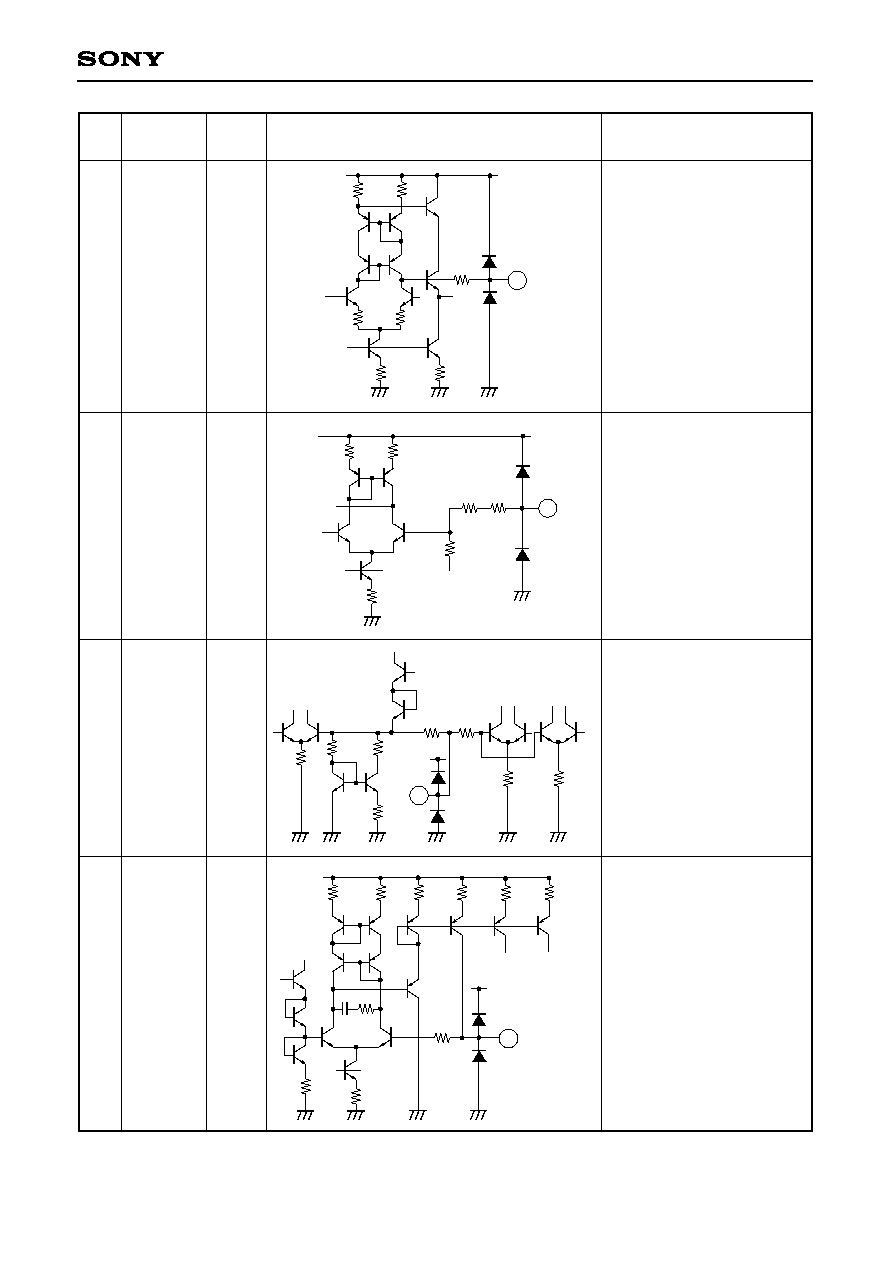

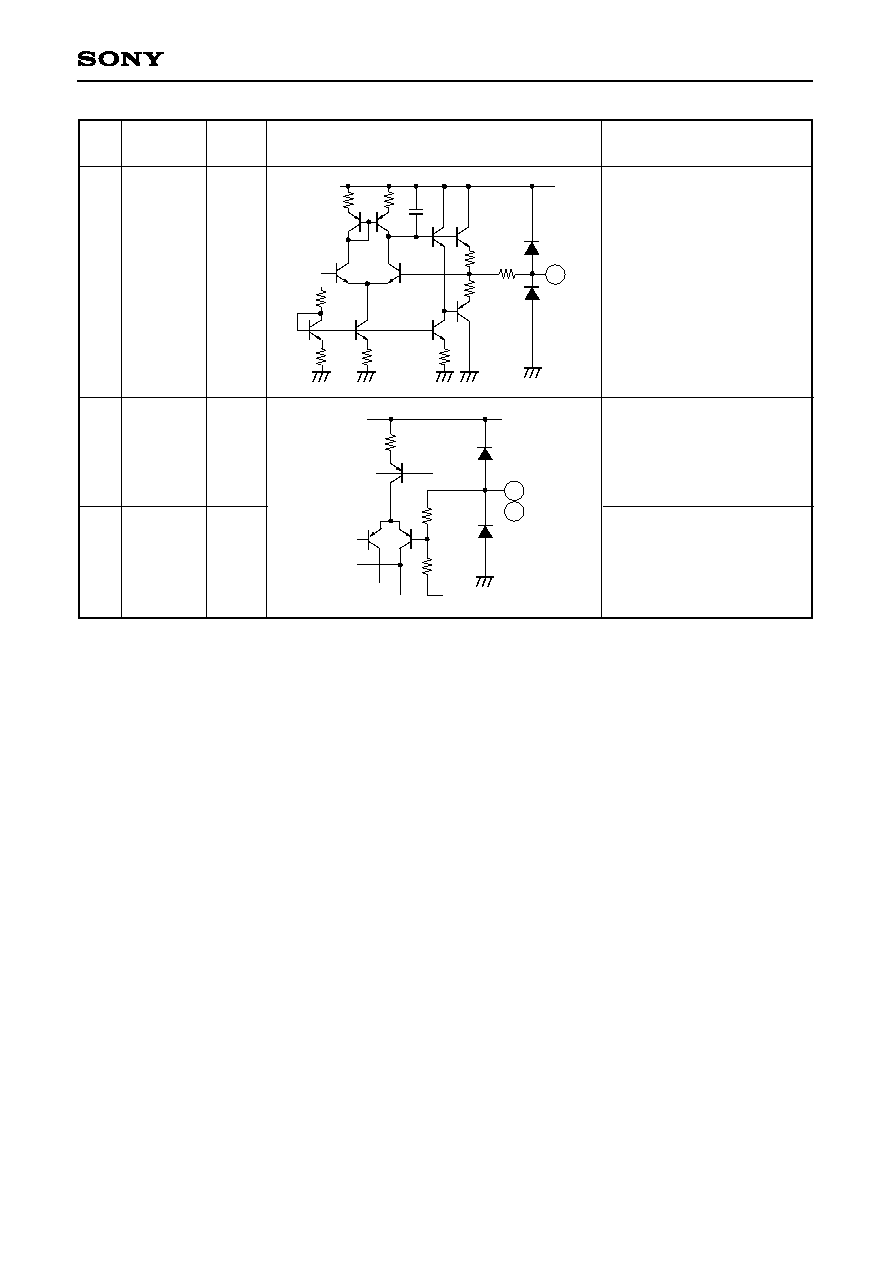

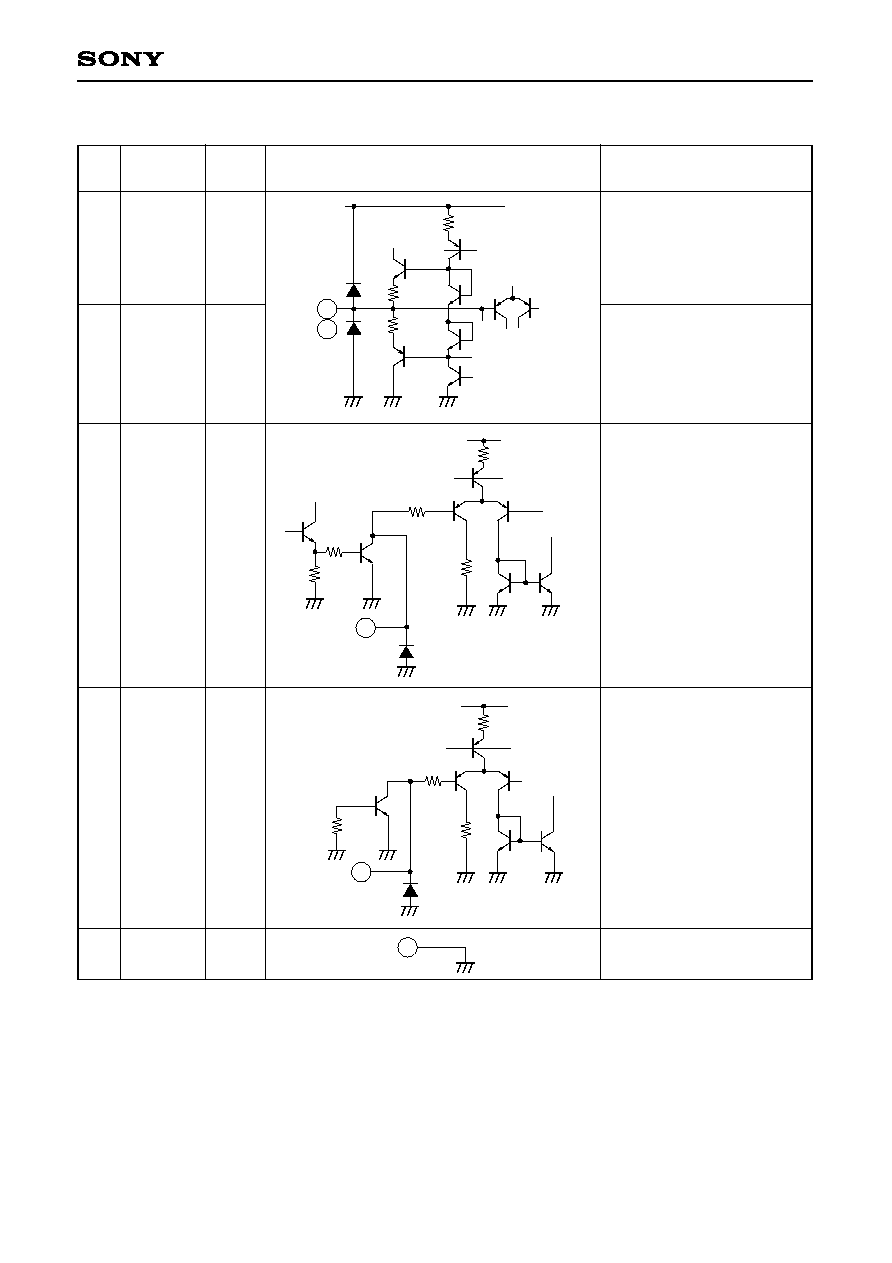

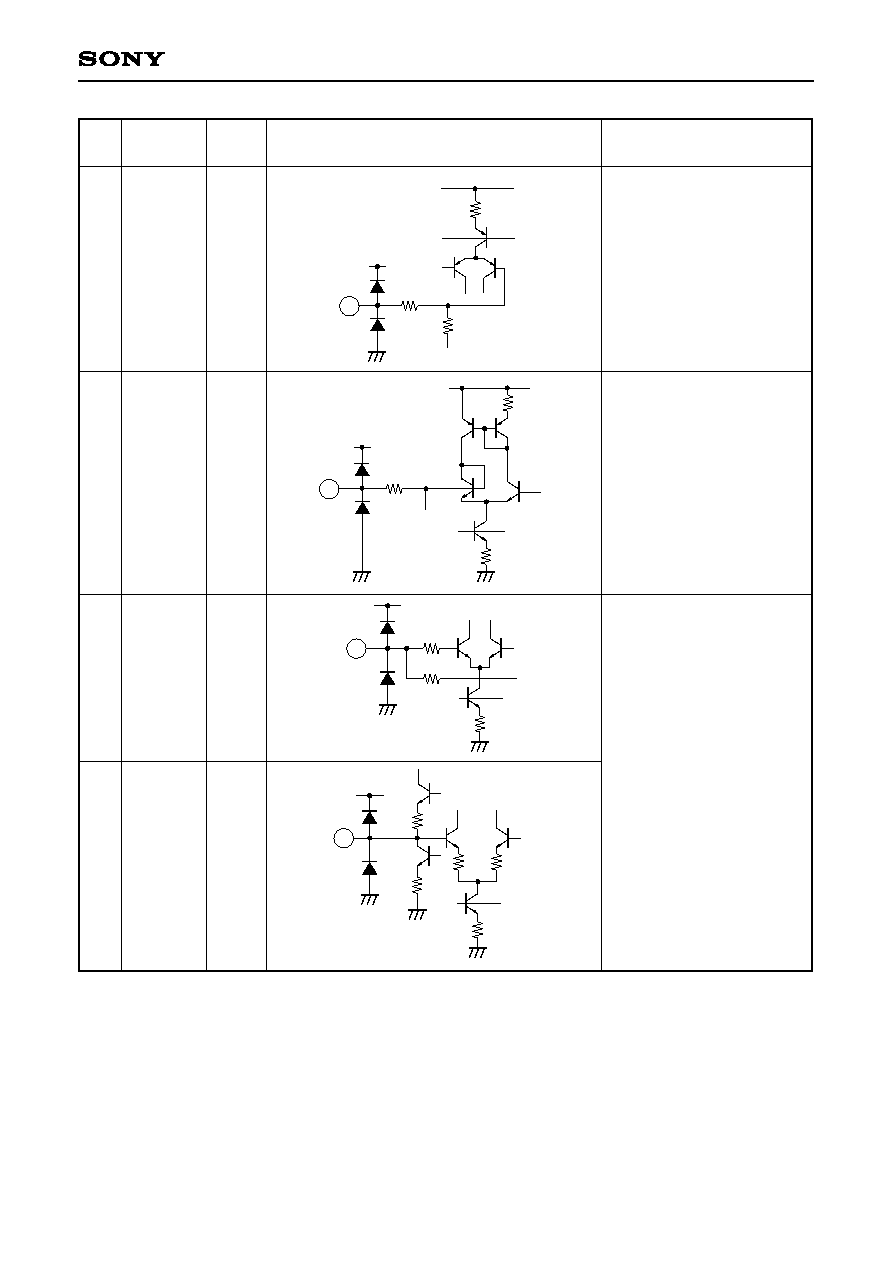

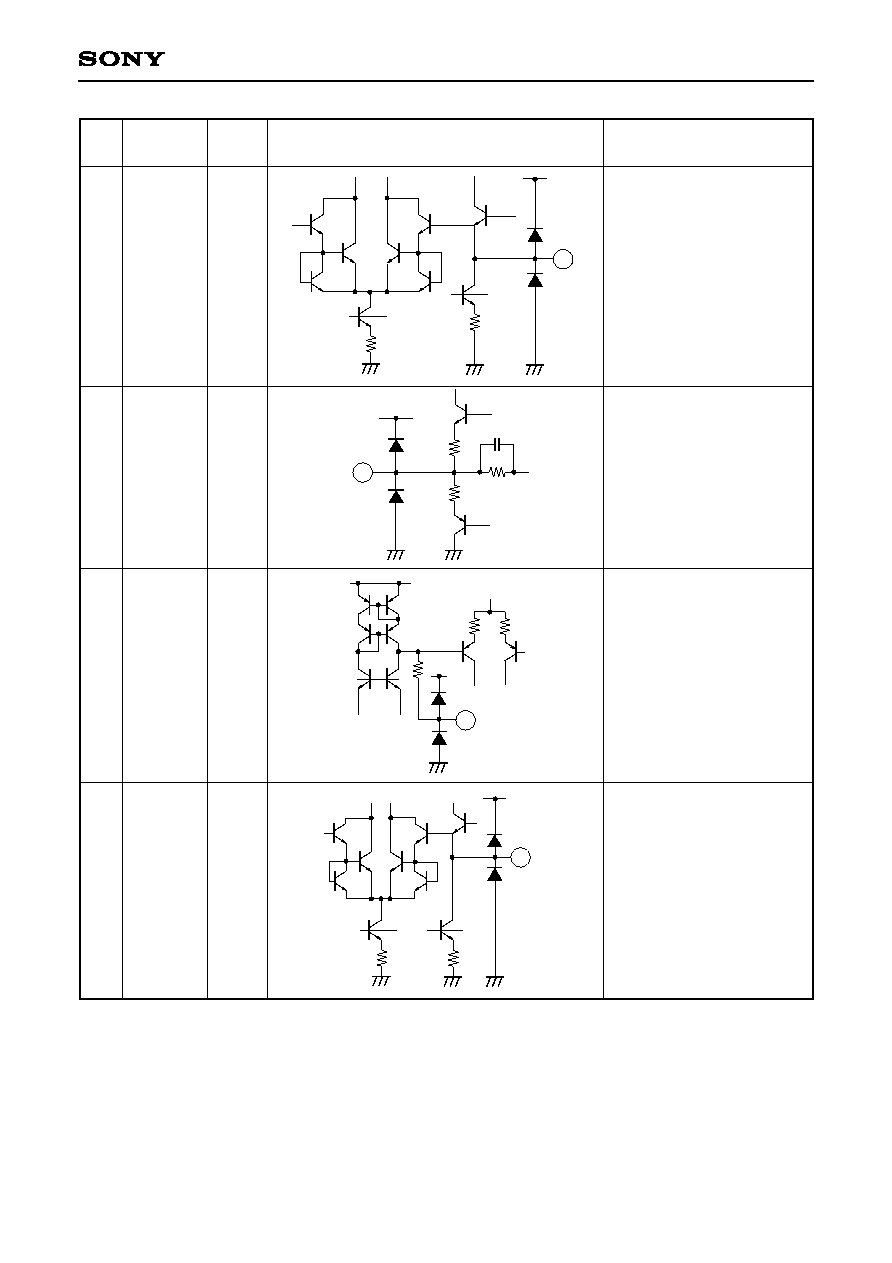

Pin Description

(Ta = 25∞C, V

CC

= 9V)

7.5k

4.5k

◊

5

4k

3k

7.5k

V

CC

35µ

2.1V

◊

2

3

7.5k

35µ

2.1V

10.5k

◊

4

4k

3k

V

CC

4

5

Pin

No.

Symbol

Pin

voltage

Equivalent circuit

Description

SDA

SCL

DGND

--

--

--

Serial data I/O pin.

V

IH

> 3.0V

V

IL

< 1.5V

Serial clock input pin.

V

IH

> 3.0V

V

IL

< 1.5V

Digital block GND.

3

4

5

LSOUT-R

4.0V

LSOUT right channel output

pin.

1

LSOUT-L

4.0V

LSOUT left channel output

pin.

2

3k

580

580

V

CC

2

1

≠ 4 ≠

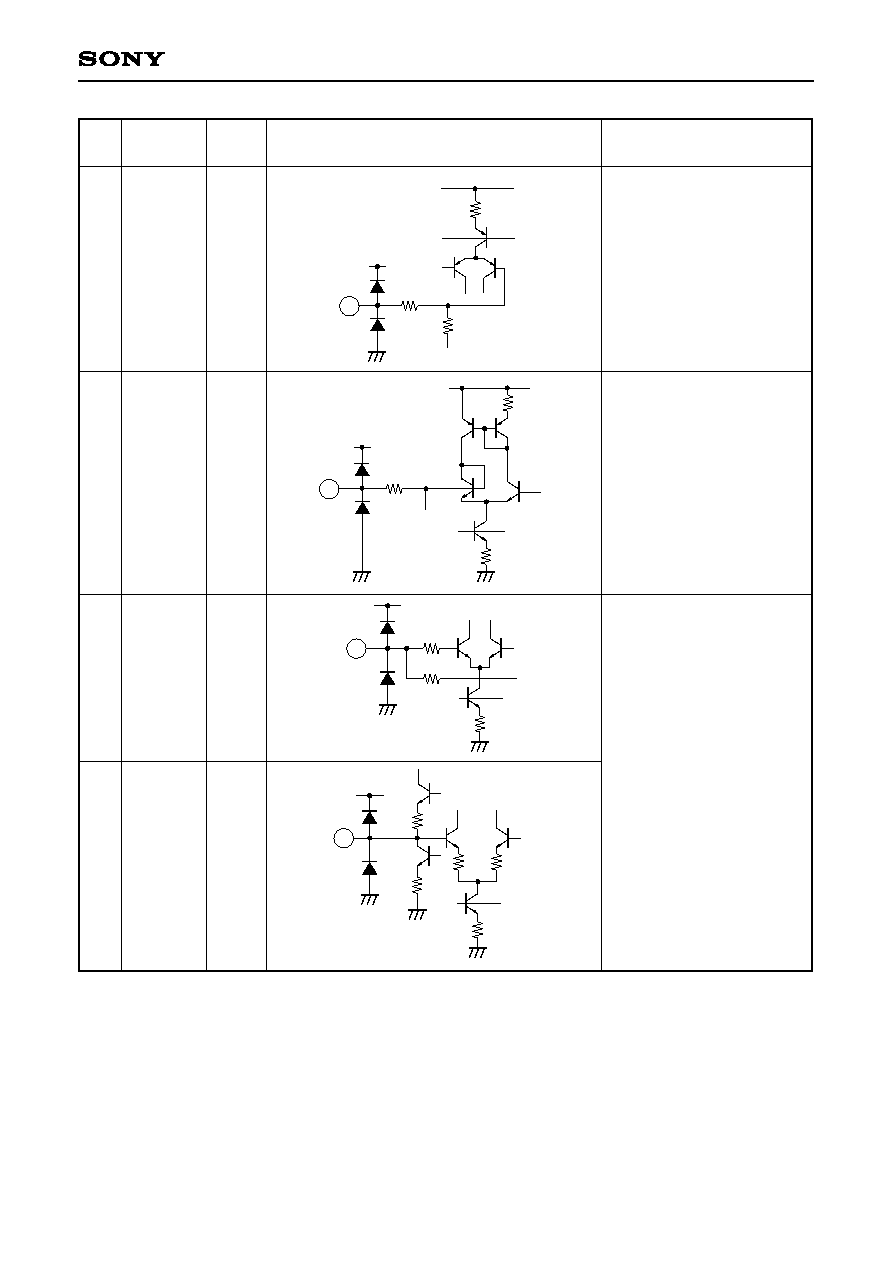

CXA2174S

MAINOUT

PCINT1

PCINT2

4.0V

4.0V

4.0V

(L + R) signal output pin.

Stereo block PLL loop filter

integrating pin.

V

CC

147

1k

15k

200µ

V

CC

◊

4

7

22k

V

CC

30k

147

8

4k

V

CC

◊

2

10k

10k

2k

147

9

7

8

9

Pin

No.

Symbol

Pin

voltage

Equivalent circuit

Description

V

CC

147

10k

53k

4V

V

CC

6

MAININ

4.0V

Input the (L + R) signal from

MAINOUT (Pin 7).

6

≠ 5 ≠

CXA2174S

COMPIN

VGR

IREF

4.0V

1.3V

1.3V

Audio multiplexing signal

input pin.

Band gap reference output

pin.

(Connect a 10µF capacitor

between this pin and GND.)

Set the filter and VCO

reference current. The

reference current is adjusted

with the BUS DATA based on

the current which flows to this

pin.

(Connect a 62k

(±1%)

resistor between this pin and

GND.)

11

12

13

11

V

CC

24k

4V

34k

14k

147

24k

24k

40k

40k

30k

30p 1.8k

16k

6.3k

147

30k

15k

30k

V

CC

◊

2

V

CC

13

◊

4

11k

9.7k

19.4k

2.06k

3k

147

V

CC

11k

11k

12

Pin

No.

Symbol

Pin

voltage

Equivalent circuit

Description

PLINT

5.1V

Pilot cancel circuit loop filter

integrating pin.

(Connect a 1µF capacitor

between this pin and GND.)

V

CC

147

20k

26µ

20k

10k

20k

50µ

20k

20k

10

10

≠ 6 ≠

CXA2174S

V

CC

SUBOUT

STIN

--

4.0V

4.0V

Supply voltage pin.

(L≠R) signal output pin.

Input the (L-R) signal from

SUBOUT (Pin 17).

16

17

18

SAPIN

4.0V

Input the (SAP) signal from

SAPOUT (Pin 20).

21

16

2k

2k

2k

4k

1k

147

580

14.4k

580

4k

10P

2k

2k

Vcc

17

23k

147

18k

20k

11.7k

23k

4V

147

18k

4V

V

CC

18

21

Pin

No.

Symbol

Pin

voltage

Equivalent circuit

Description

Set the time constant for the

SAP carrier detection circuit.

(Connect a 4.7µF capacitor

between this pin and GND.)

SAPTC

4.5V

15

8k

4k

3k

10k

V

CC

50µ

1k

V

CC

15

GND

--

Analog block GND.

14

14

≠ 7 ≠

CXA2174S

NOISETC

3.0V

Set the time constant for the

noise detection circuit.

(Connect a 4.7µF capacitor

between this pin and GND.)

19

3k

3k

3.3k

4k

4V

Vcc

8k

◊

2

10k

1k

2k

Vcc

200k

19

SAPOUT

VE

4.0V

4.0V

SAP FM detector output pin.

Variable de-emphasis

integrating pin.

(Connect a 2700pF capacitor

and a 3.3k

resistor in series

between this pin and GND.)

20

22

VEWGT

4.0V

Weight the variable

de-emphasis control effective

value detection circuit.

(Connect a 0.047µF capacitor

and a 3k

resistor in series

between this pin and GND.)

23

24k

10µ

580

Vcc

5P

580

4k

50µ

10k

147

20

Vcc

4V

36k

2.9V

580

147

580

8k

30k

8µ

4k

50µ

23

7.5k

147

V

CC

22

Pin

No.

Symbol

Pin

voltage

Equivalent circuit

Description

≠ 8 ≠

CXA2174S

VEOUT

VCAIN

4.0V

4.0V

Variable de-emphasis output

pin.

(Connect a 4.7µF non-polar

capacitor between Pins 25

and 26.)

VCA input pin.

Input the variable

de-emphasis output signal

from Pin 25 via a coupling

capacitor.

25

26

VCATC

1.7V

Determine the restoration

time constant of the VCA

control effective value

detection circuit.

(the specified restoration

time constant can be

obtained by connecting a

10µF capacitor between this

pin and GND.)

27

Vcc

10k

580

580

5P

25

50µ

V

CC

4k

20k

◊

4

◊

4

7.5µ

27

V

CC

20k

V

CC

47k

47k

26

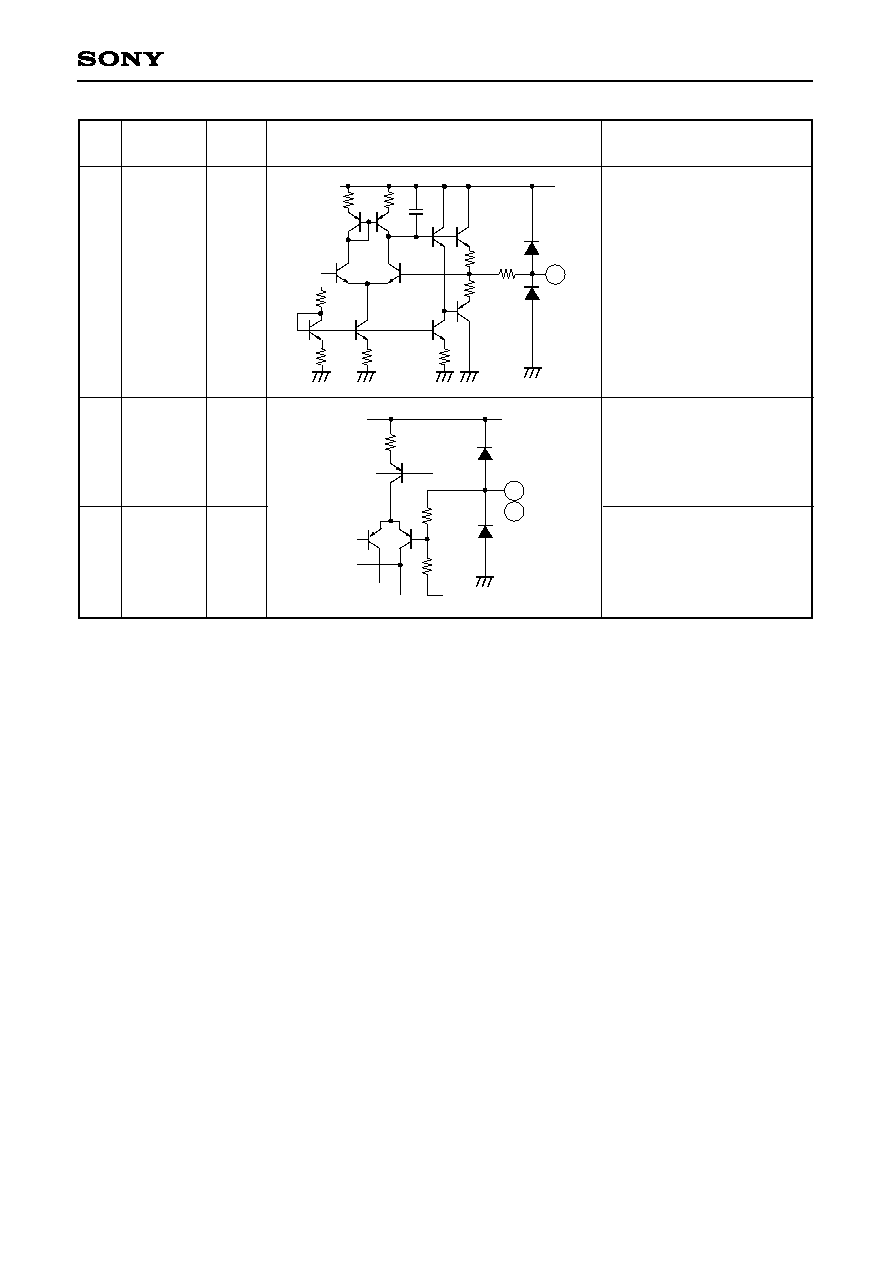

Pin

No.

Symbol

Pin

voltage

Equivalent circuit

Description

VETC

1.7V

Determine the restoration

time constant of the variable

de-rmphasis control effective

value detection circuit.

(the specified restoration time

constant can be obtained by

connecting a 3.3µF capacitor

between this pin and GND.)

24

20k

7.5µ

4k

50µ

Vcc

◊

4

◊

4

24

≠ 9 ≠

CXA2174S

VCAWGT

4.0V

Weight the VCA control

effective value detection

circuit.

(Connect a 1µF capacitor

and a 3.9k

resistor in series

between this pin and GND.)

28

4k

V

CC

30k

8k

36k

2.9V

3p

580

580147

40k

40k

50µ

8µ

28

Pin

No.

Symbol

Pin

voltage

Equivalent circuit

Description

AUX-R

4.0V

Right channel external input

pin.

Left channel external input

pin.

29

AUX-L

4.0V

30

V

CC

4V

30

29

23.5k

23.5k

10k

≠ 10 ≠

CXA2174S

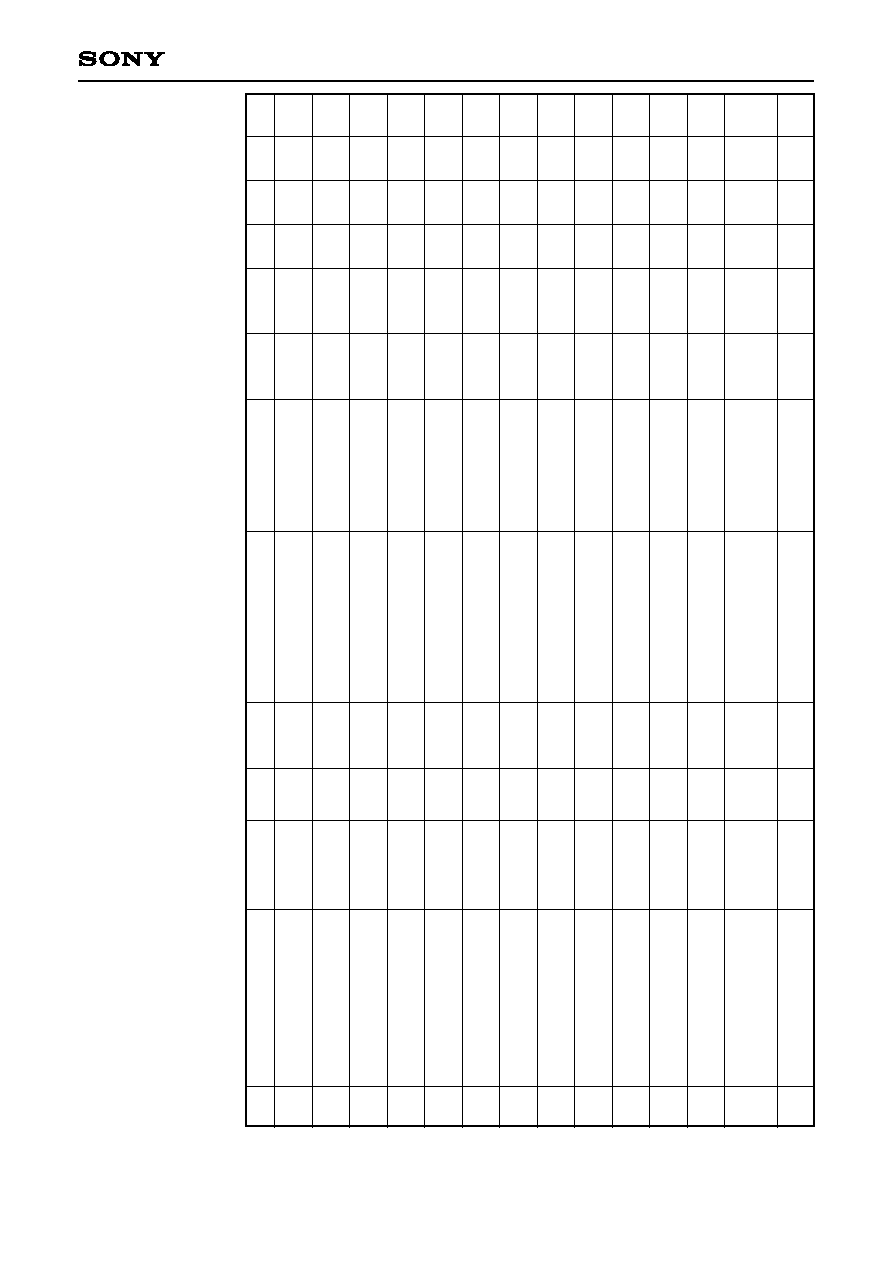

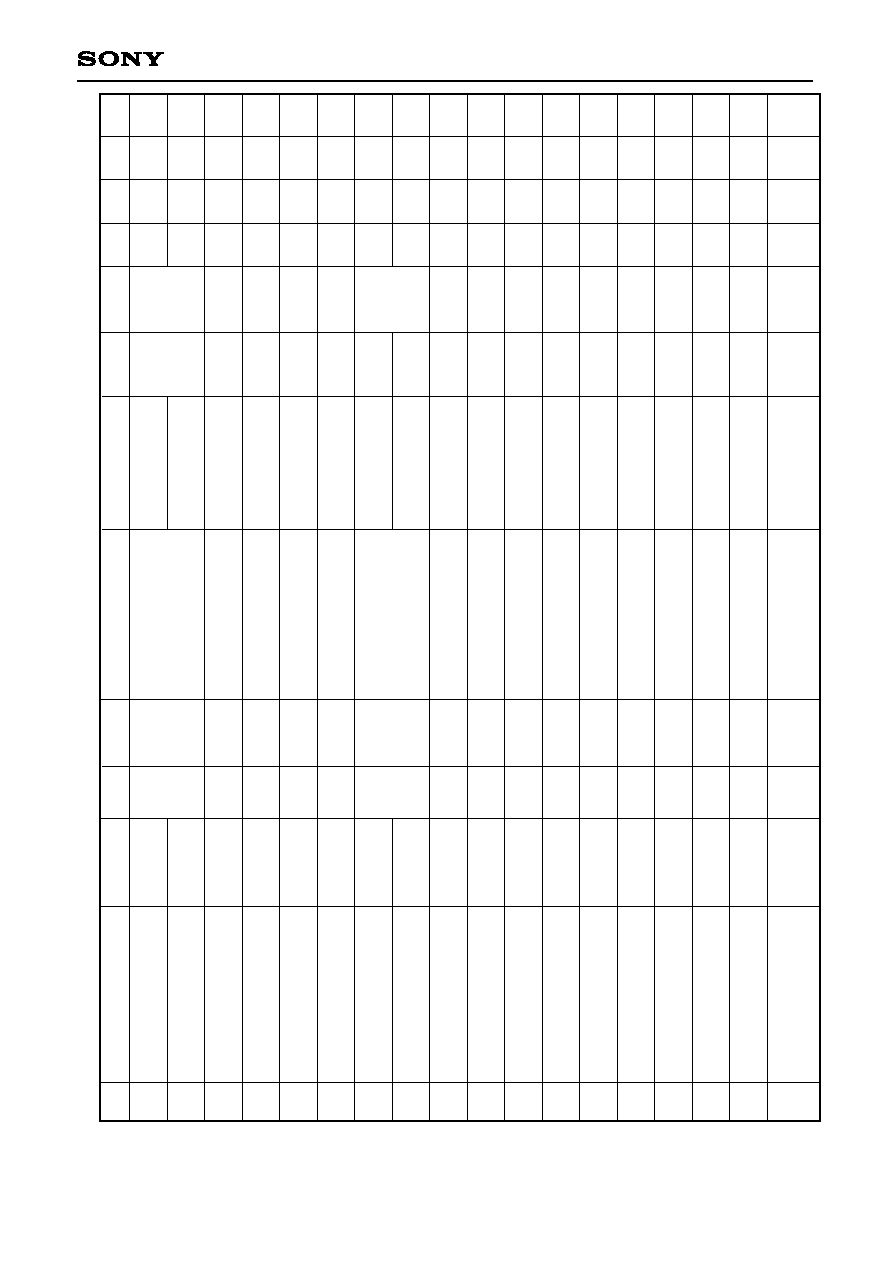

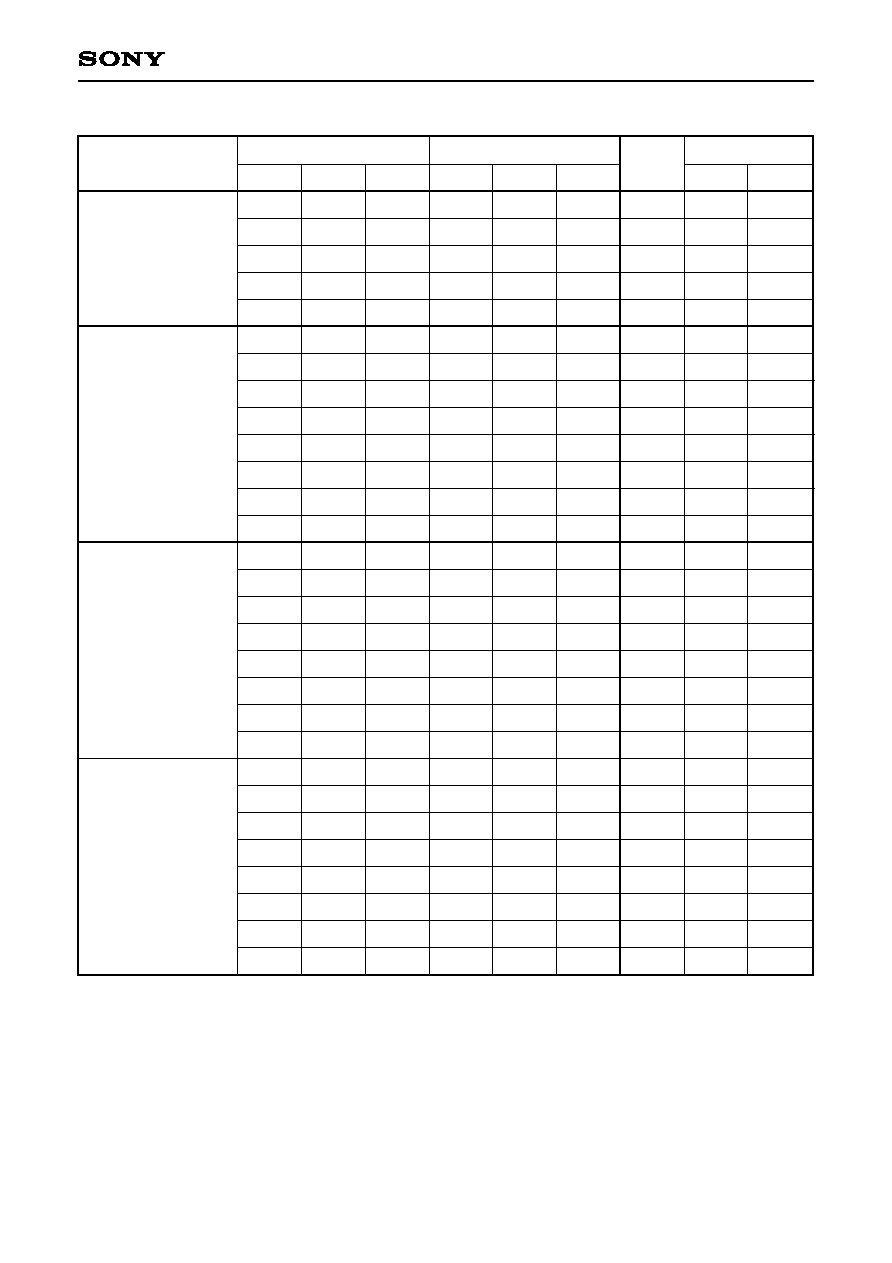

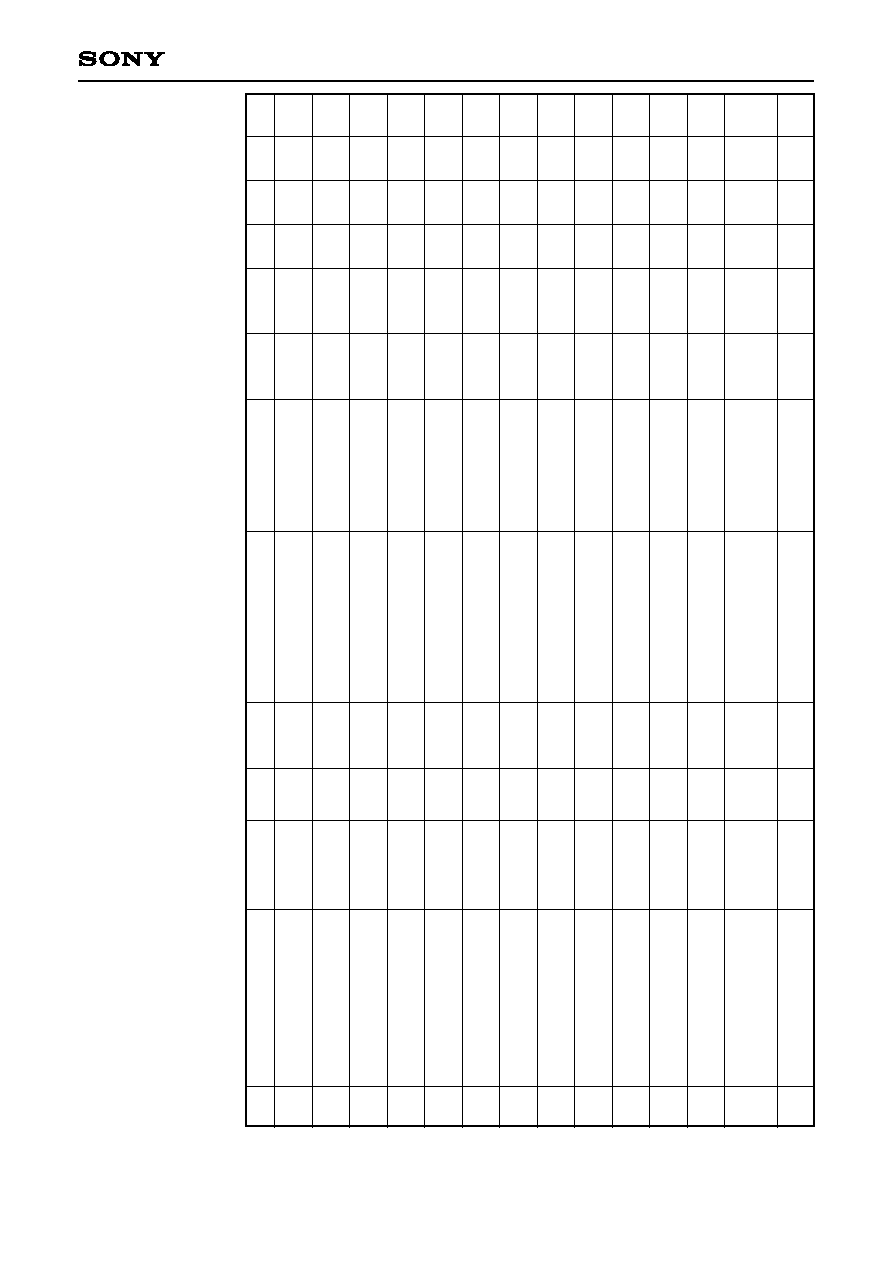

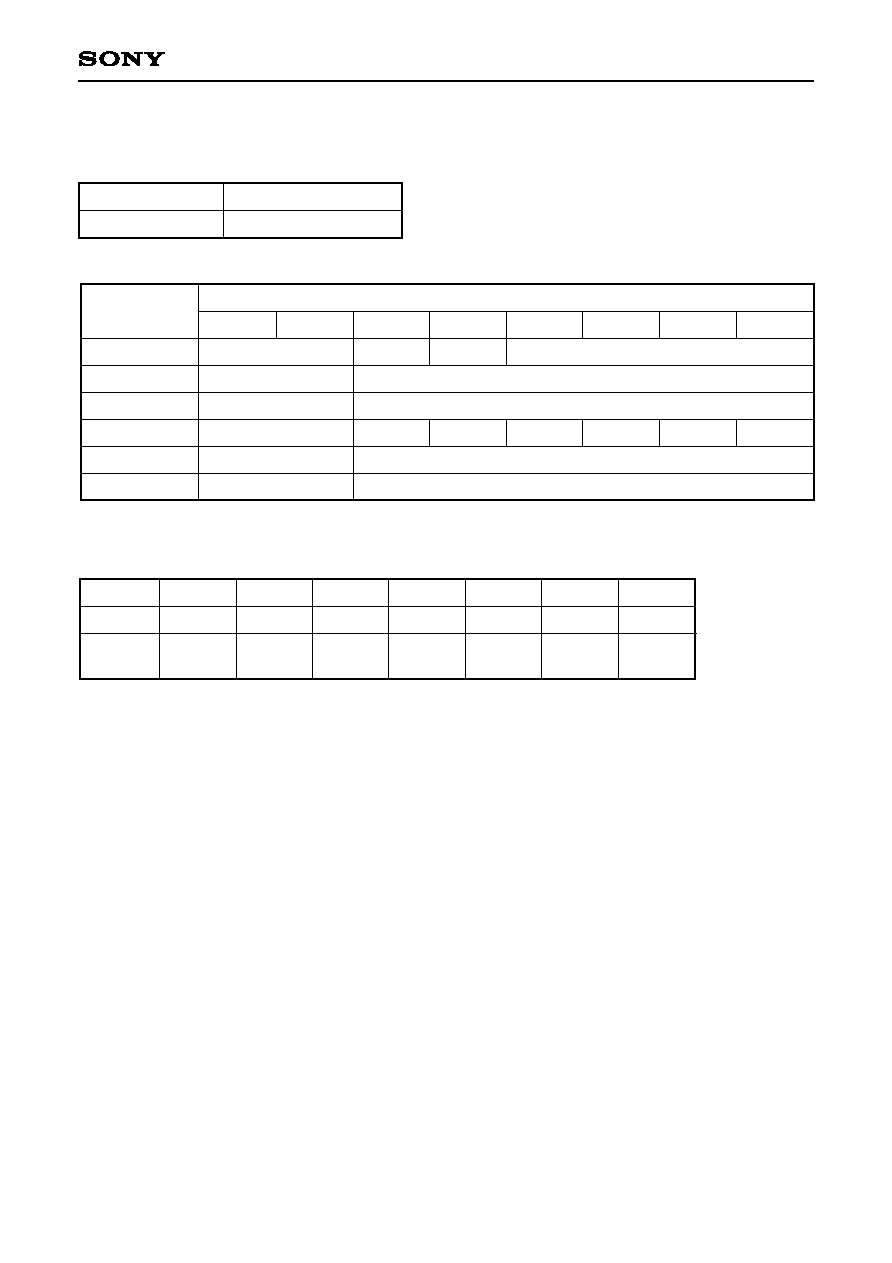

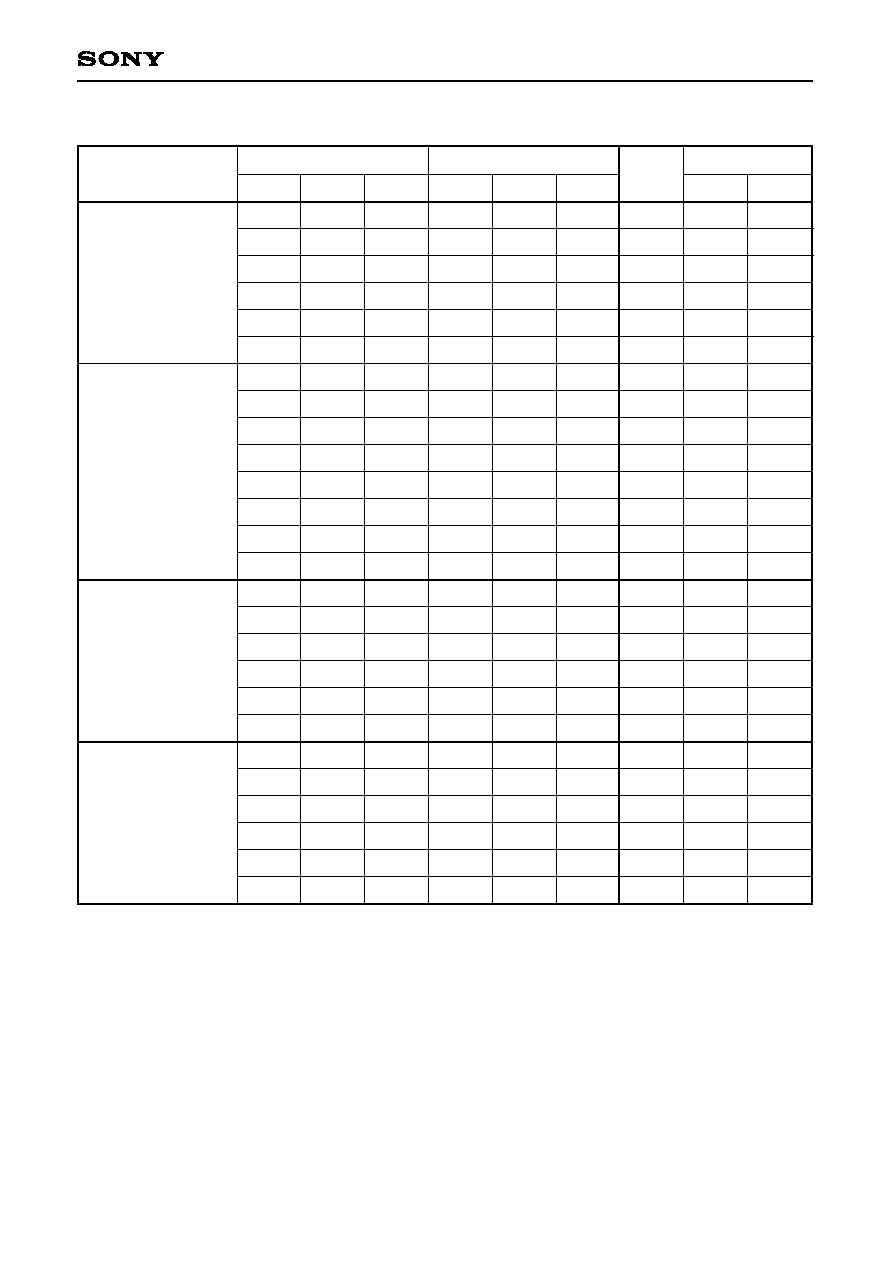

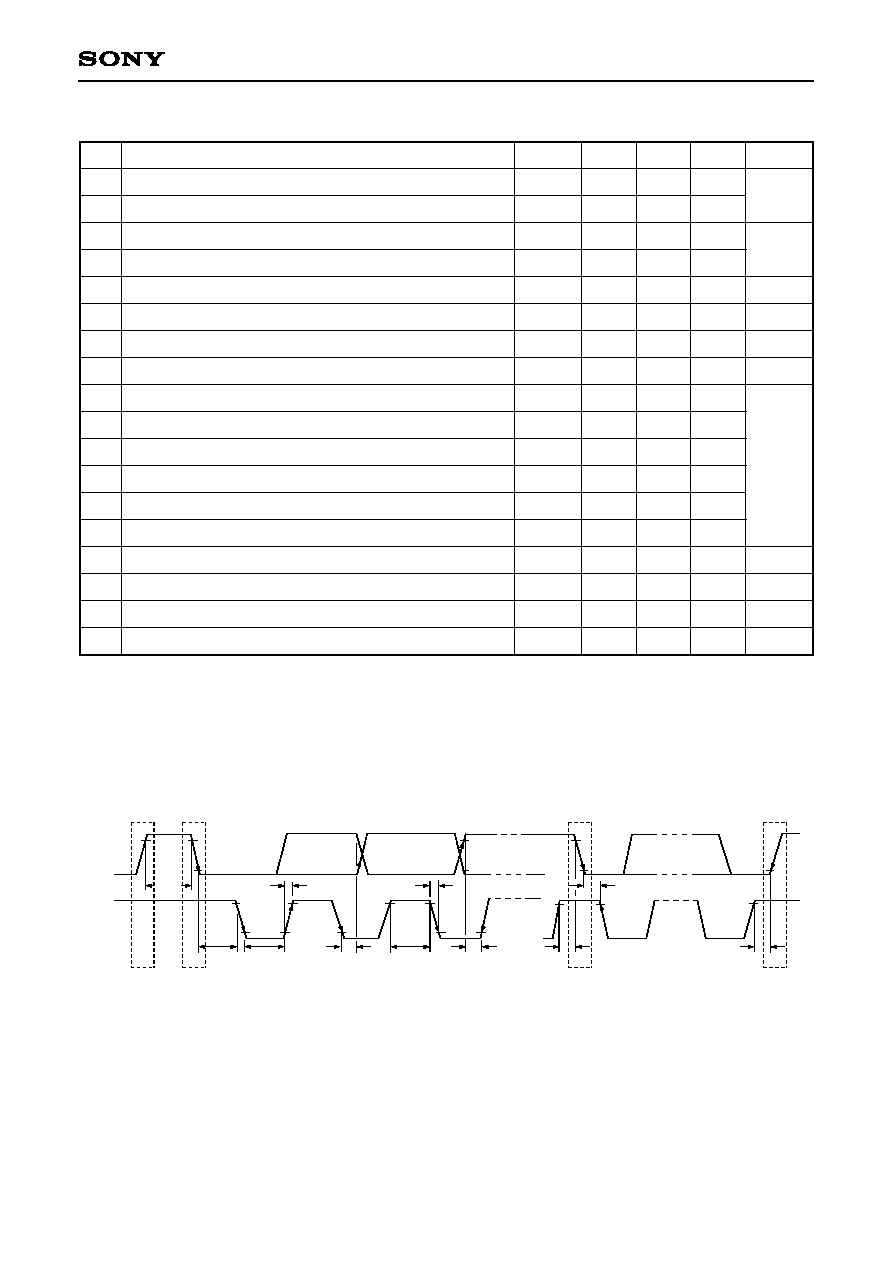

Electrical Characteristics

COMPIN input level

(100% modulation level)

(Ta = 25

∞

C, Vcc = 9V)

Current consumption

Main output level

Main de-emphasis

frequency response

Main LPF frequency

response

Main distortion

Main overload distortion

Main S/N

Sub output level

Sub LPF frequency

response

Sub distortion

Sub overload distortion

Sub S/N

Crosstalk

Stereo

SAP

Cross talk

SAP

Stereo

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Icc

Vmain

FCdeem

FCmain

THDm

THDmmax

SNmain

Vsub

FCsub

THDsub

THDsmax

SNsub

CTst

CTsap

MONO

MONO

MONO

MONO

MONO

MONO

ST

ST

ST

ST

ST

SAP

ST

--

11

11

11

11

11

11

11

11

11

11

11

11

11

23

440

≠

1.2

≠

3.0

--

--

61

150

≠

3.0

--

--

56

60

60

32

490

0

≠

1.0

0.1

0.15

69

190

≠

0.5

0.1

0.2

64

70

70

43

540

1.0

1.0

0.5

0.5

--

230

1.0

1.0

2.0

--

--

--

mA

mVrms

dB

dB

%

%

dB

mVrms

dB

%

%

dB

dB

dB

No signal

Mono 1kHz 100% mod.

Pre-em. ON

Mono 5kHz 30% mod.

Pre-em. ON

Mono 12kHz 30% mod.

Pre-em. ON

Mono 1kHz 100% mod.

Pre-em. ON

Mono 1kHz 200% mod.

Pre-em. ON

Mono 1kHz,

Pre-em. ON

SUB (L-R) 1kHz,

100% mod., NR OFF

SUB (L-R) 12kHz,

30% mod., NR OFF

SUB (L-R) 1kHz,

100% mod., NR OFF

SUB (L-R) 1kHz,

200% mod., NR OFF

SUB (L-R) 1kHz,

NR OFF

ST-L (R) 1kHz,

100% mod., NR ON,

SAP Carrier (5f

H

)

SAP 1kHz 100% mod.

NR ON, PILOT (f

H

)

20 log

('5k'/'1k')

20 log

('12k'/'1k')

20 log

('100%'/'0%')

20 log

('12k'/'1k')

20 log

('100%'/'0%')

20 log

('NRSW = 0'/

'NRSW = 1')

20 log ('NRSW

= 1'/'NRSW = 0')

15kLPF

15kLPF

15kLPF

15kLPF

15kLPF

15kLPF

1kBPF

1kBPF

1/2

1/2

1/2

1/2

1/2

1/2

17

17

17

17

17

2

2

Main (L + R) (Pre-Emphasis: OFF) = 245mVrms

SUB (L

≠

R) (dbx-TV: OFF) = 490mVrms

Pilot = 49mVrms

SAP Carrier = 147mVrms

f

H

= 15.734kHz

Item

Symbol

Mode

Input pin

Input signal

Measurement

conditions

Filter

Output pin

Min.

Typ.

Max.

Unit

No.

≠ 11 ≠

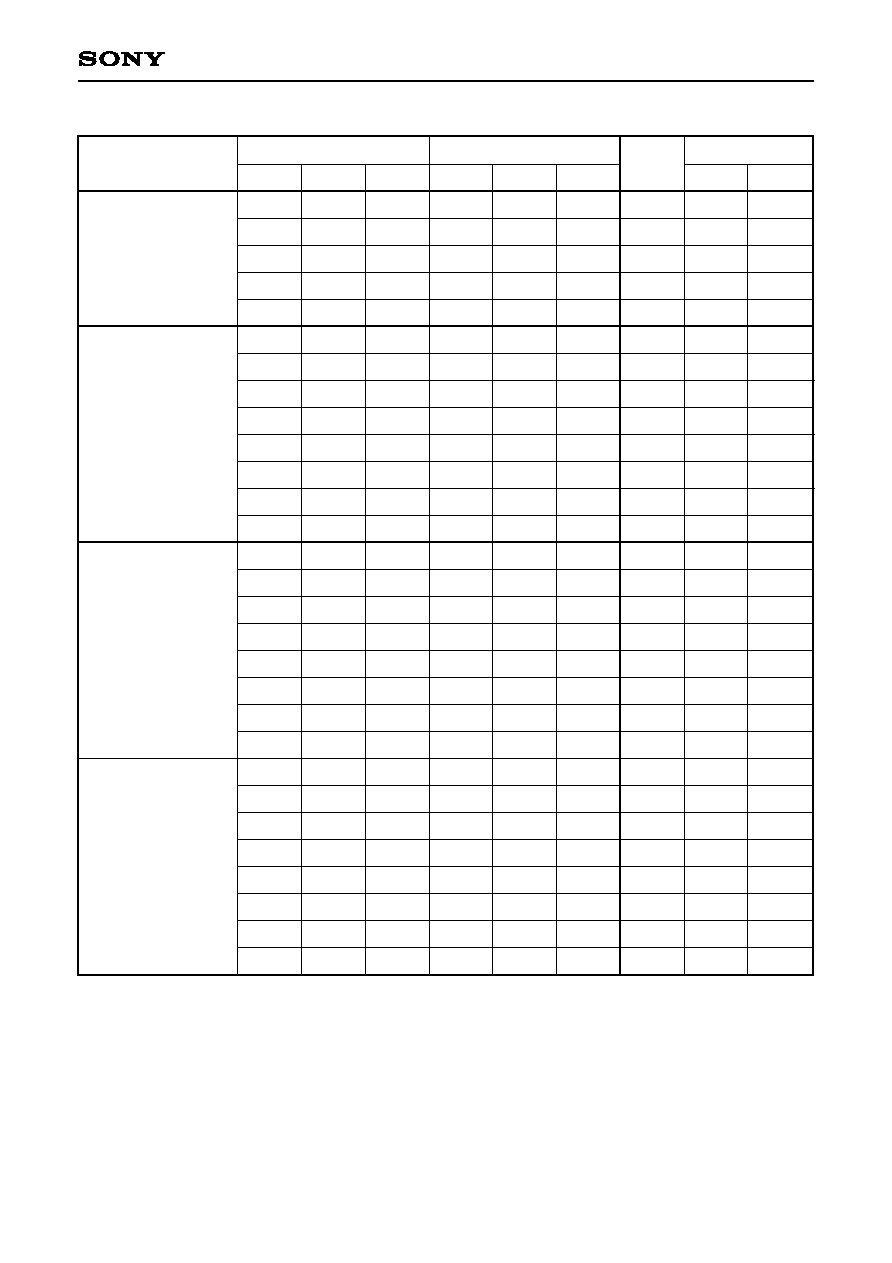

CXA2174S

(Ta = 25

∞

C, Vcc = 9V)

Stereo ON level

Stereo ON/OFF

hysteresis

SAP output level

SAP LPF frequency

response

SAP distortion

SAP S/N

SAP ON level

SAP ON/OFF hysteresis

ST separation 1 L

R

ST separation 1 R

L

ST separation 2 L

R

ST separation 2 R

L

LSOUT output level

LSOUT mute attenuation

LSOUT distortion

LSOUT overload

distortion

LSOUT S/N

LSOUT volume

maximum attenuation

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

THst

HYst

Vsap

FCsap

THDsap

SNsap

THsap

HYsap

STLsep1

STRsep1

STLsep2

STRsep2

Vls

MUls

THDls

THDlsmax

SNls

VOLmin

ST

SAP

SAP

SAP

SAP

SAP

ST

ST

ST

ST

EXT

EXT

EXT

EXT

EXT

EXT

11

11

11

11

11

11

11

11

11

11

30/29

30/29

30/29

30/29

30/29

30/29

≠

9.0

2.0

130

≠

3.0

--

46

≠

12.0

2.0

23

23

23

23

440

--

--

--

80

--

≠

6.0

6.0

160

0

2.5

55

≠

9.0

4.0

35

35

35

35

490

≠

90

0.01

0.03

88

≠

90

≠

3.0

10.0

190

2.5

6.0

--

≠

6.5

6.0

--

--

--

--

540

≠

80

0.3

0.3

--

≠

80

dB

dB

mVrms

dB

%

dB

dB

dB

dB

dB

dB

dB

mVrms

dB

%

%

dB

dB

Change

PILOT (f

H

) Level

SAP 1kHz 100% mod.

NR OFF

SAP 10kHz 30% mod.

NR OFF

SAP 1kHz 100% mod.

NR OFF

SAP 1kHz, NR OFF

Change

SAP Carrier (5f

H

)

Level

ST-L 300Hz 30% mod.

NR ON

ST-R 300Hz 30% mod.

NR ON

ST-L 3kHz 30% mod.

NR ON

ST-R 3kHz 30% mod.

NR ON

Sine wave 1kHz

490mVrms

Sine wave 1kHz

490mVrms

Sine wave 1kHz

490mVrms

Sine wave 1kHz

2Vrms

Sine wave 1kHz

490mVrms

Sine wave 1kHz

490mVrms

0dB = 49mVrms

20 log ('on level

'/'off level')

20 log

('10k'/'1k')

20 log

('100%'/'0%')

0dB = 147mVrms

20 log ('on level'

/'off level')

EXT1 = '1'

EXT1 = '1'

M1 = '0'

EXT1 = '1'

EXT1 = '1'

EXT1 = '1'

EXT1 = '1'

VOL-L = '0'

VOL-R = '0'

15kLPF

15kLPF

15kLPF

15kLPF

15kLPF

15kLPF

1kBPF

15kLPF

15kLPF

15kLPF

1kBPF

BUS

RETURN

20

20

20

20

BUS

RETURN

1/2

1/2

1/2

1/2

1/2

1/2

1/2

1/2

1/2

1/2

Item

Symbol

Mode

Input pin

Input signal

Measurement

conditions

Filter

Output pin

Min.

Typ.

Max.

Unit

No.

≠ 12 ≠

CXA2174S

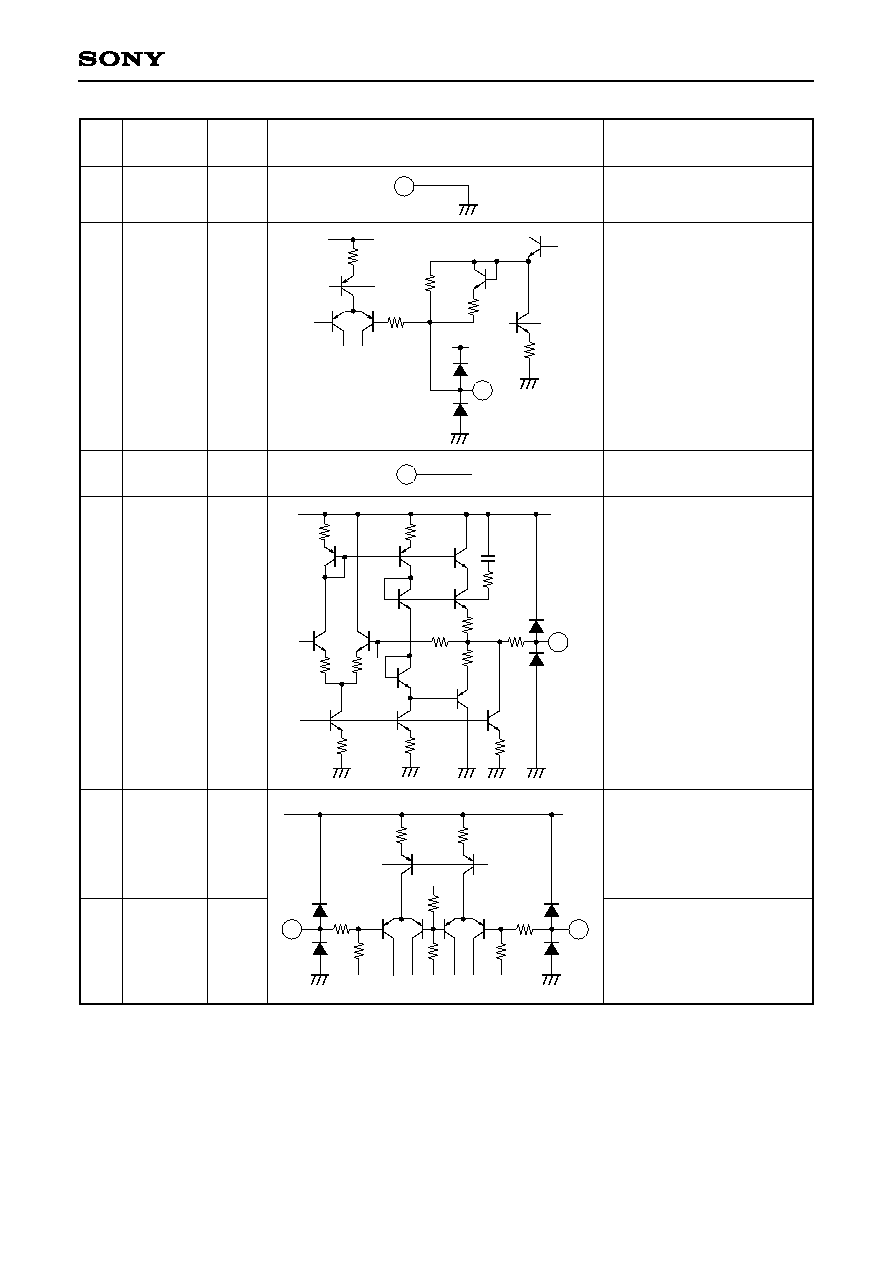

GND

V

CC

V2

9V

GND

GND

R8

62k

METAL

± 1

%

SIGNAL

GENERATOR

V1

AC

C10

5600p

R6

1MEG

R4

100k

C11

0.012µ

C7

4.7µ

DGND

I

2

C BUS DATA

R3

220

R1

220

LSOUT-R

2

3

4

5

6

7

8

9

10

11

12

13

14

15

1

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

LSOUT-L

SDA

SCL

DGND

MAININ

MAINOUT

PCINT1

PCINT2

PLINT

COMPIN

VGR

IREF

GND

SAPTC

AUX-L

AUX-R

VCAWGT

VCATC

VCAIN

VEOUT

VETC

VEWGT

VE

SAPIN

SAPOUT

NOISETC

STIN

SUBOUT

V

CC

C1

4.7µ

C3

4.7µ

C15

4.7µ

C16

10µ

C13

1µ

C19

4.7µ

C6

4.7µ

C20

100µ

C14

4.7µ

C18

4.7µ

C17

4.7µ

C12

2700P

R7

3.3k

C9

0.047µ

R5

3k

C8

3.3µ

TANTALUM

C4

1µ

R2

3.9k

C5

10µ

C2

4.7µ

TANTALUM

V3

AC

C5

4.7µ

V4

AC

S1

S2

S3

S4

BUFF

FILTERS

15kHz LPF

f

H

BPF

1kHz BPF

MEASURES

SIGNAL

GENERATOR

SIGNAL

GENERATOR

Electrical Characteristics Measurement Circuit

≠ 13 ≠

CXA2174S

Adjustment Method

1. ATT adjustment

1) TEST BIT is set to "TEST1 = 0" and "TEST-DA = 0".

2) Input a 100Hz, 245mVrms sine wave signal to COMPIN and monitor the LSOUT-L output level. Then,

adjust the "ATT" data for ATT adjustment so that the LSOUT-L output goes to the standard value

(490mVrms).

3) Adjustment range: ±20%

Adjustment bits:

4 bits

2. Separation adjustment

1) TEST BIT is set to "TEST1 = 0" and "TEST-DA = 0".

2) Set the unit to stereo mode and input the left channel only signal (modulation factor 30%, frequency 300Hz

NR-ON) to COMPIN. At this time, adjust the "WIDEBAND" adjustment data to reduce LSOUT-R output to

the minimum.

3) Next, set the frequency only of the input signal to 3kHz and adjust the "SPECTRAL" adjustment data to

reduce LSOUT-R output to the minimum.

4) The adjustments in 2 and 3 above are performed to optimize the separation.

5) "WIDEBAND"

"SPECTRAL"

Adjustment range: ±30%

Adjustment range: ±15%

Adjustment bits:

6 bits

Adjustment bits:

6 bits

Adjust this IC through Tuner and IF when this IC is mounted in the set.

≠ 14 ≠

CXA2174S

SPECTRAL

WIDEBAND

0000

0001

0010

0011

0100

0101

SLAVE RECEIVER

84H (1000 0100)

SLAVE TRANSMITTER

85H (1000 0101)

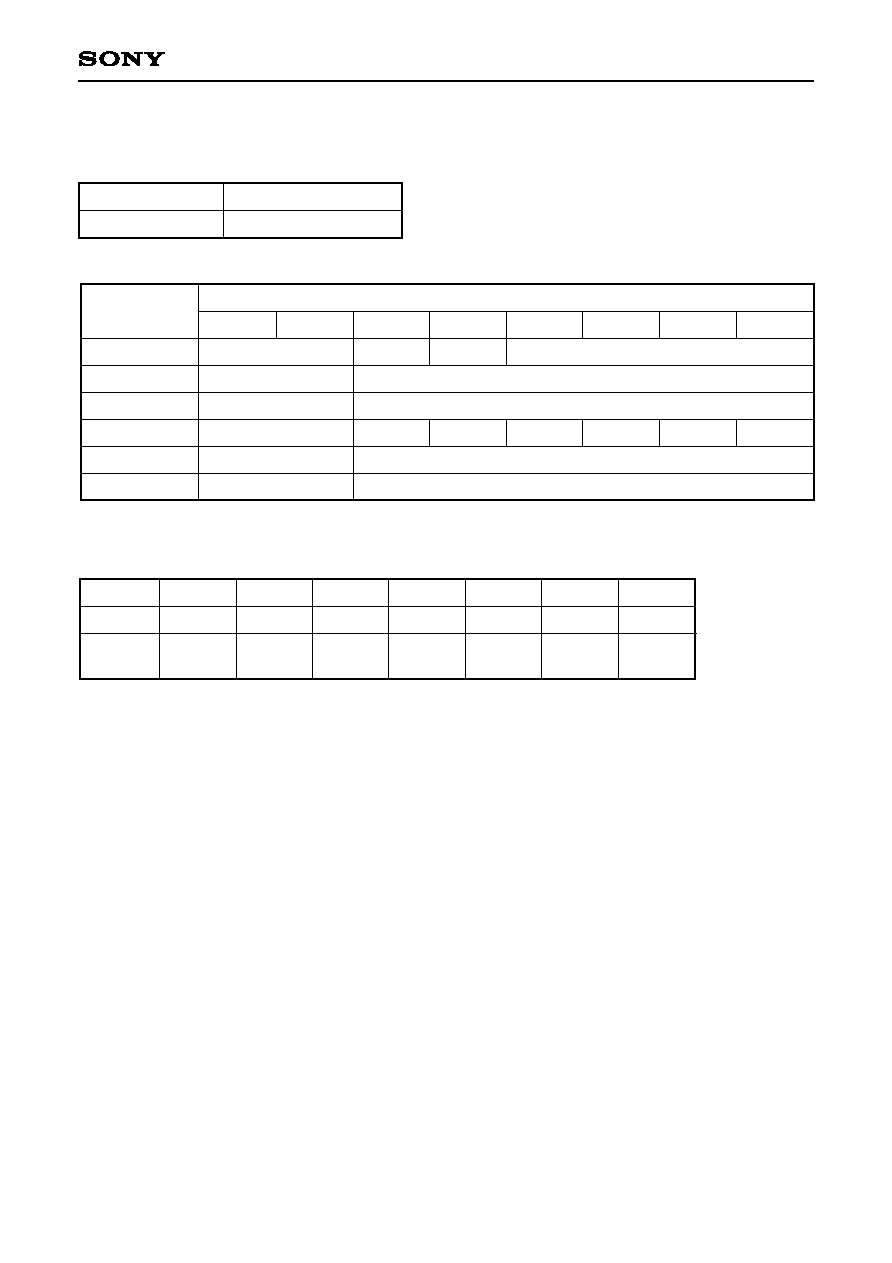

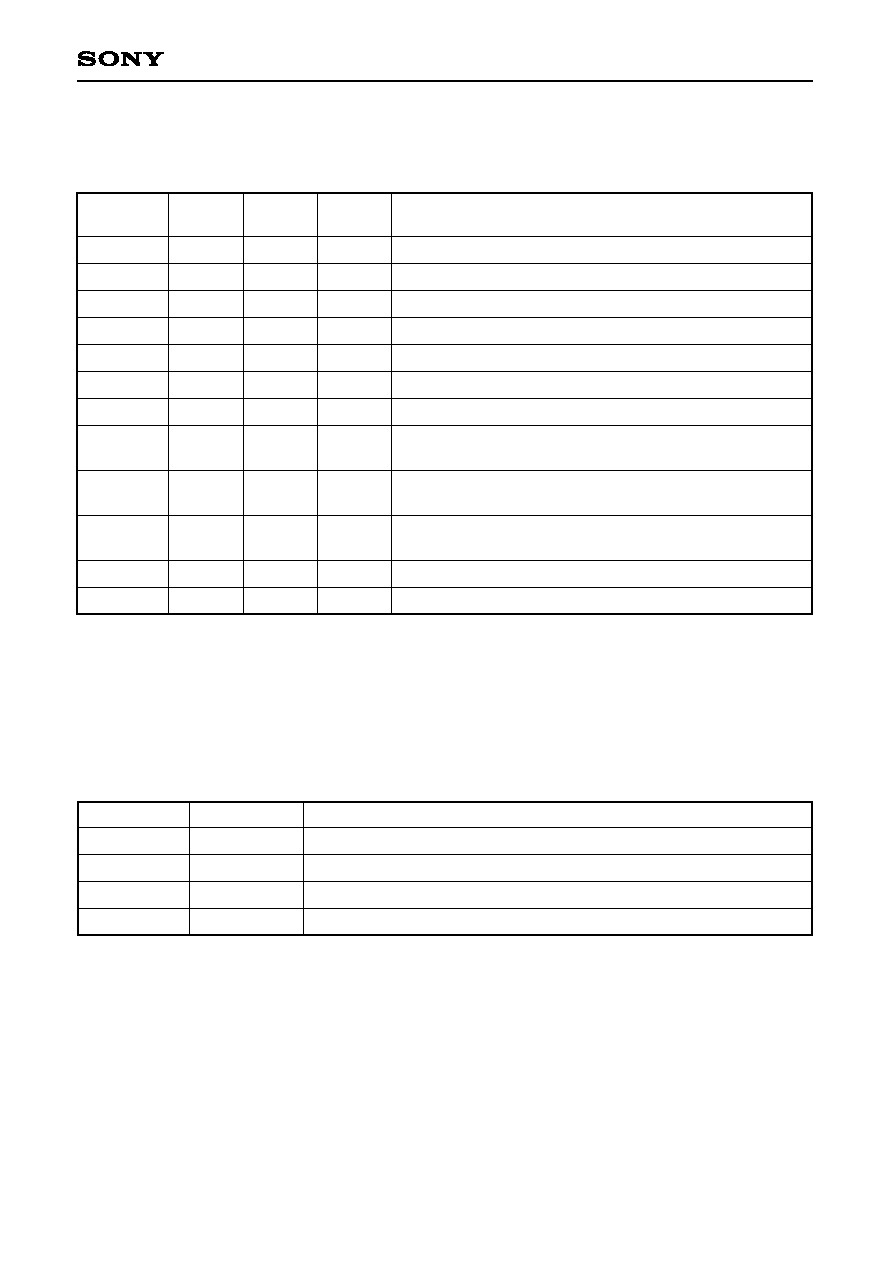

Register Specifications

Slave address

Register table

Status Registers

DATA

SUB ADDRESS

MSB

LSB

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

TEST-DA

EXT1

TEST1

NRSW

VOL-L

VOL-R

FOMO

SAPC

M1

STA1

BIT7

POWER

ON RESET

STA2

BIT6

STEREO

STA3

BIT5

SAP

STA4

BIT4

NOISE

STA5

BIT3

--

STA6

BIT2

--

STA7

BIT1

--

STA8

BIT0

--

ATT

: don't care

Note) The micro computer reads both SAP and NOISE status and judges SAP discrimination.

≠ 15 ≠

CXA2174S

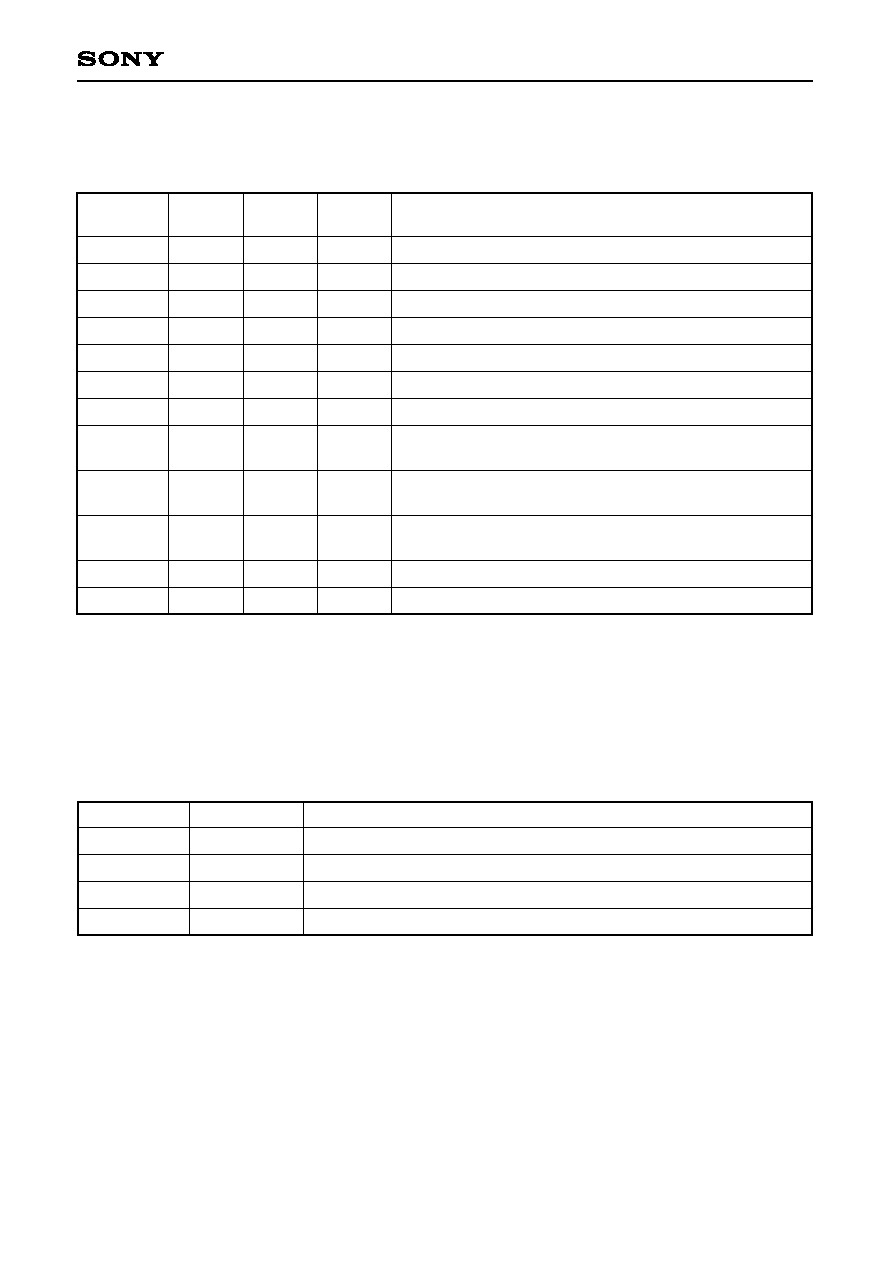

Description of Registers

Control registers

ATT

SPECTRAL

WIDEBAND

TEST-DA

TEST1

EXT1

NRSW

FOMO

M1

SAPC

VOL-L

VOL-R

Input level adjustment

Adjustment of stereo separation (3kHz)

Adjustment of stereo separation (300Hz)

DAC test mode

Test mode

Selection of TV mode or external input mode

Selection of the output signal (Stereo mode, SAP mode)

Forced MONO

(Left channel only is MONO during SAP output.)

Selection of LSOUT mute function ON/OFF

(0: mute ON, 1: mute OFF)

Selection SAP mode or L + R mode according to the

presence of SAP brodecasting

Left channel volume control

Right channel volume control

Register

Contents

4

6

6

1

1

1

1

1

1

1

1

1

A

A

A

T

T

U

U

U

U

S

U

U

9

1F

1F

0

0

0

0

0

1

0

3F

3F

Number

of bits

Classifi-

cation

1

Standard

setting

1

Classification U: User control

A: Adjustment

S: Proper to set

T: Test

Status registers

PONRES

STEREO

SAP

NOISE

1

1

1

1

POWER ON RESET detection;

1: RESET

Stereo discrimination of the COMPIN input signal;

1: Stereo

SAP discrimination of the COMPIN input signal;

1: SAP

Noise level discrimination of the SAP signal;

1: Noise

Register

Number of bits

Contents

≠ 16 ≠

CXA2174S

Description of Control Registers

ATT

(4):

Perform input level adjustment.

0 = Level min.

F = Level max.

SPECTRAL

(6):

Perform high frequency (fs = 3kHz) separation adjustment.

0 = Level max.

3F = Level min.

WIDEBAND

(6):

Perform low frequency (fs = 300Hz) separation adjustment.

0 = Level min.

3F = Level max.

TEST-DA

(1):

Set DAC output test mode.

0 = Normal mode

1 = DAC output test mode

In addition, the following output are present at Pin 2.

LSOUT-L (Pin 2): DA control DC level

TEST1

(1):

Monitor SAPBPF and NRBPF output

0 = Normal mode

1 = SAPBPF, NRBPF output

In addition, the following outputs are present at Pins 1 and 2.

LSOUT-L (Pin 2): SAP BPF OUT

LSOUT-R (Pin 1): NR BPF OUT

EXT1

(1):

Select TV mode or external input mode

0 = TV mode

1 = External input mode

NRSW

(1):

Select stereo mode or SAP mode

0 = Stereo mode

1 = SAP mode

FOMO

(1):

Select forced MONO mode

0 = Normal mode

1 = Forced MONO mode

M1

(1):

Mute the LSOUT-L and LSOUT-R output.

0 = Mute ON

1 = Mute OFF

≠ 17 ≠

CXA2174S

SAPC

(1):

Select the SAP signal output mode

When there is no SAP signal, the conditions for selecting SAP output are selected by

SAPC.

0 = L + R output is selected

1 = SAP output is selected

VOL-L

(6):

LSOUT-L output signal level control

0 =

Volume

min.

3F = Volume max.

≠1.25dB/STEP

VOL-R

(6):

LSOUT-R output signal level control

0 = Volume min.

3F = Volume max.

≠1.25dB/STEP

≠ 18 ≠

CXA2174S

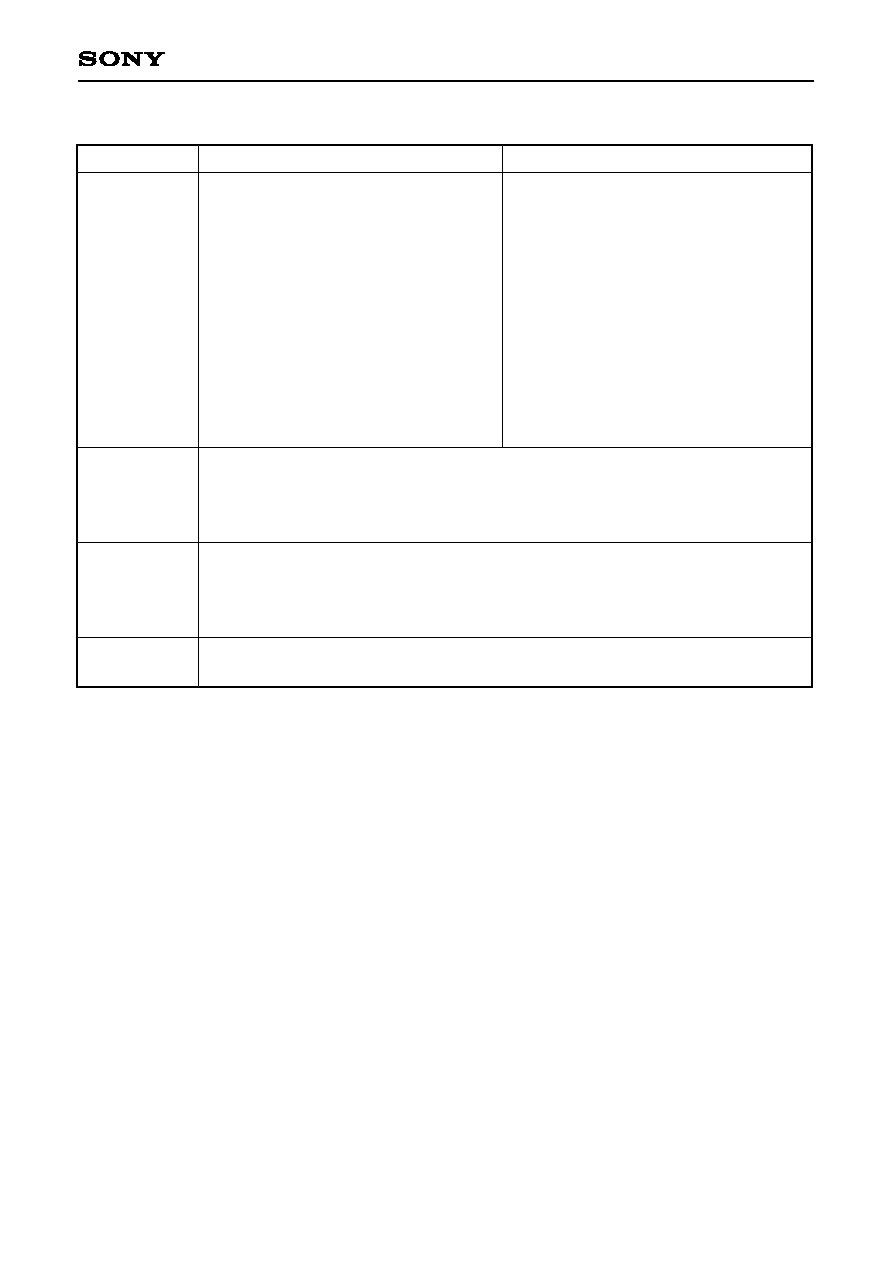

Description of Mode Control

NRSW

FOMO

SAPC

M1

"Select dbx input and TV decoder output"

Conditions: FOMO = 0

NRSW = 0 (MONO or ST output)

∑ During ST input:

left channel: L,

right channel: R

∑ During other input: left channel: L + R,

right channel: L + R

NRSW = 1 (SAP output)

∑ When there is "SAP" during SAP

discrimination

≠ left channel: SAP, right channel: SAP

∑ When there is "No SAP", output is the

same as when NRSW = 0.

"Select dbx input and TV decoder output"

Conditions: FOMO = 0

NRSW = 0 (MONO or ST output)

As on the left

NRSW = 1 (SAP output)

∑ Regardless of the presence of SAP

discrimination,

dbx input: "SAP"

left channel: SAP, right channel: SAP

However, when there is no SAP, SAPOUT

output is soft muted (≠7dB)

Mode control

SAPC = 0

SAPC = 1

"Forced MONO"

FOMO = 1

∑ During SAP output: left channel: L + R, right channel: SAP

∑ During ST or MONO output: left channel: L + R, right channel: L + R

Change the selection conditions for "MONO or ST output" and "SAP output".

SAPC = 0: Switch to SAP output when there is SAP discrimination.

Do not switch to SAP output when there is no SAP discrimination.

SAPC = 1: Switch to SAP output regardless of whether there is SAP discrimination.

"MUTE"

M1 = 0: LSOUT output is muted.

≠ 19 ≠

CXA2174S

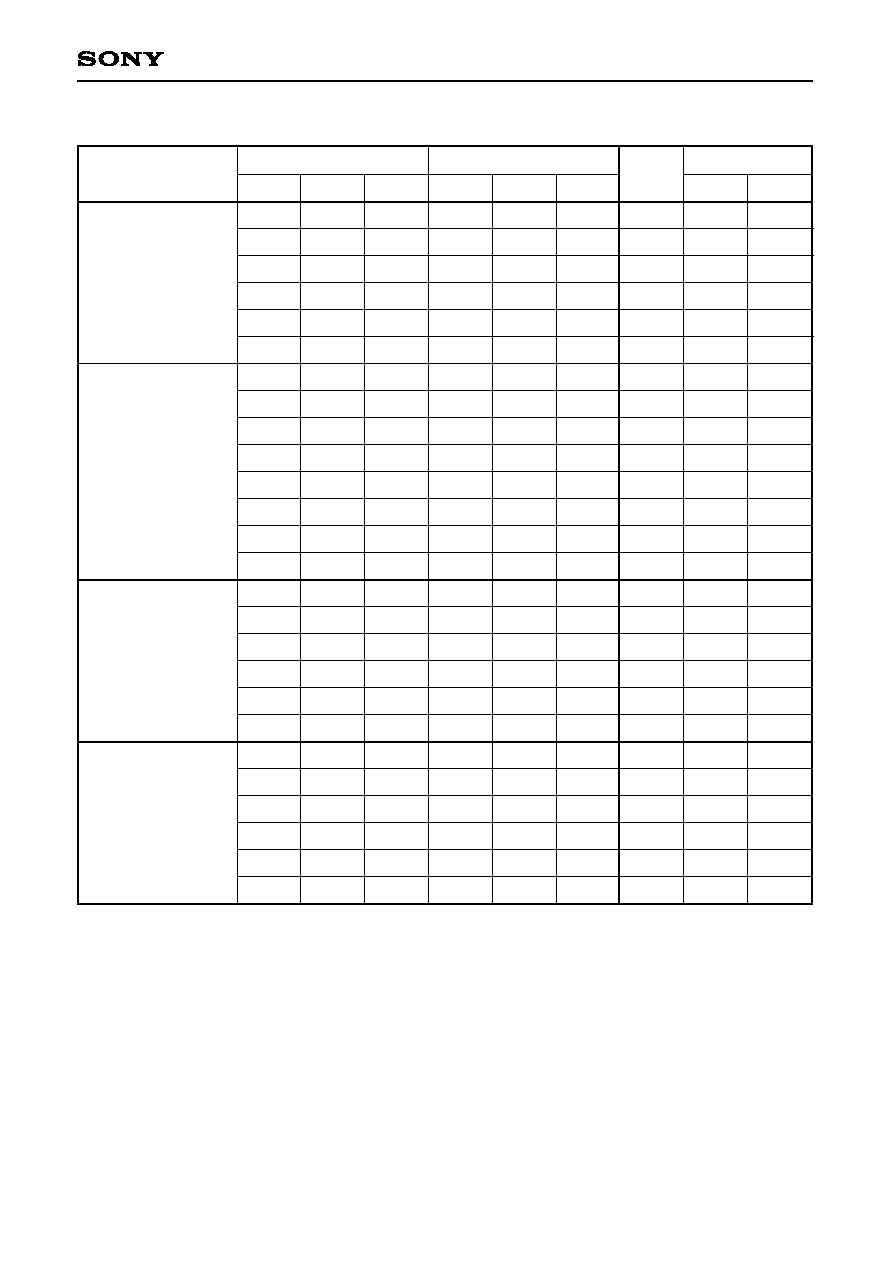

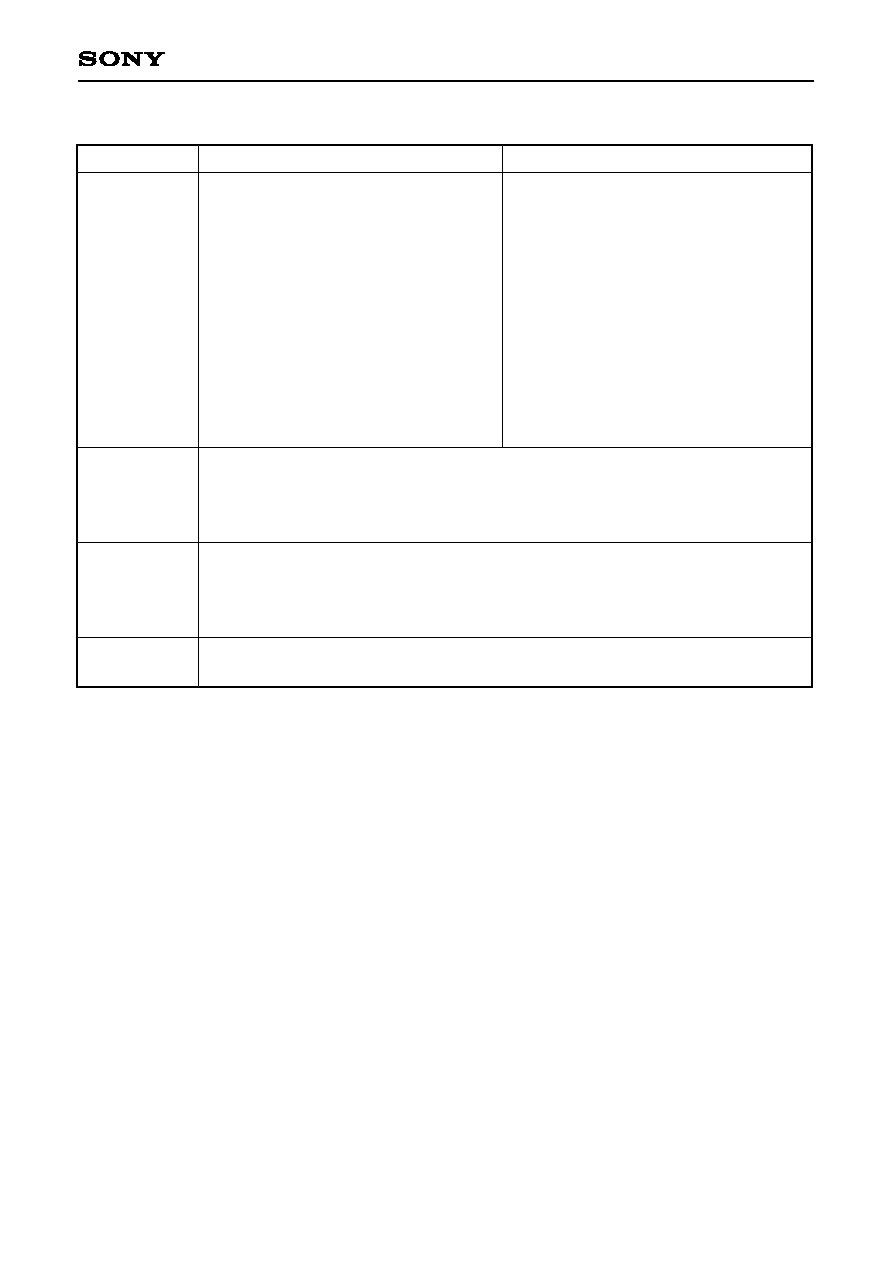

Decoder Output and Mode Control Table 1 (SAPC = 1)

Input signal mode

Mode detection

Mode control

dbx

input

Output

ST

SAP

NOISE

NRSW

FOMO

SAPC

Lch

Rch

1

1

Note

(SAP) : The SAPOUT output signal is soft muted (approximately ≠7dB).

The signal is soft muted when NOISE = 1.

: Don't care.

1

SAP or NOISE discrimination may be made during MONO or STEREO input when the noise is

inputted in the weak electric field.

Then microcomputer reads "NOISE" status from IC and decides whether SAP is outputted.

"NOISE" status rises earlier than "SAP" status when the amount of noise is increased to COMPIN.

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

1

1

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

1

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

1

0

1

1

0

0

0

0

1

1

1

1

0

0

1

1

1

1

0

0

1

1

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

MUTE

SAP

SAP

MUTE

(SAP)

(SAP)

L ≠ R

MUTE

L ≠ R

MUTE

SAP

SAP

(SAP)

(SAP)

MUTE

MUTE

SAP

SAP

(SAP)

(SAP)

L ≠ R

MUTE

SAP

SAP

(SAP)

(SAP)

L + R

SAP

L + R

L + R

(SAP)

L + R

L

L + R

L

L + R

SAP

L + R

(SAP)

L + R

L + R

L + R

SAP

L + R

(SAP)

L + R

L

L + R

SAP

L + R

(SAP)

L + R

L + R

SAP

SAP

L + R

(SAP)

(SAP)

R

L + R

R

L + R

SAP

SAP

(SAP)

(SAP)

L + R

L + R

SAP

SAP

(SAP)

(SAP)

R

L + R

SAP

SAP

(SAP)

(SAP)

MONO

STEREO

MONO & SAP

STEREO & SAP

≠ 20 ≠

CXA2174S

Decoder Output and Mode Control Table 2 (SAPC = 0)

Input signal mode

Mode detection

Mode control

dbx

input

Output

ST

SAP

NOISE

NRSW

FOMO

SAPC

Lch

Rch

1

1

Note

(SAP) : The SAPOUT output signal is soft muted (approximately ≠7dB).

The signal is soft muted when NOISE = 1.

: Don't care.

1

SAP or NOISE discrimination may be made during MONO or STEREO input when the noise is

inputted in the weak electric field.

Then microcomputer reads "NOISE" status from IC and decides whether SAP is outputted.

"NOISE" status rises earlier than "SAP" status when the amount of noise is increased to COMPIN.

MONO

STEREO

MONO & SAP

STEREO & SAP

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

1

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

MUTE

MUTE

MUTE

(SAP)

(SAP)

L ≠ R

MUTE

L ≠ R

MUTE

L ≠ R

MUTE

(SAP)

(SAP)

MUTE

MUTE

SAP

SAP

MUTE

MUTE

(SAP)

(SAP)

L ≠ R

MUTE

SAP

SAP

L ≠ R

MUTE

(SAP)

(SAP)

L + R

L + R

L + R

(SAP)

L + R

L

L + R

L

L + R

L

L + R

(SAP)

L + R

L + R

L + R

SAP

L + R

L + R

L + R

(SAP)

L + R

L

L + R

SAP

L + R

L

L + R

(SAP)

L + R

L + R

L + R

L + R

(SAP)

(SAP)

R

L + R

R

L + R

R

L + R

(SAP)

(SAP)

L + R

L + R

SAP

SAP

L + R

L + R

(SAP)

(SAP)

R

L + R

SAP

SAP

R

L + R

(SAP)

(SAP)

≠ 21 ≠

CXA2174S

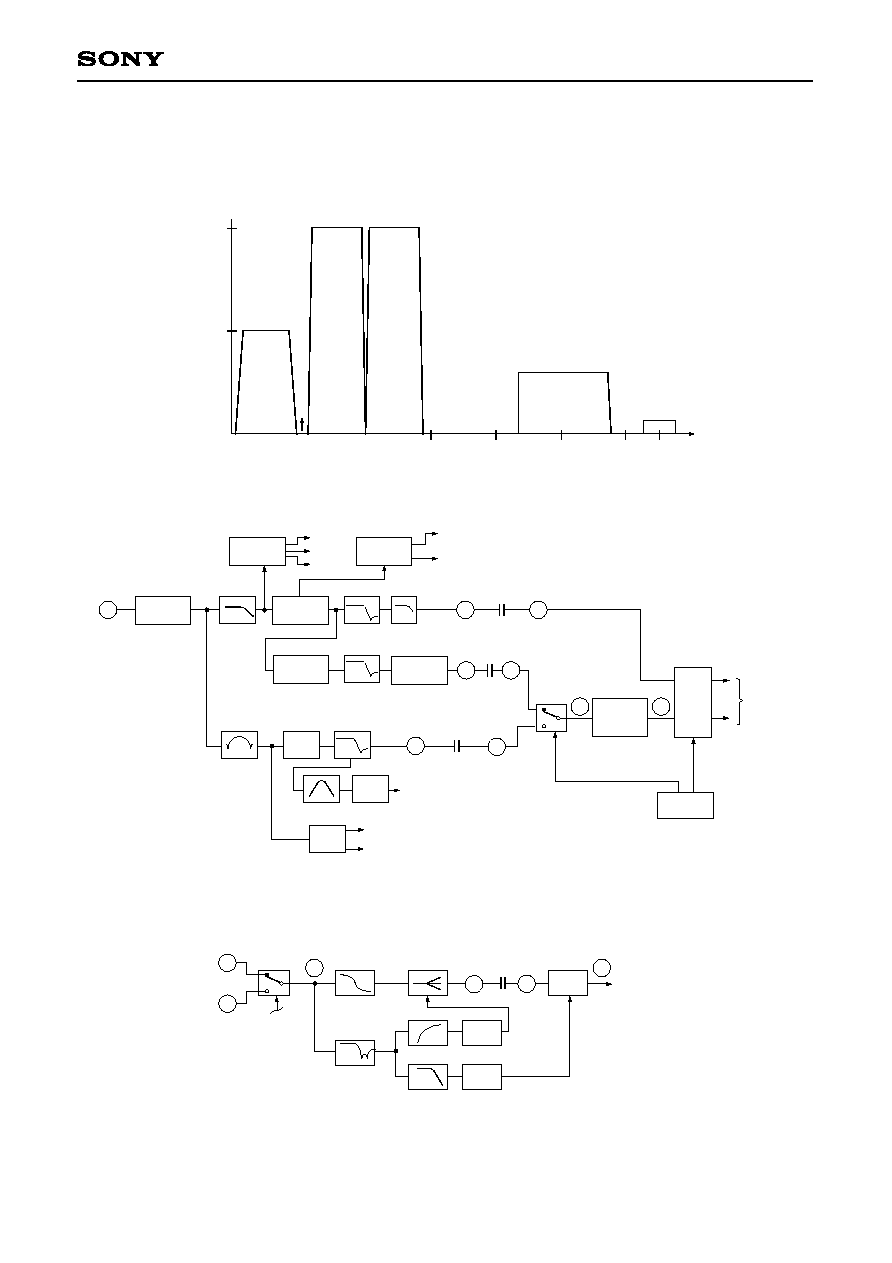

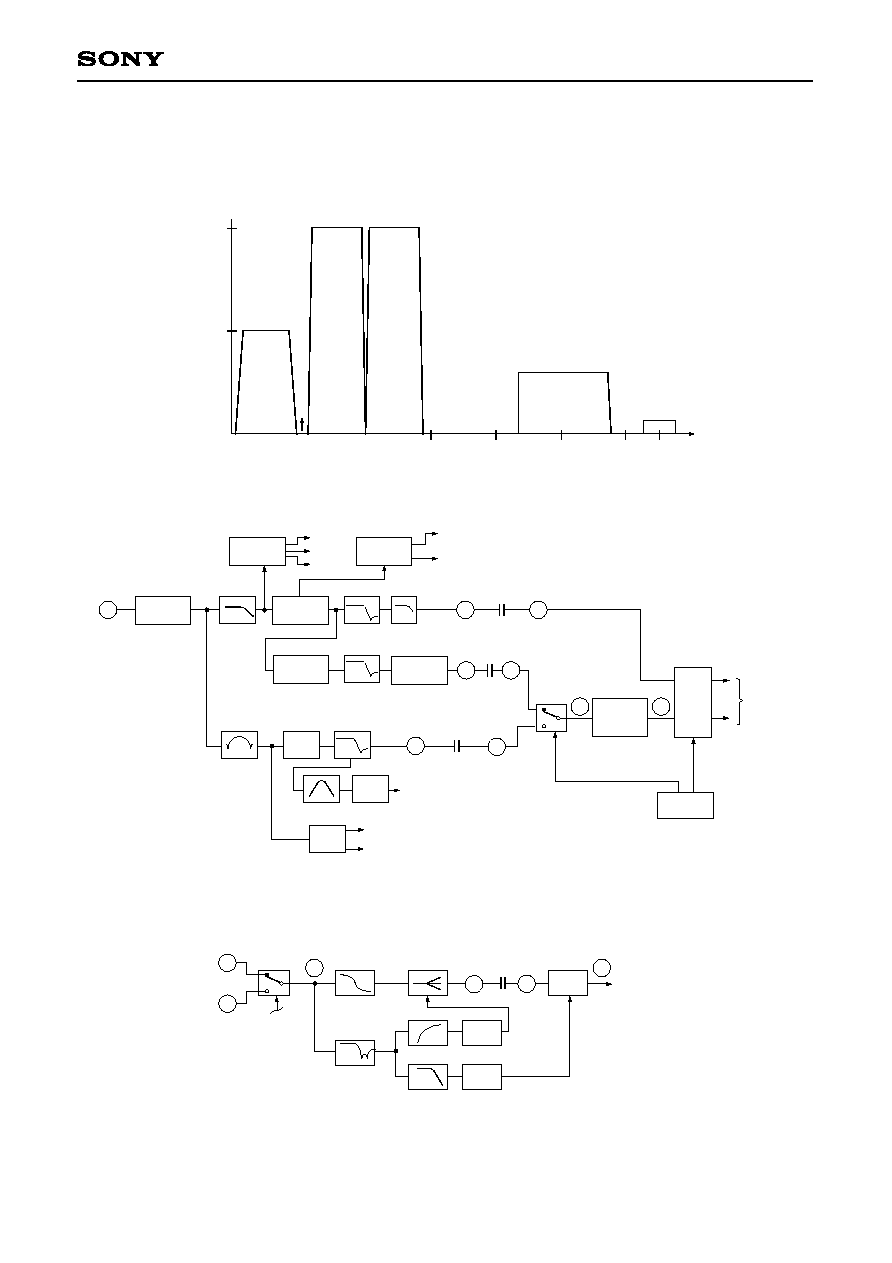

Description of Operation

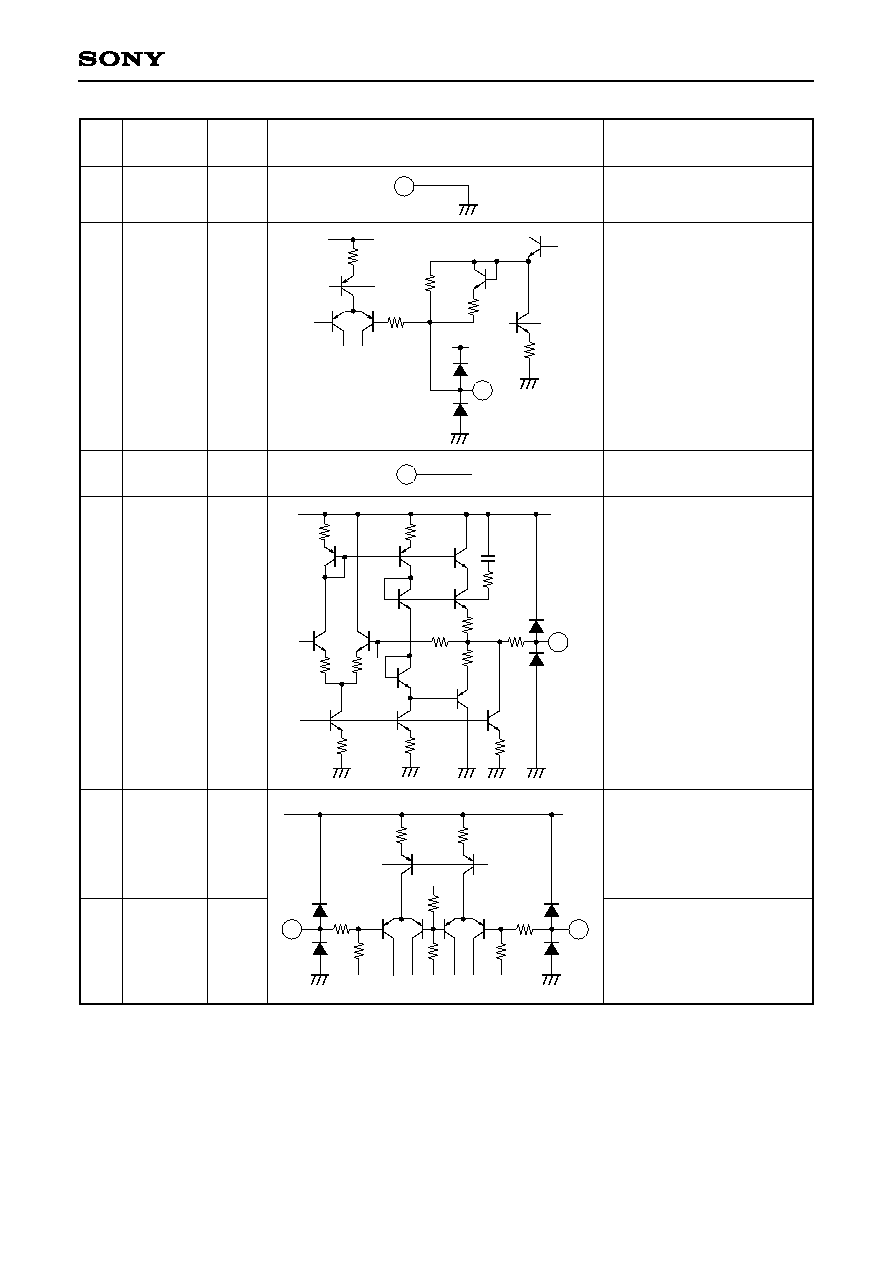

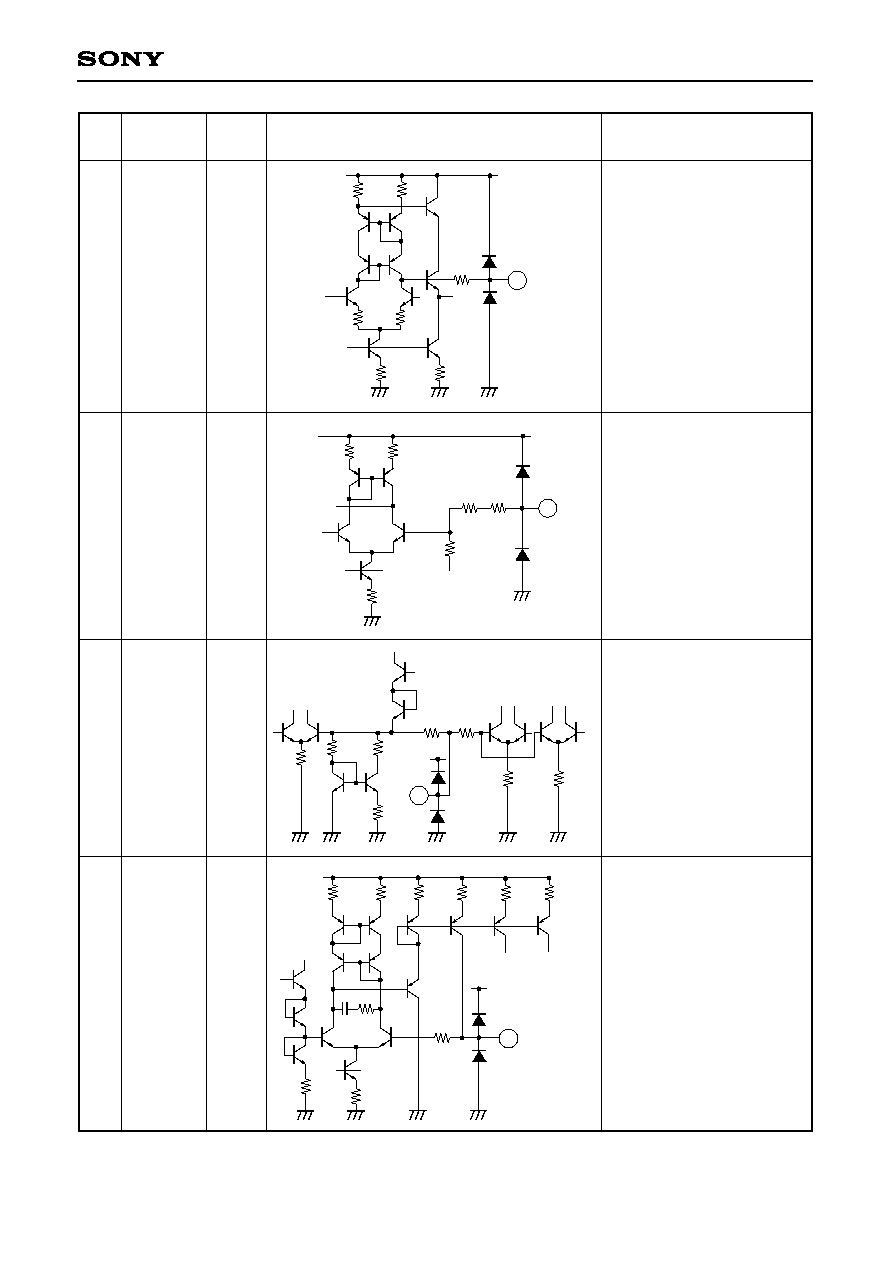

The US audio multiplexing system possesses the base band spectrum shown in Fig. 1.

Fig. 1. Base band spectrum

Fig. 2. Overall block diagram (See Fig. 3 for the dbx-TV block)

Fig 3. dbx-TV block

PEAK DEV

kHz

50

25

25

L + R

50 ≠ 15kHz

L-R

dbx-TV

NR

50

AM-DSB-SC

SAP

dbx-TV NR

FM 10kHz

50 ≠ 10kHz

TELEMETRY

FM 3kHz

15

f

H

= 15.734kHz

f

H

2f

H

3f

H

4f

H

5f

H

6f

H

6.5f

H

f

5

PILOT

3

(COMPIN)

STEREO LPF

PLL

(VCO 8f

H

)

2f

HL

0∞

f

HL

90∞

f

HL

0∞

MODE

CONTROL

PILOT

DET

MVCA

PILOT

CANCEL

MAIN LPF DE.EM

(MAIN OUT)

L + R

4.7µ

(MAIN IN)

L-R (DSB)

DET

INJ.

LOCK

SUBVCA

SUB LPF

WIDEBAND

(SUBOUT) (ST IN)

4.7µ

NR SW

dbx-TV

BLOCK

MATRIX

(Lch)

(Rch)

MODE

CONTROL

(SAP IN)

4.7µ

SAP (FM)

DET

SAP LPF

MODE

CONTROL

SAP BPF

(SAP OUT)

L ≠ R

to

TVSW

NOISE

DET

I C BUS

DECODER

2

SAP

DET

A

B

I C BUS

DECODER

2

I C BUS

DECODER

2

11

7

6

17

18

20

21

NR SW

FIXED

DEEMPHASIS

VARIABLE

DEEMPHASIS

(VE OUT)

(VCA IN)

to

MATRIX

4.7µ

HPF

LPF

LPF

RMS

DET

RMS

DET

VCA

A

B

(ST IN)

(SAP IN)

18

21

25

26

≠ 22 ≠

CXA2174S

(1) L + R (MAIN)

After the audio multiplexing signal input from COMPIN (Pin 11) passes through MVCA, the SAP signal

and telemetry signal are suppressed by STEREO LPF. Next, the pilot signals are canceled. Finally, the

L ≠ R signal and SAP signal are removed by MAIN LPF, and frequency characteristics are flattened

(de-emphasized) and input to the matrix.

(2) L ≠ R (SUB)

The L ≠ R signal follows the same course as L + R before the pilot signal is canceled. L ≠ R has no

carrier signal, as it is a suppressed-carrier double-sideband amplitude modulated signal (DSB-AM

modulated). For this reason, the pilot signal is used to regenerate the carrier signal (quasi-sine wave)

to be used for the demodulation of the L ≠ R signal. In the last stage, the residual high frequency

components are removed by SUB LPF and the L ≠ R signal is input to the dbx-TV block via the NRSW

circuit after passing through SUBVCA.

(3) SAP

SAP is an FM signal using 5f

H

as a carrier as shown in the Fig. 1. First, the SAP signal only is

extracted using SAP BPF. Then, this is subjected to FM detection. Finally, residual high frequency

components are removed and frequency characteristics flattened using SAP LPF, and the SAP signal

is input to the dbx-TV block via the NRSW circuit. When there is no SAP signal, the Pin 20 output is

soft muted.

(4) Mode discrimination

Stereo discrimination is performed by detecting the pilot signal amplitude. SAP discrimination is

performed by detecting the 5f

H

carrier amplitude. NOISE discrimination is performed by detecting the

noise near 25kHz after FM detection of SAP signal.

(5) dbx-TV block

Either the L ≠ R signal or SAP signal input respectively from ST IN (Pin 18) or SAP IN (Pin 21) is

selected by the mode control and input to the dbx-TV block.

The input signal then passes through the fixed de-emphasis circuit and is applied to the variable de-

emphasis circuit. The signal output from the variable de-emphasis circuit passes through an external

capacitor and is applied to VCA (voltage control amplifier). Finally, the VCA output is converted from a

current to a voltage using an operational amplifier and then input to the matrix.

The variable de-emphasis circuit transmittance and VCA gain are respectively controlled by Each of

effective value detection circuits. Each of the effective value detection circuits passes the input signal

through a predetermined filter for weighting before the effective value of the weighted signal is detected

to provide the control signal.

(6) Matrix, TVSW

The signals (L + R, L ≠ R, SAP) input to "MATRIX" become the outputs for the ST-L, ST-R, MONO and

SAP signals according to the mode control and whether there is ST / SAP discrimination.

"TVSW" switches the "MATRIX" output signal and external input signal.

(7) Others

"MVCA" is a VCA which adjusts the input signal level to the standard level of this IC.

"Bias" supplies the reference voltage and reference current to the other blocks. The current flowing to

the resistor connecting IREF (Pin 13) with GND become the reference current.

≠ 23 ≠

CXA2174S

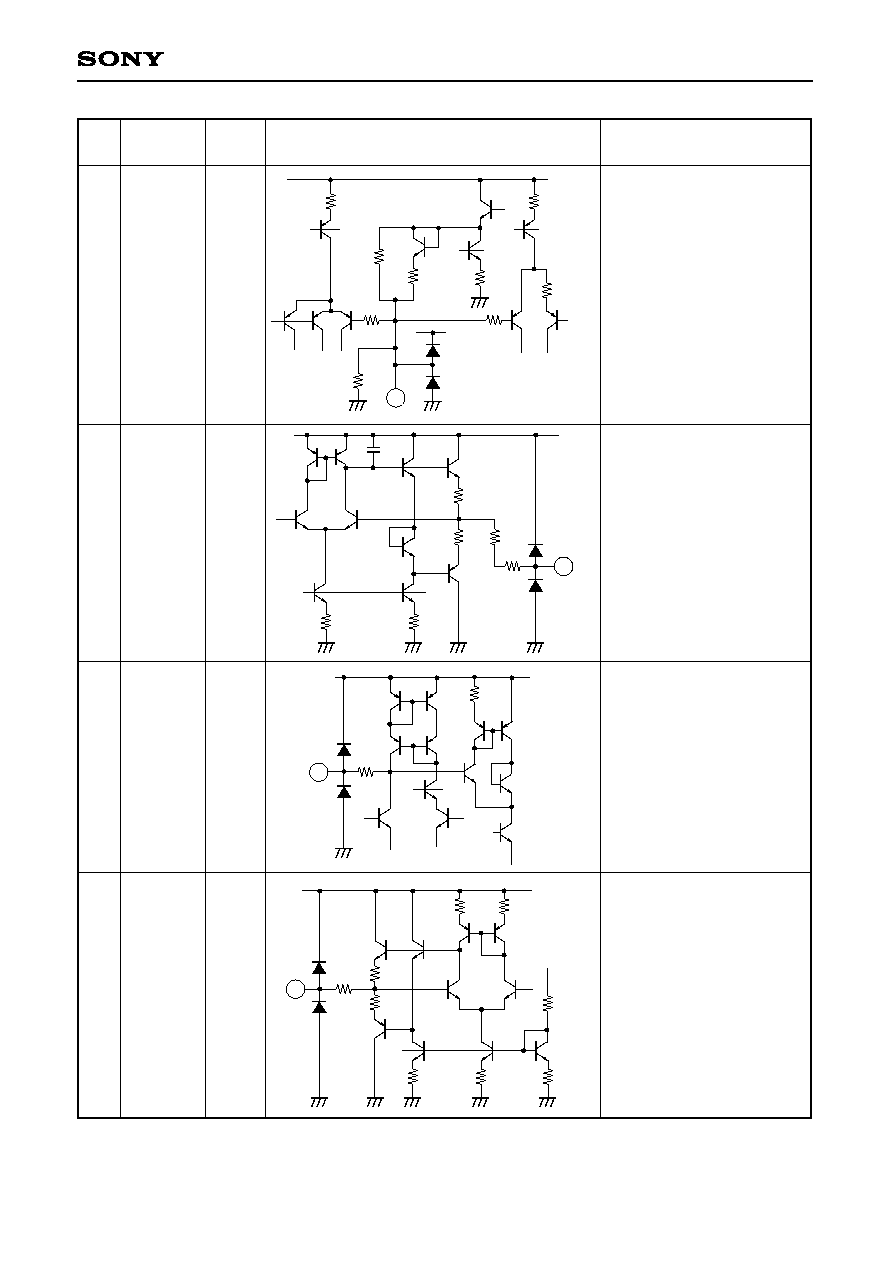

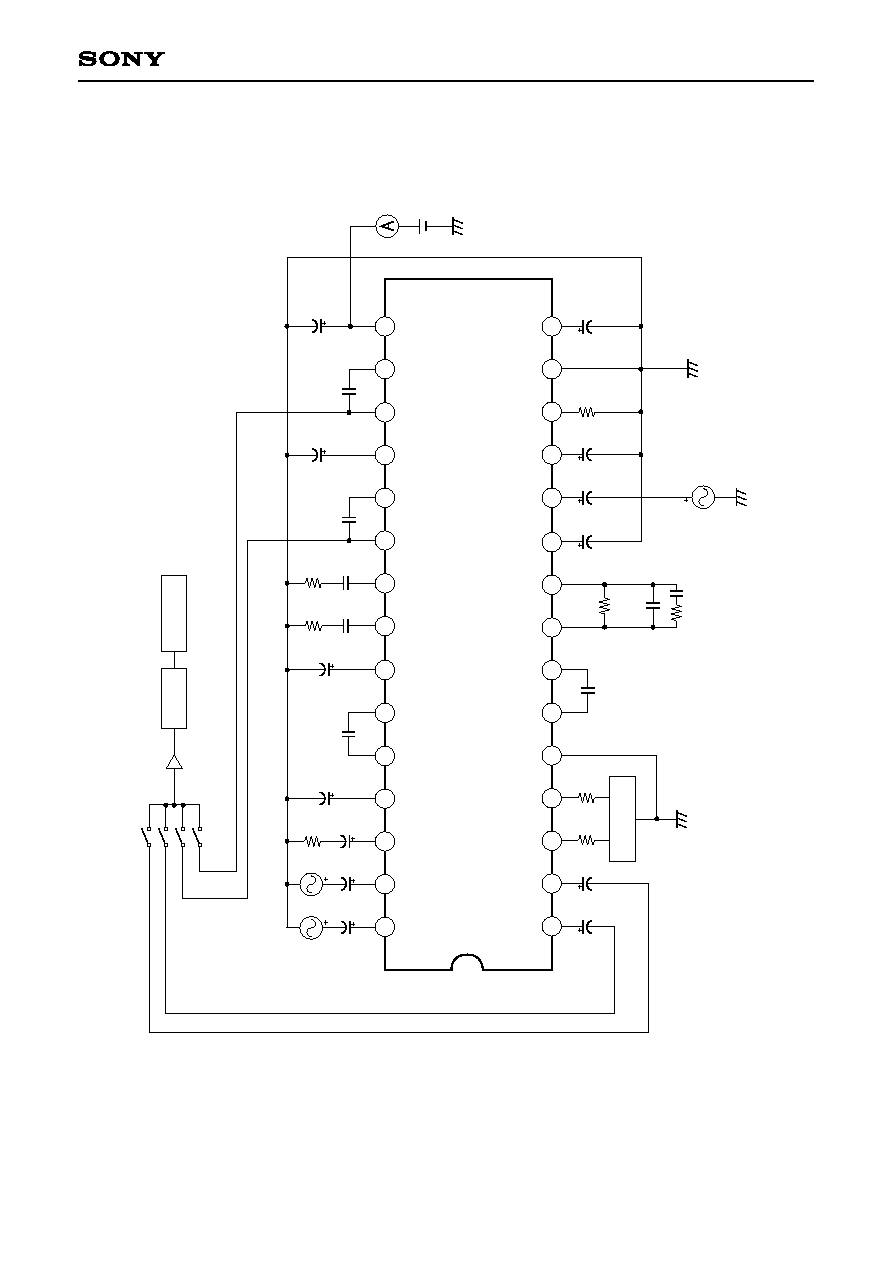

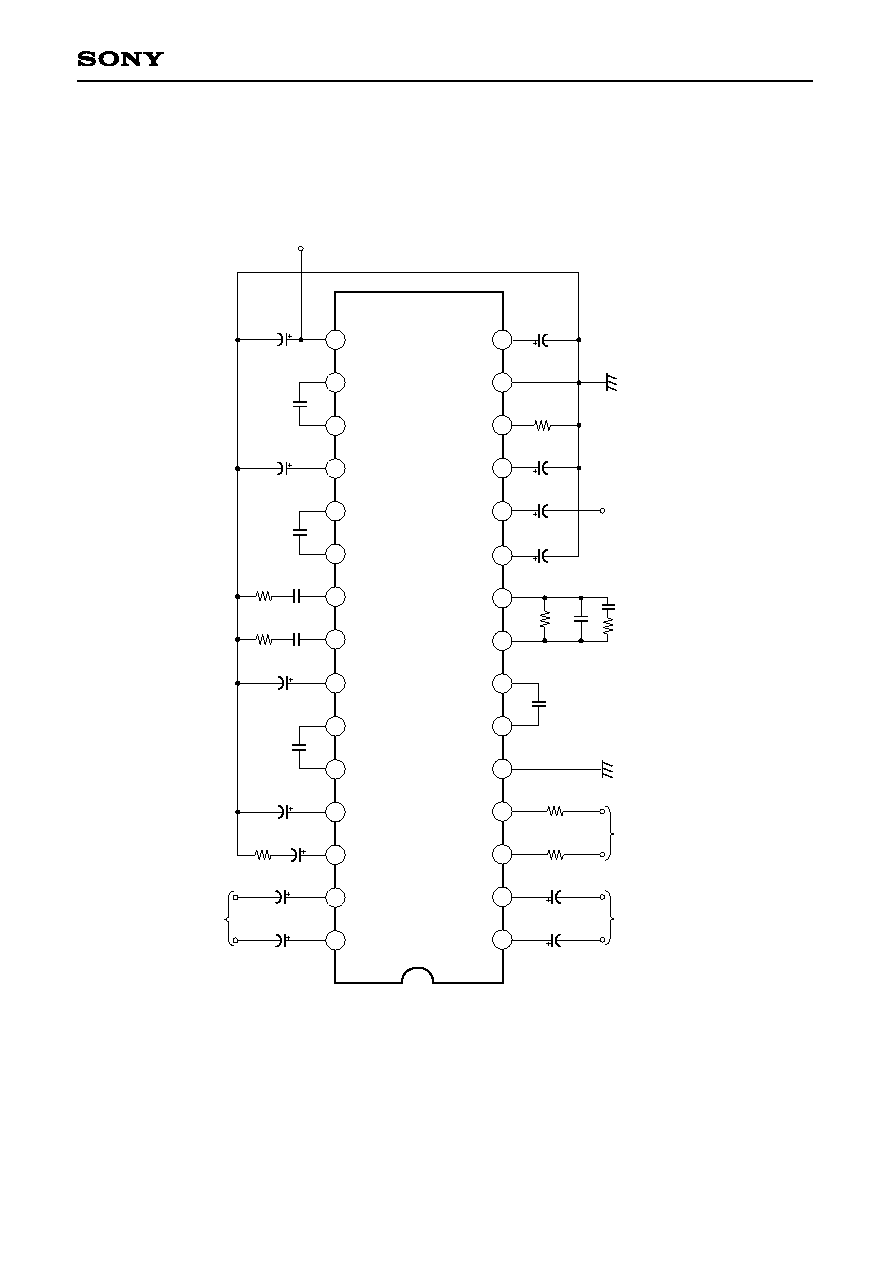

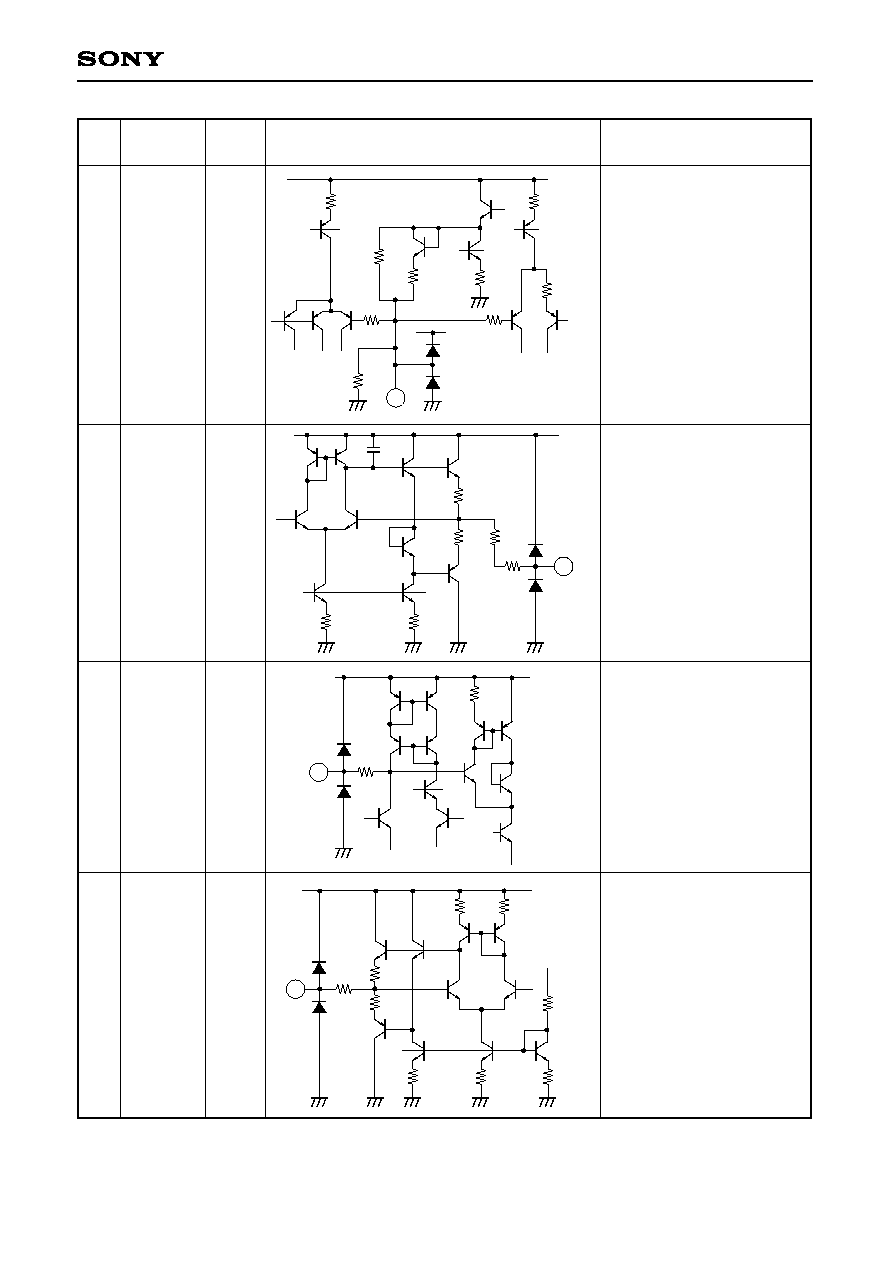

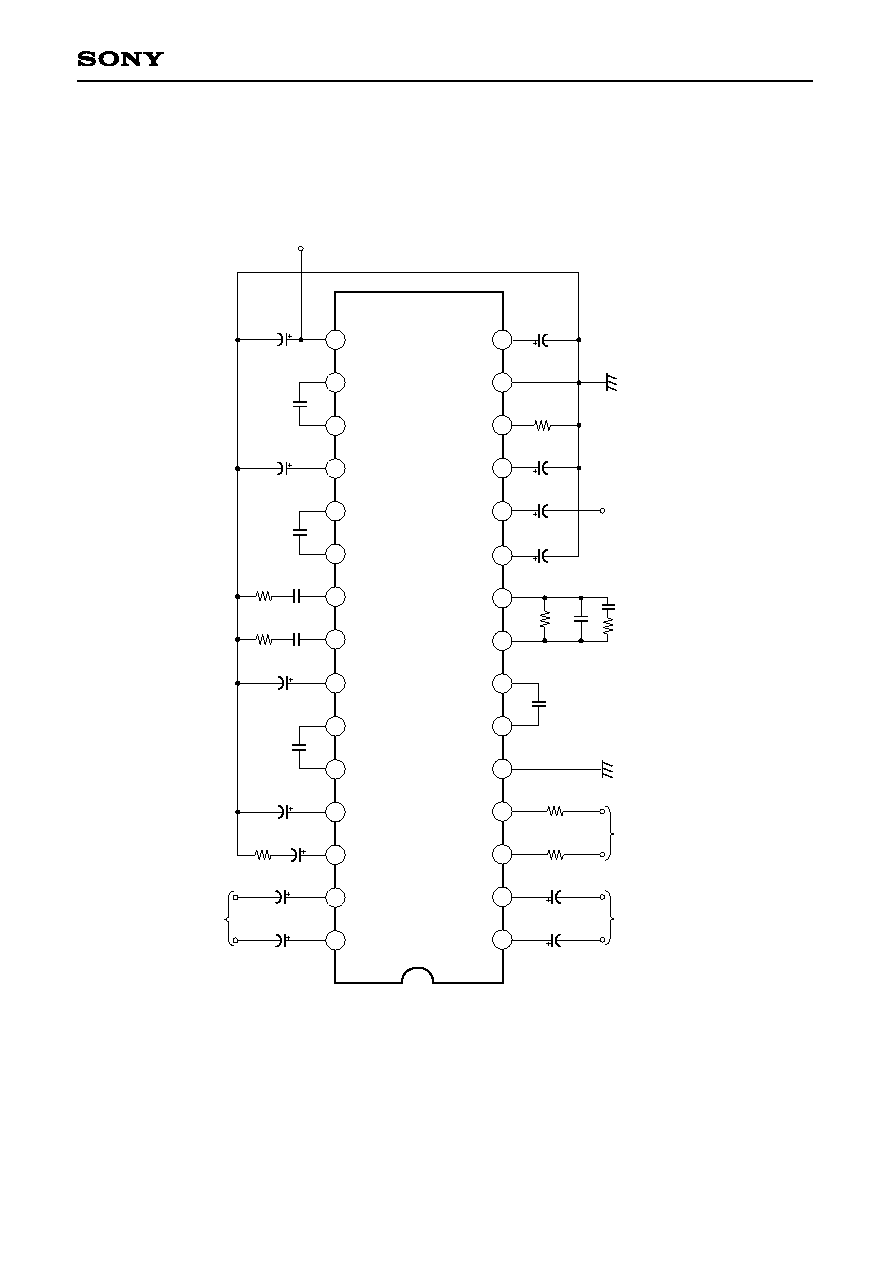

Application Circuit

GND

62k

METAL

± 1

%

5600p

1MEG

100k

0.012µ

4.7µ

DGND

220

220

LSOUT-R

2

3

4

5

6

7

8

9

10

11

12

13

14

15

1

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

LSOUT-L

SDA

SCL

DGND

MAININ

MAINOUT

PCINT1

PCINT2

PLINT

COMPIN

VGR

IREF

GND

SAPTC

AUX-L

AUX-R

VCAWGT

VCATC

VCAIN

VEOUT

VETC

VEWGT

VE

SAPIN

SAPOUT

NOISETC

STIN

SUBOUT

V

CC

4.7µ

4.7µ

4.7µ

10µ

1µ

4.7µ

4.7µ

100µ

4.7µ

4.7µ

4.7µ

2700P

3.3k

0.047µ

3k

3.3µ

TANTALUM

1µ

3.9k

10µ

4.7µ

TANTALUM

4.7µ

+9V

LS OUTPUT

µ-

c

o

m

Composite

baseband

signal input

AUX INPUT

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility fo

r

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same

.

≠ 24 ≠

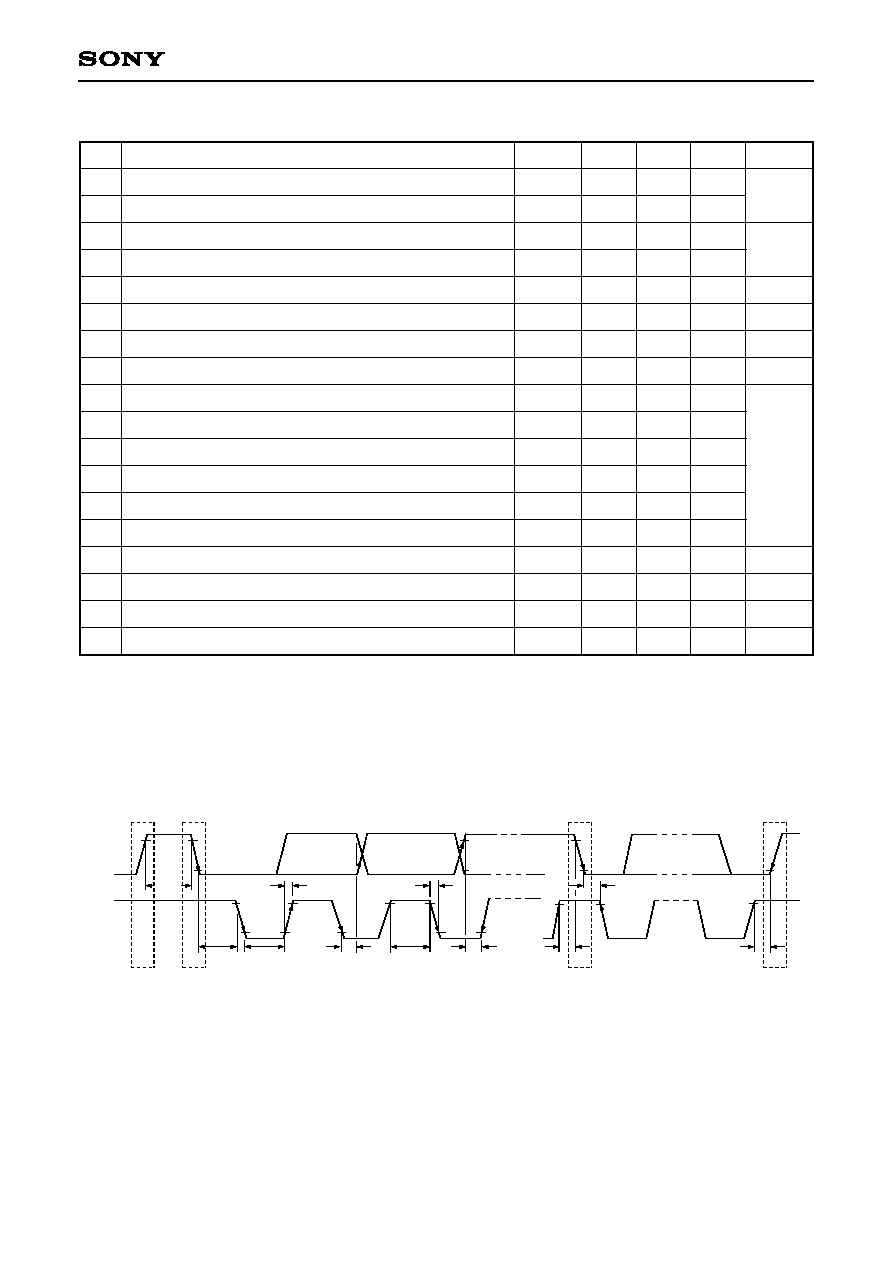

CXA2174S

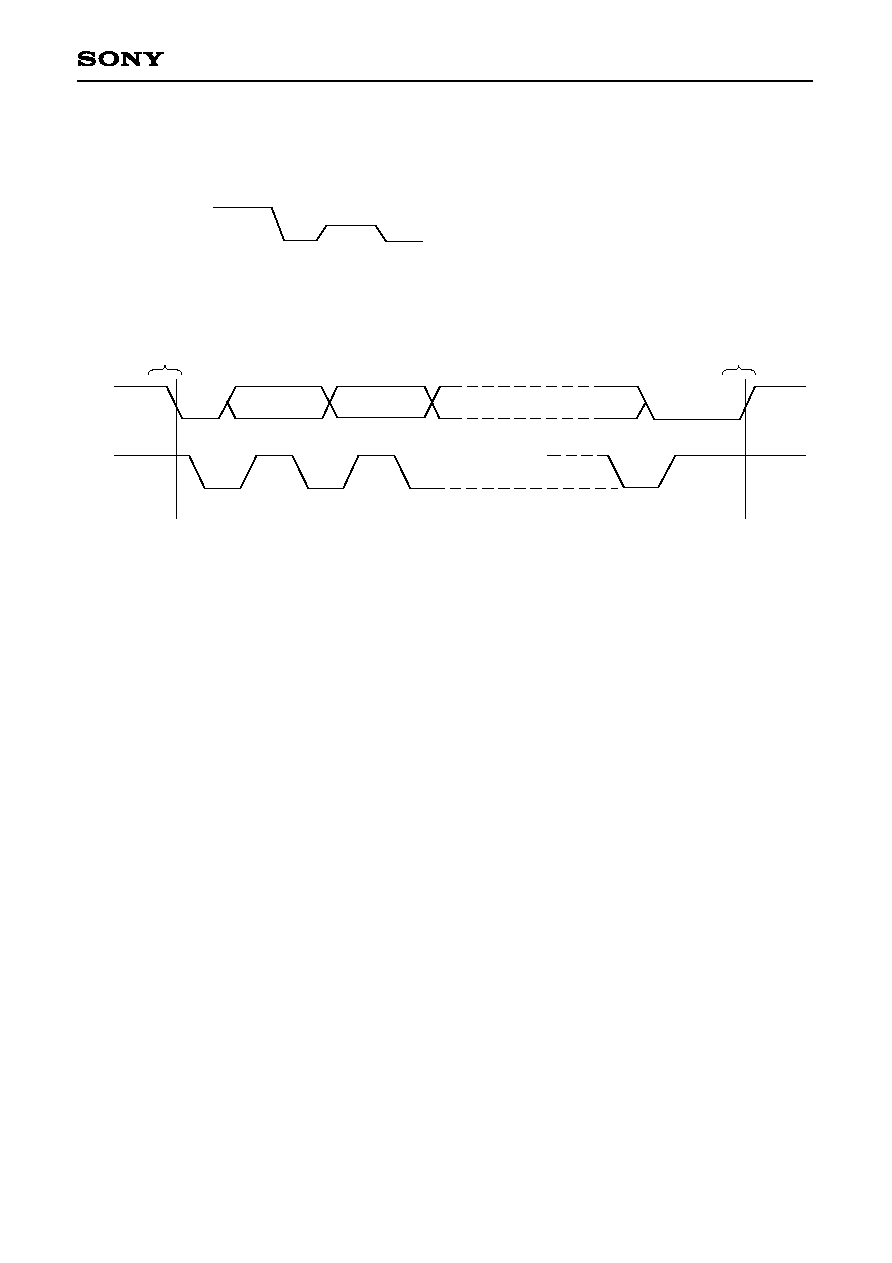

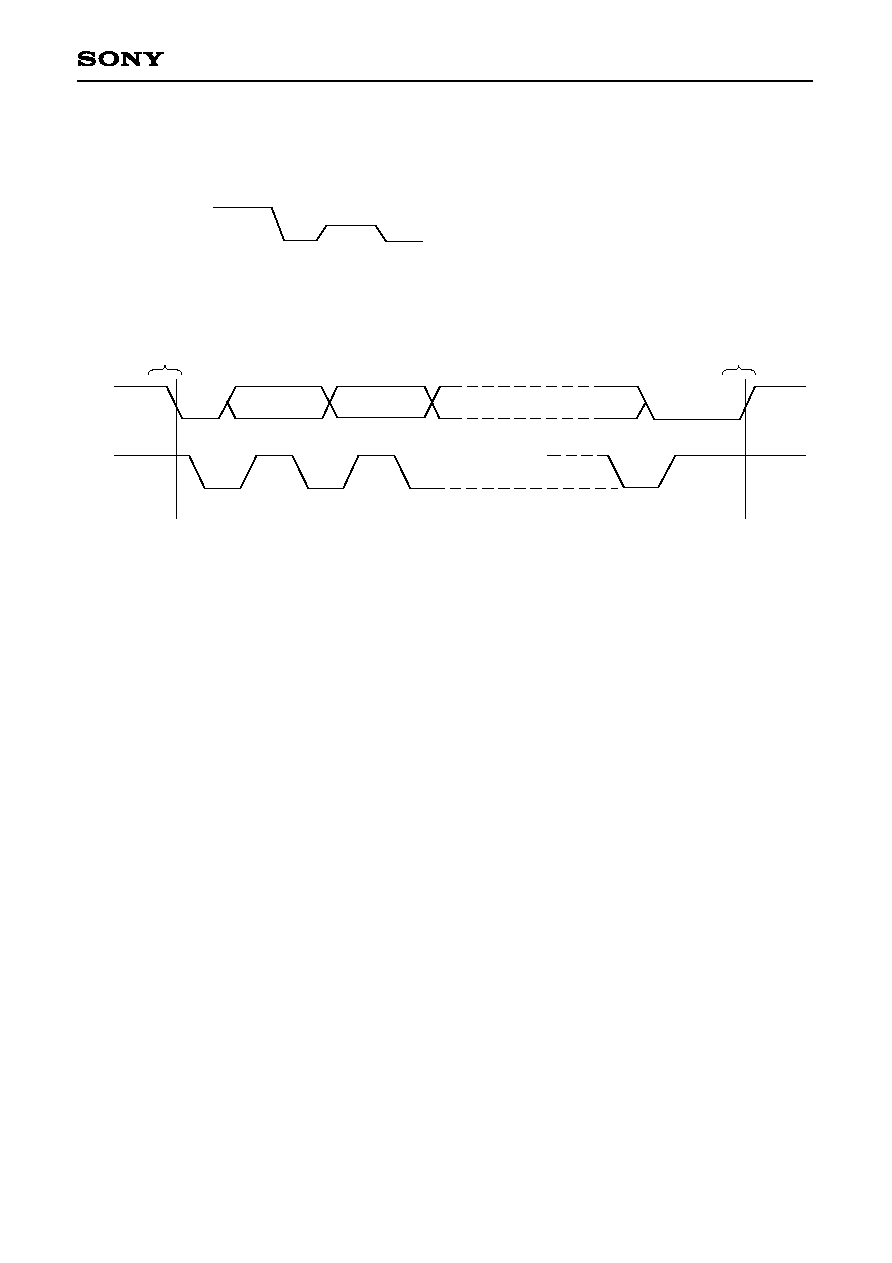

I

2

C BUS block items (SDA, SCL)

I

2

C BUS load conditions: Pull-up resistor 4k

(Connect to +5V)

Load capacity 200pF (Connect to GND)

I

2

C BUS Control Signal

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

High level input voltage

Low level input voltage

High level input current

Low level input current

Low level output voltage SDA (Pin 3) during 3mA inflow

Maximum inflow current

Input capacitance

Maximum clock frequency

Minimum waiting time for data change

Minimum waiting time for start of data transfer

Low level clock pulse width

High level clock pulse width

Minimum waiting time for start preparation

Minimum data hold time

Minimum data preparation time

Rise time

Fall time

Minimum waiting time for stop preparation

V

IH

V

IL

I

IH

I

IL

V

OL

I

OL

C

I

f

SCL

t

BUF

t

HD

: STA

t

LOW

t

HIGH

t

SU

: STA

t

HD

: DAT

t

SU

: DAT

t

R

t

F

t

SU

: STO

3.0

0

--

--

0

3

--

0

4.7

4.0

4.7

4.0

4.7

0

250

--

--

4.7

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

5.0

1.5

10

10

0.4

--

10

100

--

--

--

--

--

--

--

1

300

--

V

µA

V

mA

pF

kHz

µs

ns

µs

ns

µs

SDA

SCL

t

BUF

P

S t

HD

: STA

t

LOW

t

HD

: DAT

t

HIGH

t

R

t

F

t

HD

: STA

t

SU

: STA

Sr

t

SU

: STO

P

t

SU

: DAT

No.

Item

Symbol

Min.

Typ.

Max.

Unit

≠ 25 ≠

CXA2174S

I

2

C BUS Signal

There are two I

2

C signals, SDA (Serial DATA) and SCL (Serial CLOCK) signals. SDA is a bidirectional signal.

∑ Accordingly there are 3 values outputs, H, L and Hi-Z.

∑ I

2

C transfer begins with Start Condition and ends with Stop Condition.

SDA

SCL

Start Condition S

Stop Condition P

H

L

Hi-Z

L

≠ 26 ≠

CXA2174S

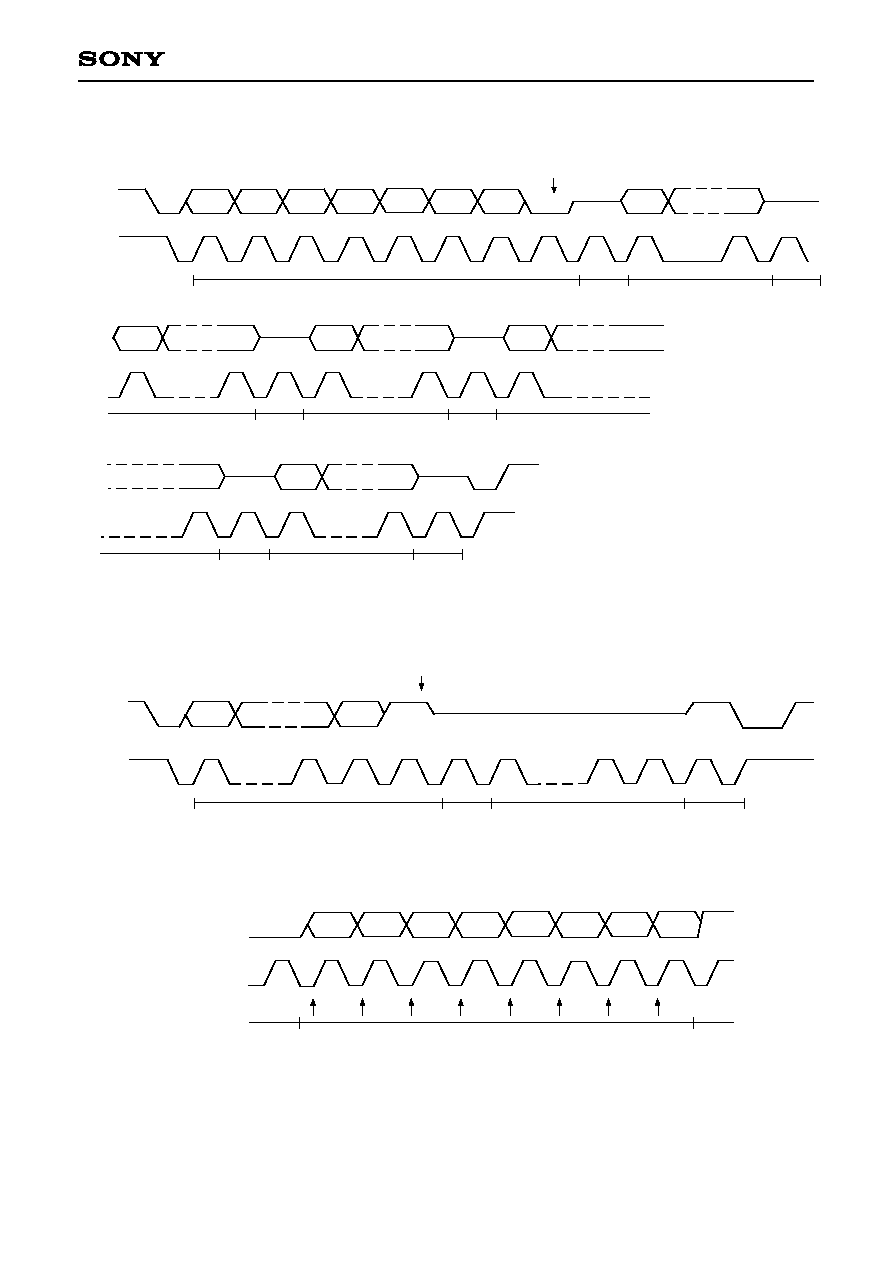

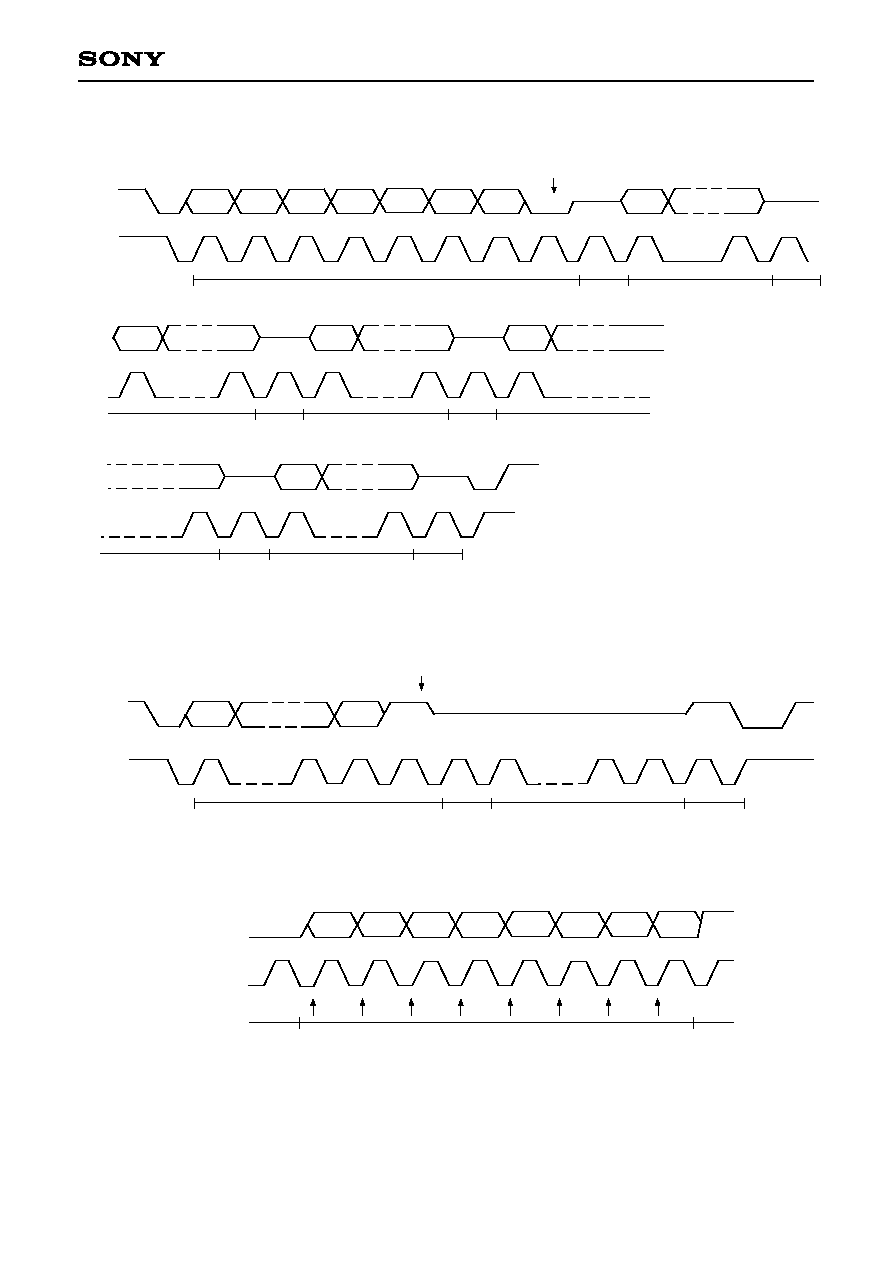

∑ I

2

C data Write (Write from I

2

C controller to the IC)

Data can be transferred in 8-bit units to be

set as required.

Sub address is incremented automatically.

∑ I

2

C data Read (Read from the IC to I

2

C controller)

∑ Read timing

Data Read is performed during SCL rise.

S

Address

1

6

7

8

9

1

8

9

SCL

ACK

DATA

ACK

SDA

H during Read

Hi-Z

7

P

DATA

1

2

3

4

5

6

7

8

9

9

IC output SDA

SCL

MSB

LSB

ACK

ACK

Read timing

ACK

ACK

DATA

DATA

P

8

9

1

8

9

Hi-Z

Hi-Z

DATA (n)

DATA (n+1)

ACK

1

8

9

1

8

9

ACK

DATA (n + 2)

Hi-Z

Hi-Z

LSB

MSB

S

Address

1

2

3

4

5

6

7

8

9

1

8

9

SDA

SCL

MSB

L during Write

MSB

LSB

Hi-Z

Hi-Z

ACK

Sub Address

ACK

≠ 27 ≠

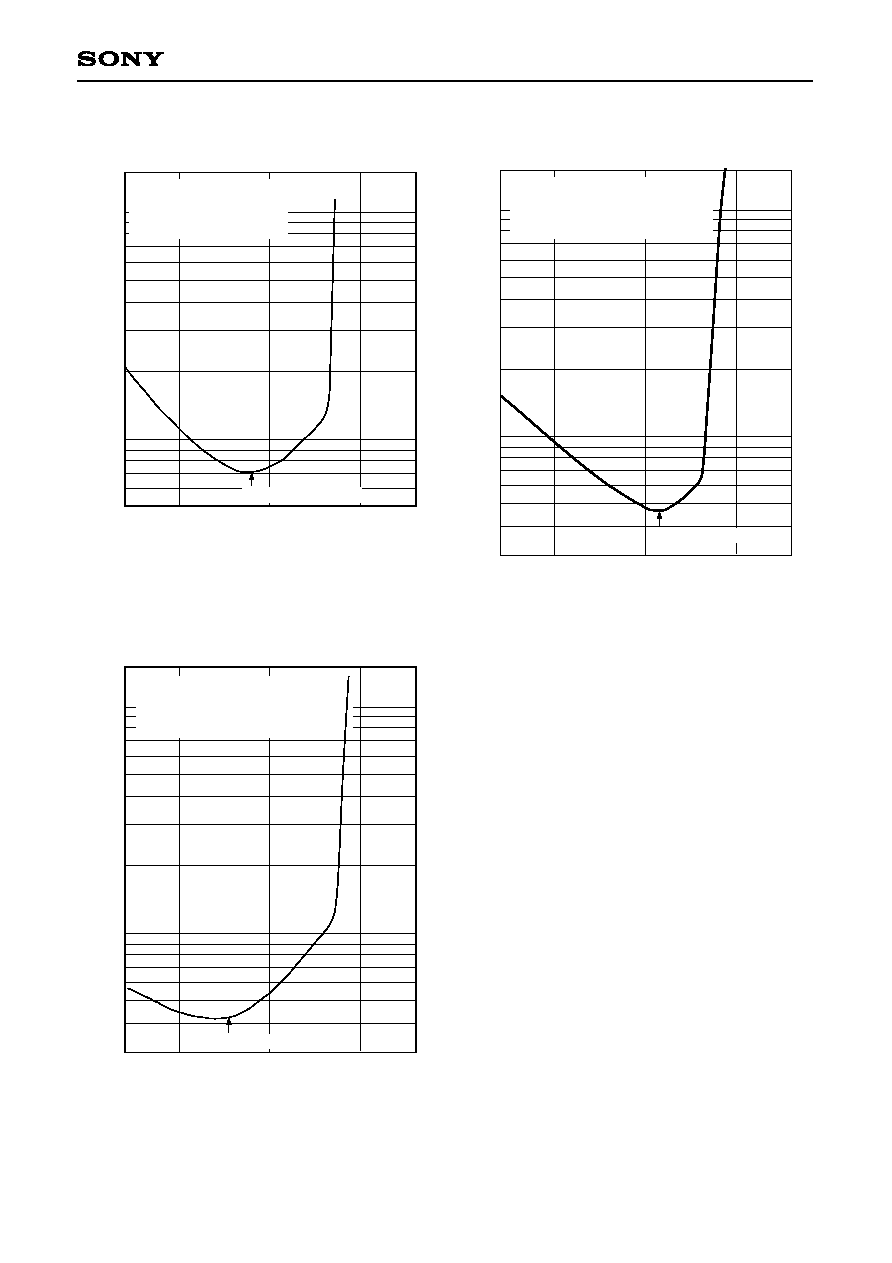

CXA2174S

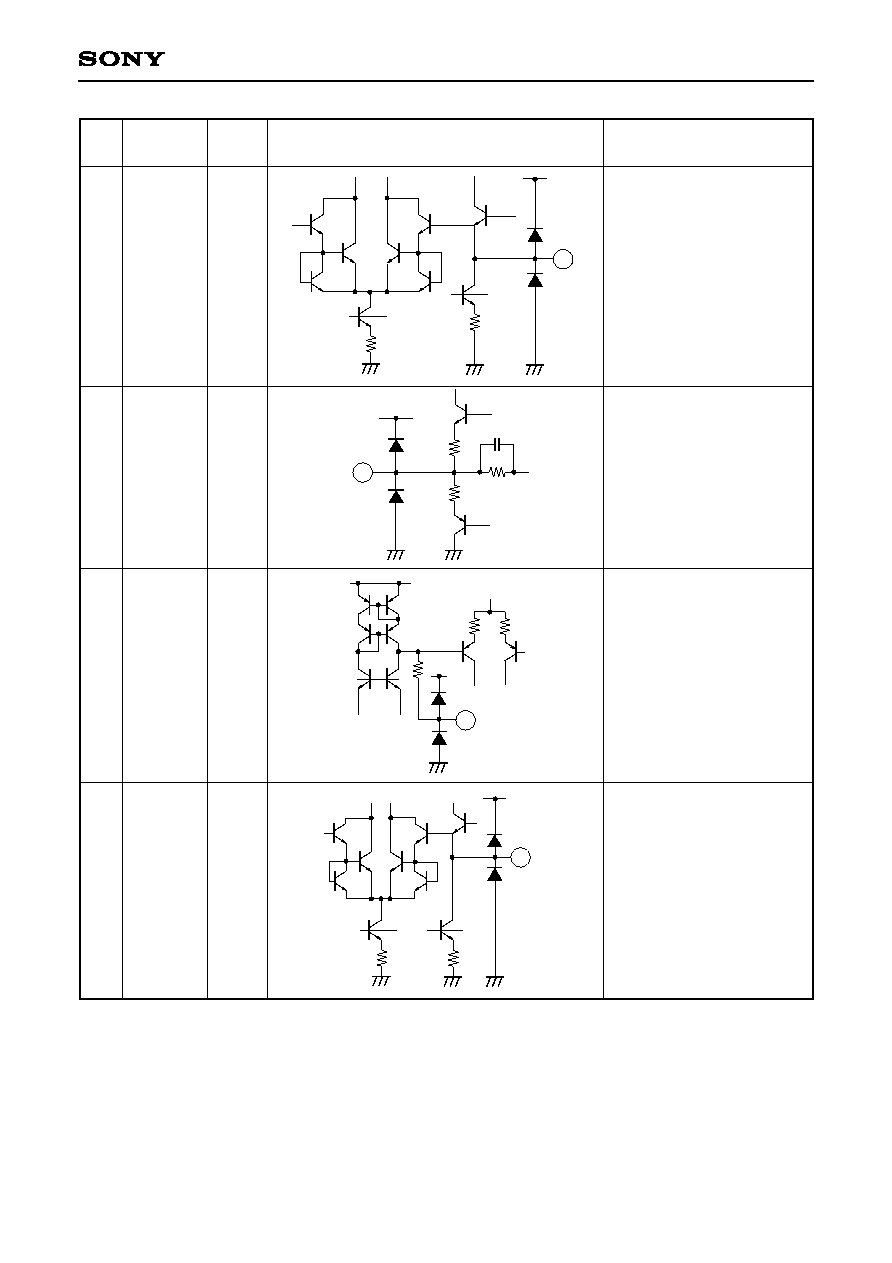

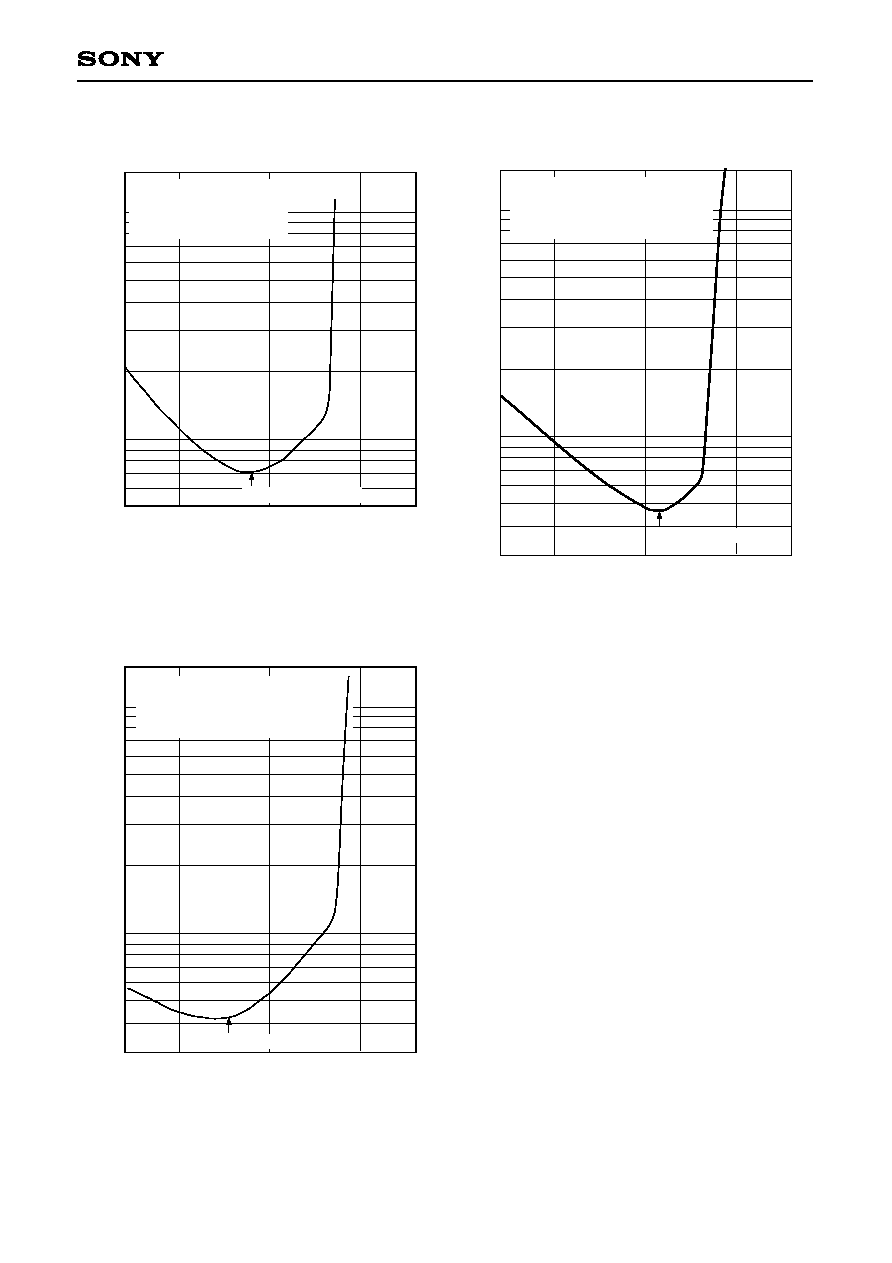

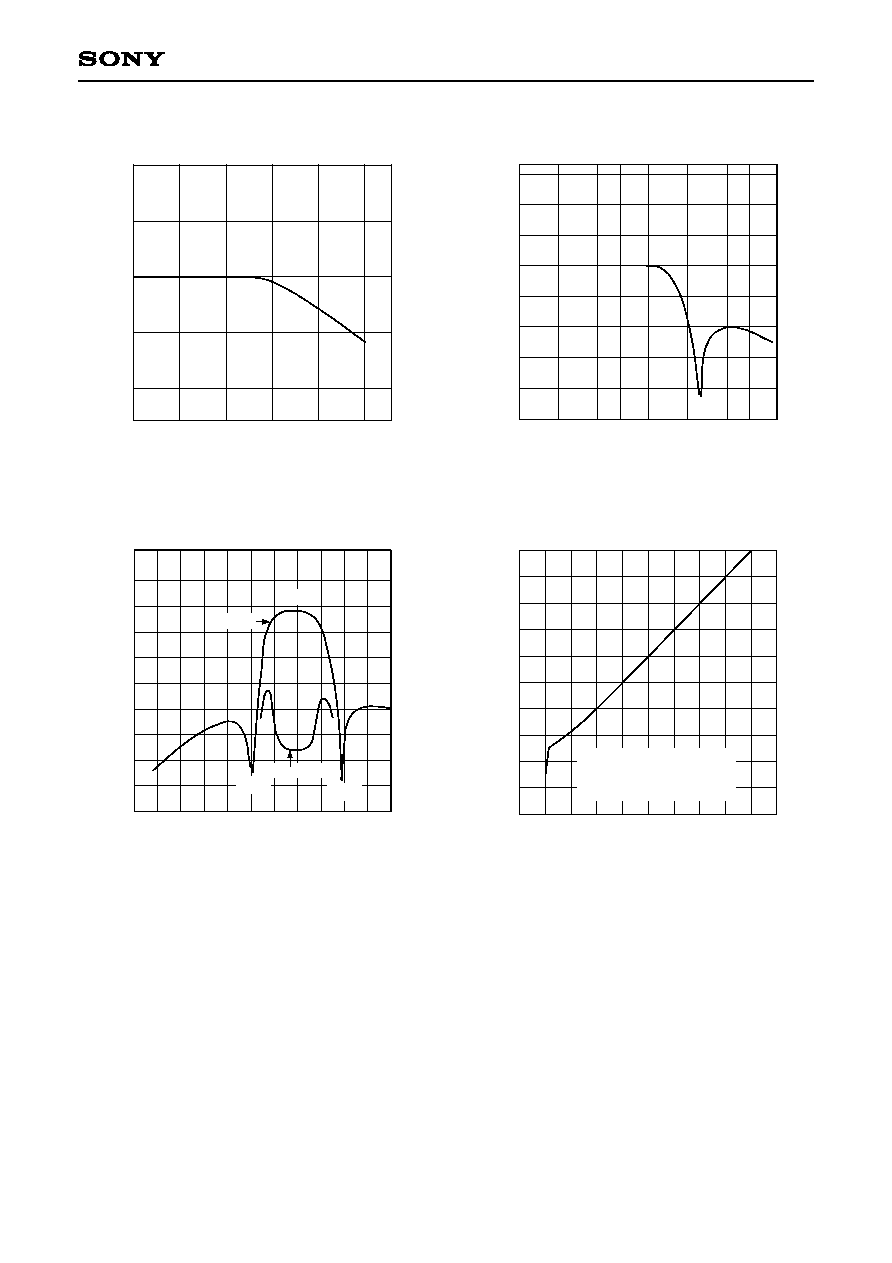

Input level vs. Distortion characteristics 1 (MONO)

Distortion [%]

1.0

0.1

≠10

0

10

Input level vs. Distortion characteristics 2 (Stereo)

Distortion [%]

10

1.0

≠10

0

10

Input level [dB]

Input signal: Stereo L = ≠R

(dbx-TVNR ON), 1kHz

0dB = 100% modulation level

V

CC

= 9V, 30kHz using LPF, ST mode

Measurement point: LSOUT-L/R

Input level vs. Distortion characteristics 3 (SAP)

Distortion [%]

10

1.0

≠10

0

10

Input level [dB]

Input level [dB]

Standard level (100%)

Standard level (100%)

Input signal: SAP (dbx-TVNR ON)

1kHz, 0dB = 100% modulation

level

V

CC

= 9V, 30kHz using LPF, SAP mode

Measurement point: LSOUT-L/R

Standard level (100%)

Input signal: MONO (Pre-emphasis on), 1kHz

0dB = 100% modulation level

V

CC

= 9V, 30kHz using LPF

Measurement point: LSOUT-L/R

≠ 28 ≠

CXA2174S

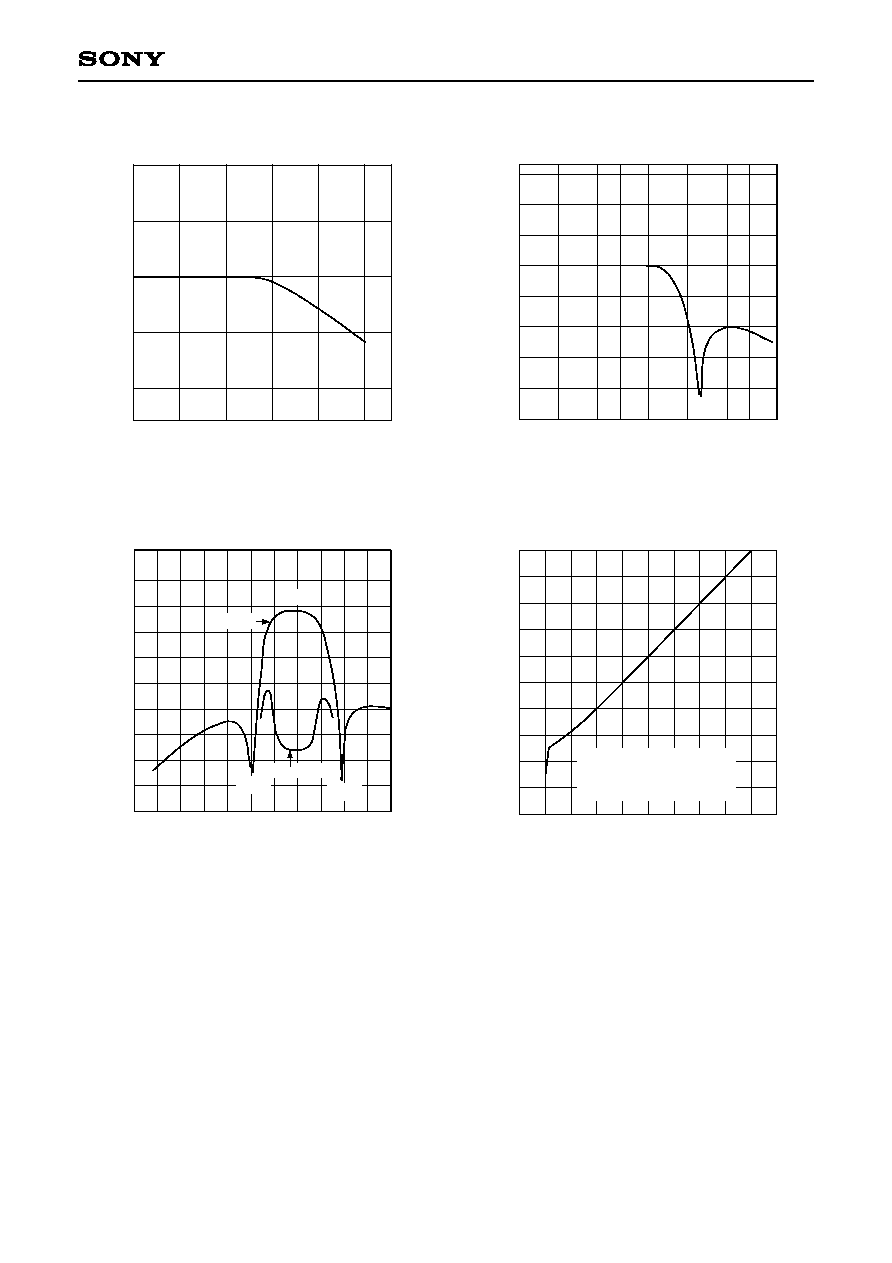

Frequency [kHz]

Gain [dB]

Stereo LPF frequency characteristics

10

5

0

≠5

≠10

0

20

40

60

80

100

30

10

0

≠20

≠50

1

2

5

10

20

50

7

70 100

≠40

≠30

≠10

20

Gain (FC main and FC sub) [dB]

Frequency [kHz]

Main LPF and Sub LPF frequency characteristics

10

0

≠20

20

40

60

80

100

120

≠10

20

SAP frequency characteristics and group delay

Group delay [µ

s]

100

90

80

70

60

50

40

10

20

0

30

5f

H

Gain

Group delay

3.8f

H

6.2f

H

Frequency [kHz]

Gain [dB]

0

F

1F

Control data VOL-L, VOL-R

2F

3F

0

≠20

≠40

≠60

≠80

≠100

LSOUT output level [dB]

Volume charactiristics

Input:

AUXIN (Pins 29, 30)

1kHz, 490mVrms

Output: LSOUT (Pins 1, 2)

≠ 29 ≠

CXA2174S

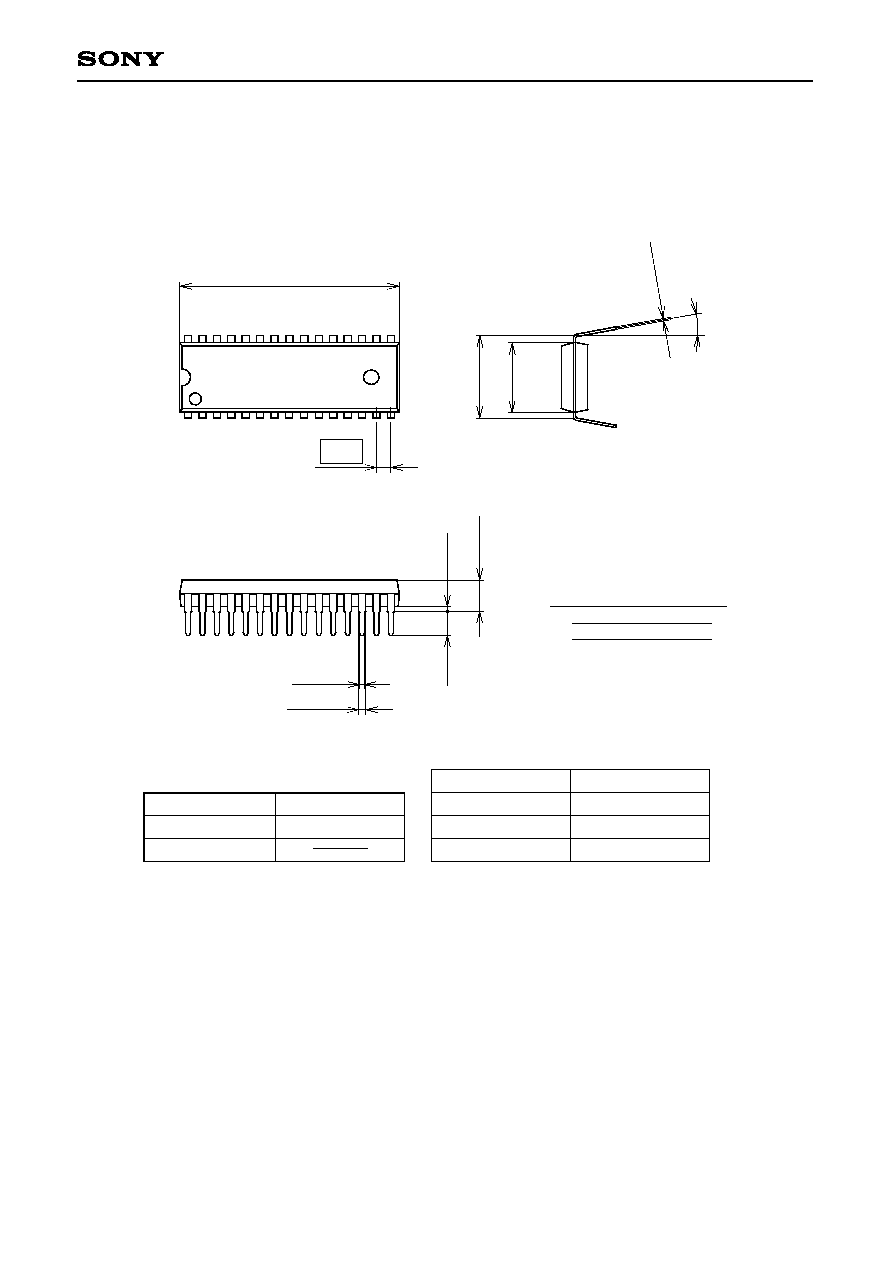

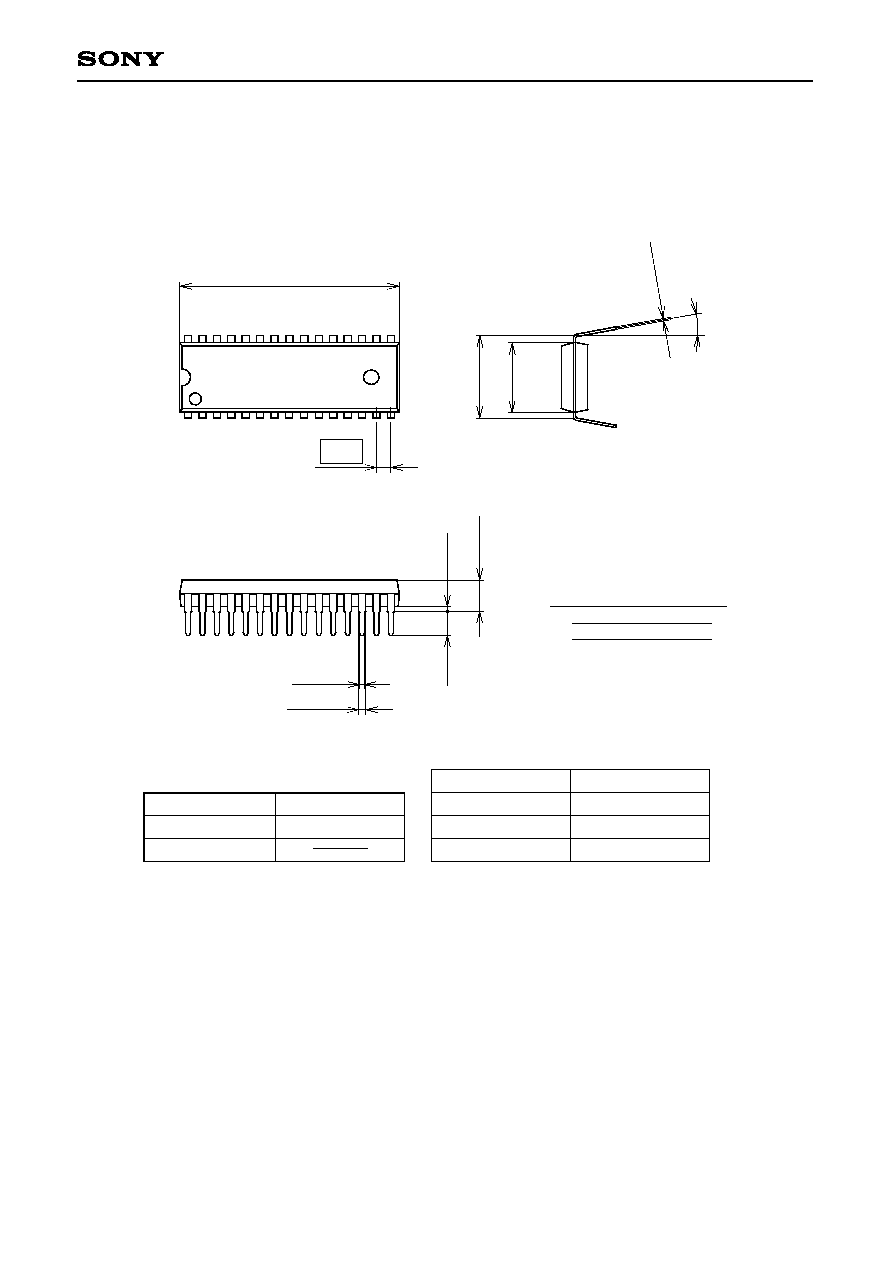

Package Outline

Unit: mm

SONY CODE

EIAJ CODE

JEDEC CODE

30PIN SDIP (PLASTIC)

26.9 ≠ 0.1

+ 0.4

15

16

30

1.778

10.16

8.5 ≠ 0.1

+ 0.3

0.25 ≠ 0.05

+ 0.1

0∞ to 15∞

0.5

±

0.1

0.9

±

0.15

3.0 MIN

0.5 MIN

3.7 ≠ 0.1

+ 0.4

SDIP-30P-01

P-SDIP30-8.5x26.9-1.778

1

PACKAGE STRUCTURE

MOLDING COMPOUND

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

COPPER ALLOY

1.8g

PALLADIUM PLATING

1.All mat surface type.

Two kinds of package surface:

2.All mirror surface type.

Sony Corporation