| –≠–Ľ–Ķ–ļ—ā—Ä–ĺ–Ĺ–Ĺ—č–Ļ –ļ–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā: CXA2581N | –°–ļ–į—á–į—ā—Ć:  PDF PDF  ZIP ZIP |

RF Signal Processor for CD Players

Description

The CXA2581N is an RF signal processing IC for

compact disc players.

Features

∑ Wide band RF signal processing

∑ RF system VCA circuit

∑ RF system equalizer (supports CAV mode)

∑ Supports pickups with built-in RF summing

amplifier

∑ Low current consumption mode (EQ Pass mode)

∑ RW/ROM switching mode

∑ Center error amplifier

∑ Output DC level shift circuit

∑ TE balance adjustment function

Functions

∑ RF AC summing amplifier, equalizer, VCA

∑ RF DC summing amplifier

∑ Focus error amplifier

∑ Tracking error amplifier

∑ Center error amplifier

∑ Automatic power control

∑ VC buffer amplifier (analog block, digital block)

Absolute Maximum Ratings

∑ Supply voltage

V

CC

7

V

∑ Storage temperature

Tstg ≠65 to +150

įC

∑ Allowable power dissipation

P

D

620

mW

Operating Conditions

∑ Operating supply voltage range

V

CC

≠ GND

3.4 to 5.5

V

(0V

Vcc ≠ DVcc < 2V)

Note) Care should be taken for the operating voltage.

See page 18.

∑ Operating temperature

Topr

≠30 to +85

įC

≠ 1 ≠

E98739A97-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXA2581N

30 pin SSOP (Plastic)

Pin Configuration

1

2

3

4

5

6

7

9

12

11

20

19

22

24

25

26

27

28

29

30

8

10

14

13

18

17

21

23

15

16

LD

PD

EQ_IN

AC_SUM

GND

A

B

D

SW

F

C

E

DVC

DV

CC

RFAC

DC_OFST

RFDCI

RFDCO

VC

RFC

VFC

BST

V

CC

TE_BAL

CE

RFG

CEI

FEI

TE

FE

≠ 2 ≠

CXA2581N

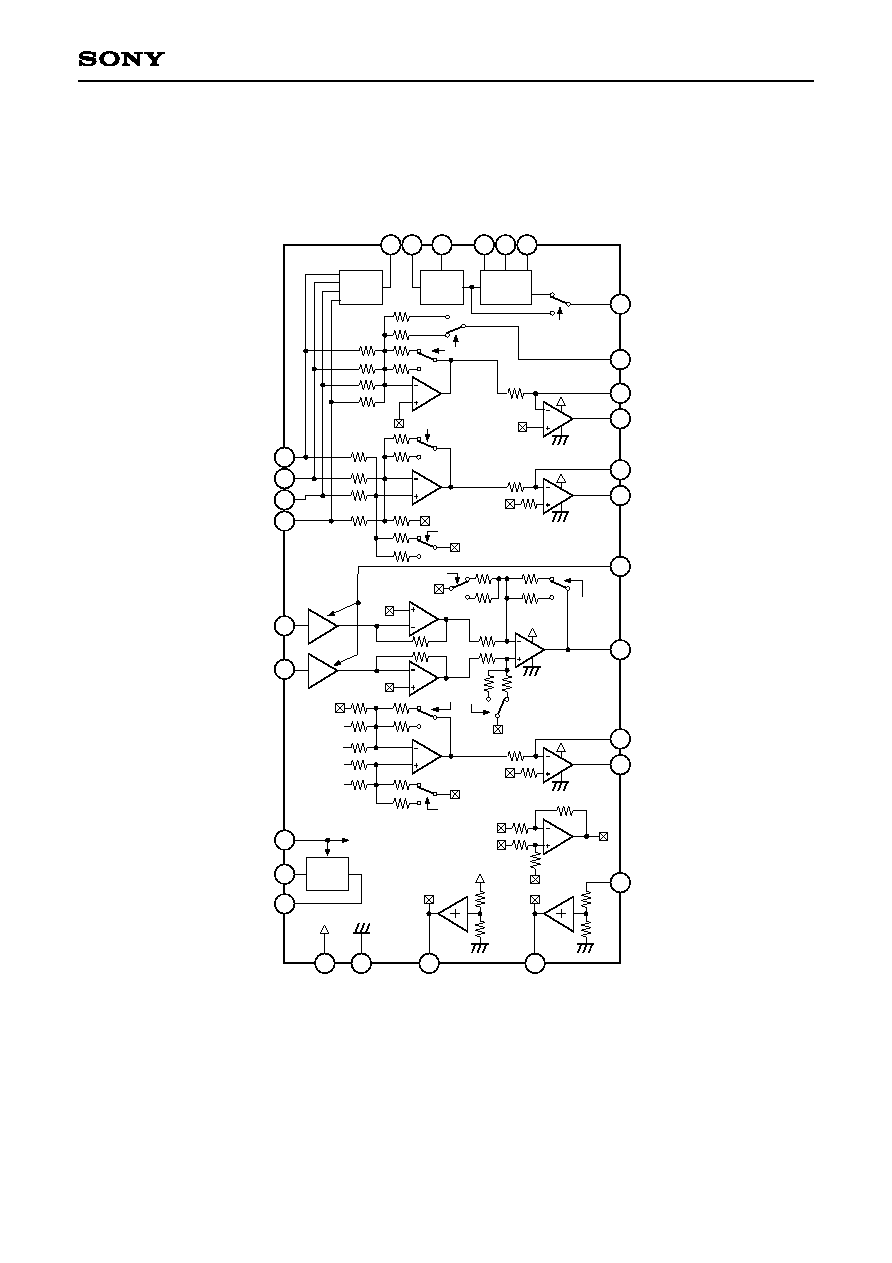

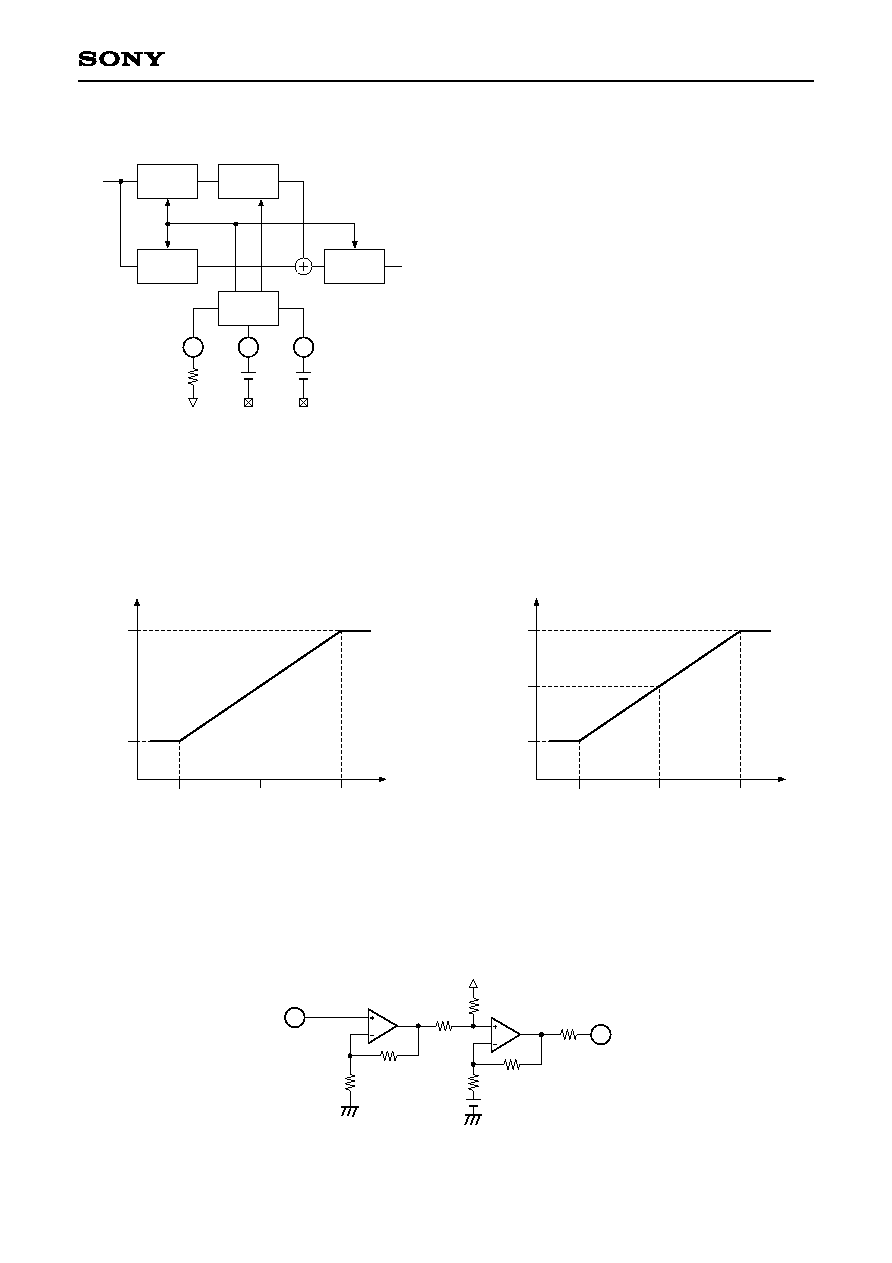

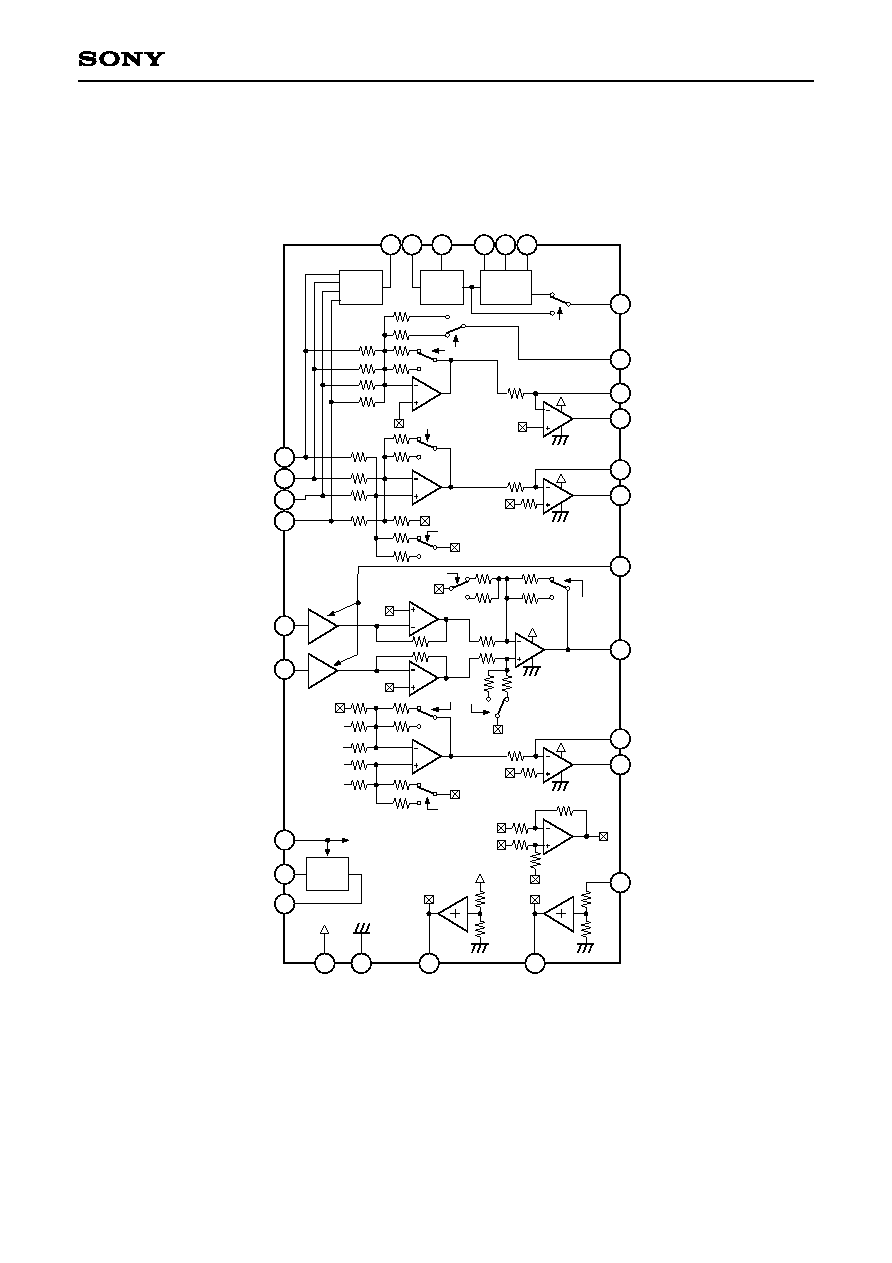

Block Diagram

DV

CC

AC

SUM

APC

AC

VCA

EQ

VC

VC

VC

RW/ROM

EQ_ON/OFF

VOFST

DVC

DV

CC

RW/ROM

VC

RW/ROM

RW/ROM

RW/ROM

DVC

DV

CC

25

15

30

29

28

17

16

26

24

23

3

4

6

7

8

9

10

19

18

DVC

DV

CC

DVC

VC

VC

VOFST

DVC

DVC

V

CC

VOFST

B

C

A

D

A

B

C

D

F

E

SW

PD

LD

V

C

C

G

N

D

V

C

D

V

C

DV

CC

CE

CEI

TE

TE_BAL

FE

FEI

RFDCO

RFDCI

RFAC

V

F

C

R

F

C

R

F

G

B

S

T

E

Q

_

I

N

A

C

_

S

U

M

DC_OFST

VC

RW/ROM

21

14

5

20

13

VC

V

CC

APC-OFF (Hi-Z)

RW/ROM

(H/L)

27

22

1

2

12

11

gm

gm

RW/ROM

VOFST

≠ 3 ≠

CXA2581N

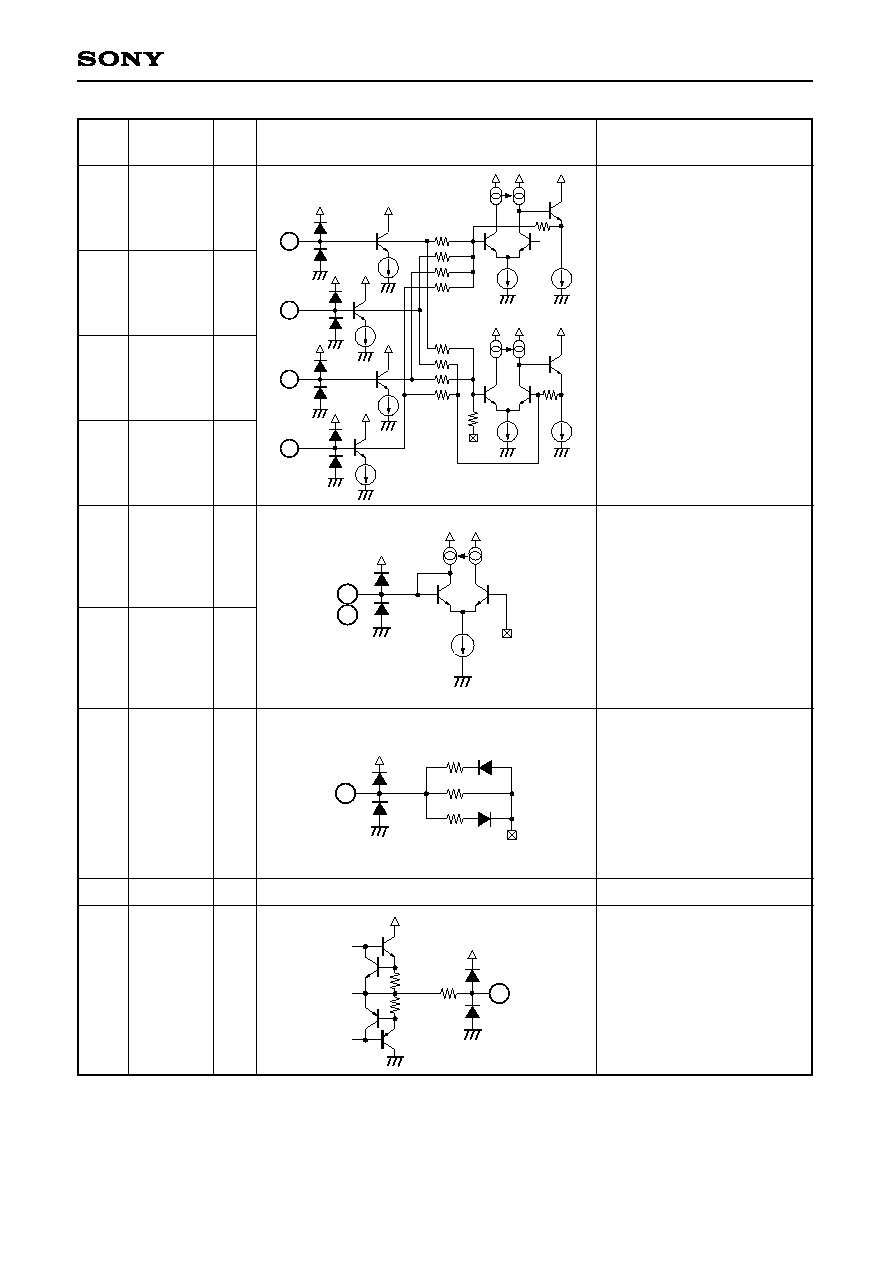

Pin Description

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

LD

PD

EQ_IN

AC_SUM

GND

A

B

C

D

E

F

SW

DV

CC

DVC

RFAC

FE

FEI

TE

TE_BAL

CE

CEI

V

CC

RFG

BST

VFC

RFC

VC

RFDCO

RFDCI

DC_OFST

APC amplifier output.

APC amplifier input.

RFAC system VCA block and EQ block input.

RFAC system RF SUM output.

GND.

A signal input.

B signal input.

C signal input.

D signal input.

E signal input.

F signal input.

Mode switching signal input.

DV

CC

.

DVC output.

RFAC signal output.

Focus error signal output.

FE amplifier virtual ground.

Tracking error signal output.

TE balance adjustment.

Center error signal output.

CE amplifier virtual ground.

V

CC

.

RFAC system VCA block low frequency gain adjustment.

EQ boost level adjustment.

EQ cut-off frequency adjustment.

EQ cut-off frequency adjustment.

VC voltage output.

RFDC signal output.

RFDC amplifier virtual ground.

RFDC signal output offset adjustment.

O

I

I

O

I

I

I

I

I

I

I

I

I

O

O

O

I

O

I

O

I

I

I

I

I

I

O

O

I

I

Symbol

I/O

Description

≠ 4 ≠

CXA2581N

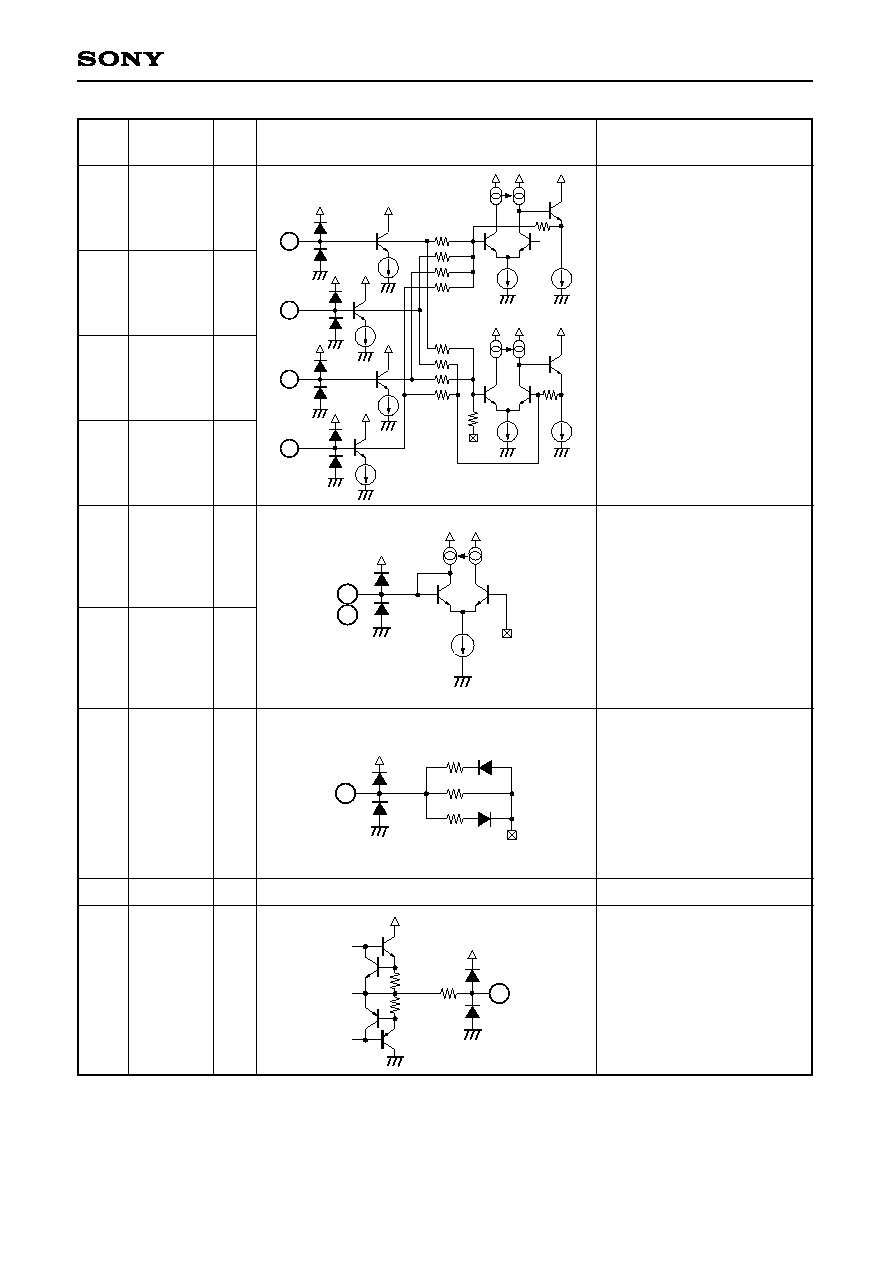

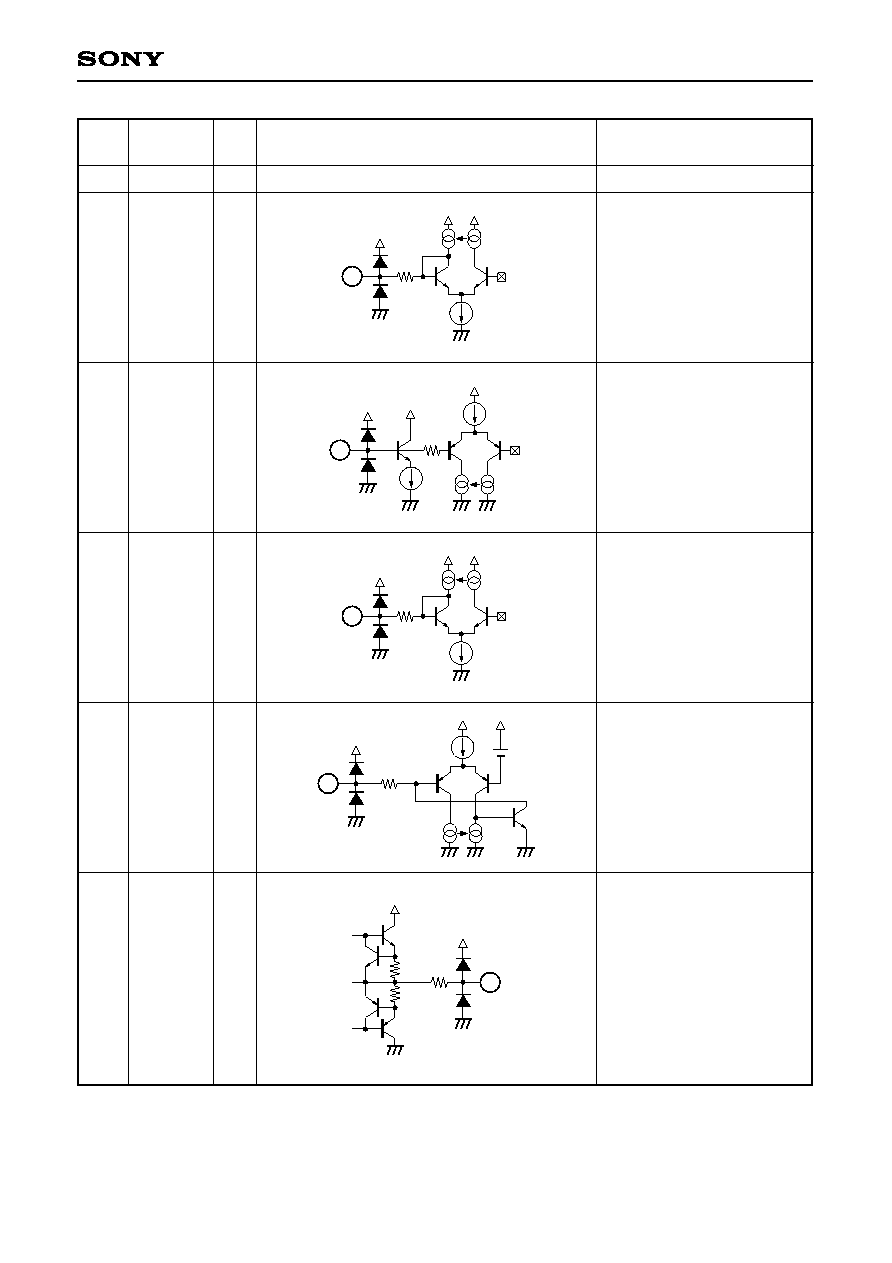

Pin Description

Pin

No.

Symbol

I/O

Equivalent circuit

Description

1

10k

1k

2

55k

20k

20k

3

1.2k

1.1k

VC

1.1k

5k

5k

VC

1.6k

1.6k

4

1

2

3

4

O

I

I

O

LD

PD

EQ_IN

AC_SUM

5

GND

APC amplifier output.

APC amplifier input.

Equalizer circuit input.

RFAC summing amplifier

output.

--

--

GND.

≠ 5 ≠

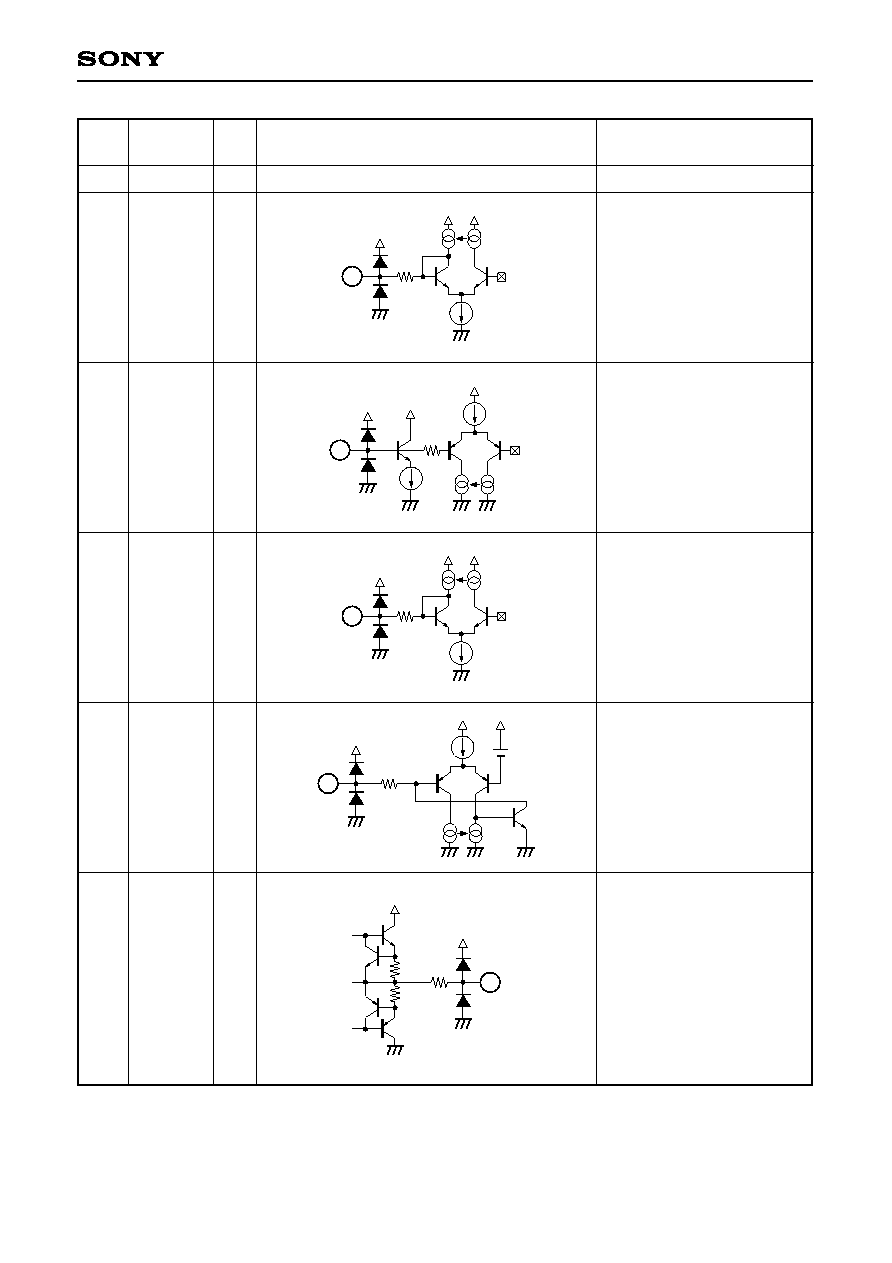

CXA2581N

Pin

No.

Symbol

I/O

Equivalent circuit

Description

47k

VC

47k

15k

30k

100

Ķ

A

100

Ķ

A

100

Ķ

A

6

100

Ķ

A

7

8

9

10

11

VC

200k

200k

200k

12

VC

14

150k

150k

25

6

I

A

7

I

B

8

I

C

9

I

D

RF summing amplifier and

focus error amplifier input.

10

I

E

Tracking error amplifier input.

11

I

F

12

I

SW

CD-ROM/RW switching input.

RW when connected to V

CC

,

ROM when connected to GND.

14

O

DVC

(DV

CC

+ GND)/2 voltage

output.

13

--

--

DV

CC

Digital power supply.

≠ 6 ≠

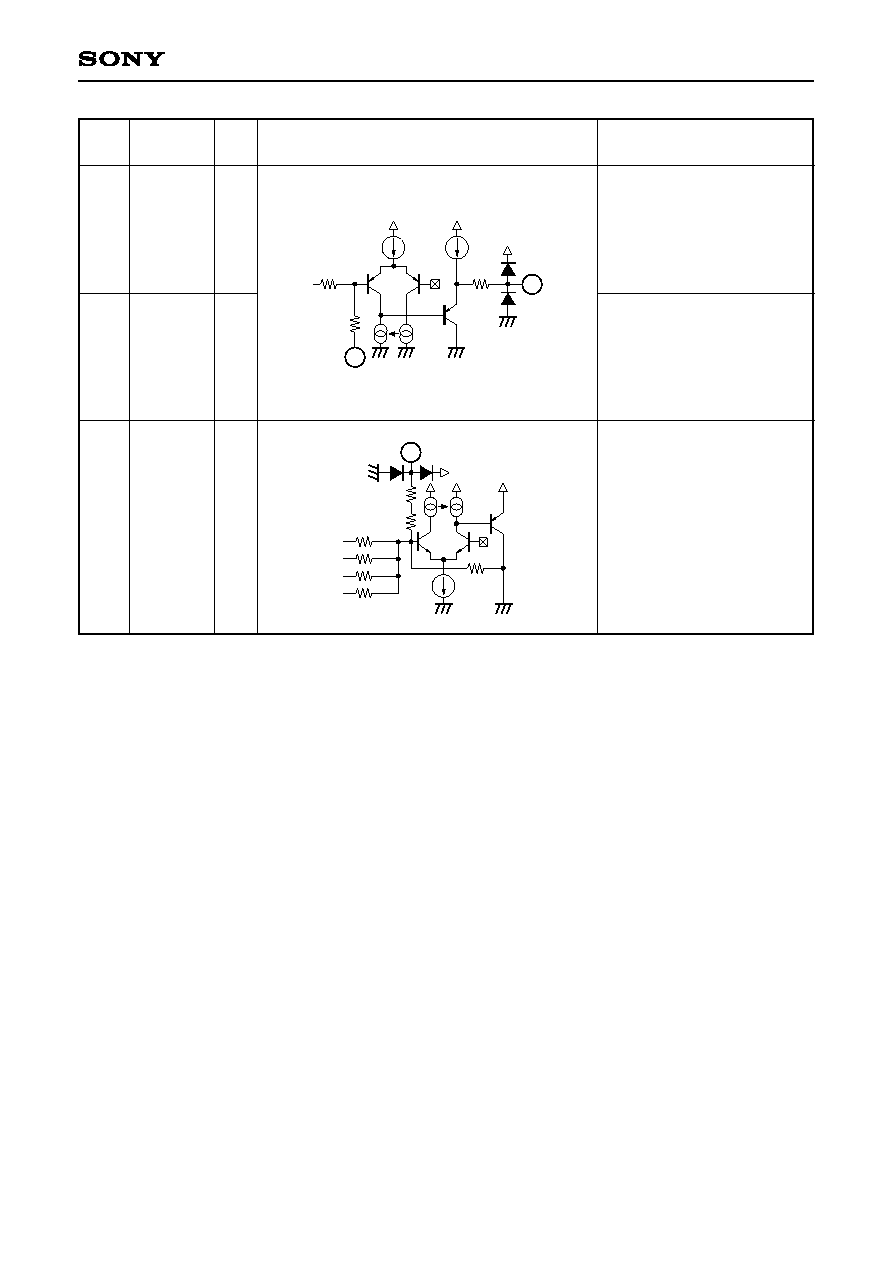

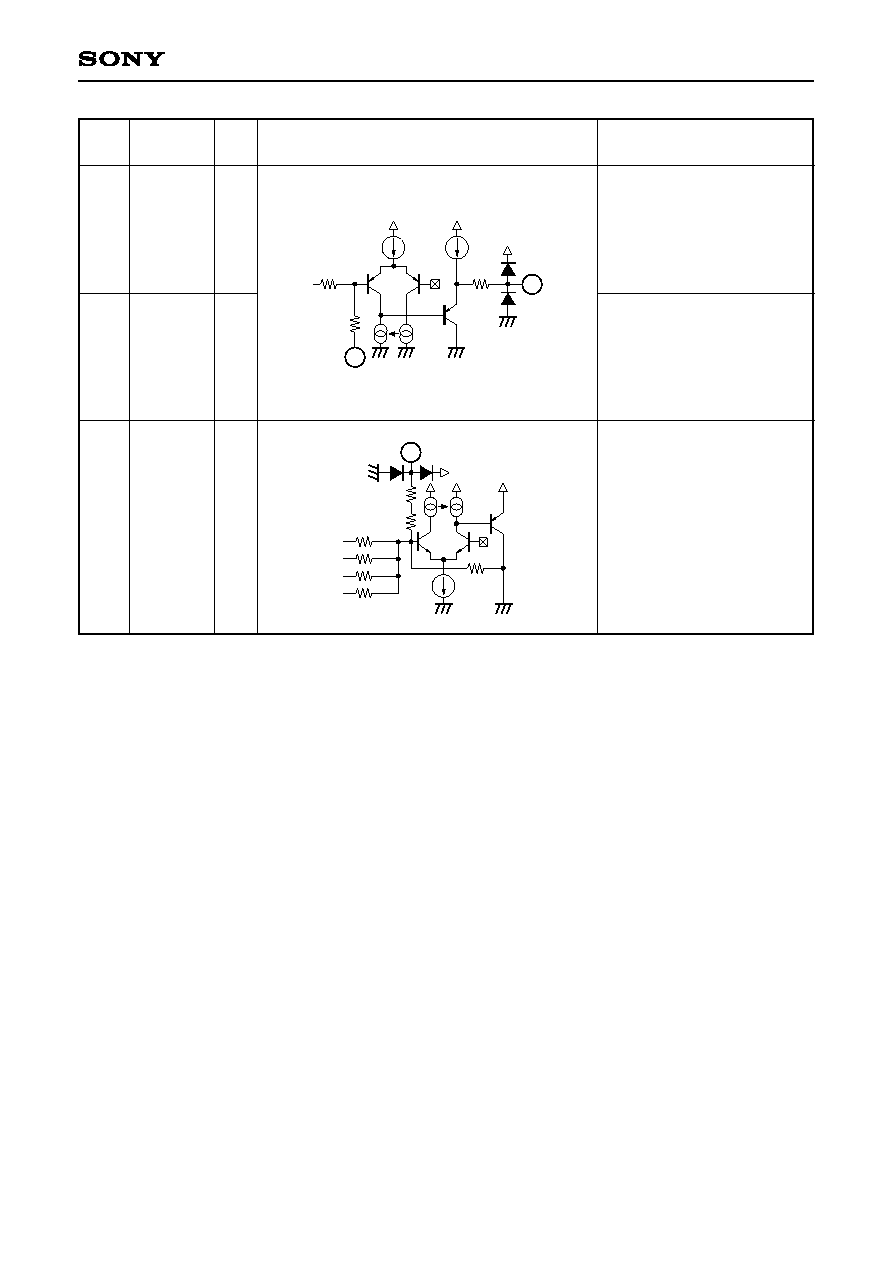

CXA2581N

Pin

No.

Symbol

I/O

Equivalent circuit

Description

15

100

2mA

15

O

RFAC

RFAC amplifier output.

17

I

FEI

Focus error amplifier gain

adjustment. The gain is

adjusted by the external

resistance value connected

between this pin and Pin 16.

50k

124

VC

16

124

17

16

O

FE

Focus error amplifier output.

19

I

TE_BAL

Tracking error E and F gain

balance adjustment.

20k

18

19

20k

20k

VC

18

O

TE

Tracking error amplifier output.

21

I

CEI

Center error amplifier gain

adjustment.

The gain is adjusted by the

external resistance value

connected between this pin

and Pin 20.

50k

124

VC

20

124

21

20

O

CE

Center error amplifier output.

≠ 7 ≠

CXA2581N

22

--

--

V

CC

V

CC

. (AV

CC

)

Pin

No.

Symbol

I/O

Equivalent circuit

Description

20k

VC

23

100

Ķ

A

50

Ķ

A

20k

VC

24

20k

VC

25

100

Ķ

A

124

1.0V

26

27

150k

150k 25

23

I

RFG

Sets the RFAC low frequency

gain.

24

I

BST

Input for adjusting the

equalizer circuit boost level.

25

I

VFC

Input for adjusting the

equalizer circuit boost

frequency with the control

voltage.

26

I

RFC

Input for adjusting the

equalizer circuit boost

frequency with external

resistance.

27

O

VC

(V

CC

+ GND)/2 voltage

output.

≠ 8 ≠

CXA2581N

Pin

No.

Symbol

I/O

Equivalent circuit

Description

VC

2k

124

1mA

28

29

124

VC

10k

124

24k

15k

30

28

O

RFDC

RFDC amplifier output.

29

I

RFDCI

RFDC amplifier gain

adjustment.

The gain is adjusted by the

external resistance value

connected between this pin

and Pin 28.

30

I

DC_OFST

RFDC amplifier offset control.

≠ 9 ≠

CXA2581N

Description of Functions

∑ RFAC

The RF signal input by connecting capacitance to the EQ_IN pin is equalized, arithmetically amplified and then

output from the RFAC pin.

AC

SUM

EQ

RW/ROM

BST = V

CC

6

7

8

9

A

B

C

D

RFG

EQ_IN

AC_SUM

RF

26

25

24

VFC

RFC

5.1k

BST

V

CC

4

3

23

15 RFAC

Amp

0.1

Ķ

The EQ can be bypassed by connecting the BST control pin (Pin 24) to V

CC

.

In this case only the EQ block enters sleep mode and low power consumption mode (slim mode) is activated.

The low frequency gain is the same value as for EQ ON mode.

If RF (summing signal) is present at the pickup output pin, input the addition output signal to EQ_IN (Pin 3)

coupled by capacitance.

When using a pickup without a summing output function, perform addition with the AC SUM block and then

input the signal to EQ_IN (Pin 3) coupled by capacitance.

RW/ROM switching is done by the VCA block, so either input method can be used without problem.

The RW gain is 12dB higher than the ROM gain.

Low frequency gain

AC_SUM:

13dB (both ROM/RW)

VCA to RFAC ROM: 0dB

RW: 12dB

VC ≠ 1

VC

VC + 1

Vcnt

[V]

8

0

≠8

Gain [dB]

VCA variable range

The VCA low frequency gain can be adjusted by the RFG

(Pin 23) voltage.

The control voltage vs. low frequency gain characteristics

are shown in the graph to the right.

The RFAC pin (Pin 15) is an NPN transistor emitter follower output.

The maximum drive current is approximately 2mA.

If the load capacitance distorts the output waveform, connect resistance between Pin 15 and GND to increase

the drive current.

≠ 10 ≠

CXA2581N

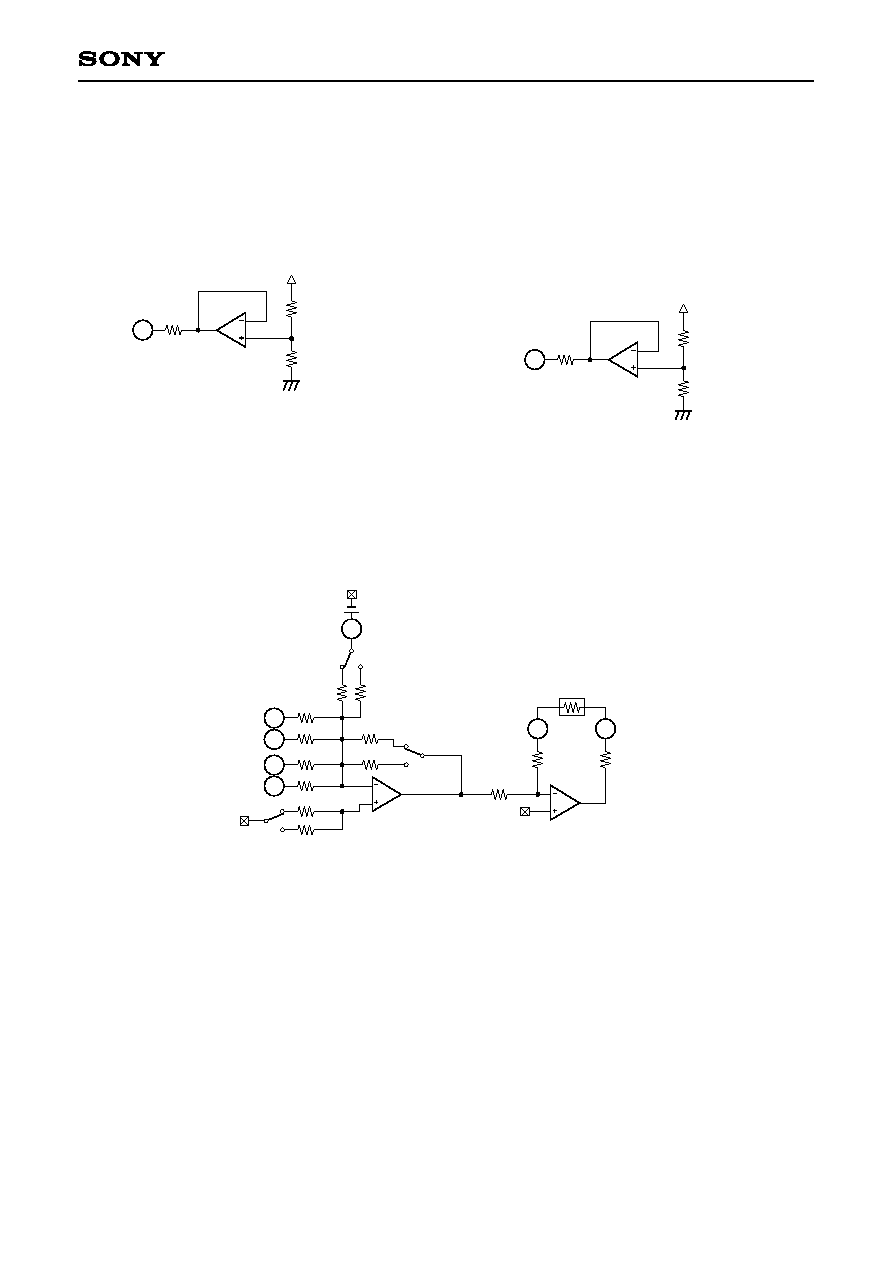

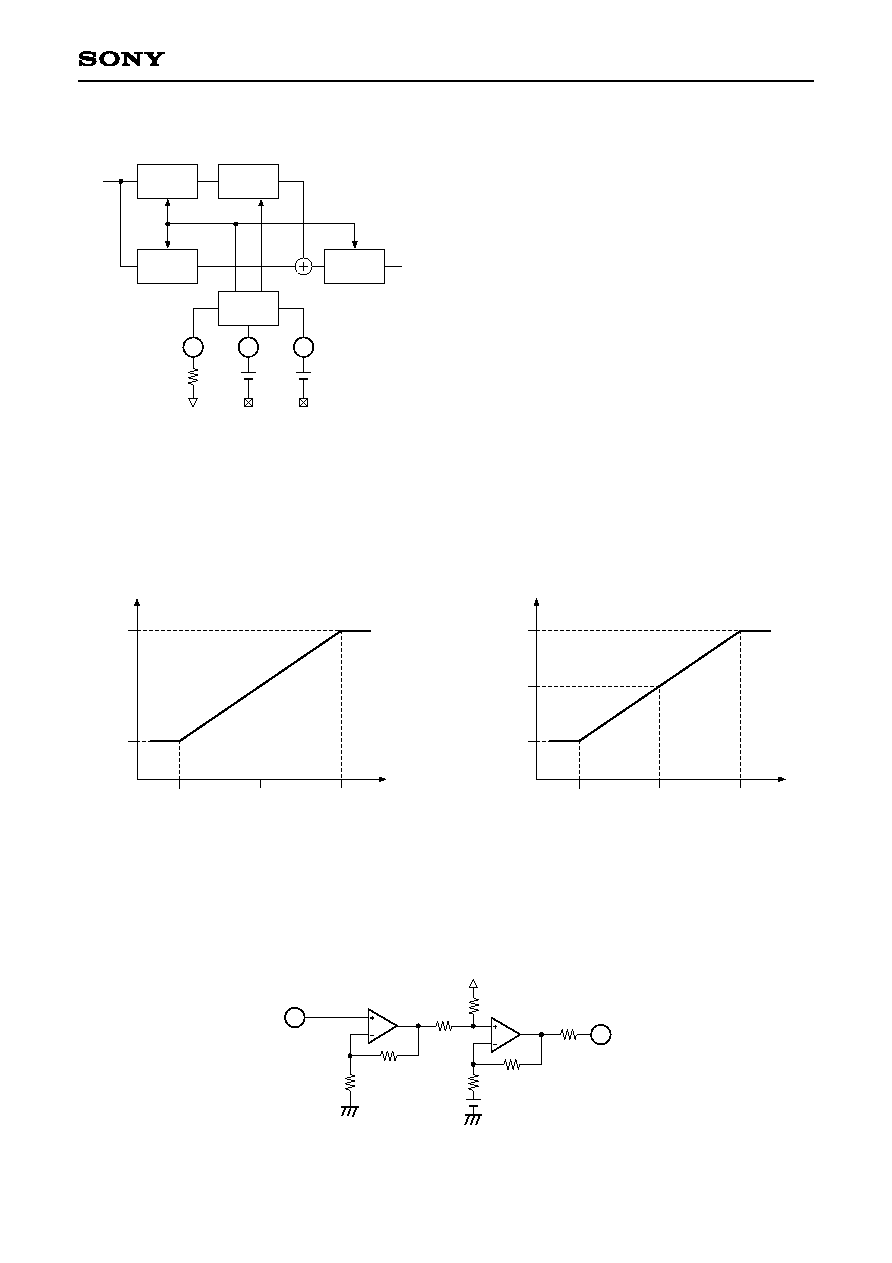

∑ EQ

V

CC

VC

EQ CNT

RFC

LPF

LPF

HPF

Amp

VC

26

VFC

fc

In

Boost

Out

25

BST 24

The diagram to the left shows the EQ internal block

diagram.

The EQ consists of a combination of HPF and LPF.

The HPF and LPF transmittance is the Bessel function.

The boost gain can be adjusted by adjusting the HPF

gain.

The boost frequency is adjusted by the RFC external

resistance value and the VFC control voltage value.

RFC resistance value: The cut-off frequency fo of each

filter is adjusted by the Pin 26

external resistance value.

The VFC voltage can be varied

using this fo as the reference.

VFC voltage: fo can be changed by the voltage applied

to Pin 25.

The boost gain can be adjusted by the BST pin control

voltage.

The control characteristics are shown in the graph below.

The cut-off frequency control characteristics are

shown in the graph below.

VC ≠ 1.0

VC

Pin 24 (BST) voltage

VC + 1.0

Vcnt

[V]

8dB

0dB

Boost Gain [dB]

VC ≠ 1.0

VC

Pin 25 (VFC) voltage

VC + 1.0

Vcnt

[V]

1.5fo

fo

0.5fo

fc [Hz]

∑ APC (Automatic Power Control)

When the laser diode is driven by a constant current, the optical power output has extremely large negative

temperature characteristics. Therefore, the current must be controlled to maintain the monitor photo diode

output at a constant level. This control is performed by the APC function.

2

PD

1 LD

10k

55k

10k

1.25V

56k

56k

V

CC

10k

1k

≠ 11 ≠

CXA2581N

∑ Focus Error

The signals input to the A and C pins and the B and D pins are arithmetically amplified and the focus error

signal is output.

This circuit has RW/ROM switching and offset addition functions.

VC

RW

100k

23.5k

30k

ROM

A

DVC

VOFST

6

FEI 17

FE

16

30k

C 8

30k

B

30k

47k

200k

47k

50k

100k

200k

7

D

ROM

RW

ROM

RW

9

124

124

FE = Gain { (B + D) ≠ (A + C) }

Low frequency gain

ROM: 16dB

RW: 28dB

Cut-off frequency fc (typ.) ROM: 300kHz

RW:

300kHz

∑ Tracking Error

The signals input to the E and F pins are arithmetically amplified and the tracking error signal is output.

This circuit has RW/ROM switching and offset addition functions.

DV

CC

ROM

RW

10

18

DVC

F

VC

VOFST

ROM

RW

VC

E

TE

TE_BAL

11

gm

gm

19

20k

20k

20k

10k

10k

31.5k

125.5k

20k

63k

251k

63k

ROM

RW

251k

TE = Gain (F ≠ E)

Low frequency gain

ROM: 16dB

RW:

28dB

TE balance adjustment

F ≠ E low frequency gain = Ī6dB

External resistance value vs. Low frequency gain

Resistance value [

]

10k

22

16

12.5

20k

30k

Low frequency

gain [dB]

≠ 12 ≠

CXA2581N

∑ VC Buffer

This outputs the VC ((1/2) V

CC

) voltage.

The maximum output current is approximately Ī3mA.

Use this voltage as the analog block VC voltage.

∑ DVC Buffer

This outputs the 1/2 DV

CC

voltage.

The maximum output current is approximately Ī3mA.

Use this voltage as the digital block VC voltage.

The output DC voltage of each block is level shifted

using the DVC voltage as the reference.

27

25

VC

40k

40k

V

CC

14

25

DVC

40k

40k

DV

CC

∑ RFDC

The signals input to the A, B, C and D pins are added, amplified and the RFDC signal is output. RW/ROM

switching and low frequency gain adjustment are possible.

VC

RW

96k

24k

15k

ROM

A

DVC

VC

6

30

RFDCI 29

RFDCO

28

15k

B 7

15k

C

15k

2.4k

3.3k

10k

2k

5.1k

40k

8

D

ROM

RW

ROM

RW

9

124

124

RFDC = Gain (A + B + C + D)

Low frequency gain ROM: 17.5dB

RW:

29.5dB

fc (Typ)

ROM: 20MHz

RW:

5MHz

The gain can be adjusted by the external resistance connected between Pins 28 and 29.

The output voltage offset can be adjusted by controlling the Pin 30 voltage.

≠ 13 ≠

CXA2581N

∑ Center Error

The signals input to the A and D pins and the B and C pins are arithmetically amplified and the center error

signal is output.

RW/ROM switching, low frequency gain adjustment and offset adjustment are possible.

VC

RW

48k

12k

30k

ROM

A

DVC

VOFST

6

CEI 21

CE

20

30k

D 9

30k

B

30k

24k

96k

24k

50k

200k

96k

7

C

ROM

RW

ROM

RW

8

The (B + C) ≠ (A + D) signal is arithmetically amplified.

Low frequency gain

ROM: 16dB

RW: 28dB

Cut-off frequency fc (typ.)

ROM: 200kHz

RW:

200kHz

∑ Output Offset Shift

The RFDC, FE, TE and CE output DC voltages are level shifted to the digital VC voltage (DVC).

The reference voltage of this IC is the VC voltage, and only the output reference voltage changes.

The maximum output voltage of each output signal should be kept to the digital V

CC

voltage (DV

CC

) or less in

order to protect the DSP_IC.

DVC

VOFST

40k

40k

VC

VC

40k

40k

The VC and DVC voltages are arithmetically amplified and

output as the VOFST voltage.

The VOFST voltage serves as the level shift reference

voltage, and is distributed to each block.

∑ SW

This controls the laser (APC) on/off, active/sleep mode, and RW/ROM mode switching.

Switching is controlled by the voltage applied to the SW pin.

12

SW

SW

RW/ROM

Active/Sleep

APC_ON/OFF

The VC buffer is always in active mode even if it enters sleep mode.

In the function block, MODE_SW is always set to active mode.

Item

Control

voltage

V

CC

VC or Hi-Z

GND

ON

OFF

ON

Active

Sleep

Active

RW

--

ROM

APC

Active/Sleep

RW/ROM

SW high/low condition

High: VC + 1V to Vcc

Low: VC ≠ 1V to GND

≠ 14 ≠

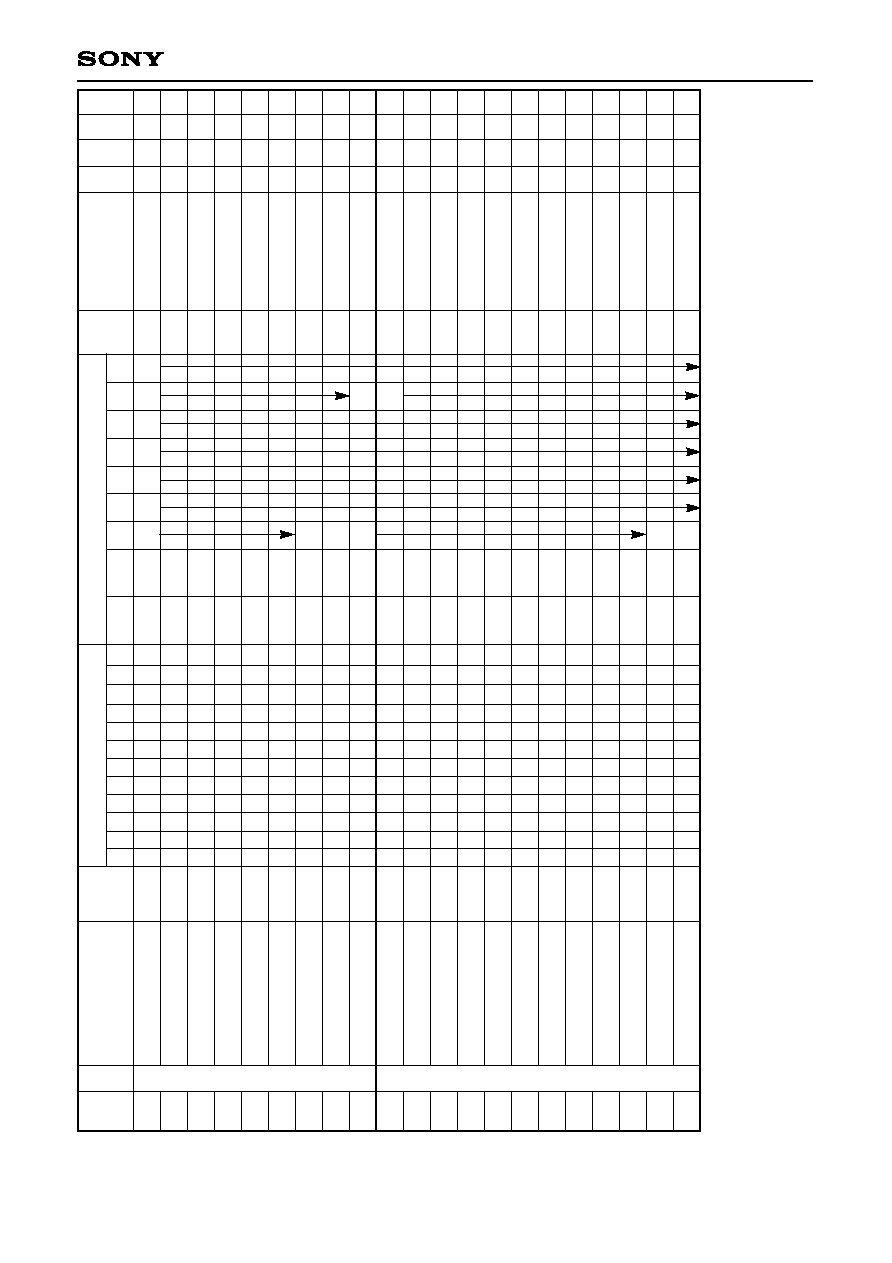

CXA2581N

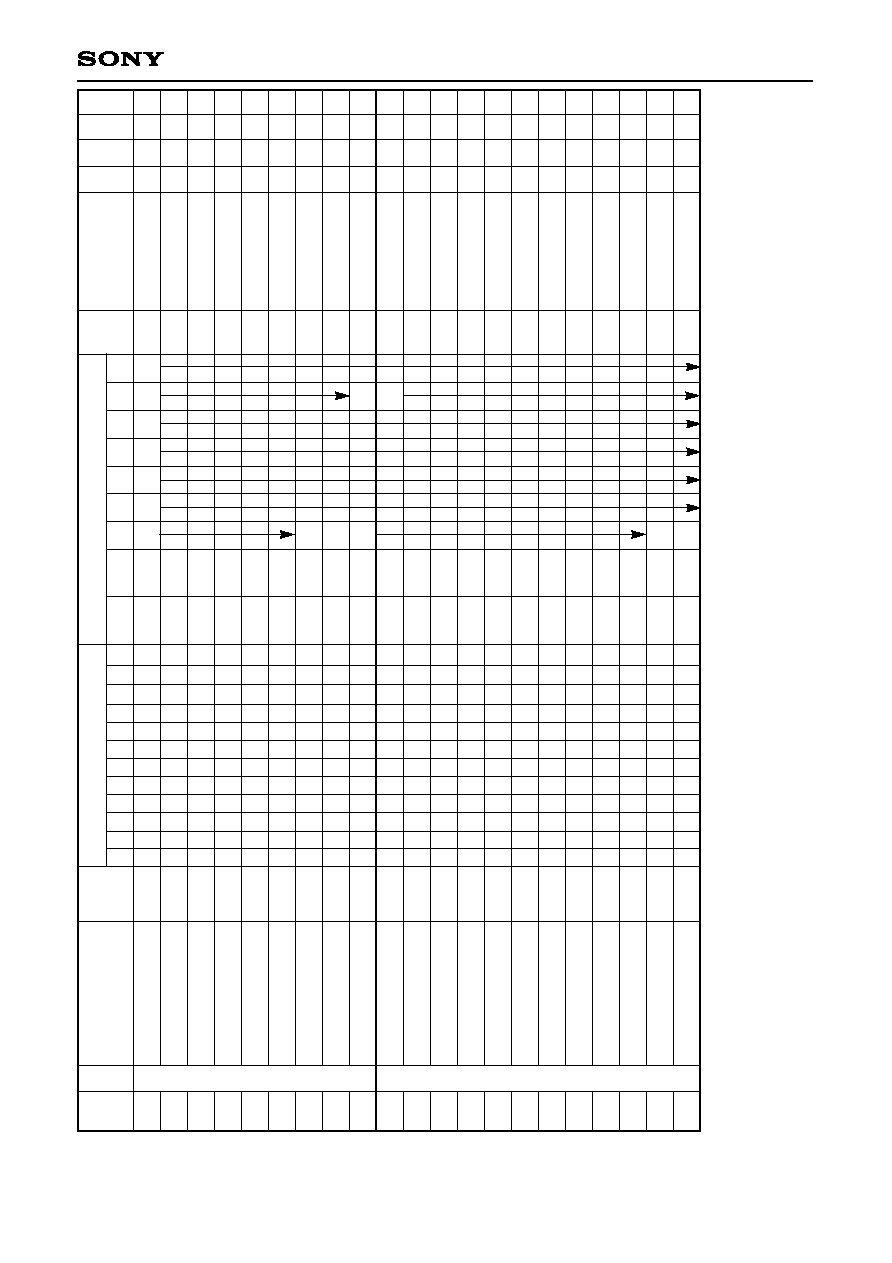

Measure-

ment No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

Current consumption (Active, EQ On)

Current consumption (Active, EQ Off)

Current consumption (DV

CC

)

Current consumption (Sleep)

SUM offset voltage

SUM low frequency gain

SUM frequency response

SUM maximum output voltage H

SUM maximum output voltage L

Offset voltage ROM

Offset voltage RW

Low frequency gain ROM_min

Low frequency gain ROM_cnt

Low frequency gain ROM_max

Low frequency gain RW_min

Low frequency gain RW_cnt

Low frequency gain RW_max

Low frequency gain EQ_off

Frequency response Min_L

Frequency response Min_H

Frequency response EQ_OFF

Maximum output voltage H

Maximum output voltage L

Icc_Aeqon

Icc_Aeqoff

Icc_Dvcc

Icc_Slp

ACSUM_Ofst

Gsum

Fsum

Vsum_H

Vsum_L

AC_OfstROM

AC_OfstRW

Gac_ROM1

Gac_ROM2

Gac_ROM3

Gac_RW1

Gac_RW2

Gac_RW3

Gac_EQoff

Fac_MinL

Fac_MinH

Fac_EQoff

Vac_H

Vac_L

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

Hi-Z

O

O

O

O

0.1Vp-p

0.1Vp-p

1.4Vp-p

0.8Vp-p

0.3Vp-p

0.35Vp-p

0.2Vp-p

75mVp-p

0.8Vp-p

0.3Vp-p

0.3Vp-p

0.3Vp-p

100kHz

10MHz

100kHz

100kHz

100kHz

50kHz

50kHz

50kHz

100kHz

10MHz

30MHz

20MHz

0V

70mV

70mV

0.4V

≠0.4V

0V

1.2V

≠1.2V

0V

0V

≠1.0V

0V

1.0V

≠1.0V

0V

1.0V

0V

0V

1.7V

0V

1.7V

0V

1.7V

0V

0V

≠1.0V

1.0V

0V

0V

22

22

13

22

4

4

4

4

4

15

15

15

15

15

15

15

15

15

15

15

15

15

15

Pin current

Pin current

Pin current

Pin current

Pin voltage

20 log (Vout/Vin)

20 log (Vout/Vin)

≠

Gsum

Pin voltage ≠ACSUM_Ofst

Pin voltage ≠ACSUM_Ofst

Pin voltage

Pin voltage

20 log (Vout/Vin) ≠ Gac_ROM2

20 log (Vout/Vin)

20 log (Vout/Vin) ≠ Gac_ROM2

20 log (Vout/Vin) ≠ Gac_RW2≠ Gac_ROM2

20 log (Vout/Vin) ≠ Gac_ROM2

20 log (Vout/Vin) ≠ Gac_RW2≠ Gac_ROM2

20 log (Vout/Vin)

20 log (Vout/Vin) ≠ Gac_ROM2

20 log (Vout/Vin) ≠ Gac_ROM2

20 log (Vout/Vin) ≠ EQoff

Pin voltage ≠ AC_OfstROM

Pin voltage ≠ AC_OfstROM

30

15

0.2

3

≠

1.2

11

≠

2.5

1.4

≠

0.5

≠

0.8

≠

0.8

≠

11

≠

3

5

≠

11

9

5

≠

2

2

2

≠

0.5

0.8

≠

1.1

50

30

0.5

5

≠

0.7

13

≠

0.5

1.6

≠

0.3

≠

0.3

≠

0.3

≠

8

0

8

≠

8

12

8

0

5

5

2.5

1

≠

0.9

70

45

0.8

8

≠

0.2

15

0.5

1.7

≠

0.1

0.2

0.2

≠

5

3

11

≠

5

15

11

2

8

8

5.5

1.2

≠

0.7

mA

mA

mA

mA

V

dB

dB

V

V

V

V

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

V

V

Func-

tion

Measurement item

Symbol

Switch conditions

Bias conditions

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

V1

amplitude

V1

frequency

E1

E2

E3

E4

E5

E6

0V

E7

Measure-

ment pin

Measurement

conditions

Min.

Typ.

Max.

Unit

RFAC SUM

RFAC EQ

Electrical Characteristics

(V

CC

= 1.7V, V

EE

= ≠1.7V, DV

CC

= 1.7V, DV

EE

= ≠1.7V)

≠ 15 ≠

CXA2581N

Measure-

ment No.

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

Offset voltage ROM

Offset voltage RW

Low frequency gain ROM

Low frequency gain RW

Frequency response ROM

Frequency response RW

Maximum output voltage H

Maximum output voltage L

Offset voltage 1

Offset voltage ROM

Offset voltage RW

Low frequency gain ROM1

Low frequency gain ROM2

Low frequency gain RW1

Low frequency gain RW2

Frequency response ROM1

Frequency response ROM2

Frequency response RW1

Frequency response RW2

Maximum output voltage H

Maximum output voltage L

DC_OfstROM

DC_OfstRW

Gdc_ROM

Gdc_RW

Fdc_ROM

Fdc_RW

Vdc_H

Vdc_L

DC_Ofst1

FE_OfstROM

FE_OfstRW

Gfe_ROM1

Gfe_ROM2

Gfe_RW1

Gfe_RW2

Ffe_ROM1

Ffe_ROM2

Ffe_RW1

Ffe_RW2

Vfe_H

Vfe_L

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

50mVp-p

12.5mVp-p

50mVp-p

12.5mVp-p

0.1Vp-p

0.1Vp-p

25mVp-p

25mVp-p

0.1Vp-p

0.1Vp-p

25mVp-p

25mVp-p

100kHz

100kHz

20MHz

5MHz

1kHz

1kHz

1kHz

1kHz

300kHz

300kHz

300kHz

300kHz

0V

0.3V

≠

0.3V

0V

0.3V

0.3V

0V

0V

0V

0V

0V

≠0.5V

0V

28

28

28

28

28

28

28

28

28

16

16

16

16

16

16

16

16

16

16

16

16

Pin voltage

Pin voltage

20 log (Vout/Vin)

20 log (Vout/Vin) ≠ Gdc_ROM

20 log (Vout/Vin) ≠ Gdc_ROM

20 log (Vout/Vin) ≠ Gdc_RW ≠ Gdc_ROM

Pin voltage

Pin voltage

Pin voltage

Pin voltage

Pin voltage

20 log (Vout/Vin)

20 log (Vout/Vin)

20 log (Vout/Vin) ≠ Gfe_ROM1

20 log (Vout/Vin) ≠ Gfe_ROM2

20 log (Vout/Vin) ≠ Gfe_ROM1

20 log (Vout/Vin) ≠ Gfe_ROM2

20 log (Vout/Vin) ≠ Gfe_RW1≠ Gfe_ROM1

20 log (Vout/Vin) ≠ Gfe_RW2≠ Gfe_ROM2

Pin voltage

Pin voltage

≠

150

≠

150

14.5

10

≠

3.5

≠

4.5

0.6

≠

1.7

≠

0.7

≠

150

≠

150

12.5

12.5

10

10

≠

5.5

≠

5.5

≠

5.5

≠

5.5

1.3

≠

1.7

0

0

17.5

12

≠

0.5

≠

1.5

0.8

≠

1.5

≠

0.6

0

0

15.5

15.5

12

12

≠

2.5

≠

2.5

≠

2.5

≠

2.5

1.5

≠

1.5

150

150

20.5

14

0.5

≠

0.5

1

≠

1.3

≠

0.5

150

150

18.5

18.5

14

14

0.5

0.5

0.5

0.5

1.7

≠

1.3

mV

mV

dB

dB

dB

dB

V

V

V

mV

mV

dB

dB

dB

dB

dB

dB

dB

dB

V

V

Func-

tion

Measurement item

Symbol

Switch conditions

Bias conditions

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

V1

amplitude

V1

frequency

E1

E2

E3

E4

E5

E6

0V

E7

Measure-

ment pin

Measurement

conditions

Min.

Typ.

Max.

Unit

RFDC

FE

≠ 16 ≠

CXA2581N

Measure-

ment No.

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

Offset voltage ROM

Offset voltage RW

Low frequency gain ROM1

Low frequency gain ROM2

Low frequency gain RW1

Low frequency gain RW2

Frequency response ROM1

Frequency response ROM2

Frequency response RW1

Frequency response RW2

Balance gain 1

Balance gain 2

Maximum output voltage H

Maximum output voltage L

Offset voltage ROM

Offset voltage RW

Low frequency gain ROM1

Low frequency gain ROM2

Low frequency gain RW1

Low frequency gain RW2

Frequency response ROM1

Frequency response ROM2

Frequency response RW1

Frequency response RW2

Maximum output voltage H

Maximum output voltage L

TE_OfstROM

TE_OfstRW

Gte_ROM1

Gte_ROM2

Gte_RW1

Gte_RW2

Fte_ROM1

Fte_ROM2

Fte_RW1

Fte_RW2

Gte1

Gte2

Vte_H

Vte_L

CE_OfstROM

CE_OfstRW

Gce_ROM1

Gce_ROM2

Gce_RW1

Gce_RW2

Fce_ROM1

Fce_ROM2

Fce_RW1

Fce_RW2

Vce_H

Vce_L

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

0.1Vp-p

0.1Vp-p

25mVp-p

25mVp-p

0.1Vp-p

0.1Vp-p

25mVp-p

25mVp-p

0.1Vp-p

0.1Vp-p

0.1Vp-p

0.1Vp-p

25mVp-p

25mVp-p

0.1Vp-p

0.1Vp-p

25mVp-p

25mVp-p

1kHz

1kHz

1kHz

1kHz

100kHz

100kHz

100kHz

100kHz

1kHz

1kHz

1kHz

1kHz

1kHz

1kHz

200kHz

200kHz

200kHz

200kHz

0V

0.6V

0.6V

0V

0.5V

0.5V

0V

0V

0V

0V

0V

18

18

18

18

18

18

18

18

18

18

18

18

18

18

20

20

20

20

20

20

20

20

20

20

20

20

Pin voltage

Pin voltage

20 log (Vout/Vin)

20 log (Vout/Vin)

20 log (Vout/Vin) ≠ Gte_ROM1

20 log (Vout/Vin) ≠ Gte_ROM2

20 log (Vout/Vin) ≠ Gte_ROM1

20 log (Vout/Vin) ≠ Gte_ROM2

20 log (Vout/Vin) ≠ Gte_RW1≠ Gte_ROM1

20 log (Vout/Vin) ≠ Gte_RW2≠ Gte_ROM2

E, F gain difference

E, F gain difference

Pin voltage

Pin voltage

Pin voltage

Pin voltage

20 log (Vout/Vin)

20 log (Vout/Vin)

20 log (Vout/Vin) ≠ Gce_ROM1

20 log (Vout/Vin) ≠ Gce_ROM2

20 log (Vout/Vin) ≠ Gce_ROM1

20 log (Vout/Vin) ≠ Gce_ROM2

20 log (Vout/Vin) ≠ Gce_RW1≠ Gce_ROM1

20 log (Vout/Vin) ≠ Gce_RW2≠ Gce_ROM2

Pin voltage

Pin voltage

≠

200

≠

500

13

13

10

10

≠

3.2

≠

3.2

≠

3.5

≠

3.5

4

≠

8

1.3

≠

1.7

≠

150

≠

150

12.5

12.5

10

10

≠

3.8

≠

3.8

≠

3.8

≠

3.8

1.15

≠

1.7

0

0

16

16

12

12

≠

1.2

≠

1.2

≠

1.5

≠

1.5

6

≠

6

1.5

≠

1.5

0

0

15.5

15.5

12

12

≠

2.3

≠

2.3

≠

2.3

≠

2.3

1.35

≠

1.5

200

500

19

19

14

14

0.8

0.8

0.5

0.5

8

≠

4

1.7

≠

1.3

150

150

18.5

18.5

14

14

≠

0.8

≠

0.8

≠

0.8

≠

0.8

1.55

≠

1.3

mV

mV

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

V

V

mV

mV

dB

dB

dB

dB

dB

dB

dB

dB

V

V

Func-

tion

Measurement item

Symbol

Switch conditions

Bias conditions

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

V1

amplitude

V1

frequency

E1

E2

E3

E4

E5

E6

0V

1.0V

≠1.0V

0V

E7

Measure-

ment pin

Measurement

conditions

Min.

Typ.

Max.

Unit

TE

CE

≠ 17 ≠

CXA2581N

Measure-

ment No.

71

72

73

74

75

76

77

Output voltage 1

Output voltage 2

Output voltage 3

APC OFF voltage

Maximum output current

Output voltage

Output voltage

Vapc1

Vapc2

Vapc3

Vapc_off

Iapc_max

Vavc

Vdvc

O

O

O

O

O

O

Hi-Z

O

0V

0V

0V

0V

0V

0V

0V

1, 2

1

1

1

1

27

14

Input at which output voltage = 0V

Pin voltage

Pin voltage

Pin voltage

Pin voltage

Pin voltage

Pin voltage

0

0.5

≠1

1.4

≠0.55

≠100

≠100

150

0.75

≠0.75

1.6

≠0.15

0

0

300

1

≠0.5

1.7

0.25

100

100

mV

V

V

V

V

mV

mV

Func-

tion

Measurement item

Symbol

Switch conditions

Bias conditions

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

V1

amplitude

V1

frequency

E1

E2

E3

E4

E5

E6

0V

E7

Measure-

ment pin

Measurement

conditions

Min.

Typ.

Max.

Unit

Vapc1 +

20mV

Vapc1 ≠

20mV

APC

AVC

DVC

≠ 18 ≠

CXA2581N

1

2

3

4

5

6

7

9

12

11

20

19

22

24

25

26

27

28

29

30

8

10

14

13

18

17

21

23

15

16

L

D

P

D

E

Q

_

I

N

A

C

_

S

U

M

G

N

D

A

B

D

S

W

F

C

E

D

V

C

D

V

C

C

R

F

A

C

D

C

_

O

F

S

T

R

F

D

C

I

R

F

D

C

O

V

C

R

F

C

V

F

C

B

S

T

V

C

C

T

E

_

B

A

L

C

E

R

F

G

C

E

I

F

E

I

T

E

F

E

E6

E5

E4

E3

E7

5.1k

5.1k

10k

200k

10k

10k

20k

20k

10k

10k 100k

10k

V

CC

S12

V

CC

DV

CC

V

EE

V

EE

V

CC

V

CC

V

EE

S11

S10

S9

S8

S7

S6

S5

S3

S2

S1

S4

V1

0.1

Ķ

E1

E2

0.8mA

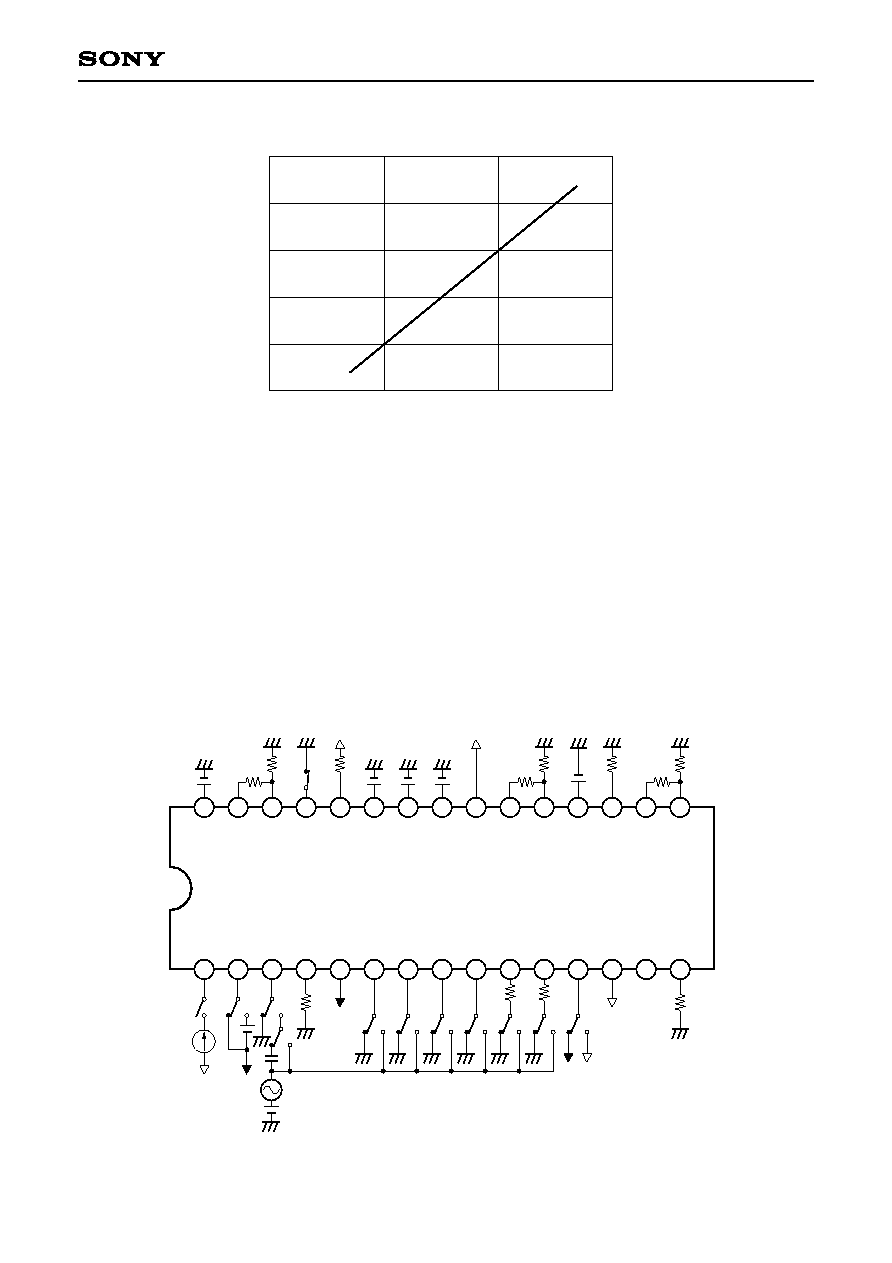

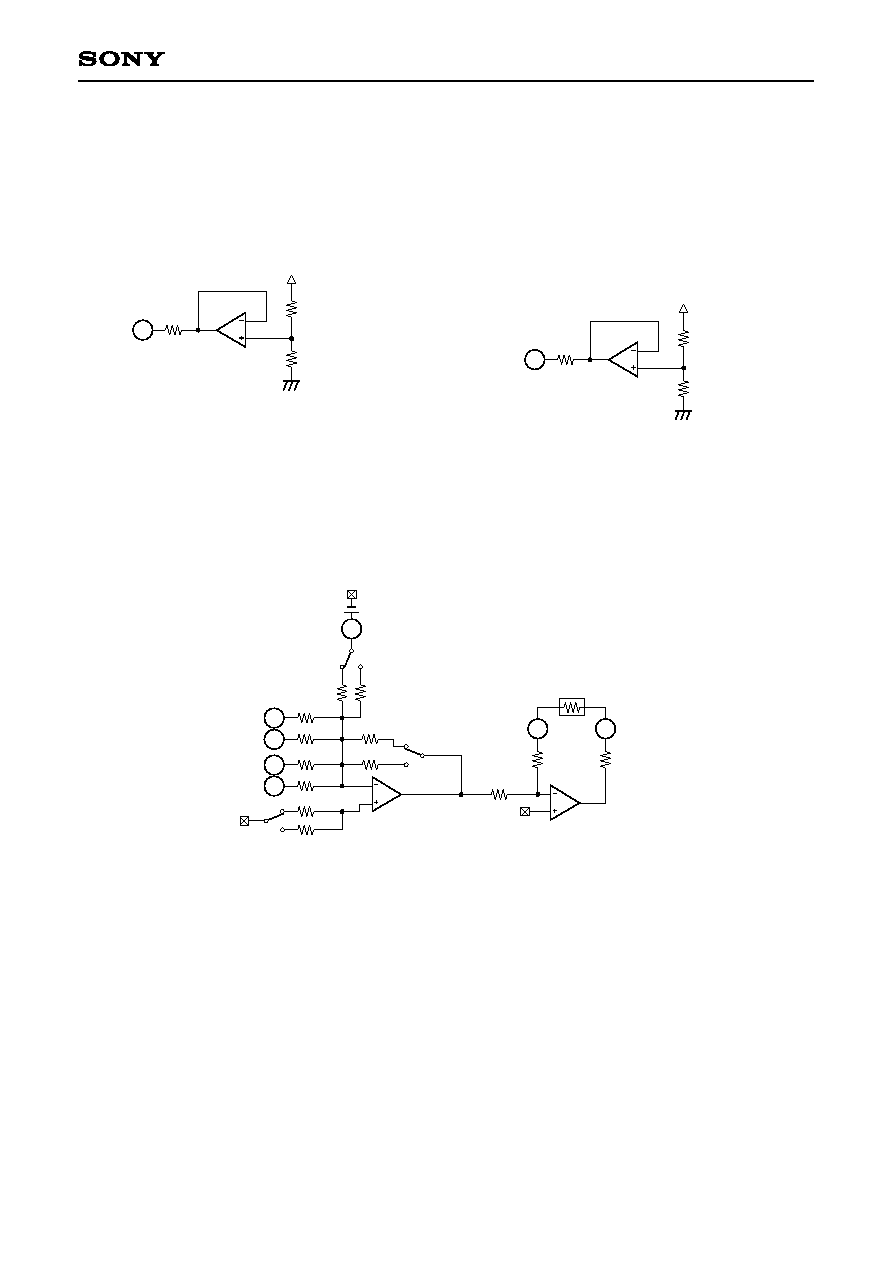

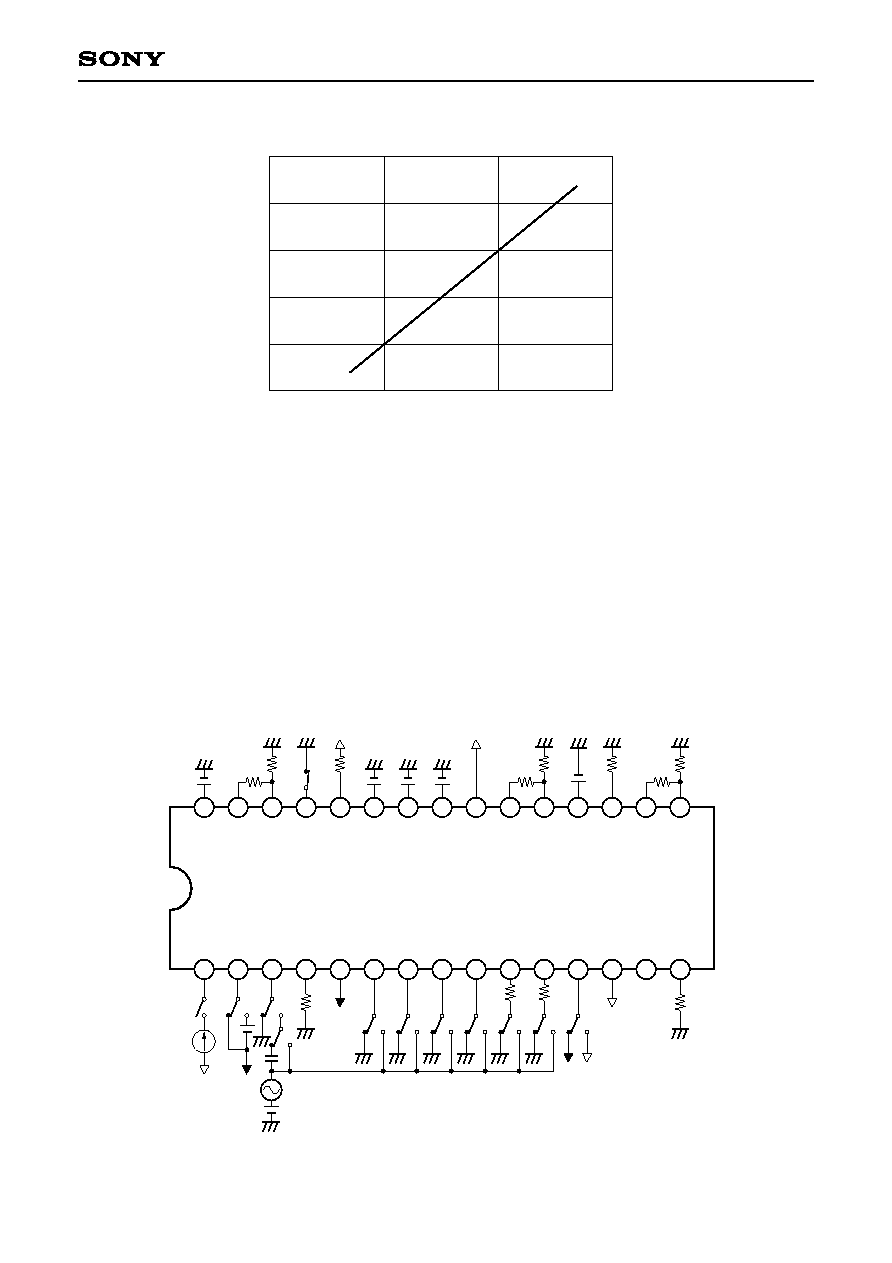

Notes on Supply Voltage

2.5

6.5

6

5.5

5

4.5

4

3

DVcc (Pin 13) [V]

V

CC

voltage value at which the waveform is clipped when DV

CC

is fixed

V

c

c

(

P

i

n

2

2

)

[

V

]

3.5

2

The voltage difference between V

CC

(Pin 22) and DV

CC

(Pin 13) should be kept to the value shown in the graph

above or less.

Example) When DV

CC

= 2.5V

From the graph, V

CC

= 4.5V

Therefore, V

CC

should be from 3.4 to 4.5V.

(3.4V is the minimum operating voltage for the IC.)

Electrical Characteristics Measurement Circuit

≠ 19 ≠

CXA2581N

LD

Drive

1

2

3

4

5

6

7

9

12

20

19

22

24

25

26

27

28

29

30

8

14

13

18

17

21

23

15

16

L

D

P

D

E

Q

_

I

N

A

C

_

S

U

M

G

N

D

A

B

D

S

W

F

C

E

D

V

C

D

V

C

C

R

F

A

C

D

C

_

O

F

S

T

R

F

D

C

I

R

F

D

C

O

V

C

R

F

C

V

F

C

B

S

T

V

C

C

T

E

_

B

A

L

C

E

R

F

G

C

E

I

F

E

I

T

E

F

E

VC

RFDC

OUT

V

CC

DV

CC

CE

OUT

TE

OUT

FE

OUT

DVC

RFAC

OUT

MODE

Control

F

E

D

C

B

A

PD IN

RF SUM RF SUM inputs the signal when A, B, C

and D are added by the front and PD.

0.1

Ķ

11

10

0.1

Ķ

AC

SUM

APC

AC

VCA

EQ

VC

VC

RW/ROM

EQ_ON/OFF

VOFST

DVC

DV

CC

RW/ROM

DVC

DV

CC

25

15

30

29

28

17

16

26

24

23

3

4

6

7

8

9

DVC

DV

CC

VC

VC

VOFST

DVC

DVC

V

CC

VOFST

B

C

A

D

F

E

SW

PD

LD

V

CC

GND

VC

V

CC

GND

VC

DVC

DV

CC

CE

CEI

FE

FE

RFDC

RFAC

FEI

RFDCO

RFDCI

RFAC

VFC

RFC

RFG

V

CC

V

CC

<CXA2581N>

<DSP>

BST

EQ_IN

0.1

Ķ

AC_SUM

DC_OFST

VC

RW/ROM

21

14

20

13

VC

APC-OFF (Hi-Z)

RW/ROM

(H/L)

F

E

<OP>

1

2

12

A

B

C

D

A

B

C

D

5

27

22

VC

A

A

B

C

D

RF

VC

TE

CE

V

CC

VC

B

VC

C

VC

D

VC

F

VC

E

VC

DV

CC

RW/ROM

RW/ROM

RW/ROM

VOFST

VC

VC

19

18

DVC

TE

TE_BAL

gm

gm

11

10

0.1

Ķ

Application Circuits

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

≠ 20 ≠

CXA2581N

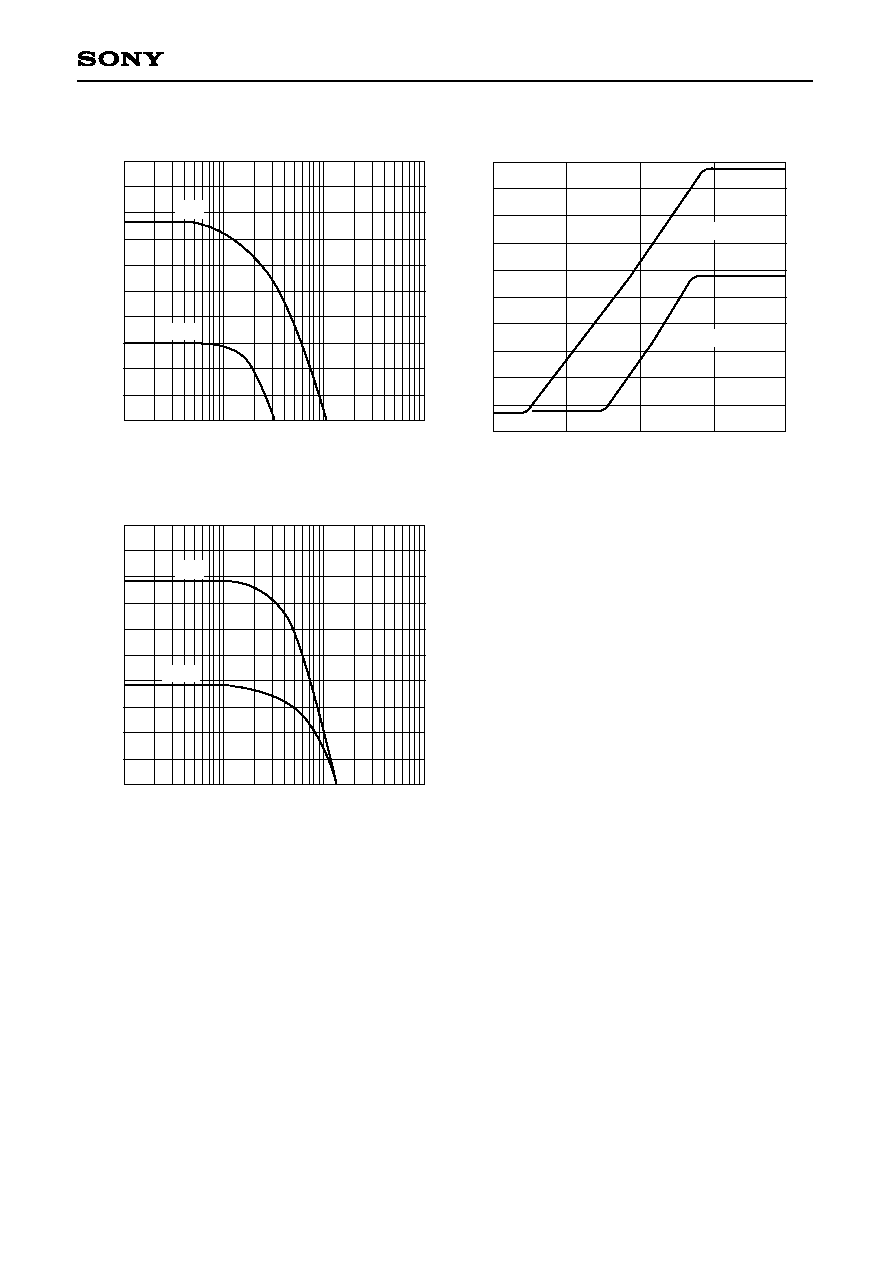

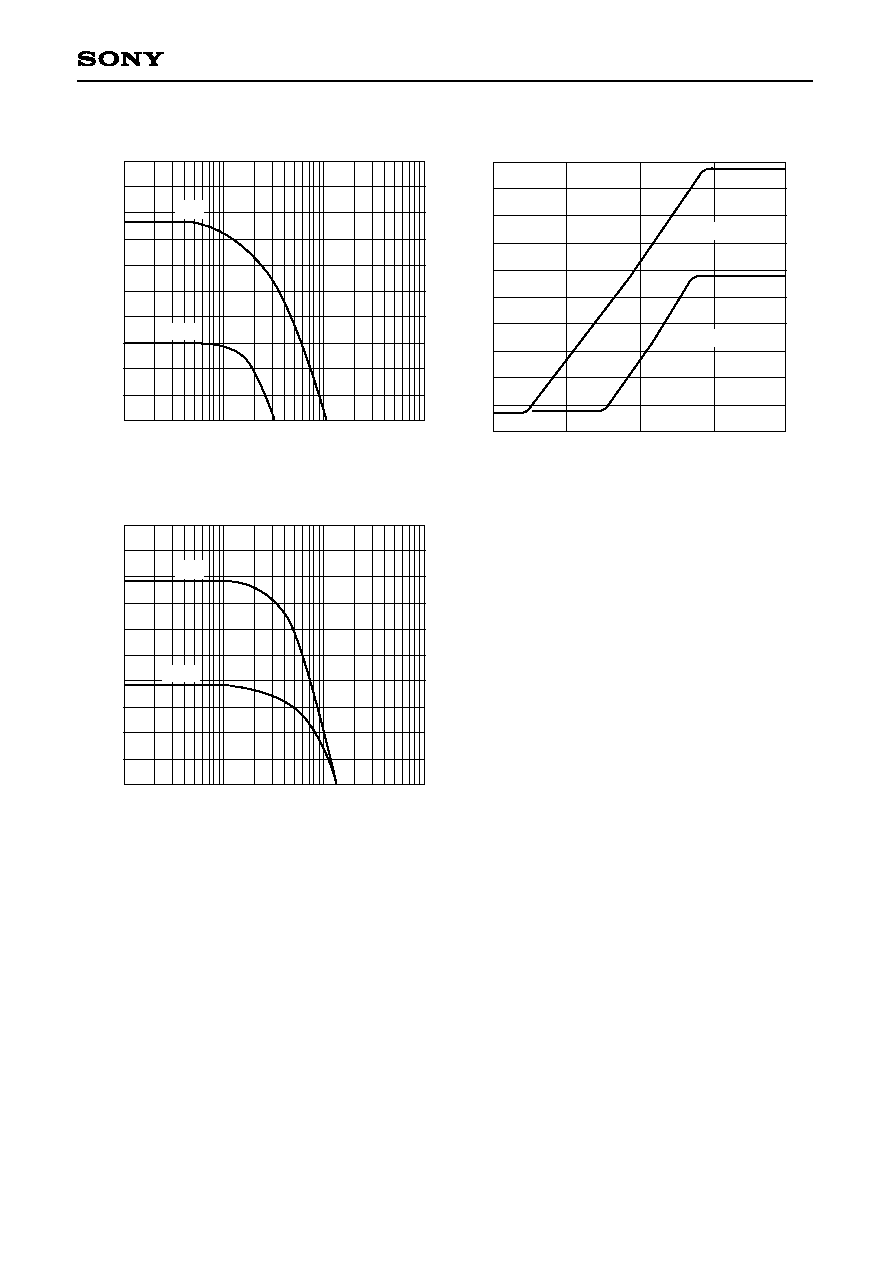

Characteristics Graphs

EQ Rfc resistance value vs. Frequency response

[MHz]

Vbst = VC, Vfc = VC

8

[

d

B

]

7

6

5

4

3

2

1

0

0.1

1

Rfc = 100k

Rfc = 20k

Rfc = 5.1k

10

100

≠1

≠2

RF DC frequency response

[MHz]

RW

38

[

d

B

]

35

32

29

26

23

20

17

14

0.1

1

ROM

10

100

11

8

FE frequency response

[MHz]

RW

34

[

d

B

]

31

28

25

22

19

16

13

10

0.01

0.1

ROM

1

10

7

4

RF AC frequency response

[MHz]

AC SUM

EQ_Pass

RW mode

EQ_Pass

ROM mode

24

[

d

B

]

21

18

15

12

9

6

3

0

0.1

1

10

100

≠3

≠6

EQ Vfc vs. frequency response

[MHz]

Rfc = 20k

Vfc = ≠1V

Rfc = 20k

Vfc = 0V

Rfc = 20k

Vfc = 1V

8

[

d

B

]

7

6

5

4

3

2

1

0

0.1

1

10

100

≠1

≠2

EQ boost voltage vs. Frequency response

[MHz]

Vfc = VC

12

[

d

B

]

10

8

6

4

2

0

≠2

≠4

0.1

1

Rfc = 100k

Vboost = 1.0V

Rfc = 100k

Vboost = 0V

Rfc = 5.1k

Vboost = 1.0V

Rfc = 5.1k

Vboost = 0V

Rfc = 100k

Vboost = ≠1.0V

Rfc = 5.1k

Vboost = ≠1.0V

10

100

≠6

≠8

Vbst = VC

≠ 21 ≠

CXA2581N

TE frequency response

[MHz]

RW

35

[

d

B

]

32

29

26

23

20

17

16

13

0.01

0.1

ROM

1

10

10

7

APC I/O characteristics

VPD ≠ Input voltage [V]

5.5

V

L

D

≠

O

u

t

p

u

t

v

o

l

t

a

g

e

[

V

]

5.0

4.5

4.0

3.5

3.0

2.5

2.0

1.5

0.05

0.1

0.15

0.2

0.25

1.0

0.5

CE frequency response

[MHz]

RW

34

[

d

B

]

31

28

25

22

19

16

13

10

0.01

0.1

ROM

1

10

7

4

Vcc = 5.5V

Vcc = 3.4V

≠ 22 ≠

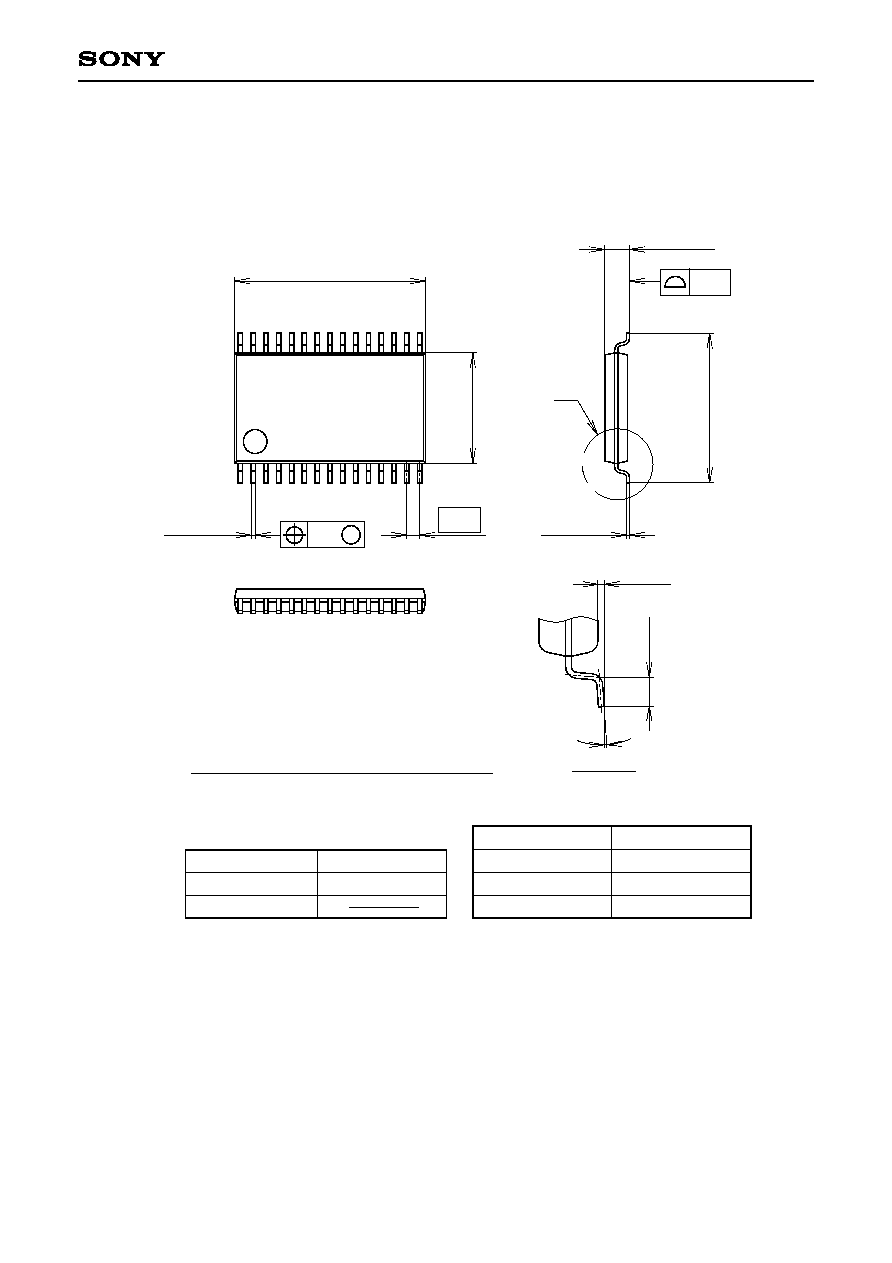

CXA2581N

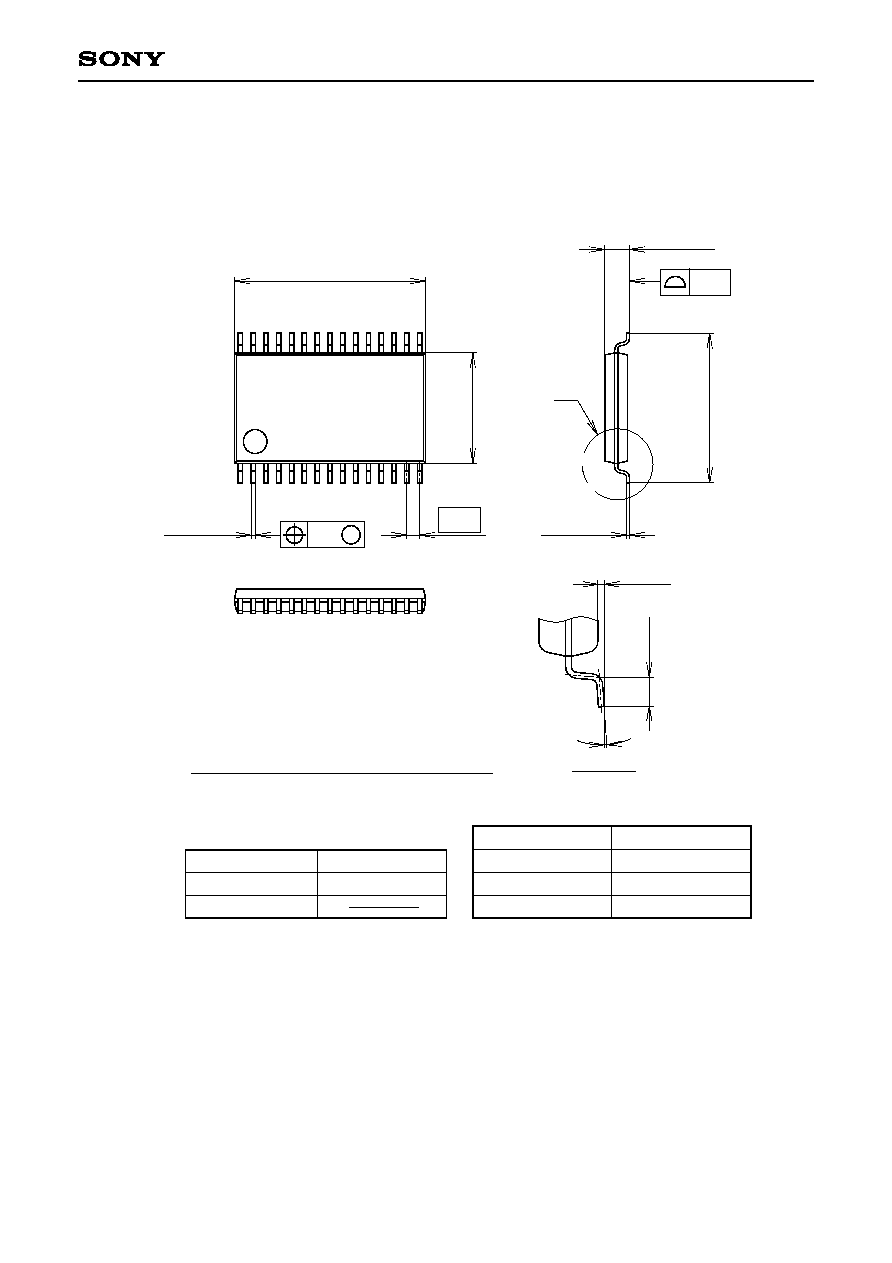

Package Outline

Unit: mm

SONY CODE

EIAJ CODE

JEDEC CODE

PACKAGE STRUCTURE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

SOLDER/PALLADIUM

42/COPPER ALLOY

30PIN SSOP (PLASTIC)

9.7 Ī 0.1

5

.

6

Ī

0

.

1

0.65

0.22 ≠ 0.05

30

1

15

16

1.25

+ 0.2

≠ 0.1

7

.

6

Ī

0

.

2

0.15

+ 0.05

≠ 0.02

0.1 Ī 0.1

0

.

5

Ī

0

.

2

0į to 10į

A

DETAIL A

SSOP-30P-L01

SSOP030-P-0056

0.1g

NOTE: Dimension "

" does not include mold protrusion.

PLATING

0.10

0.13 M

+ 0.1

NOTE : PALLADIUM PLATING

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).