| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXA3246Q | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

CXA3246Q

8-bit 120MSPS Flash A/D Converter

Description

The CXA3246Q is an 8-bit high-speed flash A/D

converter capable of digitizing analog signals at the

maximum rate of 120MSPS. ECL, PECL or TTL can

be selected as the digital input level in accordance

with the application. The TTL digital output level

allows 1: 2 demultiplexed output.

Features

∑ Differential linearity error: ±0.5LSB or less

∑ Integral linearity error: ±0.5LSB or less

∑ High-speed operation with a maximum conversion

rate of 120MSPS

∑ Low input capacitance: 10pF

∑ Wide analog input bandwidth: 250MHz

∑ Low power consumption: 500mW

∑ 1: 2 demultiplexed output

∑ 1/2 frequency-divided clock output

(with reset function)

∑ Compatible with ECL, PECL and TTL digital input

levels

∑ TTL output "H" levels: 2.8V (Typ.)

∑ +3.3V line CMOS IC direct connecting available

∑ Single +5V power supply operation available

∑ Surface mounting package (48-pin QFP)

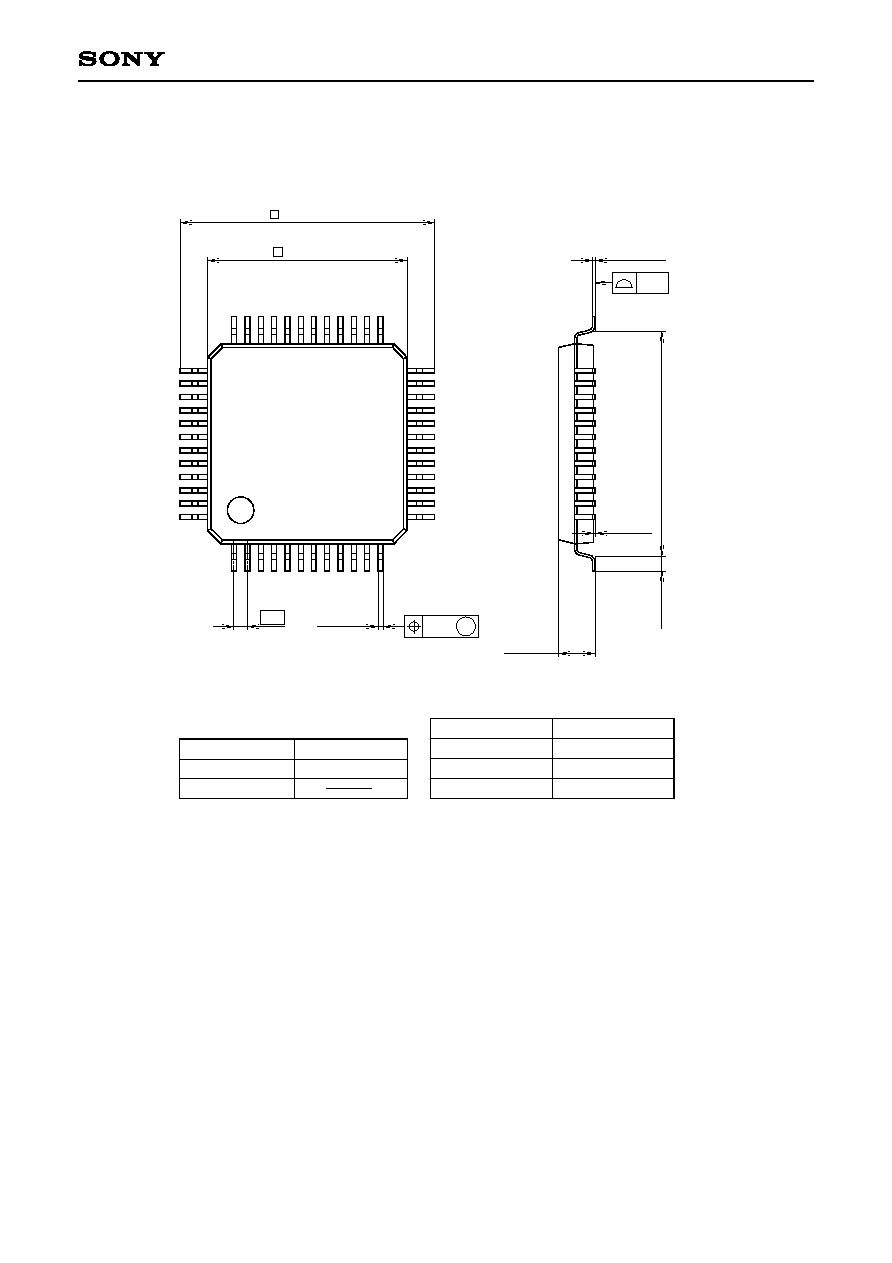

Pin Configuration (Top View)

Structure

Bipolar silicon monolithic IC

Applications

∑ Magnetic recording (PRML)

∑ Communications (QPSK, QAM)

∑ LCDs

∑ Digital oscilloscopes

≠ 1 ≠

E97902A8X-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CLK/E

N.C.

CLK/T

N.C.

N.C.

DV

CC

2

DGND2

PAD0

PAD1

PAD2

PAD3

CLKN/E

PAD4

PAD7

PAD6

DGND1

DV

CC

1

DV

CC

2

DGND2

PBD0

PBD1

PBD2

PBD3

PAD5

RESETN/E

SELECT

RESETN/T

INV

CLKOUT

DV

CC

2

DGND2

PBD7

PBD6

PBD5

PBD4

RESET/E

DV

EE

3

V

RM

1

AGND

AV

CC

V

IN

V

RM

2

AV

CC

V

RM

3

AGND

V

RT

DGND3

V

RB

13

14

15

16

17

18

19

20

21

22

23

24

25 26 27 28 29 30

40

39

38

37

36

35

34

31 32 33

41

42

43

44

45

46

47

48

2

3

4

5

6

7

8

9

10

11

12

1

48 pin QFP (Plastic)

LEAD TREATMENT: PALLADIUM PLATING

≠ 2 ≠

CXA3246Q

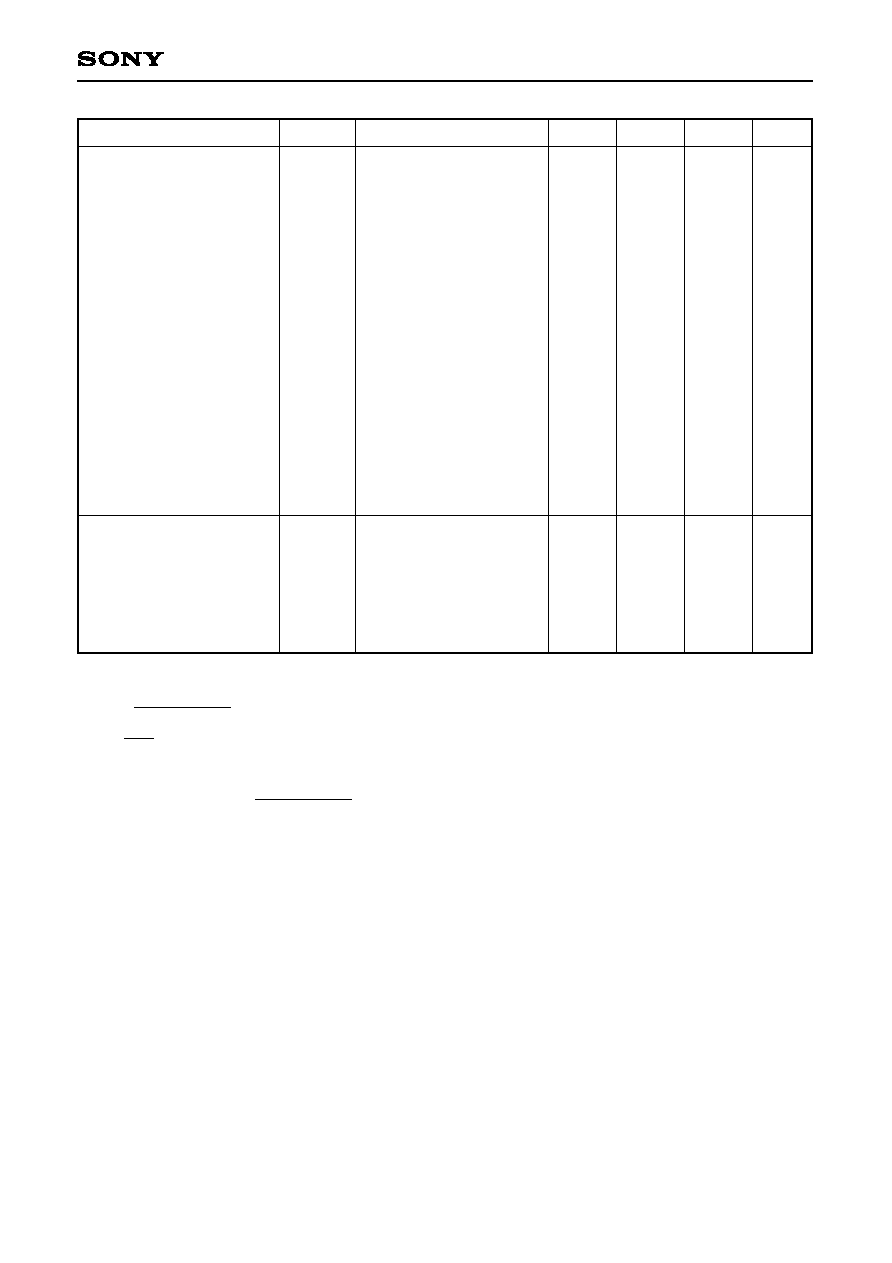

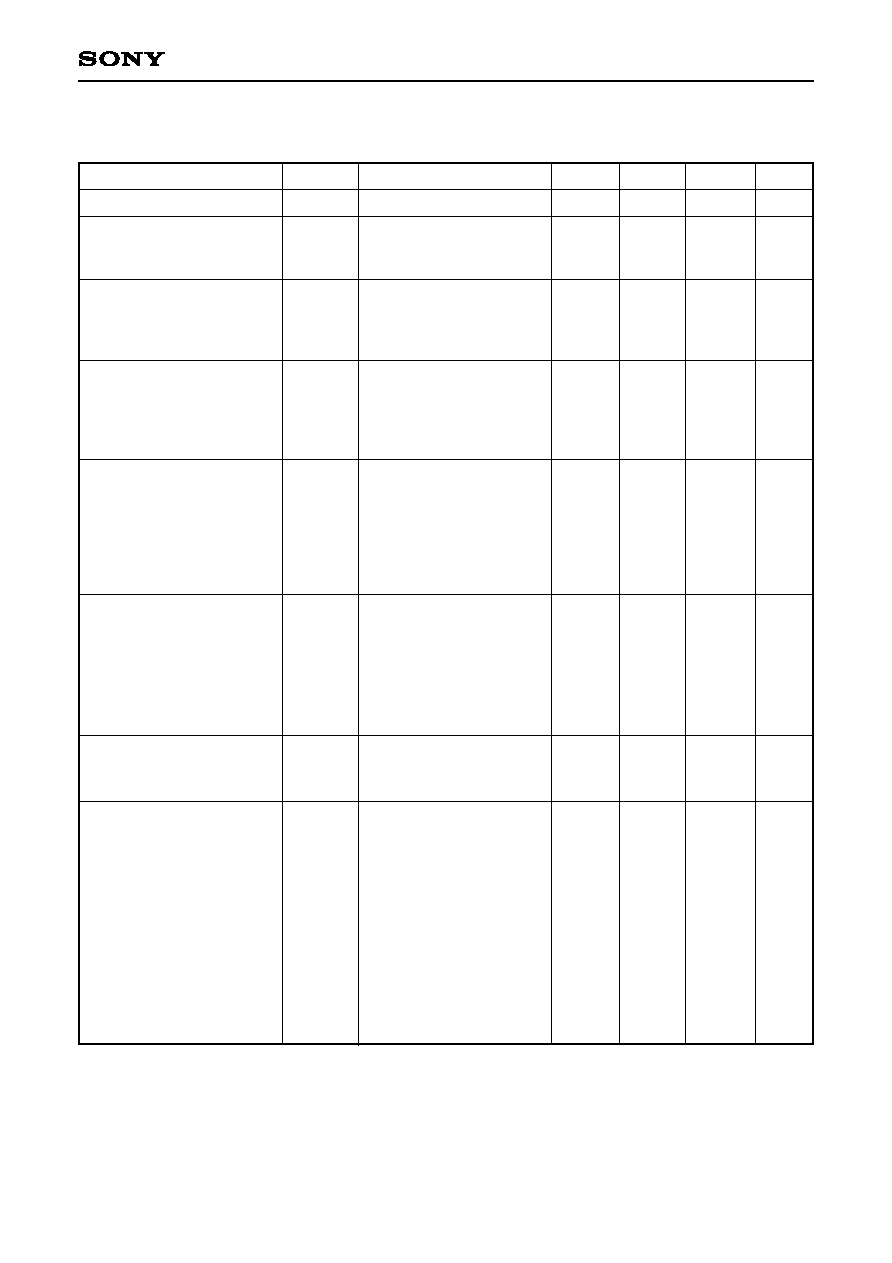

Absolute Maximum Ratings (Ta = 25∞C)

Unit

∑ Supply voltage

AV

CC

, DV

CC

1, DV

CC

2

≠0.5 to +7.0

V

DGND3

≠0.5 to +7.0

V

DV

EE

3

≠7.0 to +0.5

V

DGND3 ≠ DV

EE

3

≠0.5 to +7.0

V

∑ Analog input voltage

V

IN

V

RT

≠ 2.7 to AV

CC

V

∑ Reference input voltage

V

RT

2.7 to AV

CC

V

V

RB

V

IN

≠ 2.7 to AV

CC

V

|V

RT

≠ V

RB

|

2.5

V

∑ Digital input voltage

ECL/PECL input pin

DV

EE

3 ≠ 0.5 to DGND3 + 0.5

V

TTL input pin

DGND1 ≠ 0.5 to DV

CC

1 + 0.5

V

VID

1

(|

/E ≠

N/E|)

2.7

V

∑ Storage temperature

Tstg

≠65 to +150

∞C

∑ Allowable power dissipation P

D

1.6

W

(when mounted on a two-layer glass fabric base epoxy board with dimentions of 50mm

◊

50mm, 1.6mm thick)

Recommended Operating Conditions

With a single power supply

With dual power supply

Unit

Min.

Typ.

Max.

Min.

Typ.

Max.

∑ Supply voltage

DV

CC

1, DV

CC

2, AV

CC

+4.75

+5.0

+5.25

+4.75

+5.0

+5.25

V

DGND1, DGND2, AGND

≠0.05

0

+0.05

≠0.05

0

+0.05

V

DGND3

+4.75

+5.0

+5.25

≠0.05

0

+0.05

V

DV

EE

3

≠0.05

0

+0.05

≠5.5

≠5.0

≠4.75

V

∑ Analog input voltage

V

IN

V

RB

V

RT

V

RB

V

RT

V

∑ Reference input voltage V

RT

+2.9

+4.1

+2.9

+4.1

V

V

RB

+1.4

+2.6

+1.4

+2.6

V

|V

RT

≠ V

RB

|

1.5

2.1

1.5

2.1

V

∑ Digital input voltage

ECL/PECL input pin : V

IH

DV

EE

3 + 1.5

DGND3 DV

EE

3 + 1.5

DGND3

V

: V

IL

DV

EE

3 + 1.1

V

IH

≠ 0.4 DV

EE

3 + 1.1

V

IH

≠ 0.4

V

TTL input pin

: V

IH

2.0

2.0

V

: V

IL

0.8

0.8

V

VID

1

(|

/E ≠

N/E|)

0.4

0.8

0.4

0.8

V

∑ Maximum conversion rate Fc (Straight mode)

100

100

MSPS

(DMUX mode)

120

120

MSPS

∑ Ambient temperature

Ta

≠20

+75

≠20

+75

∞C

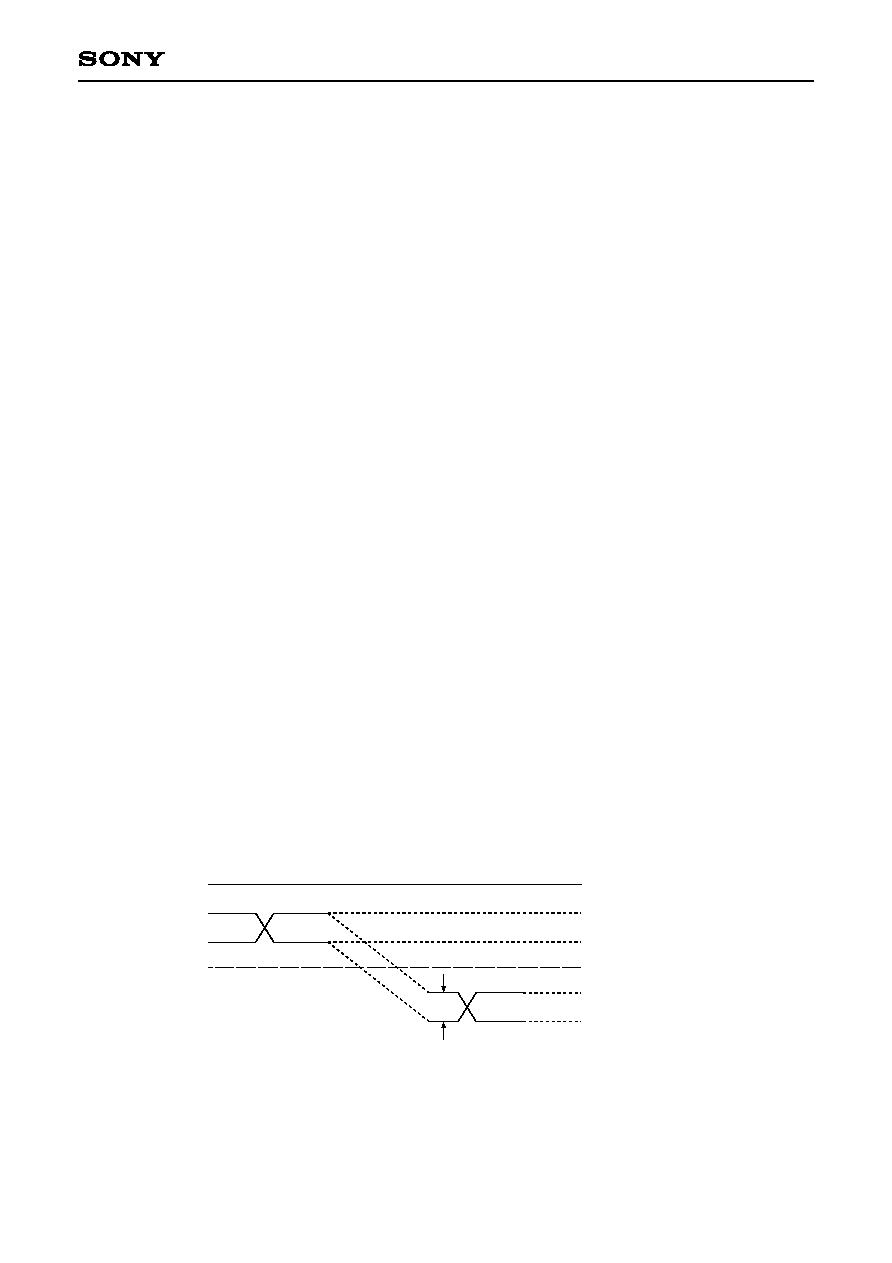

1

VID: Input Voltage Differential

ECL and PECL switching level

VID

V

IL

(min.)

V

IH

V

TH

(DGND3 ≠ 1.2V)

V

IL

V

IH

(max.)

DGND3

≠ 3 ≠

CXA3246Q

Pin Description

[Symbol]

[Pin No.]

[Description]

Digital power supply

Bottom reference voltage

Analog ground

Reference voltage mid point

Analog power supply

Analog signal input

Reference voltage mid point

Analog power supply

Reference voltage mid point

Analog ground

Reference voltage (typ.)

Digital power supply

ECL/PECL clock input

ECL/PECL clock input

TTL clock input

No connected pin

Digital power supply

Digital ground

PA side data output

Digital ground

Digital power supply

Digital power supply

Digital ground

PB side data output

Digital ground

Digital power supply

Clock output

Data output polarity inversion

Output mode selection

TTL reset input

ECL/PECL reset input

ECL/PECL reset input

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16 to 18

19

20

21 to 28

29

30

31

32

33 to 40

41

42

43

44

45

46

47

48

DV

EE

3

V

RB

AGND

V

RM

1

AV

CC

V

IN

V

RM

2

AV

CC

V

RM

3

AGND

V

RT

DGND3

CLK/E

CLKN/E

CLK/T

N.C.

DV

CC

2

DGND2

PAD0 to PAD7

DGND1

DV

CC

1

DV

CC

2

DGND2

PBD0 to PBD7

DGND2

DV

CC

2

CLKOUT

INV

SELECT

RESETN/T

RESET/E

RESETN/E

0V

1.4 to 2.6V

0V

--

+5V

V

RB

to V

RT

--

+5V

--

0V

2.9 to 4.1V

+5V

PECL

PECL

TTL

--

+5V

0V

TTL

0V

+5V

+5V

0V

TTL

0V

+5V

TTL

TTL

TTL

TTL

PECL

PECL

≠5.0V

1.4 to 2.6V

0V

--

+5V

V

RB

to V

RT

--

+5V

--

0V

2.9 to 4.1V

0V

ECL

ECL

TTL

--

+5V

0V

TTL

0V

+5V

+5V

0V

TTL

0V

+5V

TTL

TTL

TTL

TTL

ECL

ECL

Typical voltage

level with a single

power supply

Typical voltage

level with dual

power supply

≠ 4 ≠

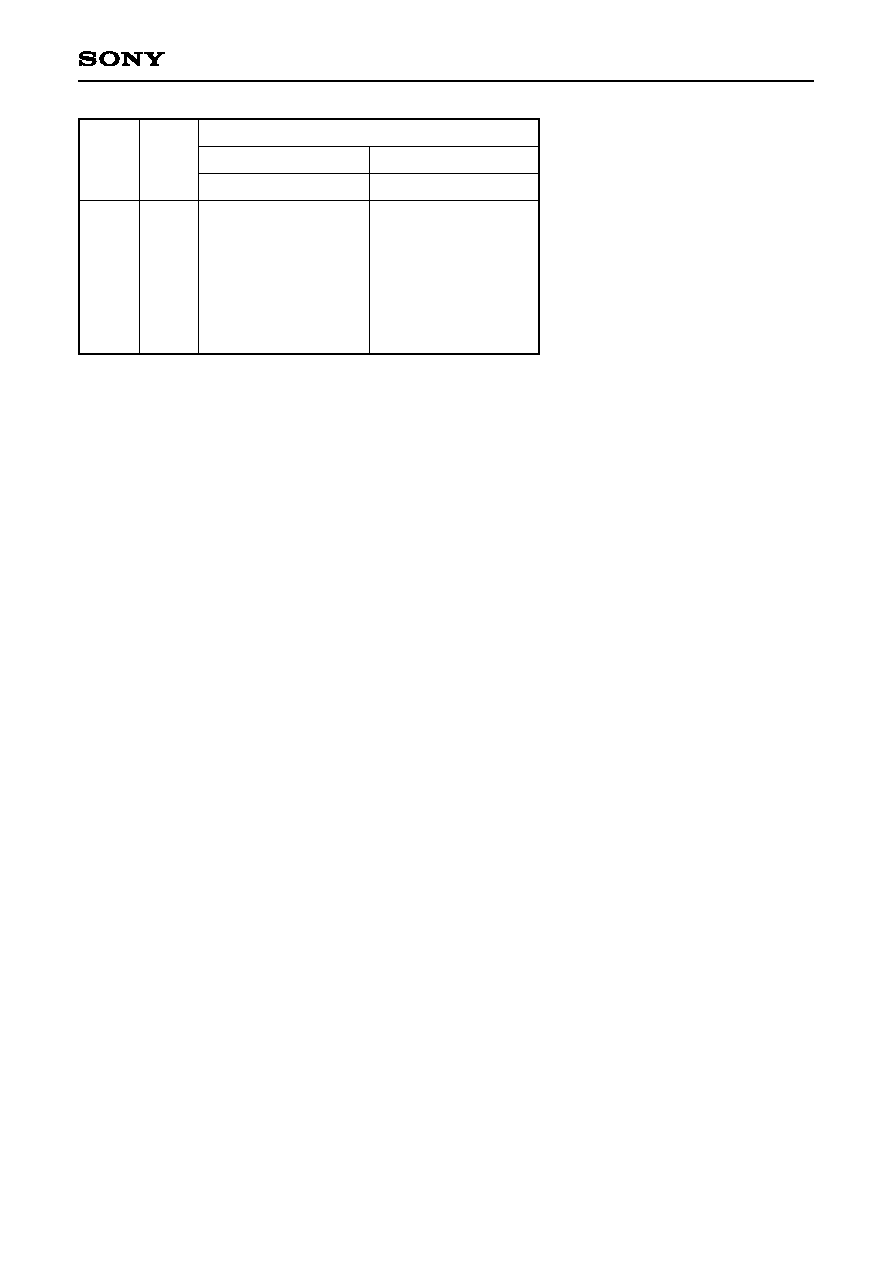

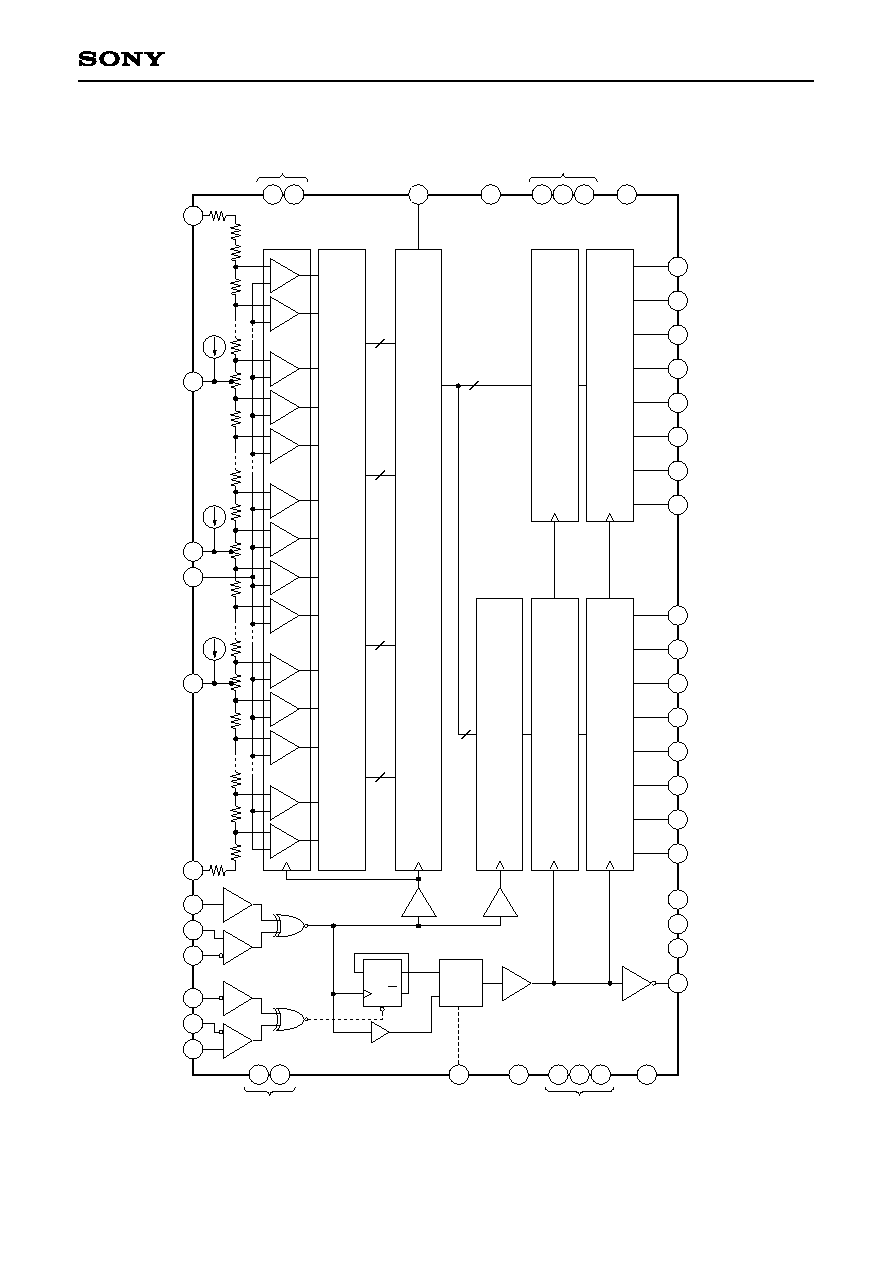

CXA3246Q

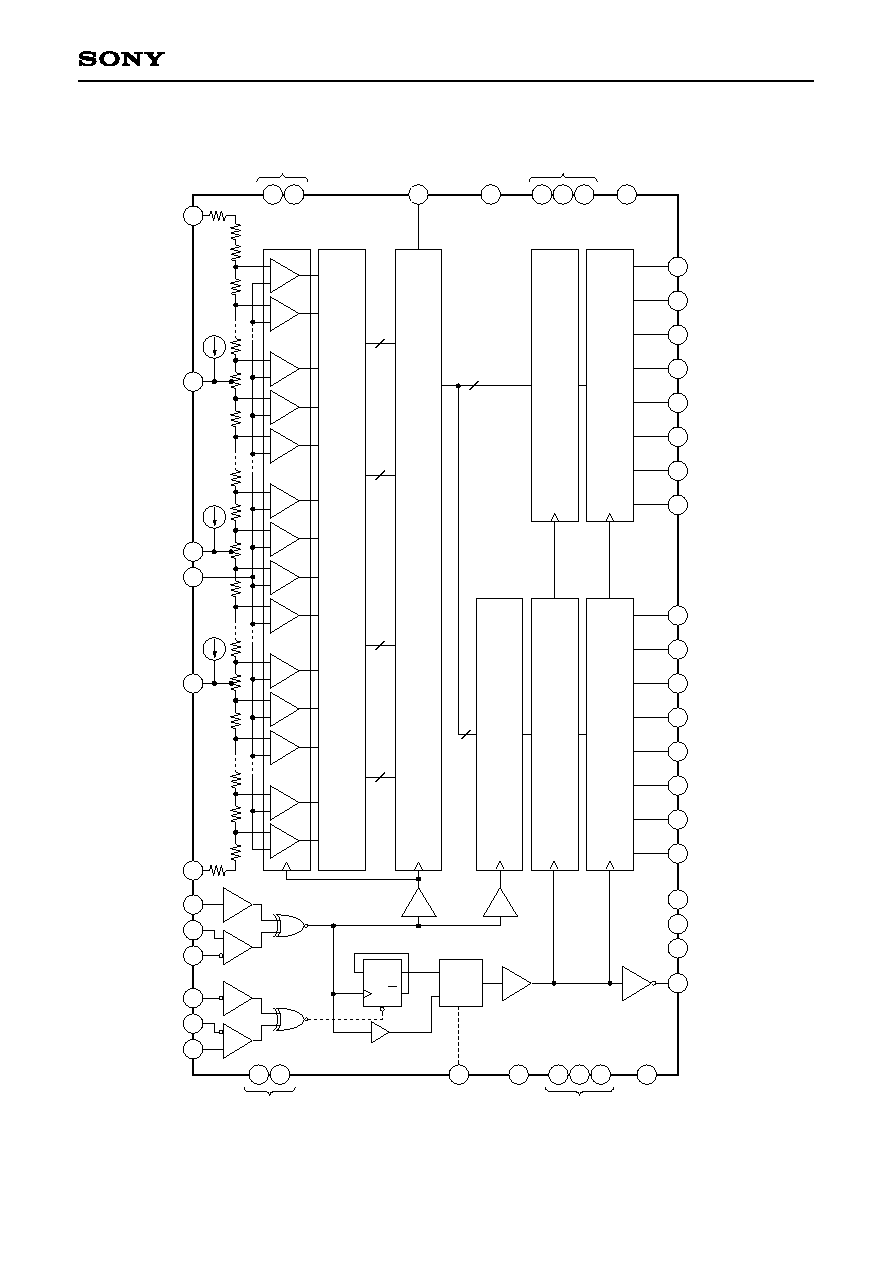

Block Diagram

6bit

V

RT

2

3

5

8

10

12

13

14

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

40

39

38

37

36

35

34

31

32

33

41

42

44

1

1

2

r

/2

63

64

∑

∑

∑

65

126

127

∑

∑

∑

128

129

191

192

∑

∑

∑

193

254

255

∑

∑

∑

r

6bit

9

7

4

r

1

r

2

r

r

r

r

r

r

r

r

r

r

r

r

r

r

/2

6bit

6bit

8bit

8bit

15

46

47

48

Select

D

Q

Q

45

SELECT

11

43

DGND1

DV

EE

3

DGND2

AGND

AV

CC

DV

CC

2

DV

CC

1

INV

DGND3

VRM3

V

IN

VRM2

6

V

RB

VRM1

CLK/T

CLK/E

CLKN/E

RESETN/T

RESETN/E

RESET/E

CLKOUT

PAD0

PAD1

PAD2

PAD3

PAD4

PAD5

PAD6

PAD7

PBD0

PBD1

PBD2

PBD3

PBD4

PBD5

PBD6

PBD7

T

T

L

O

U

T

L

A

T

C

H

A

T

T

L

O

U

T

L

A

T

C

H

B

6

b

i

t

L

A

T

C

H

+

E

N

C

O

D

E

R

E

N

C

O

D

E

R

(LSB)

(MSB)

(LSB)

(MSB)

L

A

T

C

H

B

N.C.

N.C.

N.C.

≠ 5 ≠

CXA3246Q

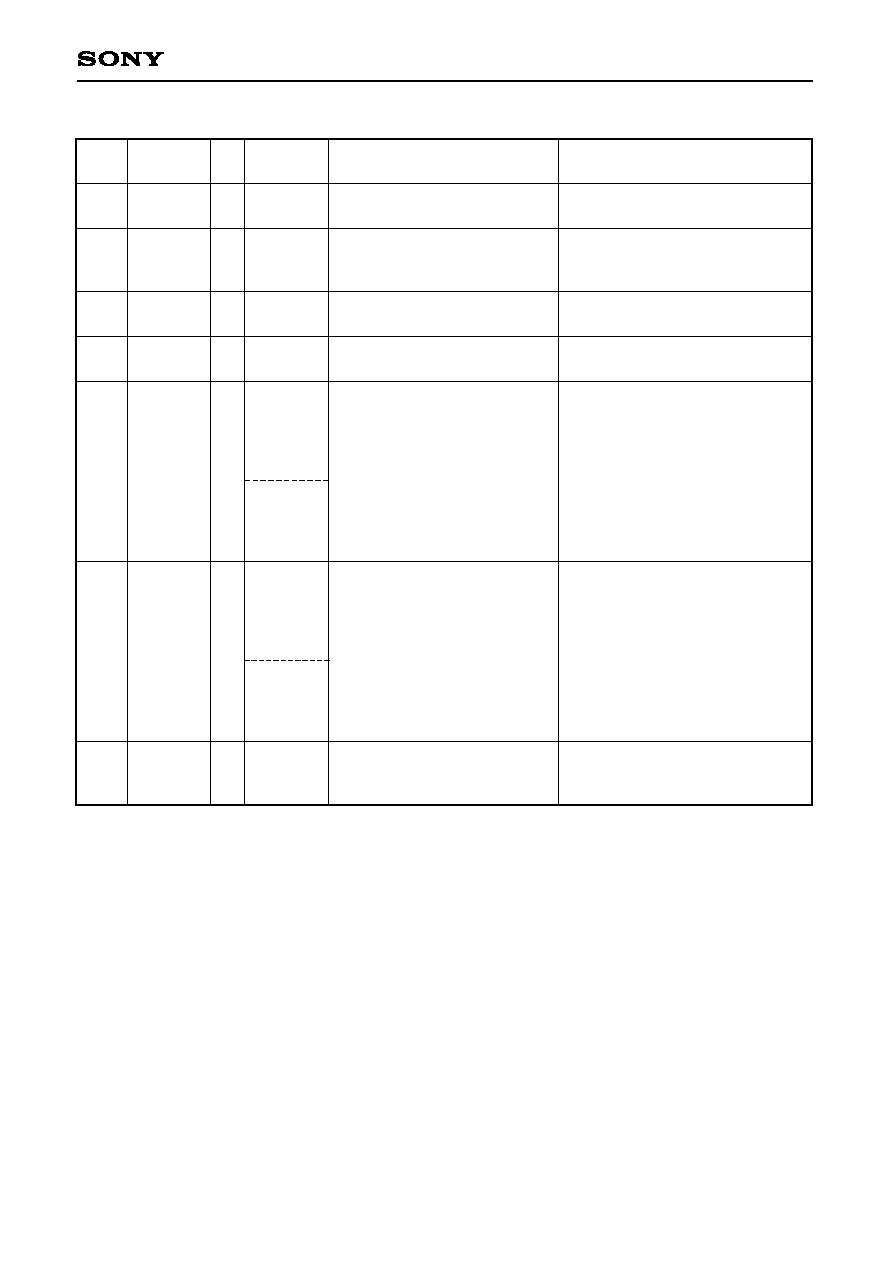

Pin Description and I/O Pin Equivalent Circuit

Analog ground.

Separated from the digital ground.

Analog power supply.

Separated from the digital power

supply.

Digital ground.

Digital power supply.

Digital power supply.

Ground for ECL input.

+5V for PECL and TTL inputs.

Digital power supply.

≠5V for ECL input.

Ground for PECL and TTL inputs.

No connected pin.

Not connected with the internal

circuits.

N.C.

16, 17

18

3, 10

5, 8

20, 29

32, 41

19, 30

31, 42

12

1

AGND

AV

CC

DGND1

DGND2

DV

CC

1

DV

CC

2

DGND3

DV

EE

3

GND

+5V

(typ.)

GND

+5V

(typ.)

+5V (typ.)

(With a

single

power

supply)

GND

(With dual

power

supply)

GND

(With a

single

power

supply)

≠5V (typ.)

(With dual

power

supply)

Pin

No.

Symbol

I/O

Standard

voltage level

Equivalent circuit

Description

≠ 6 ≠

CXA3246Q

Pin

No.

15

CLK/T

Clock input.

46

RESETN/T

TTL

TTL

Vcc

or

GND

Reset signal input.

When left open, this pin goes to high

level. When set to low level, the

built-in CLK frequency divider circuit

can be reset.

44

INV

Data output polarity inversion input.

When left open, this input goes to

high level.

(See Table 1. I/O Correspondence

Table.)

45

SELECT

Data output mode selection.

(See Table 2. Operation Mode

Table.)

Symbol

Standard

voltage level

Equivalent circuit

Description

15 46

DV

CC

1

DGND1

DV

EE

3

44

45

or

,

1.5V

I

I

I

I/O

Clock input.

CLK/E complementary input.

When left open, this pin goes to the

threshold voltage.

Only CLK/E can be used for

operation, but complementary inputs

are recommended to attain fast and

stable operation.

Reset signal input.

When set to low level, the built-in

CLK frequency divider circuit can be

reset.

RESETN/E complementary input.

When left open, this pin goes to the

threshold voltage. Only RESETN/E

can be used for operation.

ECL/

PECL

13

14

48

47

CLK/E

CLKN/E

RESETN/E

RESET/E

I

I

I

I

13

14

48

47

DGND3

DV

EE

3

≠ 7 ≠

CXA3246Q

4.0V

(typ.)

11

V

RT

Top reference voltage.

By-pass to AGND with a 1µF tantal

capacitor and a 0.1µF chip capacitor.

V

RB

+

(V

RT

≠ V

RB

)

9

V

RM

3

Reference voltage mid point.

By-pass to AGND with a 0.1µF chip

capacitor.

7

V

RM

2

Reference voltage mid point.

By-pass to AGND with a 0.1µF chip

capacitor.

4

V

RM

1

Reference voltage mid point.

By-pass to AGND with a 0.1µF chip

capacitor.

2.0V

(typ.)

2

V

RB

Bottom reference voltage.

By-pass to AGND with a 1µF tantal

capacitor and a 0.1µF chip capacitor.

r

1

r

/2

Comparator 1

Comparator 63

Comparator 64

Comparator 128

Comparator 191

Comparator 127

Comparator 192

Comparator 255

r

r

2

r

/2

r

r

r

r

4

7

9

2

11

r

I

I

4

3

4

2

V

RB

+

(V

RT

≠ V

RB

)

4

1

V

RB

+

(V

RT

≠ V

RB

)

Pin

No.

Symbol

I/O

Standard

voltage level

Equivalent circuit

Description

Clock output.

(See Table 2. Operation Mode Table.)

TTL output; the high level is

clamped to approximately 2.8V.

21

to

28

PAD0

to

PAD7

Port A side data output.

TTL output; the high level is

clamped to approximately 2.8V.

33

to

40

PBD0

to

PBD7

43

CLKOUT

Port B side data output.

TTL output; the high level is

clamped to approximately 2.8V.

6

V

IN

V

RT

to

V

RB

I

TTL

O

O

O

Analog input.

AV

CC

Comparator

Vref

AGND

DV

EE

3

AV

CC

6

DV

CC

2

DGND2

DV

CC

1

DGND1

1

0

0

k

D

VEE

3

21

28

33

40

43

to

to

≠ 8 ≠

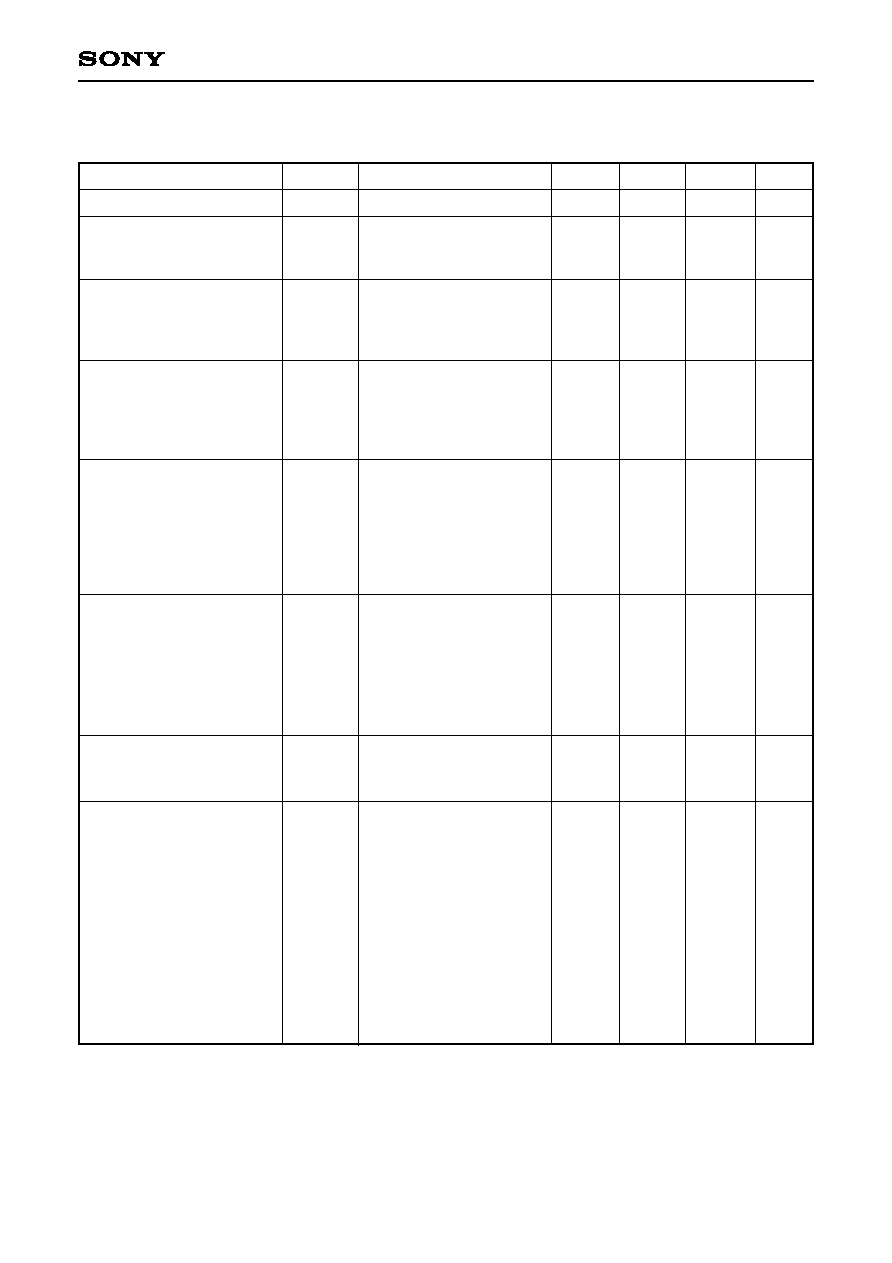

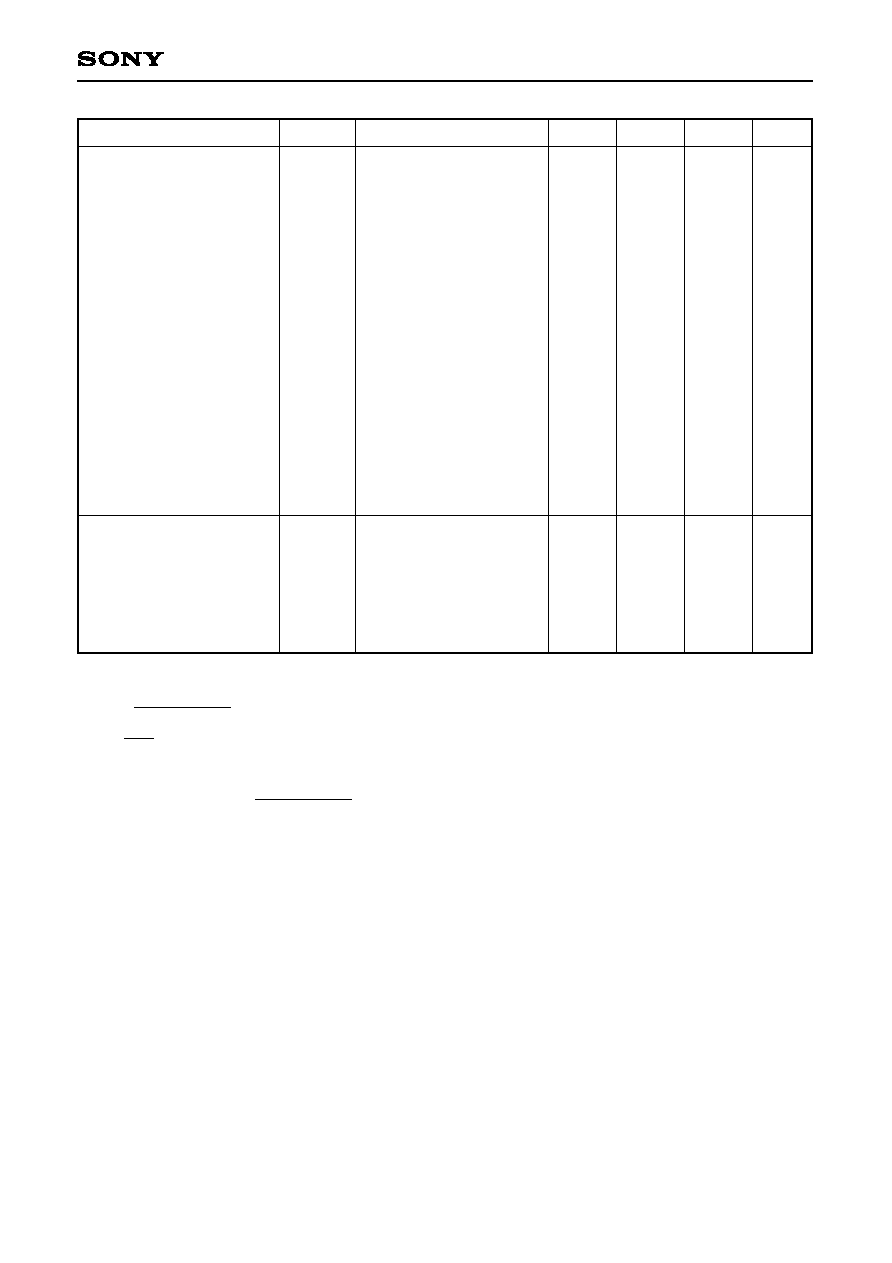

CXA3246Q

Resolution

DC characteristics

Integral linearity error

Differential linearity error

Analog input

Analog input capacitance

Analog input resistance

Analog input current

Reference input

Reference resistance

Reference current

Offset voltage V

RT

side

V

RB

side

Digital input (ECL, PECL)

Digital input voltage: High

: Low

Threshold voltage

Digital input current : High

: Low

Digital input capacitance

Digital input (TTL)

Digital input voltage: High

: Low

Threshold voltage

Digital input current : High

: Low

Digital input capacitance

Digital output (TTL)

Digital output voltage : High

: Low

Switching characteristics

Maximum conversion rate

Aperture jitter

Sampling delay

Clock high pulse width

Clock low pulse width

Reset signal setup time

Reset signal hold time

Clock output delay

Data output delay

Output rise time

Output fall time

Electrical Characteristics

(AV

CC

, DV

CC

1, 2, DGND3 = +5V, AGND, DGND1, 2, DV

EE

3 = 0V, V

RT

= 4V, V

RB

= 2V, Ta = 25∞C)

Item

Symbol

Min.

Typ.

Max.

Unit

Conditions

E

IL

E

DL

C

IN

R

IN

I

IN

Rref

2

Iref

3

EOT

EOB

V

IH

V

IL

V

TH

I

IH

I

IL

V

IH

V

IL

V

TH

I

IH

I

IL

V

OH

V

OL

Fc

Taj

Tds

Tpw1

Tpw0

T_rs

T_rh

Td_clk

Tdo1

Tdo2

Tr

Tf

7

0

400

2.7

6

0

DV

EE

3 + 1.5

DV

EE

3 + 1.1

≠50

≠50

2.0

≠10

≠20

2.4

120

1.2

3.0

4.5

1.0

≠0.5

3.0

3.5

8

10

20

100

600

3.3

8

1.5

DGND3 ≠ 1.2

1.5

10

1.4

4.5

T

4

+ 0.5

5.0

1

1

±0.5

±0.5

40

285

740

5.0

10

3

DGND3

V

IH

≠ 0.4

20

20

5

0.8

5

0

5

0.5

1.6

7.0

7.5

bits

LSB

LSB

pF

k

µA

mA

mV

mV

V

V

V

µA

µA

pF

V

V

V

µA

µA

pF

V

V

MSPS

ps

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

V

IN

= 2Vp-p, Fc = 5MSPS

V

IN

= +3.0V + 0.07Vrms

V

IH

= DGND3 ≠ 0.8V

V

IL

= DGND3 ≠ 1.6V

V

IH

= 3.5V

V

IL

= 0.2V

I

OH

= ≠2mA

I

OL

= 1mA

DMUX mode

CLK

CLK

RESETN ≠ CLK

RESETN ≠ CLK

(C

L

= 5pF)

DMUX mode

(C

L

= 5pF)

(C

L

= 5pF)

0.8 to 2.0V

(C

L

= 5pF)

0.8 to 2.0V

(C

L

= 5pF)

These characteristics are for PECL input unless otherwise specified.

≠ 9 ≠

CXA3246Q

4

T =

5

TPS: Times Per Sample

6

Pd = (I

CC

+ I

EE

) ∑ V

CC

+

(V

RT

≠ V

RB

)

2

Rref

Dynamic characteristics

Input bandwidth

S/N ratio

Error rate

Power supply

Supply current

AVcc Pin supply current

DVcc1 pin supply current

DVcc2 pin supply current

DGND3 pin supply current

Power consumption

I

CC

+ I

EE

AI

CC

DI

CC

1

DI

CC

2

I

EE

Pd

6

250

70

45

20

5

0.5

400

46

42

98

500

10

≠12

10

≠9

10

≠9

140

87

36

15

1.5

700

MHz

dB

dB

TPS

5

TPS

TPS

mA

mA

mA

mA

mA

mW

V

IN

= 2Vp-p, ≠3dB

Fc = 120MSPS,

fin = 1kHz Fs

DMUX mode

Fc = 120MSPS,

fin = 29.999MHz Fs

DMUX mode

Fc = 120MSPS,

fin = 1kHz Fs

DMUX mode

Error > 16LSB

Fc = 120MSPS,

fin = 29.999MHz Fs

DMUX mode

Error > 16LSB

Fc = 100MSPS,

fin = 24.999MHz Fs

Straight mode

Error > 16LSB

{

{

{

{

{

1

Fc

Item

Symbol

Min.

Typ.

Max.

Unit

Conditions

2

Rref: Resistance value between V

RT

and V

RB

3

Iref =

V

RT

≠ V

RB

Rref

≠ 10 ≠

CXA3246Q

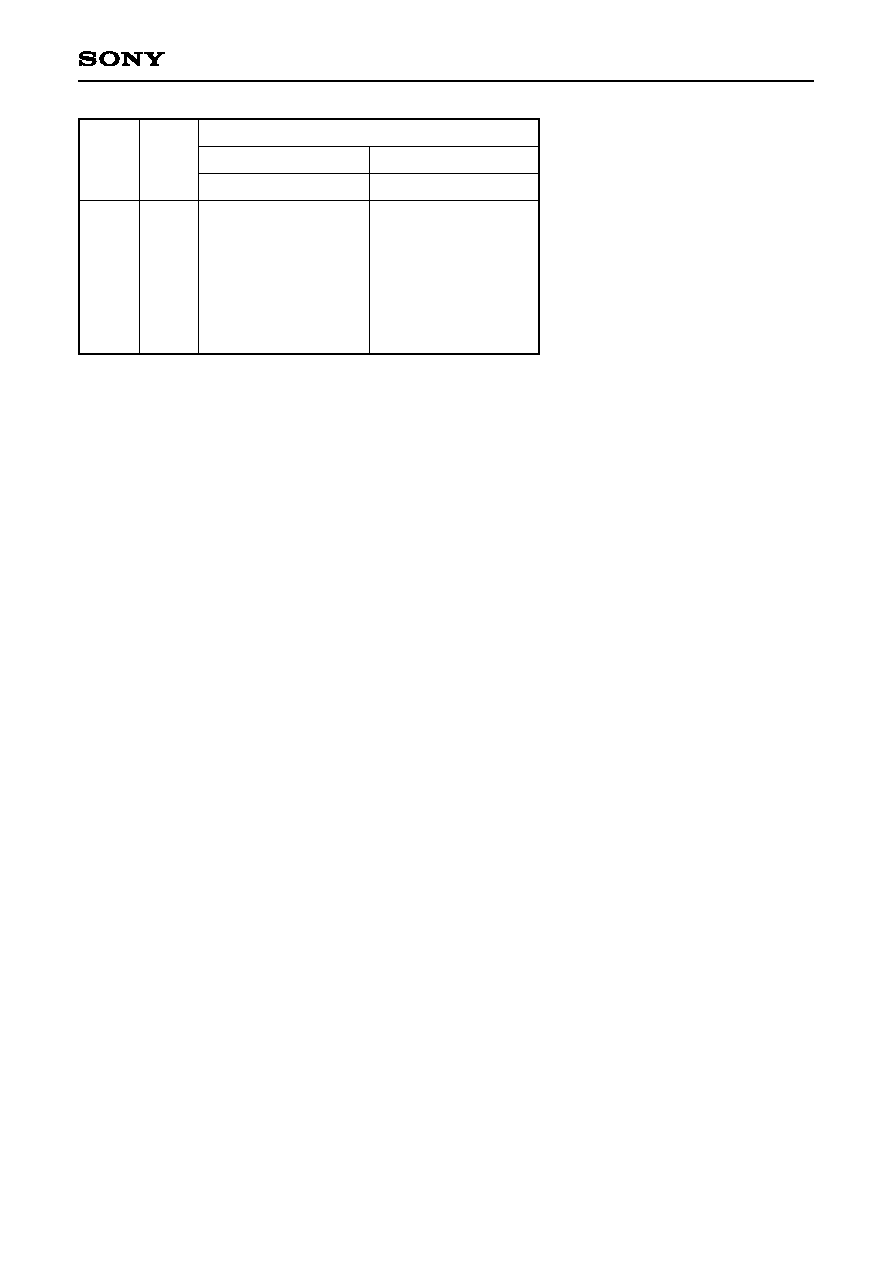

Table 1. I/O Correspondence Table

INV

1

D7

D0

D7

D0

0

V

IN

V

RT

V

RM

2

V

RB

255

254

.

.

.

128

127

.

.

.

1

0

1 1 1 1 1 1 1 1

1 1 1 1 1 1 1 0

.

.

.

1 0 0 0 0 0 0 0

0 1 1 1 1 1 1 1

.

.

.

0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1

.

.

.

0 1 1 1 1 1 1 1

1 0 0 0 0 0 0 0

.

.

.

1 1 1 1 1 1 1 0

1 1 1 1 1 1 1 1

Step

≠ 11 ≠

CXA3246Q

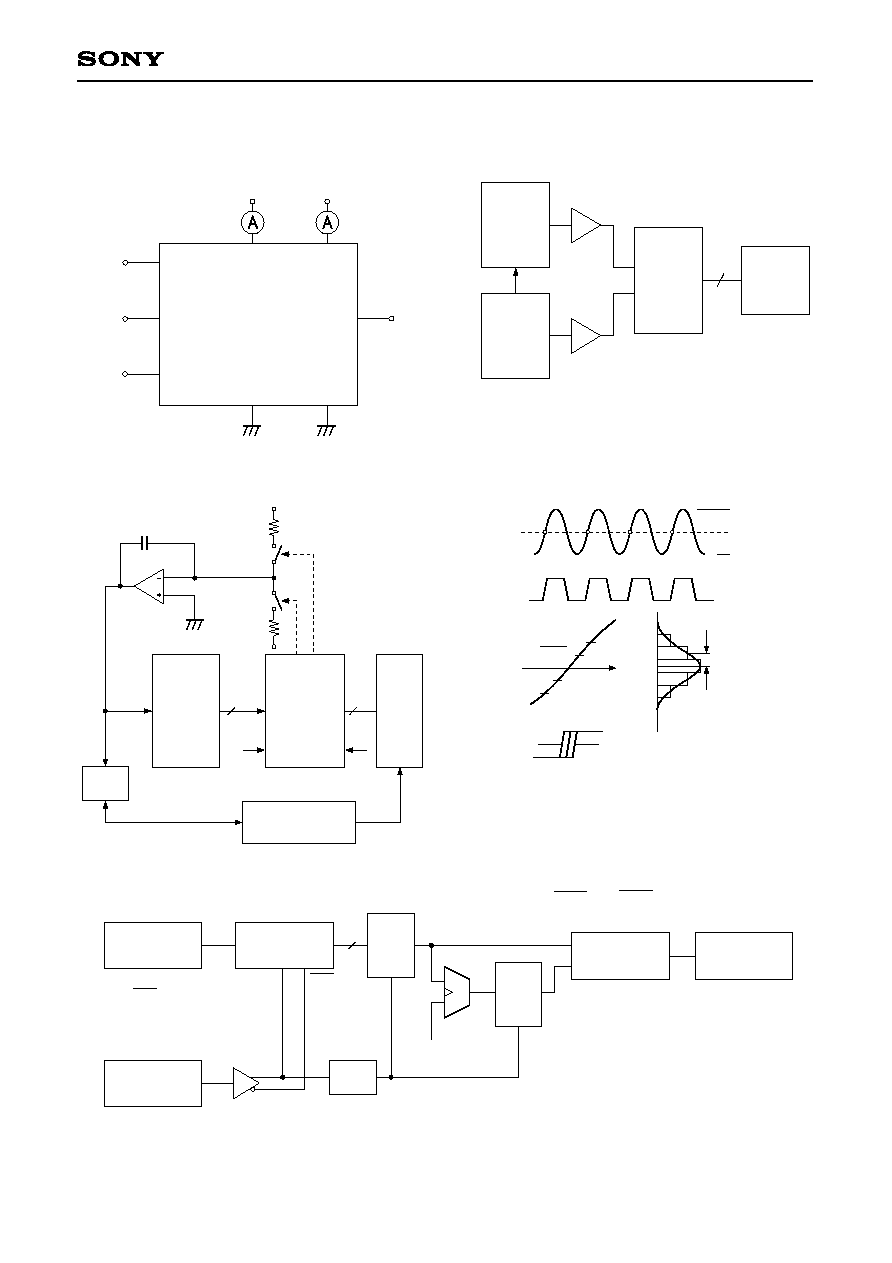

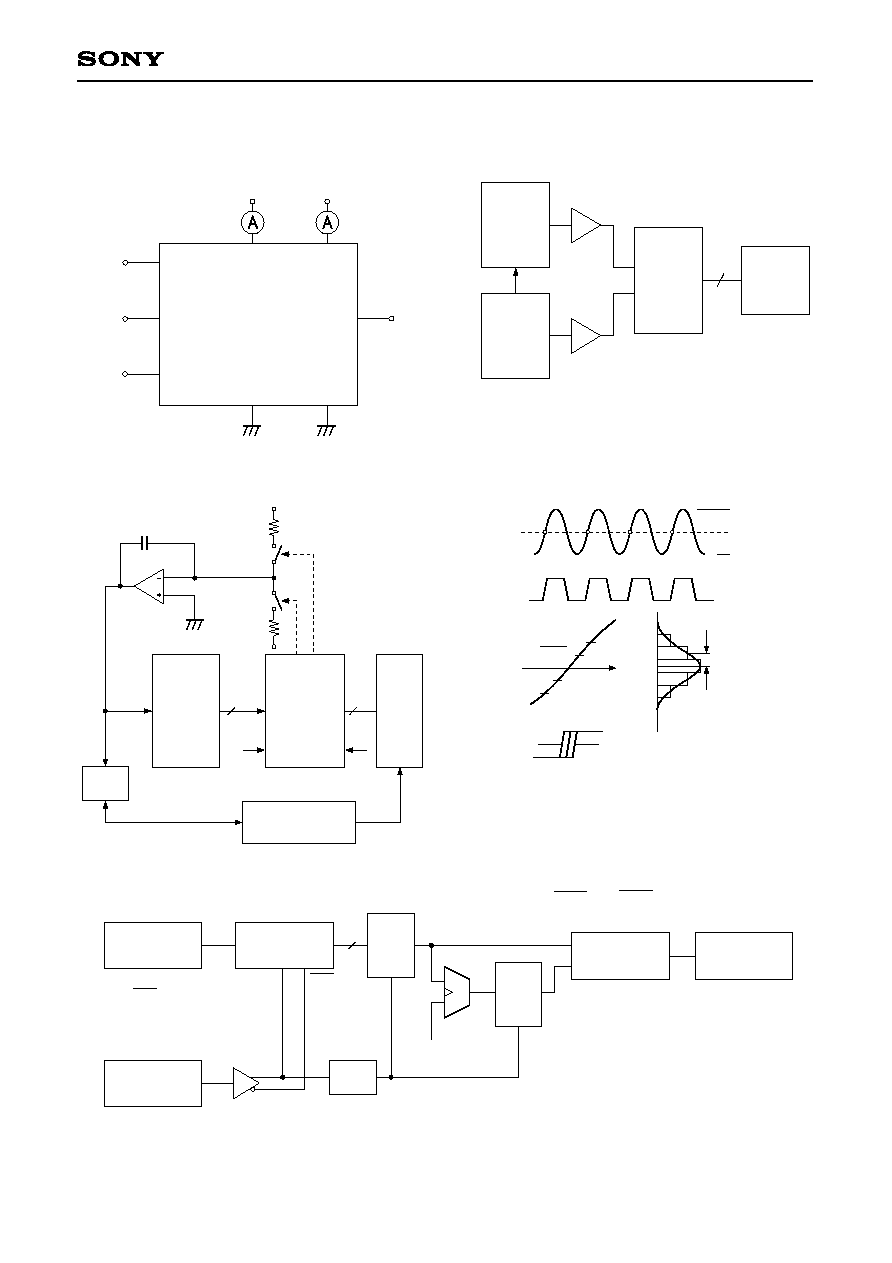

Electrical Characteristics Measurement Circuit

Current Consumption Measurement Circuit

V

RT

V

IN

V

RB

AV

CC

DV

CC

1

DV

CC

2

DGND3

DGND2

DGND1

AGND

CLK/E

DV

EE

3

5MHz PECL

4V

1.95V

2V

5V

5V

Icc

I

EE

Integral Linearity Error Measurement Circuit

Differential Linearity Error Measurement Circuit

CXA3246Q

A < B A > B

Comparator

A8

to

A1

A0

B8

to

B1

B0

Buffer

Controller

DVM

8

8

"1"

"0"

000∑∑∑00

to

111∑∑∑10

V

IN

+V

≠V

S2

S1

S1: ON when A < B

S2: ON when A > B

Sampling Delay Measurement Circuit

Aperture Jitter Measurement Circuit

CXA3246Q

OSC1

: Variable

OSC2

Logic

Analizer

100MHz

100MHz

Amp

ECL

Buffer

CLK

V

IN

8

fr

1024

samples

Aperture Jitter Measurement Method

V

IN

CLK

V

IN

CLK

V

RT

V

RM

2

V

RB

129

128

127

126

125

Sampling timing fluctuation

(= aperture jitter)

(LSB)

t

Error Rate Measurement Circuit

Comparator

A > B

Pulse

Counter

CXA3246Q

Signal

Source

Latch

Latch

1/8

+

Signal

Source

Fc

4

≠ 1kHz

2Vp-p Sine Wave

Fc

V

IN

CLK

CLK

8

16LSB

A

B

Where

(LSB) is the deviation of the output codes when

the largest slew rate point is sampled at the clock which

has exactly the same frequency as the analog input

signal, the aperture jitter Taj is:

Taj =

/ =

/ ( )

t

2

256

◊

2

f

≠ 12 ≠

CXA3246Q

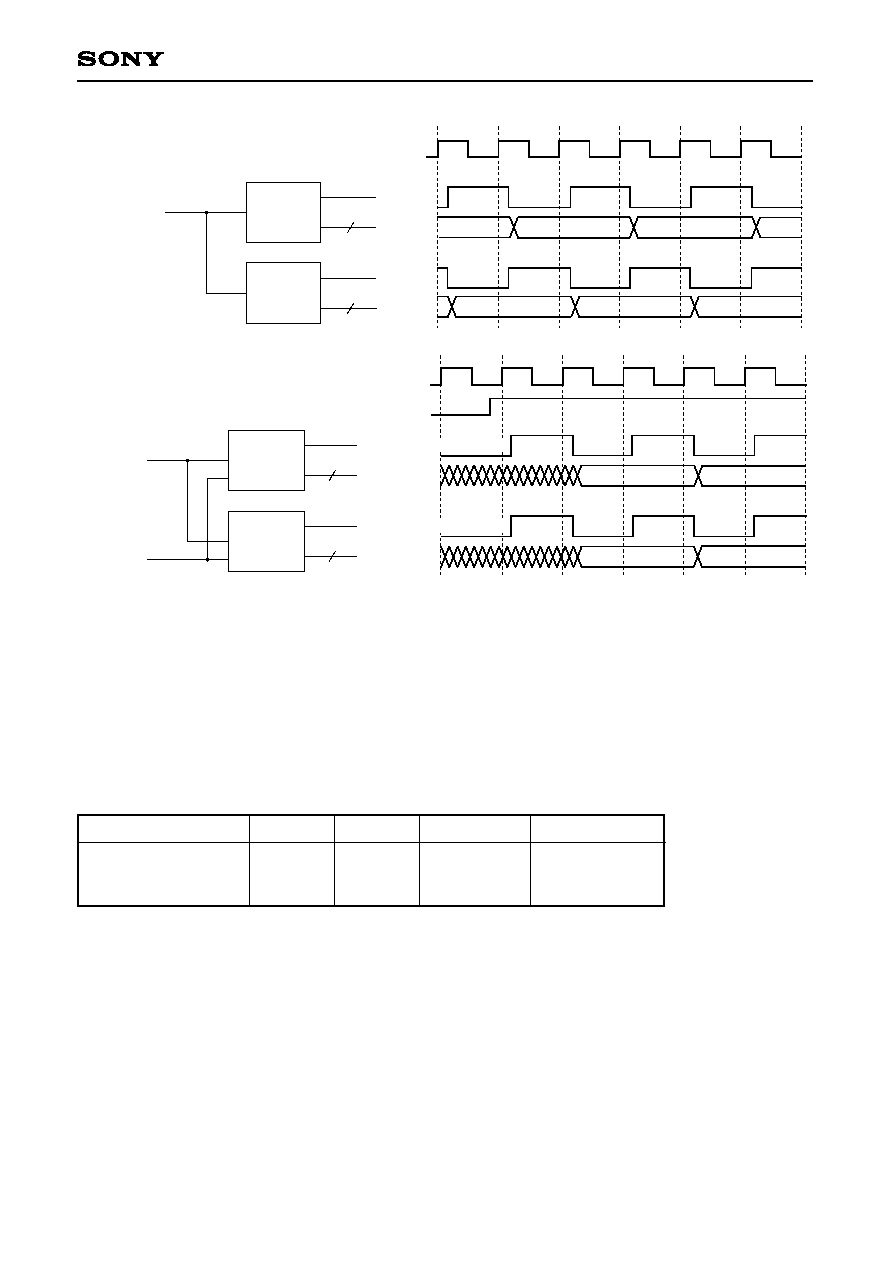

Description of Operation Modes

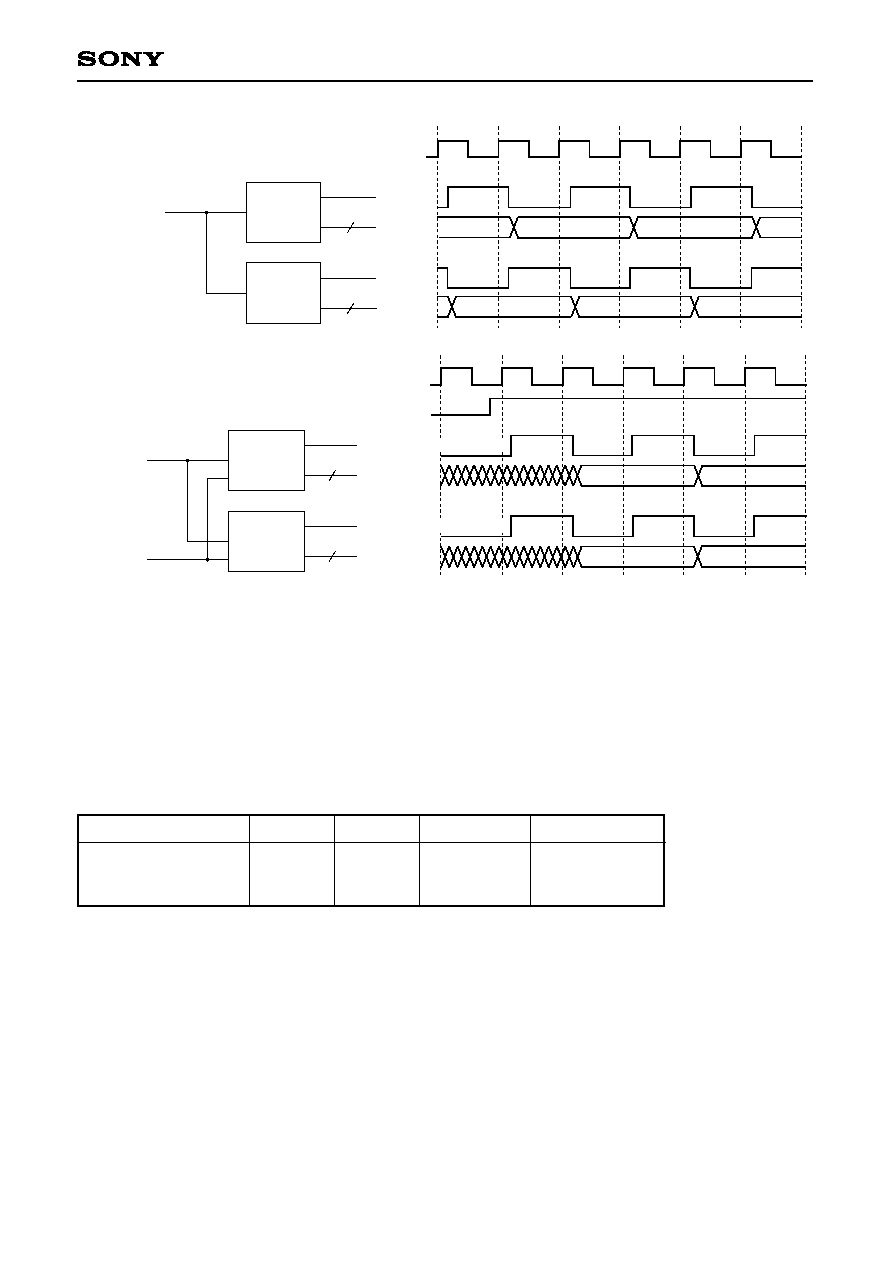

The CXA3246Q has two types of operation modes which are selected with Pin 45 (SELECT).

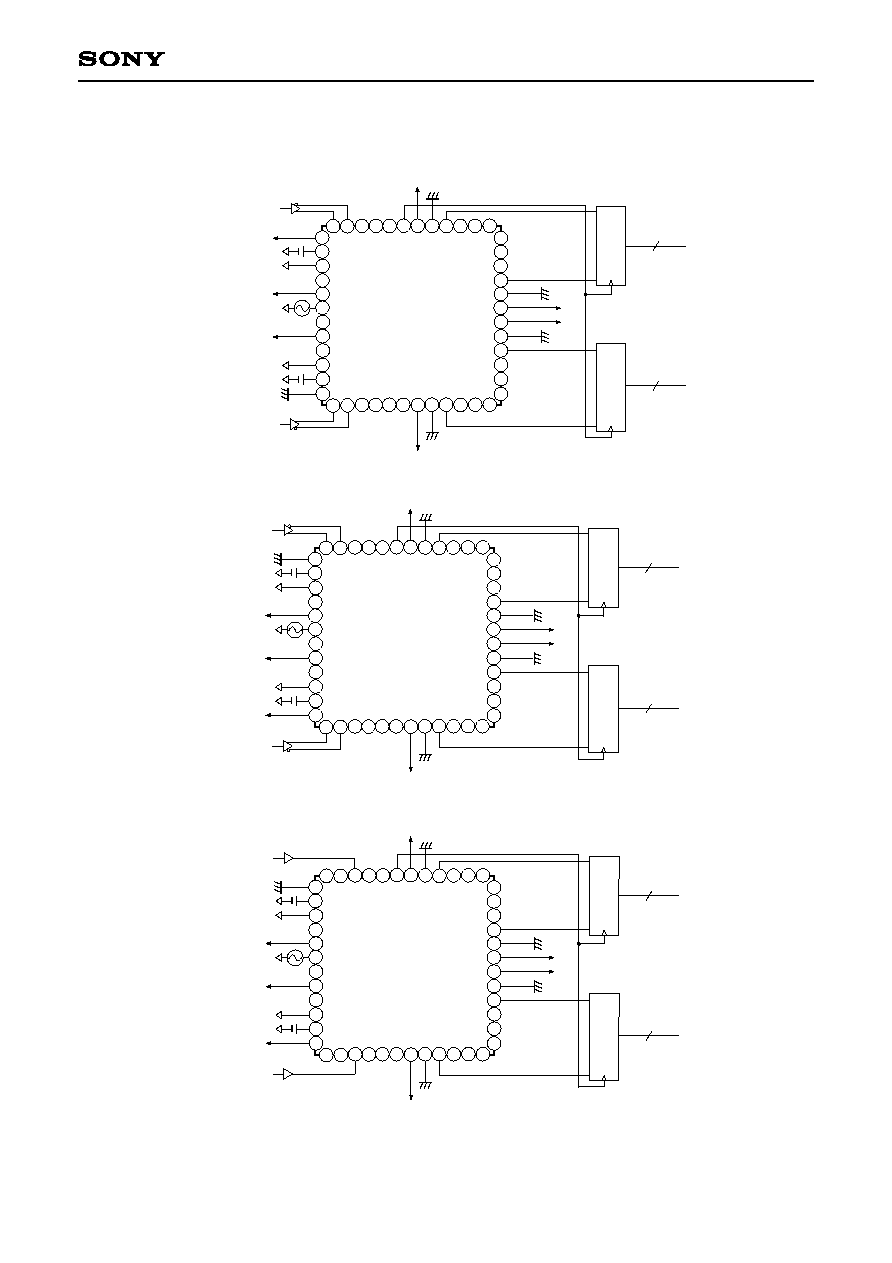

1. DMUX mode (See Application Circuit 1-(1), (2) and (3).)

Set the SELECT pin to Vcc for this mode. In this mode, the clock frequency is divided by 2 in the IC, and the

data is output after being demultiplexed by this 1/2 frequency-divided clock. The 1/2 frequency-divided clock,

which has adequate setup time and hold time for the output data, is output from the clock output pin.

When using the multiple CXA3246Q in DMUX mode, the start timing of the 1/2 frequency-divided clocks

becomes out of phase, producing operation such as that shown in the example on the next page. As a

countermeasure, the CXA3246Q has a function that resets the 1/2 frequency-divided clocks.

When resetting this 1/2 frequency-divided clock, the low level of the reset signal should be input to the

RESETN pin (Pin 46 or 48). The reset signal requires the setup time (T_rs

1.0ns) and hold time (T_rh

≠0.5ns) to the clock rising edge because it is synchronized with and taken in the clock.

The reset period can be extended by making the low level period of the reset signal longer because the clock

output pin is fixed to low (reset) during the low level period at the clock rising edge. If the reset start timing is

regarded as not important, the timing where the reset signal is set from high to low is not so consequence.

However, when the reset is released the timing where the reset signal is set from low to high must become

significant because the timing is used to commence the 1/2 frequency-divided clock. In this case, the setup

time (T_rs) is also necessary.

See the timing chart for detail. (This chart shows the example of reset for 2T.)

The A/D converter can operate at Fc (min.) = 120MSPS in this mode.

Table 2. Operation Mode Table

SELECT

pin

V

CC

GND

DMUX mode

Straight mode

120MSPS

100MSPS

Demultiplexed output

60Mbps

Straight output

100Mbps

The input clock is 1/2 frequency divided

and output.

60MHz

The input clock is inverted and output.

100MHz

Operation

mode

Maximum

conversion rate

Data output

Clock output

≠ 13 ≠

CXA3246Q

8bit

CLKOUT

DATA

8bit

CLKOUT

DATA

CLK

A

B

CLK

CXA3246Q

CXA3246Q

CLK

RESETN

CLK

RESETN

A

B

8bit

CLKOUT

DATA

8bit

CLKOUT

DATA

CLK

CXA3246Q

CXA3246Q

A

B

CLK

RESETN

CLK

RESETN

CLK

Reset signal

Reset signal

(Reset period)

(Reset period)

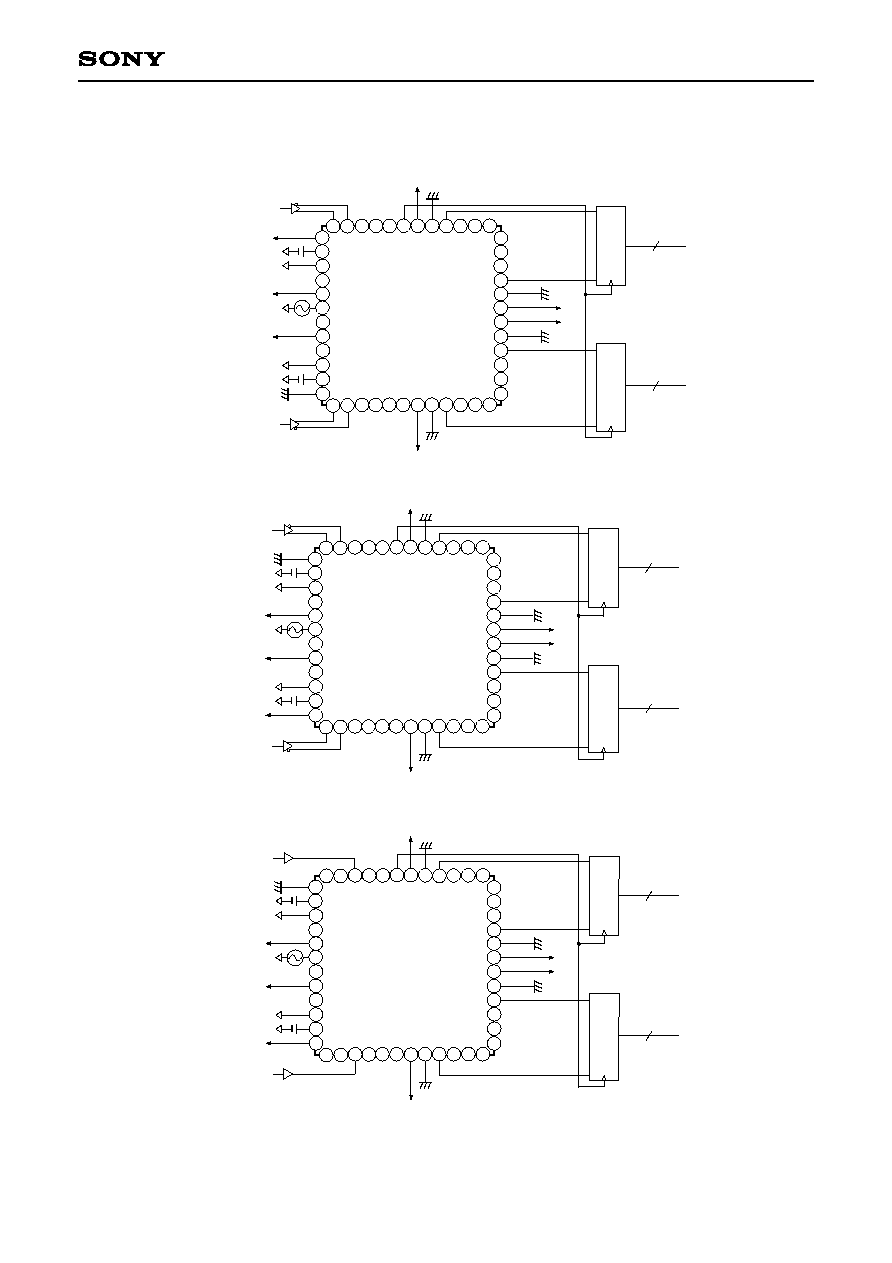

2. Straight mode (See Application Circuits 1-(4), (5) and (6).)

Set the SELECT pin to GND for this mode. In this mode, data output can be obtained in accordance with the

clock frequency applied to the A/D converter for applications which use the clock applied to the A/D converter

as the system clock.

The A/D converter can operate at Fc (min.) = 100MSPS in this mode.

Digital input level and supply voltage settings

The logic input level for the CXA3246Q supports ECL, PECL and TTL levels.

The power supplies (DV

EE

3, DGND3) for the logic input block must be set to match the logic input (CLK and

reset signals) level.

Digital input level

ECL

PECL

TTL

≠5V

0V

0V

0V

+5V

+5V

±5V

+5V

+5V

(1) (4)

(2) (5)

(3) (6)

DV

EE

3

DGND3

Supply voltage Application circuits

Table 3. Logic Input Level and Power Supply Settings

When the reset signal is not used

When the reset signal is used

≠ 14 ≠

CXA3246Q

Application Circuit 1

(1) DMUX ECL input

+5V(D)

DG

≠

5

V

(

D

)

A

G

D

G

+

5

V

(

A

)

4

V

+5V(D)

DG

8 bit Digital Data

Latch

8 bit Digital Data

Latch

PBD0 to PBD7

8 bit Digital Data

PAD0 to PAD7

8 bit Digital Data

ECL RESET signal

ECL-CLK

D

G

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

25

26

27

28

29

30

40 39 38 37

36

35

34

31

32

33

41

42

43

44

45

46

47

48

1

D

G

+

5

V

(

D

)

2

V

+

5

V

(

A

)

2

A

G

A

G

A

G

A

G

(2) DMUX PECL input

+5V(D)

DG

+5V(D)

DG

8 bit Digital Data

Latch

8 bit Digital Data

Latch

PBD0 to PBD7

8 bit Digital Data

PAD0 to PAD7

8 bit Digital Data

PECL-CLK

D

G

3

4

5

6

7

8

9

10

11

13 14 15 16 17 18 19 20 21 22 23 24

25

26

27

28

29

30

40 39 38 37

36

35

34

31

32

33

41

42

43

44

45

46

47

48

1

D

G

+

5

V

(

D

)

2

+

5

V

(

D

)

A

G

D

G

+

5

V

(

A

)

4

V

2

V

+

5

V

(

A

)

A

G

A

G

A

G

A

G

PECL RESET signal

12

(3) DMUX TTL input

+5V(D)

DG

A

G

A

G

+

5

V

(

A

)

4

V

+5V(D)

DG

8 bit Digital Data

Latch

8 bit Digital Data

Latch

PBD0 to PBD7

8 bit Digital Data

PAD0 to PAD7

8 bit Digital Data

TTL RESET signal

TTL-CLK

D

G

3

4

5

6

7

8

9

10

11

13 14 15 16 17 18 19 20 21 22 23 24

25

26

27

28

29

30

40 39 38 37

36

35

34

31

32

33

41

42

43

44

45

46

47

48

1

D

G

+

5

V

(

D

)

2

V

A

G

+

5

V

(

A

)

2

+

5

V

(

D

)

D

G

A

G

A

G

12

≠ 15 ≠

CXA3246Q

(4) Straight ECL input

+5V(D)

DG

+5V(D)

DG

8-bit Digital Data

Latch

PBD0 to PBD7

8-bit Digital Data

ECL-CLK

D

G

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

25

26

27

28

29

30

40 39 38 37

36

35

34

31

32

33

41

42

43

44

46

47

48

1

D

G

+

5

V

(

D

)

2

ECL

TTL

DG

45

A

G

A

G

+

5

V

(

A

)

4

V

2

V

A

G

+

5

V

(

A

)

≠

5

V

(

D

)

D

G

A

G

A

G

(5) Straight PECL input

+5V(D)

DG

+5V(D)

DG

8-bit Digital Data

Latch

PBD0 to PBD7

8-bit Digital Data

PECL-CLK

D

G

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

25

26

27

28

29

30

40 39 38 37

36

35

34

31

32

33

41

42

43

44

46

47

48

1

D

G

+

5

V

(

D

)

2

PECL

TTL

DG

45

A

G

A

G

+

5

V

(

A

)

4

V

2

V

A

G

+

5

V

(

A

)

+

5

V

(

D

)

D

G

A

G

A

G

(6) Straight TTL input

+5V(D)

DG

+5V(D)

DG

8-bit Digital Data

Latch

PBD0 to PBD7

8-bit Digital Data

TTL-CLK

D

G

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

25

26

27

28

29

30

40 39 38 37

36

35

34

31

32

33

41

42

43

44

46

47

48

1

D

G

+

5

V

(

D

)

2

DG

45

A

G

A

G

+

5

V

(

A

)

4

V

2

V

A

G

+

5

V

(

A

)

+

5

V

(

D

)

D

G

A

G

A

G

≠ 16 ≠

CXA3246Q

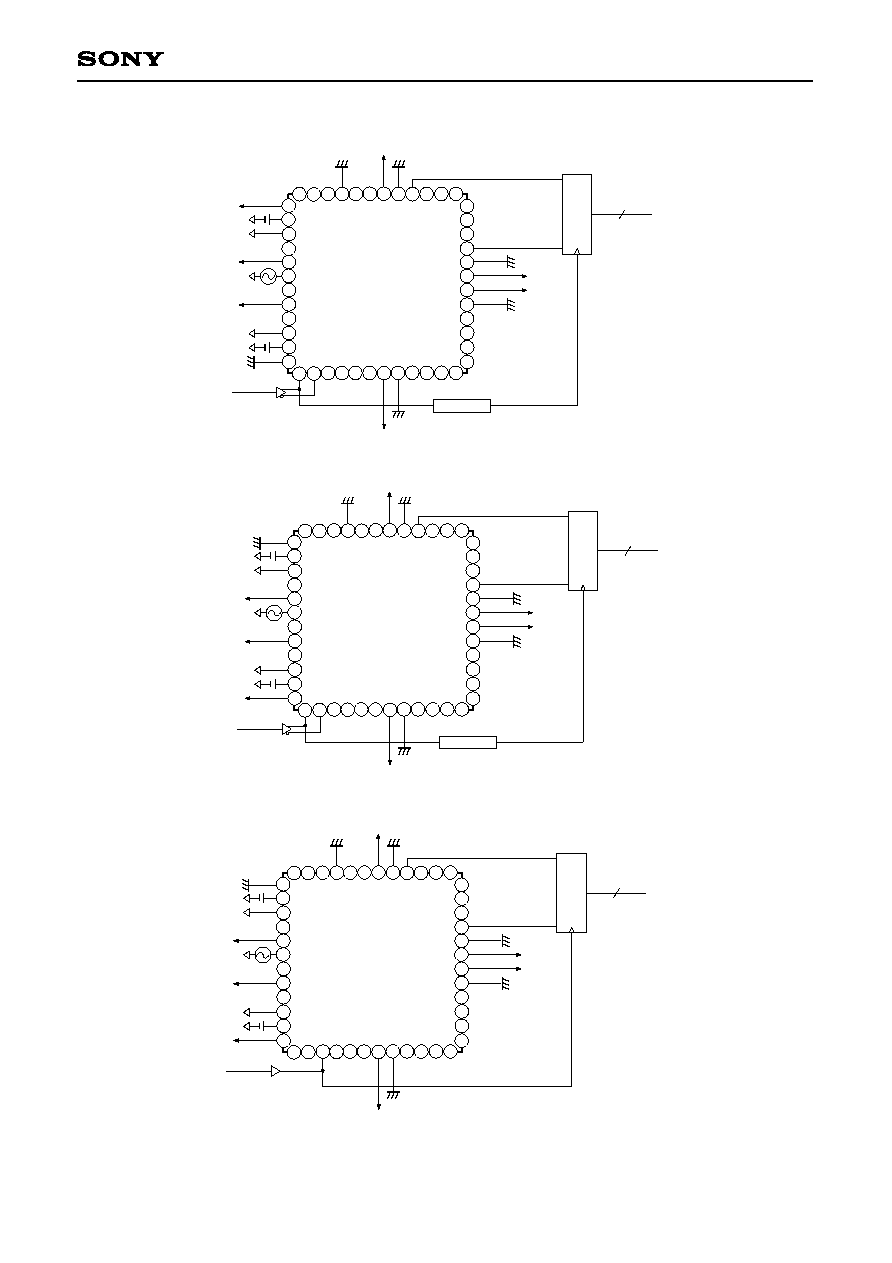

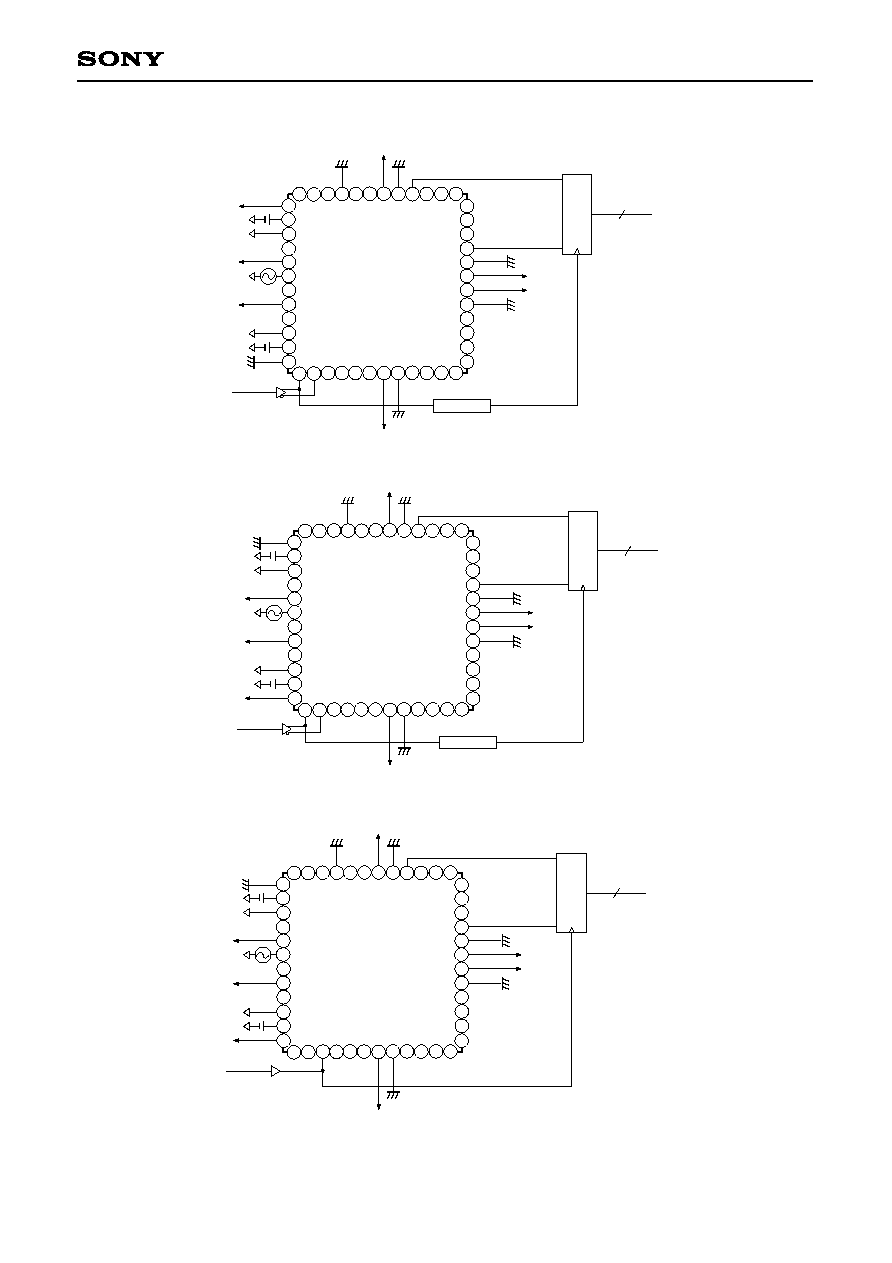

Application Circuit 2

DMUX Mode TTL I/O (When a single power supply is used)

CLK/E

N.C.

CLK/T

N.C.

N.C.

DV

CC

2

DGND2

PAD0

PAD1

PAD2

PAD3

CLKN/E

RESETN/E

SELECT

RESETN/T

INV

CLKOUT

DV

CC

2

DGND2

PBD7

PBD6

PBD5

PBD4

RESET/E

D

V

E

E

3

V

R

M

1

A

G

N

D

A

V

C

C

V

I

N

V

R

M

2

A

V

C

C

V

R

M

3

A

G

N

D

V

R

T

D

G

N

D

3

V

R

B

P

A

D

4

P

A

D

7

P

A

D

6

D

V

C

C

1

D

V

C

C

2

D

G

N

D

2

P

B

D

0

P

B

D

1

P

B

D

2

P

B

D

3

P

A

D

5

D

G

N

D

1

Analog

input

AG

+5V (A)

2V

4V

TTL CLK

(

L

S

B

)

P

A

D

0

P

A

D

1

P

A

D

2

P

A

D

3

P

A

D

4

P

A

D

5

P

A

D

6

(

M

S

B

)

P

A

D

7

(

L

S

B

)

P

B

D

0

(

M

S

B

)

P

B

D

7

P

B

D

1

P

B

D

2

P

B

D

3

P

B

D

4

P

B

D

5

P

B

D

6

1µF

10µF

10µF

1µF

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

25

26

27

28

29

30

40

39

38

37

36

35

34

31

32

33

41

42

43

44

45

46

47

48

1

AG

AG

DG

+5V

(D)

AG

AG

24

short

short

Short the analog system and digital system at one point immediately

under the A/D converter. See the Notes on Operation.

is the chip capacitor of 0.1µF. Also, C

is important to suppress the noise generated

during the TTL output circuit is operating. Place C

at the fixed position

between the pins with the shortest distance.

C

C

C

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

≠ 17 ≠

CXA3246Q

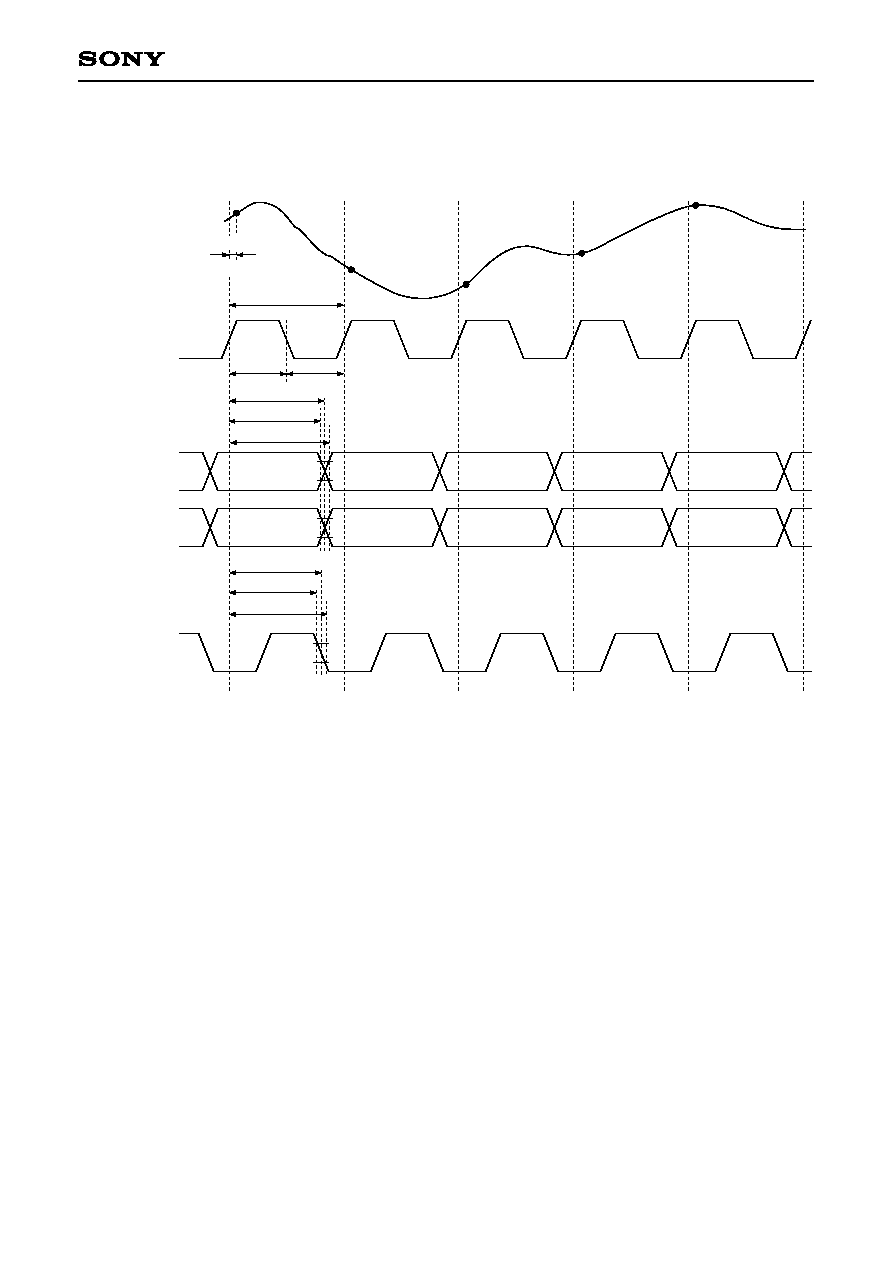

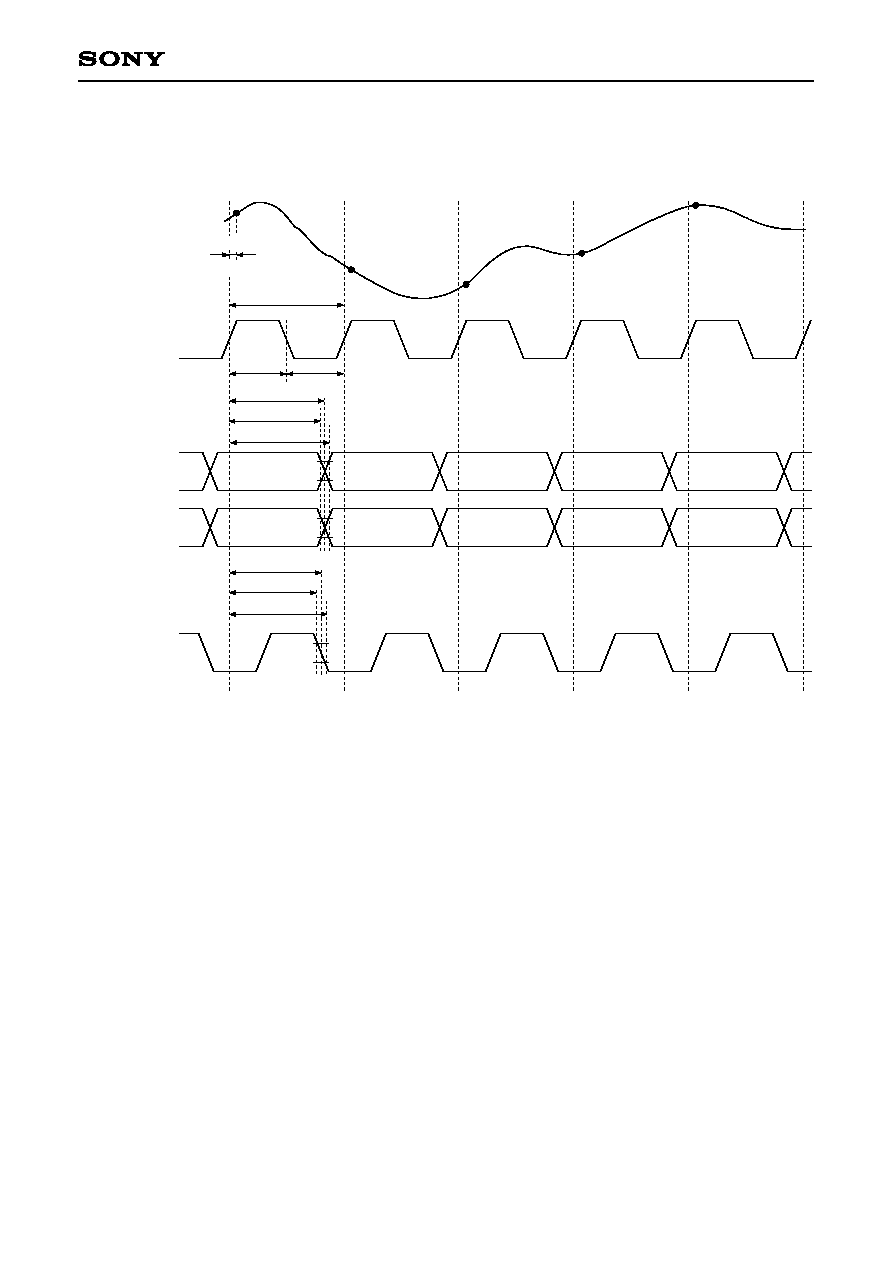

DMUX Mode Timing Chart (Select = V

CC

)

CLK

V

IN

T

Tpw0

Tpw1

N + 2

N + 3

N + 1

N + 4

N + 5

N

N + 6

Tds

1.4ns (typ.)

N ≠ 1

N ≠ 2

2.0V

0.8V

N + 1

2.0V

0.8V

Tdo1

T

T

PBD0 to D7

PAD0 to D7

N

N + 2

N + 3

CLK OUT

RESETN

T_rs

T_rh

T_rs

T_rh

2.0V

0.8V

(Reset period)

2.0V

0.8V

Tdo2; 5.0ns (typ.)

Td_clk; 4.5ns (typ.)

2.0V

0.8V

T + 0.5ns (typ.)

3.5ns (min)

7.5ns (max)

7.0ns (max)

3.0ns (min)

(Pin 6)

(Pin 13)

(Pins 21 to 28)

(Pins 33 to 40)

(Pin 43)

(Pin 48)

≠ 18 ≠

CXA3246Q

Straight Mode Timing Chart (Select = GND)

Tds

T

Tpw1

N + 1

N ≠ 1

N

N + 2

N + 3

CLK

V

IN

Tpw0

1.4ns (typ.)

N ≠ 2

N

PBD0 to D7

N + 1

N ≠ 1

N ≠ 3

2.0V

0.8V

PAD0 to D7

N ≠ 3

N ≠ 1

N

N ≠ 2

N ≠ 4

2.0V

0.8V

CLK OUT

(CLK is inverted

and output.)

2.0V

0.8V

Td_clk; 4.5ns (typ.)

Tdo2; 5.0ns (typ.)

7.0ns (max)

3.0ns (min)

3.5ns (min)

7.5ns (max)

(Pin 6)

(Pin 13)

(Pins 21 to 28)

(Pins 33 to 40)

(Pin 43)

≠ 19 ≠

CXA3246Q

Notes on Operation

∑ The CXA3246Q has the PECL and TTL input pins for the clock and reset input pins. When the clock is input

in PECL level, inputting the reset signal in PECL level is recommended. Also, when the clock is input in TTL

level, inputting the reset signal in TTL is recommended.

∑ The impedance of the input signal should be properly matched to ensure the CXA3246Q's stable operation at

the high speed.

∑ The power supply and grounding have a profound influence on converter performance. The power supply

and grounding method are particularly important during high-speed operation. General points for caution are

as follows.

-- The ground pattern should be as large as possible. It is recommended to make the power supply and

ground patterns wider at an inner layer using a multi-layer board.

-- To prevent interference between AGND and DGND and between AVcc and DVcc, make sure the

respective patterns are separated. To prevent a DC offset in the power supply pattern, connect the AVcc

and DVcc lines at one point each via a ferrite-bead filter, etc. Shorting the AGND and DGND patterns in

one place immediately under the A/D converter improves A/D converter performance.

-- Be sure to turn the analog and digital power supplies on simultaneously. If not simultaneously, the IC does

not operate correctly.

-- Ground the power supply pins (AVcc, DVcc1, DVcc2, DV

EE

3) as close to each pin as possible with a

0.1µF or larger ceramic chip capacitor.

(Connect the AVcc pin to the AGND pattern and the DVcc1, DVcc2 and DV

EE

3 pins to the DGND pattern.)

-- It is recommended to place the ceramic chip capacitor of 0.1µF or more, in particular, between DVcc2

and DGND2 with the shortest distance. This has the effect to suppress the noise generated when the

CXA3246Q TTL output circuit operates.

-- The digital output wiring should be as short as possible. If the digital output wiring is long, the wiring

capacitance will increase, deteriorating the output slew rate and resulting in reflection to the output

waveform since the original output slew rate is quite fast.

∑ The analog input pin V

IN

has an input capacitance of approximately 10pF. To drive the A/D converter with the

proper frequency response, it is necessary to prevent performance deterioration due to parasitic capacitance

or parasitic inductance by using a large capacity drive circuit, keeping wiring as short as possible, and using

chip parts for resistors and capacitors, etc.

∑ The V

RT

and V

RB

pins must have adequate by-pass to protect them from high-frequency noise. By-pass them

to AGND with approximately 1µF tantal capacitor and 0.1µF chip capacitor as short as possible.

∑ If the CLKN/E pin is not used, by-pass this pin to DGND with an approximately 0.1µF capacitor. At this time,

approximately DGND3 ≠ 1.2V voltage is generated. However, this is not recommended for use as the threshold

voltage V

BB

because it is too weak.

∑ When the digital input level is ECL or PECL level,

/E pins should be used and

/T pins left open. When

the digital input level is TTL,

/T pins should be used and

/E pins left open.

∑ The CXA3246Q TTL output high level is clamped to approximately 2.8V in the IC. This makes it possible to

directly interface with the 3.5V system CMOS IC.

∑ The CXA3026Q has the output pins P1

and P2

. However, in the CXA3246Q, these symbols are

changed as PA

and PB

. At this time, the P1 side of the CXA3026Q is changed to the PB side for the

CXA3246Q; the P2 side of the CXA3026Q to the PA side for the CXA3246Q.

∑ The pipeline delay of the CXA3246Q is smaller by one clock, compared to that of CXA3026Q.

≠ 20 ≠

CXA3246Q

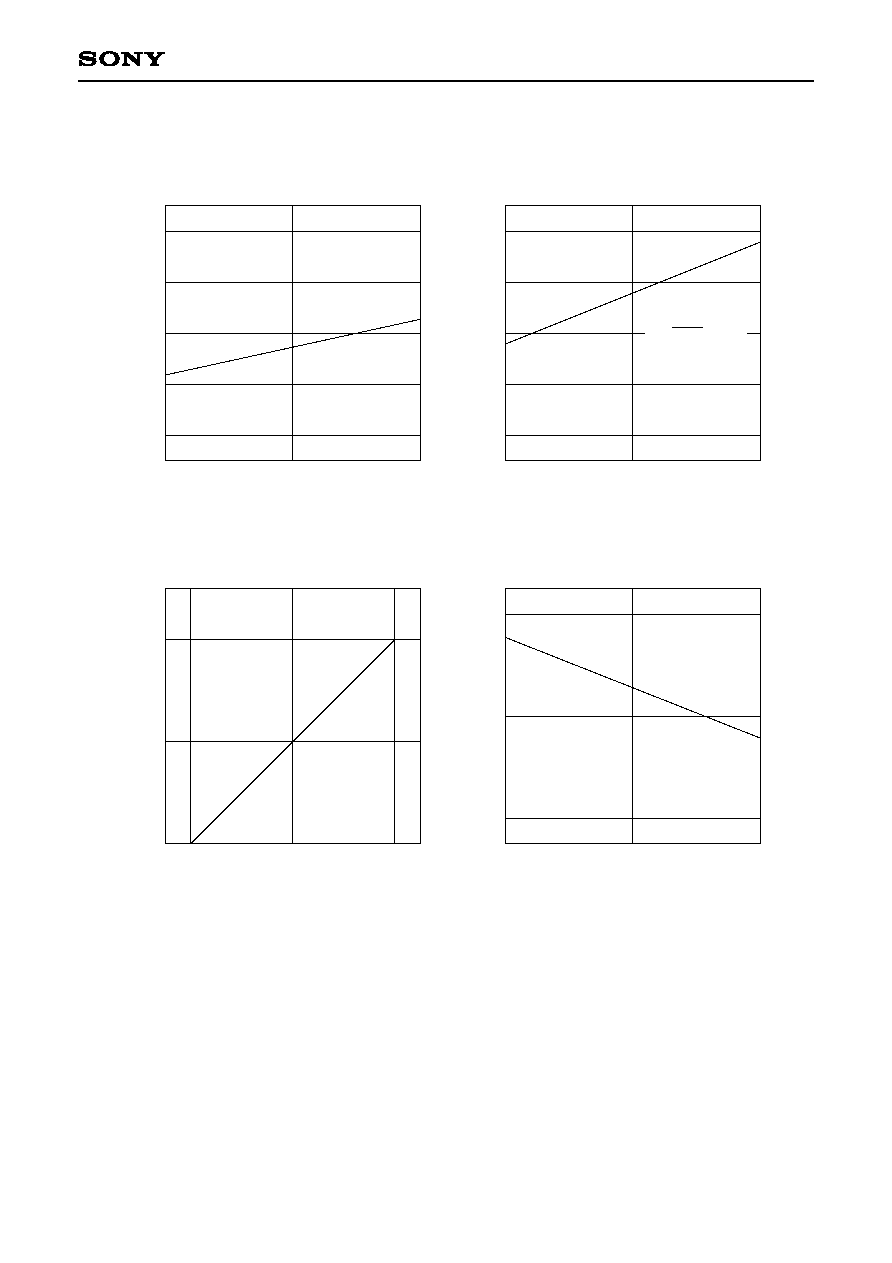

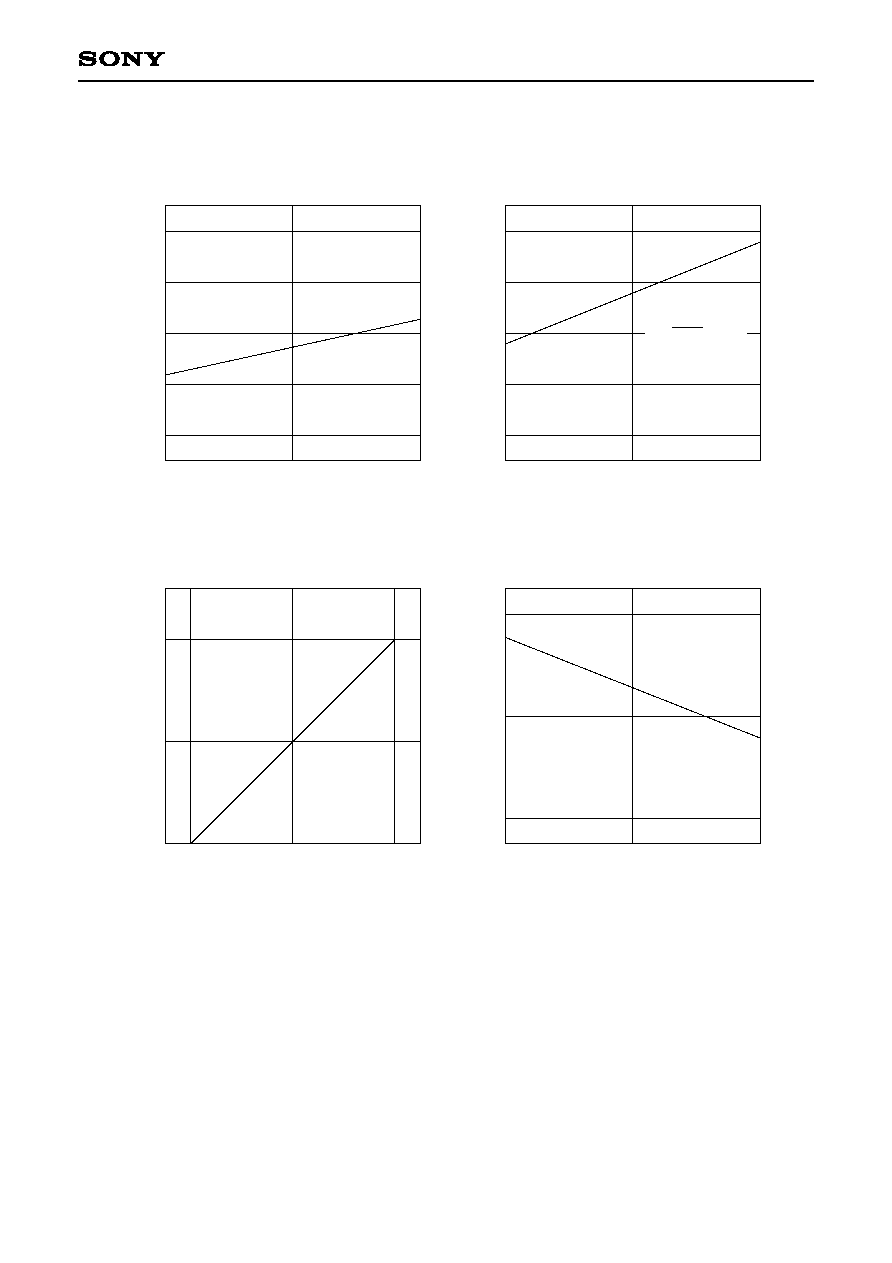

Current consumption vs.

Ambient temperature characteristics

Ta ≠ Ambient temperature [∞C]

≠25

90

25

75

C

u

r

r

e

n

t

c

o

n

s

u

m

p

t

i

o

n

[

m

A

]

95

100

105

110

Current consumption vs.

Conversion rate characteristics

Fc ≠ Conversion rate [MSPS]

0

90

60

C

u

r

r

e

n

t

c

o

n

s

u

m

p

t

i

o

n

[

m

A

]

95

100

105

110

120

DMUX mode

C

L

= 5pF

fin = ≠ 1kHz

f

CLK

4

Analog input current vs.

Analog input voltage characteristics

Analog input voltage [V]

2

3

4

A

n

a

l

o

g

i

n

p

u

t

c

u

r

r

e

n

t

[

µ

A

]

50

100

0

Reference current vs.

Ambient temperature characteristics

Ta ≠ Ambient temperature [∞C]

≠25

2

25

75

R

e

f

e

r

e

n

c

e

c

u

r

r

e

n

t

[

m

A

]

3

4

V

RT

= 4V

V

RB

= 2V

Example of Representative Characteristics

≠ 21 ≠

CXA3246Q

SNR vs. Input frequency response

Input frequency [MHz]

1

20

5

50

S

N

R

[

d

B

]

30

40

50

30

3

10

Error rate vs. Conversion rate characteristics

120

140

160

10

≠6

10

≠7

10

≠8

10

≠9

10

≠10

Error > 16LSB

fin = ≠ 1kHz

f

CLK

4

Maximum conversion rate vs.

Ambient temperature characteristics

Ta ≠ Ambient temperature [∞C]

≠25

130

25

75

F

c

≠

M

a

x

i

m

u

m

c

o

n

v

e

r

s

i

o

n

r

a

t

e

[

M

S

P

S

]

150

170

fin = ≠ 1kHz

f

CLK

4

140

160

Fc = 120MSPS

Error > 16LSB

Error rate: 10

≠9

TPS

E

r

r

o

r

R

a

t

e

[

T

P

S

]

Fc ≠ Conversion rate [MSPS]

≠ 22 ≠

CXA3246Q

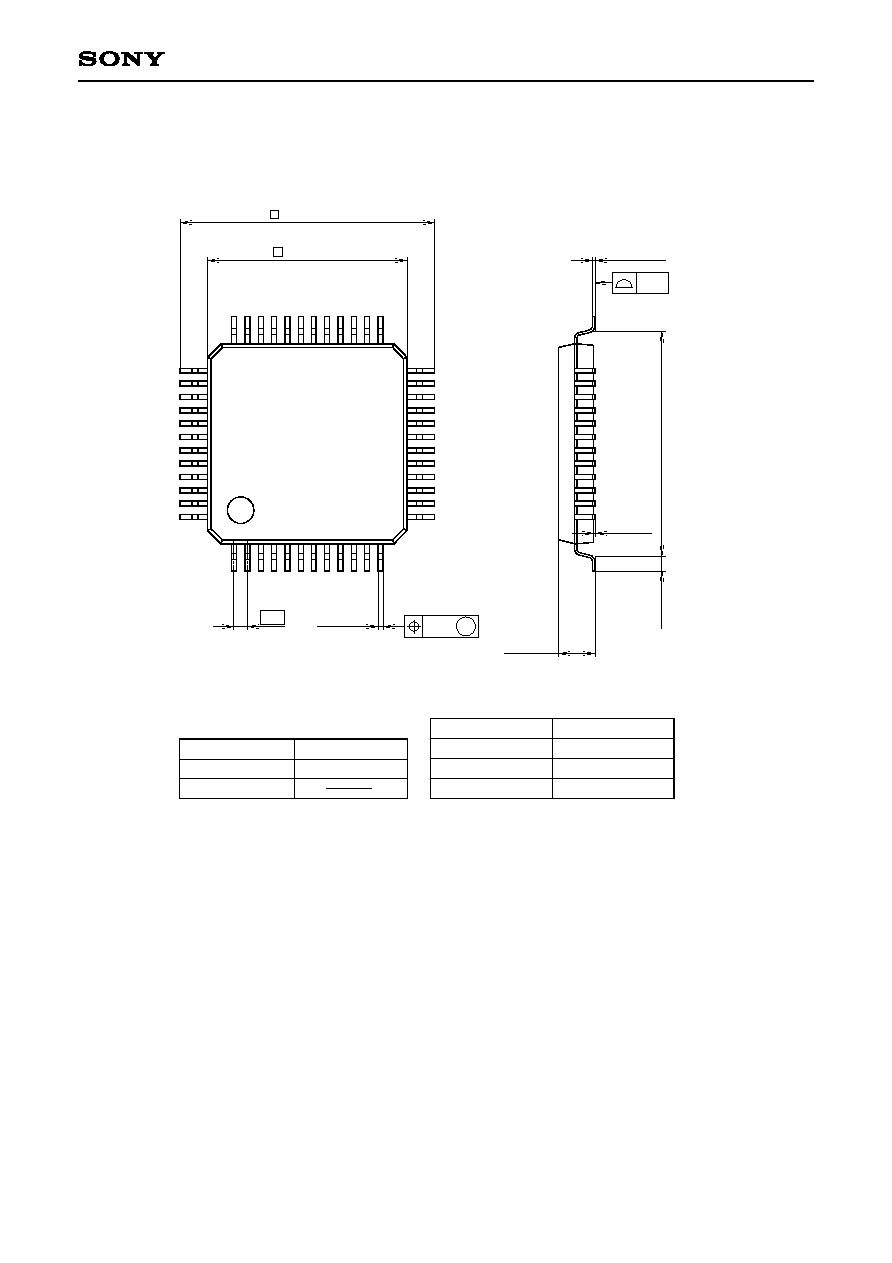

Package Outline

Unit: mm

SONY CODE

EIAJ CODE

JEDEC CODE

M

PACKAGE STRUCTURE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

SOLDER / PALLADIUM

PLATING

42/COPPER ALLOY

48PIN QFP (PLASTIC)

15.3 ± 0.4

12.0 ≠ 0.1

+ 0.4

0.8

0.3 ≠ 0.1

+ 0.15

0.24

13

24

25

36

37

48

1

12

2.2 ≠ 0.15

+ 0.35

0

.

9

±

0

.

2

0.1 ≠ 0.1

+ 0.2

1

3

.

5

0.15 ≠ 0.05

+ 0.1

QFP-48P-L04

QFP048-P-1212

0.7g

0.15

NOTE : PALLADIUM PLATING

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).