| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXA7002R | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

≠ 1 ≠

E02750A41

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXA7002R

64 pin LQFP (Plastic)

I

2

C Bus Compatible Audio Video (AV) Switch & Electronic Volume Control

Description

The Sony CXA7002R is an Audio/Video switch

designed primarily for application in Digital Set Top

Boxes. It provides video and audio routing from the

digital encoder source to the TV and VCR scart

(peri-television) connectors. In addition, the TV audio

output has a programmable volume control. The chip

is programmed by means of an I

2

C interface and can

operate from a single or dual power supply.

Target specifications: Canal+, BSkyB, TPS, NorDig,

and ECCA Euro-Box

Features

Supply

∑ Single: 0V, +5V, +12V

∑ Dual:

0V, ≠5V, +5V and +12V

(Low number of external parts required)

Video

∑ 2 scart switching (VCR, TV)

∑ VCR input supports RGB mode

∑ Integrated 75

drivers for direct video connection

∑ Y/C mixer with trap for RF modulators

∑ Switchable clamps on inputs

∑ Low pass filters on six inputs

∑ Controllable gain on encoder inputs

∑ Adjustable gain on RGB outputs

∑ Video output shutdown for low power modes

∑ Fast blanking switch

∑ Slow blanking switch for TV and VCR output

∑ SVHS switch on VCR output

∑ Y/C auxiliary input

Audio

∑ Four stereo audio inputs

∑ Volume control (≠56dB to +6dB in 2dB steps)

∑ Additional +6dB gain on audio DAC inputs

∑ Audio overlay facility

∑ Volume bypass for TV and Phono outputs

∑ Mono switching on TV, VCR outputs

∑ Switchable audio limiter function

∑ Switchable Mono output for RF modulators

∑ Audio output disable for standby mode

I

2

C and Logic

∑ Fast mode compatible I

2

C bus

∑ Function monitor with loop through

∑ Interrupt output for function monitor and sync

detect

∑ Logic output pin

∑ Sync detector for Y/CVBS inputs

Applications

∑ Digital Set Top Box

∑ Integrated digital television

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings (Ta = 25∞C)

unless stated

∑ Supply voltage

V

CC

14

V

∑ Storage temperature

Tstg

≠65 to +150

∞C

∑ Allowable power dissipation

P

D

1.1

W

(when mounted on the board)

Operating Conditions

∑ Single supply

12 ± 0.6

V

5 ± 0.25

V

∑ Dual supply

≠5 ± 0.25

V

5 ± 0.25

V

12 ± 0.6

V

∑ Operating temperature

Topr

≠20 to +75

∞C

∑ Maximum ESD voltage

±2

kV

(Human Body Model)

≠ 2 ≠

CXA7002R

Block Diagram

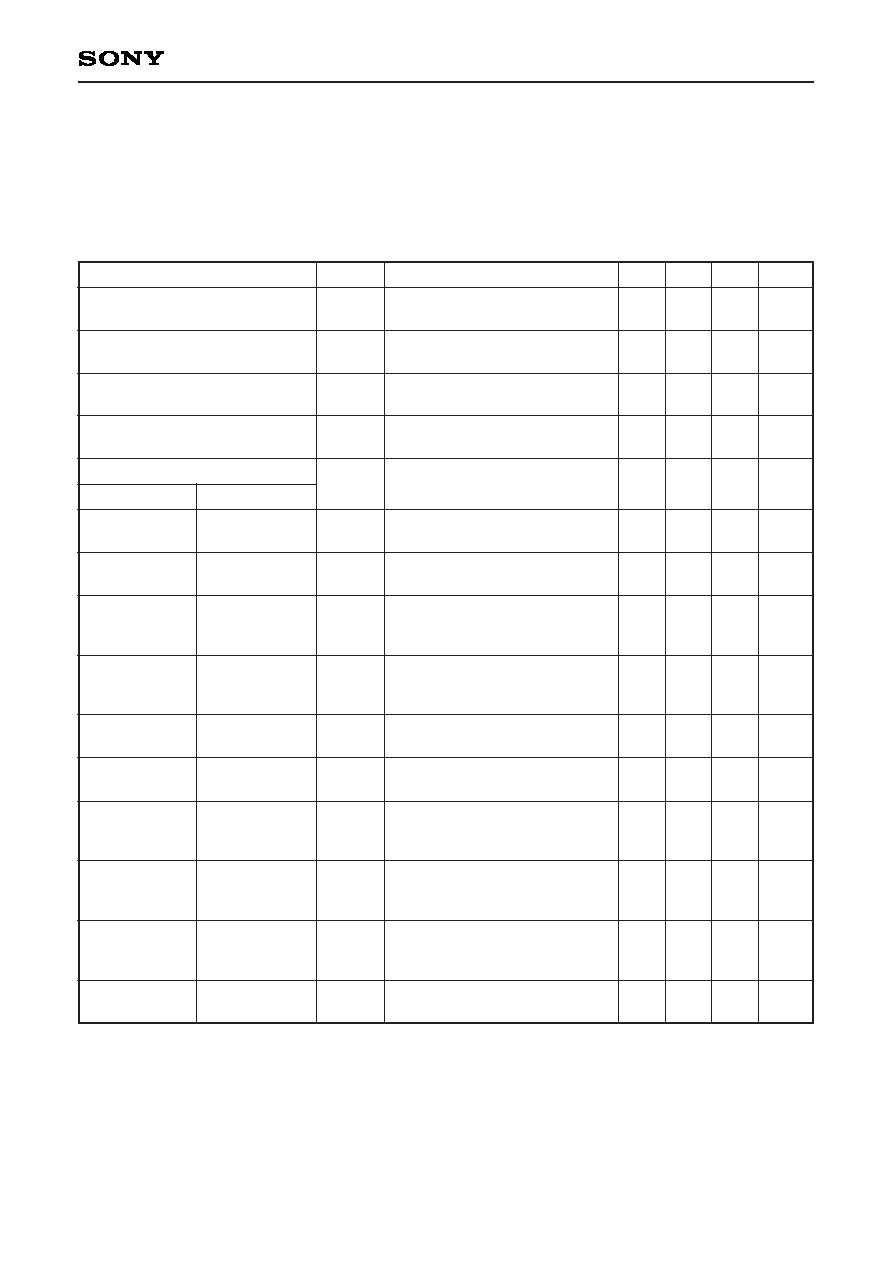

(1) Video Section

Note) All video outputs contain 75

drivers.

DC

Restore

2

6

VOUT_1

RGB Gain Control

(+1, 2, 3dB)

GAIN

ADJUST

BLUE

VIN_1

DIG BLUE

54

VIN_2

VCR BLUE

53

VIN_4

VCR GREEN

51

VIN_7

VCR RED/CHROMA

TV

TV

VCR

DC

Restore

DC

Restore

DC Restore

/C Bias

Sync

Detector

DC

Restore

1

7

VOUT_2

GREEN

VIN_3

DIG GREEN/CVBS

DC

Restore/

C Bias

Sync

Tip

Clamp

63

8

VOUT_3

RED/CHROMA

62

VOUT_4

LUMA/CVBS

VOUT_7

Mix Switch

Mix Switch

RF MOD

60

VOUT_5

Bi-directional

Control

CHROMA

61

VOUT_6

GND_VID

V

CC

_AUD

AUD_BIAS

+5V_VID

+5V_VOUT

LUMA/CVBS

3

4

TRAP

VIN_5

DIG RED/CHROMA

C Bias

9

VIN_6

DIG CHROMA

C Bias

55

VIN_13

AUX CHROMA

10

VIN_8

DIG CVBS/LUMA

11

VIN_9

DIG CVBS/LUMA

Sync

Tip

Clamp

52

VIN_10

VCR CVBS/LUMA

Sync

Tip

Clamp

57

VIN_11

TV CVBS

Sync

Tip

Clamp

56

VIN_12

INTERUPT

5

VID_BIAS

12

GND

37

GND

13

≠5V_GNDA

36

≠5V_GNDA

27

≠5V_GNDA

17

+12V

24

+5V_DIG

25

GND_DIG

26

AUD_BIAS

28

59

64

58

46

35

+5/12V_V

CC

A

AUX Y/CVBS

Sync

Tip

Clamp

≠ 3 ≠

CXA7002R

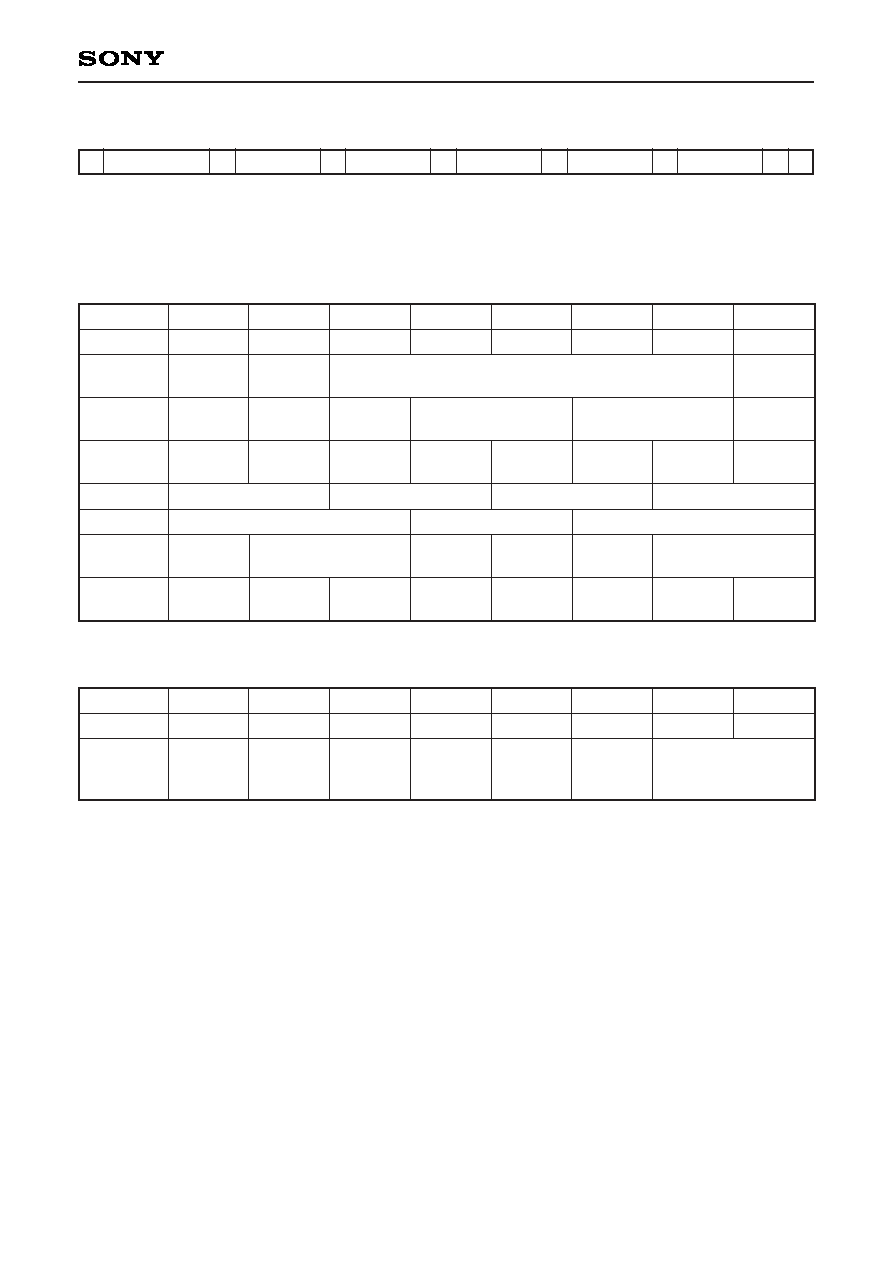

(2) Audio Section

32

12dB

Vol Bypass

(TV)

AUDIO SWITCH1 (TV)

47

44

41

16

15

29

30

31

49

≠6dB

≠12dB

≠12dB

≠12dB

47

45

42

50

≠6dB

≠12dB

≠12dB

≠12dB

AUDIO SWITCH2 (VCR)

RIN_1 (DIG)

MONO

PHONO_R

RTV

LTV

PHONO_L

ROUT1

LOUT1

VCR

RIN_2 (VCR)

RIN_3 (TV/OVERLAY)

RIN_4 (AUX)

LIN_1 (DIG)

LIN_2 (VCR)

LIN_3 (TV/OVERLAY)

LIN_4 (AUX)

Overlay on/off

Tone mix

Overlay on/off

Bias

Mute

Limiter

2.2Vrms

Hardware

Mute

2dB

Limiter

2.2Vrms

2dB

Volume Control

+6 to ≠56dB

ZCD

Vol Bypass

(Phono)

Mono Switch

Mono Switch

Mono and R/L

Switch

Vol Bypass

(TV)

Vol Bypass

(Phono)

12dB

12dB

12dB

12dB

12dB

12dB

TV

33

19

H/W MUTE

≠ 4 ≠

CXA7002R

(3) Digital Section

+3.5V

TV_FBLK

21

LOGIC

14

FNC_TV

18

FBLK_IN1

FBLK_IN2

Logic

Control

INTERUPT

40

Interrupt

Control

Monitor

0/6/12V

0/6/12V

Sync Detector

0V

FBLK_SW

20

23

SDA

SCL

38

39

FNC_VCR

22

≠ 5 ≠

CXA7002R

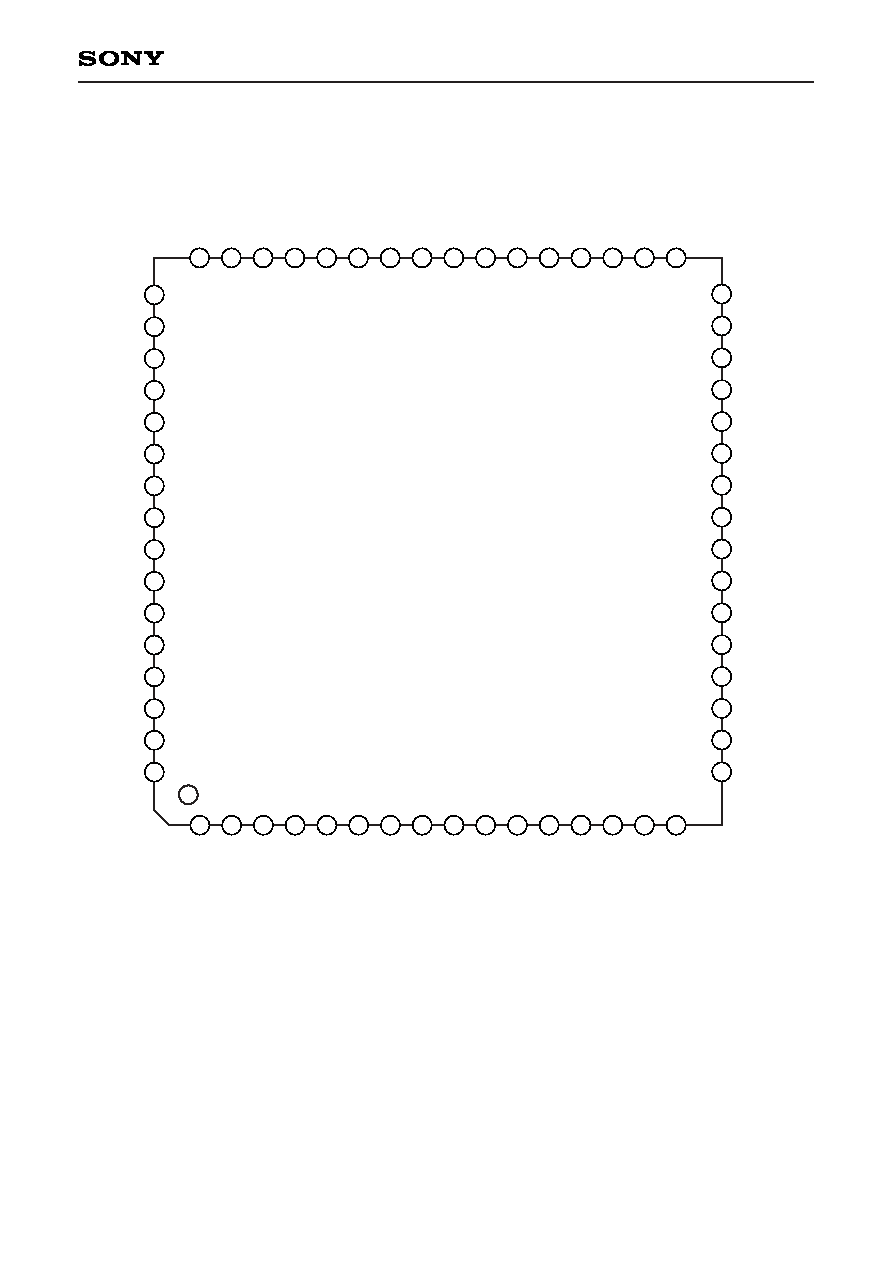

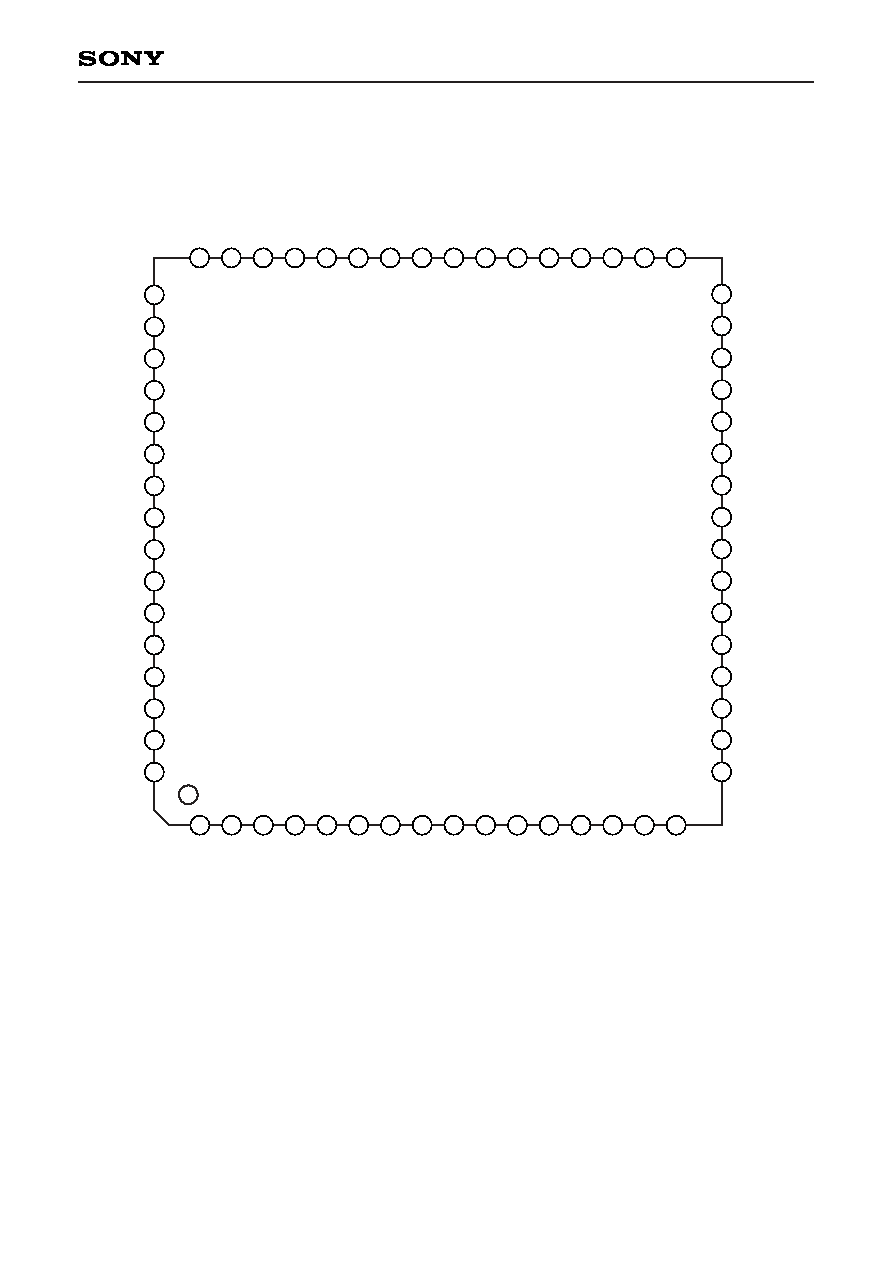

Pin Configuration

RIN_4

LIN_4

VIN_7

VIN_10

VIN_4

VIN_2

VIN_13

VIN_12

VIN_11

+5V_VID

GND_VID

VOUT_5

VOUT_6

VOUT_4

VOUT_3

+5V_VOUT

V

OUT_2

V

OUT_1

V

OUT_7

TRAP

VID_BIAS

VIN_1

VIN_3

VIN_5

VIN_6

VIN_8

VIN_9

GND

≠5V_GND

A

LOGIC

LT

V

RT

V

LIN_3

RIN_3

A

UD_BIAS

LIN_2

RIN_2

SYNC_ID

LIN_1

RIN_1

INTER

UPT

SCL

SD

A

GND

≠5V_GND

A

Vcc_A

UD

GND_A

UD

R

OUT1

1

2

3

4

5

6

7

8

9

11

12

13

14

19

20

21

22

23

25

26

27

28

29

30

31

32

35

37

38

39

40

41

42

43

44

45

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

17

18

63

64

10

24

36

15

16

33

34

46

LOUT1

MONO

PHONO_R

PHONO_L

+5/+12V_VccA

≠5V_GNDA

AUD_BIAS

GND_DIG

+5V_DIG

FBLK_IN2

FNC_VCR

TV_FBLK

FBLK_IN1

HW_MUTE

FNC_TV

+12V

≠ 6 ≠

CXA7002R

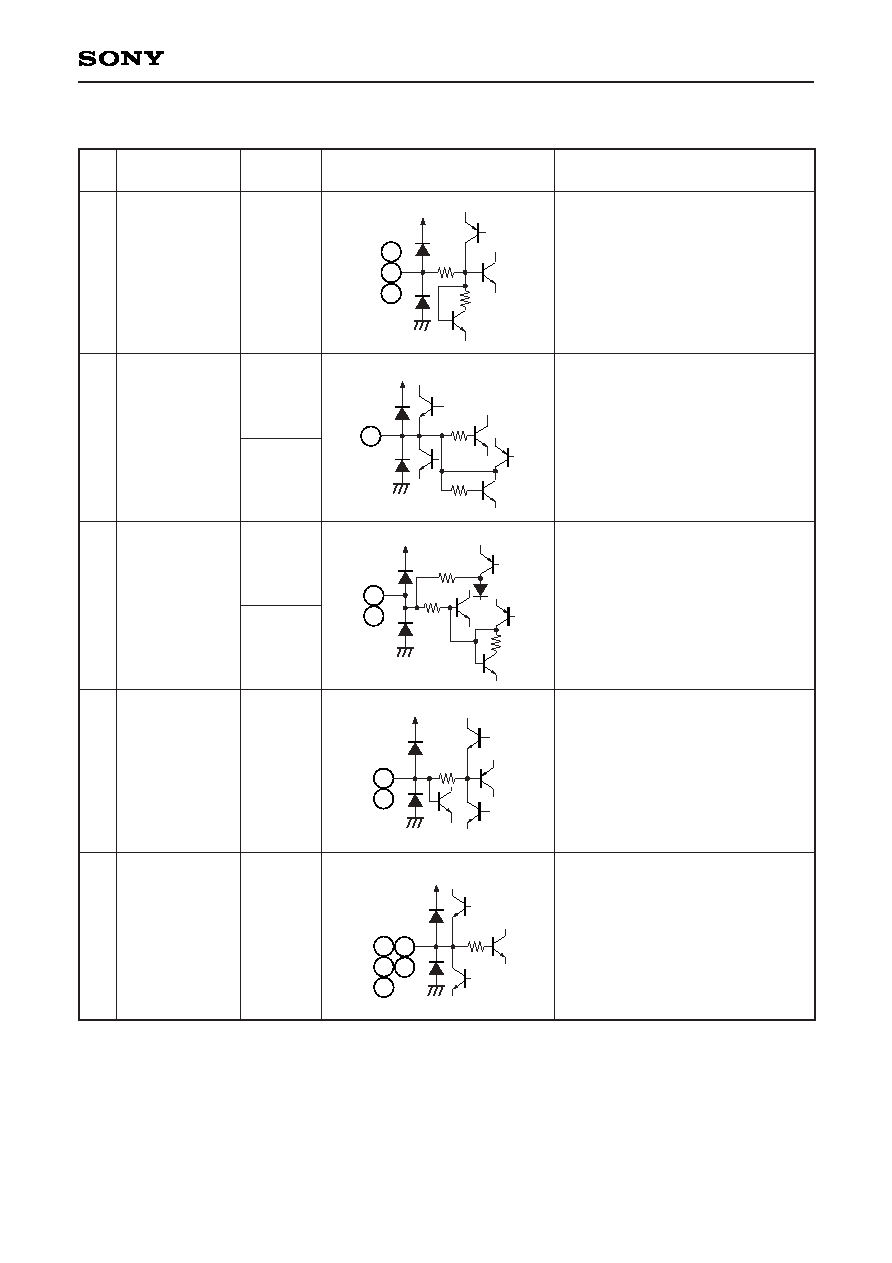

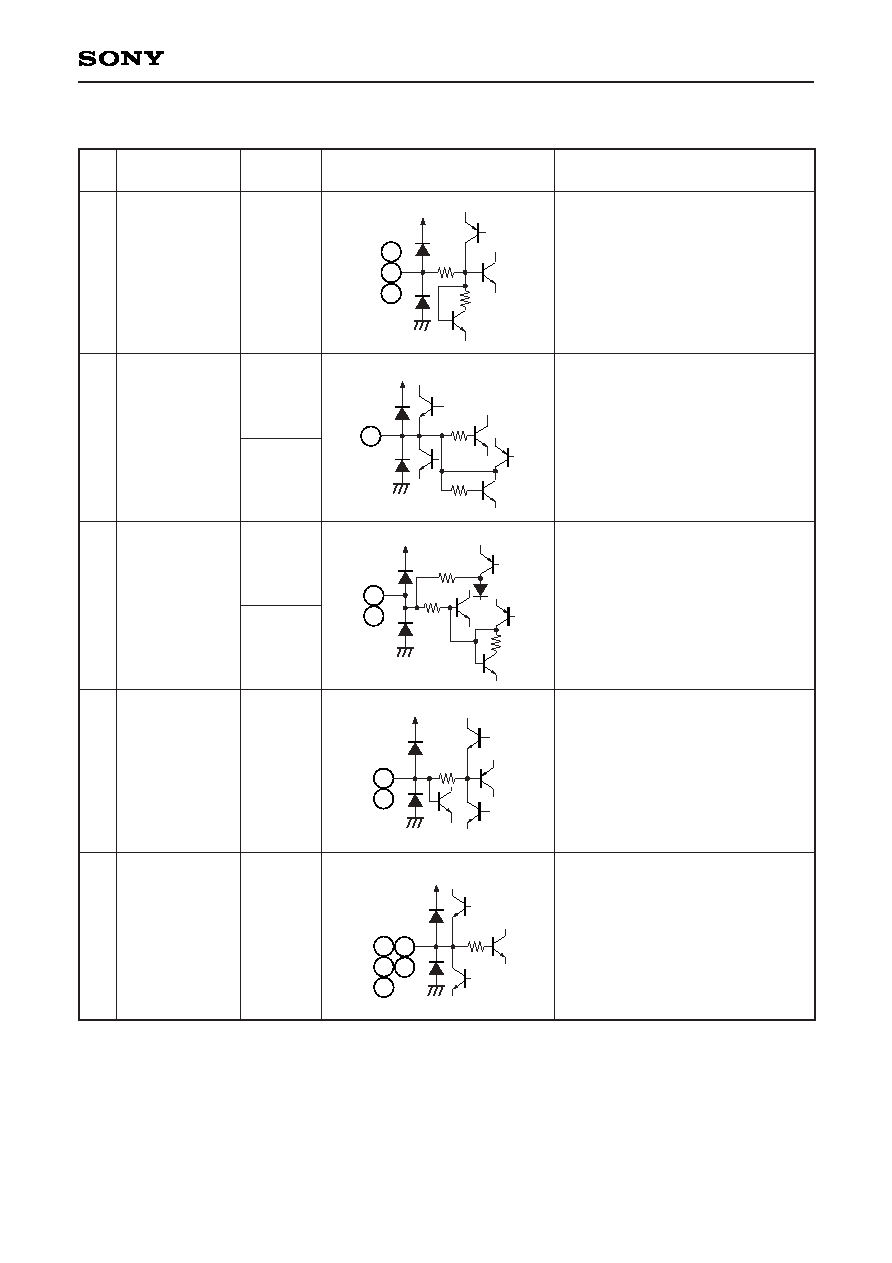

Pin Description

Pin

No.

Symbol

Pin

voltage [V]

Equivalent circuit

Description

V

CC

1.2k

2k

54

53

6

6

54

53

VIN_1

VIN_2

VIN_4

2.5

RGB signal inputs

V

CC

1.2k

3k

7

7

VIN_3

2.5

RGB signal input

or

CVBS signal input

2.4

8

51

VIN_5

VIN_7

2.5

RGB signal inputs

or

Chrominance signal inputs

3.1

V

CC

1.2k

50k

8

51

V

CC

50k

9

55

9

55

VIN_6

VIN_13

3.1

Chrominance signal inputs

10

11

52

57

56

VIN_8

VIN_9

VIN_10

VIN_11

VIN_12

2.4

CVBS/Luminance signal inputs

V

CC

1.2k

57

56

10

52

11

≠ 7 ≠

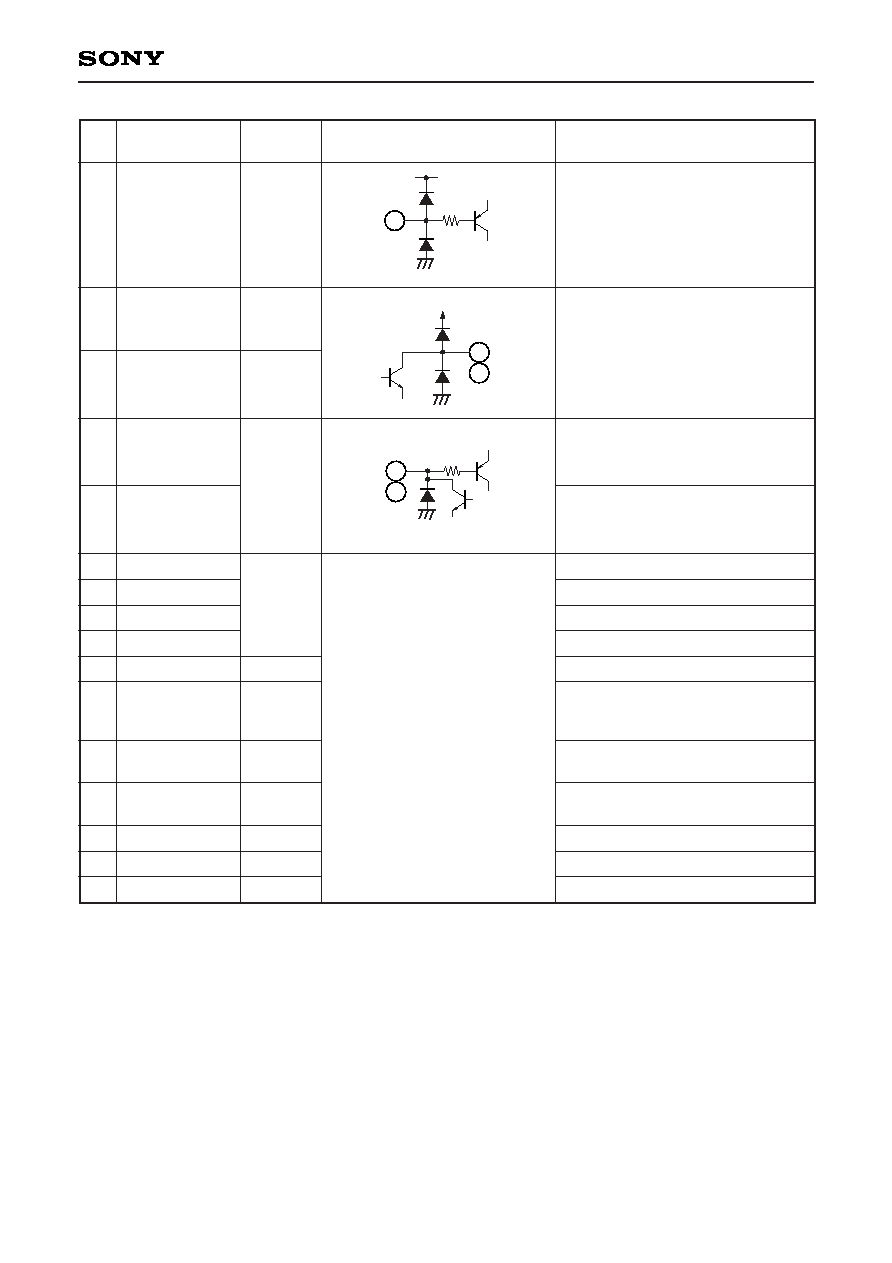

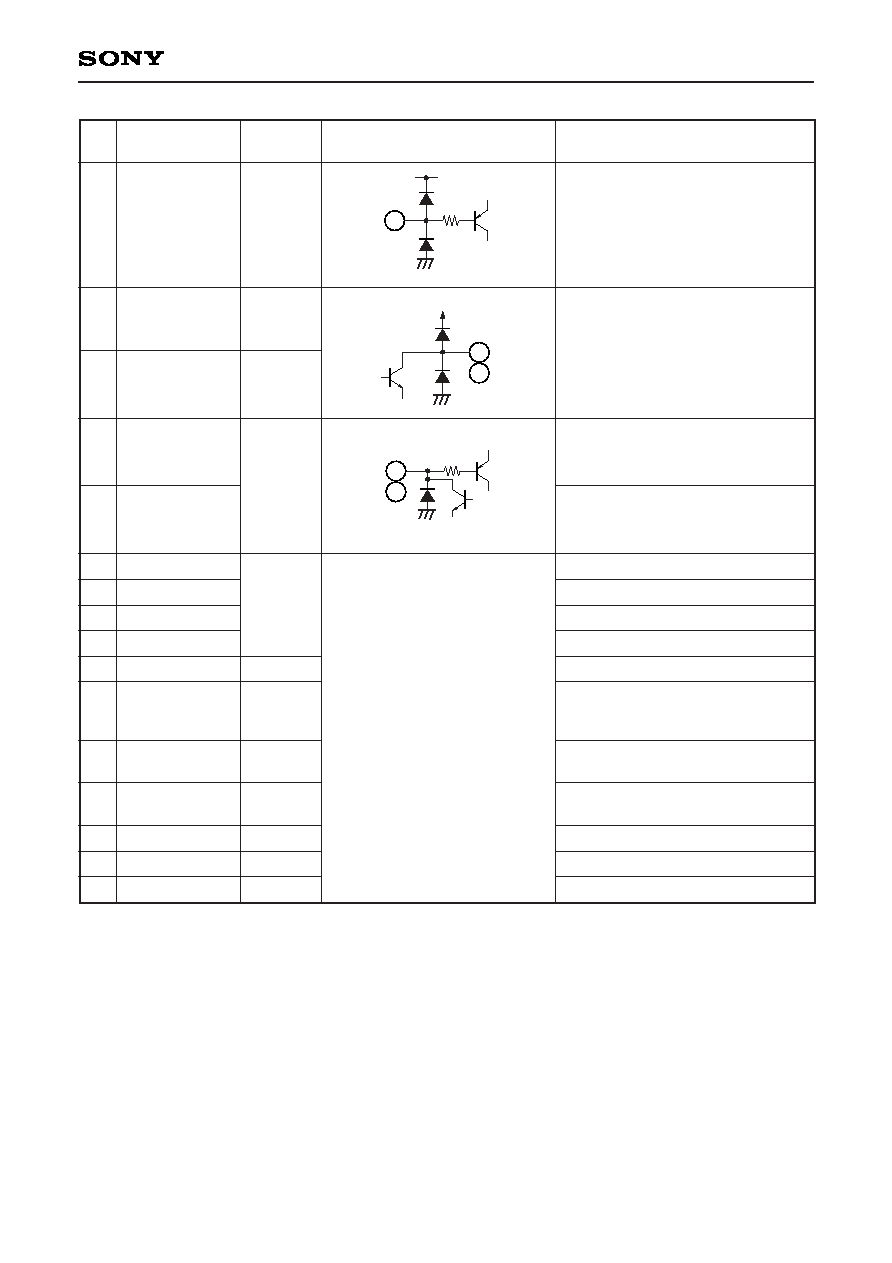

CXA7002R

Pin

No.

Symbol

Pin

voltage [V]

Equivalent circuit

Description

2

1

63

62

61

3

VOUT_1

VOUT_2

VOUT_3

VOUT_4

VOUT_6

VOUT_7

0.6

RGB/CVBS signal outputs

V

CC

20k

1

63

2

61

3

62

V

CC

20k

60

60

VOUT_5

1.8

Chrominance signal output

5

VID_BIAS

0.9

Internal reference bias for video

circuits. A capacitor is connected

from this pin to GND.

Typically 100nF

V

CC

V

CC

9.2k

40.8k

5

4

TRAP

2.4

Connects trap circuit for subcarrier

V

CC

1.2k

1.2k

4

43

SYNC_ID

2.5

Sync detect circuit time constant,

resistor and capacitor connection pin

V

CC

200

200

43

V

CC

V

CC

/2

50k

50k

42

41

V

CC

V

CC

6.25k 50k

44

49

47

45

50

48

42

41

LIN_1

RIN_1

2.5

Audio signal inputs

45

44

48

47

50

49

LIN_2

RIN_2

LIN_3

RIN_3

LIN_4

RIN_4

2.5

Audio signal inputs

≠ 8 ≠

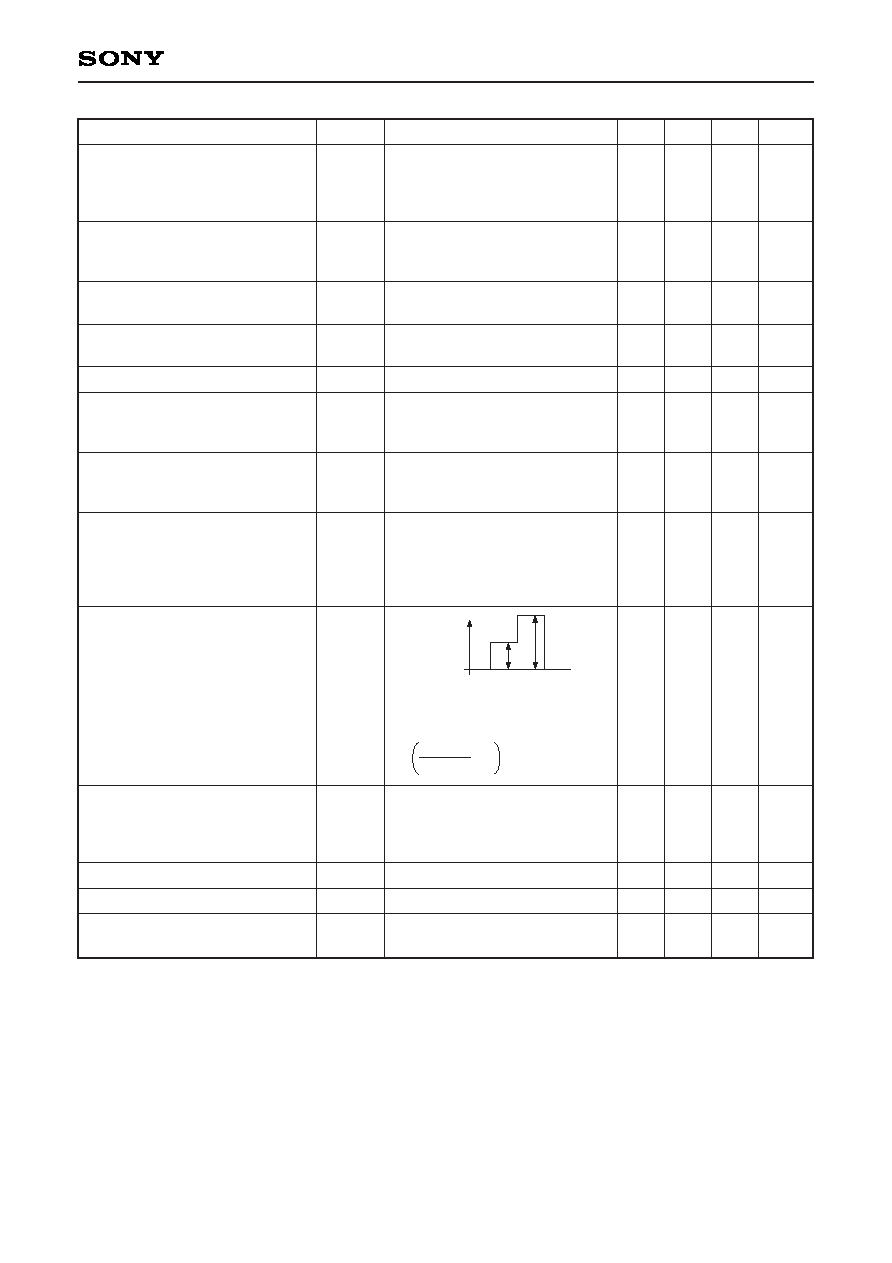

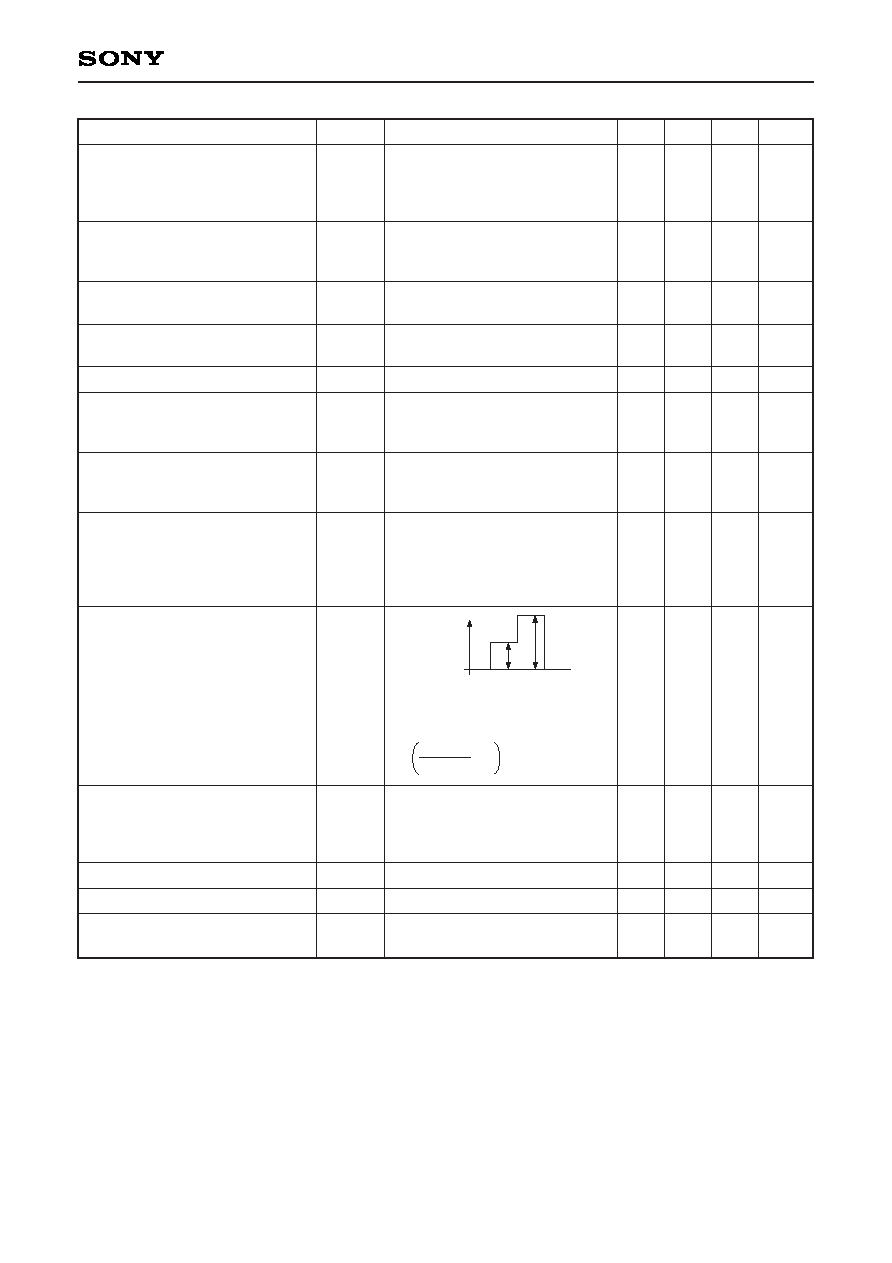

CXA7002R

Pin

No.

Symbol

Pin

voltage [V]

Equivalent circuit

Description

15

16

32

33

29

30

31

LTV

RTV

LOUT1

ROUT1

PHONO_L

PHONO_R

MONO

6.0

(Single)

Audio signal outputs

0.0

(Dual)

V

CC

40k

32

29

31

15

33

30

16

V

CC

V

CC

25k

25k

46

46

AUD_BIAS

Internal

reference bias

for audio circuit

2.5V

(Single/

Dual)

Capacitor

connected to GND.

(Typically 22µF)

26

AUD_BIAS

Internal

reference bias

for audio circuit

Capacitor

connected to GND.

(Typically 22µF)

Connected

directly to GND.

6.0

(Single)

0.0

(Dual)

V

CC

124

20

23

20

23

FBLK_IN1

FBLK_IN2

--

Fast blanking signal inputs

21

TV_FBLK

--

Fast blanking signal output

V

CC

21

22

FNC_VCR

--

SCART function pin 8 input/output

to VCR

124

16.5k

76.7k

22

18

FNC_TV

--

SCART function pin 8 output to TV

124

36k

19k

18

V

CC

V

CC

40k

124

40k

26

≠ 9 ≠

CXA7002R

Pin

No.

Symbol

Pin

voltage [V]

Equivalent circuit

Description

19

HW_MUTE

--

Mutes audio outputs when pin

voltage is below 2V. This pin is

normally connected to +5V.

124

19

V

CC

14

40

Open connector logic outputs

Typically connect to +5V through

10k

resistor.

14

LOGIC

(Vcc = +12V)

--

40

INTERUPT

(Vcc = +5V)

--

39

SCL

--

38

SDA

8k

38

39

I

2

C bus clock line

I

2

C bus data line

24

64

58

35

17

13

17

36

28

12

37

25

34

59

+5V_DIG

+5V_VOUT

+5V_VID

Vcc_AUD

+12V

≠5V_GNDA

+5V/12V_VccA

GND

GND_DIG

GND_AUD

GND_VID

Digital supply

Video output supply

Video supply

Audio supply

Digital supply

Audio supply/ground

Audio supply

Digital ground

Audio Ground

Video ground

5.0

12.0

≠5.0 (Dual)

0.0 (Single)

5.0 (Dual)

12.0 (Single)

0.0

0.0

0.0

0.0

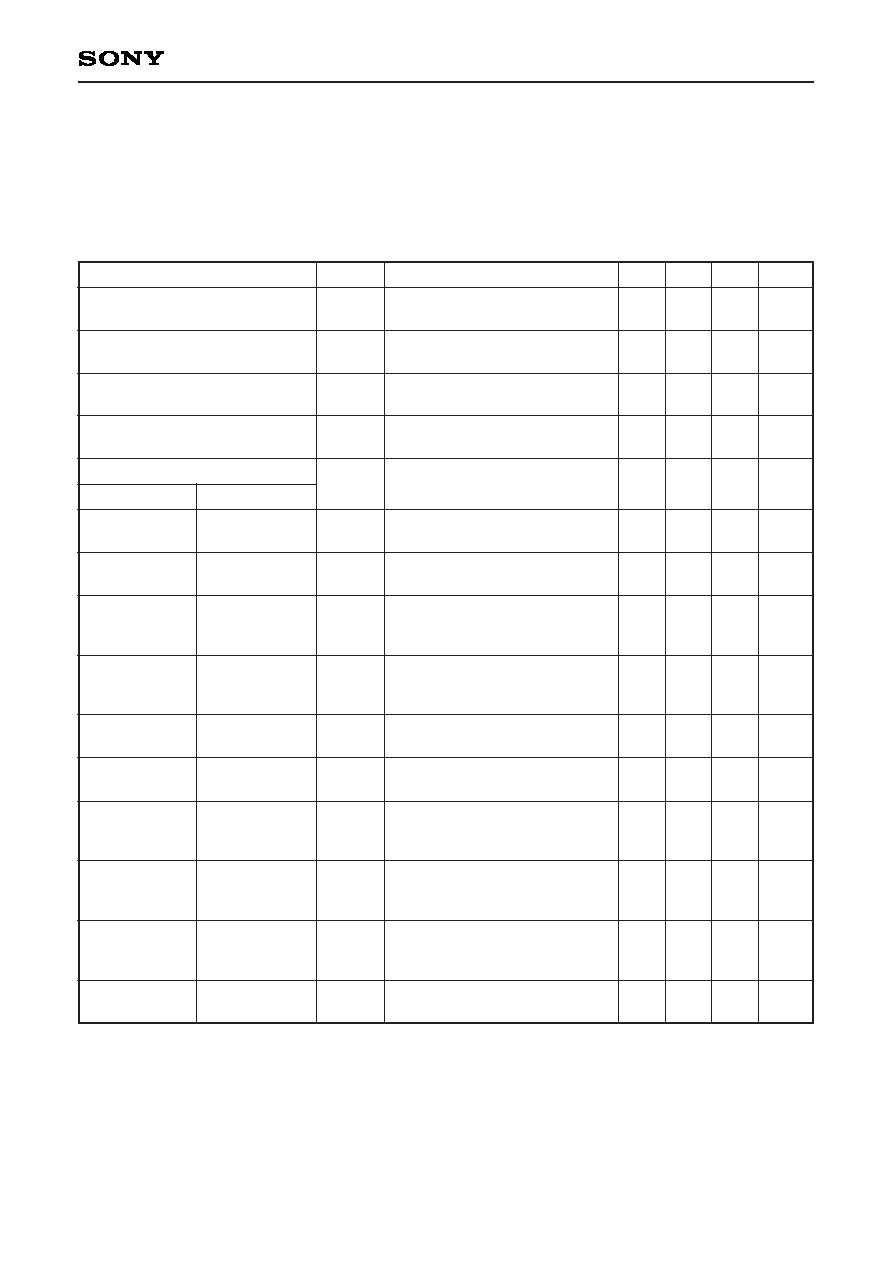

≠ 10 ≠

CXA7002R

Electrical Characteristics

Nominal conditions (Ta = 25∞C)

Item

Current consumption

(Single ended supply)

Current consumption

(Dual supply)

Symbol

Icc1

Icc2

Icc3

Icc4

Icc5

Conditions

+12 supply, no signal, no load

+5 supply, no signal, no load

+12 supply, no signal, no load

+5 supply, no signal, no load

≠5 supply, no signal, no load

Min.

--

--

--

--

≠50

Typ.

30

60

10

80

≠20

Max.

55

85

30

110

--

Unit

mA

mA

mA

mA

mA

(1) Video System

Nominal conditions single supply (Ta = 25∞C, +5V/12V_VccA = +12V, ≠5V_GNDA = 0V,

+5V_VID = +5V, +5V_VOUT = +5V, +5V_DIG = +5V)

Item

Sync tip clamp voltage at input

Chroma bias input voltage

RGB dc restore input voltage

Sync tip clamp voltage at output

Chroma bias output voltage

RGB dc restore output voltage

Gain (Vout1 to 7)

Gain (Vout1, 2, 3)

Video input gain

Vin 1, 3, 5, 6, 8, 9

Symbol

Vclmp1

Cbias1

Cbias2

RGB1

Vclmp2

Cbias3

RGB2

GVv

GV

RGB1

GV

RGB2

GV

RGB3

G

i/p1

G

i/p1

G

i/p1

Conditions

Vin3, Vin8, Vin9, Vin10, Vin11,

Vin12 inputs. (Vin3 set to CVBS

mode) (Fig. 1)

Vin5, Vin7 inputs. Clamps set to

Chroma bias mode. (Fig. 1)

Vin6, Vin13 inputs. (Fig. 1)

Vin1, Vin2, Vin3, Vin4, Vin5, Vin7

inputs. (Vin3 & Vin5 set to RGB

mode) (Fig. 1)

Vout4, Vout6 outputs (Fig. 1)

Vout3, Vout5 outputs (Fig. 1)

Vout1, Vout2, Vout3 outputs

(Fig. 1)

f = 200kHz, 0.3Vp-p input,

RGB Gain = 0dB,

Input Gain = 0dB (Fig. 2)

f = 200kHz, 0.3Vp-p input,

RGB Gain = +1dB,

Input Gain = 0dB (Fig. 2)

f = 200kHz, 0.3Vp-p input,

RGB Gain = +2dB,

Input Gain = 0dB (Fig. 2)

f = 200kHz, 0.3Vp-p input,

RGB Gain = +3dB,

Input Gain = 0dB (Fig. 2)

f = 200kHz, 0.3Vp-p input,

Video gain = +1dB (Fig. 2)

f = 200kHz, 0.3Vp-p input,

Video gain = +3dB (Fig. 2)

f = 200kHz, 0.3Vp-p input,

Video gain = +6dB (Fig. 2)

Min.

--

--

--

--

--

--

--

5.5

6.5

7.5

8.5

6.5

8.5

11.5

Typ.

2.4

3.1

2.45

2.5

0.3

1.8

0.6

6.0

7.0

8.0

9.0

7.0

9.0

12.0

Max.

--

--

--

--

--

--

--

6.5

7.5

8.5

9.5

7.5

9.5

12.5

Unit

V

V

V

V

V

V

V

dB

dB

dB

dB

dB

dB

dB

≠ 11 ≠

CXA7002R

Item

Bandwidth (Vout1 to 6)

Bandwidth (Vout7)

Mixer on ≠ No trap components

Input dynamic range

Output dynamic range

Cross talk

Fast blanking to RGB delay

Vout5 impedance when switched

to ground

S/N ratio

Non-linearity

Differential gain

Differential phase

Filter specification

Attenuation @27MHz

Symbol

f

V3dB

f

V3dB

V

DRVI

V

DRVO

Vctv

Del

FB

Z

Vout5

S/N

V

Lin

DG

DP

Attn

Conditions

0.3Vp-p input, frequency where

output level is ≠3dB with 200kHz

serving as 0dB.

Filter Bypassed. (Fig. 2)

0.3Vp-p input, frequency where

output level is ≠3dB with 200kHz

serving as 0dB. (Fig. 2)

200kHz input applied to any

video (Fig. 2)

200kHz input applied to any

video (Fig. 2)

f = 4.43MHz, 1Vp-p input (Fig. 2)

Falling edge delay from RGB to

fast blank signal. Measured at

20% level. (Fig. 2)

2V applied to Vout5 with series

75

resistor. Measured voltage

at pin and calculate Zout. (Fig. 2)

Ratio of 0.7Vp-p white video

signal to "black line" noise.

Weighted using CCIR

567. HPF@5kHz, LPF@5MHz.

(Fig. 2)

V1 = Pin voltage + 0.5V,

V2 = Pin voltage + 1V

At output, non-linearity

= ≠1

◊

100 (Fig. 2)

1.7Vp-p 5-step modulated

staircase.

(Chroma & Burst are 150mVp-p,

4.43MHz) (Fig. 2)

As above. (Fig. 2)

Measured 27MHz signal relative

to signal at 1MHz. (Fig. 2)

Min.

15

8

1.4

2.8

--

--

--

≠4

≠3

≠3

--

Typ.

30

30

--

--

≠65

1

74

0

0

0

≠47

Max.

--

--

--

--

--

50

--

--

4

3

3

≠24

Unit

MHz

MHz

Vp-p

Vp-p

dB

ns

dB

%

%

deg

dB

Input pin

V

plus

V1

V2

V2

V1

◊

2

≠ 12 ≠

CXA7002R

Audio System

Unless otherwise stated: input coupling capacitor 1µF; output coupling capacitor of 10µF; load of 10k

.

Nominal conditions single supply (Ta = 25∞C, +5V/12V_V

CC

A = +12V, ≠5V_GNDA = 0V, +5V_VID = +5V,

+5V_VOUT = +5V, +5V_DIG = +5V, GND_VID = 0V)

Nominal conditions dual supply

(Ta = 25∞C, +5V/12V_V

CC

A = +5V, ≠5V_GNDA = ≠5V, +5V_VID = +5V,

+5V_VOUT = +5V, +5V_DIG = +5V, GND_VID = 0V)

Item

Input pin voltage

(Single/Dual supply)

Output pin voltage

(Single supply)

Output pin voltage

(Dual supply)

Output pin voltage when

disabled (Single/Dual supply)

Gain

Input

Rin1 or Lin1

Rin1 or Lin1

Rin1 + Lin1

Rin1 + Lin1

Rin2, 3, 4 or

Lin2, 3, 4

Rin1 + Lin1

Rin2 + Lin2

Rin3 + Lin3

Rin4 + Lin4

Rin2 + Lin2

Rin3 + Lin3

Rin4 + Lin4

Rin3

Lin3

Symbol

V

APIN1

V

APIN2

V

APIN2

V

APIN3

GV

A1

GV

A2

GV

A3

GV

A4

GV

A5

GV

A6

GV

A7

GV

A9

GV

A10

GV

A11

Conditions

No signal, no load (Fig. 3)

No signal, no load (Fig. 3)

No signal, no load (Fig. 3)

No signal, no load (Fig. 3)

f = 10kHz, 0.3Vp-p input

(Fig. 4)

f = 10kHz, 0.3Vp-p input

(Fig. 4)

f = 10kHz, 0.3Vp-p stereo input,

TV volume set to 0dB, TV mono

switch on (Fig. 4)

f = 10kHz, 0.3Vp-p stereo input,

TV volume set to 0dB (Note 1)

(Fig. 4)

f = 10kHz, 0.3Vp-p input,

TV volume set to 0dB (Fig. 4)

f = 10kHz, 0.3Vp-p stereo input,

VCR mono switch on (Fig. 4)

f = 10kHz, 0.3Vp-p stereo input,

TV volume set to 0dB (Note 1)

(Fig. 4)

f = 10kHz, 0.3Vp-p input,

VCR mono switch on (Fig. 4)

f = 10kHz, 0.3Vp-p, Lin3 has

no signal Audio overlay enabled.

(Fig. 4)

f = 10kHz, 0.3Vp-p input Audio

overlay enabled. (Fig. 4)

Min.

2.25

5.75

≠0.25

≠0.25

5.7

5.7

5.7

5.7

≠0.3

5.7

≠0.3

≠0.3

≠12.5

≠12.5

Typ.

2.5

6

0

0

6.2

6.2

6.2

6.2

0.2

6.2

0.2

0.2

≠11.75

≠11.75

Max.

2.75

6.25

0.25

0.25

6.7

6.7

6.7

6.7

0.7

6.7

0.7

0.7

≠11.25

≠11.25

Unit

V

V

V

V

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Output

TV or Phono

VCR

TV (mono mix)

MONO

TV, VCR,

Phono

VCR

(mono mix)

MONO

VCR

(mono mix)

RTV, ROUT1,

Phono_R

LTV, LOUT1,

Phono_L

Note 1) Mono switch set to mix RTV & LTV after volume control.

≠ 13 ≠

CXA7002R

Item

Audio frequency response

Distortion

Input dynamic range

Rin2, 3, 4/Lin2, 3, 4

Input dynamic range

Rin1/Lin1

Cross talk

(Channel separation)

Input impedance

Rin1, 2, 3, 4/Lin1, 2, 3, 4

S/N ratio

Electronic Volume Control

Volume attenuation step

Audio limiter level

Mute

TV I/P Mute or

VCR I/P MUTE

Symbol

F

AF

THD

Vd

A1

Vd

A1

Vct

A

Zin1

S/N

A

A

EVC

Alimit

Amute

Condition

0.3Vp-p input. Output/Input gain

at 30kHz with 10kHz serving as

0dB (Fig. 4)

f = 1kHz, 0.5Vrms, unweighted

response; LPF @400Hz, HPF

@80kHz (Fig. 4)

f = 1kHz, RIN1/LIN1 input

amplifier set to ≠6dB. Dual

supply mode used. (Fig. 4)

f = 1kHz (Fig. 4)

f = 10kHz, 1Vrms input on one

input, measure on any audio

output (Fig. 4)

(Excluding any external series

resistor) (Fig. 4)

f = 1kHz, 1Vrms input (0dB

volume). (20Hz to 20kHz) BPF +

A weighting filter (Fig. 4)

f = 10Hz, 0.5Vp-p. Set by I

2

C

(Fig. 4)

f = 1kHz, 2.5Vrms input.

Measure TV pk-pk output with

limiter switched on. (Fig. 4)

f = 1kHz, 1Vrms input

(Fig. 4)

Min.

≠0.3

--

2.5

1.25

--

--

80

1.6

--

--

Typ.

0

0.005

2.9

1.45

≠90

100

--

2

2.2

≠85

Max.

0.3

0.1

--

--

--

--

--

2.4

--

--

Unit

dB

%

Vrms

Vrms

dB

dB

dB

dB

Vrms

dB

≠ 14 ≠

CXA7002R

t

BUF

t

HD;STA

S

P

t

LOW

t

R

t

HIGH

t

SU;DAT

t

SU;STA

t

SU;DAT

P

Sr

t

SU;STO

t

F

t

HD;STA

Digital Characteristics

(1) I

2

C Interface

The I

2

C interface is compliant with Philips I

2

C Fast Mode specification (data April 1995). The interface is also

capable of interfacing to +3.3V or +5V logic levels.

Item

High level input voltage

Low level input voltage

Low level output voltage

Hysteresis of schmitt trigger input

Spike suppression

Fall time for SDA line

SCL clock frequency

Bus free time between a stop

and start

Hold time (repeated start condition)

Low period of SCL clock

High period of SCL clock

Setup time for a repeated start

condition

Data hold time

Data setup time

Setup time for stop condition

Symbol

V

IH

V

IL

V

OL

V

HYST

t

SP

t

F

t

SCL

t

BUF

t

HD;STA

t

LOW

t

HIGH

t

SU;SDA

t

HD;DAT

t

SU;DAT

t

SU;STO

Condition

With SDA, 3mA current supplied

With SDA, 6mA current supplied

V

IH

≠ V

IL

400pF bus load

I

2

C bus line requirement

I

2

C bus line requirement

I

2

C bus line requirement

I

2

C bus line requirement

I

2

C bus line requirement

I

2

C bus line requirement

I

2

C bus line requirement

I

2

C bus line requirement

I

2

C bus line requirement

Min.

2.3

0

0

0

--

--

--

0

1.3

0.6

1.3

0.6

0.6

0

100

0.6

Typ.

--

--

--

--

0.5

--

--

--

--

--

--

--

--

--

--

--

Max.

5.5

1.5

0.4

0.6

--

50

300

400

--

--

--

--

--

0.9

--

--

Unit

V

V

V

V

ns

ns

kHz

µs

µs

µs

µs

µs

µs

µs

µs

≠ 15 ≠

CXA7002R

(2) Slow Blanking

Load = 10k

, supply +12V = +12V

Item

Input threshold low level

Input threshold high level

Output low level (Int TV mode)

Output level (Ext 16:9 mode)

Output level (Ext 4:3 mode)

Symbol

V

TH1

V

TH2

V

OUT1

V

OUT2

V

OUT3

Condition

Load = 10k

Load = 10k

Load = 10k

Min.

--

--

--

4.8

10

Typ.

3

8.1

0.3

5.5

11

Max.

--

--

0.8

6.5

--

Unit

V

V

V

V

V

(3) Fast Blanking

Output load = 150

, supply +5V_VOUT = +5V

Item

Input threshold

Input current

Output low level

Output high level

Symbol

V

TH3

I

IN1

V

OUT4

V

OUT5

Condition

Measured on fast blanking input

1, 2

+2V applied to input

Load = 150

Load = 150

Min.

--

--

3

Typ.

0.7

2

--

Max.

--

--

0.2

--

Unit

V

µA

V

V

(4) logic and interrupt output

These outputs are open collector type and normally connected to +5V through a 10k

resistor.

Item

Output low voltage

Symbol

DIG

VOUTL

Condition

I

OL

= 1mA

Min.

--

Typ.

--

Max.

0.4

Unit

V

≠ 16 ≠

CXA7002R

100nF

+5V

+5V

Measurement

Point

Measurement

Point

+5V

+5V

SDA

SCL

+12V

+5V

+12V

I

2

C

22µF

22µF

68k

100nF

75

100nF

75

100nF

75

100nF

75

100nF

75

100nF

75

100nF

75

100nF

75

100nF

100nF

75

100nF

75

100nF

75

100nF

75

100nF

75

V

Measurement

Point

V

V

2

3

4

5

6

7

8

9

11

12

13

14

15

16

34

33

17

18

19

20

21

23

24

25

26

27

28

29

30

31

32

50

49

35

37

38

39

40

41

42

43

44

45

47

48

51

52

53

54

55

56

57

58

59

60

61

62

63

64

10

22

36

46

1

Fig. 1. Video System (DC Tests)

DC measured from Pins 1, 2, 3, 4, 6, 7, 8, 9, 10, 11, 51, 52, 53, 54, 55, 56, 57, 60, 61, 62, 63

Notes) 1. All supplies de-coupled close to the supply pins, 17, 24, 28, 58, 64 with 10nF and 10µF capacitors.

2. All video outputs are unloaded during tests.

≠ 17 ≠

CXA7002R

100nF

+5V

+5V

Measurement

Point

+5V

+5V

SDA

SCL

+12V

+5V

+12V

I

2

C

22µF

22µF

68k

100nF

75

100nF

75

100nF

75

100nF

75

100nF

75

100nF

75

100nF

75

100nF

75

100nF

150

150

150

150

150

150

150

100nF

75

100nF

75

100nF

75

100nF

75

100nF

75

V

Input

Signal

Input

Signal

2

3

4

5

6

7

8

9

11

12

13

14

15

16

34

33

17

18

19

20

21

23

24

25

26

27

28

29

30

31

32

50

49

35

37

38

39

40

41

42

43

44

45

47

48

51

52

53

54

55

56

57

58

59

60

61

62

63

64

10

22

36

46

1

Fig. 2. Video System

(Gain, Dynamic Range, Bandwidth, Differential Gain, Differential Phase, Crosstalk, Linearity)

Signal applied to Pins 51, 52, 53, 54, 55, 56, 57, 6, 7, 8, 9, 10, 11

Output signal measured from Pins 60, 61, 62, 63, 64, 1, 2, 3

Notes) 1. All supplies de-coupled close to the supply pins, 17, 24, 28, 58, 64 with 10nF and 10µF capacitors.

2. For video crosstalk tests all video inputs are terminated with 37.5

.

≠ 18 ≠

CXA7002R

+5V

+5V

≠5V

+5V

SDA

SCL

+12V

≠5V

+5V

+12V

I

2

C

22µF

22µF

100nF

Output

Measurement

Point

V

V

Input

Measurement

Point

+5V

2

3

4

5

6

7

8

9

11

12

13

14

15

16

34

33

17

18

19

20

21

23

24

25

26

27

28

29

30

31

32

50

49

35

37

38

39

40

41

42

43

44

45

47

48

51

52

53

54

55

56

57

58

59

60

61

62

63

64

10

22

36

46

1

≠5V

Fig. 3. Audio System (DC Tests)

DC measured from Pins 29, 30, 31, 32, 41, 42, 44, 45, 47, 48, 49, 50

Notes) 1. Single audio supply configuration shown. Operate switches for dual supply configuration.

2. All supplies de-coupled close to the supply pins, 17, 24, 28, 58, 64 with 10nF and 10µF capacitors.

≠ 19 ≠

CXA7002R

+5V

+5V

≠5V

+5V

SDA

SCL

+12V

≠5V

+5V

+12V

I

2

C

22µF

22µF

1µF

100nF

1µF

1µF

1µF

1µF

1µF

1µF

10µF

10µF

10µF

10µF

10µF

10k

10µF

10µF

1µF

Output

Measurement

Point

V

Input

Signal

+5V

2

3

4

5

6

7

8

9

11

12

13

14

15

16

34

33

17

18

19

20

21

23

24

25

26

27

28

29

30

31

32

50

49

35

37

38

39

40

41

42

43

44

45

47

48

51

52

53

54

55

56

57

58

59

60

61

62

63

64

10

22

36

46

1

≠5V

Fig. 4. Audio System

(Gain, Bandwidth, Signal to Noise, Electronic Volume, Zero Cross Detection, Dynamic Range,

Crosstalk)

Signal applied to Pins 41, 42, 44, 45, 47, 48, 49, 50

Output signal measured from Pins 29, 30, 31, 32, 33

Notes) 1. Single audio supply configuration shown. Operate switches for dual supply configuration.

2. All supplies de-coupled close to the supply pins, 17, 24, 58, 64 with 10nF and 10µF capacitors.

≠ 20 ≠

CXA7002R

I

2

C Control Data Format

S Slave address A

DATA1

A

DATA2

A

DATA3

A

DATA4

A

DATAn

A

P

S: Start condition A: Acknowledge P: Stop condition

Address = 90H

I

2

C Data Structure (write mode)

Address

Data1

Data2

Data3

Data4

Data5

Data6

Data7

b7

1

AUDIO

LIMITER

MONO

SWITCH

TV AUD

MUTE

FILTER

CONTROL

VOUT5_0

V

b6

0

VCR MONO

SWITCH

TV MONO

SWITCH

TV INPUT

MUTE

ENABLE

VOUT7

b5

0

TV VOL

BYPASS

ZCD

ENABLE

VOUT6

b4

1

AUDIO

DISABLE

VIN5

CLAMP

ENABLE

VOUT5

b3

0

LOGIC

LEVEL

VIN7

CLAMP

ENABLE

VOUT4

b2

0

0

VIN3

CLAMP

ENABLE

VOUT3

b1

0

VCR INPUT

MUTE

ENABLE

VOUT2

b0

0 = Write

TV AUD

MUTE

PHONO

BYPASS

OVERLAY

ENABLE

ENABLE

VOUT1

VOLUME CONTROL

VCR AUDIO SELECT

TV AUDIO SELECT

VIDEO INPUT GAIN

FNC VCR

FNC TV

FAST BLANK

VCR VIDEO SWITCH

RGB GAIN

TV VIDEO SWITCH

SYNC SEL

MIXER CONTROL

Address

Data

b7

1

NOT

USED

b6

0

NOT

USED

b5

0

ZERO

CROSS

STATUS

b4

1

P.O.D.

b3

0

NOT

USED

b2

0

SYNC

DETECT

b1

0

b0

1 = Read

I

2

C Data Structure (read mode)

FNC_VCR

Note) ZCD

= Zero Cross Detect

P.O.D. = Power on Detect

≠ 21 ≠

CXA7002R

I

2

C Video Control

TV Video Control [Data 5 Bits 0, 1, 2]

Switch setting

0 xxxxx000

1 xxxxx001

2 xxxxx010

3 xxxxx011

4 xxxxx100

5 xxxxx101

6 xxxxx110

7 xxxxx111

Vout1

Blue

Encoder

Blue

VIN1

Bias

VCR Blue

VIN2

Bias

Bias

Encoder

blue

VIN1

Bias

Bias

Vout2

Green

Encoder

Green

VIN3

Bias

VCR Green

VIN4

Bias

Bias

Encoder

Green

VIN3

Bias

Bias

Vout3

Red/Chroma

Encoder

Red

VIN5

Encoder

Chroma

VIN6

VCR

Chroma/Red

VIN7

Bias

Encoder

Chroma

VIN5

Encoder

Red

VIN5

Aux Chroma

VIN13

Bias

Vout4

CVBS/Y

Encoder

CVBS

VIN8

Encoder

Luma

VIN9

VCR CVBS/Y

VIN10

TV CVBS

VIN11

Encoder

Luma

VIN3

Aux

CVBS

VIN12

Aux

CVBS/Y

VIN12

Bias

Comment

Digital encoder RGB or

CVBS

Digital encoder Y/C

VCR Y/C or RGB

TV

Digital encoder Y/C

Encoder RGB and AUX CVBS

Aux Y/C or CVBS

Video Mute

After power on all TV outputs are off (high impedance) and muted.

TV RGB Gain Control [Data 5 Bits 3, 4]

I

2

C setting "RGB GAIN"

0 xxx00xxx

1 xxx01xxx

2 xxx10xxx

3 xxx11xxx

Extra gain/dB

0

+1

+2

+3

The power on default is 0dB.

≠ 22 ≠

CXA7002R

VCR Video Control [Data 5 Bits 5, 6, 7]

Switch setting

0 000xxxxx

1 001xxxxx

2 010xxxxx

3 011xxxxx

4 100xxxxx

5 101xxxxx

6 110xxxxx

7 111xxxxx

Vout5

Chroma

Encoder Chroma

VIN5

Encoder Chroma

VIN6

VCR Chroma

VIN7

Bias

Encoder Chroma

VIN5

Bias

Aux Chroma

VIN13

Bias

Vout6

CVBS/Y

Encoder CVBS/Y

VIN8

Encoder Luma

VIN9

VCR CVBS/Y

VIN10

TV CVBS

VIN11

Encoder Luma

VIN3

Aux CVBS

VIN12

Aux CVBS

VIN12

Bias

Comment

Digital encoder Y/C

Digital encoder Y/C

VCR Y/C

TV CVBS

Encoder Y/C

AUX CVBS

AUX Y/C

Video mute

After power on VCR outputs are off (high impedance) and muted.

"Y/C MIXER CONTROL" [Data 6 Bits 0, 1]

I

2

C setting

0 xxxxxx00

1 xxxxxx01

2 xxxxxx10

3 xxxxxx11

Vout7 Mixer output

No mix, Vout7 = Vout4 (CVBS)

Mix Vout4 (Y) + Vout3 (C)

No mix, Vout7 = Vin8 (CVBS)

No mix Vout7 = Vout4 (CVBS)

The power on default is no mix.

Input Clamp Control "VIN3 Clamp" [Data 6 Bit 2]

xxxxx0xx = GREEN input on VIN3. DC restore clamp active. (Power on default)

xxxxx1xx = CVBS input on VIN3. Sync tip clamp active.

Input Clamp Control "VIN7 Clamp" [Data 6 Bit 3]

xxxx0xxx = CHROMA input on VIN7. Chroma bias applied. (Power on default)

xxxx1xxx = RED input on VIN7. DC restore clamp applied.

Input Clamp Control "VIN5 Clamp" [Data 6 Bit 4]

xxx0xxxx = RED input on VIN5. DC restore clamp applied. (Power on default)

xxx1xxxx = CHROMA input on VIN5. Chroma bias applied.

≠ 23 ≠

CXA7002R

Sync Select Control for RGB DC Restore Circuits "SYNC_SEL" [Data 6 Bits 5, 6]

When the TV output is set to RGB + Y/CVBS mode. Then it is necessary to select the input that contains the

sync information for the RGB signal. This will normally be the digital encoder CVBS or VCR CVBS input.

I

2

C setting "SYNC_SEL"

0 x00xxxxx

1 x01xxxxx

2 x10xxxxx

3 x11xxxxx

Input with sync

VIN8

VIN9

VIN10

VIN12

The power on default is Vin8 ie. Digital encoder input.

Video Input Gain [Data 4 Bits 6, 7]

Extra gain applied to Vin1, 3, 5, 6, 8, 9

I

2

C setting "VIDEO INPUT GAIN"

0 00xxxxxx

1 01xxxxxx

2 10xxxxxx

3 11xxxxxx

Extra gain/dB

0 (Bypass)

+1

+3

+6

The power on default is bypass.

Filter Control [Data 6 Bit 7]

The filters on the six digital encoder inputs Vin1, 3, 5, 6, 8, 9 are switched on with this control bit.

0xxxxxxx = Filter bypass. Power on default.

1xxxxxxx = Filter on.

Standby Mode Control [Data 7 Bits 0, 1, 2, 3, 4, 5, 6]

The video outputs VOUT1, 2, 3, 4, 5, 6, 7 can be individually turned off using data byte 7.

0 = Video output off. (Power on default)

1 = Video output on.

Note) When switched off, the video outputs are in a high impedance state. With a normal 150

load, the

outputs will be pulled to 0V.

≠ 24 ≠

CXA7002R

Bi-directional Line Control on VCR Scart "Vout5_0V" [Data 7 Bit 7]

0xxxxxxx = Vout5 active. Connected to input specified in VCR switch table.

1xxxxxxx = Vout5 set to 0V.

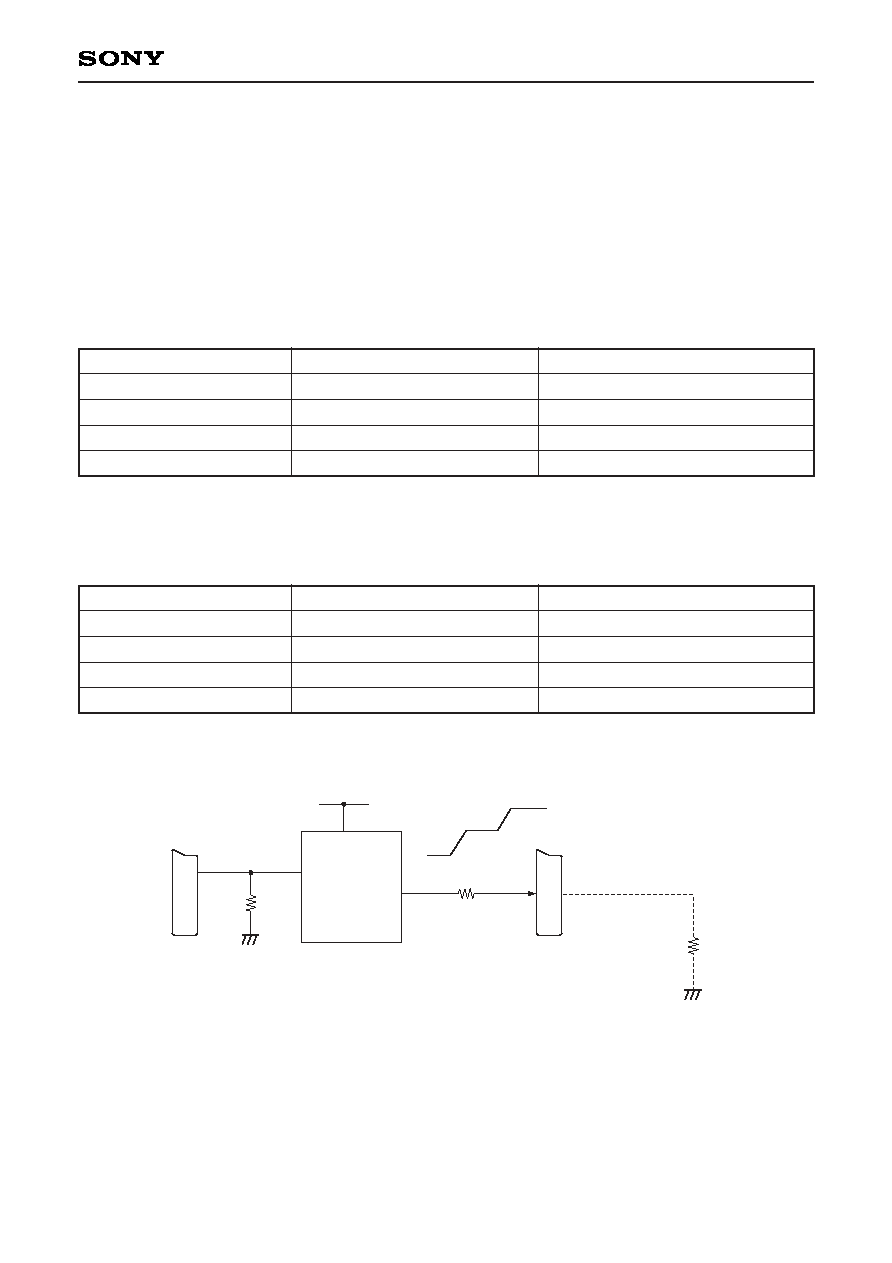

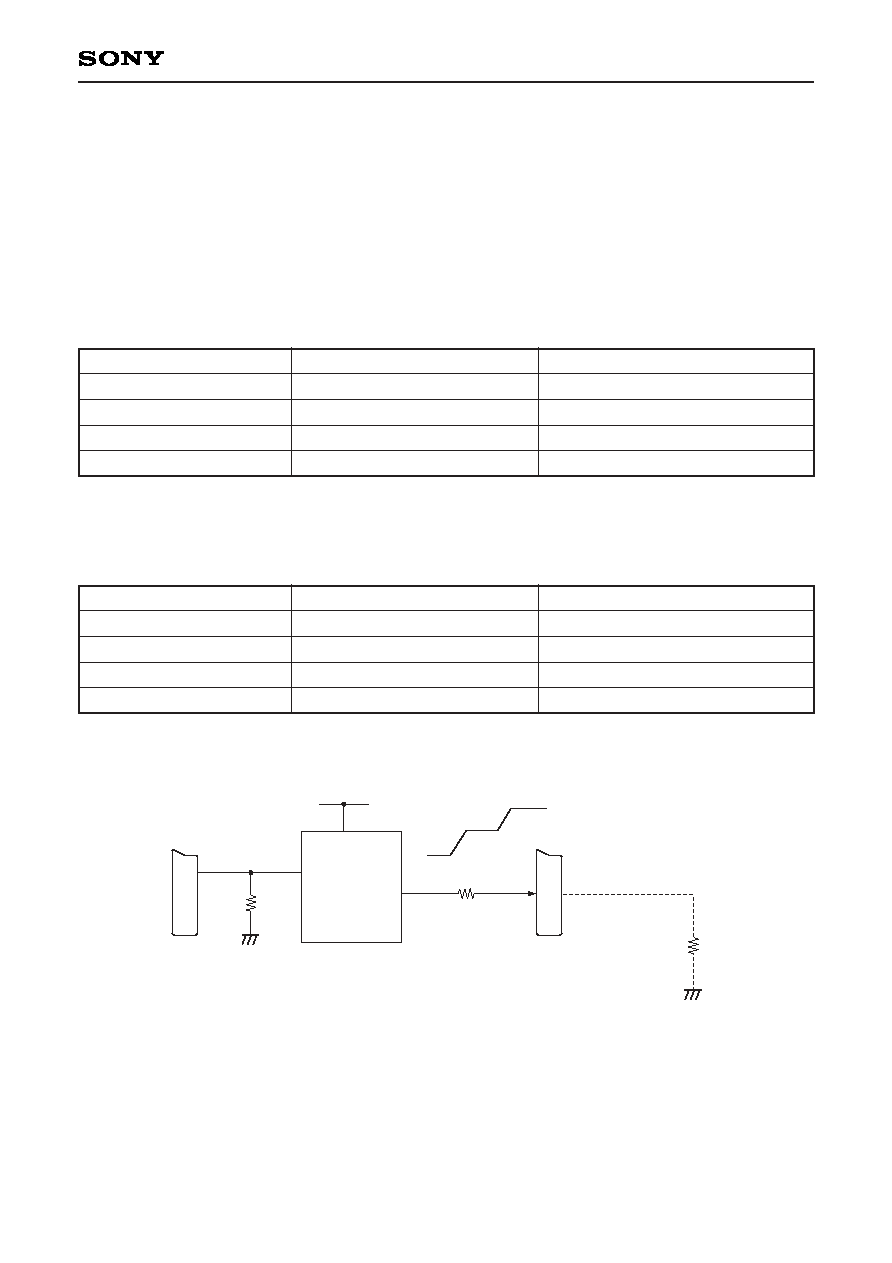

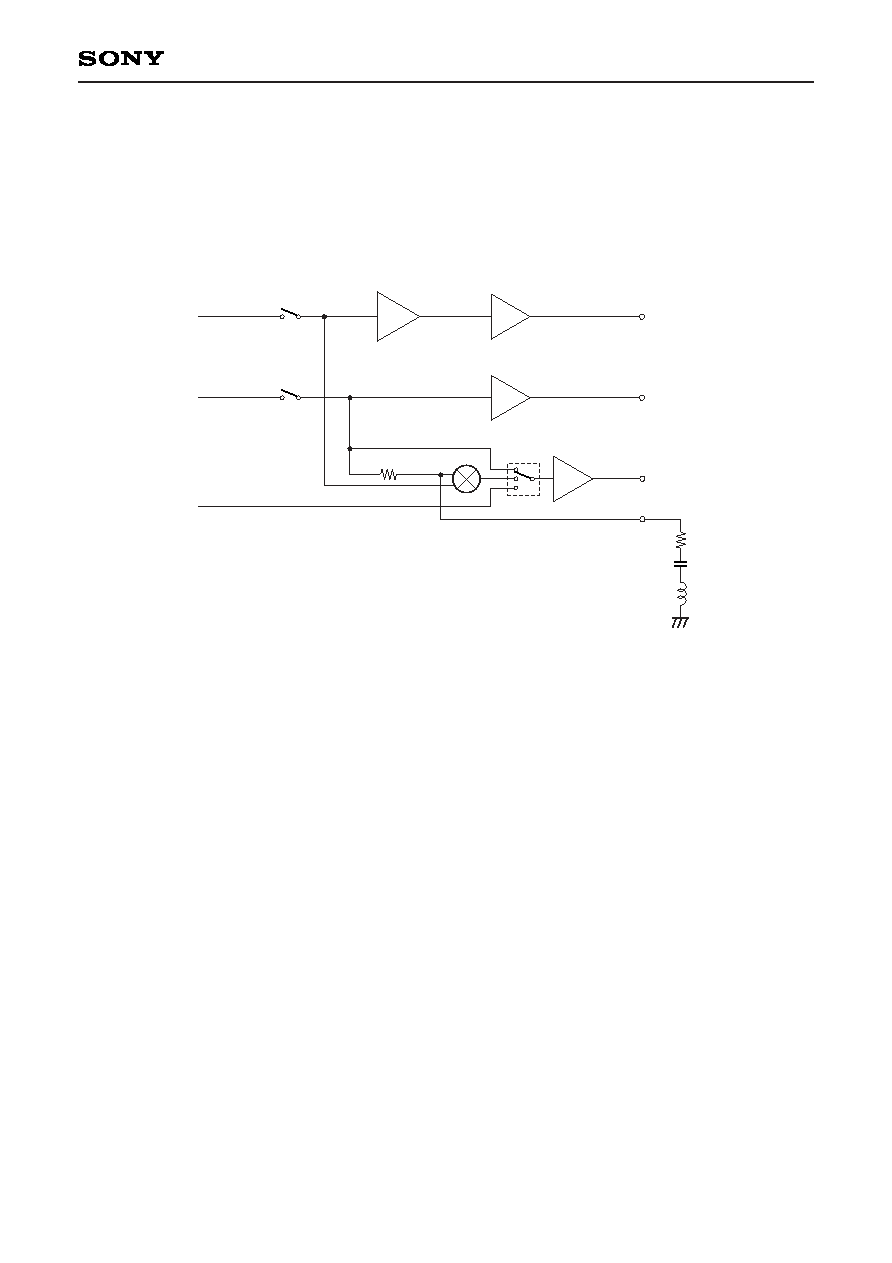

Fig 5. Bi-directional Line to VCR

As Pin 15 on the VCR scart can be bi-directional, either chroma output or red/chroma input, it is necessary for

output Vout5 to be individually controlled. When the red or chroma signal comes from the VCR, then output

Vout5 is set to 0V giving the required line termination impedance of 75

.

6dB

Vout5

0V

VCR Scart

Pin 15

Red in

Chroma in

Chroma out

VOUT_5

Chroma output

Red in

Chroma in

VIN_7

I = 10mA

(When set to 0V mode)

75

≠ 25 ≠

CXA7002R

I

2

C Audio Signal Control

TV and Phono Audio Control [Data 2 Bits 1, 2]

After power on Rin1/Lin1 are selected.

VCR Audio Control [Data 2 Bits 3, 4]

Switch setting

0

xxxxx00x

1

xxxxx01x

2

xxxxx10x

3

xxxxx11x

RTV, Phono_R

Rin1

Rin2

Rin3

Rin4

LTV, Phono_L

Lin1

Lin2

Lin3

Lin4

After power on Rin1/Lin1 are selected.

TV Mono Switch [Data 2 Bit 6]

Switch setting

0

xxx00xxx

1

xxx01xxx

2

xxx10xxx

3

xxx11xxx

Rout1

Rin1

RTV signal

Rin3

Rin4

Lout1

Lin1

LTV signal

Lin3

Lin4

Switch setting

0

x0xxxxxx

1

x1xxxxxx

Connection to R channel

output

R

(R + L mix)

Connection to L channel

output

L

(R + L mix)

Comment

Normal

Mono mix

VCR Mono Switch [Data 1 Bit 6]

Switch setting

0

x0xxxxxx

1

x1xxxxxx

Connection to R channel

output

R

(R + L mix)

Connection to L channel

output

L

(R + L mix)

Comment

Normal

Mono mix

"AUDIO DISABLE" [Data 3 Bit 4]

xxx0xxxx = Normal outputs

xxx1xxxx = All outputs disabled. When the outputs are disabled, they are in a high impedance state.

For a single supply configuration, the output voltage will drop to 0V.

"PHONO BYPASS" [Data 2 Bit 0]

xxxxxxx0 = Phono outputs connected after volume control block. (Default)

xxxxxxx1 = Phono outputs connected before volume control block.

≠ 26 ≠

CXA7002R

"TV VOL BYPASS" [Data 2 Bit 5]

xx0xxxxx = TV outputs connected after volume control block. (Default)

xx1xxxxx = TV outputs connected before volume control block.

"MONO SWITCH" [Data 2 Bit 7]

0xxxxxxx = Mono output connected to mix of TV R + L channels. (Default)

1xxxxxxx = Mono output connected to mix of RIN1 + LIN1 inputs.

"VOLUME CONTROL" [Data 1 Bits 1, 2, 3, 4, 5]

Setting

0

xx00000x

1

xx00001x

2

xx00010x

3

xx00011x

4

xx00100x

5

xx00101x

6

xx00110x

7

xx00111x

8

xx01000x

9

xx01001x

10

xx01010x

11

xx01011x

:

31

xx11111x

Volume gain

+6dB

+4dB

+2dB

0dB (power on default)

≠2dB

≠4dB

≠6dB

≠8dB

≠10dB

≠12dB

≠14dB

≠16dB

:

≠56dB

"OVERLAY ENABLE" [Data 3 Bit 0]

xxxxxxx0 = Overlay off (Power on default)

xxxxxxx1 = Overlay on: Rin3 and Lin3 are mixed and added to Rin1, Lin1 channels.

TV Mute and Zero Cross Operation

When the zero cross is switched on (ZCD = 1), volume control changes are only implemented when the audio

signal passes though the zero cross point. Similarly, when a mute instruction is sent, the TV outputs are only

muted when the signal passes the zero cross point. This eliminates any click noise.

There are two TV audio mute control bits in the bus map. By having two bits it allows the TV outputs to be

muted, the TV channel changed and then un-muted all in one I

2

C write operation. The normal structure for a

click free audio channel change is as follows:

Data 1: Mute the TV audio output with the ZCD switched on.

Data 2: Change the TV audio source.

Data 3: Un-mute the TV audio output again with the ZCD switched on.

≠ 27 ≠

CXA7002R

Operation of the Mute circuit

TV Audio Mute

[Data 1 Bit 0], [Data 3 Bit 7]

0

0

1

1

ZCD

[Data 3 Bit 5]

0

1

0

1

Operation

TV, Phono, Mono output

Un-mute immediately

Un-mute on next zero cross

Mute immediately

Mute on next zero cross

After power on TV Audio Mute = 1 and ZCD are set to 1.

"TV INPUT MUTE" [Data 3 Bit 6]

x0xxxxxx = The input to the TV switch is not muted.

x1xxxxxx = The input to the TV switch is muted. (Power on default)

"VCR INPUT MUTE" [Data 3 Bit 1]

xxxxxx0x = The input to the VCR switch is not muted.

xxxxxx1x = The input to the VCR switch is muted. (Power on default)

"AUDIO LIMITER" [Data 1 Bit 7]

When active, the output of the volume control block is limited to 2.2Vrms maximum.

0xxxxxxx = The volume control outputs are not limited. (Power on default)

1xxxxxxx = The volume control outputs are limited to 2.2Vrms.

≠ 28 ≠

CXA7002R

Fast Blanking Operation (Pin 16 on SCART), FBLK

The fast blanking signal instructs the TV to select either the external CVBS information or the external RGB

information. This is used to superimpose an on screen display (OSD) presentation (normally RGB) upon a

CVBS background. Fast blanking information has the same nominal phase as the RGB and CVBS signal, and

is defined as follows,

Fast blanking output at scart,

1. CVBS mode: Scart pin voltage = 0 to 0.4V

2. RGB mode: Scart pin voltage = 1 to 3.0V

The threshold voltage is approximately 0.75V at the scart input.

Fast Blanking I

2

C Control

In the CXA7002R has two fast blanking inputs, one associated with the digital encoder input (FBLK_IN1) and

another associated with the VCR RGB/CVBS input (FBLK_IN2). These can be selected and switched to the

output using an I

2

C instruction. In addition, the fast blank output pin can be set to a constant 0V or +3.5V by

means of the I

2

C control. Hence there are four possible states. These are set according to the following table.

"FAST_BLANK" [Data 4 Bits 0, 1]

I

2

C setting "BLANK_LEVEL"

0

xxxxxx00

1

xxxxxx01

2

xxxxxx10

3

xxxxxx11

Fast blank output pin voltage

0V (Power on default)

Same status as Fast Blank in 1 (0/+3.5V)

Same status as Fast Blank in 2 (0/+3.5V)

+3.5V

Fast Blank Output Interface

The Fast Blanking output pin is connected to the scart via a 75

resistor. Optional ESD protection circuitry can

be added.

Fig. 6. Fast Blanking Output Interface

TV_FBLK

0V/3.5V

75

75

Scart line 16

T.V.

CXA7002R

≠ 29 ≠

CXA7002R

Function Switching Operation (Pin 8 on scart)

Both, VCR and TV function lines can be set to outputs and controlled independently. The TV function line has

two modes, the first being control via I

2

C and secondly the follow mode where the output will follow the same

state as the VCR input.

When the VCR function lines is set as input, the level can be read back from the status resistor. An interrupt is

generated when the level changes.

"FNC TV_LEVEL" [Data 4 Bits 2, 3]

These bits set the voltage at the output TV_FNC function line (Pin 8).

Note) After power on the output is internal TV mode ie. 0V at the pin.

"FNC VCR_LEVEL" [Data 4 Bits 4, 5]

These bits set the voltage at the output VCR_FNC function line (Pin 8).

I

2

C control "FNC_TV"

0

xxxx00xx

1

xxxx01xx

2

xxxx10xx

3

xxxx11xx

Voltage at output

Follows VCR input

< 1V

> 4.5V, < 7V

> 9.5V

Mode

Follows VCR input

Internal TV

External scart input 16:9 mode

External scart input 4:3 mode

I

2

C control FNC_VCR

0

xx00xxxx

1

xx01xxxx

2

xx10xxxx

3

xx11xxxx

Voltage at output

NA

< 1V

> 4.5V, < 7V

> 9.5V

Mode

Input

Internal

External scart input 16:9 mode

External scart input 4:3 mode

Note) The power on default is "Input" mode.

Fig. 7. TV Function Switch Output

FNC_VCR

+12V_DIG

Inside T.V.

< 1V

> 9.5V

> 4.5V, < 7V

10k

Scart Pin 8

Scart Pin 8

330

maximum

FNC_TV

10k

≠ 30 ≠

CXA7002R

Logic and Interrupt Output Pins

These two pins are open collector type and require an external pull-up resistor.

Interrupt Output

The interrupt pin will become a current sink for approximately 1µs when the VCR input function line changes

from:

a) 0 to 6V, 6 to 0V b) 0 to 12V, 12 to 0V c) 6 to 12V, 12 to 6V

OR

When the sync detector detects that a valid video signal has been added or removed.

This pin will normally be connected to +5V through a 10k

resistor.

Multiple interrupt signal may be generated for signals on the threshold of having a valid sync.

Logic Output

The logic output level can be changed using the logic output bit in the I

2

C register, "LOGIC_LEVEL".

"LOGIC LEVEL" [Data 3 Bit 3]

xxxxx0xx = Current sink mode resulting in < 0.4V saturation voltage on logic pin. (default)

xxxxx1xx = Open collector/high output impedance on logic pin.

Imax during current sink = 1mA

Fig. 8. INT and Logic Line Interface

External resistors

10k

1µs

To Micro

+3 to +5V

INT

LOGIC

10k

≠ 31 ≠

CXA7002R

Read Mode Status Register

The following information can be read from the status register:

FNC VCR [Bits 0, 1]

The status register bits 0, 1 hold the level of the input function line.

Input pin voltage

FNC_VCR

SCART mode

Data 8

b1

b0

0 to +2V (default)

+4.5 to +7V

+9.5 to +12V

(Internal)

(16:9 External)

(4:3 External)

0

1

1

0

0

1

"SYNC DETECT" [Bit 2]

Once a valid sync signal is detected on the input selected by "SYNC_SELECT" this bit is set to 1. The bit is

reset to 0 every time the SYNC_SELECT is changed. It is assumed that when a video input is in-active then

the input level will be 0V with minimum noise.

"POD" (Power on Detect) [Bit 4]

This bit is set to 1 after power on. It is then changed to 0 after the first I

2

C read. It is used to detect if the supply

has been corrupted. If the POR bit is read as 1 at any time then the IC should be re-initialized to the correct

I

2

C settings.

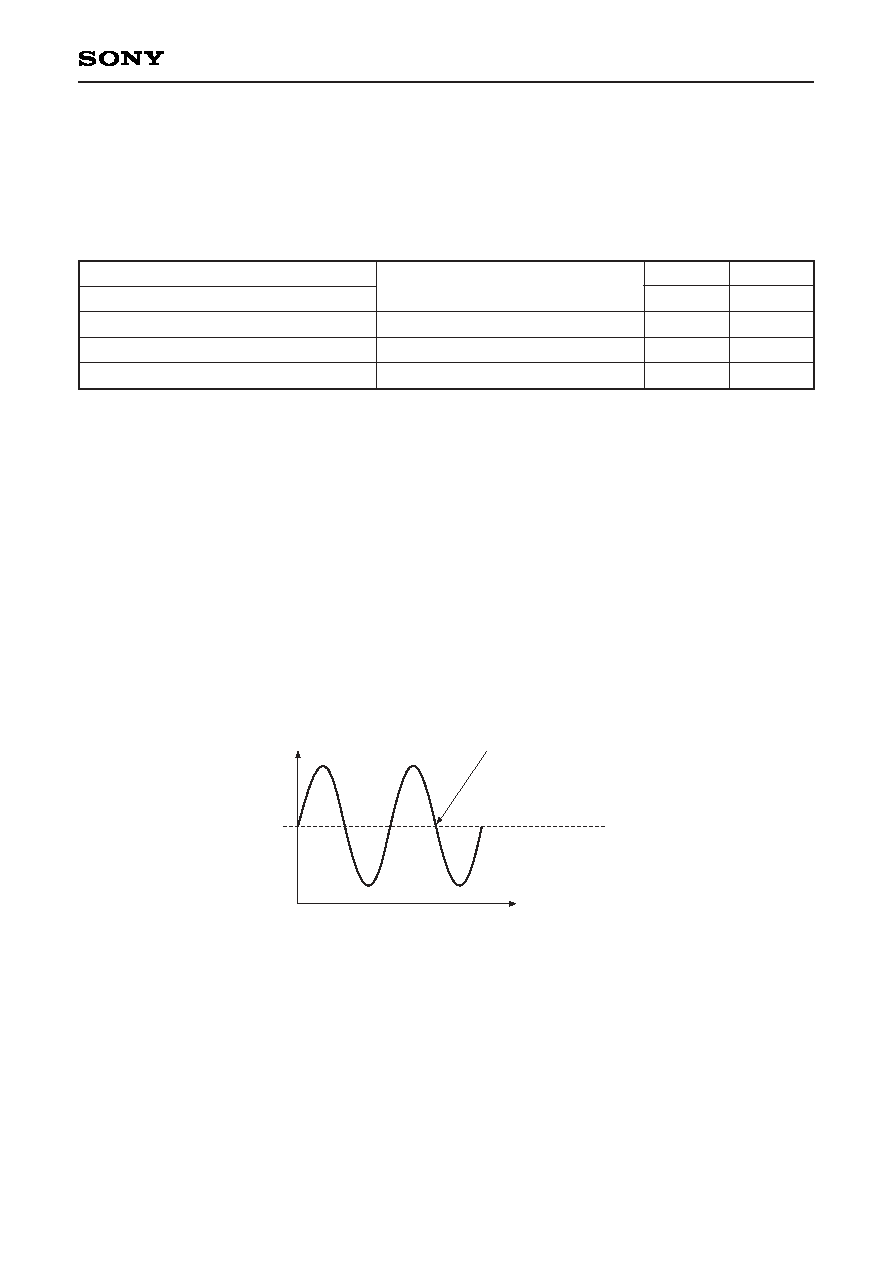

"ZERO CROSS STATUS" [Bit 5]

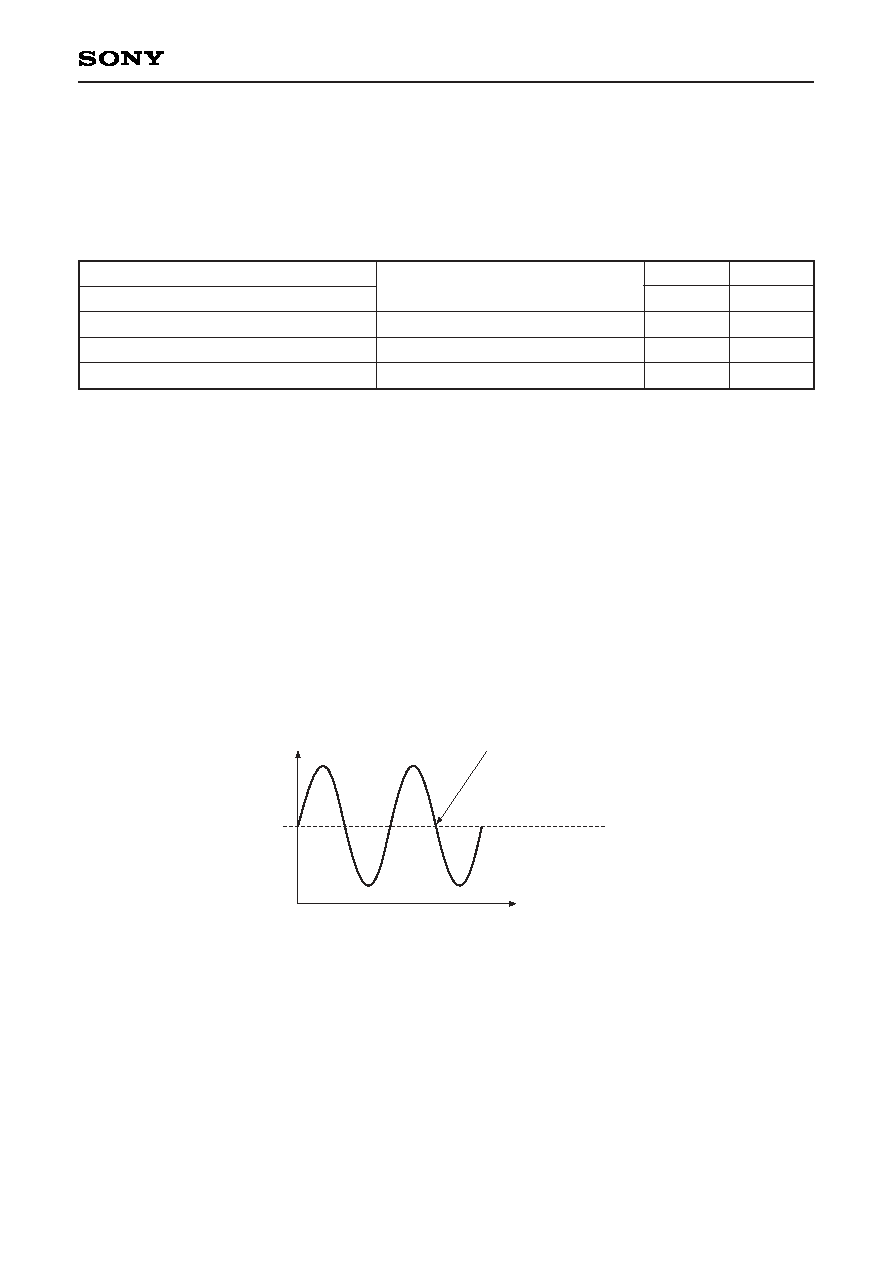

This audio function is used to determine if an input audio signal has passed the zero cross point.

Input signal

Bias voltage (2.5V)

Zero cross point

Fig. 9. Zero Cross Point

0 = No zero cross detected.

1 = Signal has passed through zero cross point.

Read

≠ 32 ≠

CXA7002R

Description of Operation

Video Section

Inputs and Outputs

The video section comprises of thirteen (13) high impedance inputs switched through to seven (7) video

outputs. An internal +6dB amplifier is connected to each output. The amplifier is required to compensate for the

6dB attenuation that occurs at the 75

series output resistor. Outputs VOUT_1 to VOUT_7 are capable of

driving 150

loads. Output VOUT_7 is designed to interface to an RF Modulator.

Composite/Luminance Inputs

The 4 composite (or luma) inputs are ac coupled to the input pins. The signals are first sync tip clamped to a

set level. These clamps are permanently active, therefore these inputs should only be used for signals with a

sync.

2.4V

0V

1Vp-p

V

CC

= +5V

Input signal

0.3V

0V

2Vp-p

V

CC

= +5V

Output signal

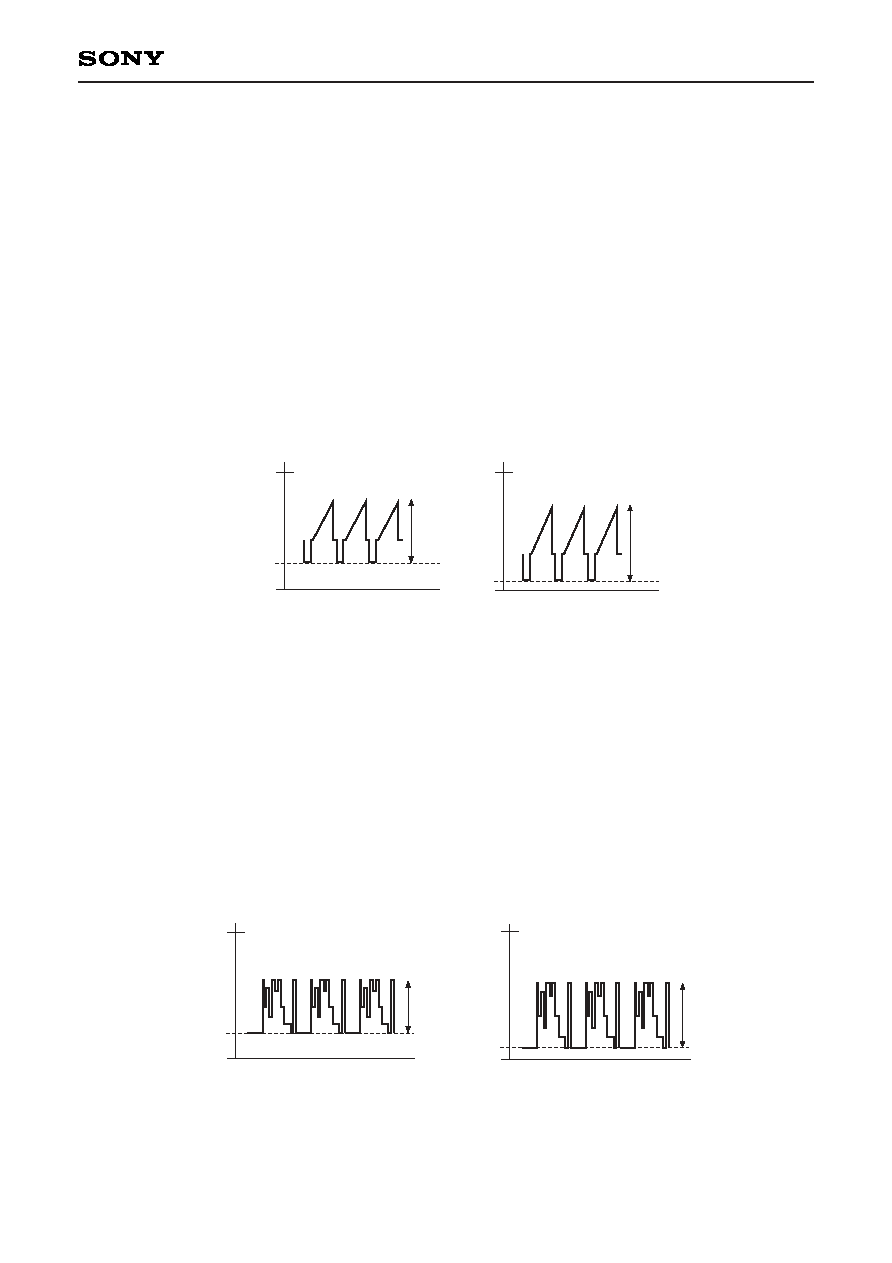

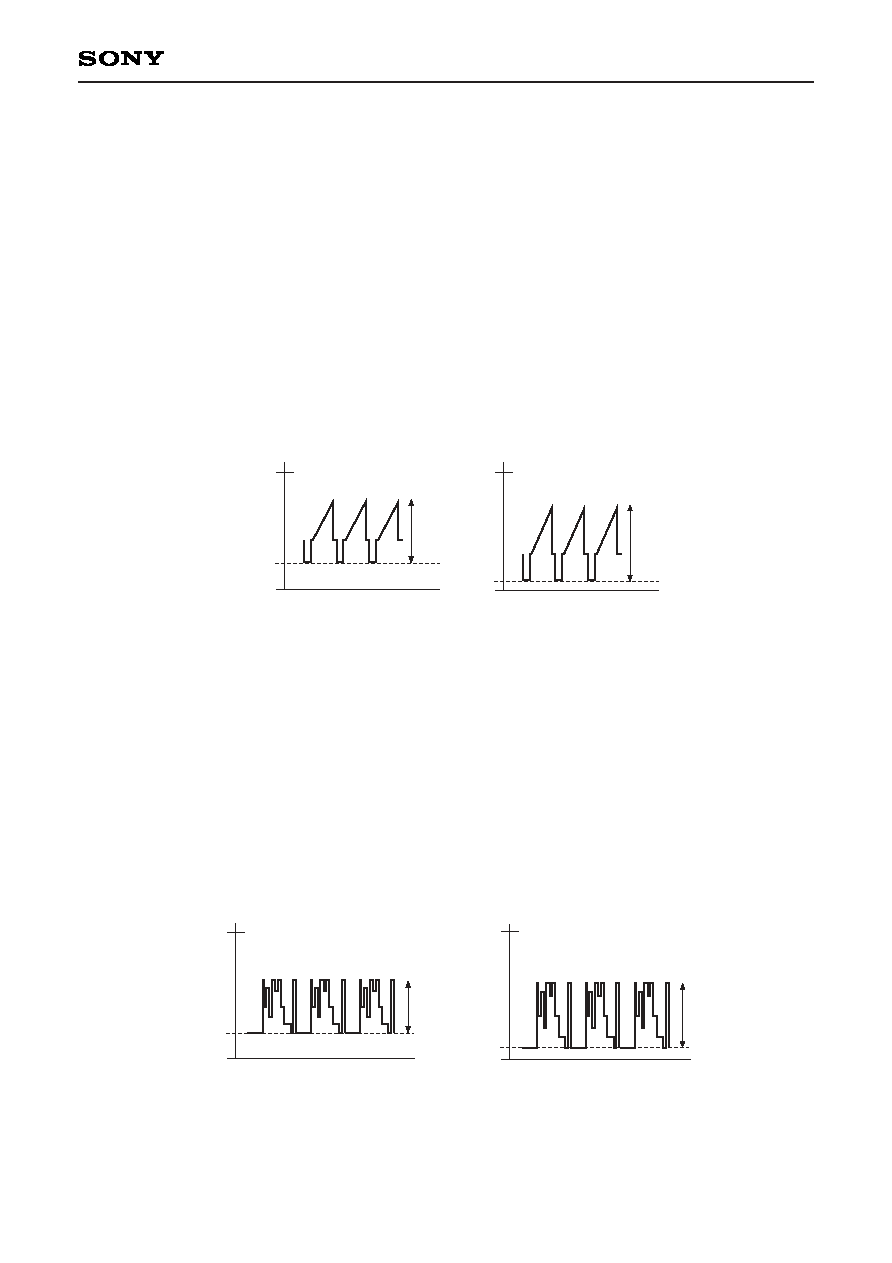

Fig. 10. CVBS/Y Waveforms

RGB Inputs

The RGB inputs are ac coupled to the input pins. The inputs have a dc restore circuit, which is used to set the

blanking level to a fixed voltage. The clamps are controlled by the timing signal provided by the sync detect

circuit. It is necessary to select the correct luma or CVBS signal associated with the RGB inputs for the sync

select circuit. It is assumed that a sync signal will not be present on any of the RGB input signals. For inputs

that can be either red or chroma then the clamp can be switched between the dc restore mode (for red input)

and average level bias (for chroma). The RGB signals are fed through additional gain amplifiers which are

controlled by I

2

C. These allow the nominal 0.7Vp-p signal to be increased to 0.8Vp-p, 0.9Vp-p or 1Vp-p. When

the TV output is in Y/C mode, the RGB gain should be set to 0dB to prevent over amplification of the chroma

output.

2.5V

0V

0.7Vp-p

V

CC

= +5V

Input signal

0.6V

0V

1.4Vp-p

V

CC

= +5V

Output signal

Fig. 11. RGB Waveforms

≠ 33 ≠

CXA7002R

Sync Detection Circuit

The clamp signals, used to restore the RGB level, are generated from the sync detect circuit. By using the

"SYNC_DETECT" control bits, the 4 different CVBS/Y inputs may be selected. Once selected, the signal is

compared with a threshold voltage 65mV above the tip level. If the signal is less than this threshold it is not

passed to the next block. If greater than the threshold, it is passed to the discrimination circuit which checks

that the duty cycle is greater than 91%. The discrimination block also contains a time constant which, when a

sync is detected, holds the status line high for at least 7 video lines. If a valid sync signal is detected the

"SYNC_DETECT" bit in the read register is set to 1.

Comparator

Duty

Discrimination

LOGIC

DIG CVBS/Y

DIG CVBS/Y

VCR CVBS/Y

A

U

X CVBS/Y

RGB input clamp timing

"SYNC_SELECT"

Interupt Control

Status register

"SYNC_DETECT" bit

I

2

C

Sync detect circuit

External R/C

SYNC_ID

GND_VID

+5V_VID

68k

0.1µF

Fig. 12. Sync Detection Circuit

Chroma Inputs

The chroma signals are ac coupled to the input pins. The inputs have a fixed dc bias that sets the average level

to approximately 3.1V for VIN_5 & VIN_7 and 2.45V for VIN_6 & VIN_13. For inputs that can also be RED

signals the input circuit can be switched to the dc restore mode.

Typical waveforms:

2.45V or 3.1V

0V

0.7Vp-p

V

CC

= +5V

Chroma input pin signal

1.8V

0V

1.4Vp-p

V

CC

= +5V

Chroma output pin voltage

Fig. 13. Chroma Waveforms

≠ 34 ≠

CXA7002R

Video Input Gain Stage

The six inputs from the digital encoder, VIN_1, 3, 5, 6, 8, 9 may need further amplification. An adjustable gain

stage is provided with settings of +1, 3, 6dB extra gain. For normal inputs (1Vp-p for CVBS, 0.7Vp-p for RGB),

the gain section may be bypassed.

Video Input filters

To reduce any digital noise, the six inputs from the digital encode pass through a low pass filter. The filter has

a high attenuation at the clock frequency of 27MHz.

Fig. 14. Basic Filter Response

27MHz

freq

5MHz

≠30dB

0dB

±0.3dB

≠ 35 ≠

CXA7002R

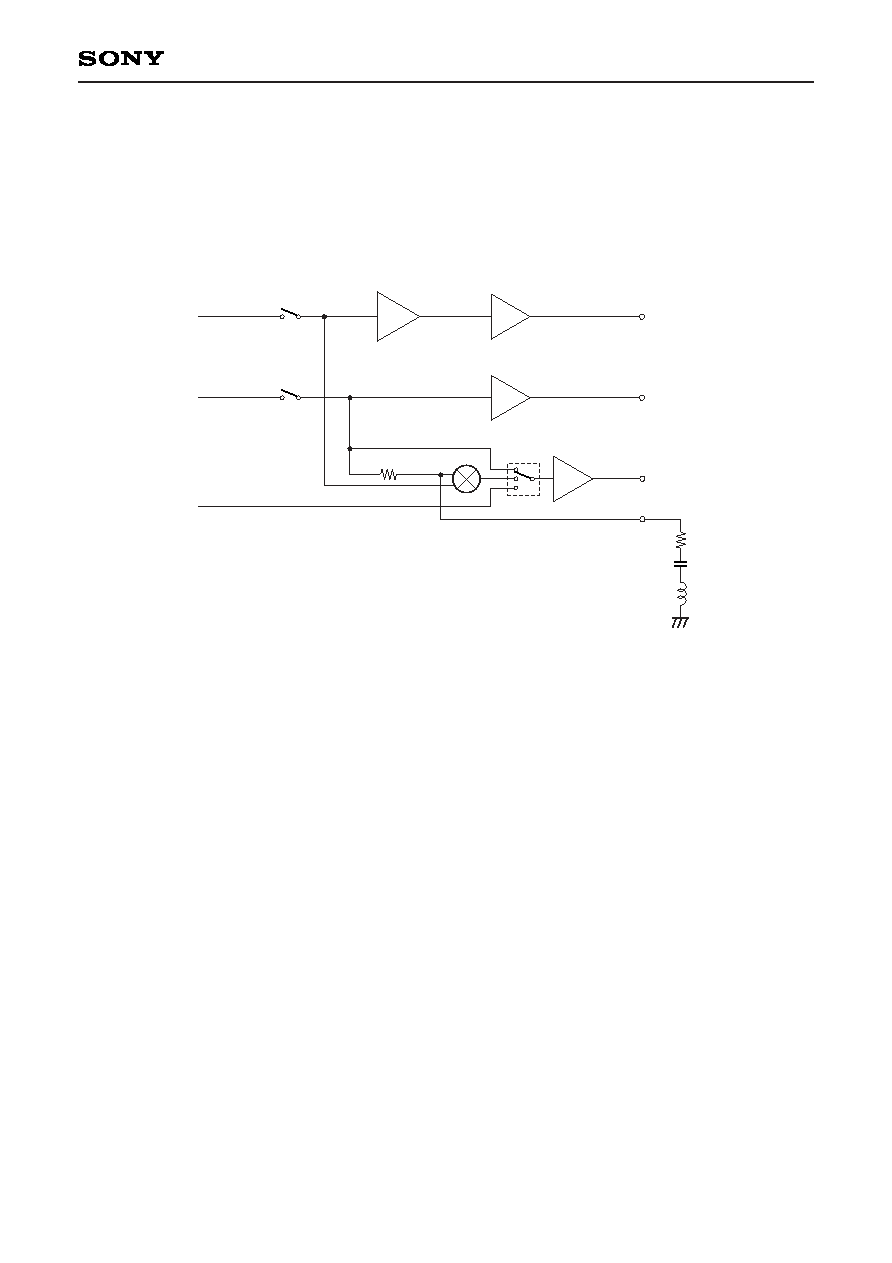

Y/C Mixer

A Y/C mixer can be used for mixing Luma and Chroma signals for use with an external RF modulator

connected to VOUT_7. The Y/C mixer is controlled via the I

2

C data bus. The signal may be a mix of the TV Y/C

signals or simply the TV CVBS signal. It is also possible to select the CVBS signal from the digital encoder. The

circuit is shown in Fig. 15 with a trap circuit used to give 6dB attenuation at 4.43MHz of the Luma signal.

6dB

0, 1, 2 or 3dB

VIN_8 = CVBS

R/C

CVBS/Y

VOUT_3

VOUT_4

VOUT_7

TRAP

Mixer

switch

For recommended values:

see application circuit.

6dB

R

C

L

2k

6dB

Fig. 15. Internal Y/C Mixer Circuit

Switching the Video Outputs Off

Each video output can be individually turned off using the I

2

C. When turned off, the output is set to a high

impedance state and hence the current consumption and power dissipation is reduced. After power on, all the

video outputs are set to the high impedance state.

≠ 36 ≠

CXA7002R

Typical Video Interface Circuits

Single or Dual Supply

75

(Line C = 400pF max.)

75

Scart

VOUT_1 to VOUT_7

100nF

75

Scart

VIN_1 to VIN_13

Fig. 16. Video Input Interface

Fig. 17. Video Output Interface

≠ 37 ≠

CXA7002R

Audio Section

Inputs and Outputs

The audio system consists of 4 stereo inputs, 2 stereo outputs and separate mono and Phono outputs. The

stereo outputs can be connected to any one of the 4 stereo inputs. All audio inputs have a ≠12dB attenuator

except RIN_1 and LIN_1. Therefore, as an amplifier having +12dB of gain follows the interval switch, the net

gain of the audio system from input to output is 0dB. The stereo input RIN_1/LIN_1 has fixed gain from input to

output of +6dB. This input is typically connected to an audio DAC with full scale of 1Vrms or less.

The output impedance of each audio amplifier is near zero. The output may be directly coupled to the scart for

the dual supply case but must be ac coupled through a capacitor (typically 10µF) for the single supply case.

The outputs are capable of driving 600

loads. The user may add additional low pass filters to the outputs.

TV Output Switching

The TV audio section is composed of an audio switch followed by a volume control stage. The volume is

adjustable from +6dB to ≠56dB in 2dB steps. The volume control block includes a switchable limiter function to

prevent the output signals exceeding 2.2Vrms. When activated, the output signals from the volume control

block will be clamped to 2.2Vrms. A mono switch that allows the mixed R + L signal to be switched to the R

and L output channels follows the volume control section.

TV Mute

This I

2

C mute function acts on the TV, Phono and Mono audio circuits. Audio mute will be implemented after an

audio zero cross detection to reduce click noise if "ZCD" = 1.

Zero Cross Detector (ZCD)

The zero cross detector reduces the effect of "click noise" when implementing a volume change or an audio

mute. The volume change or mute instruction sent by I

2

C will only be implemented when a minimal (ie zero

cross) signal amplitude is detected.

It can be seen from the I

2

C write format that the same mute bit occurs in DATA1 and DATA3. This allows the

software to action a mute, then after a delay (1/Audio_freq (min)) make any suitable changes to the audio

source and then un-mute the output buffer. Such a period provides ample time to allow any audio signals to

pass the zero cross point before the signal source is changed.

VCR Output Switching

The outputs ROUT1, LOUT1 have a fixed gain of 0dB from the input except when position 2 is selected.

Position 2 selects the RTV and LTV signals. These signals are affected by the TV volume control.

Phono outputs

There is a stereo Phono output that carries the same signal as the TV output. This is typically used for

connection to a hi-fi. The signal level of the Phono outputs is normally the same as the TV outputs however it is

possible to bypass the volume section and set the Phono outputs to a fixed level. If any attenuation is required

then this can be done externally.

≠ 38 ≠

CXA7002R

Mono Output

The mono output for the RF modulator has two settings. The first is a mix of the TV R + L channels. In this

case, the output signal will have the same volume control as the RTV/LTV outputs. The second setting is a mix

of the audio DAC inputs (RIN_1 + LIN_1). In this setting the output will always have fixed volume and if the

tone overlay is used, this will appear on the output.

Audio Overlay

The inputs RIN_3, LIN_3 may be used for a normal stereo audio input or alternatively to overlay an external

audio source onto the TV outputs. This may be a tone or voice. The R and L inputs are mixed and then added

equally to the RIN_1 and LIN_1 inputs. The I

2

C control bit "AUDIO OVERLAY ENABLE" is used to switch on

this facility.

Audio Disable

All the audio outputs may be disabled using the "Audio Output Disable" function (Data Byte 3 Bit 4). This

disable mode is different from the normal mute as it puts the outputs into a high impedance state. The disable

mode is different from the normal mute as it can be used for power reduction in standby modes.

Hardware Mute

The hardware mute input pin is used to instantaneously mute all the audio outputs. It has the same operation

as the audio disable function. The outputs are muted when the pin goes below +2V.

≠ 39 ≠

CXA7002R

Typical Audio Interface Circuits

Supply type 1: Dual supply

Scart

RIN_1, 2, 3, 4

LIN_1, 2, 3, 4

0.1µF

Fig. 18. Audio Input Interface

Scart

To RF modulator

Optional protection

resistor

600

to 10k

(Line C = 400pF max.)

600

to 10k

(Line C = 400pF max.)

Optional protection

resistor

RTV, LTV

ROUT1, LOUT1

PHONO_R,

PHONO_L

MONO

Fig. 19. Audio Output Interface

Supply type 2: Single supply

Fig. 20. Audio Input Interface

Fig. 21. Audio Output Interface

Scart

RIN_1, 2, 3, 4

LIN_1, 2, 3, 4

0.1µF

Scart

To RF modulator

For loads = 600

, larger capacitors may be needed

10µF

600

to 10k

(Line C = 400pF max.)

600

to 10k

(Line C = 400pF max.)

RTV, LTV

ROUT1, LOUT1

PHONO_R,

PHONO_L

MONO

10µF

≠ 40 ≠

CXA7002R

Application in Set Top Box

VIN_1

B

B

VOUT_1

G

VOUT_2

R/C

VOUT_3

CVBS/Y

VOUT_4

TV_FBLK

FNC_TV

FAST BLANKING

FUNCTION SWITCH

C

VOUT_5

CVBS/Y

VOUT_6

CVBS

VOUT_7

VIN_3

G

VIN_5

R

VIN_8

CVBS

VIN_6

C

VIN_9

FBLK_IN1

Y

FAST BLANKING

VIN_2

B

VIN_11

CVBS

VIN_12

CVBS/Y

VIN_13

C

VIN_4

G

VIN_7

R/C

VIN_10

FBLK_IN2

FNC_VCR

CVBS/Y

FAST BLANKING

FUNCTION SWITCH

Digital

Encoder

VCR

VCR

RF

MOD.

T.V.

T.V.

AUX

Inputs

Outputs

A/V switch

Fig. 22. Video Application with 6 Output Digital Encoder

VIN_1

B

B

VOUT_1

G

VOUT_2

R/C

VOUT_3

CVBS/Y

VOUT_4

TV_FBLK

FNC_TV

FAST BLANKING

FUNCTION SWITCH

C

VOUT_5

CVBS/Y

VOUT_6

CVBS

VOUT_7

VIN_3

G/CVBS

VIN_5

R/C

VIN_8

FBLK_IN1

CVBS/Y

FAST BLANKING

VIN_6

VIN_9

C

CVBS/Y

VIN_2

B

VIN_11

CVBS

VIN12

CVBS/Y

VIN13

C

VIN_4

G

VIN_7

R/C

VIN_10

FBLK_IN2

FNC_VCR

CVBS/Y

FAST BLANKING

FUNCTION SWITCH

Digital

Encoder

VCR

Analogue

Sat.

VCR

RF

MOD.

T.V.

T.V.

AUX

Inputs

Outputs

A/V switch

Fig. 23. Video Application with 4 Output Digital Encoder

≠ 41 ≠

CXA7002R

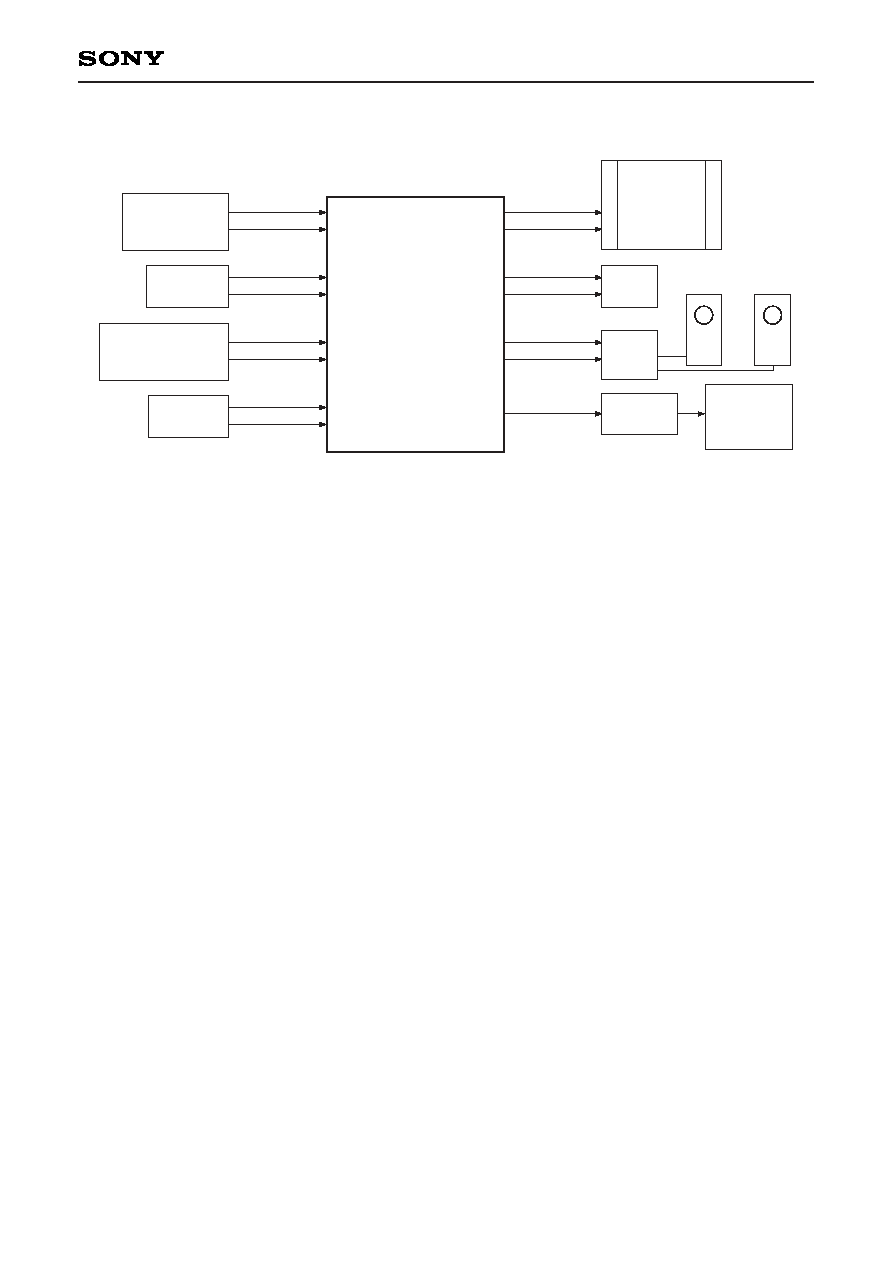

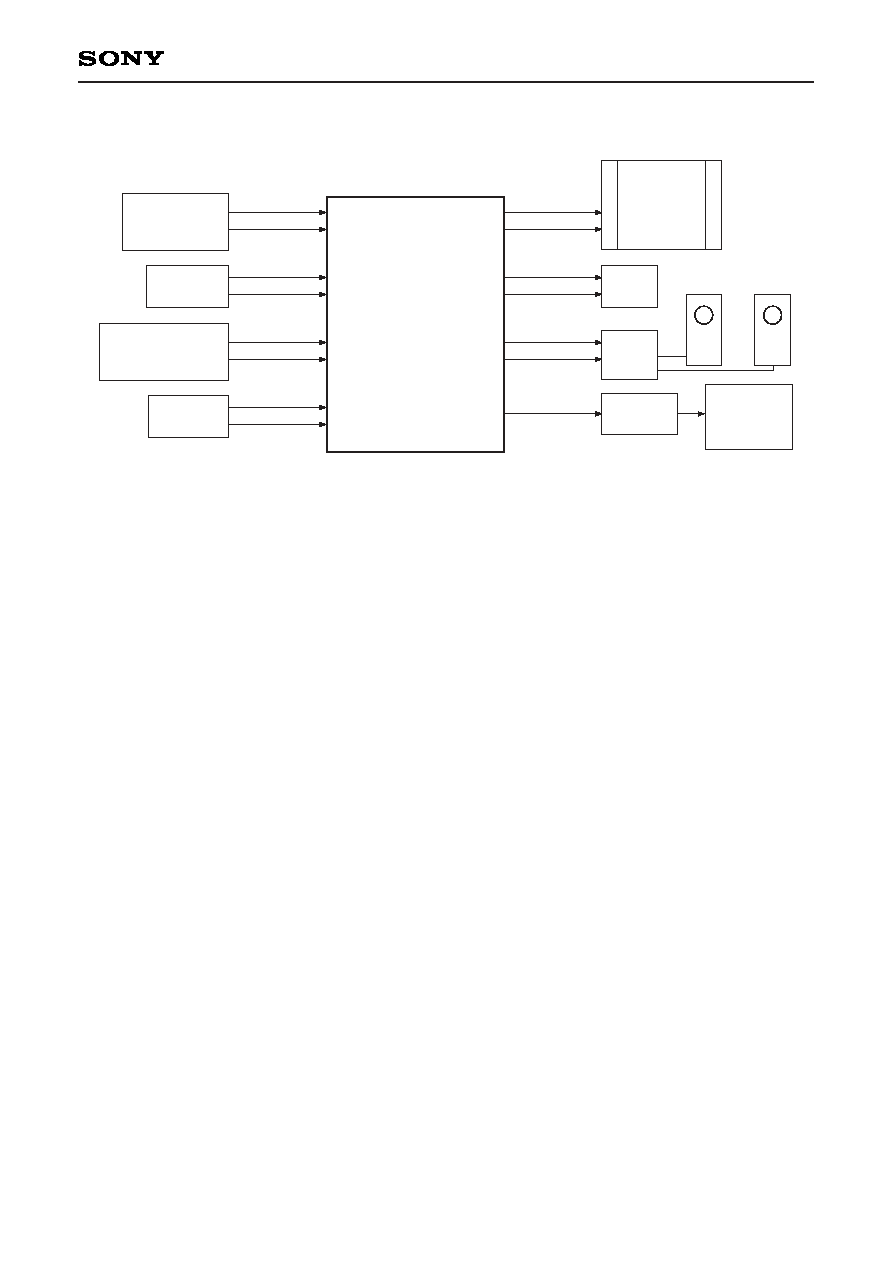

Audio Application

STB Audio DAC

fs = 1Vrms

RIN_1

LIN_1

VCR

fs = 2Vrms

RIN_2

LIN_2

TV or

STB Generated Voice/

Tone

RIN_3

LIN_3

AUX

fs = 2Vrms

RIN_4

LIN_4

RTV

LTV

ROUT1

LOUT1

PHONO_R

PHONO_L

TV

(Mono)

MONO

TV

L

R

VCR

Hi-Fi

RF

Modulator

L

R

Fig. 24. Audio Application

≠ 42 ≠

CXA7002R

Supply Connections

Fig. 25. Dual Supply

+12V (±0.6V)

≠5V (±0.25V)

+5V (±0.25V)

+5V/12V_V

CC

A

+12V

+5V_DIG

+5V_VID

GND_VID

GND_DIG

≠5V_GNDA

AUD_BIAS

(Pin 26)

+5V_VOUT

VID_BIAS

0.1µF

22µF

AUD_BIAS

(Pin 46)

GND

+12V (±0.6V)

+5V (±0.25V)

+5V/12V_V

CC

A

+12V

+5V_DIG

+5V_VID

GND_VID

GND_DIG

≠5V_GNDA

+5V_VOUT

VID_BIAS

0.1µF

GND

AUD_BIAS

(Pin 26)

22µF

AUD_BIAS

(Pin 46)

22µF

Fig. 26. Single Ended Supply

≠ 43 ≠

CXA7002R

Application Circuit 1

Single Supply

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

75

75

330

330

VCR_FBLANK

VCR_FNC

TV_FBLANK

TV_FNC

TV_ROUT

TV_LOUT

TV_BLUE

RF_VD

75

TV_GREEN

DIG BLUE

DIG GREEN

DIG RED/

CHROMA

DIG CHROMA

DIG CVBS

DIG LUMA

+12V

+5V

10µF

LOUT1

ROUT1

10µF

MONO

10µF

PHONO_R

10µF

22µF

VCR_LOUT

10µF

10k

10µF

100nF

+12V

+5V

+12V

+5V

SUPPLIES

4 HEADER

PHONO_L

+5V/12V_V

CC

A

TV SCART

21

19

TV_CVBS_OUT

17

15

TV_RED/C

13

11

TV_GREEN

9

7

TV_BLUE

5

3

TV_LOUT

1

TV_ROUT

20

TV_CVBS_IN

18

16

TV_FBLANK

14

12

10

8

TV_FNC

6

TV_LIN

4

2

TV_RIN

VCR SCART

SKT1

SKT2

21

19

VCR_CVBS_OUT

17

15

VCR_RED/C

13

11

VCR_GREEN

9

7

VCR_BLUE

5

3

VCR_LOUT

1

VCR_ROUT

20

VCR_CVBS_IN

18

16

VCR_FBLANK

14

12

10

8

VCR_FNC

6

VCR_LIN

4

2

VCR_RIN

≠5V_GNDA

AUD_BIAS

GND_DIG

+5V_DIG

FBLK_IN2

FNC_VCR

TV_FBLK

FBLK_IN1

HW_MUTE

FNC_TV

+12V

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

RIN_4

LIN_4

VIN_7

VIN_10

VIN_4

VIN_2

VIN_13

VIN_12

VIN_11

+5V_VID

GND_VID

VOUT_5

VOUT_6

VOUT_4

VOUT_3

+5V_

VOUT

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

GND_AUD

V

CC

_AUD

≠5V_GNDA

GND

SDA

SCL

INTERUPT

RIN_1

LIN_1

100nF

TV_RIN

VCR_LIN

VCR_RIN

VCR_ROUT

TV_LIN

SYNC_ID

RIN_2

LIN_2

AUD_BIAS

RIN_3

LIN

_3

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

RTV

LTV

LOGIC

≠5V_GNDA

GND

VIN_9

VIN_8

VIN_6

VIN_5

VIN_3

VIN_1

VID_BIAS

TRAP

VOUT_7

VOUT_1

VOUT_2

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

+5V

+5V

RF MODULATOR

SCL

SDA

DIGITAL RIN1

DIGITAL LIN1

RF_VID

MONO

PHONO R

PHONO L

FAST

BLANKING

INPUT

1

2

+5V

75

75

+5V

TV_CVBS_IN

75

75

75

75

AUX CHROMA

AUX AUDIO R

AUX CVBS

VCR_RED/C

VCR_CVBS_IN

VCR_GREEN

VCR_BLUE

75

75

75

75

75

10k

+5V

68k

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

VCR_RED/C

VCR_CVBS_OUT

TV_CVBS_OUT

TV_RED/C

100nF

100nF

100nF

100nF

100nF

100nF

100nF

22µF

22µF

10µF

100nF

AUX AUDIO L

100nF

22µF

Place Close to

Supply Pins 24, 58, 64

Place Close to

Supply Pins 17, 28

100nF

100µH

2

1

100nF

10µF

12pF

1.8k

75

75

1

2

3

4

10k

≠ 44 ≠

CXA7002R

Application Circuit 2

Dual Supply

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

75

75

330

330

VCR_FBLANK

VCR_FNC

TV_FBLANK

TV_FNC

TV_ROUT

TV_LOUT

TV_BLUE

RF_VD

75

TV_GREEN

DIG BLUE

DIG GREEN

DIG RED/

CHROMA

DIG CHROMA

DIG CVBS

DIG LUMA

+12V

+5V

10µF

LOUT1

ROUT1

10µF

MONO

10µF

PHONO_R

10µF

VCR_LOUT

10µF

10k

10µF

100nF

+5V

+5V

PHONO_L

+5V/12V_V

CC

A

TV SCART

21

19

TV_CVBS_OUT

17

15

TV_RED/C

13

11

TV_GREEN

9

7

TV_BLUE

5

3

TV_LOUT

1

TV_ROUT

20

TV_CVBS_IN

18

16

TV_FBLANK

14

12

10

8

TV_FNC

6

TV_LIN

4

2

TV_RIN

VCR SCART

SKT1

SKT2

21

19

VCR_CVBS_OUT

17

15

VCR_RED/C

13

11

VCR_GREEN

9

7

VCR_BLUE

5

3

VCR_LOUT

1

VCR_ROUT

20

VCR_CVBS_IN

18

16

VCR_FBLANK

14

12

10

8

VCR_FNC

6

VCR_LIN

4

2

VCR_RIN

≠5V_GNDA

AUD_BIAS

GND_DIG

+5V_DIG

FBLK_IN2

FNC_VCR

TV_FBLK

FBLK_IN1

HW_MUTE

FNC_TV

+12V

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

RIN_4

LIN_4

VIN_7

VIN_10

VIN_4

VIN_2

VIN_13

VIN_12

VIN_11

+5V_VID

GND_VID

VOUT_5

VOUT_6

VOUT_4

VOUT_3

+5V_

VOUT

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

GND_AUD

V

CC

_AUD

≠5V_GNDA

GND

SDA

SCL

INTERUPT

RIN_1

LIN_1

100nF

TV_RIN

VCR_LIN

VCR_RIN

VCR_ROUT

TV_LIN

SYNC_ID

RIN_2

LIN_2

AUD_BIAS

RIN_3

LIN

_3

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

RTV

LTV

LOGIC

≠5V_GNDA

GND

VIN_9

VIN_8

VIN_6

VIN_5

VIN_3

VIN_1

VID_BIAS

TRAP

VOUT_7

VOUT_1

VOUT_2

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

+5V

≠5V

+5V

RF MODULATOR

SCL

SDA

DIGITAL RIN1

DIGITAL LIN1

RF_VID

MONO

PHONO R

PHONO L

FAST

BLANKING

INPUT

1

2

≠5V

+5V

75

75

+5V

TV_CVBS_IN

75

75

75

75

AUX CHROMA

AUX AUDIO R

AUX CVBS

VCR_RED/C

VCR_CVBS_IN

VCR_GREEN

VCR_BLUE

75

75

75

75

75

10k

+5V

68k

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

VCR_RED/C

VCR_CVBS_OUT

TV_CVBS_OUT

TV_RED/C

100nF

100nF

100nF

100nF

100nF

100nF

22µF

10µF

100nF

AUX AUDIO L

100nF

100µH

2

1

100nF

10µF

12pF

1.8k

75

75

10k

+12V

+5V

SUPPLIES

4 HEADER

100nF

22µF

100nF

22µF

Place Close to

Supply Pins 24, 58, 64

Place Close to

Supply Pins 17, 28

100nF

22µF

Place Close to

Supply Pins 13, 27, 36

≠5V

1

2

3

4

≠5V

≠ 45 ≠

CXA7002R

Notes on Operation

1) Supply de-coupling capacitors, 10nF and 10µF in parallel should be inserted as close as possible to the

supply Pins 17, 24, 28, 35, 58 and 64. When using the dual supply configuration apply the capacitors to

Pins 13, 27, 36 in addition to the listed supply pins.

2) To minimize crosstalk, attention should be given to the routing of audio and video to the IC inputs. PCB

track lengths should be kept as short as possible and preferably, audio placed on a separate layer to the

video.

3) Attention should be given to the electrolytic capacitors on the output pins. In single supply configuration

the audio pin dc bias voltage will be approximately 6.0V, therefore the positive terminal of the capacitors

should be orientated towards the device pin.

4) To minimize stray capacitance the 75

series resistor on video outputs VOUT_1 to VOUT_7 should be

mounted as close as possible to the device Pins 1, 2, 3, 60, 61, 62 and 63.

5) Pins 10, 11, 46, 52, 56, 57 have reduced ESD performance and external protection circuitry may be

added. As shown in the application schematic, zener diodes may be added. Zener diodes with a rating > 5V

may be used.

≠ 46 ≠

CXA7002R

Typical Performance Curves

7

6

5

1

Gain [dB]

Frequency [MHz]

Video gain ≠ VOUT_1, 2, 3, 4, 5, 6

10

100

4

3

2

1

0

VOUT_1, 2, 3