| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXB1567Q | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Description

The CXB1567Q achieves the 2R optical-fiber

communication receiver functions (Reshaping and

Regenerating) on a single chip. This IC is also

equipped with the signal interruption alarm output

function, which is used to discriminate the existence

of data input.

Features

∑ Auto-offset canceller circuit

∑ Signal interruption alarm outputs

∑ Single 5V power supply

Applications

∑ SONET/SDH: 622.08Mb/s

∑ Fiber channel: 531.25Mb/s

Absolute Maximum Ratings

∑ Power supply

V

CC

≠ V

EE

≠0.3 to +7.0

V

∑ Storage temperature

Tstg

≠65 to +150

∞C

∑ Input voltage difference: | V

D

≠ V

D

|

Vdif

0.0 to +2.5

V

∑ Input voltage

Vi

≠0.3 to V

CC

V

∑ Output current

(Continuous)

I

O

0 to 50

mA

(Surge current)

0 to 100

mA

Recommended Operating Conditions

∑ Supply voltage

V

CC

≠ V

EE

5.0 ± 0.5

V

∑ Operating temperature

Ta

≠40 to +85

∞C

∑ Termination resistor (Q/Q)

R

T1

45 to 55

∑ Termination resistor (SD/SD)

R

T2

45 to 55

∑ Termination voltage

V

CC

≠ V

TT

1.8 to 2.2

V

Structure

Bipolar silicon monolithic IC

≠ 1 ≠

CXB1567Q

E94709A63-ST

Limiting Amplifier for Optical Fiber Communication Receiver

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

48 pin QFP (Plastic)

For the availability of this product, please contact the sales office.

≠ 2 ≠

CXB1567Q

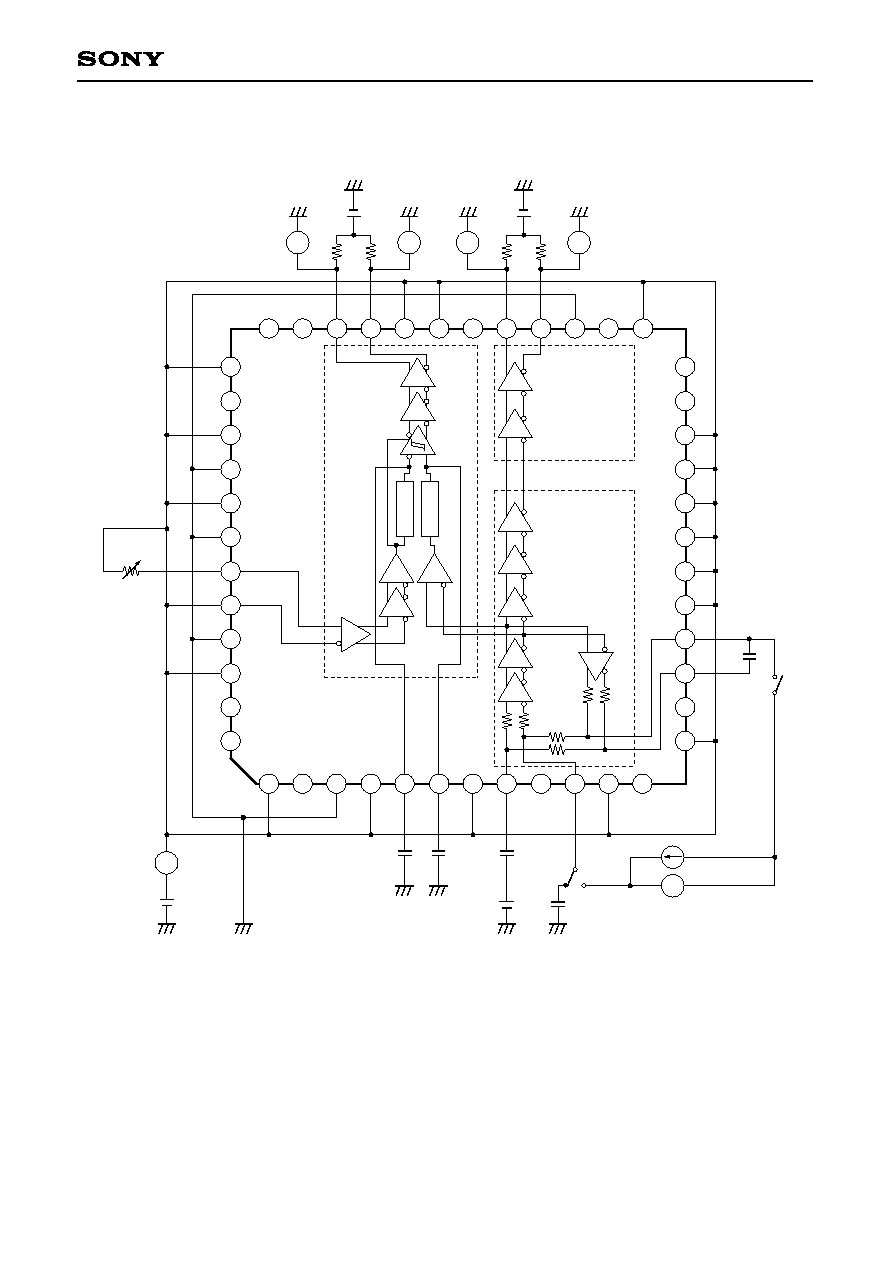

Block Diagram and Pin Configuration

Output

Buffer

Block

Alarm

Block

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

36

35

34

31

32

33

40

39

38

37

41

42

43

44

45

46

47

48

Peak Hold2

Limiting Amplifier Block

Peak Hold1

R2

R1

R3

R2

R3

R1

2

3

4

5

6

7

8

9

10

11

12

1

N.C.

N.C.

V

EE

D

V

EE

D

V

EE

D

V

EE

D

V

EE

D

V

EE

D

CAP1

N.C.

V

EE

CAP1

V

EE

N.C.

V

EE

D

V

CC

D

V

EE

D

V

CC

D

UP

DOWN

V

CC

A

V

EE

A

N.C.

N.C.

N.C.

N.C.

SD

SD

V

EE

D

V

EE

D

N.C.

Q

Q

V

CC

DA

N.C.

V

EE

V

EE

N.C.

V

CC

A

V

EE

A

CAP3

CAP2

V

EE

A

D

N.C.

D

V

EE

A

N.C.

≠ 3 ≠

CXB1567Q

Capacitance connection pins for

alarm block peak hold circuit.

Connect each pin to V

CC

in

2000pF.

CAP2 pin

Peak hold

capacitance

connection pin for

the limiting

amplifier signal

CAP3 pin

Peak hold

capacitance

connection pin for

the alarm

level setting block

Negative power supply pin for

analog block.

Limiting amplifier input pins

Ensure that these inputs are

AC-coupled.

Negative power supply pin for

analog block.

No connection.

≠1.8V

≠5V

≠0.9V

to

≠1.7V

DC

AC

Typical pin

voltage (V)

Symbol

Pin

No.

Pin Description

1

2

3

4

V

EE

N.C.

V

CC

A

V

EE

A

≠5V

0V

≠5V

Negative power supply pin.

No connection.

Positive power supply pin for

analog block.

Negative power supply pin for

analog block.

Negative power supply pin for

digital block.

7

V

EE

A

≠5V

8

D

≠1.3V

9

N.C.

10

D

≠1.3V

11

V

EE

A

12

N.C.

13

V

EE

≠5V

Negative power supply pin.

14

N.C.

No connection.

15

CAP1

16

CAP1

≠1.8V

17 to 22

V

EE

D

≠5V

No connection.

23, 24

N.C.

25

V

EE

≠5V

Negative power supply pin.

5

CAP3

≠1.8V

6

CAP2

≠1.8V

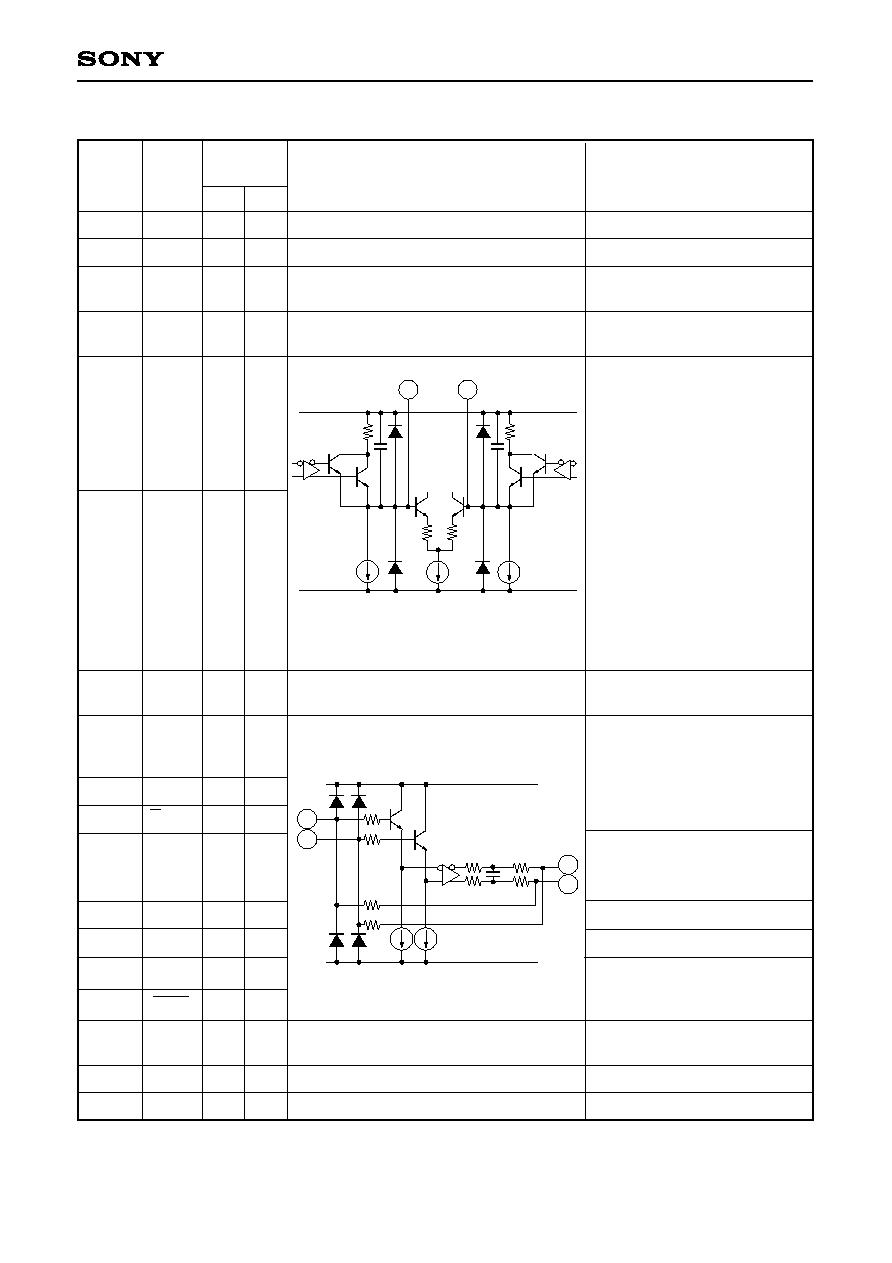

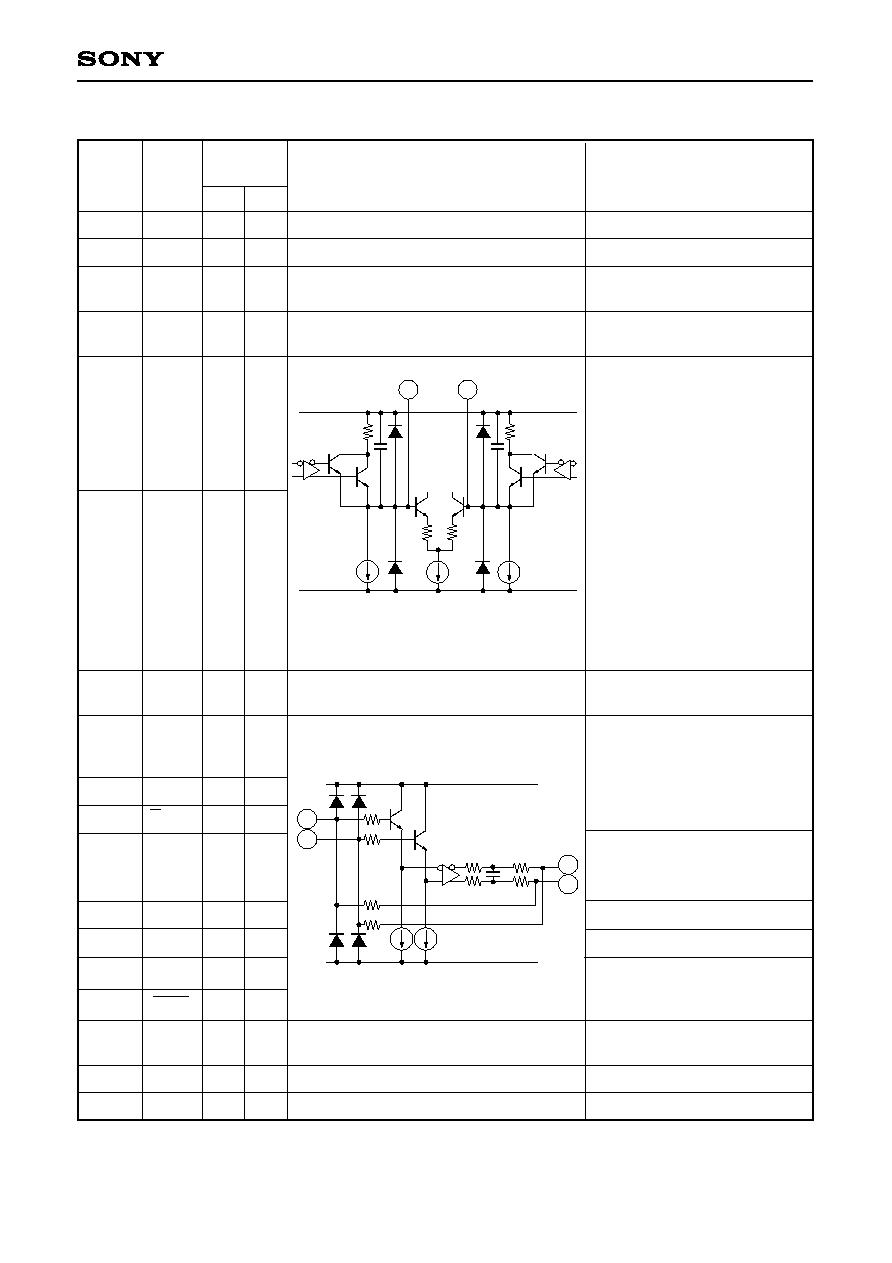

Description

V

CC

A

V

EE

A

100

100

1K

1K

7.5k

7.5k

130p

200

200

8

10

15

16

V

CC

A

V

EE

A

80

40µA

40µA

10p

10p

80

5

6

Capacitance connection pins to

determine the cut-off frequency

for feedback block.

Equivalent circuit

≠ 4 ≠

CXB1567Q

42

Typical pin

voltage (V)

Pin

No.

28

Q

≠0.9V

to

≠1.7V

29

Q

30

N.C.

≠0.9V

to

≠1.7V

≠0.9V

to

≠1.7V

≠0.9V

to

≠1.7V

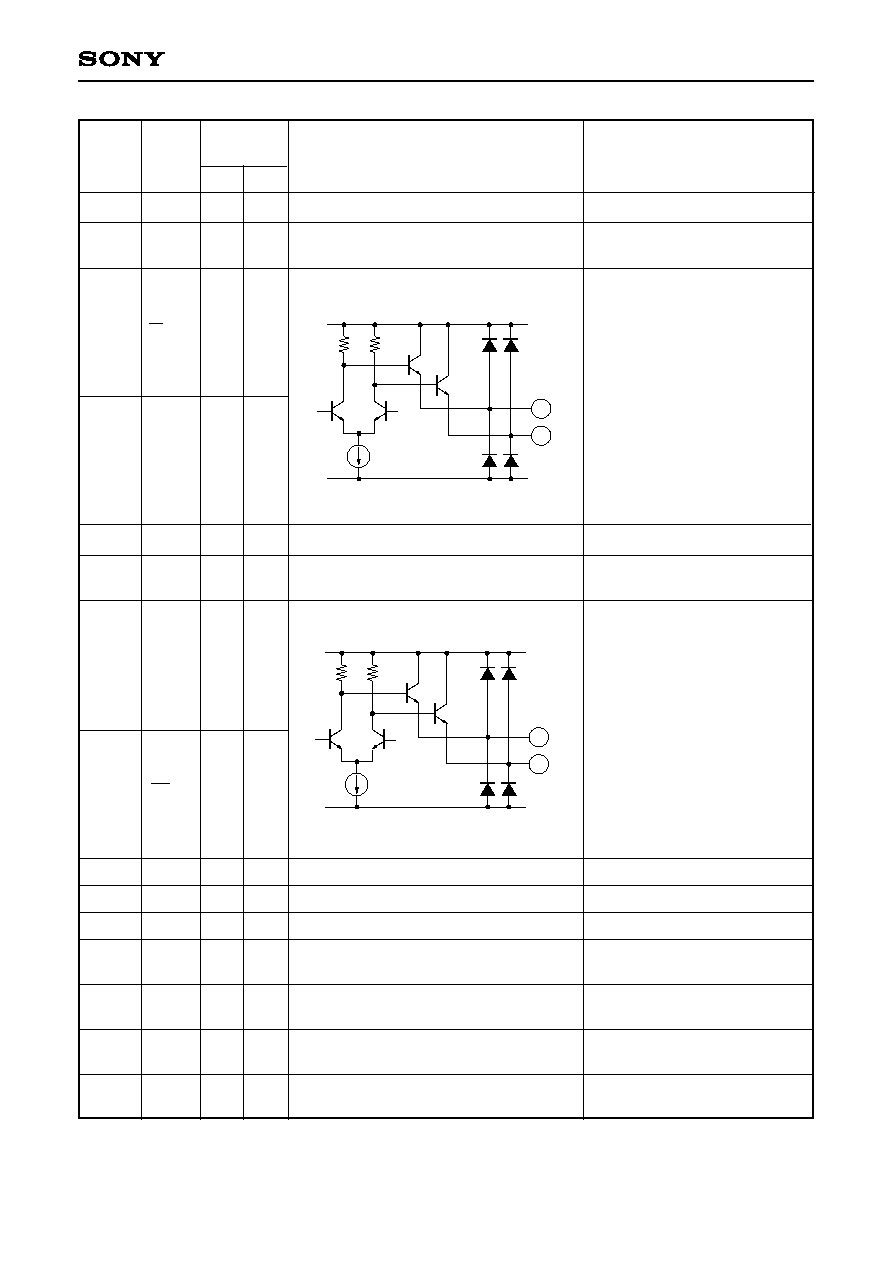

Data signal output pins.

Terminate these pins in 50

at

VTT = ≠2V.

No connection.

Negative power supply pin for

digital block.

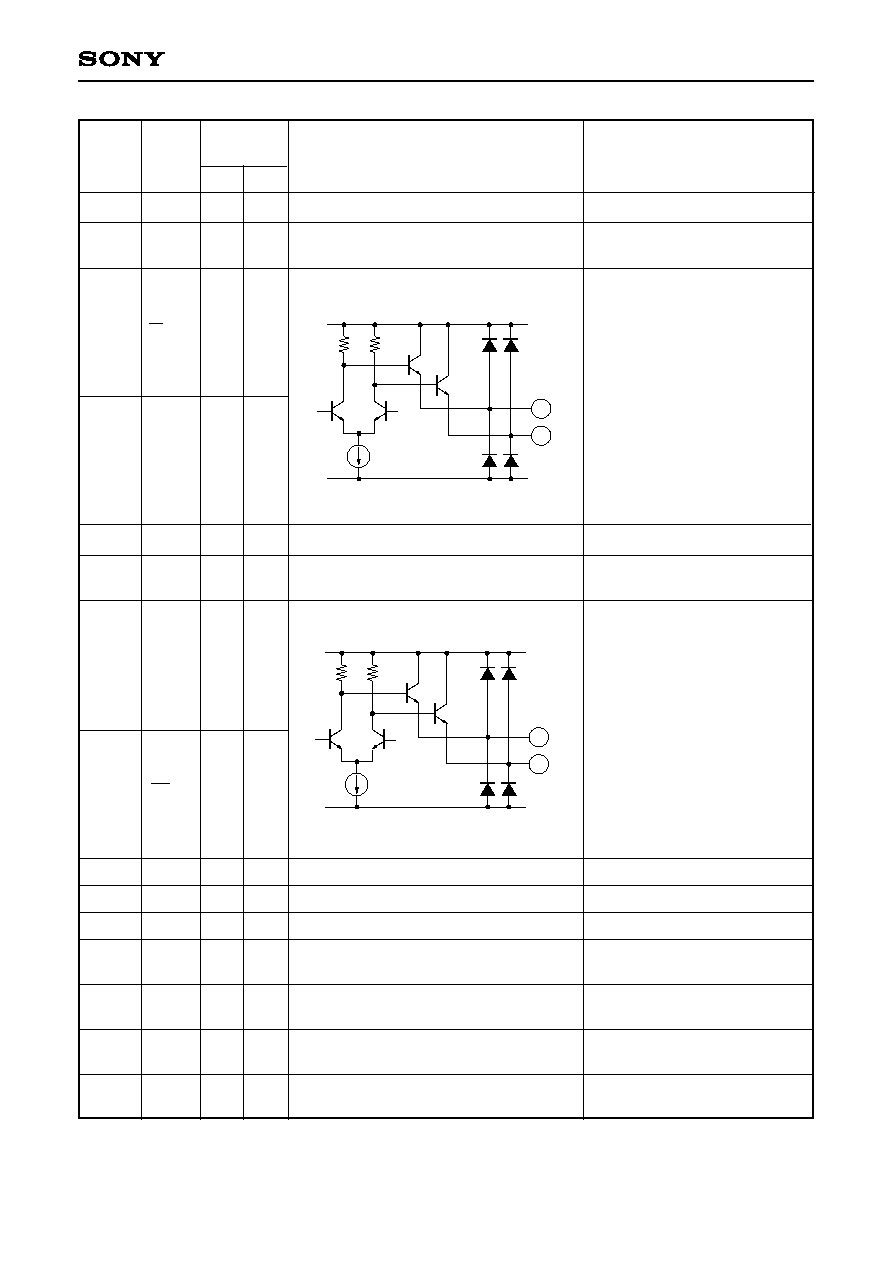

Symbol

DC

AC

Equivalent circuit

Description

V

EE

D

V

CC

DA

28

29

33

SD

31, 32

V

EE

D

≠5V

No connection.

35, 36

N.C.

Negative power supply pin.

37

V

EE

≠5V

No connection.

38

N.C.

Negative power supply pin for

digital block.

Negative power supply pin for

digital block.

Positive power supply pin for

digital block.

Positive power supply pin for

digital block.

39

V

EE

D

≠5V

40

V

CC

D

0V

41

V

EE

D

≠5V

V

CC

D

0V

34

SD

Alarm signal output pins.

Terminate these pins in 50

at

VTT = ≠2V.

V

EE

D

V

CC

DA

33

34

27

V

CC

DA

0V

Positive power supply pin for

output buffer.

26

N.C.

No connection.

≠ 5 ≠

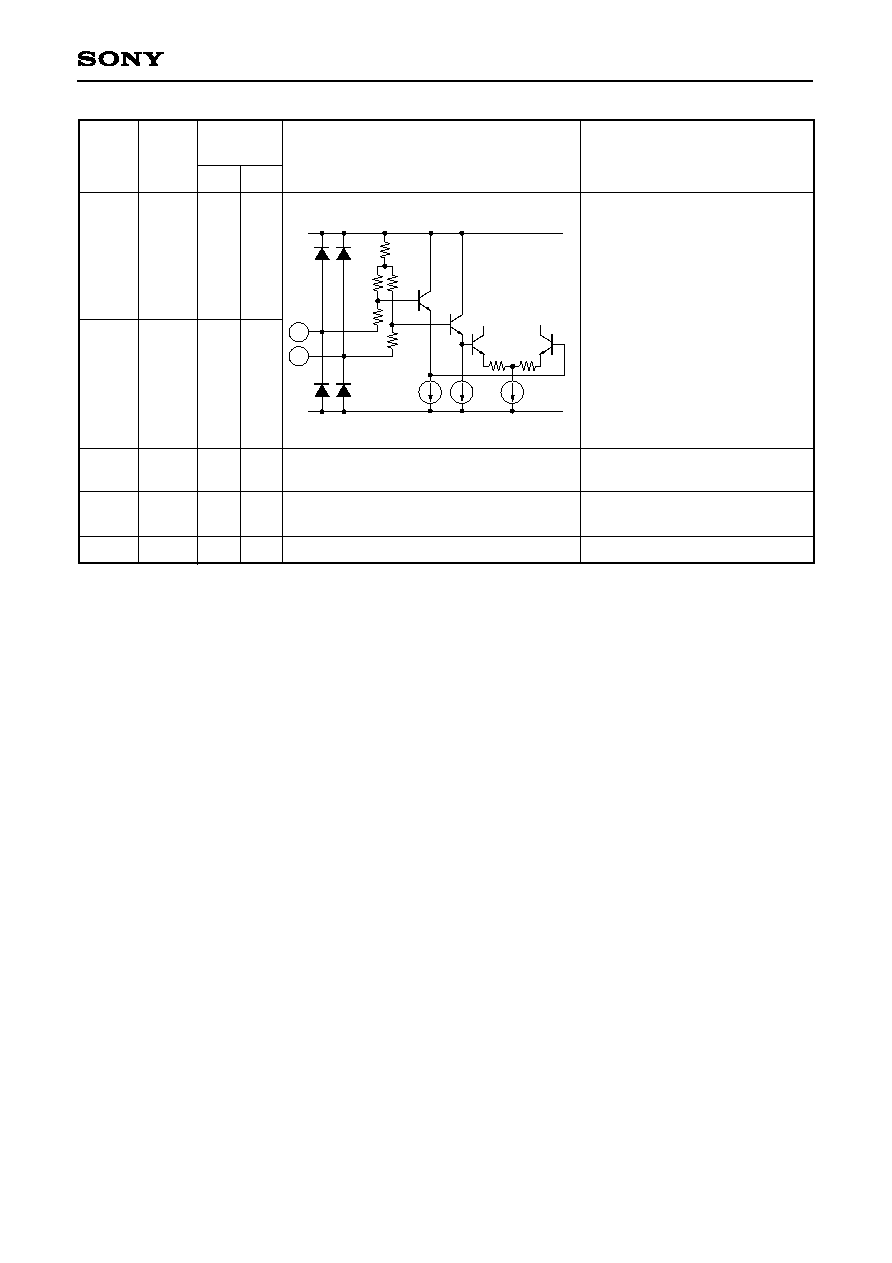

CXB1567Q

0V

Pin

No.

Description

43

UP

≠4.7V

44

DOWN

45

V

CC

A

≠5V

Resistor connection pins for alarm

level setting.

UP pin

When the

resistance

connected to this

pin is increased, the

alarm level

becomes higher.

DOWN pin

Normally

connect this pin

to V

EE

.

Positive power supply pin for

analog block.

Negative power supply pin for

analog block.

No connection.

Symbol

Typical pin

voltage (V)

DC

AC

Equivalent circuit

1k

100

100

V

EE

A

V

CC

A

5k

5k

43

44

46

V

EE

A

47, 48

N.C.

≠5V

≠ 6 ≠

CXB1567Q

Unit

450

450

8

100

100

B

V

MAX

GL

T

TLH

T

THL

V

MIN

Hys

T

AS

T

DAS

Mbps

mVpp

dB

ps

mVpp

dB

µs

Maximum input data rate

Maximum input voltage

Limiting amplifier gain

Q/Q rise time

Q/Q fall time

Identification maximum voltage

amplitude of alarm level

Hysteresis width

Alarm response assert time

Alarm response deassert time

Single-ended input voltage at D

IC internal amplitude 400mVpp

20% to 80%

Electrically tested

Low

High

1

(SD)

High

Low

2

(SD)

622.08

1000

66

20

4

0

2.5

240

240

6

∑ AC characteristics (

VCC = VCCA = 0V, VEED= VEEA= VEE = ≠5V±10%, Ta = ≠40∞C to +85∞C, RT = 50

, VTT = ≠2V)

Item

Symbol

Conditions

Min.

Typ.

Max.

Electrical Characteristics

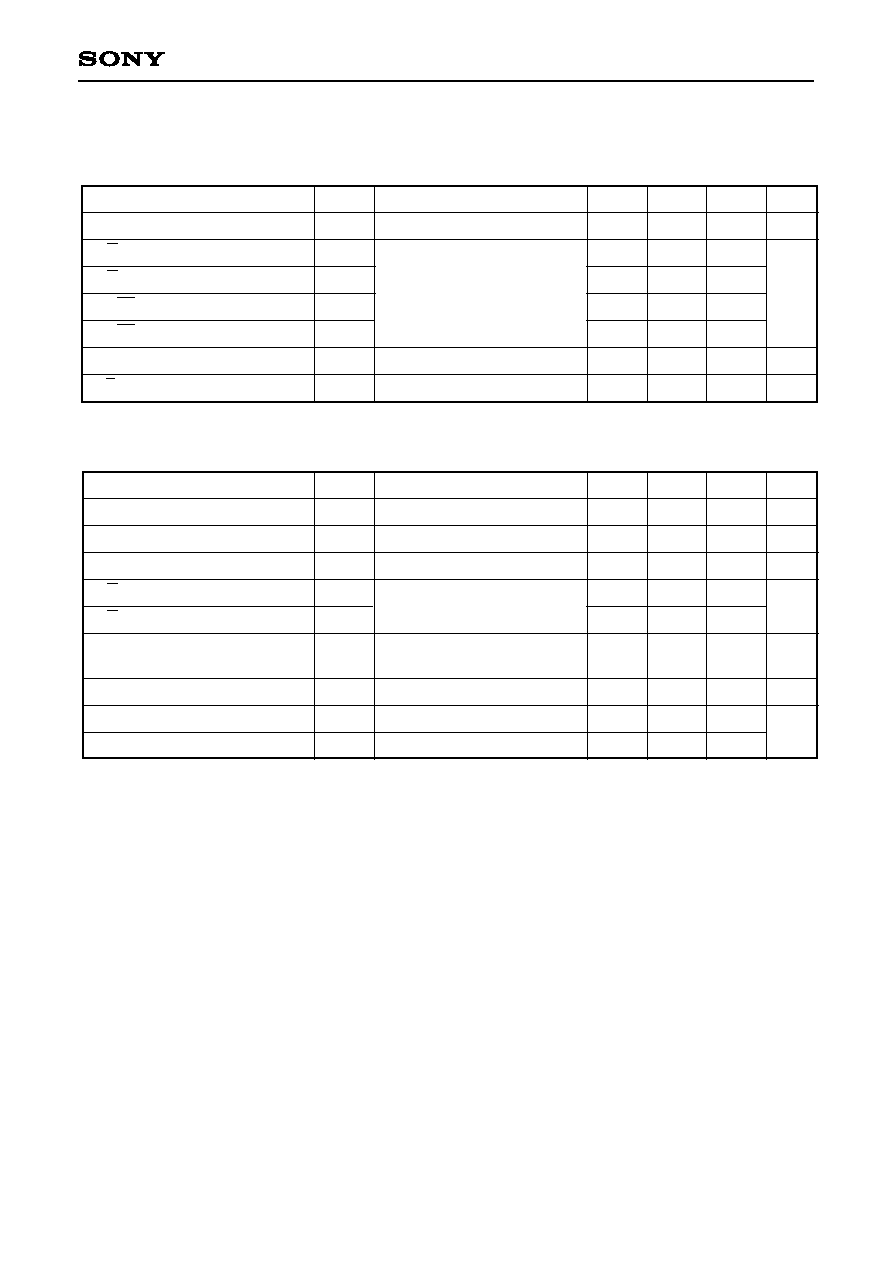

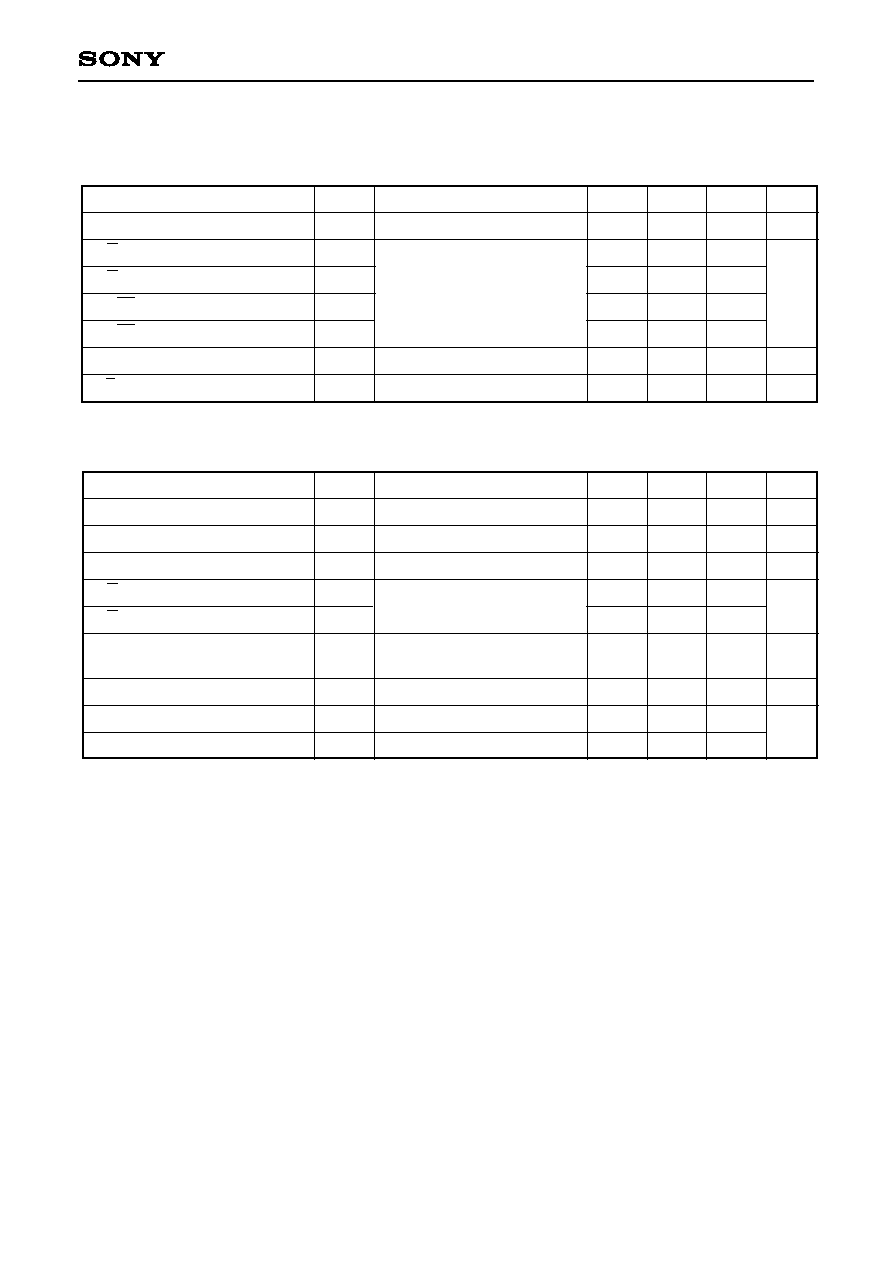

∑ DC characteristics (

VCC = VCCA = 0V, VEED= VEEA= VEE = ≠5V±10%, Ta = ≠40∞C to +85∞C, RT = 50

, VTT = ≠2V)

Item

Symbol

Conditions

Min.

Typ.

Max.

Unit

Supply current

Q/Q High output voltage

Q/Q Low output voltage

SD/SD High output voltage

SD/SD Low output voltage

Input offset voltage

D/D input resistance

I

EE

V

OH

V

OL

V

OHS

V

OLS

V

OFF

Rin

≠93

≠1.03

≠1.81

≠1.25

≠1.95

0.75

≠59

≠0.95

≠1.70

≠0.95

≠1.76

70

1.0

≠0.88

≠1.62

≠0.70

≠1.57

1.25

mA

V

µV

k

1

CAP2, CAP3 pin capacitance = 2000pF, REX = 400

, Vin = 20mVpp (single ended)

2

CAP2, CAP3 pin capacitance = 2000pF, REX = 400

, Vin = 60mVpp (single ended)

Ta = 0 to 85∞C

≠ 7 ≠

CXB1567Q

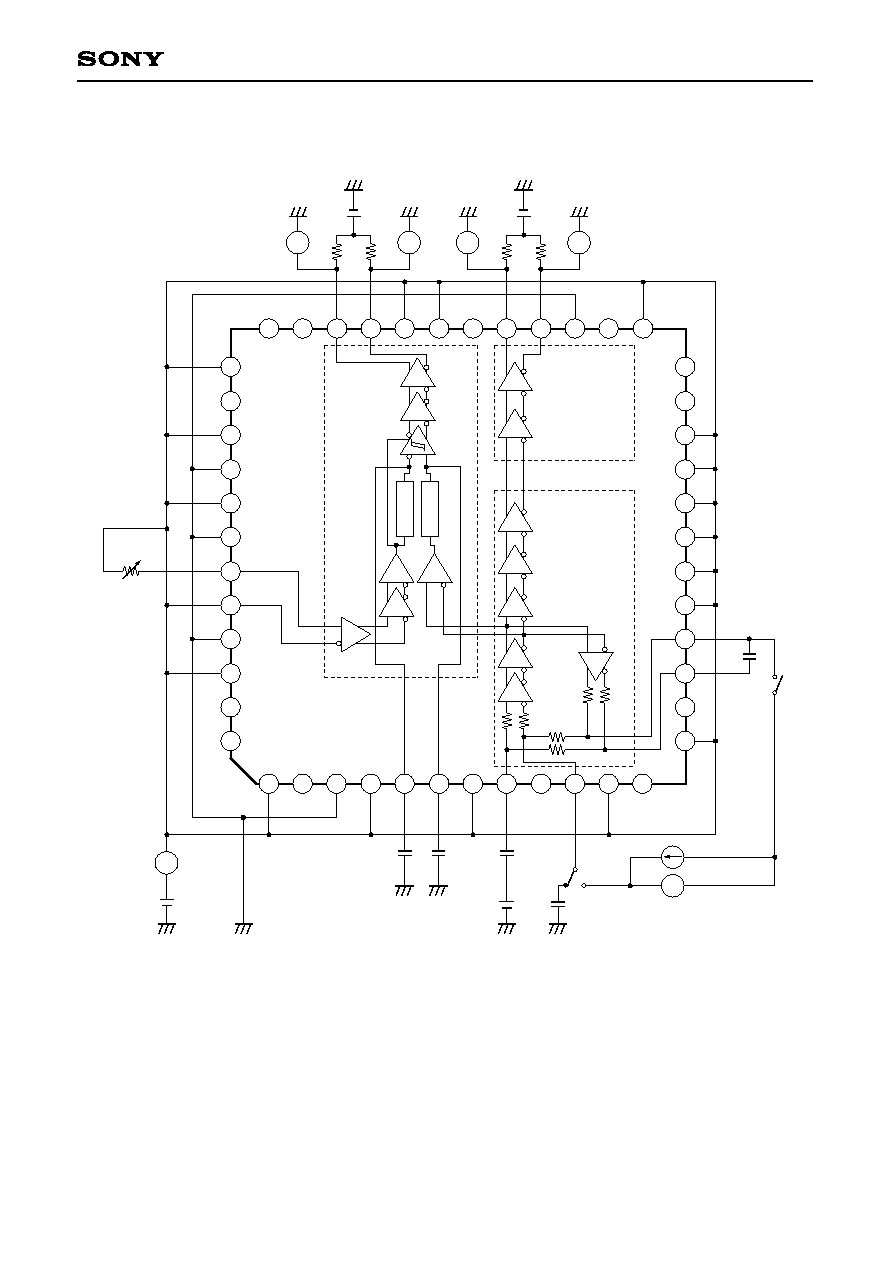

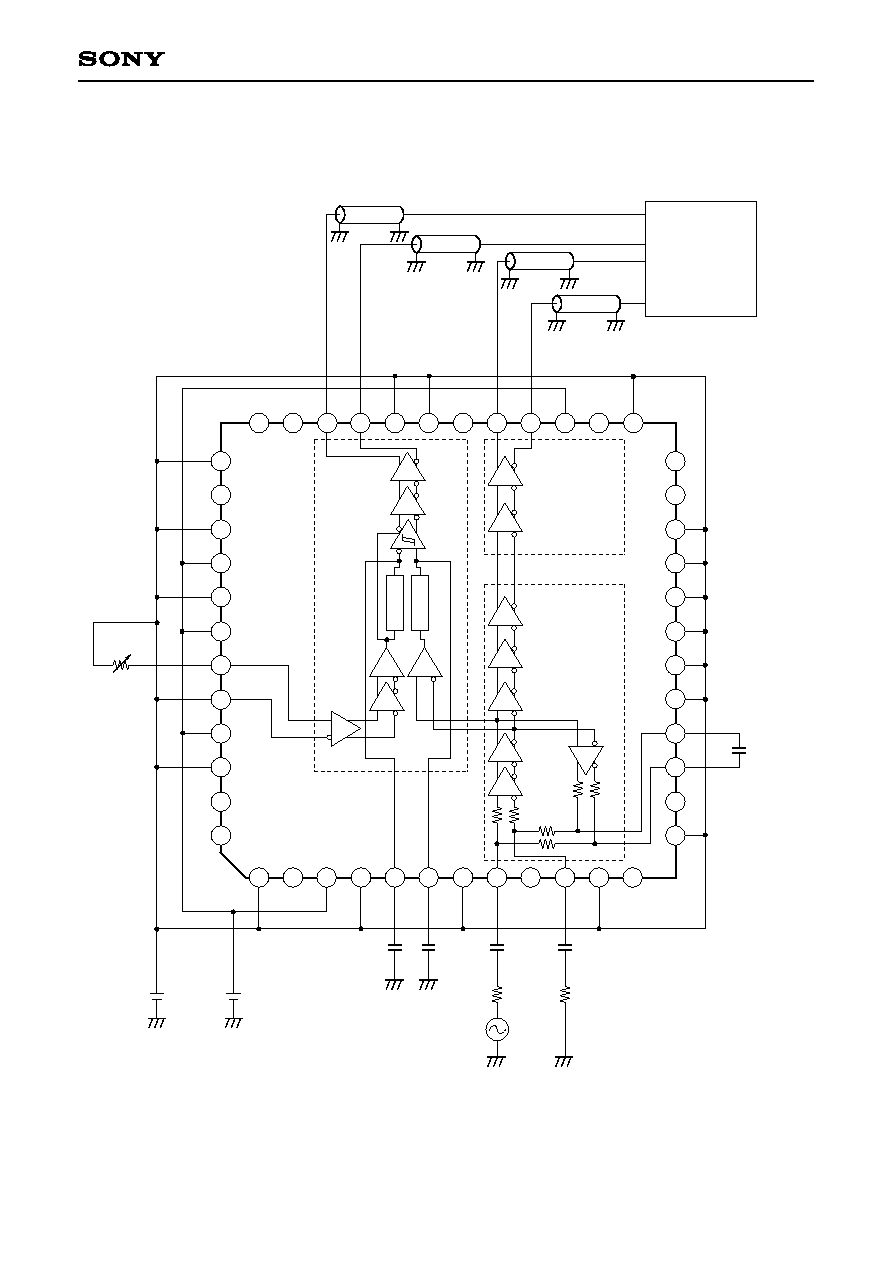

DC Electrical Characteristics Measurement Circuit

Output

Buffer

Block

Alarm

Block

P/H 2

P/H 1

Limiting Amplifier Block

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

36

35

34

31

32

33

40

39

38

37

41

42

43

44

45

46

47

48

2

3

4

5

6

7

8

9

10

11

12

1

V

EE

≠5V

C3

C3

C1

V

D

R

EX

C2

V

C1

A

V

51

51

V

V

TT

≠2V

V

51

51

V

V

TT

≠2V

≠ 8 ≠

CXB1567Q

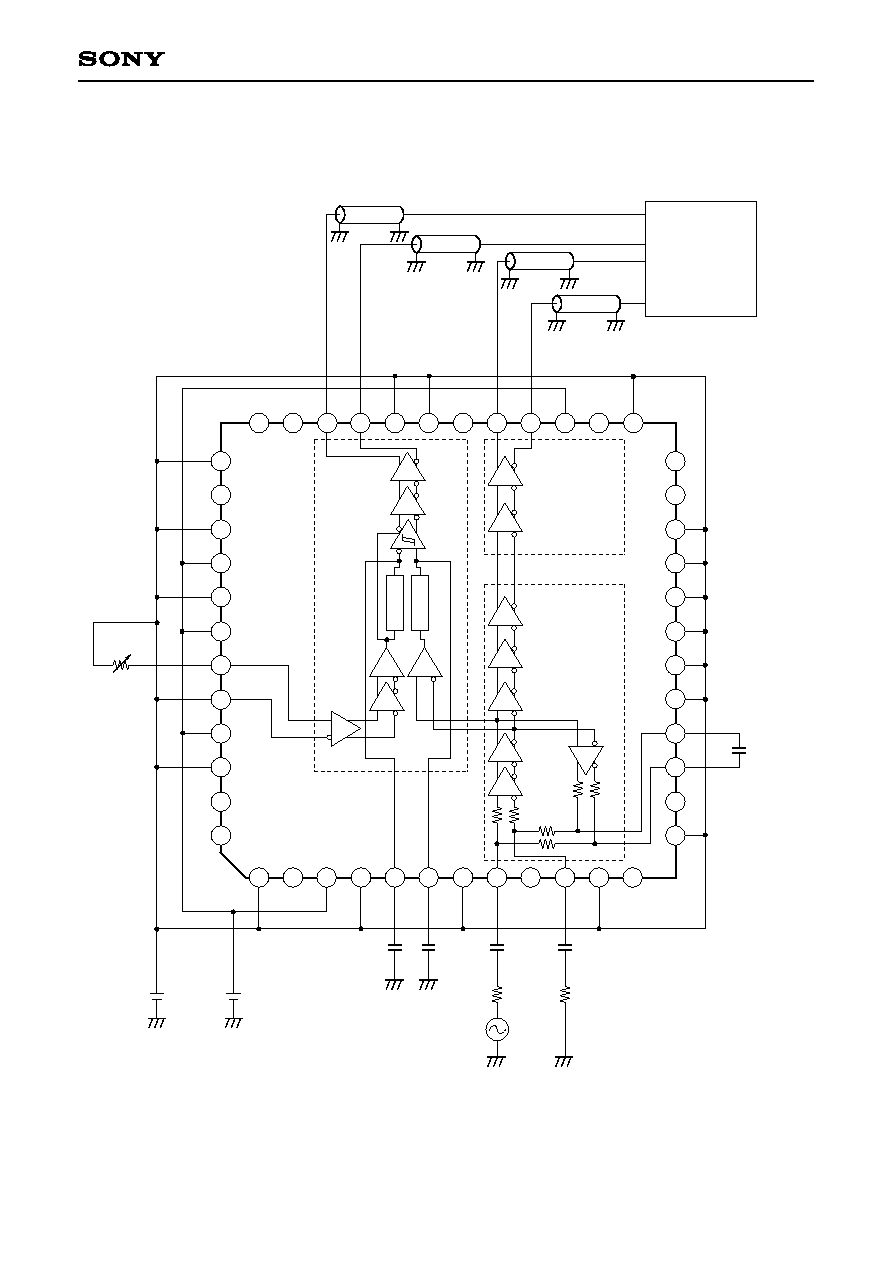

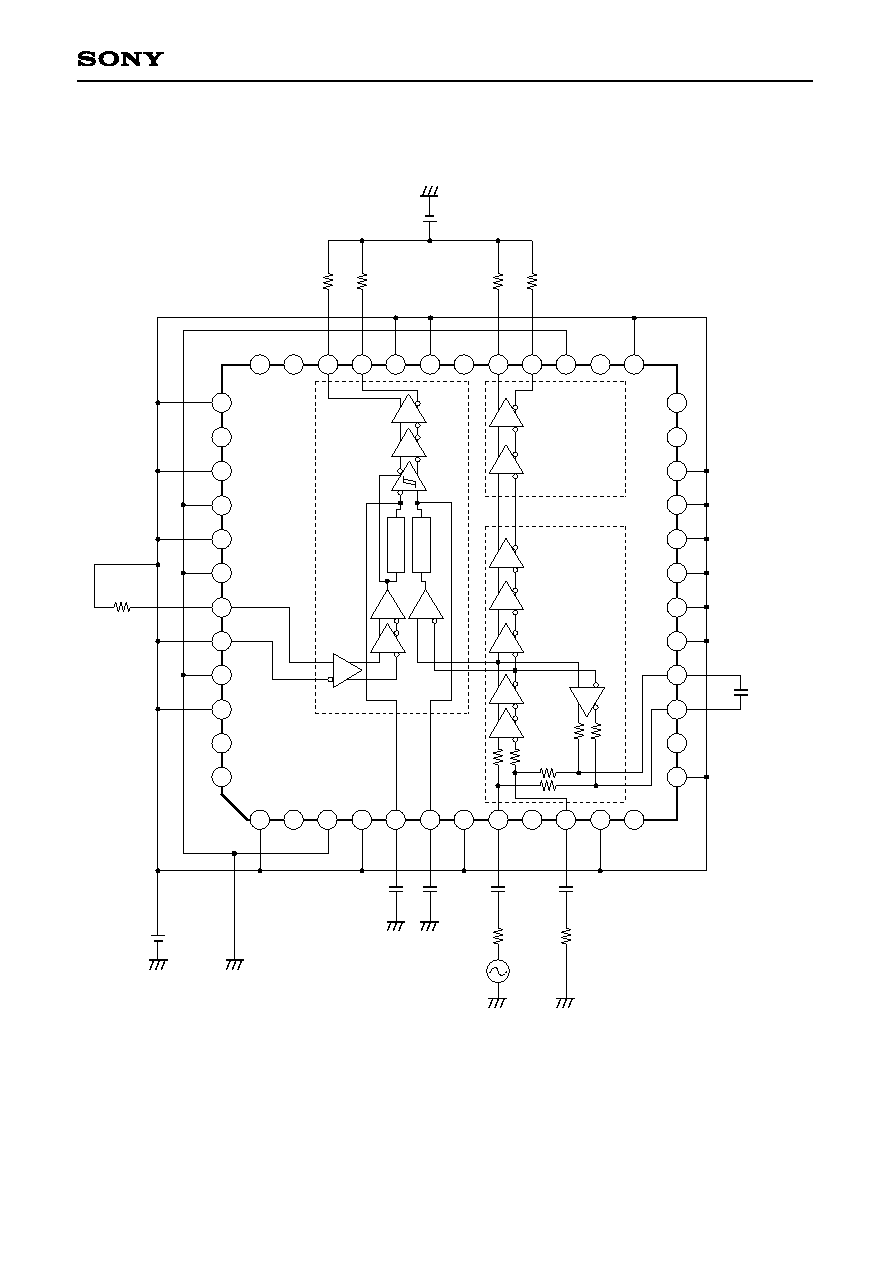

AC Electrical Characteristics Measurement Circuit

Output

Buffer

Block

Alarm

Block

P/H 2

P/H 1

Limiting Amplifier Block

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

36

35

34

31

32

33

40

39

38

37

41

42

43

44

45

46

47

48

2

3

4

5

6

7

8

9

10

11

12

1

V

EE

≠3V

V

CC

+2V

2000pF

2000pF

1000pF

1000pF

R

D

V

D

R

D

Z0 = 50

Z0 = 50

Z0 = 50

Z0 = 50

Oscilloscope

50

Input

R

EX

0.047µF

≠ 9 ≠

CXB1567Q

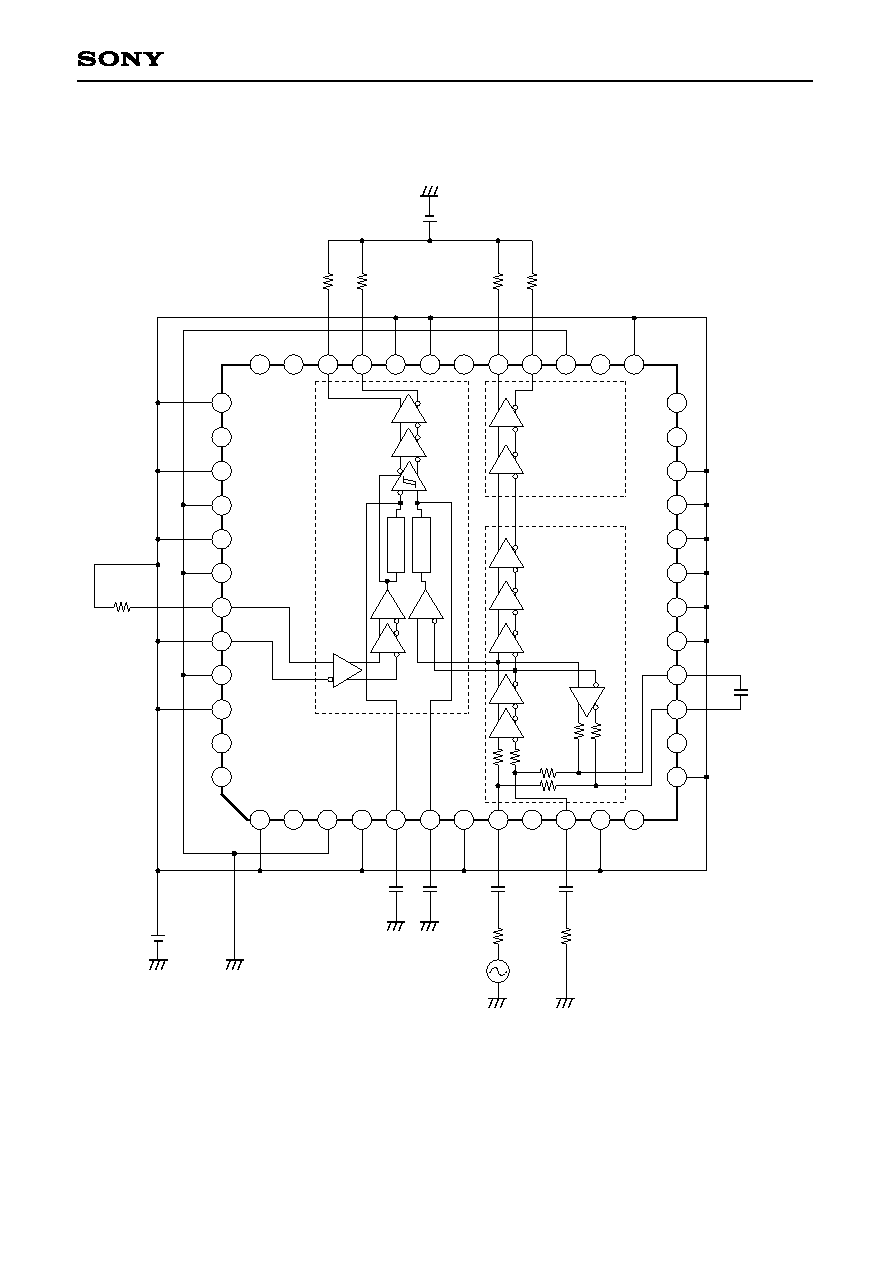

Application Circuit

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume

responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent

and other right due to same.

V

TT

≠2.0V

Output

Buffer

Block

Alarm

Block

P/H 2

P/H 1

Limiting Amplifier Block

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

36

35

34

31

32

33

40

39

38

37

41

42

43

44

45

46

47

48

2

3

4

5

6

7

8

9

10

11

12

1

V

EE

≠5.0V

2000pF

2000pF

1000pF

1000pF

50

V

D

50

273

0.047µF

51

51

51

51

≠ 10 ≠

CXB1567Q

Notes on Operation

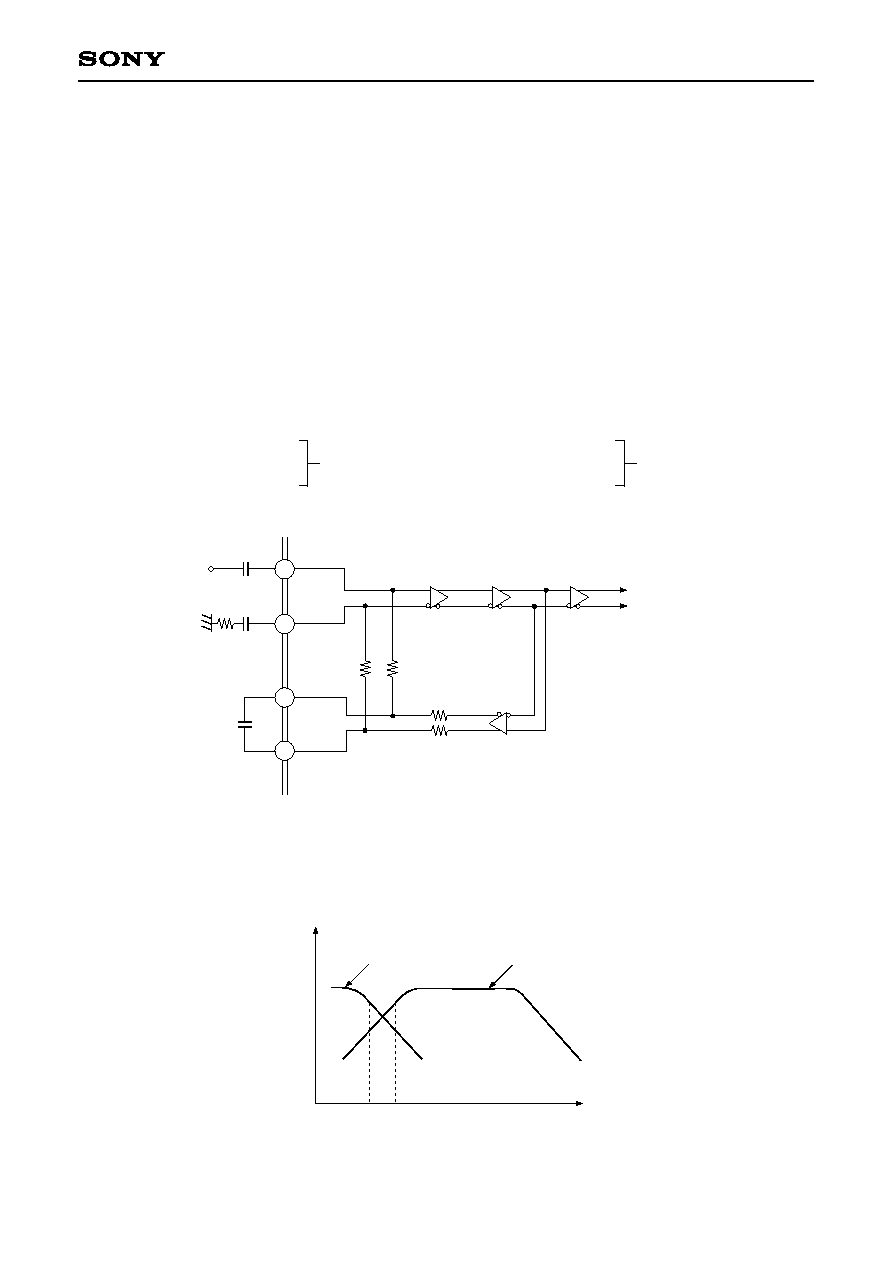

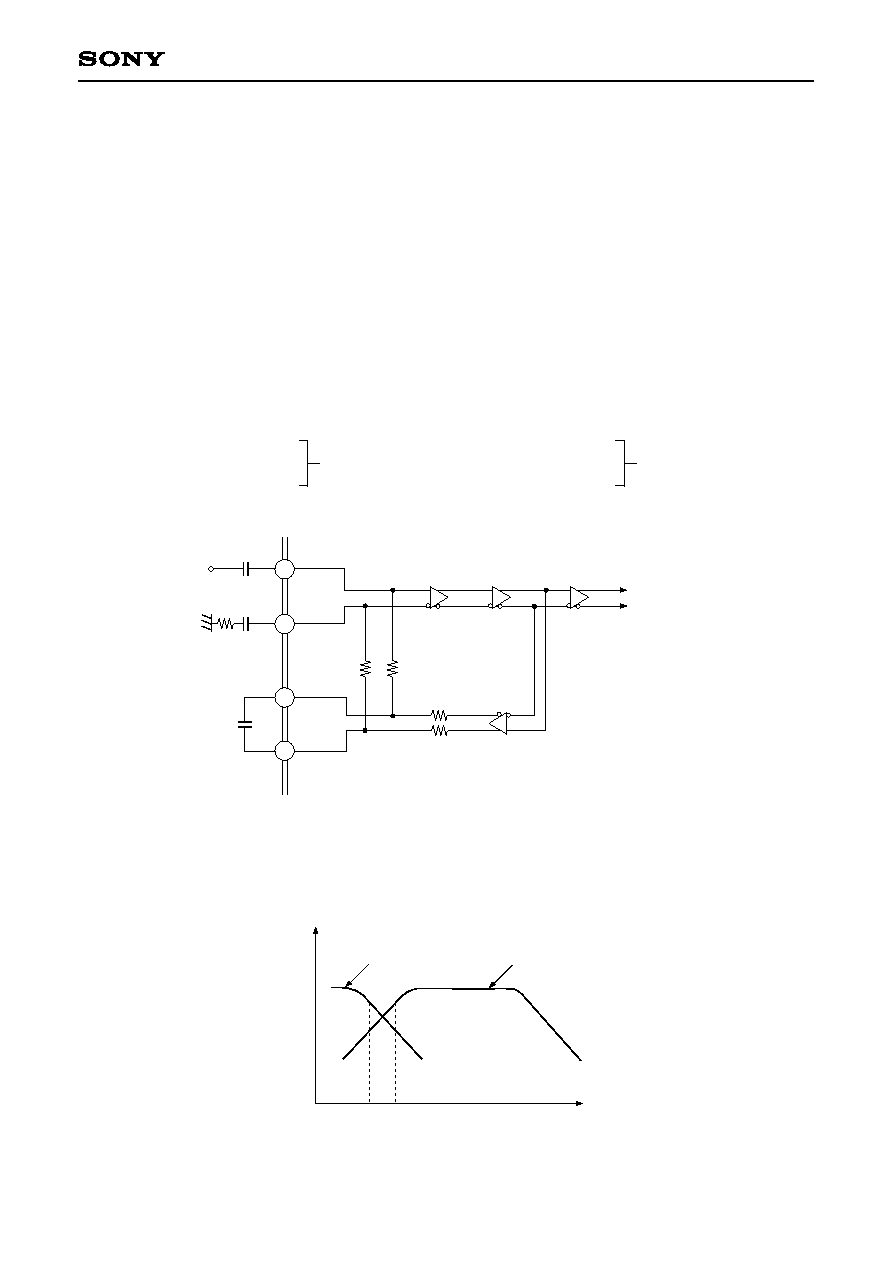

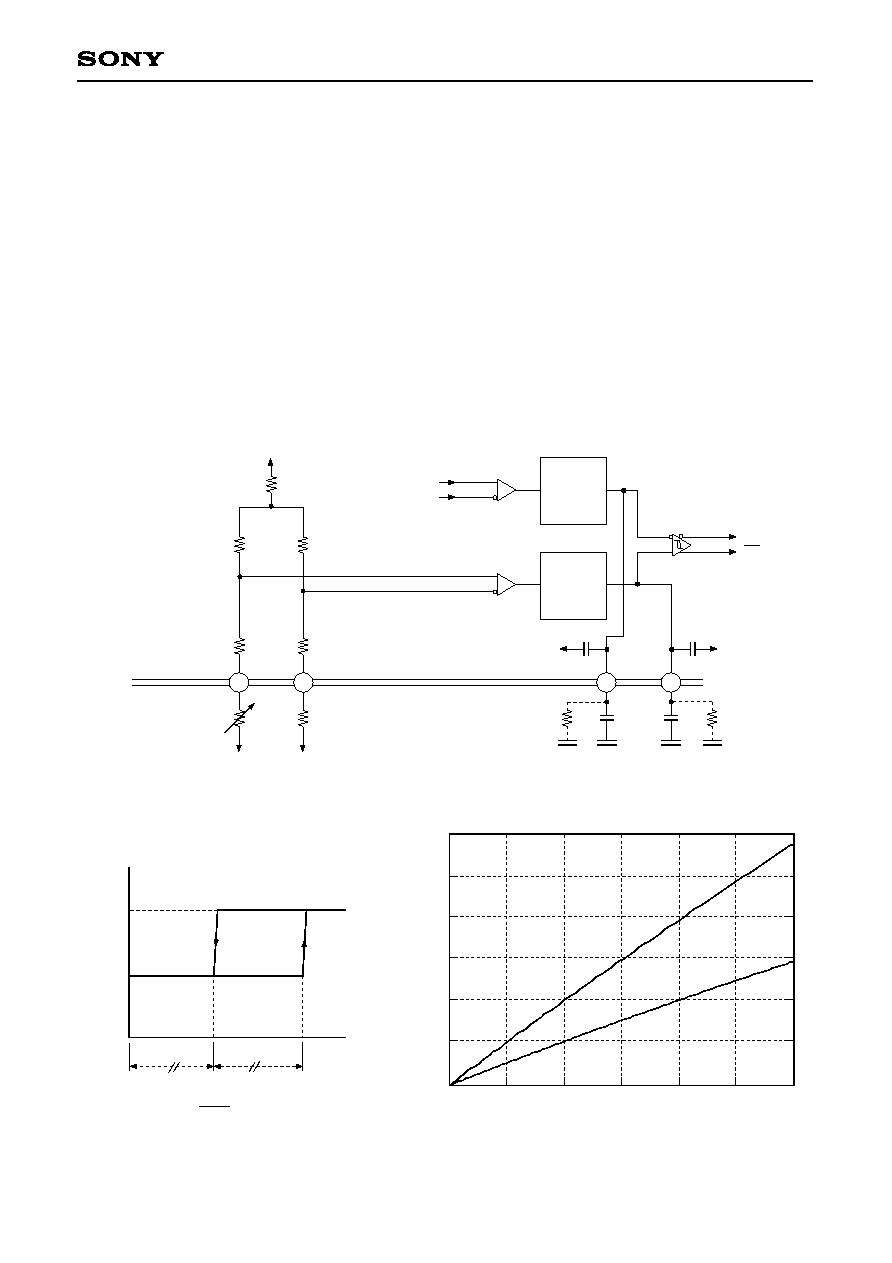

1. Limiting amplifier block

The limiting amplifier block is equipped with the auto-offset canceller circuit. When external capacitors C1 and

C2 are connected as shown in Fig. 1, the DC bias is set automatically in this block. External capacitor C1 and

IC internal resistor R1 determine the low input cut-off frequency f2, as shown in Fig. 2. Similarly, external

capacitor C2 and internal resistor R2 determine the high cut-off frequency f1 for DC bias feedback. Since

peaking characteristics may occur in the low frequency area of the amplifier gain characteristics depending on

the f1/f2 combination, set the C1 and C2 values so as to avoid the occurrence of peaking characteristics. The

typical values of R1,R2, C1 and C2 are as indicated below. When a single-ended input is used, provide AC

grounding by connecting Pin 10 to a capacitor which has the same capacitance as capacitor C1. R

D

is the

resistor for impedance matching. The same level of output impedance as for the signal source should be

applied to Pin 10.

R1 (internal) :

1k

R2 (internal) : 7.5k

f2: 160kHz

f1: 450Hz

C1 (external) : 1000pF

C2 (external) : 0.047µF

C1

C1

C2

R1

R1

R2

R2

To IC interior

D

8

10

15

16

R

D

Fig. 1

f1

f2

Frequency

Gain

Feedback frequency

responce

Amplifier frequency

responce

Fig. 2

≠ 11 ≠

CXB1567Q

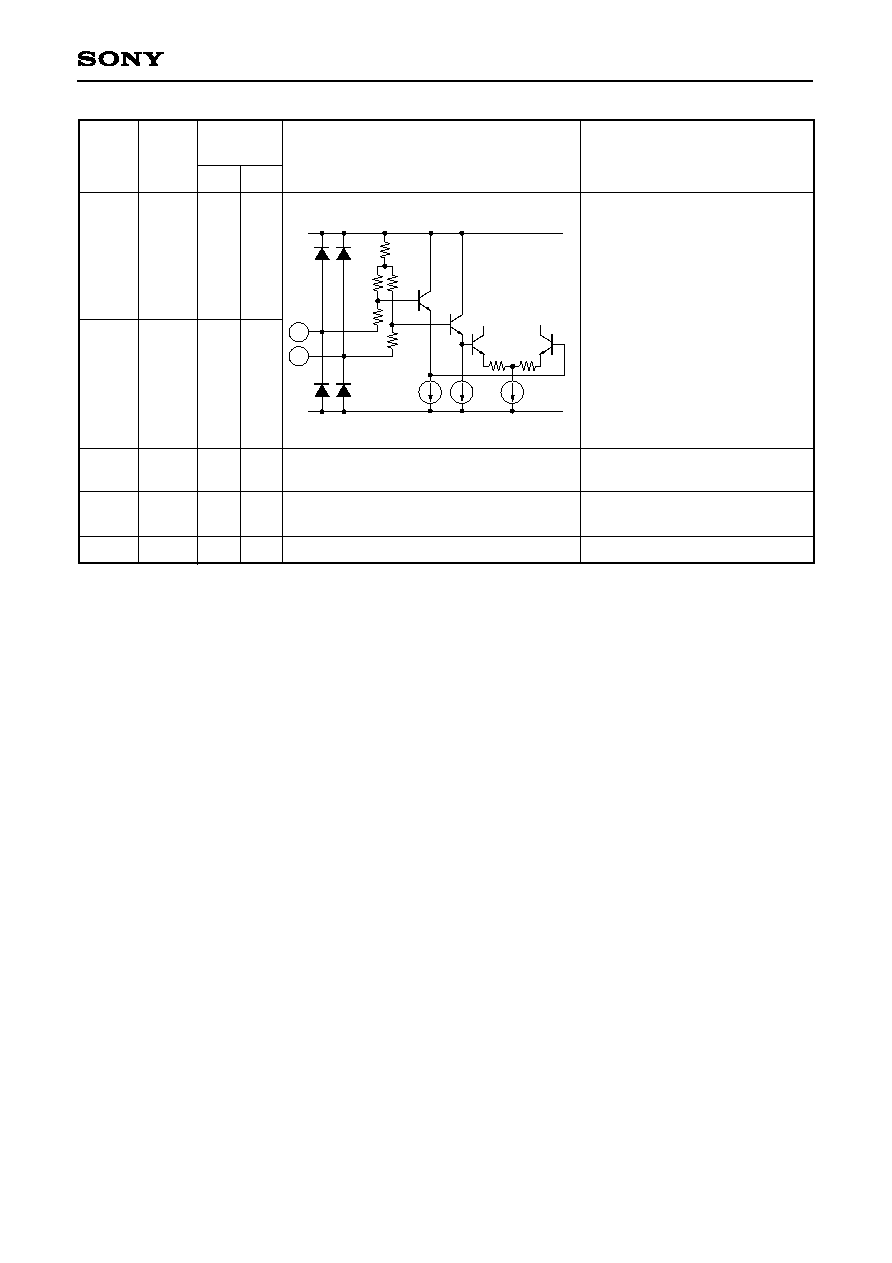

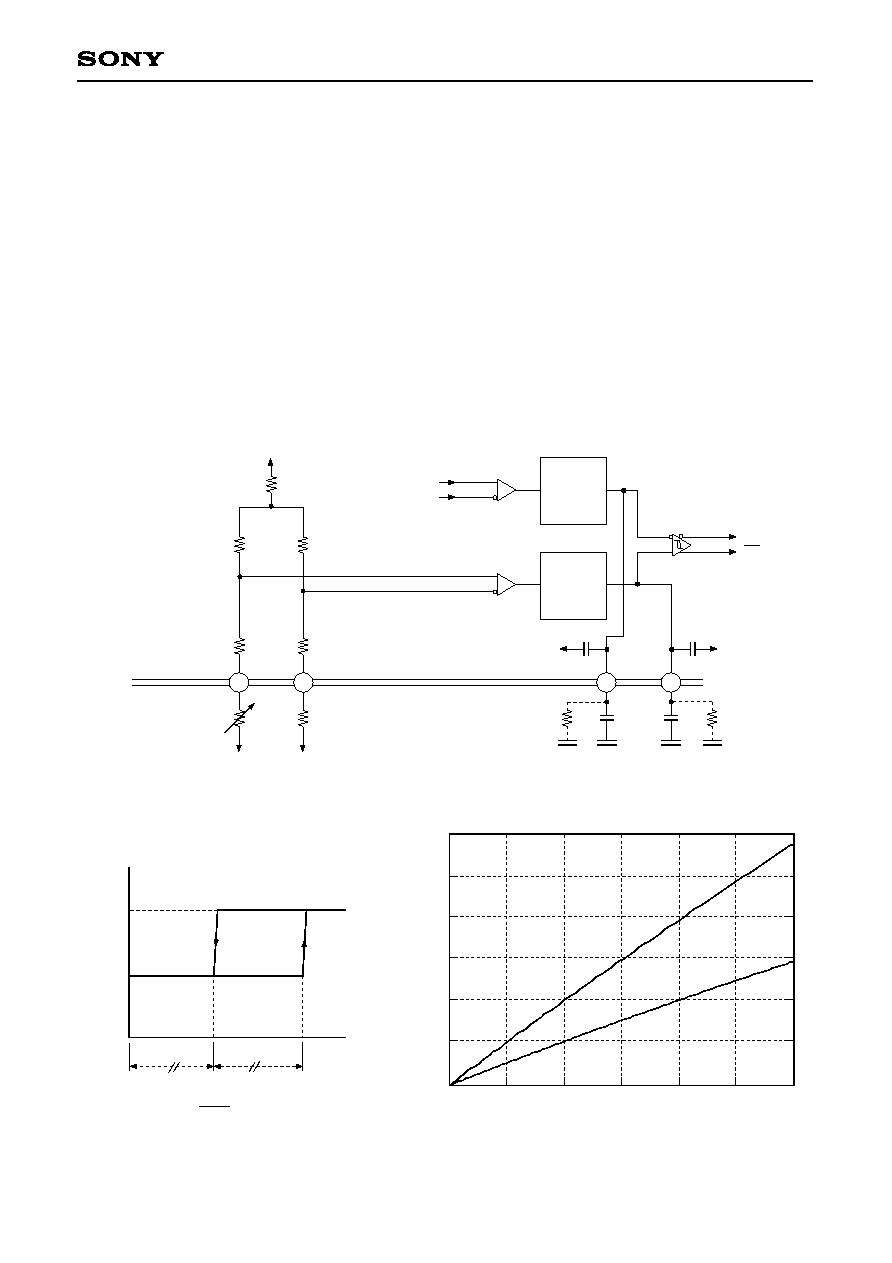

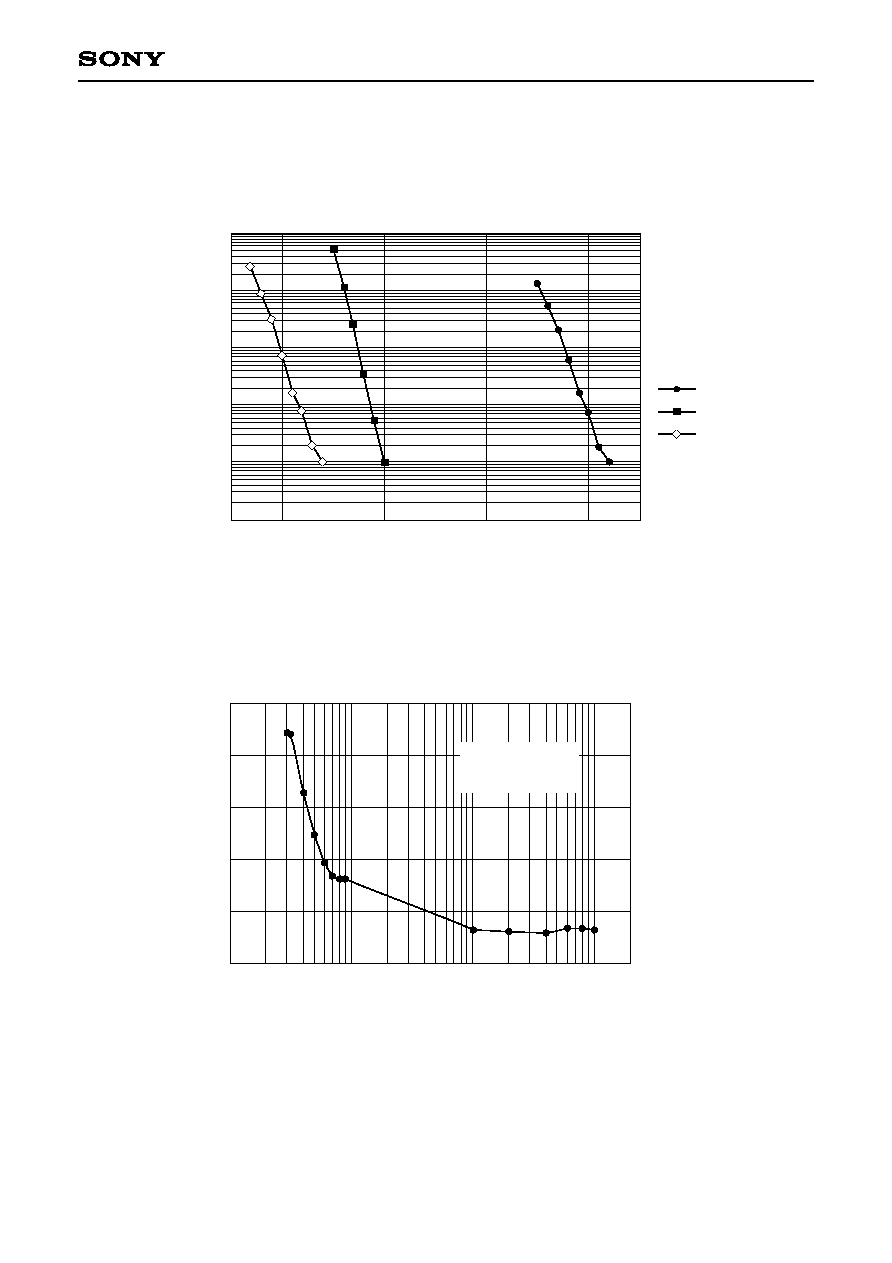

2. Alarm block

As shown in Fig. 3, the alarm block requires external resistor R

EX1

for alarm level setting and peak hold

capacitor C3. When the resistance value provided for resistor R

EX1

is increased, the alarm setting level rises.

When the resistance value provided for R

EX2

is increased, the alarm setting level lowers. However, the voltage

of Pin 43 should always be higher than that of Pin 44. Normally, short-circuit Pin 44 to V

EE

(R

EX2

= 0). See

Fig. 5 for the alarm setting level. In the relationship between the alarm setting level and hysteresis width, the

hysteresis width is designed to maintain a constant gain (design target value: 6dB) as shown in Fig. 4.

External capacitors C3 are used for input signal and alarm level peak hold capacitance. The C3 capacitance

value should be set so as to obtain desired assert time and deassert time settings for the alarm signal. The

deassert time becomes smaller by connecting resistor R10 between V

EE

and Pin 5 and resistor R11 between

V

EE

and Pin 6. The R

EX1

and C3 typical values are indicated below. (A capacitance of approximately 10pF is

built in Pins 5 and 6 respectively.)

R

EX1

:

273

(V

DAS

= 3mVpp)

C3:

2000pF

From

Limiting

amplifier

Peak hold

SD

SD

VccA

10p

VccA

10p

Vcc

C3

Vcc

R

EX2

V

EE

R

EX1

V

EE

R10

V

EE

R11

V

EE

Peak hold

5k

5k

R9

R9

100

100 R8

R8

1k

R7

V

CC

A

IC interior

IC exterior

R7, R8, and R9 values

are typical values.

43

44

5

6

C3

Fig. 3

SD output

Hysteresis width

Input amplitude

VDAS

deassert level

VAS

assert level

0

High

level

Low

level

V

DAS

V

AS

20 log ( ) = 6.0 dB

V

AS

V

DAS

Fig. 4

V

AS

V

DAS

24

20

16

12

8

4

0

0

200

400

600

800

1000

1200

R

EX1

(

)

V

AS

, V

DAS

(mVpp)

Fig. 5

≠ 12 ≠

CXB1567Q

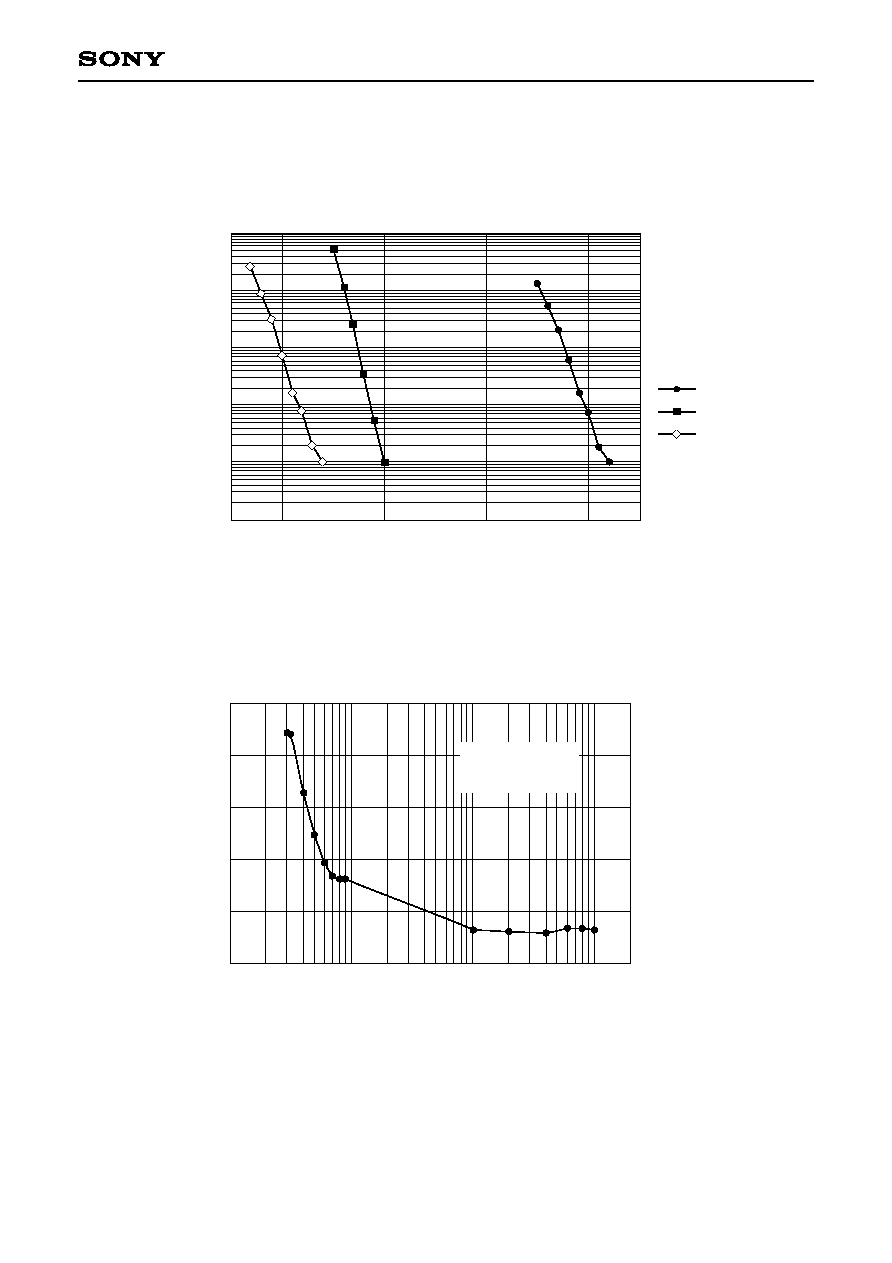

Example of Representative Characteristics

Output RMS jitter vs. Data input level

Data input level [mVp-p]

1

0

Output RMS jitter [ps]

V

EE

= ≠5.0V

Ta = 27∞C

D = 622.08Mbps

pattern : PRBS2

23

≠1

1000

100

10

50

40

30

20

10

Bit error rate vs. Data input level for each data rate

V

EE

= ≠5.0V,

Ta = 27∞C,

pattern : PRBS2

23

≠1

Bit error rate

10

≠6

10

≠7

10

≠8

10

≠9

10

≠10

10

≠11

2

3

4

5

Data input level [mVp-p]

1062.5Mbps

622.08Mbps

265.5Mbps

≠ 13 ≠

CXB1567Q

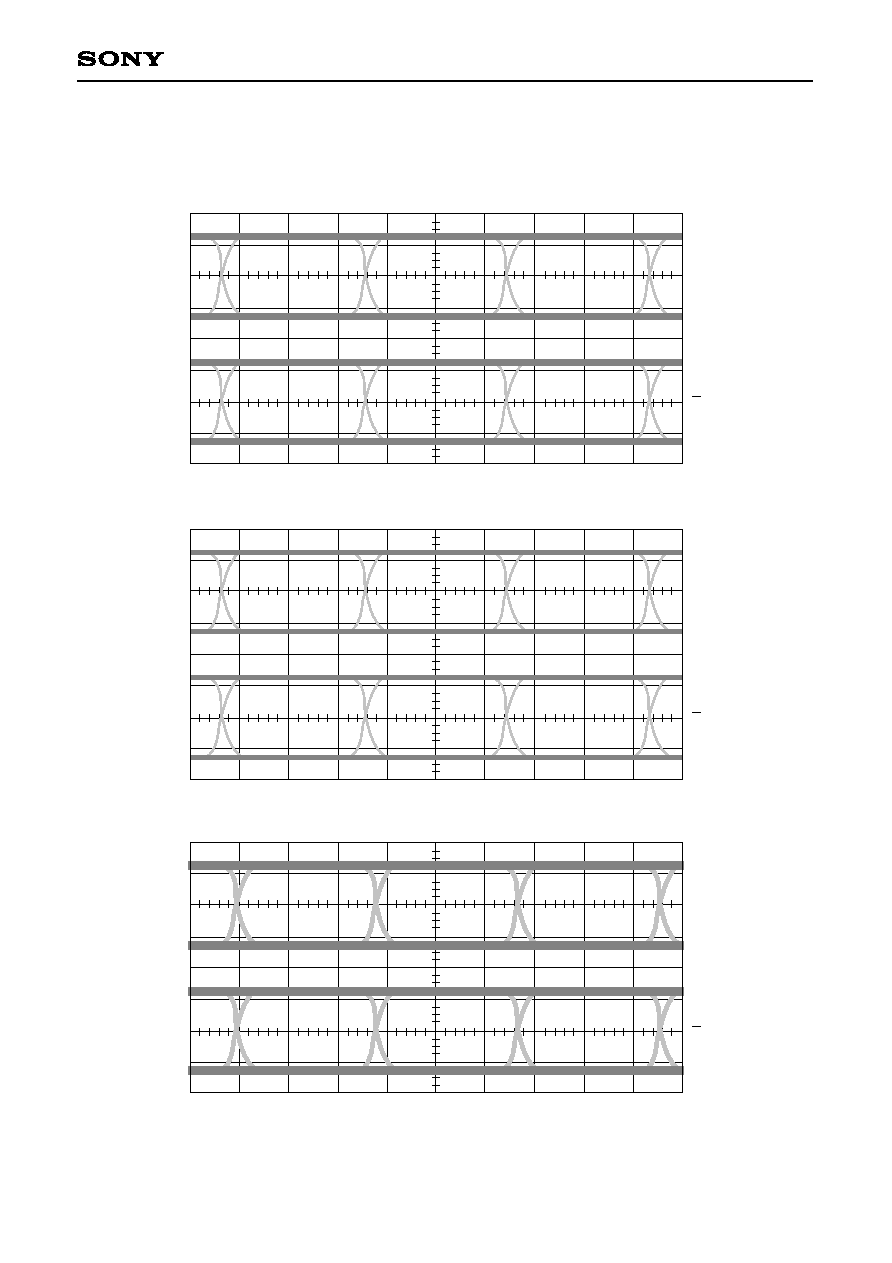

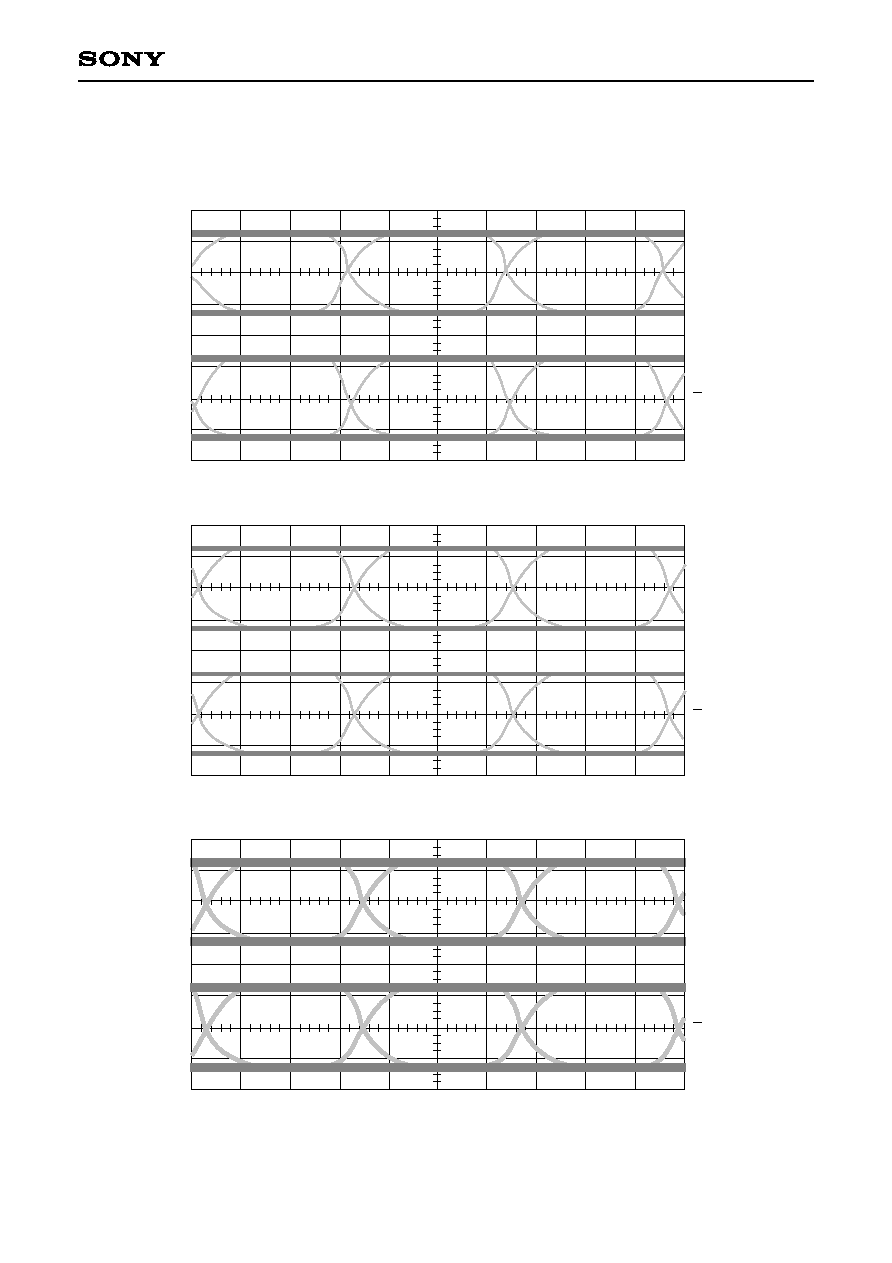

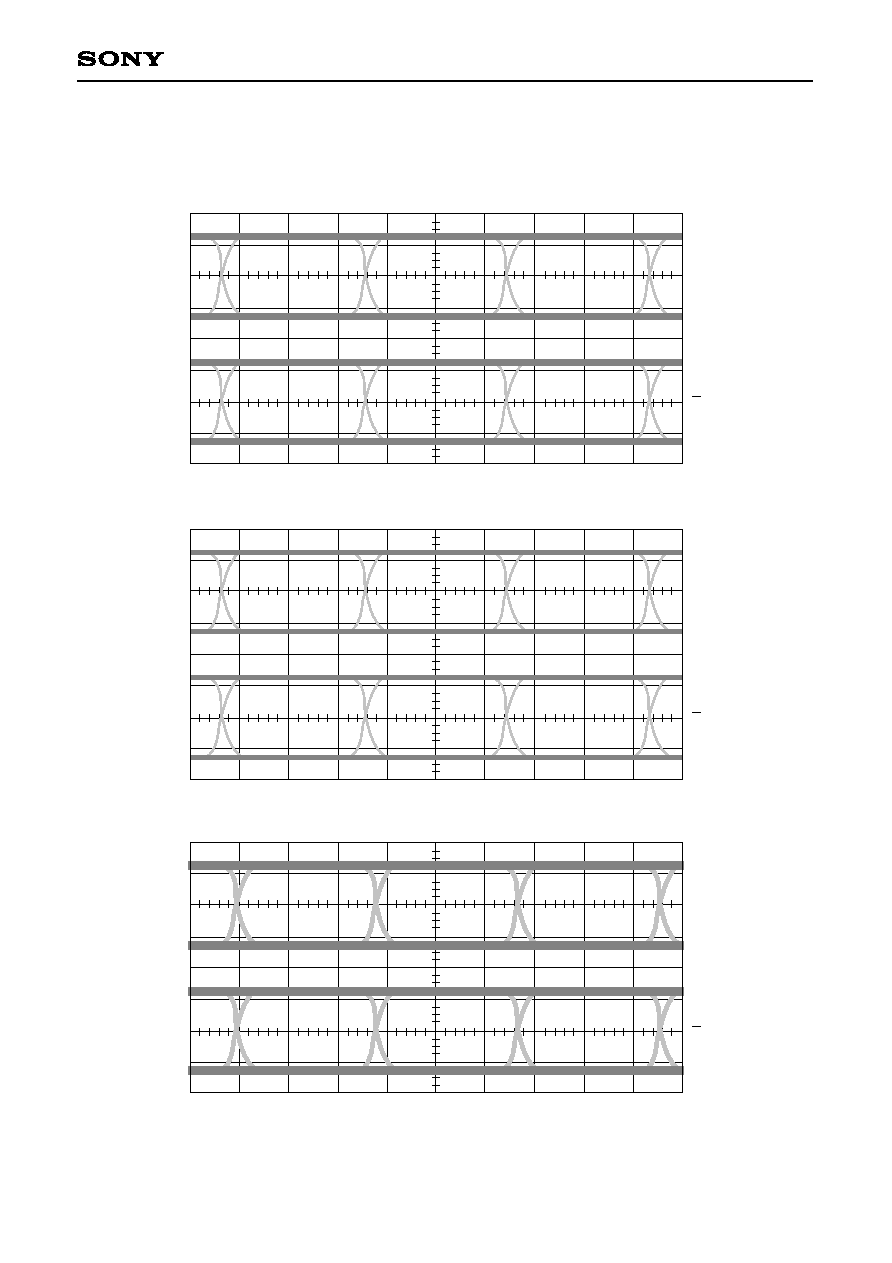

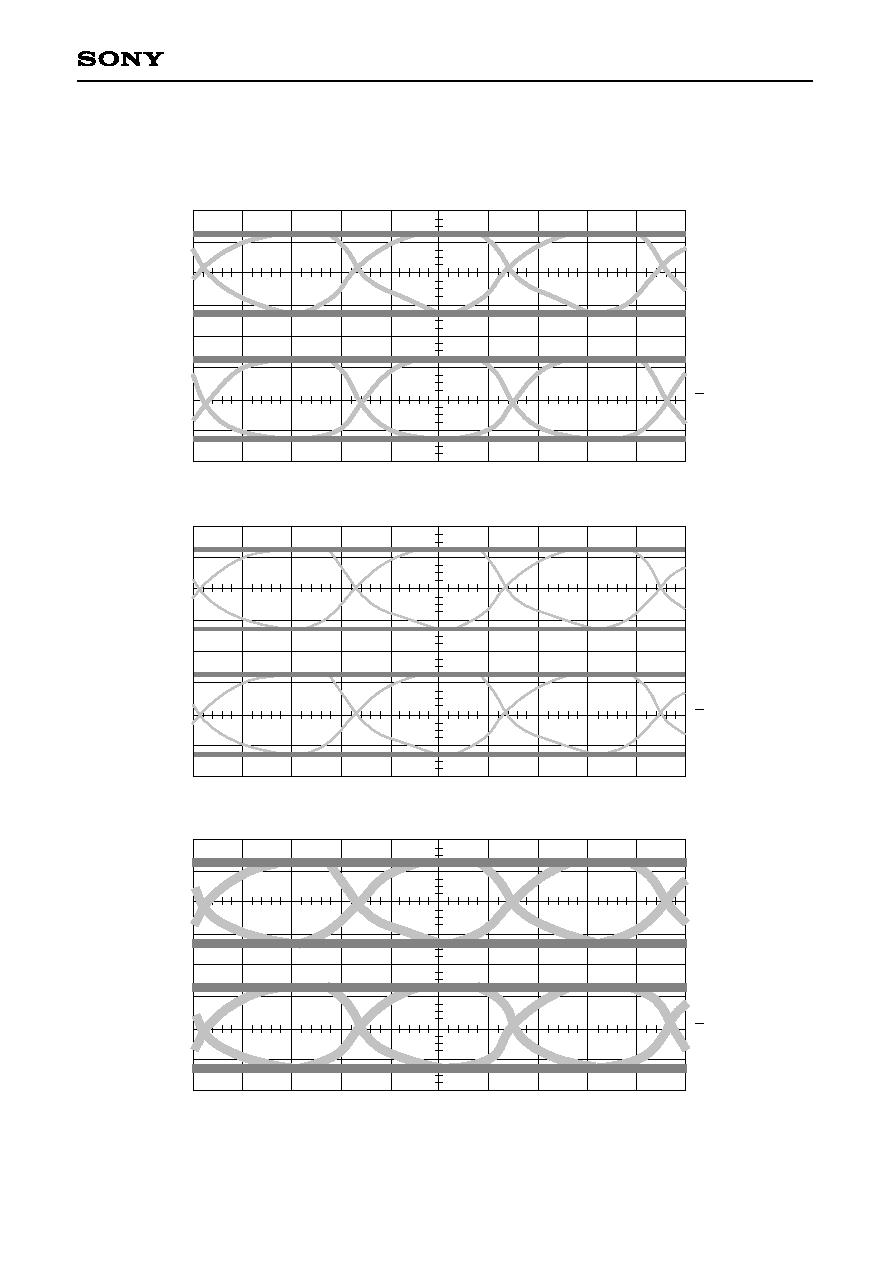

32.6040ns

39.1040ns

26.1040ns

Q

Q

V

DIN

= 2.0Vp-p

32.6040ns

39.1040ns

26.1040ns

Q

Q

V

DIN

= 500mVpp

32.6040ns

39.1040ns

26.1040ns

Q

Q

V

DIN

= 2.5mVpp

V

EE

= ≠5.0V

Ta = 27∞C

D = 265.5Mbps

pattern = PRBS2

23

≠1

Y Axis = 300mV/div

X Axis = 1300ps/div

≠ 14 ≠

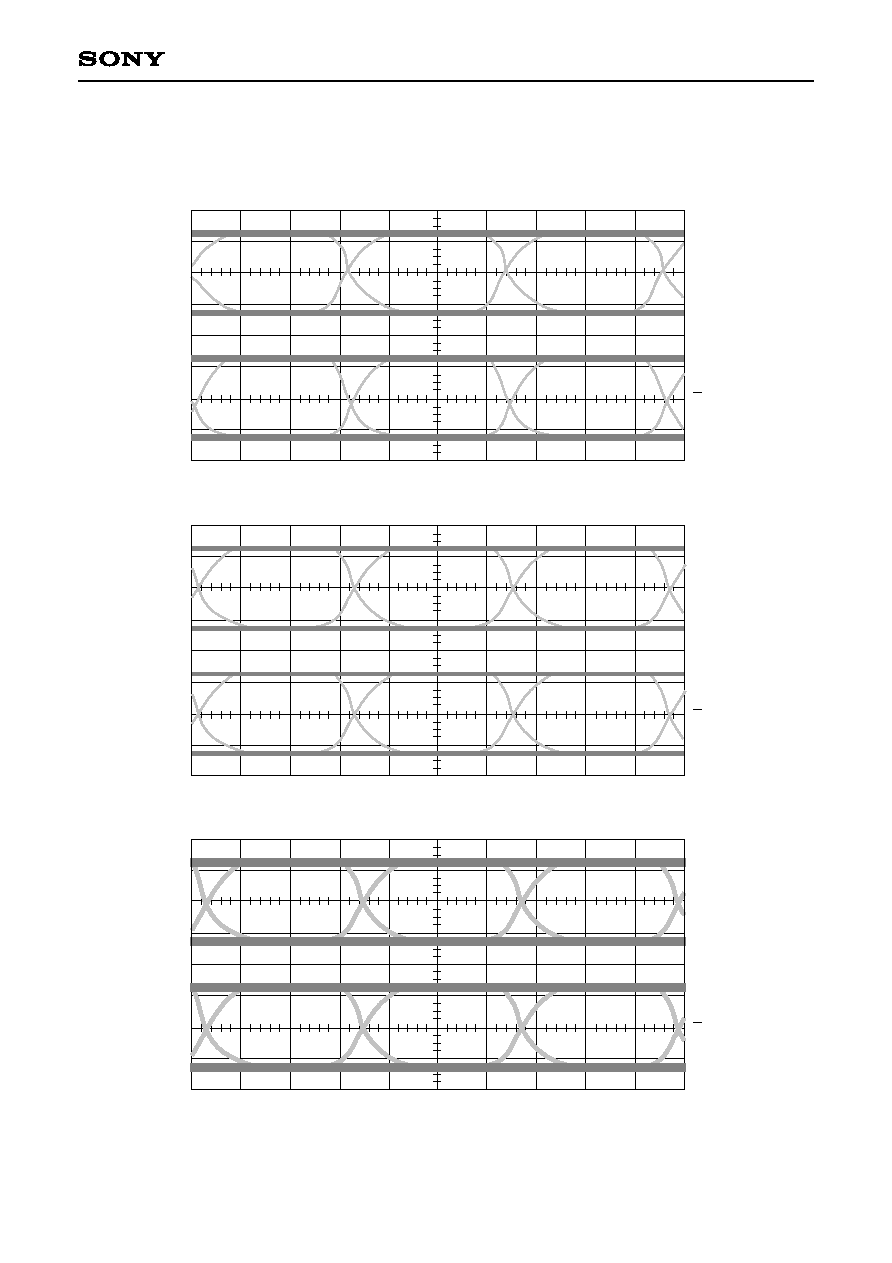

CXB1567Q

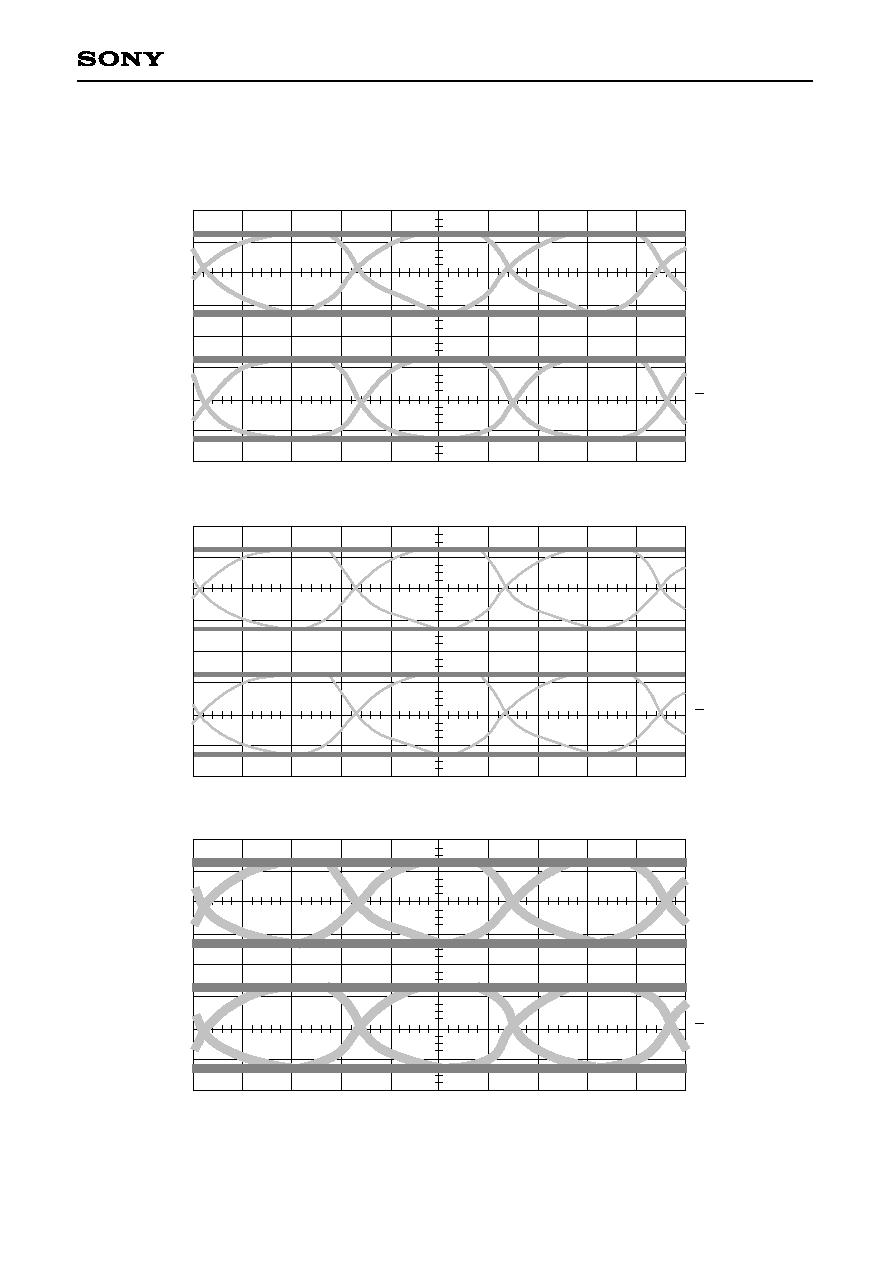

26.2300ns

28.7300ns

23.7300ns

Q

Q

V

DIN

= 2.0Vp-p

26.1600ns

28.6600ns

23.6600ns

Q

Q

V

DIN

= 500mVpp

26.2500ns

28.7500ns

23.7500ns

Q

Q

V

DIN

= 3.0mVpp

V

EE

= ≠5.0V

Ta = 27∞C

D = 622.08Mbps

pattern = PRBS2

23

≠1

Y Axis = 300mV/div

X Axis = 500ps/div

≠ 15 ≠

CXB1567Q

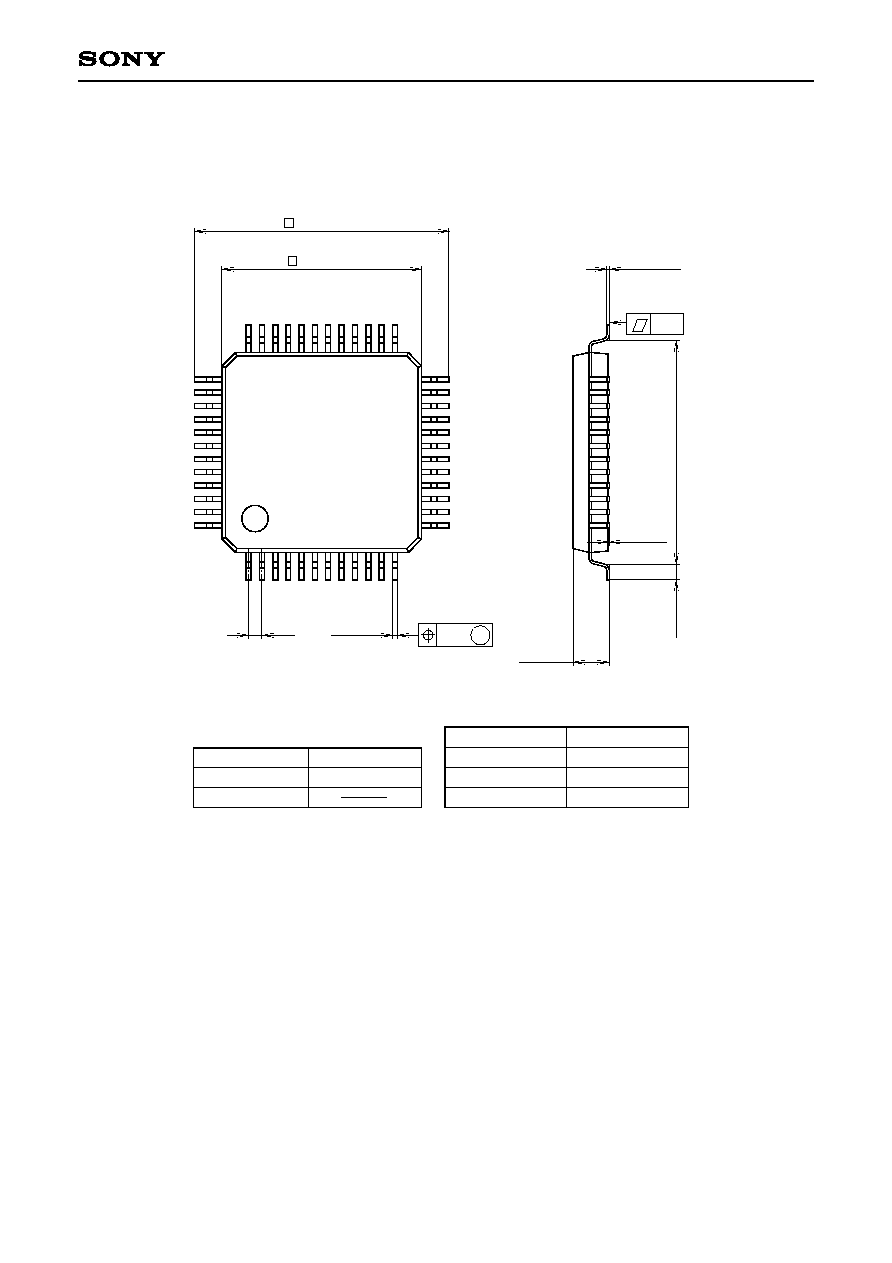

27.9900ns

29.4900ns

26.4900ns

Q

Q

V

DIN

= 2.0Vp-p

27.9900ns

29.4900ns

26.4900ns

Q

Q

V

DIN

= 500mVpp

17.8740ns

19.3740ns

16.3740ns

Q

Q

V

DIN

= 10mVpp

V

EE

= ≠5.0V

Ta = 27∞C

D = 1062.5Mbps

pattern = PRBS2

23

≠1

Y Axis = 300mV/div

X Axis = 300ps/div

≠ 16 ≠

CXB1567Q

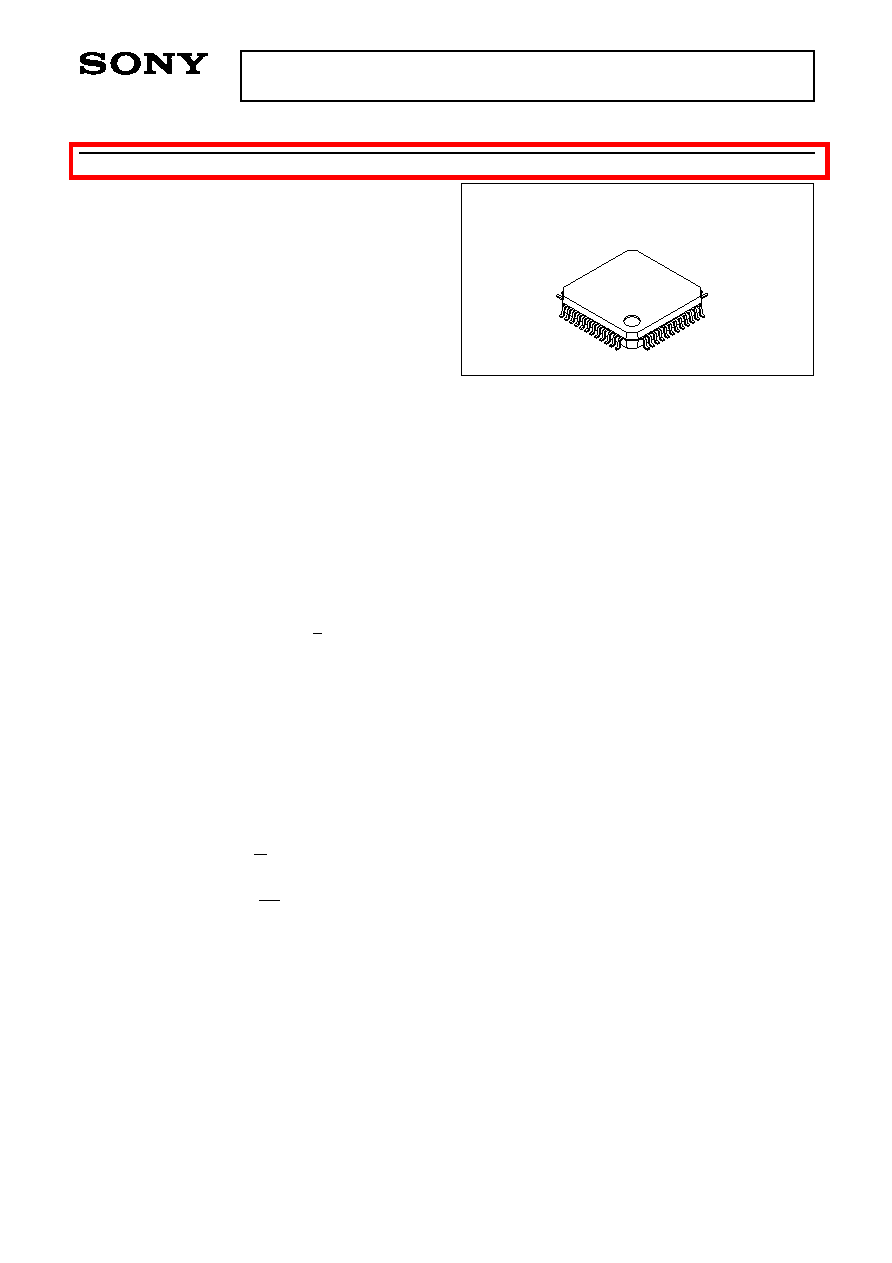

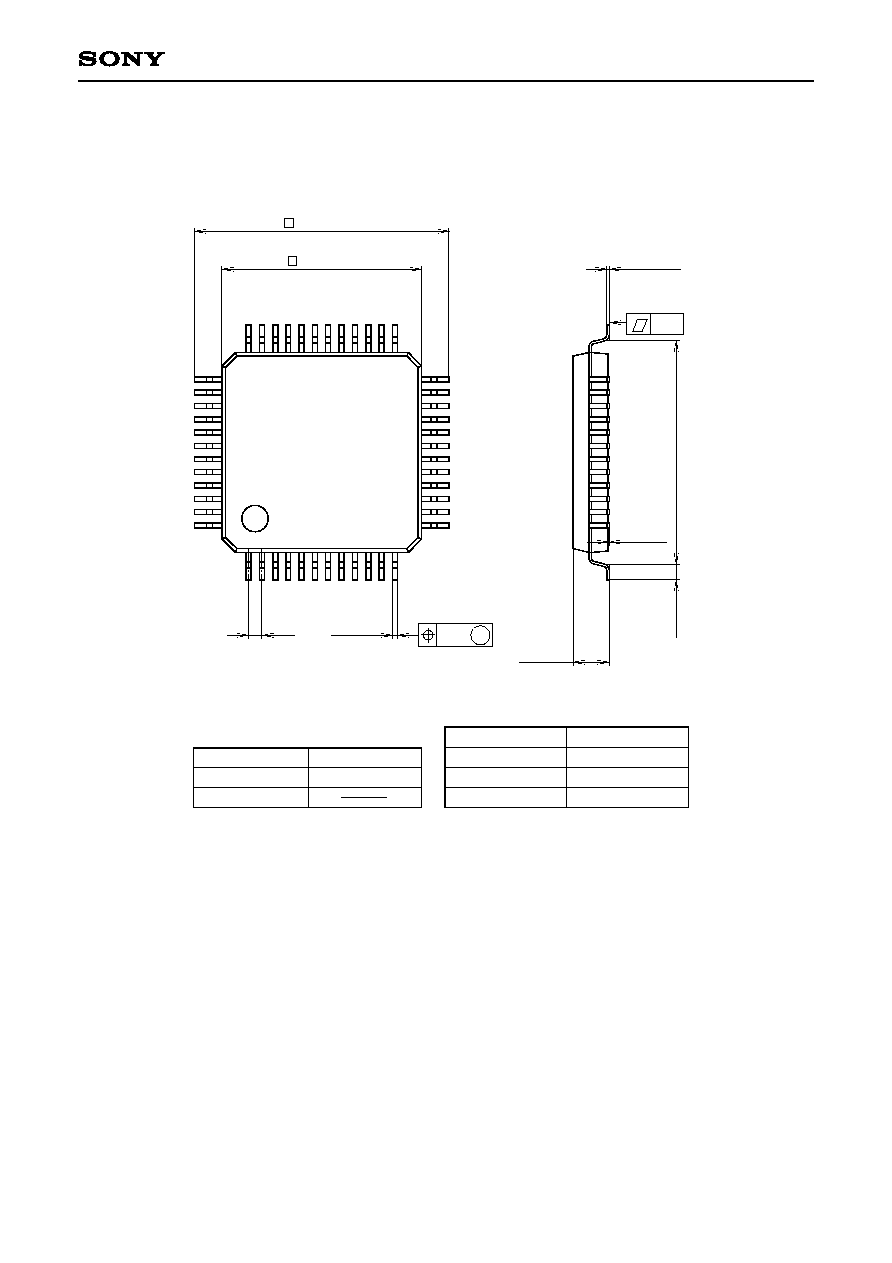

Package Outline

Unit: mm

SONY CODE

EIAJ CODE

JEDEC CODE

M

PACKAGE STRUCTURE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE WEIGHT

EPOXY RESIN

SOLDER / PALLADIUM

PLATING

COPPER / 42 ALLOY

48PIN QFP (PLASTIC)

15.3 ± 0.4

12.0 ≠ 0.1

+ 0.4

0.8

0.3 ≠ 0.1

+ 0.15

± 0.12

13

24

25

36

37

48

1

12

2.2 ≠ 0.15

+ 0.35

0.9 ±

0.2

0.1 ≠ 0.1

+ 0.2

13.5

0.15

0.15 ≠ 0.05

+ 0.1

QFP-48P-L04

QFP048-P-1212-B

0.7g