| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXD1172AP | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Description

CXD1172AM/AP is a 6-bit CMOS A/D converter for

video use. The adoption of a 2-step parallel system

achieves low consumption at a maximum conversion

speed of 20MSPS minimum, 35MSPS typical.

Features

∑ Resolution: 6-bit

±

1/2LSB

∑ Max. sampling frequency: 20MSPS

∑ Low power consumption: 40mW (at 20MSPS typ.)

(Reference current excluded)

∑ Built-in sampling and hold circuit.

∑ 3-state TTL compatible output.

∑ Power supply: 5V single

∑ Low input capacitance: 4pF

∑ Reference impedance: 250

(typ.)

Applications

TV, VCR digital systems and a wide range of fields

where high speed A/D conversion is required.

Structure

Silicon gate CMOS monolithic IC

Absolute Maximum Ratings (Ta = 25∞C)

∑ Supply voltage

V

DD

7

V

∑ Reference voltage

V

RT

, V

RB

V

DD

+ 0.5 to V

SS

≠ 0.5 V

∑ Input voltage

V

IN

V

DD

+ 0.5 to V

SS

≠ 0.5 V

(Analog)

∑ Input voltage

V

CLK

V

DD

+ 0.5 to V

SS

≠ 0.5 V

(Digital)

∑ Output voltage

V

OH

, V

OL

V

DD

+ 0.5 to V

SS

≠ 0.5 V

(Digital)

∑ Storage temperature

Tstg

≠55 to +150

∞C

Recommended Operating Conditions

∑ Supply voltage

AV

DD

, AV

SS

4.75 to 5.25

V

DV

DD

, DV

SS

4.75 to 5.25

V

∑ Reference input voltage

V

RB

0 to 4.1

V

V

RT

0.9 to 5.0

V

V

RT

≠ V

RB

0.9 to AV

DD

V

∑ Analog input voltage

V

IN

V

RB

to V

RT

V

∑ Clock pulse width

T

PW1

, T

PW0

23ns (min.) to 1.1µs (max.)

∑ Operating temperature

Topr

≠20 to +75

∞C

≠ 1 ≠

E89320C78-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXD1172AM/AP

6-bit 20MSPS Video A/D Converter (CMOS)

CXD1172AM

16 pin SOP (Plastic)

CXD1172AP

16 pin DIP (Plastic)

≠ 2 ≠

CXD1172AM/AP

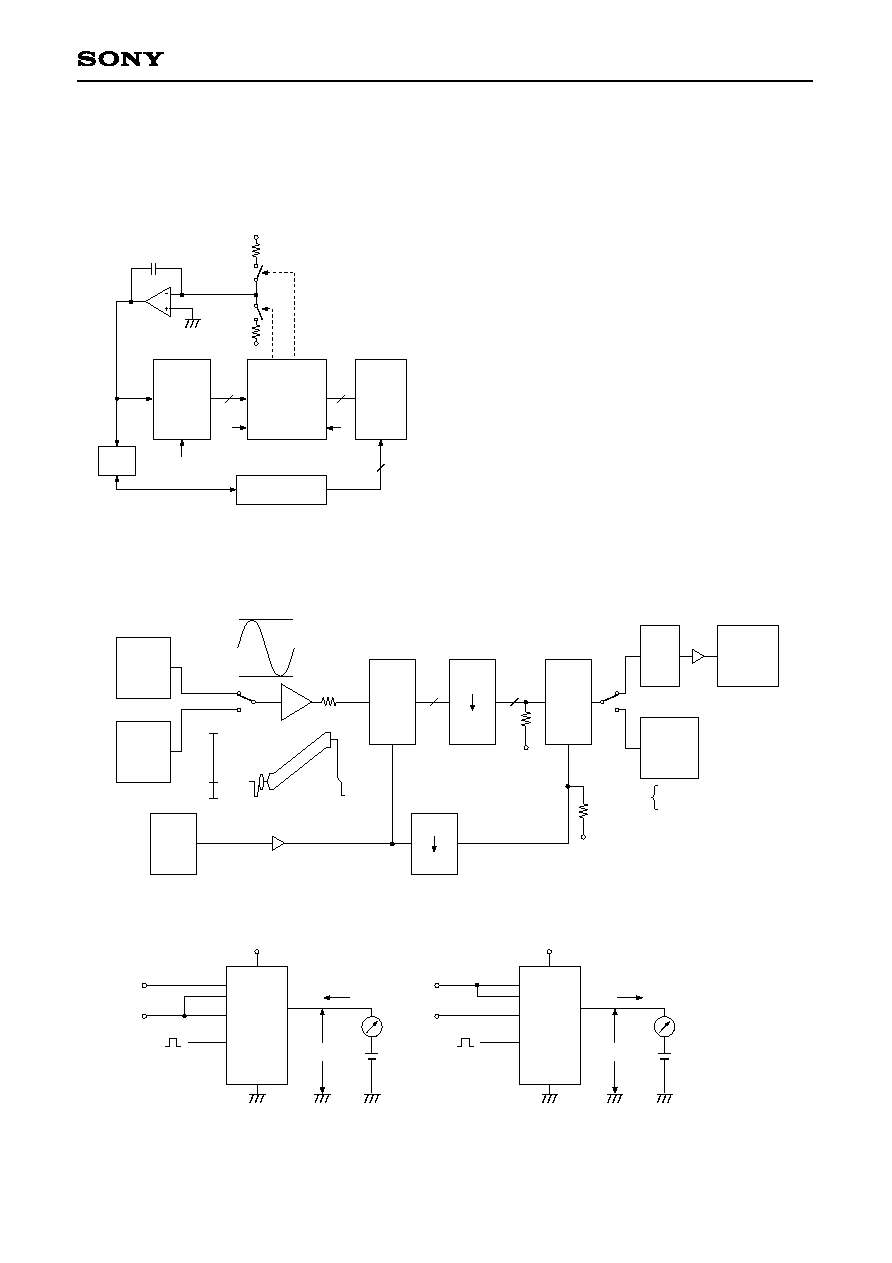

Block Diagram and Pin Configuration

Pln Description and Equivalent Circuits

Reference voltage

Lower

Sampling comparators

(3BIT)

Lower

Sampling comparators

(3BIT)

Upper

Sampling comparators

(3BIT)

Lower encoder

(3BIT)

Lower encoder

(3BIT)

Upper encoder

(3BIT)

Lower data

latchs

Upper data

latchs

Clook generator

9

10

11

12

13

14

15

16

2

3

4

5

6

7

8

1

AV

SS

DV

DD

AV

DD

VRB

V

IN

AV

DD

DV

DD

VRT

D

0

D

1

D

2

CLK

D

3

D

5

DV

SS

D

4

No. Symbol

Equivalent

Circuit

Description

D

0

(LSB) to D

5

(MSB) output

1 to 6

D

0

to D

5

Di

Analog input

12

V

IN

12

AV

DD

AV

SS

Analog GND

16

AV

SS

Clock input

7

8

9, 15

10, 14

DV

SS

DV

DD

AV

DD

Digital GND

Digital +5V

Analog +5V

CLK

DV

DD

7

DV

SS

Reference voltage (Top)

Reference voltage (Bottom)

11

13

VRT

VRB

13

11

AV

DD

AV

SS

≠ 3 ≠

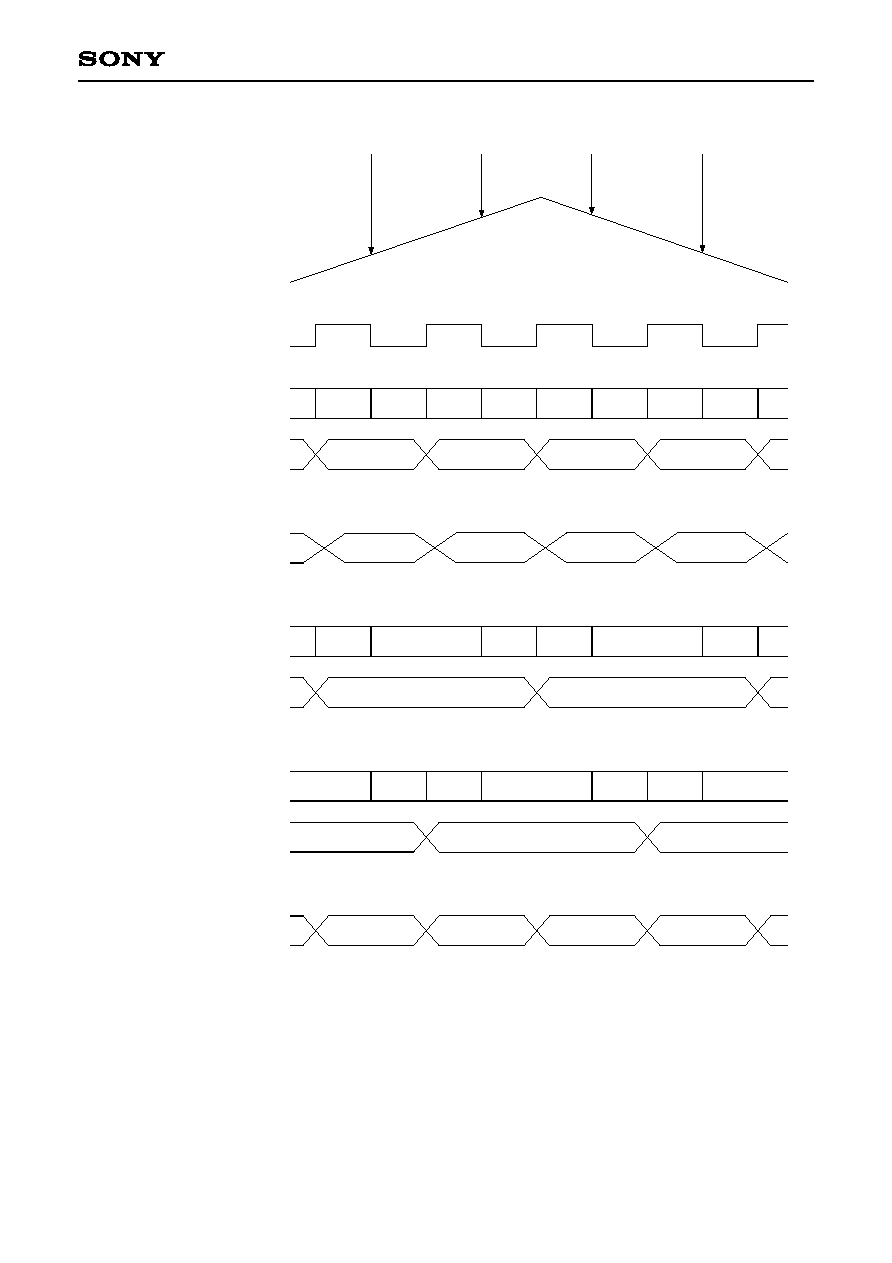

CXD1172AM/AP

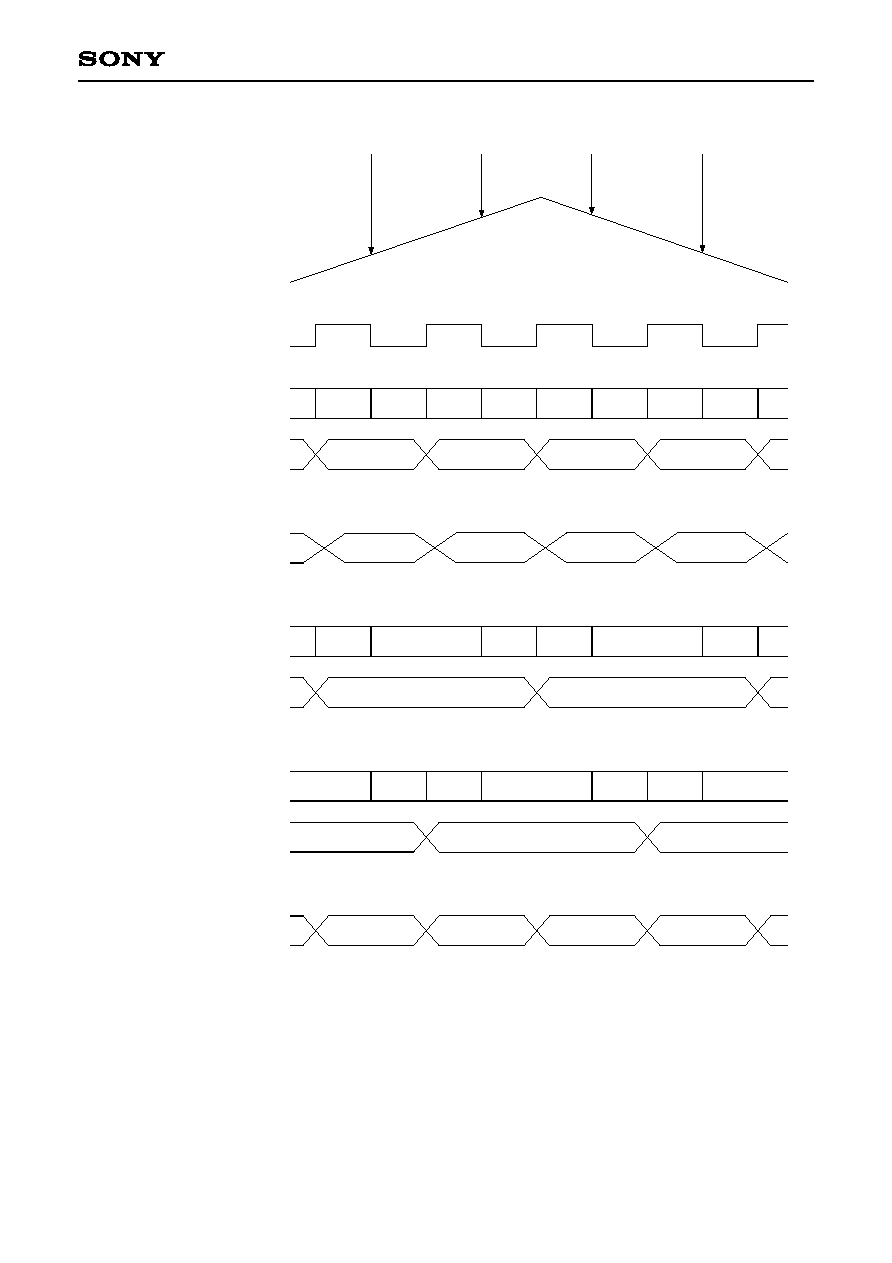

Clock

Data output

Analog input

T

PW1

T

PW0

N

N + 1

N + 2

N + 3

N + 4

N ≠ 3

N ≠ 2

N ≠ 1

N

N + 1

Td = 18ns

: Point for analog signal sampling.

Timing Chart 1

Input signal

voltage

Step

Digital output code

MSB LSB

V

RT

V

RB

0

31

32

63

1 1 1 1 1 1

1 0 0 0 0 0

0 1 1 1 1 1

0 0 0 0 0 0

Digital Output

Compatibility between Analog input voltage and the digital output code is indicated in the chart below.

..............

...

...

...

...

≠ 4 ≠

CXD1172AM/AP

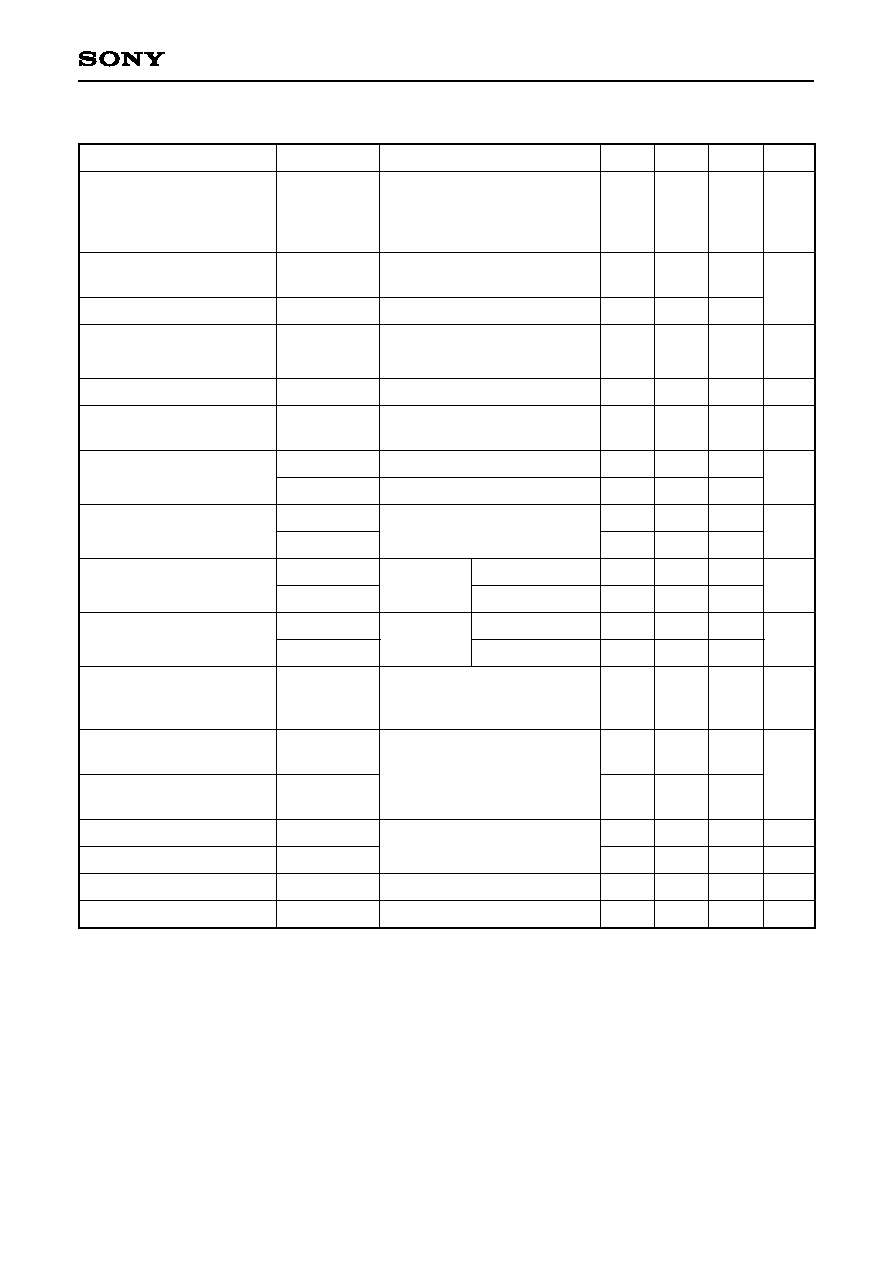

Electrical Characteristics

(V

DD

= 5V, V

RB

= 1.0V, V

RT

= 2.0V, Ta = 25∞C)

Conversion speed

Supply current

Reference pin current

Analog input band width

(≠1dB)

Analog input capacitance

Reference resistance

(V

RT

to V

RB

)

Offset voltage

1

Digital input voltage

Digital input current

Digital output current

Output data delay

Integral non-linearity error

Differential non-linearity

error

Differential gain error

Differential phase error

Aperture jitter

Sampling delay

0.5

3

175

0

15

4.0

≠1.1

3.7

V

DD

= 4.75 to 5.25V

Ta = ≠20 to +75∞C

V

IN

= 1.0 to 2.0V

f

IN

= 1kHz ramp

Fc = 20MSPS

NTSC ramp wave input

Envelope

V

IN

= 1.5V + 0.07Vrms

Potential difference to VRT

Potential difference to VRB

V

DD

= 4.75 to 5.25V

Ta = ≠20 to +75∞C

V

DD

= max.

V

DD

= min.

With TTL 1 gate and 10pF load

Ta = ≠20 to +75∞C

V

DD

= 4.75 to 5.25V

End point

NTSC 40 IRE mod ramp

Fc = 14.3MSPS

7

4

18

4

250

≠20

35

18

±

0.3

±

0.3

1.0

1.0

40

4

20

12

5.7

325

≠40

55

1.0

5

5

30

±

0.5

±

0.5

MSPS

mA

MHz

pF

mV

V

µA

mA

ns

LSB

%

deg

ps

ns

Item

Symbol

Conditions

Min.

Typ.

Max.

Unit

1

The offset voltage EOB is a potential difference between VRB and a point of position where the voltage

drops equivalent to 1/2 LSB of the voltage when the output data changes from "00000000" to "00000001".

EOT is a potential difference between VRT and a potential of point where the voltage rises equivalent to

1/2 LSB of the voltage when the output data changes from "11111111" to "11111110".

V

IH

= V

DD

V

IL

= 0V

V

OH

= V

DD

+ 0.5V

V

OL

= 0.4V

Fc

I

DD

I

REF

BW

C

IN

R

REF

E

OT

E

OB

V

IH

V

IL

I

IH

I

IL

I

OH

I

OL

T

DL

E

L

E

D

DG

DP

Taj

Tsd

≠ 5 ≠

CXD1172AM/AP

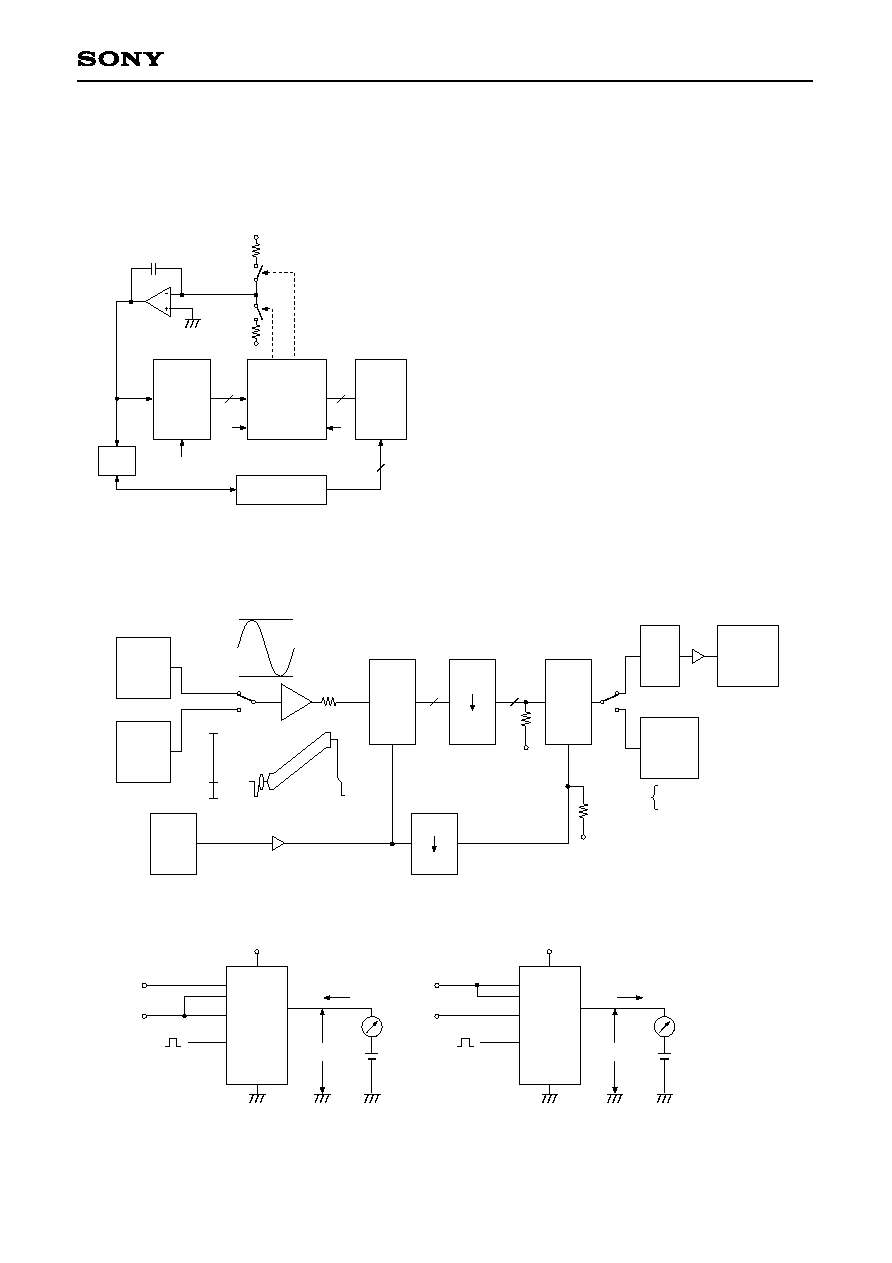

Integral non-linearity error

Differential non-linearity

}

Test Circuit

Offset voltage

CXD1172A

A < B

A > B

COMPARATOR

BUFFER

DVM

CONTROLLER

CLK (20MHz)

S

1

: ON

IF

A < B

S

2

: ON

IF

B > A

A6

A1

to

A0

B6

B1

B0

≠V

+V

S

2

S

1

6

6

6

"0"

"1"

000

...

00

to

111

...

0

V

IN

to

Maximum operational speed

Differential gain error

}

Test Circuit

Differential phase error

S. G.

NTSC

SIGNAL

SOURCE

S. G.

(CW)

TTL

ECL

CXD

1172A

10bit

D/A

TTL

ECL

COUNTER

ERROR RATE

VECTOR

SCOPE

H. P. F

1

2

620

≠5.2V

CX20202A-1

≠5.2V

CLK

6

6

620

AMP

1

2

100

0

≠40

1.0V

2.0V

40 IRE

MODULATION

BURST

SYNC

IAE

FC

2.0V

1.0V

F

C

≠ 1kHz

V

IN

D. G

D. P

Digital output current test circuit

V

CC

V

RT

V

IN

V

RB

CLK

GND

I

OH

V

OH

+

≠

2.0V

1.0V

V

CC

V

RT

V

IN

V

RB

CLK

GND

I

OL

V

OL

+

≠

2.0V

1.0V

Electrical Characteristics Test Circuit

≠ 6 ≠

CXD1172AM/AP

Analog input

Vi (1)

Vi (2)

Vi (3)

Vi (4)

S (1)

C (1)

S (2)

C (2)

S (3)

C (3)

S (4)

C (4)

MD (0)

MD (1)

MD (2)

MD (3)

RV (0)

RV (1)

RV (2)

RV (3)

S (1)

C (1)

H (1)

C (3)

H (3)

S (3)

LD (≠1)

LD (1)

C (0)

H (0)

C (2)

H (2)

S (2)

H (4)

S (4)

LD (≠2)

LD (0)

Out (≠2)

Out (≠1)

Out (0)

Out (1)

LD (2)

External clock

Upper comparators block

Upper data

Lower reference voltage

Lower comparators A block

Lower data A

Lower comparators B block

Lower data B

Digital output

Timing Chart 2

≠ 7 ≠

CXD1172AM/AP

Operation (See Block Diagram and Timing Chart)

1. CXD1172AM/AP is a 2-step parallel system A/D converter featuring a 3-bit upper comparators group and 2

Iower comparators groups of 3-bit each. The reference voltage that is equal to the voltage between VRT-

VRB/8 is constantly applied to the upper 3-bit comparator block. Voltage that corresponded to the upper

data is fed through the reference supply to the lower data.

2. This IC uses an offset cancel type comparator and operates synchronously with an external clock. It features

the following operating modes which are respectively indicated on the timing chart with S, H, C symbols.

That is input sampling (auto zero) mode, input hold mode and comparison mode.

3. The operation of respective parts is as indicated in the chart. For instance input voltage Vi (1) is sampled with

the falling edge of the first clock by means of the upper comparator block and the Iower comparator A block.

The upper comparators block finalizes comparison data MD (1) with the rising edge of the first clock.

Simultaneously the reference supply generates the lower reference voltage RV (1) that corresponded to the

upper results. The lower comparator block finalizes comparison data LD (1) with the rising edge of the

second clock. MD (1) and LD (1) are combined and output as Out (1) with the rising edge of the 3rd clock.

Accordingly there is a 2.5 clock delay from the analog input sampling point to the digital data output.

Operation Notes

1. V

DD

, Vss

To reduce noise effects, separate the analog and digital systems close to the device. For both the digital and

analog V

DD

pins, use a ceramic capacitor of about 0.1µF set as close as possible to the pin to bypass to the

respective GND's.

2. Analog input

Compared with the flash type A/D converter, the input capacitance of the analog input is rather small.

However it is necessary to conduct the drive with an amplifier featuring sufficient band and drive capability.

When driving with an amplifier of low output impedance, parasite oscillation may occur. That may be

prevented by inserting a resistance of about 100

in series between the amplifier output and A/D input.

3. Clock input

The clock line wiring should be as short as possible also, to avoid any interference with other signals,

separate it from other circuits.

4. Reference input

Voltage between VRT to VRB is compatible with the dynamic range of the analog input. Bypassing VRT and

VRB pins to GND, by means of a capacitor about 0.1µF, stable characteristics are obtained.

5. Timing

Analog input is sampled with the falling edge of CLK and output as digital data with a delay of 2.5 clocks and

with the following rising edge. The delay from the clock rising edge to the data output is about 18ns.

6. About latch up

It is necessary that AV

DD

and DV

DD

pins be the common source of power supply.

This is to avoid latch up due to the voltage difference between AV

DD

and DV

DD

pins when power is ON.

See "For latch up prevention" of CXD1172P/CXA1106P PCB description. (Page 6, 7)

≠ 8 ≠

CXD1172AM/AP

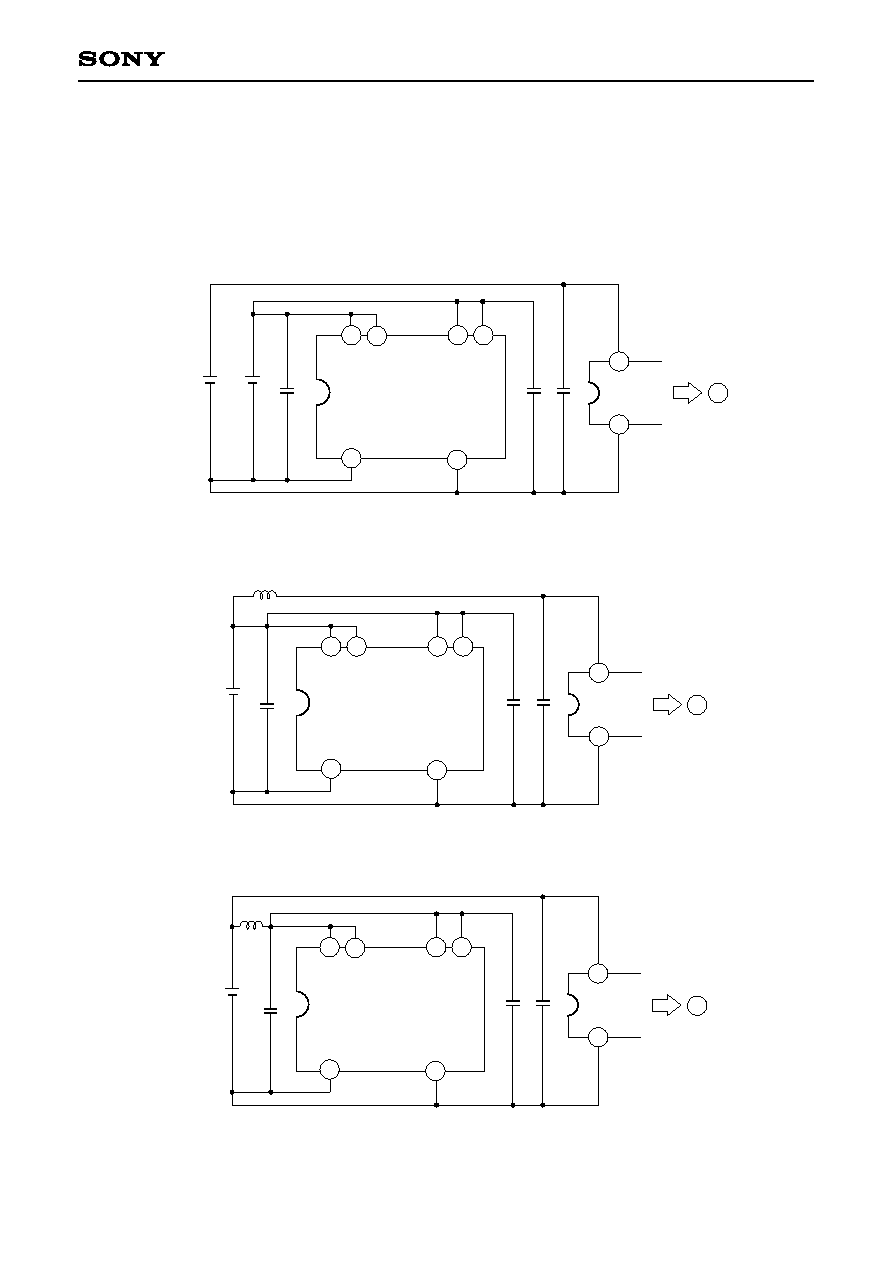

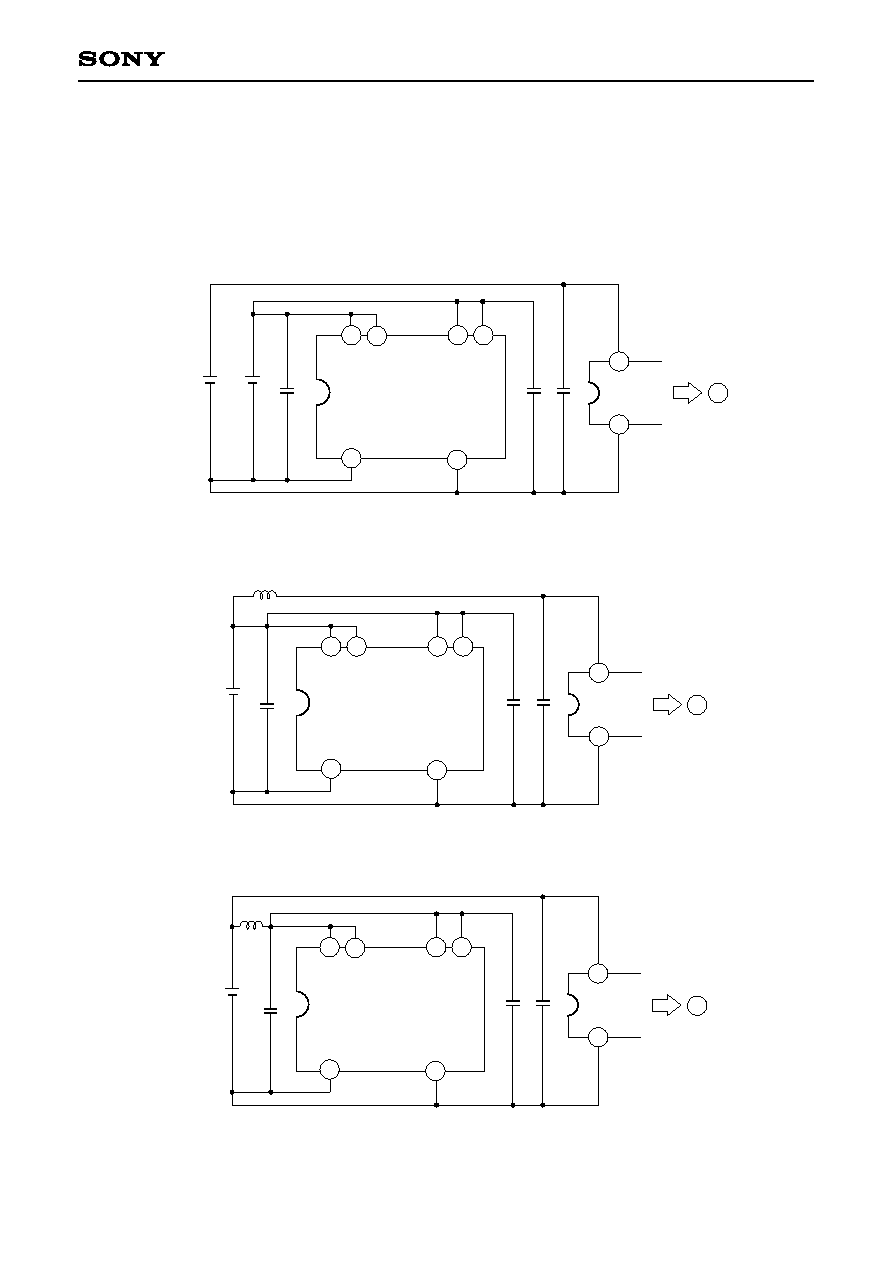

Latch Up Prevention

The CXD1172A is a CMOS IC which requires latch up precautions. Latch up is mainly generated by the lag in

the voltage rising time of AV

DD

(Pins 10 and 14) and DV

DD

(Pins 9 and 15), when power supply is ON.

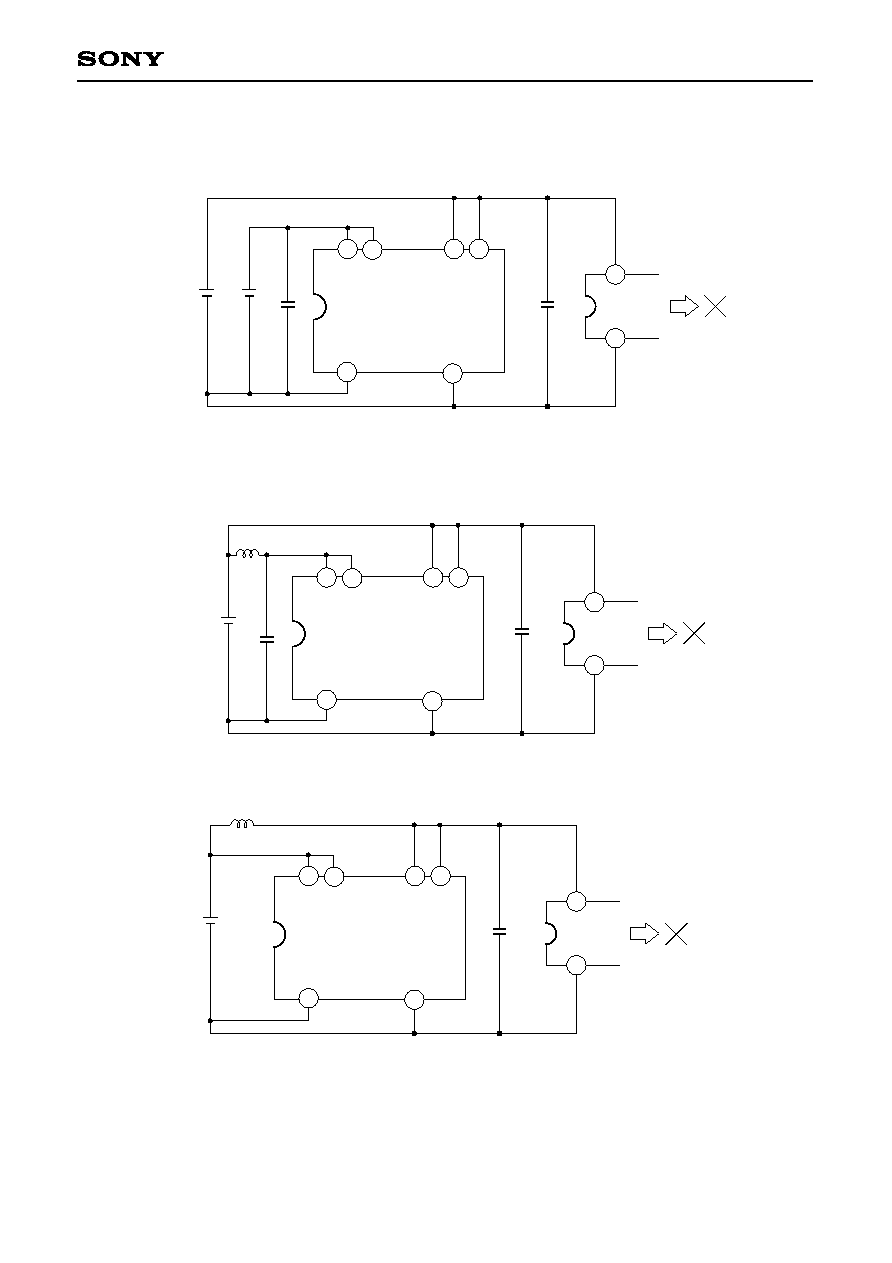

1. Correct usage

a. When analog and digital supplies are from different sources

+5V

AV

DD

+5V

AV

SS

DV

SS

C14

DV

DD

DIGITAL IC

C6

AV

SS

DV

SS

AV

DD

DV

DD

CXD1172A

14

15

9

10

8

16

b. When analog and digital supplies are from a common source

(i)

+5V

AV

SS

DV

SS

C14

DV

DD

DIGITAL IC

C6

AV

SS

DV

SS

AV

DD

DV

DD

CXD1172A

14

15

9

10

8

16

(ii)

+5V

C6

AV

SS

DV

SS

C14

DV

DD

DIGITAL IC

AV

SS

DV

SS

AV

DD

DV

DD

CXD1172A

14

15

9

10

8

16

≠ 9 ≠

CXD1172AM/AP

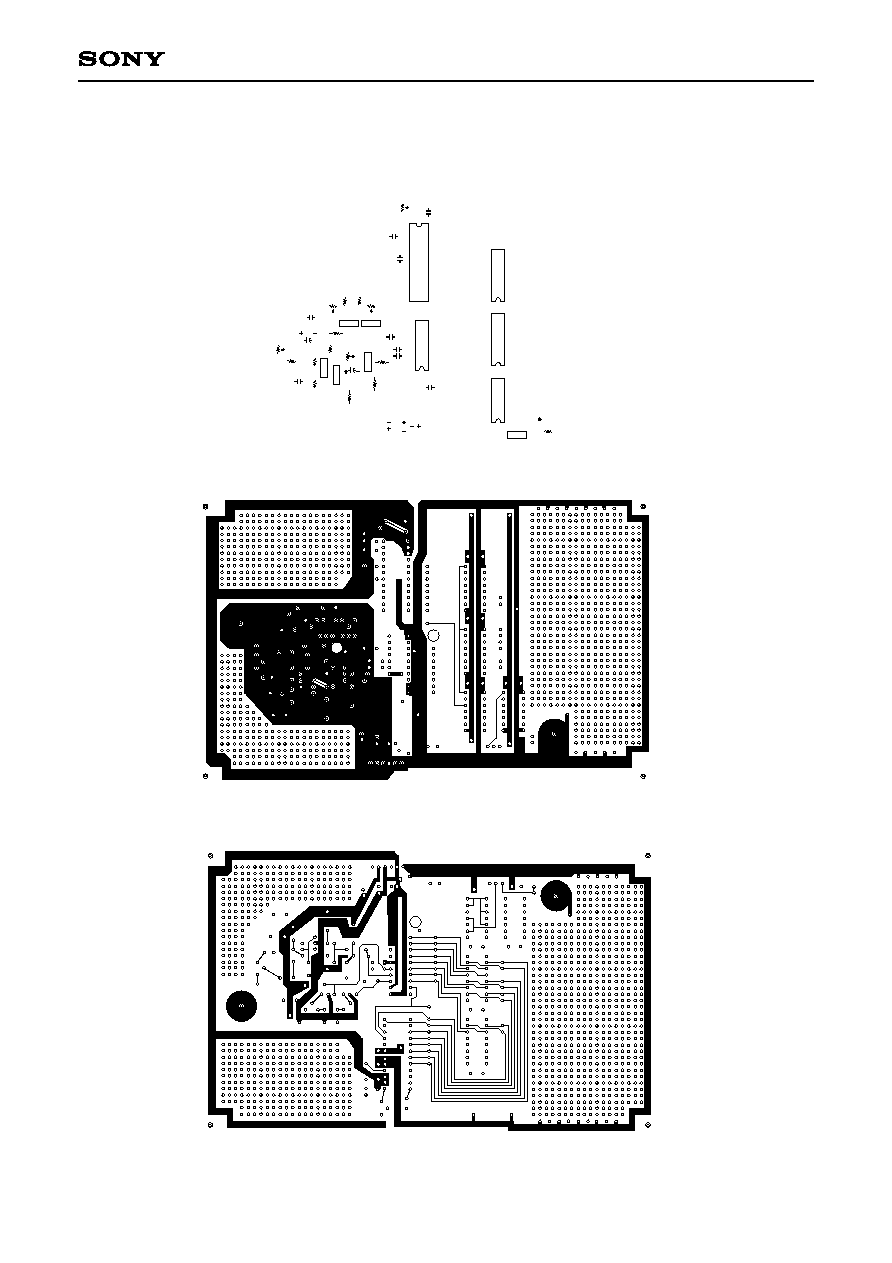

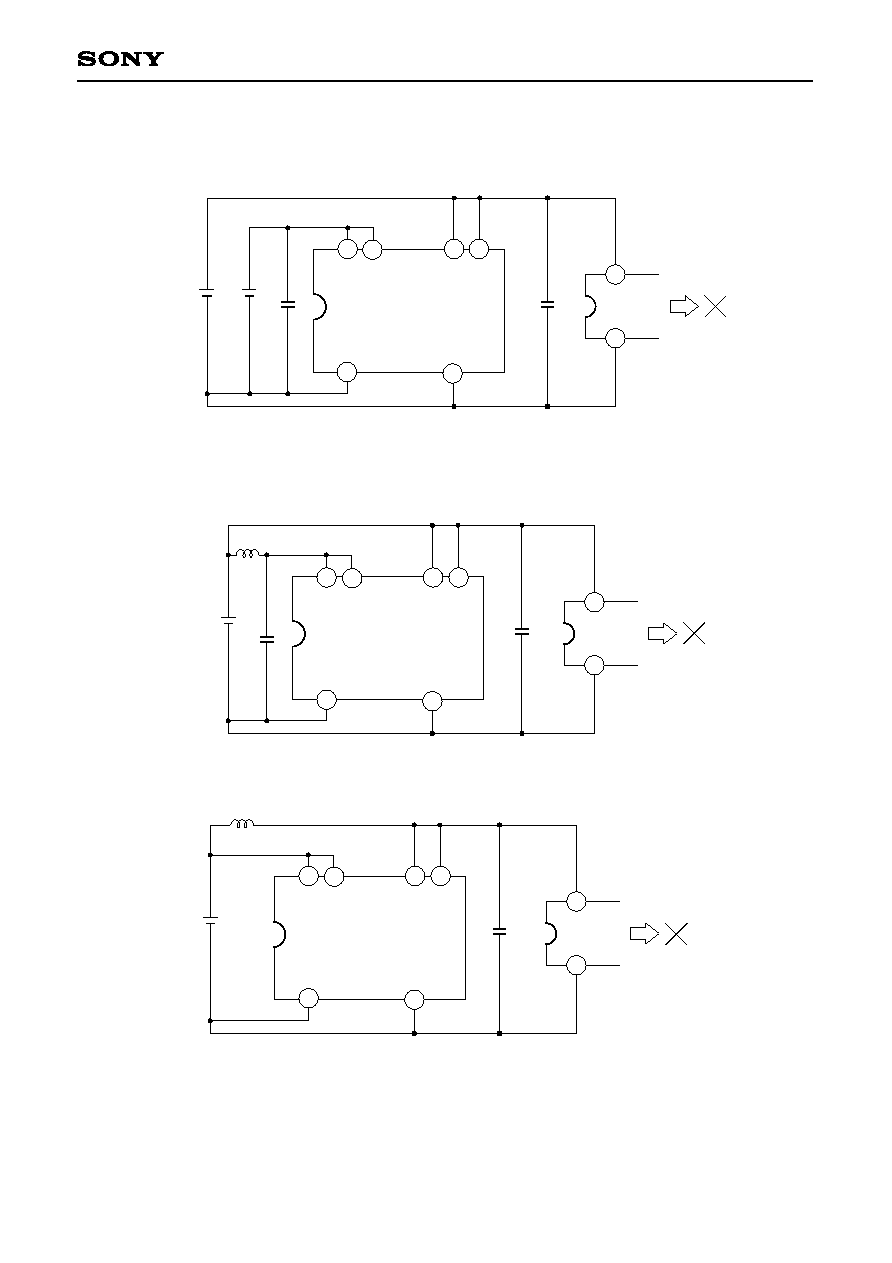

2. Example when latch up easily occurs

a. When analog and digital supplies are from different sources

+5V

AV

DD

+5V

AV

SS

DV

SS

DV

DD

DIGITAL IC

C6

AV

SS

DV

SS

AV

DD

DV

DD

CXD1172A

14

15

9

10

8

16

b. When analog and digital supplies are from common source

(i)

+5V

C6

AV

SS

DV

SS

DV

DD

DIGITAL IC

AV

DD

AV

SS

DV

SS

AV

DD

DV

DD

CXD1172A

14

15

9

10

8

16

(ii)

+5V

AV

SS

DV

SS

DV

DD

DIGITAL IC

AV

DD

AV

SS

DV

SS

AV

DD

DV

DD

CXD1172A

14

15

9

10

8

16

≠ 10 ≠

CXD1172AM/AP

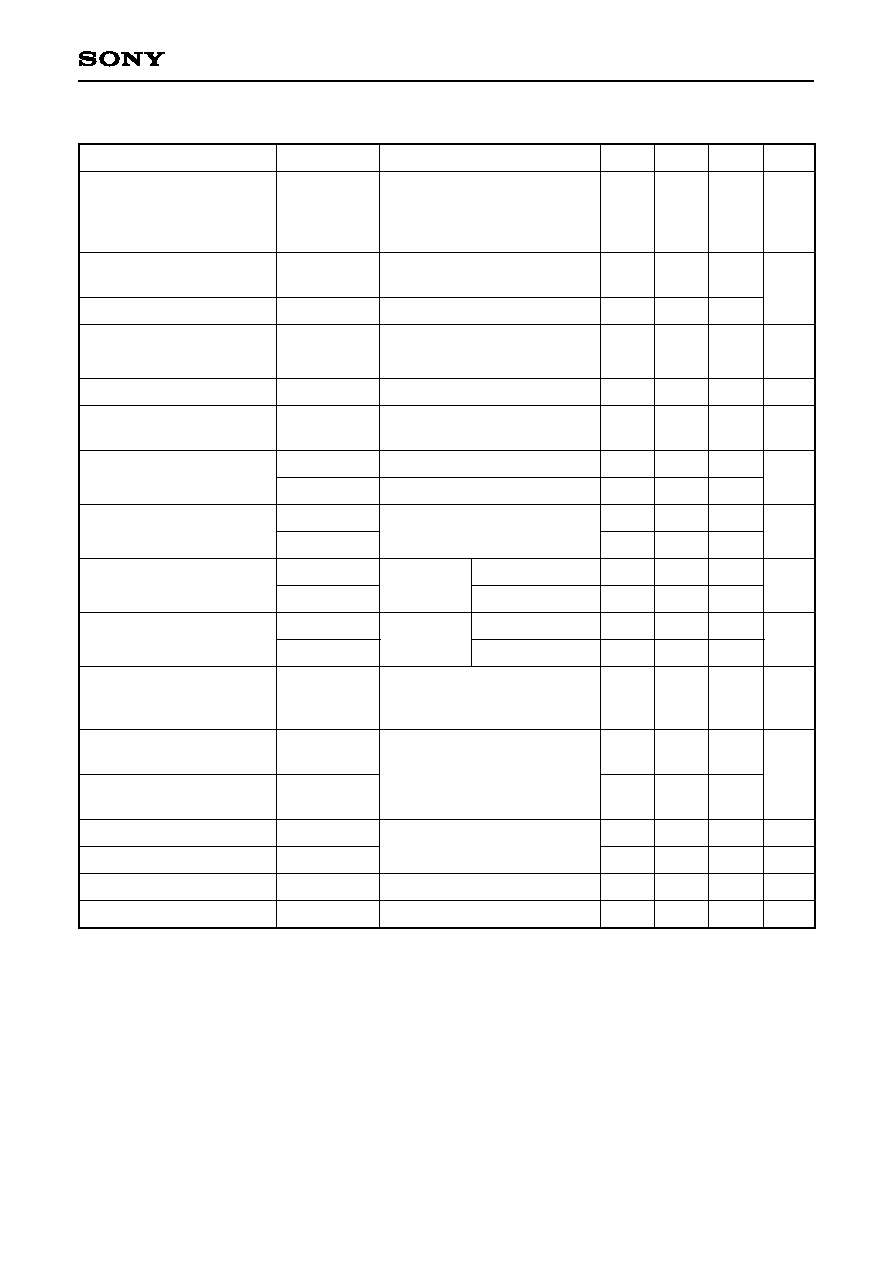

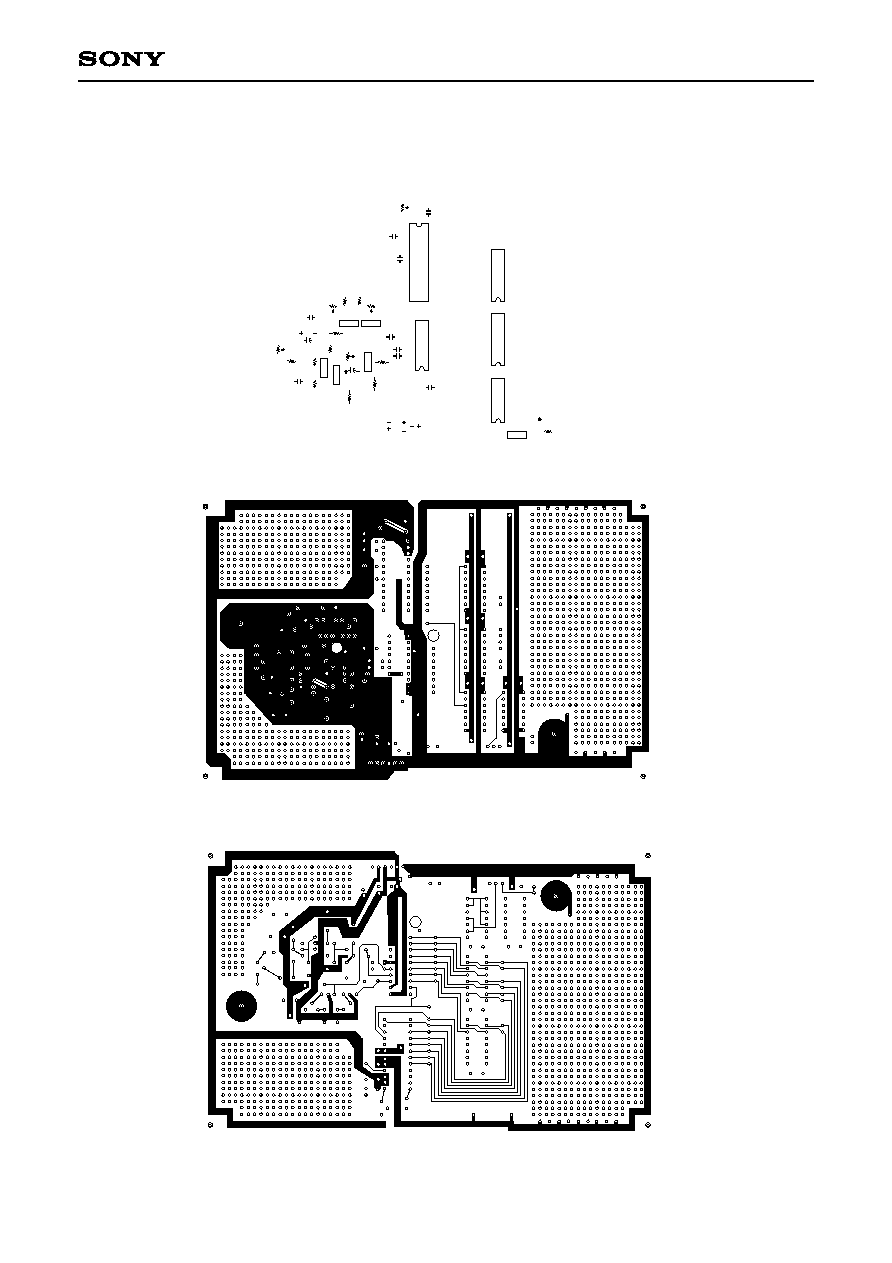

Component Side

Soldering Side

Silk Side

Analog

C8

C9

C10

DA OUT

VR5

VR4

R10

R9

VR3

C2

C1

VR1

S IN

R1 C3

R3

Q1

Q2

R2

R4

R5

VR2

C4

Q3

Q4

Q5

AGND

C5

C6

R7

R8

C7

R6

Analog

A.GND

C11 C12

C13

DV

DD

AV

DD

GND

+5V

≠5V

C14

D6

D4

D2

D7

D5

D3

D1

D0

CLK

CLK

D7

D6

Logic

D5

D4

D3

D2

D1

D0

OSC

SW

D.GND

R11

CLK IN

A1106P

D1172P

74S174

74S174

74HC04

2

1

3

6-bit, 20MSPS ADC and DAC Evaluation Board

≠ 11 ≠

CXD1172AM/AP

Package Outline

Unit: mm

CXD1172AM

PACKAGE STRUCTURE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE WEIGHT

SONY CODE

EIAJ CODE

JEDEC CODE

SOP-16P-L01

SOP016-P-0300-A

COPPER ALLOY

SOLDER PLATING

EPOXY RESIN

16PIN SOP (PLASTIC) 300mil

9.9 ≠ 0.1

+ 0.4

16

9

1

8

1.27

0.45 ± 0.1

5.3 ≠ 0.1

+ 0.3

7.9 ±

0.4

6.9

1.85 ≠ 0.15

+ 0.4

0.5 ±

0.2

0.2 ≠ 0.05

+ 0.1

0.1 ≠ 0.05

+ 0.2

0.2g

0.15

M

± 0.12

CXD1172AP

PACKAGE STRUCTURE

PACKAGE MATERIAL

LEAD TREATMENT

LEAD MATERIAL

PACKAGE MASS

EPOXY RESIN

SOLDER PLATING

COPPER ALLOY

19.2 ≠ 0.1

+ 0.4

9

1

8

2.54

0.5 ± 0.1

1.2 ± 0.15

3.0 MIN

0.5 MIN

3.7 ≠ 0.1

+ 0.4

6.4 ≠ 0.1

+ 0.3

7.62

0.25 ≠ 0.05

+ 0.1

0∞ to 15∞

16

16PIN DIP (PLASTIC)

1.0 g

SONY CODE

EIAJ CODE

JEDEC CODE

DIP-16P-01

DIP016-P-0300

Similar to MO-001-AE

1.All mat surface type.

Two kinds of package surface:

2.All mirror surface type.