| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXD1818 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

≠ 1 ≠

CXD1818R

E97528-PS

CD-ROM Decoder

Description

The CXD1818R is a CD-ROM decoder LSI with a

built-in Fast SCSI controller. This supports 32

◊

speed

playback.

Features

∑ Ultra SCSI controller (Target mode)

∑ Maximum transfer speed of 20MB/s (when using

Ultra SCSI synchronous transfer)

∑ SCSI overhead reduced by executing multiple

SCSI sequences

∑ Supports SCAM Level 2

∑ Compatible with CD-ROM, CD-I and CD-ROM XA

formats

∑ Real-time error correction

∑ Capable of handling up to 32

◊

speed playback

∑ Multiblock auto-transfer function

∑ Can read subcode-Q data for each byte from the

sub CPU

∑ Real-time subcode (R to W) error correction

∑ Serial transfer of commands to CD DSP

∑ Connectable with standard DRAM of up to 8M bits

(1024K bytes)

∑ DRAM bit width selectable for 8 bits or 16 bits

∑ ESP function

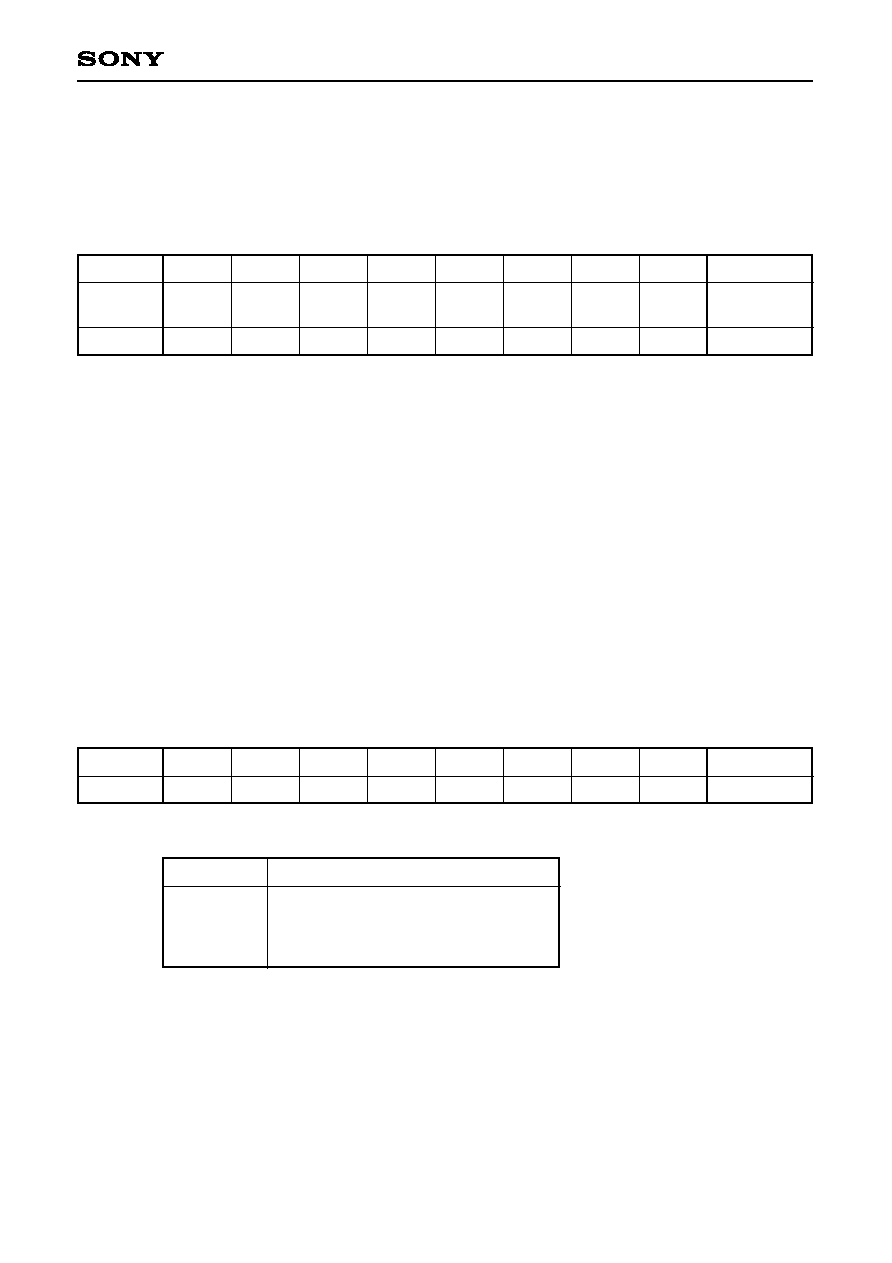

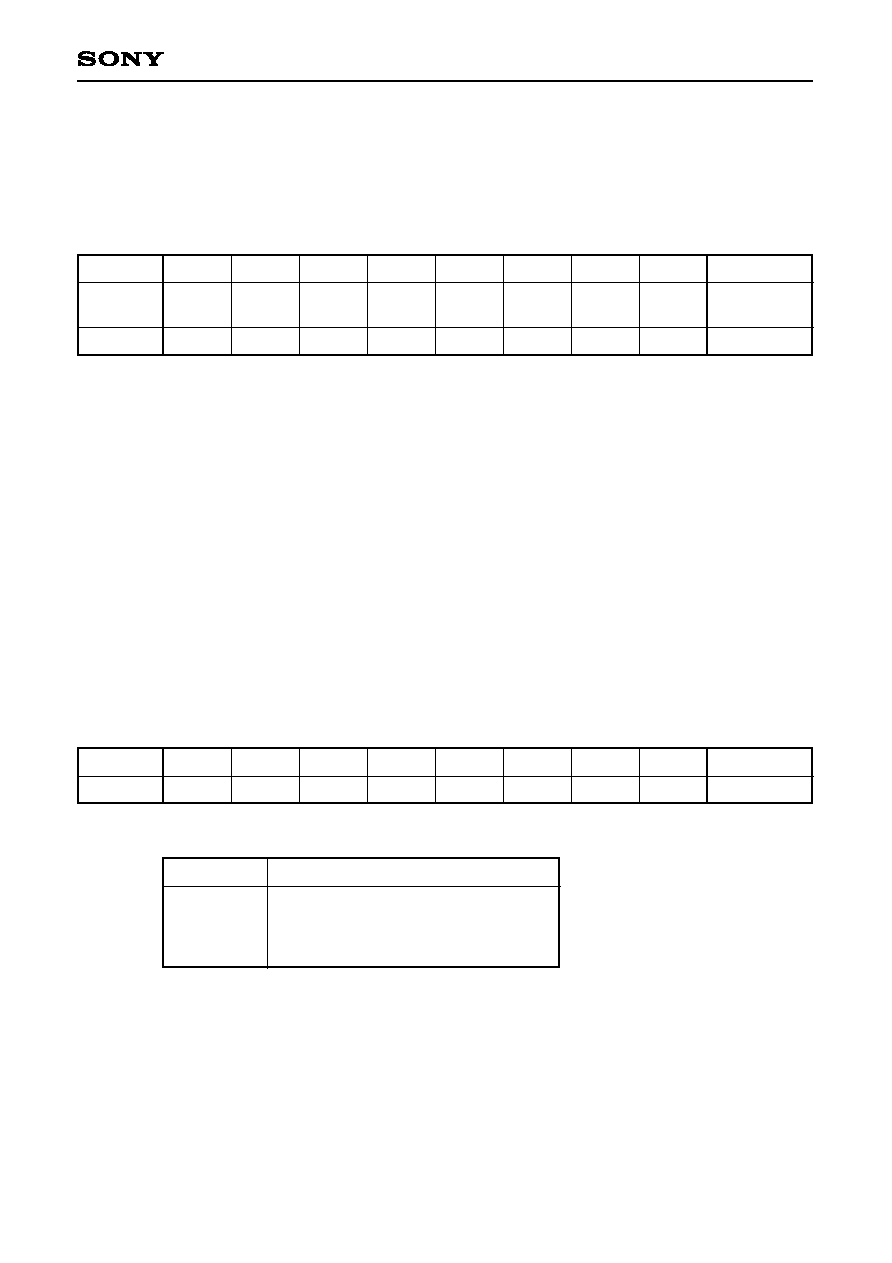

Absolute Maximum Ratings (Ta = 25∞C)

∑ Supply voltage

V

DD

≠0.5 to +7.0

V

∑ Input voltage

V

I

≠0.5 to V

DD

+ 0.5

V

∑ Output voltage

V

O

≠0.5 to V

DD

+ 0.5

V

∑ Operating temperature Topr

≠20 to +75

∞C

∑ Storage temperature

Tstg

≠55 to +150

∞C

Recommended Operating Conditions

∑ Supply voltage

V

DD

4.5 to 5.5 (5.0 typ.) V

∑ Operating temperature Topr

≠20 to +75

∞C

∑ Crystal oscillation

X'tal

40

MHz

Applications

CD-ROM drives

Structure

Silicon gate CMOS IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

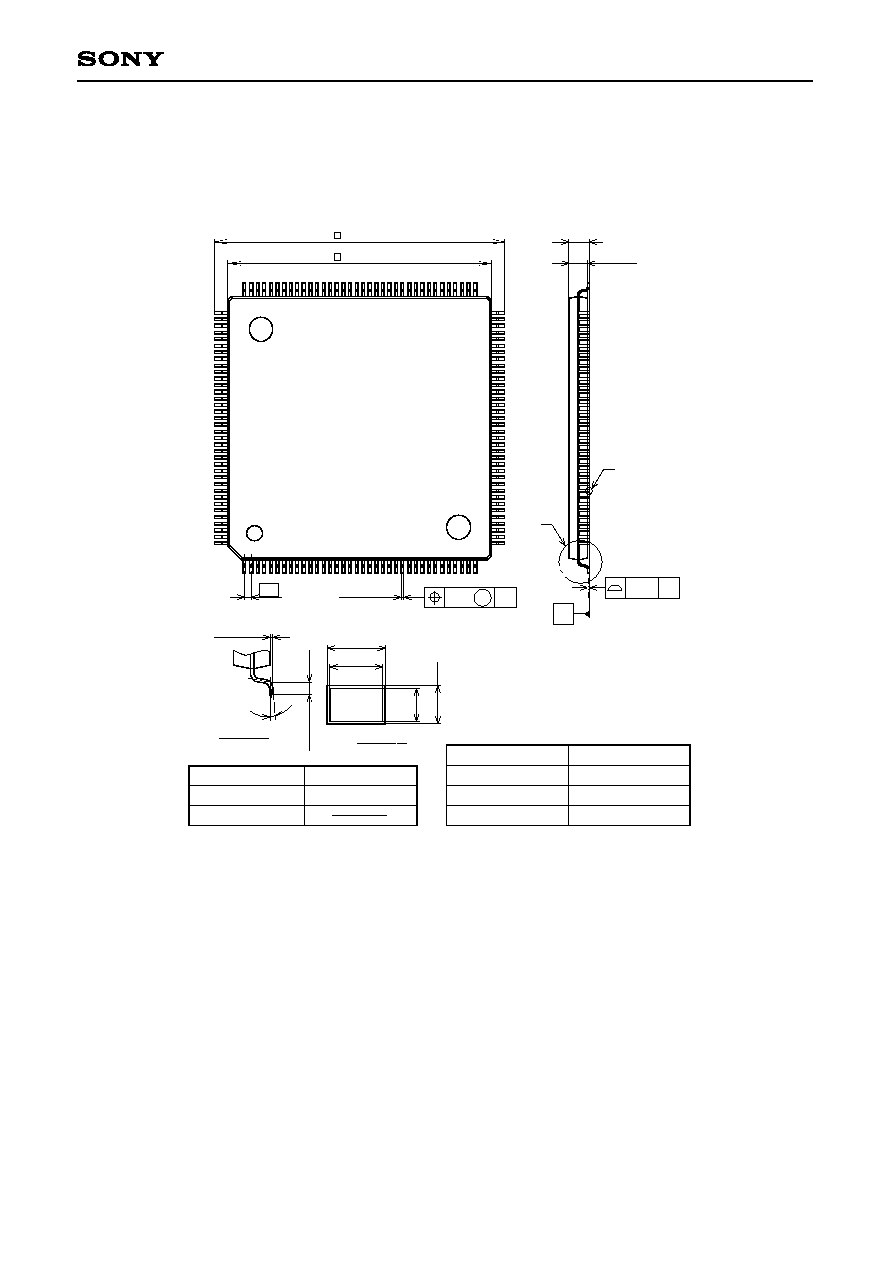

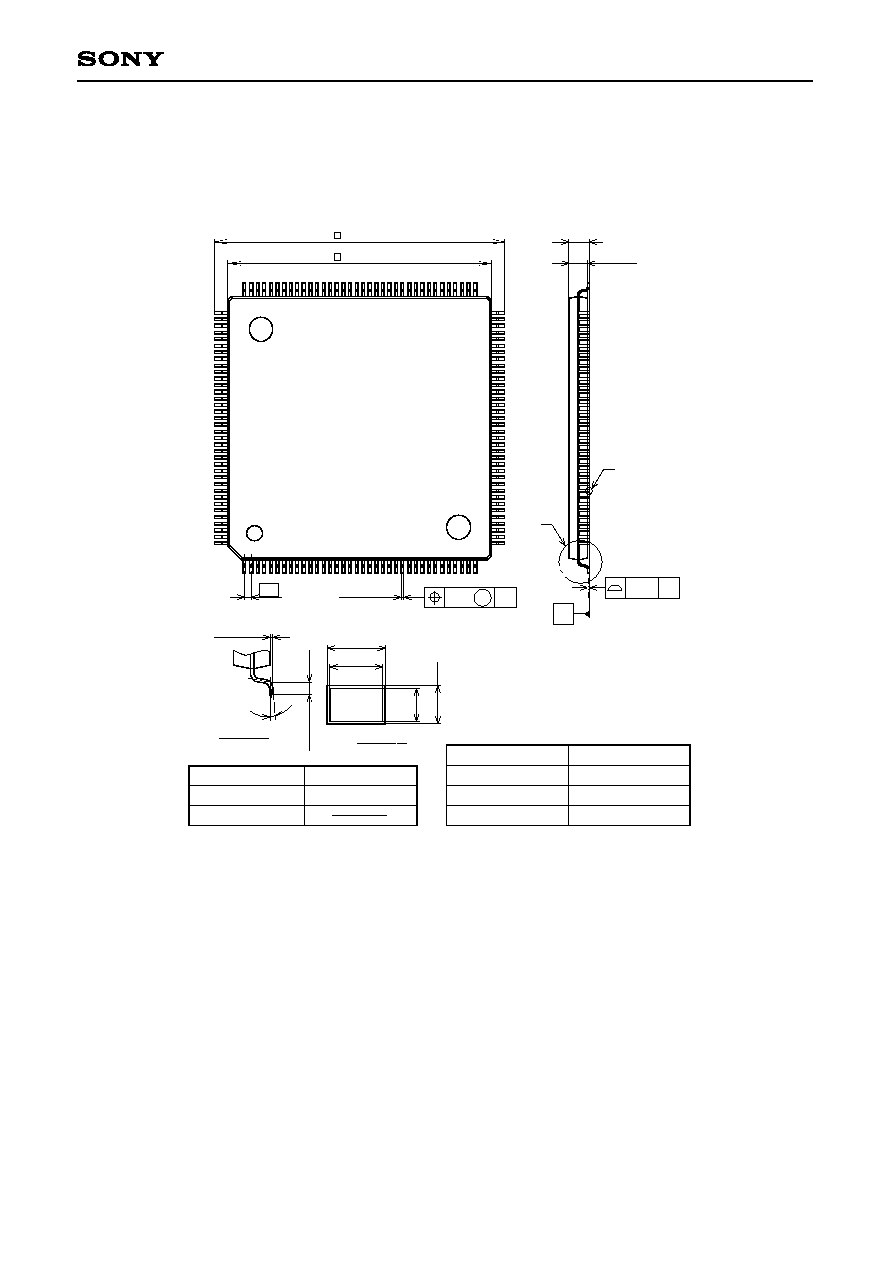

144 pin LQFP (Plastic)

For the availability of this product, please contact the sales office.

≠ 2 ≠

CXD1818R

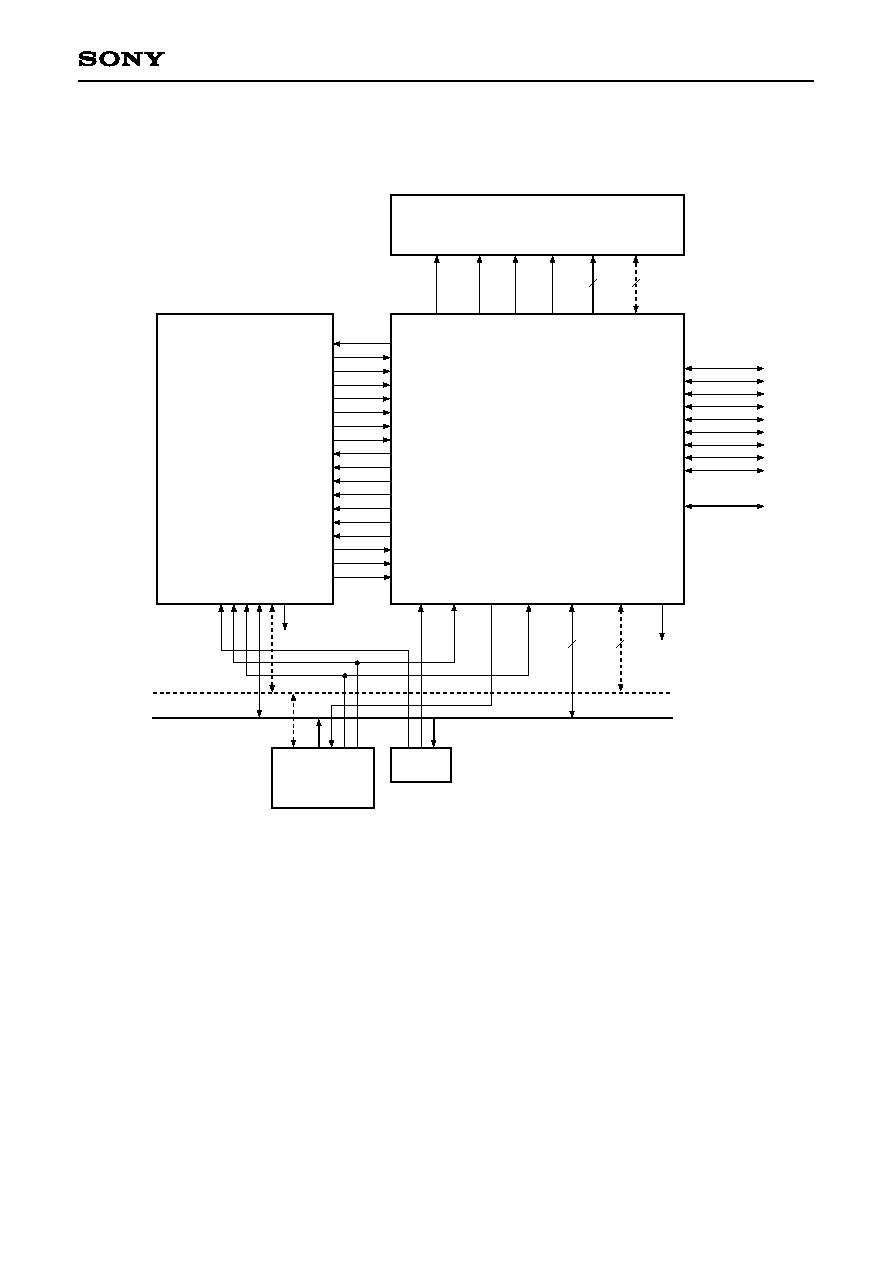

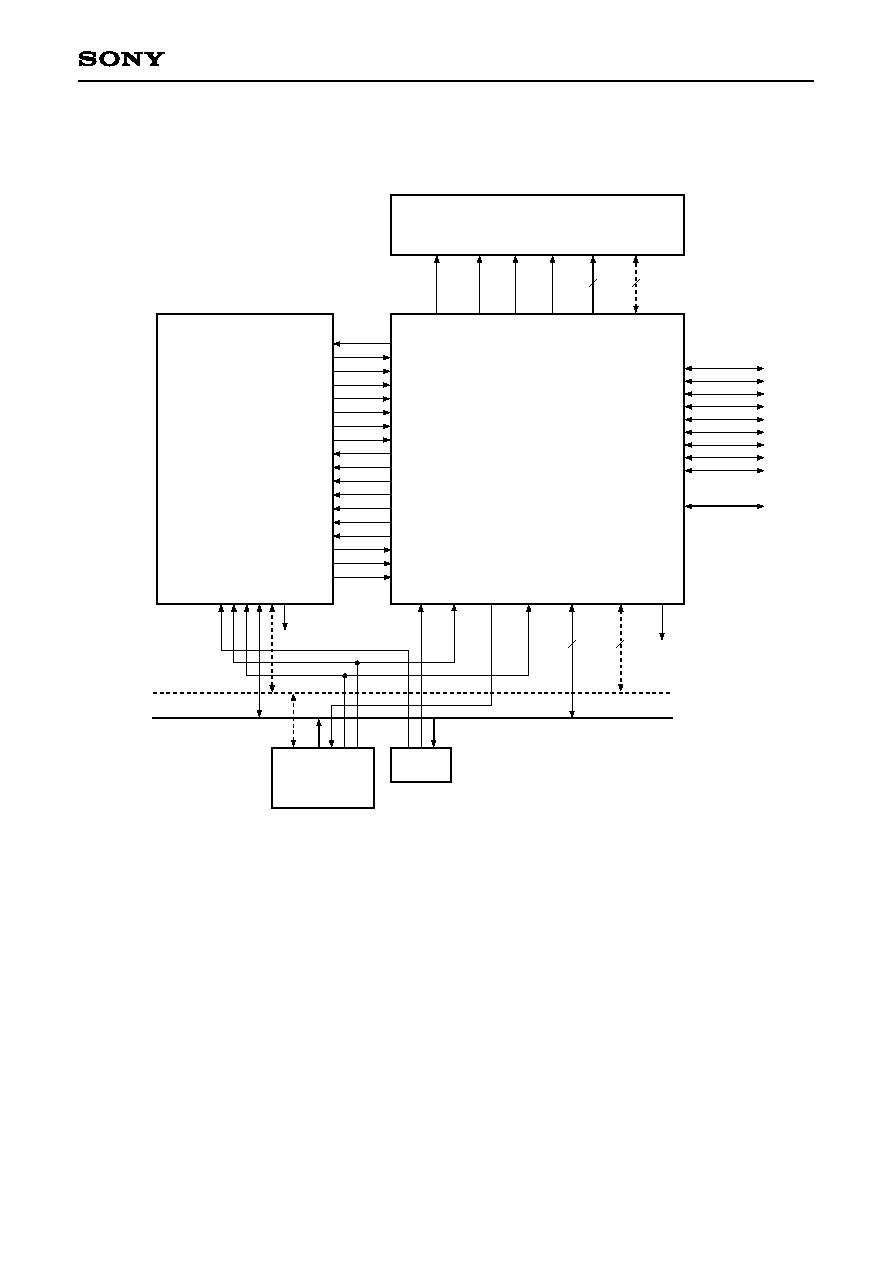

Connection Example

Address

Decoder

sub CPU

CPU data bus

CPU address bus

8bit

7bit

16bit

10bit

SCSI Bus

XATN

XBSY

XACK

XRST

XSEL

XMSG

XCD

XREQ

XIO

XDBP,

XDB (7:0)

EXCK

SBIN

SCOR

WFCK

C2PO

BCLK

MDAT

LRCK

XLAT

DATO

DSTB

A (6:0)

XCS XWR XWAT XRD

D (7:0)

INT

MDB

(15:0)

MA

(9:0)

XRAS

XLCAS

XUCAS

XMWR

CXD1818R

CD-ROM Decoder

&

SCSI I/F

CD DSP

Buffer RAM

GRST

DACD

DSPCK

LRCO

BCKO

GSCR

XROF

≠ 3 ≠

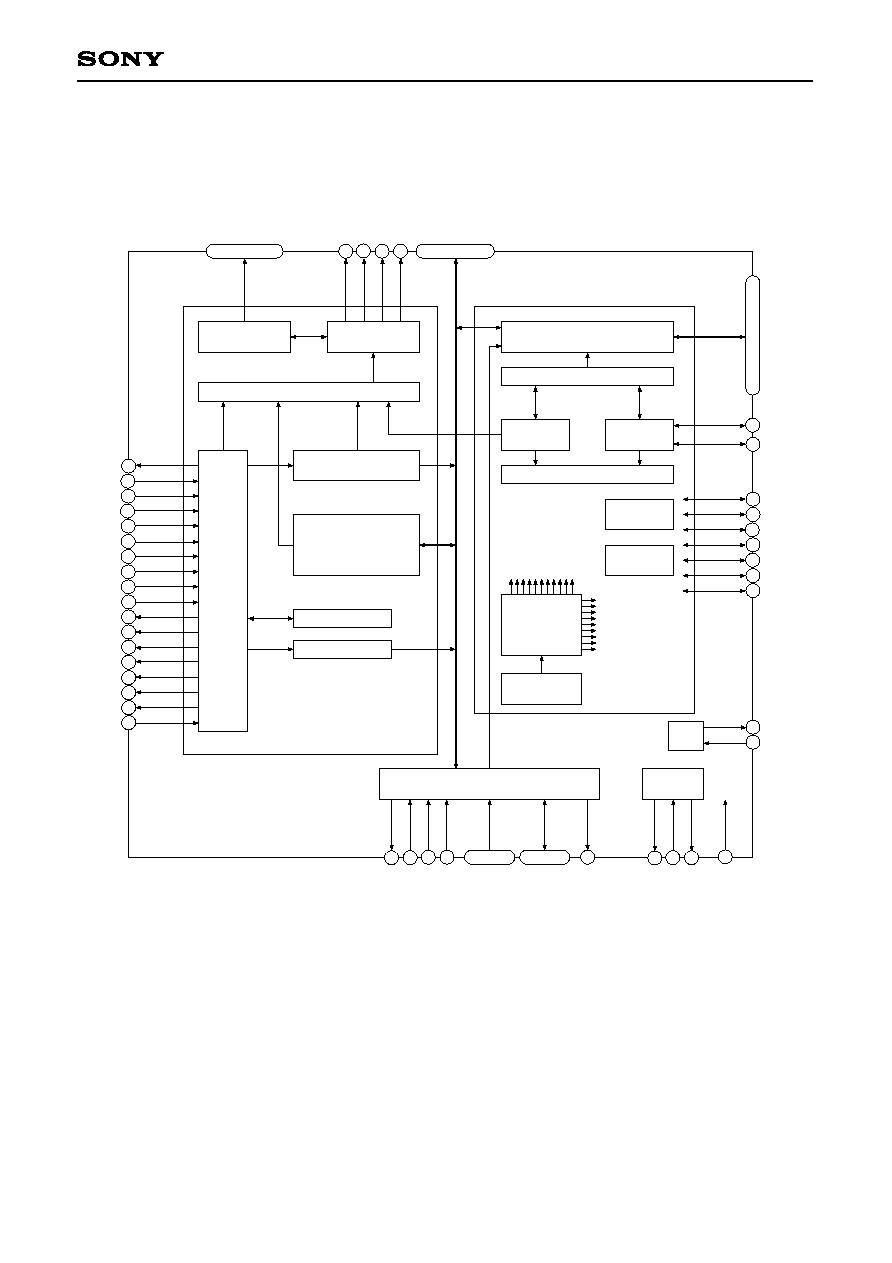

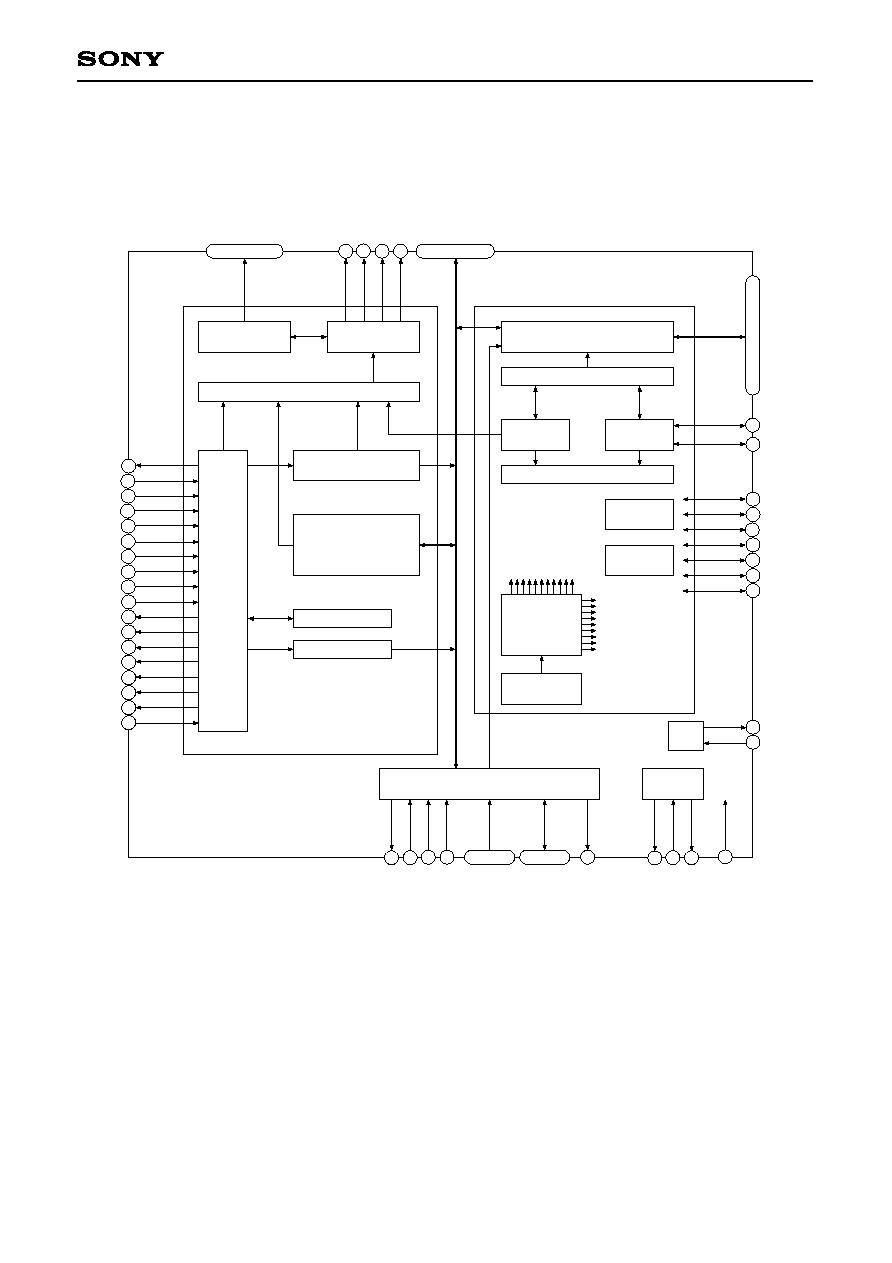

CXD1818R

Block Diagram

65

141 142 143 144

122

123 to 129

131 to 138

54 to 60, 62 to 64

71 to 78, 80 to 87

3

∑

5

∑

8

∑

10

∑

11

∑

15

∑

17

∑

19

∑

22

CD-ROM Decoder Block

SCSI Controller Block

sub CPU

I/F

Descrambler

Sync Control

Priority Resolver

FIFO Control

16byte FIFO

24bit Transfer Byte Counter

Microcode

ROM

Microcode

Core

&

Registers

Arbitration

Selection

SCSI

Phase Ctrl

SCSI

Handshake

Buffer

Handshake

Buffer

Address Gen.

DMA

Sequencer

Subcode

Deinterleave & ECC

Main Data

Error Correction

CD DSP

I/F

MA (0:9)

MDB (0:15)

XMWR

XUCAS

XLCAS

XRAS

EXCK

SBIN

SCOR

WFCK

C2PO

BCLK

MDAT

LRCK

DSPCK

GSCR

DATO

XDB (0:7)

XDBP

XREQ

XACK

XRST

XBSY

XATN

XSEL

XCD

XMSG

XIO

D (7:0)

A (0:6)

XWAT

XTL2

CLK

XTL1

XRES

XCS

XWR

INT

XRD

101

102

103

106

107

108

109

90

91

92

93

94

95

96

97

99

100

110

XLAT

DSTB

BCKO

DACD

LRCO

GRST

XROF

66

67

68

41

29

30

26

24

36

39

35

43

VCO

44

45

48

49

50

53

Clock

Gen.

CM1

AC

≠ 4 ≠

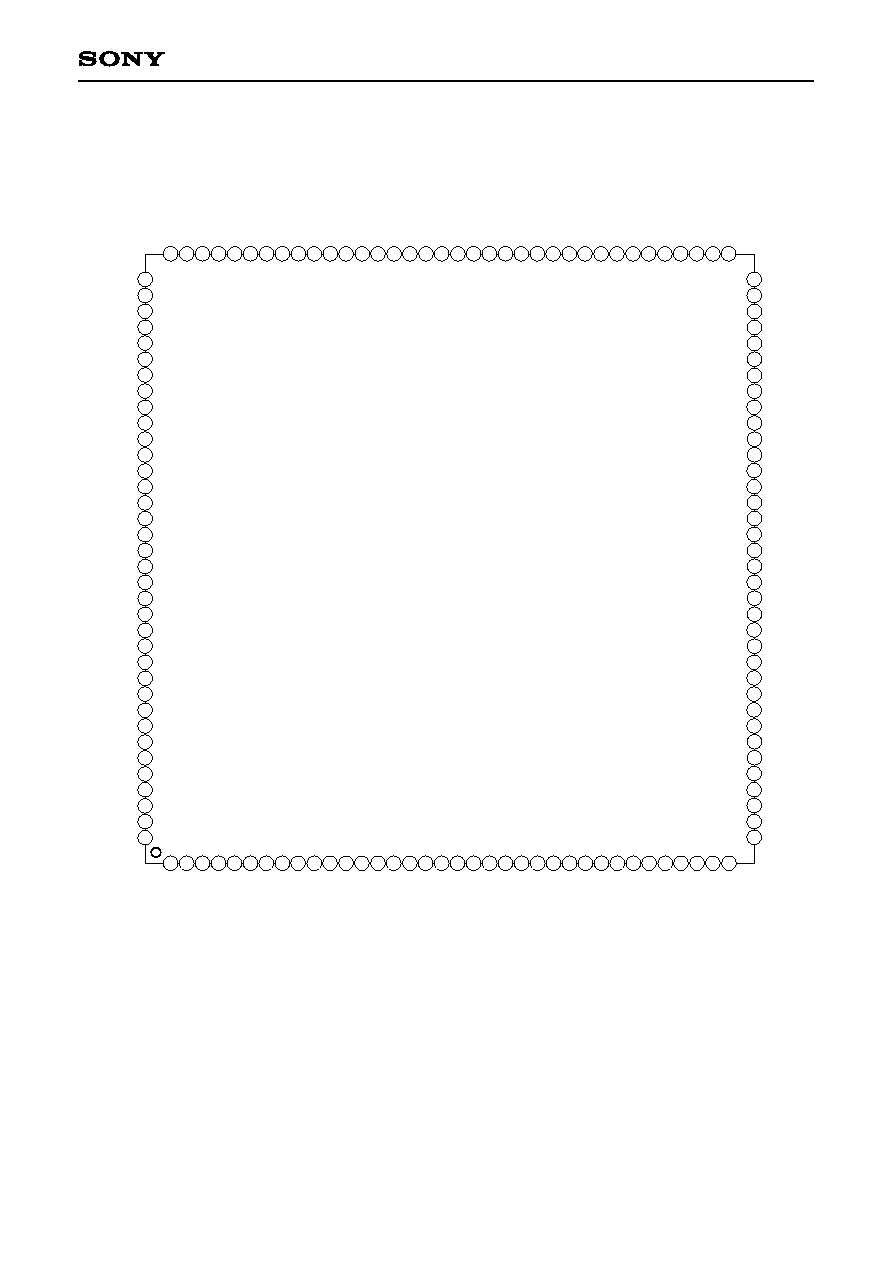

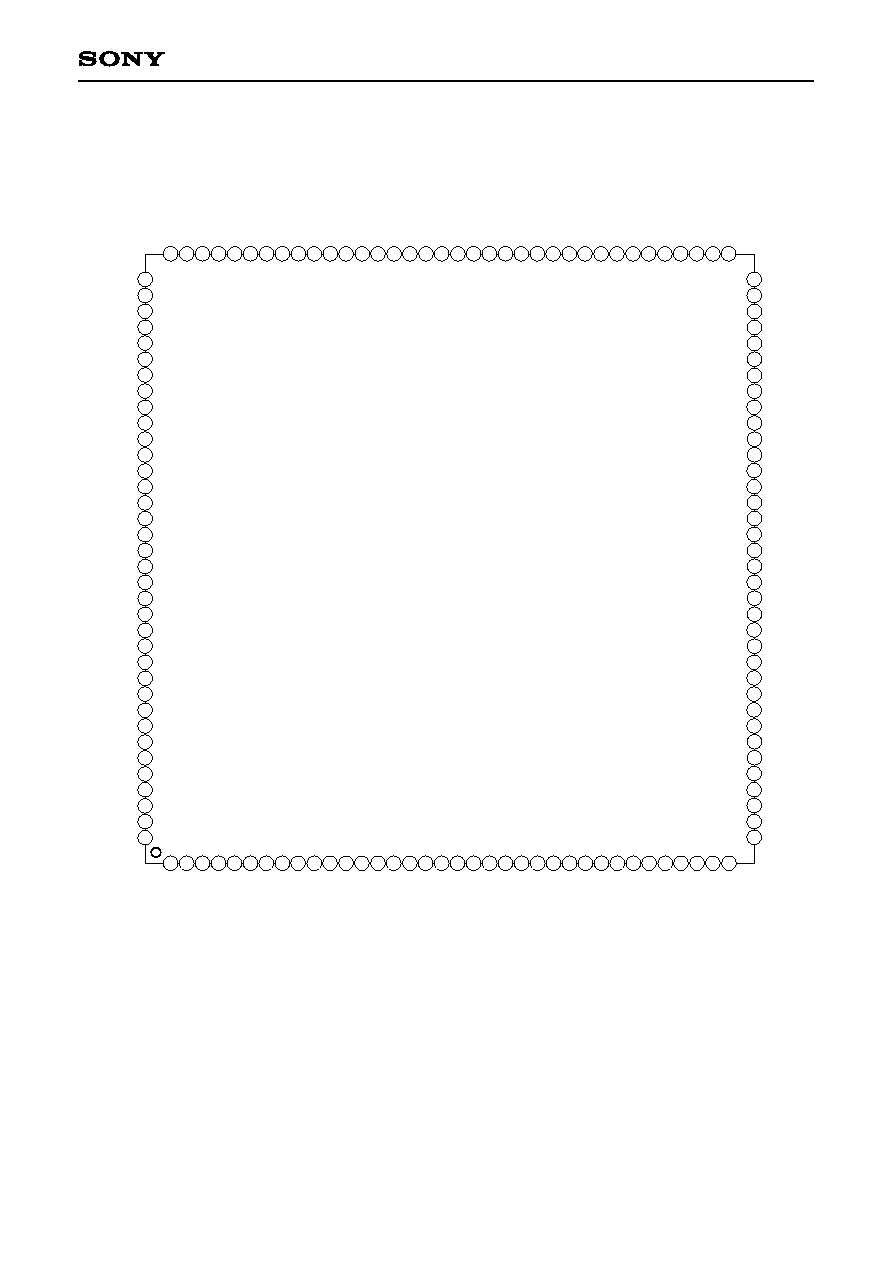

CXD1818R

Pin Configuration

36

35

34

31 32 33

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30

1

40

39

38

37

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

70

69

68

67

63

64

65

66

61

62

71

72

97 96 95 94

91

92

93

100 99 98

101

102

103

104

105

106

107

108

73

74

81

82

83

84

75

76

77

78

88 87 86 85

79

80

89

90

111

109

110

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

MA4

MA3

MA2

MA1

MA0

XRES

V

DD

V

SS

XTL1

XTL2

AV

DD

AV

SS

AC

CM1

XIO

V

SS

XREQ

V

SS

V

SS

V

DD

XDB0

V

DD

XDB2

V

SS

XDB3

XDB4

V

SS

V

SS

V

DD

XDB5

V

SS

XDB6

V

SS

XDB7

V

SS

V

DD

XDBP

V

SS

XATN

V

SS

XBSY

V

SS

XACK

XRST

V

SS

V

SS

V

DD

TST1

TST2

TST3

V

SS

TST4

TST5

TST6

TST7

V

SS

V

DD

XWAT

A0

A1

A2

A3

A4

A5

A6

V

SS

D0

D1

D2

D3

D4

D5

D6

D7

V

SS

V

DD

INT

XCS

XWR

XRD

TST0

LRCO

DACD

V

DD

V

SS

DSTB

XLAT

GSCR

DSPCK

MDB6

V

SS

LRCK

MDAT

BCLK

C2PO

WFCK

SCOR

V

DD

V

SS

MDB15

MDB14

MDB13

MDB12

MDB11

MDB10

MDB8

V

SS

MDB7

MDB5

MDB4

MDB3

XMWR

XLCAS

XUCAS

XRAS

MA9

MA8

MA7

V

SS

MA6

MA5

MDB0

V

DD

V

SS

MDB1

CLK

BCKO

DATO

SBIN

EXCK

MDB9

MDB2

XROF

GRST

XDB1

V

SS

V

SS

V

DD

XCD

V

DD

V

SS

V

SS

XWSG

XSEL

≠ 5 ≠

CXD1818R

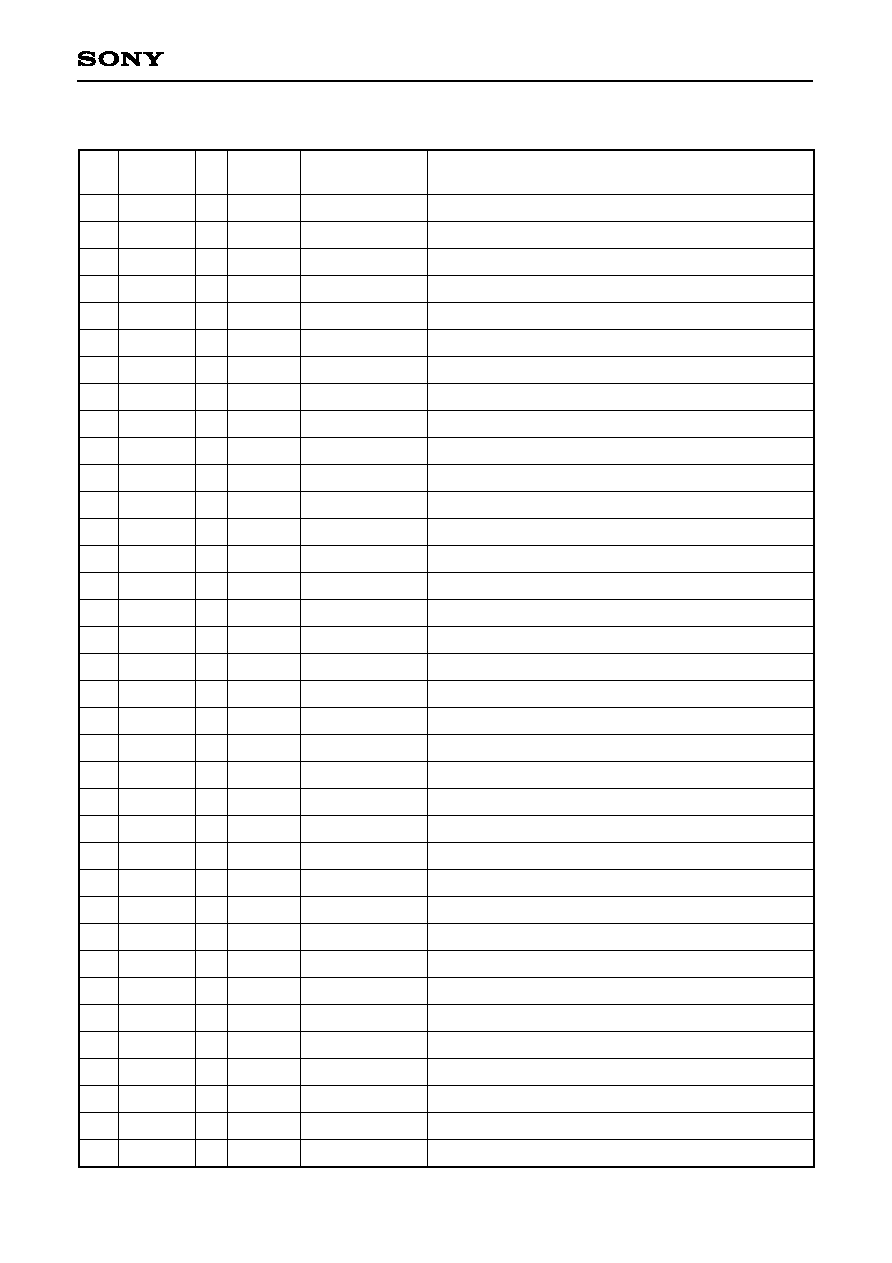

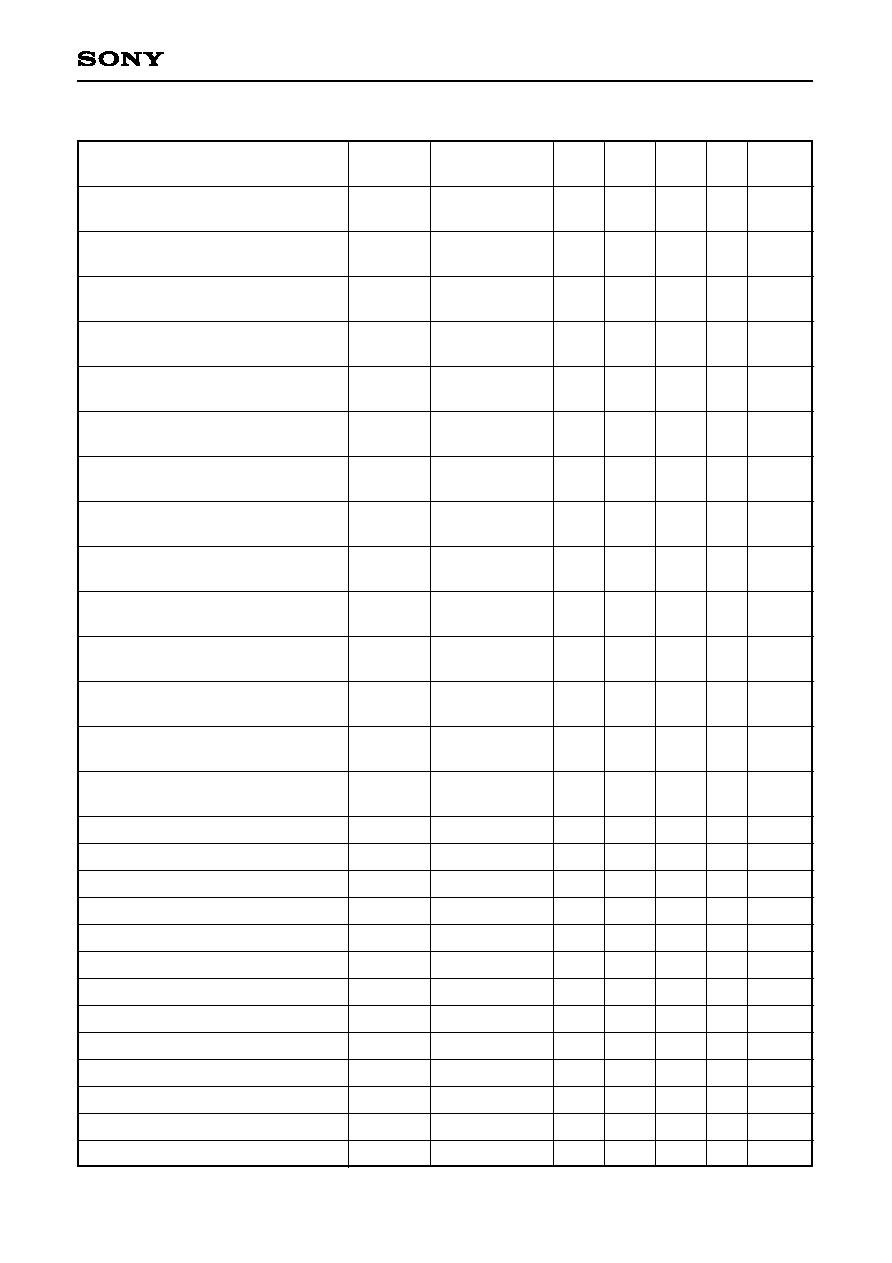

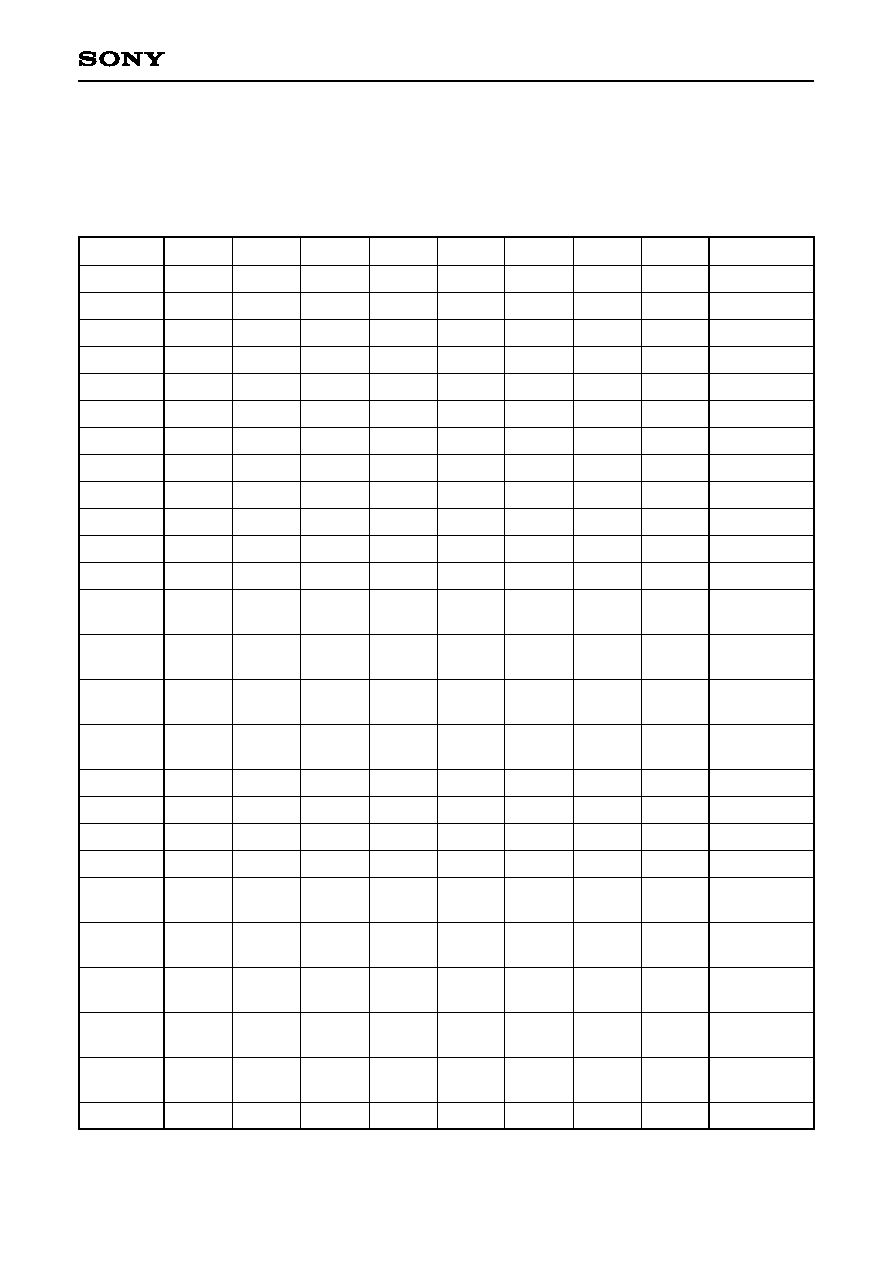

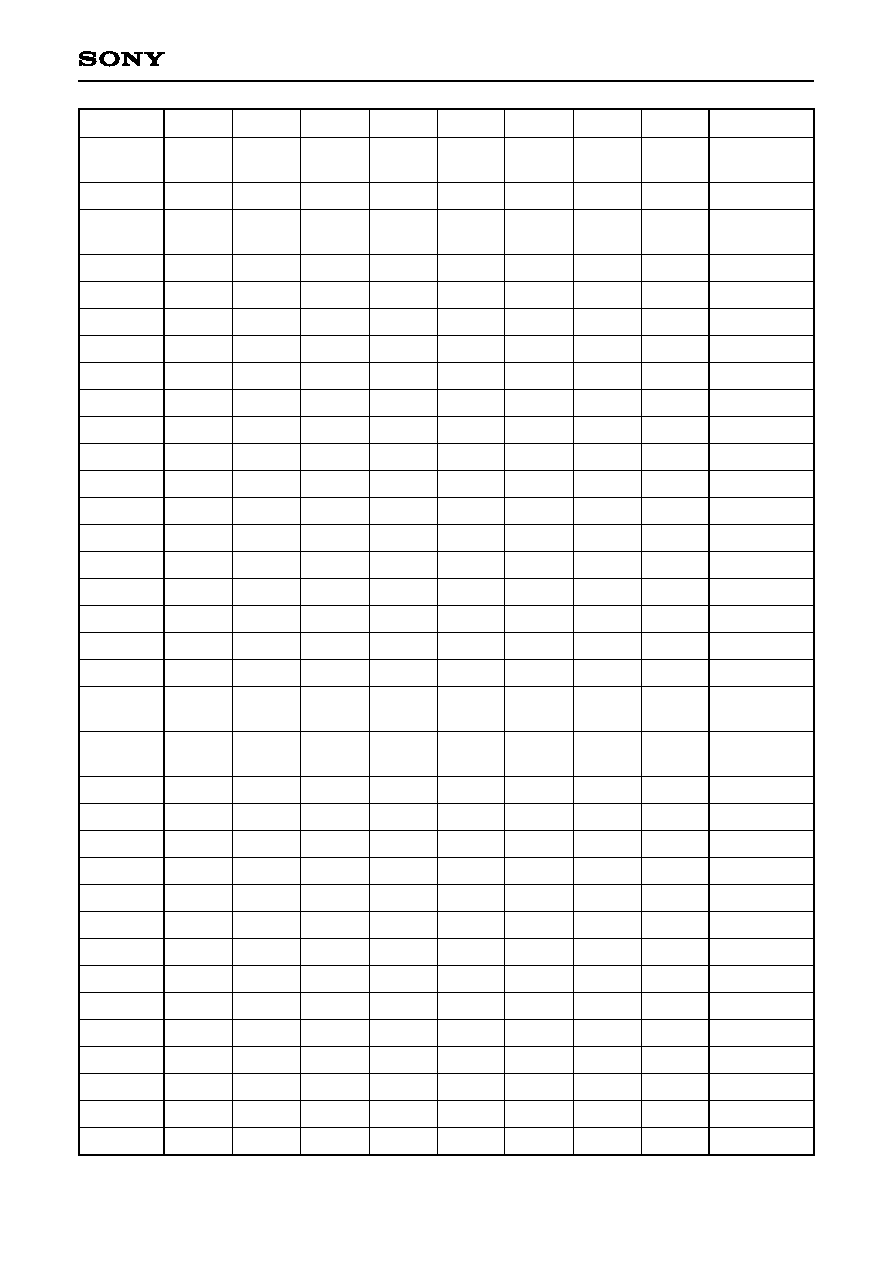

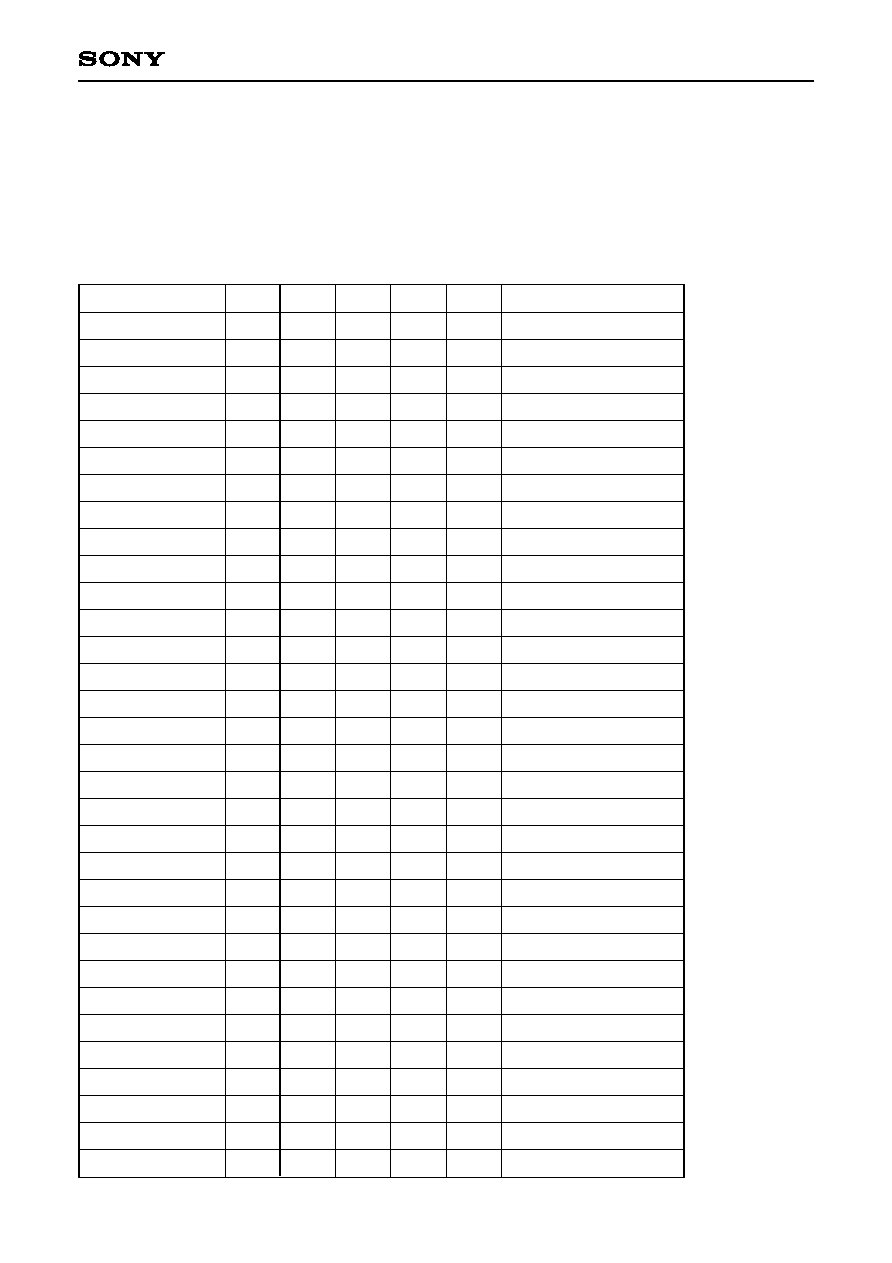

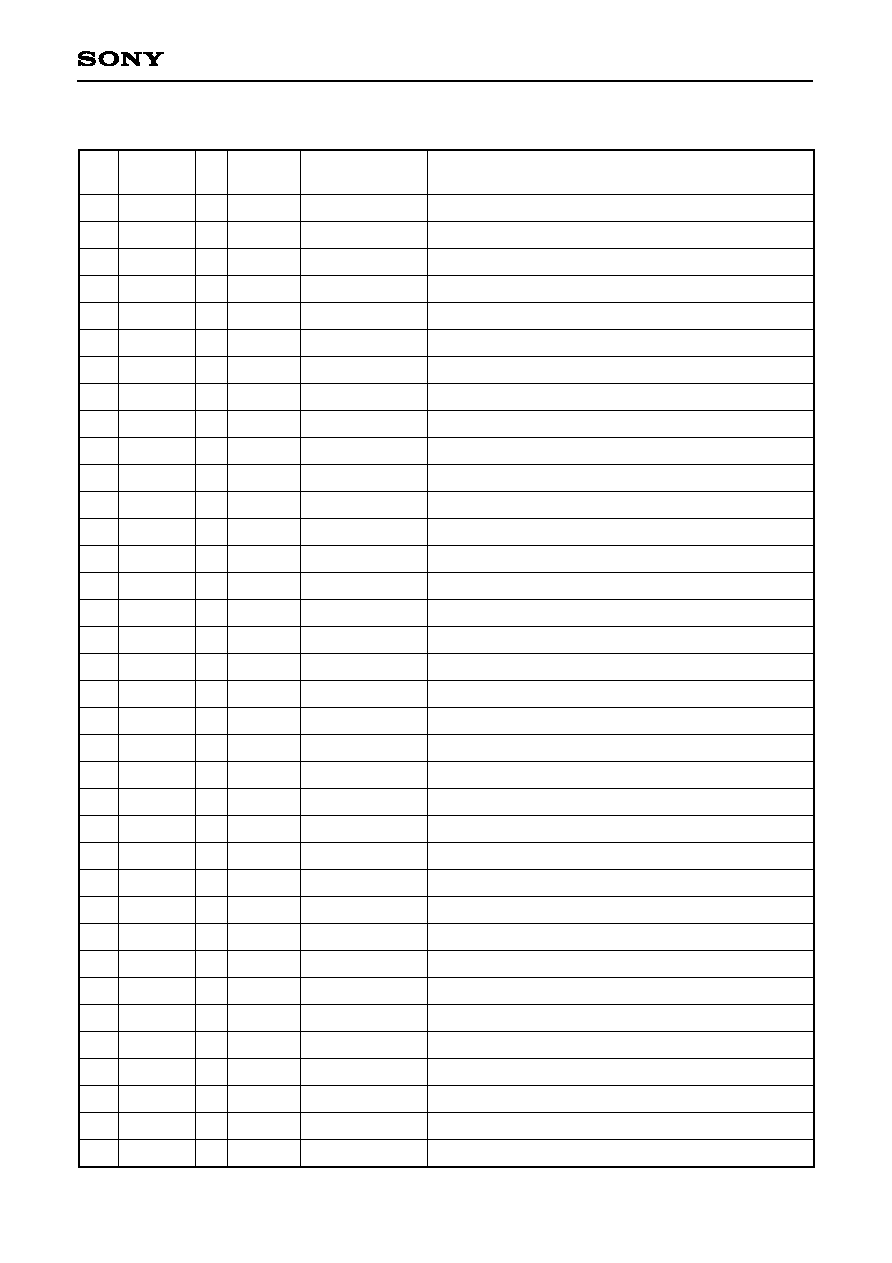

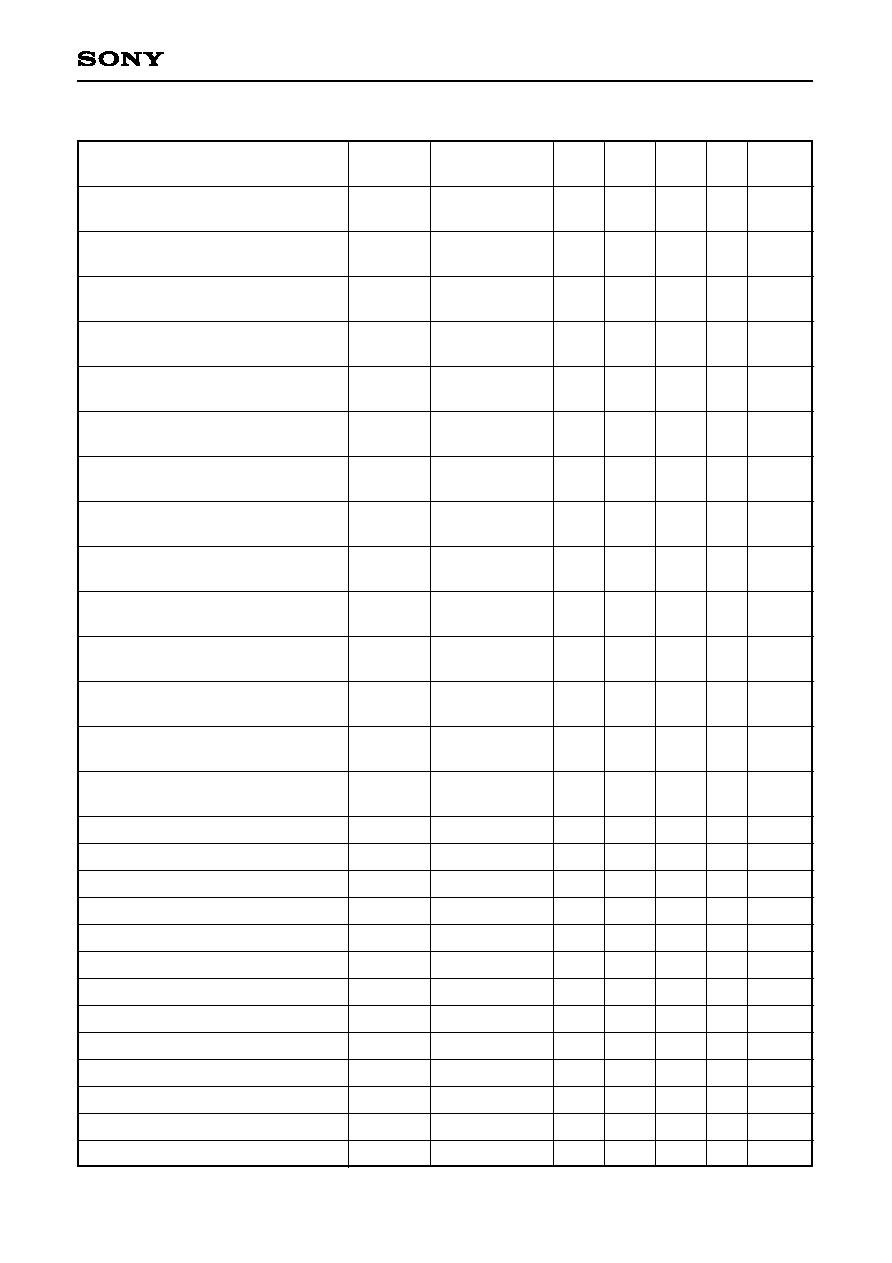

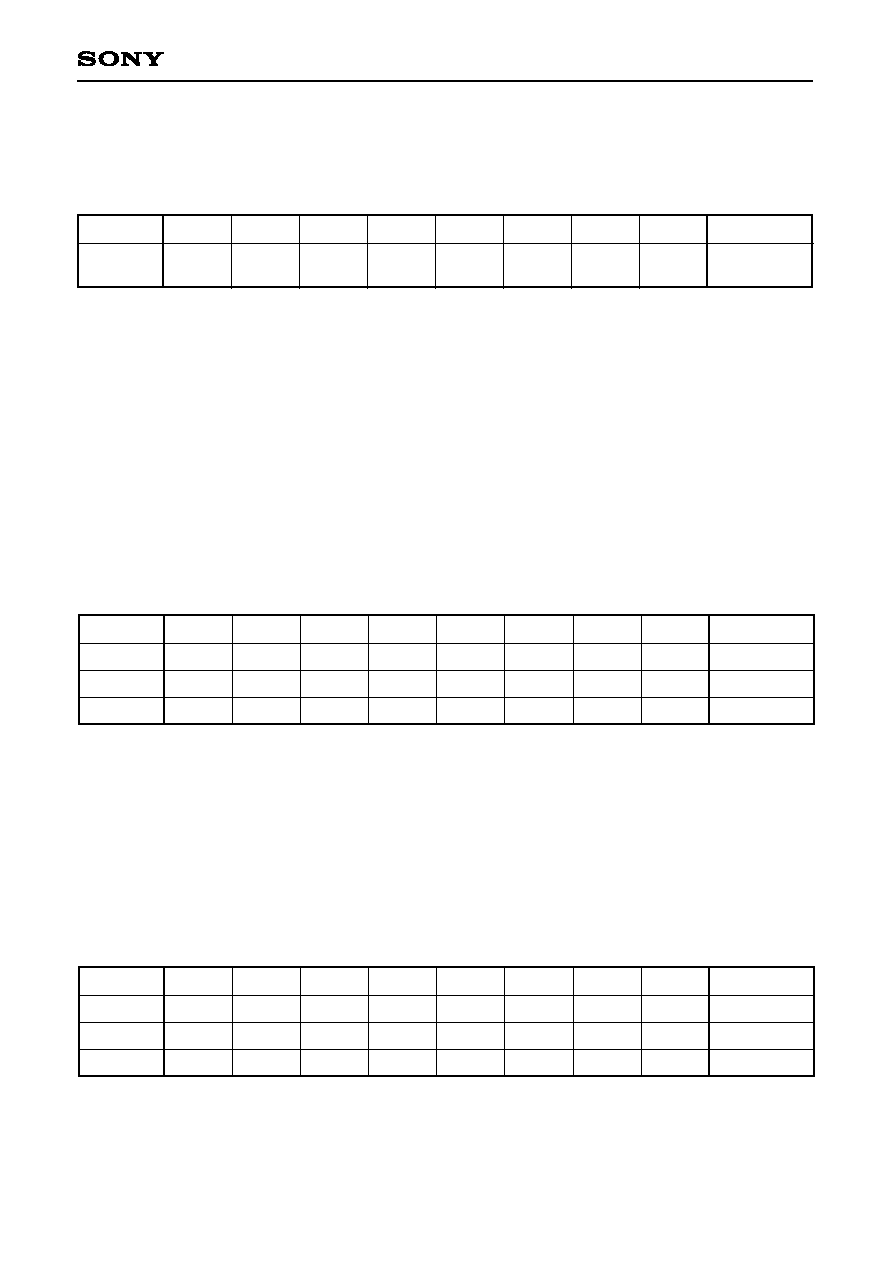

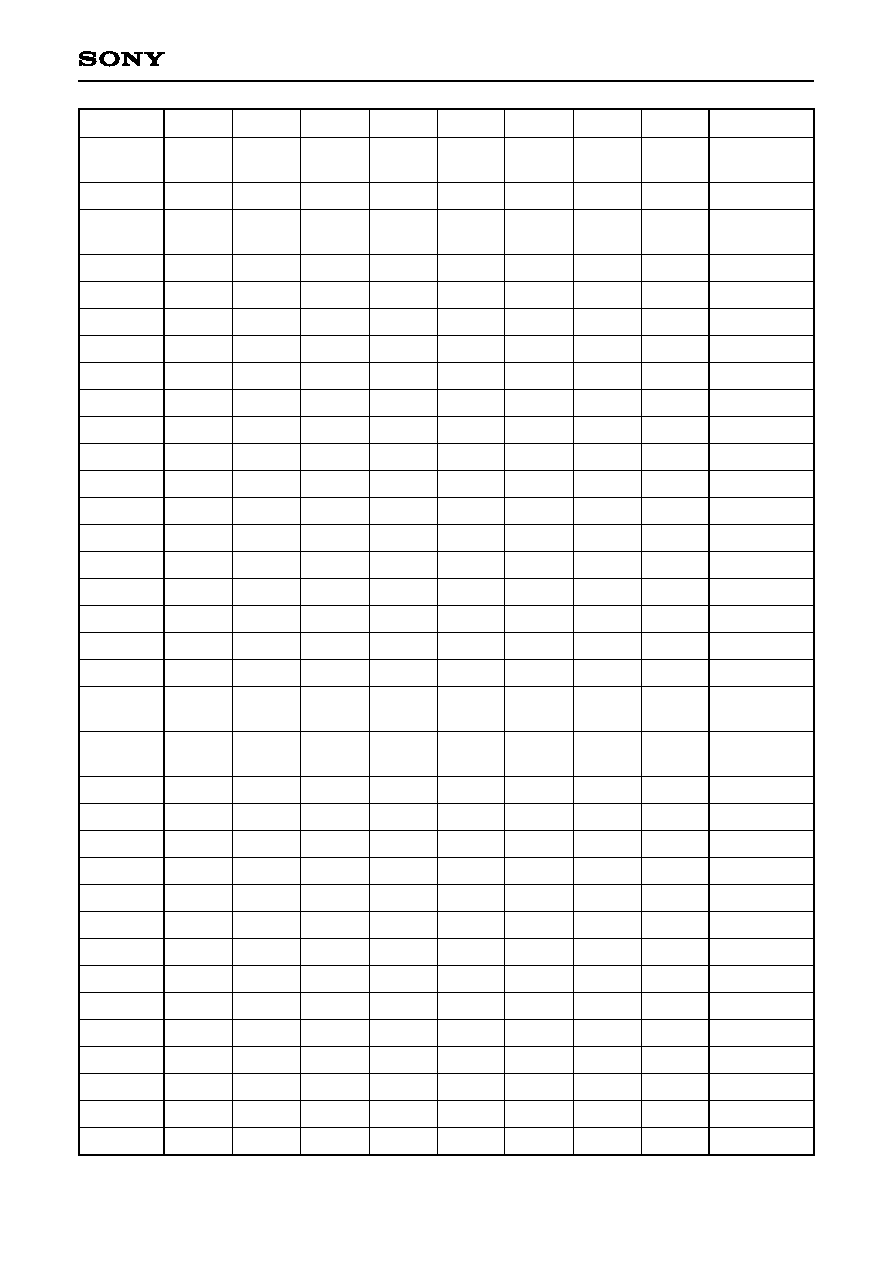

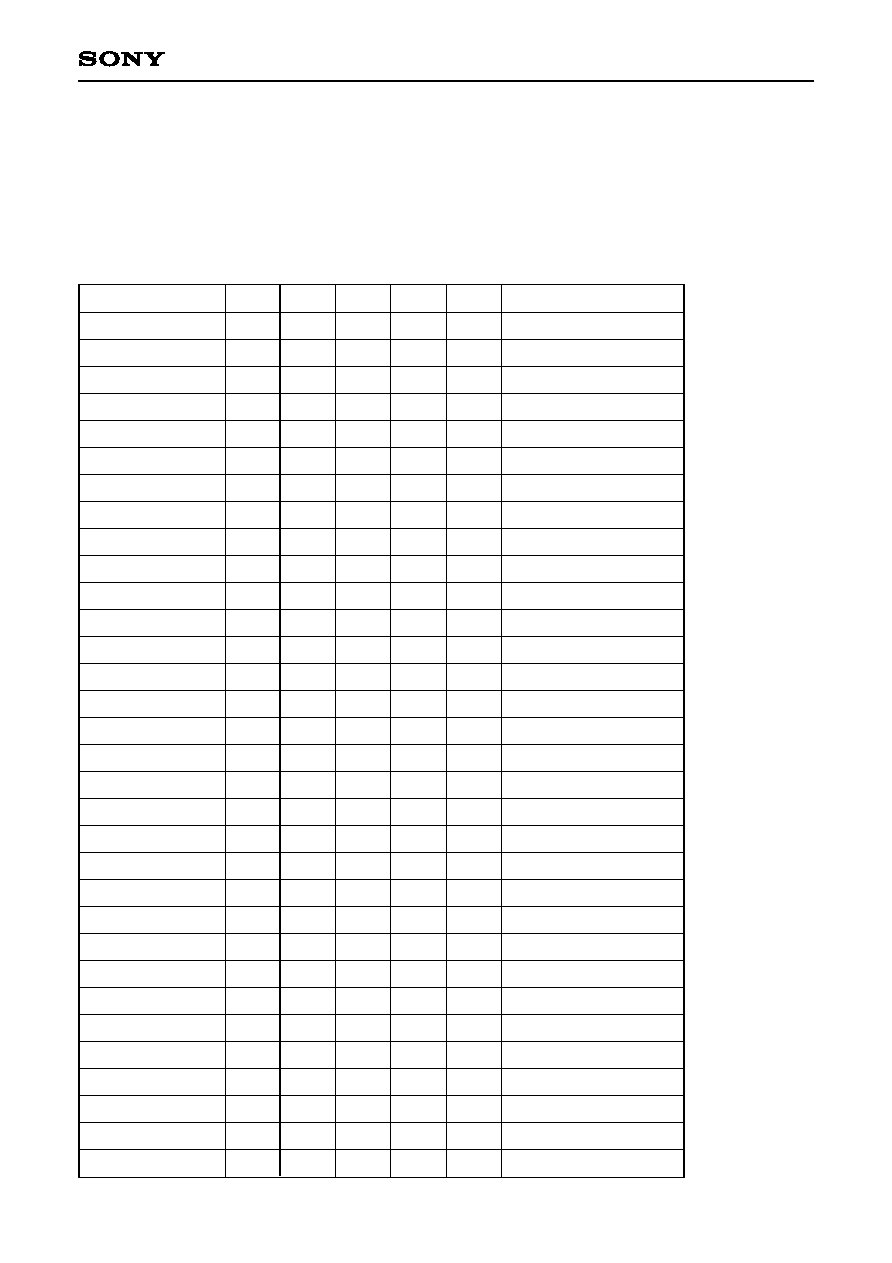

Pin Description

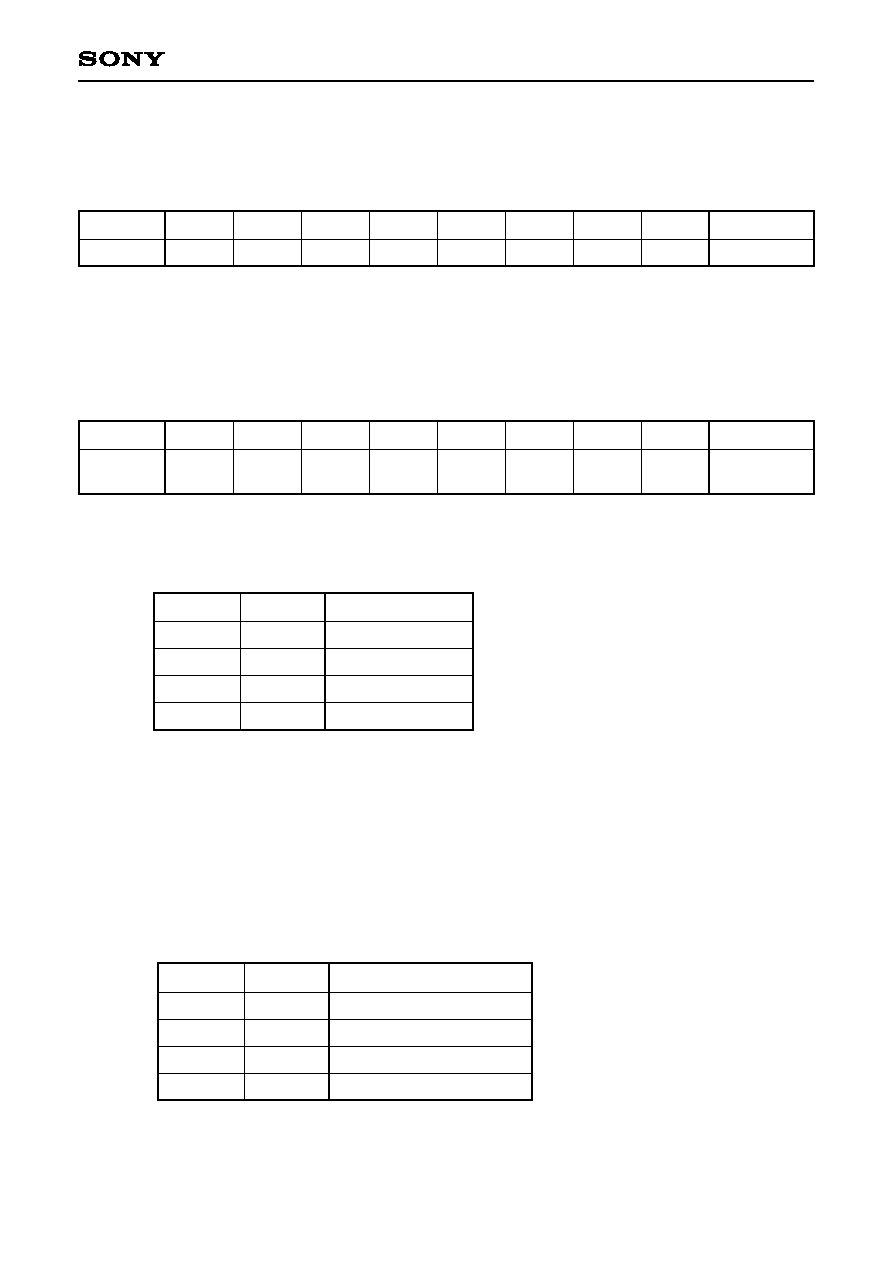

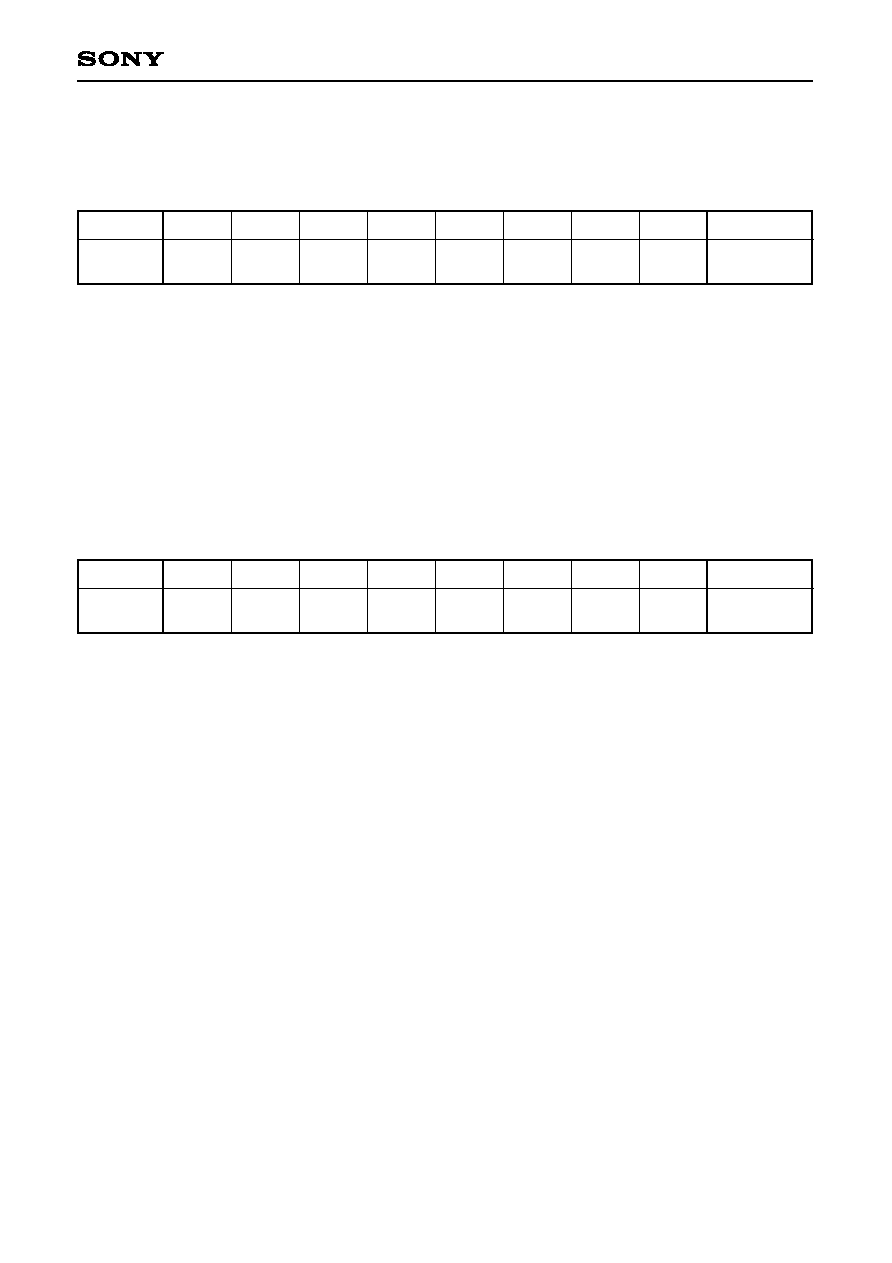

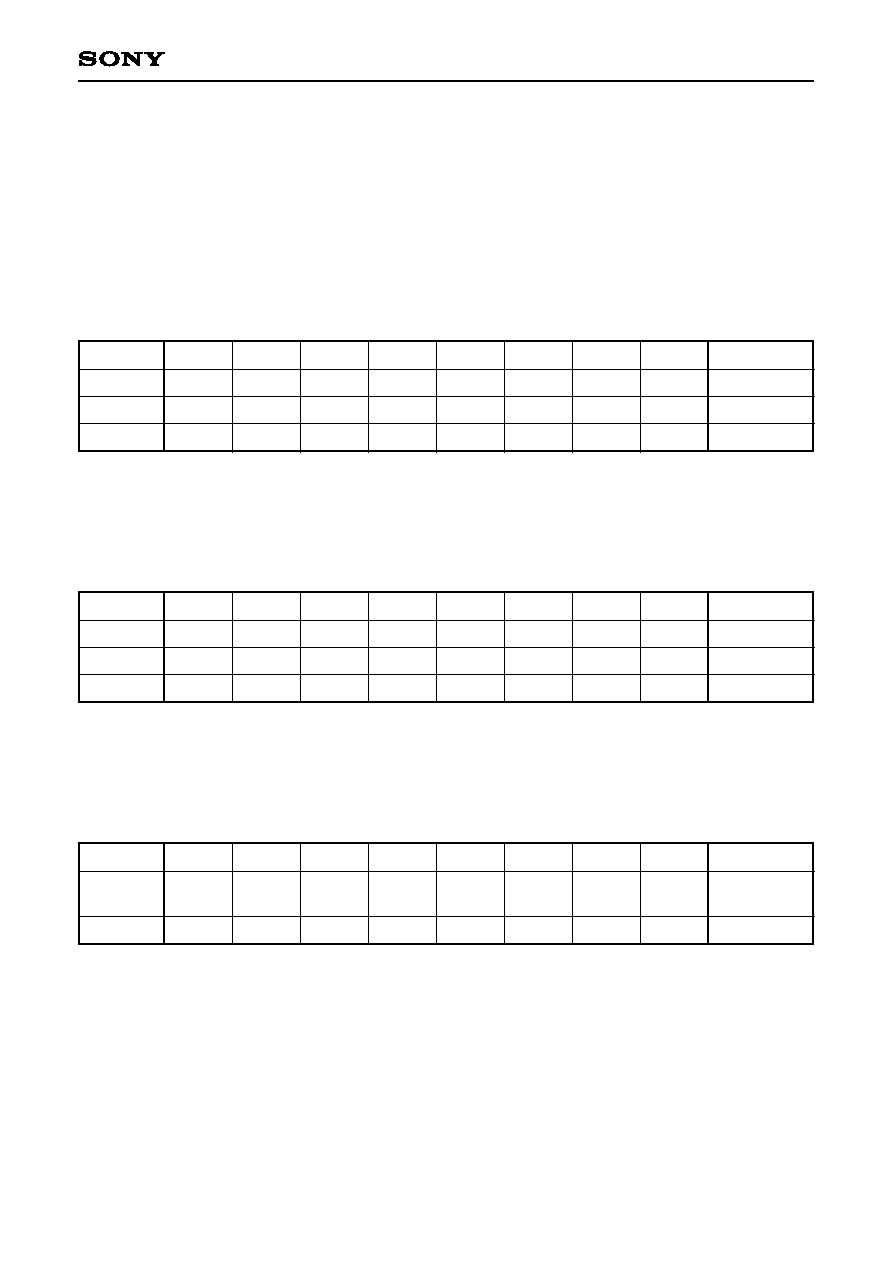

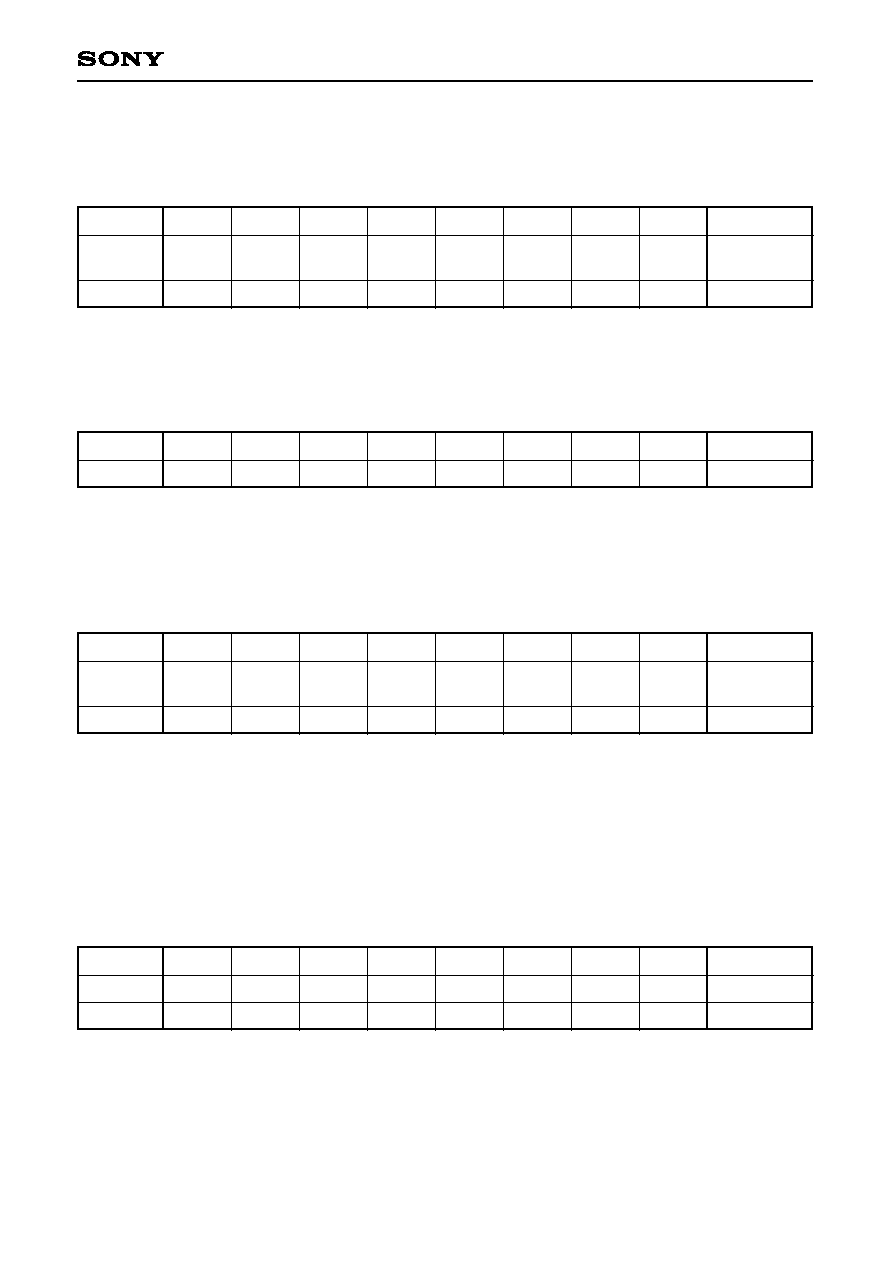

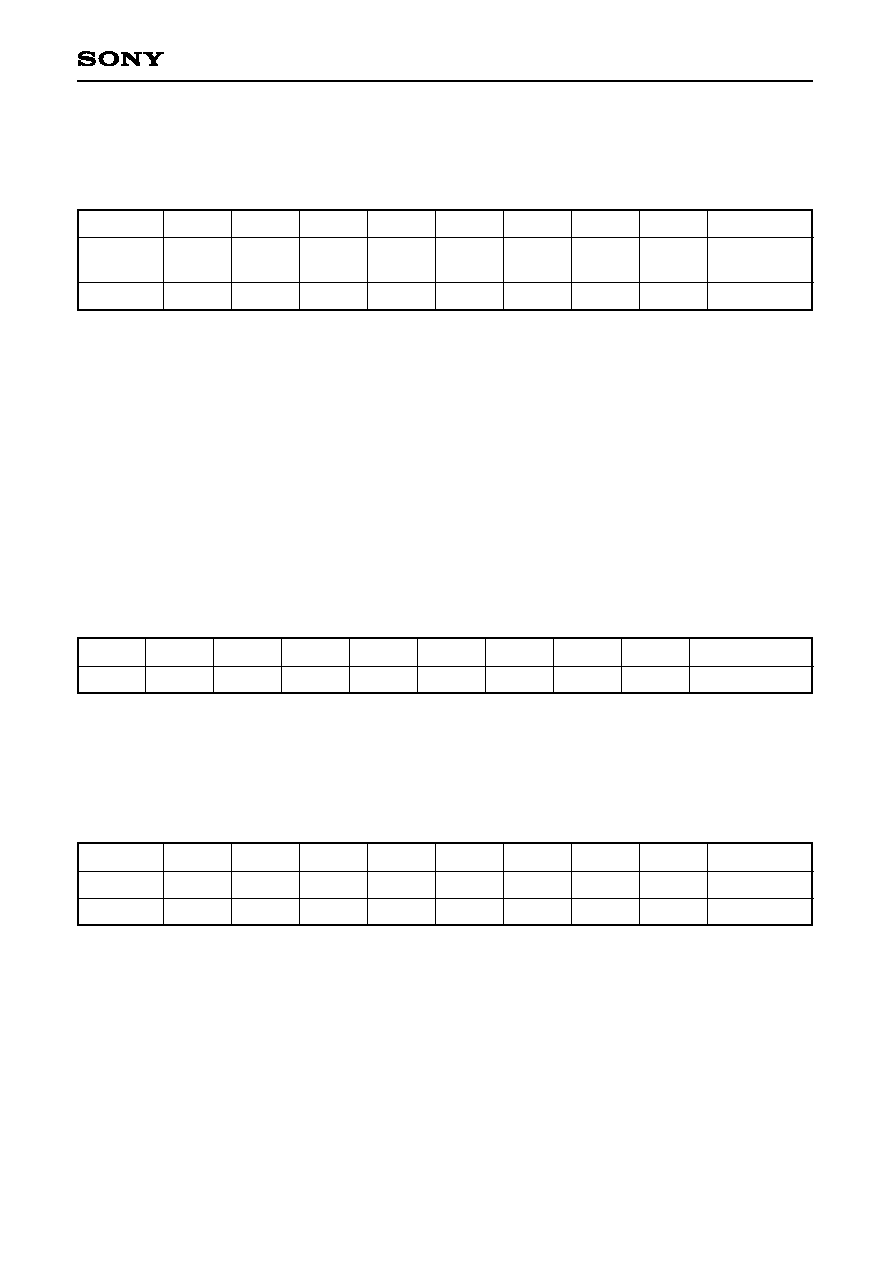

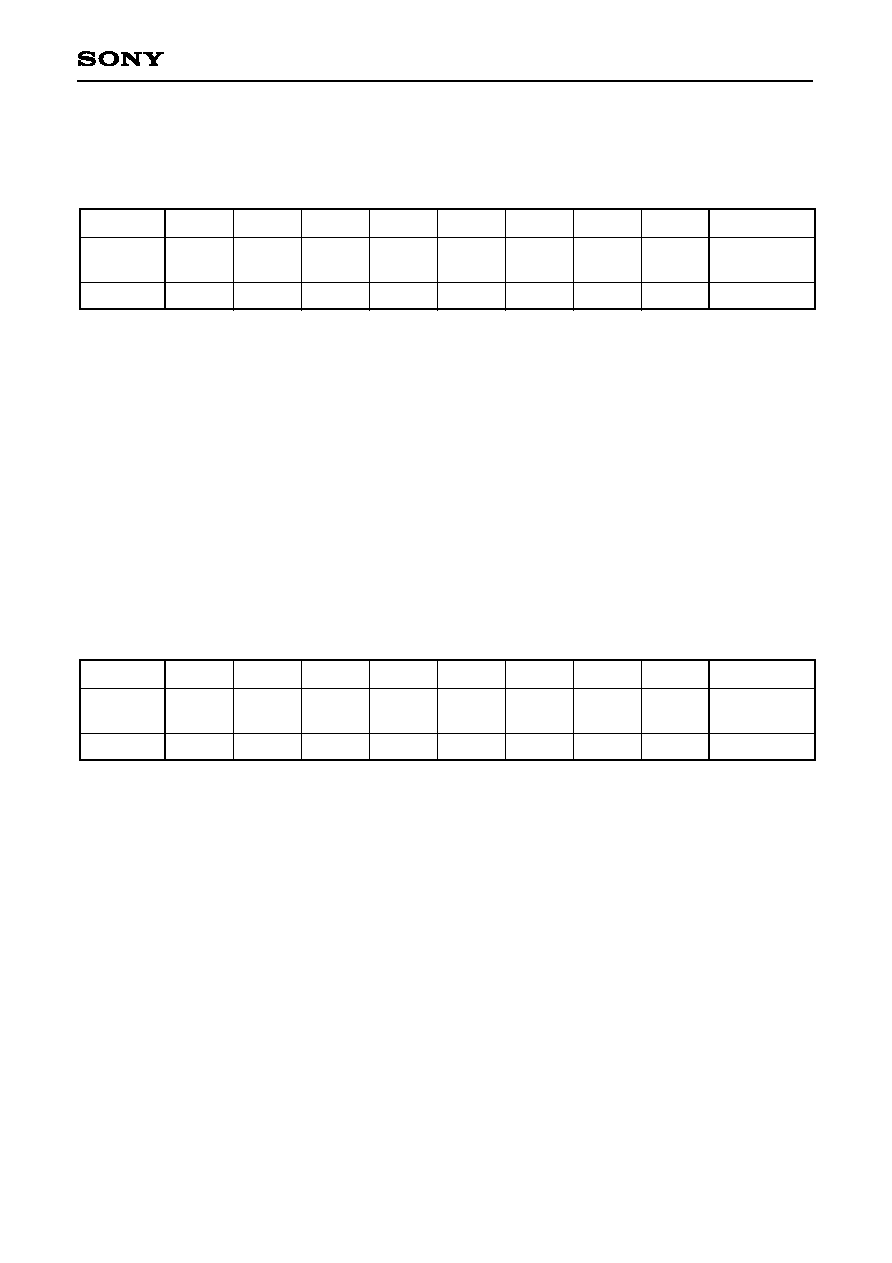

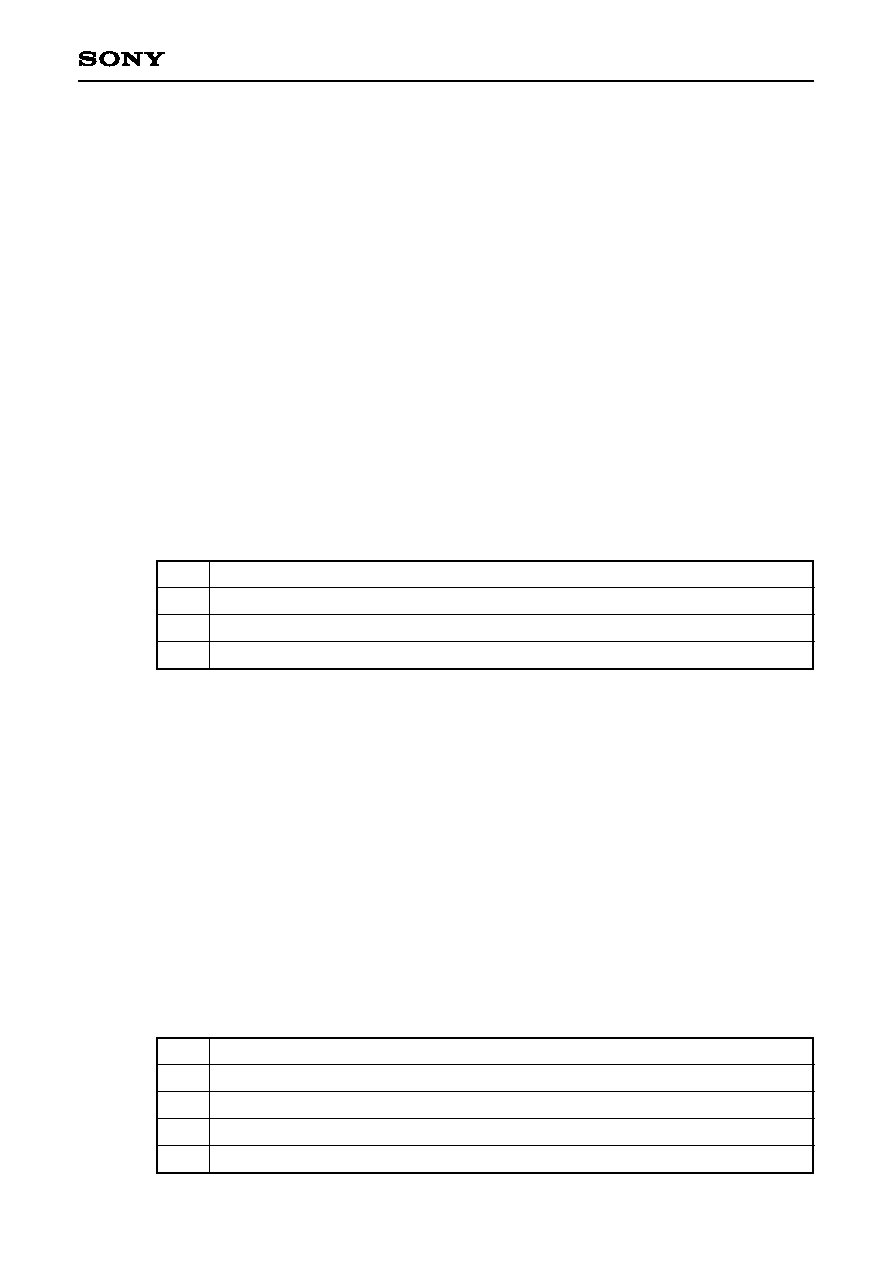

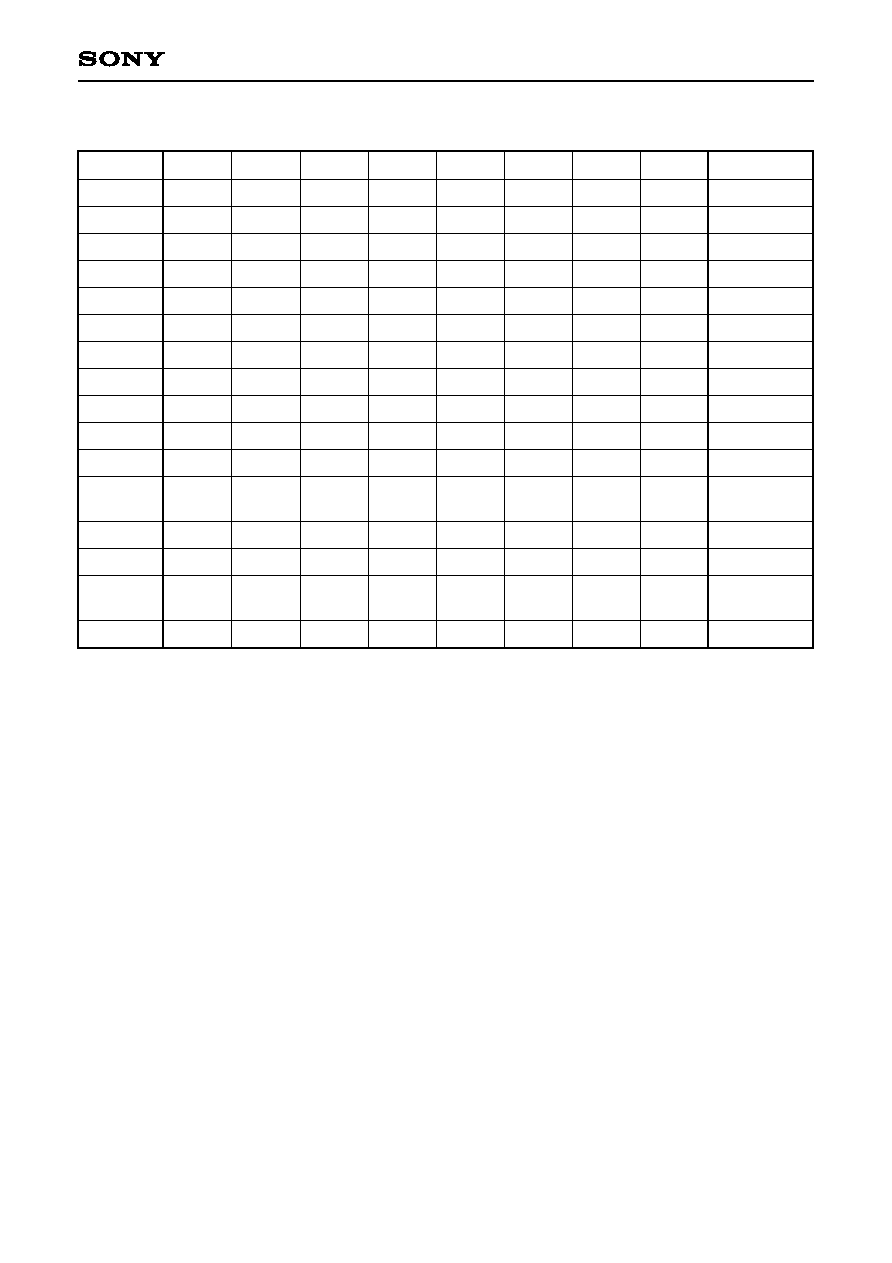

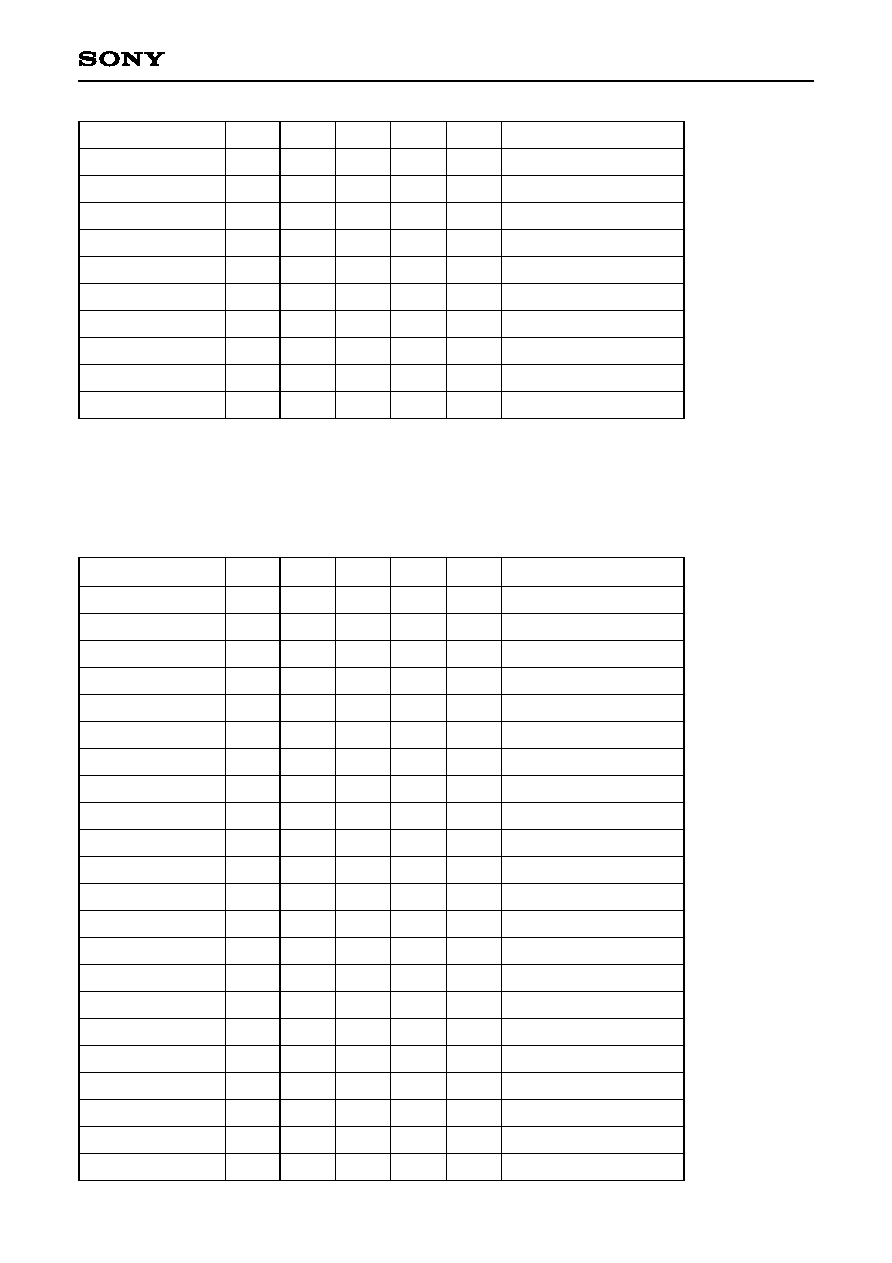

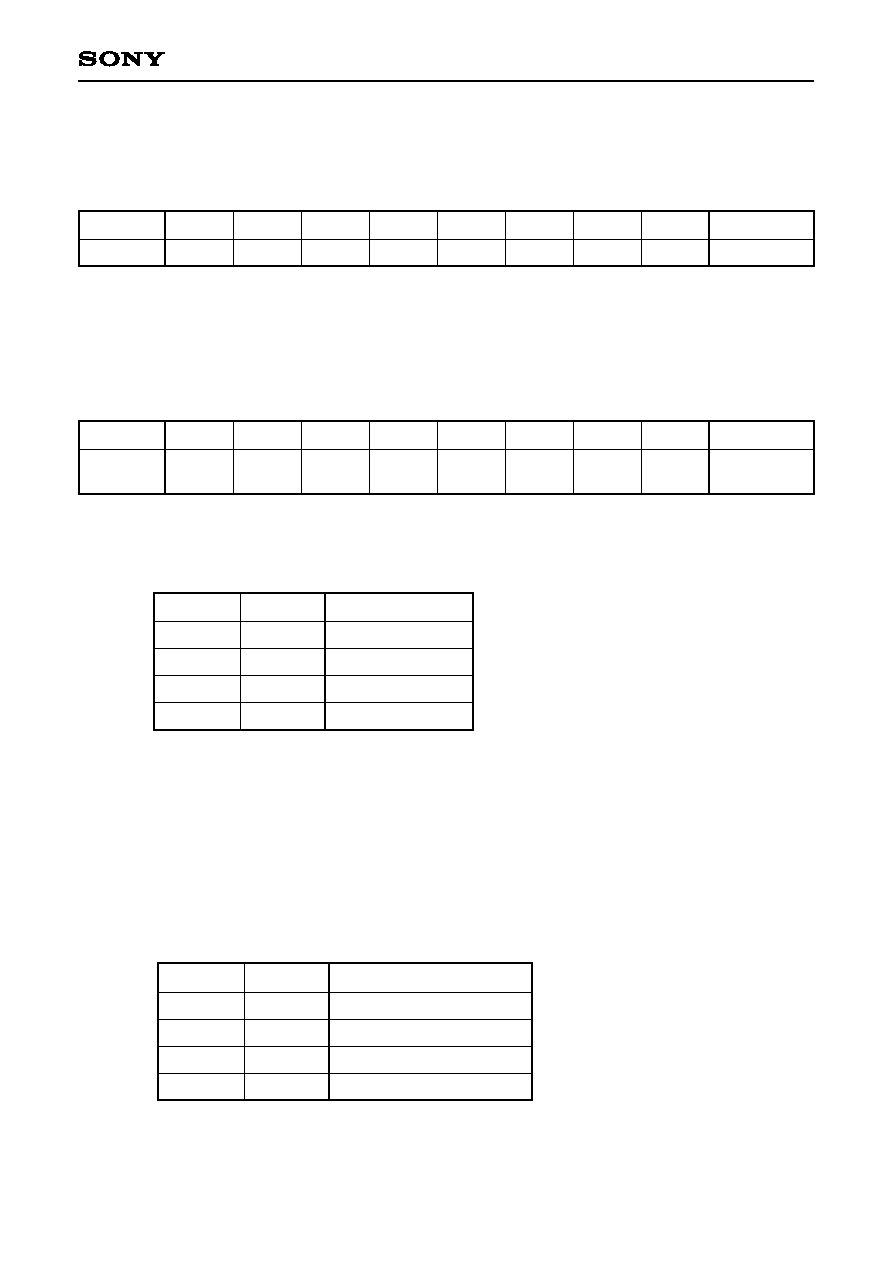

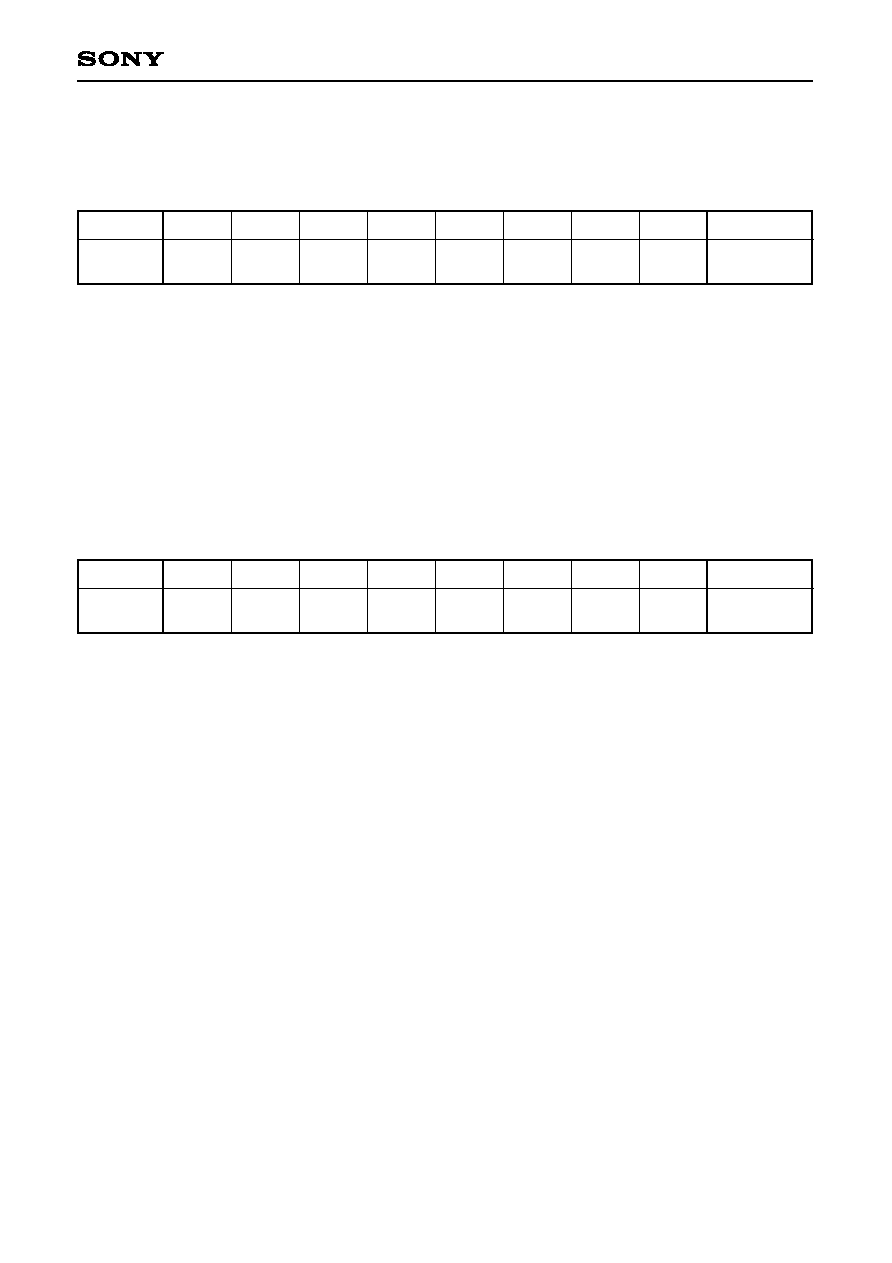

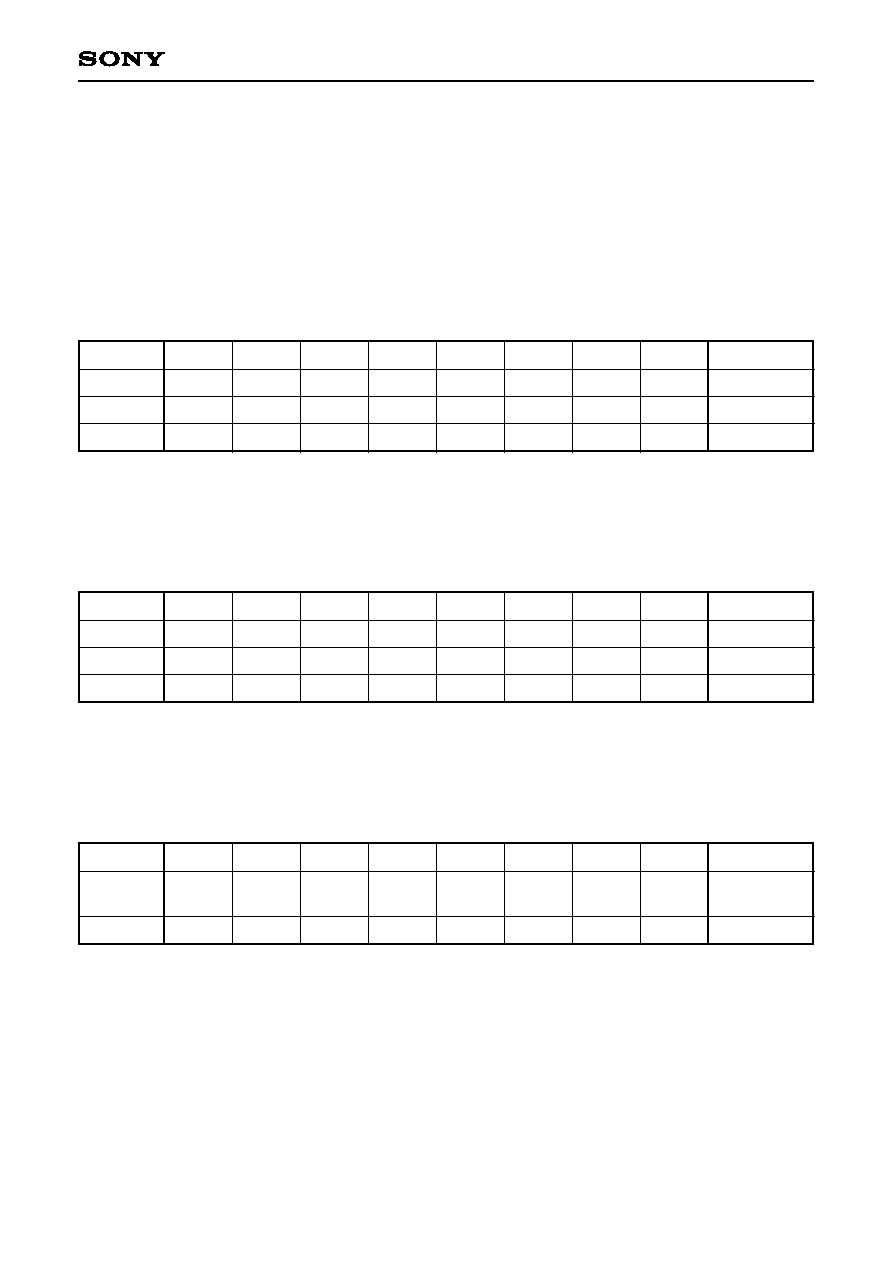

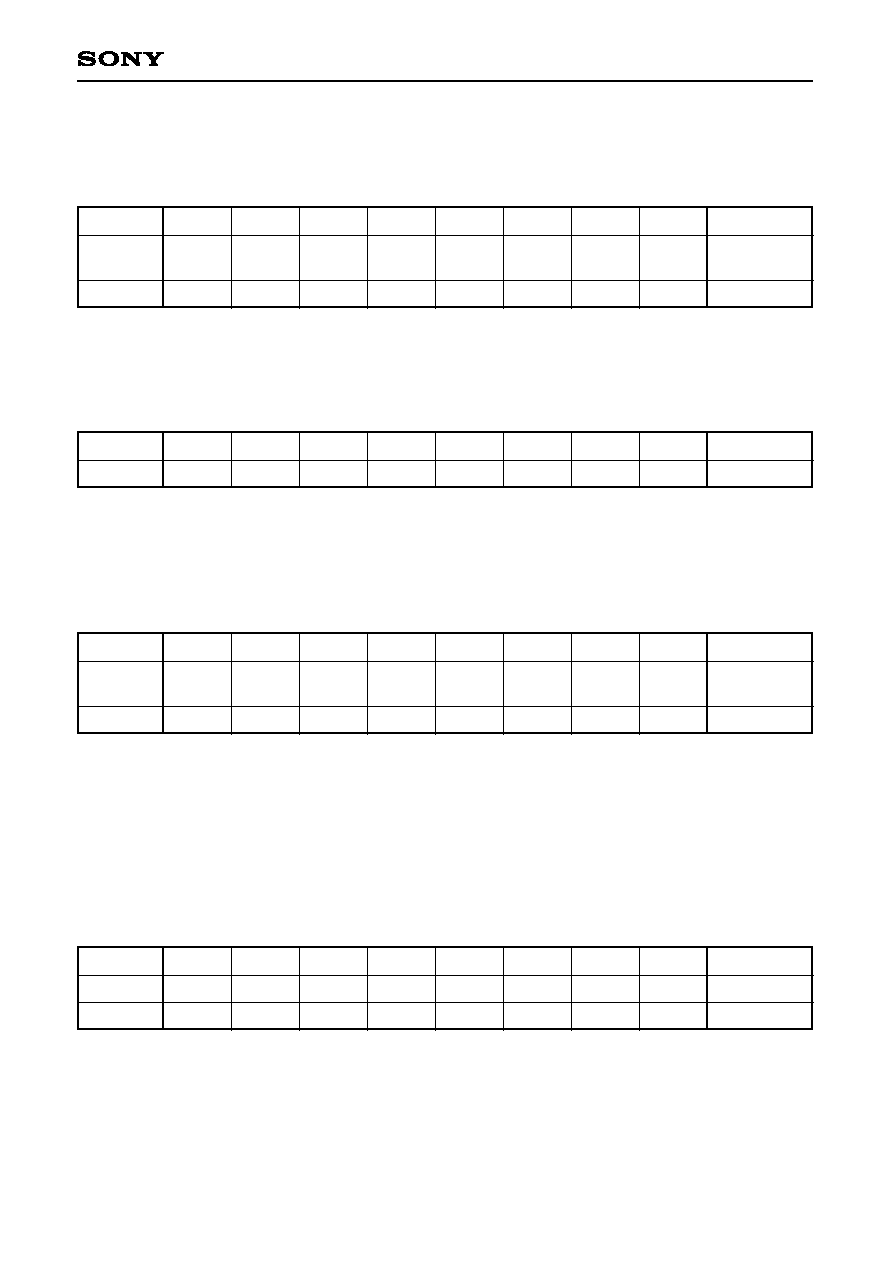

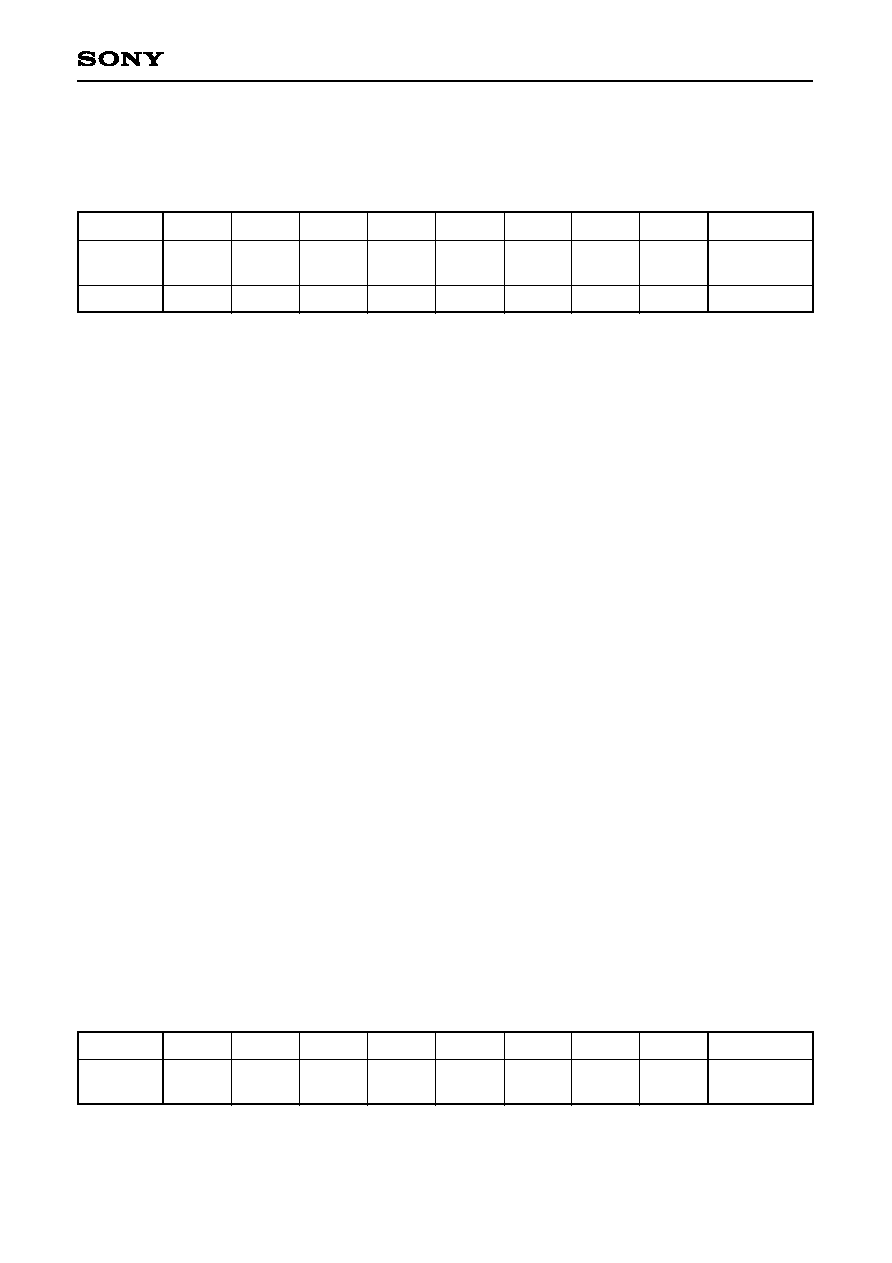

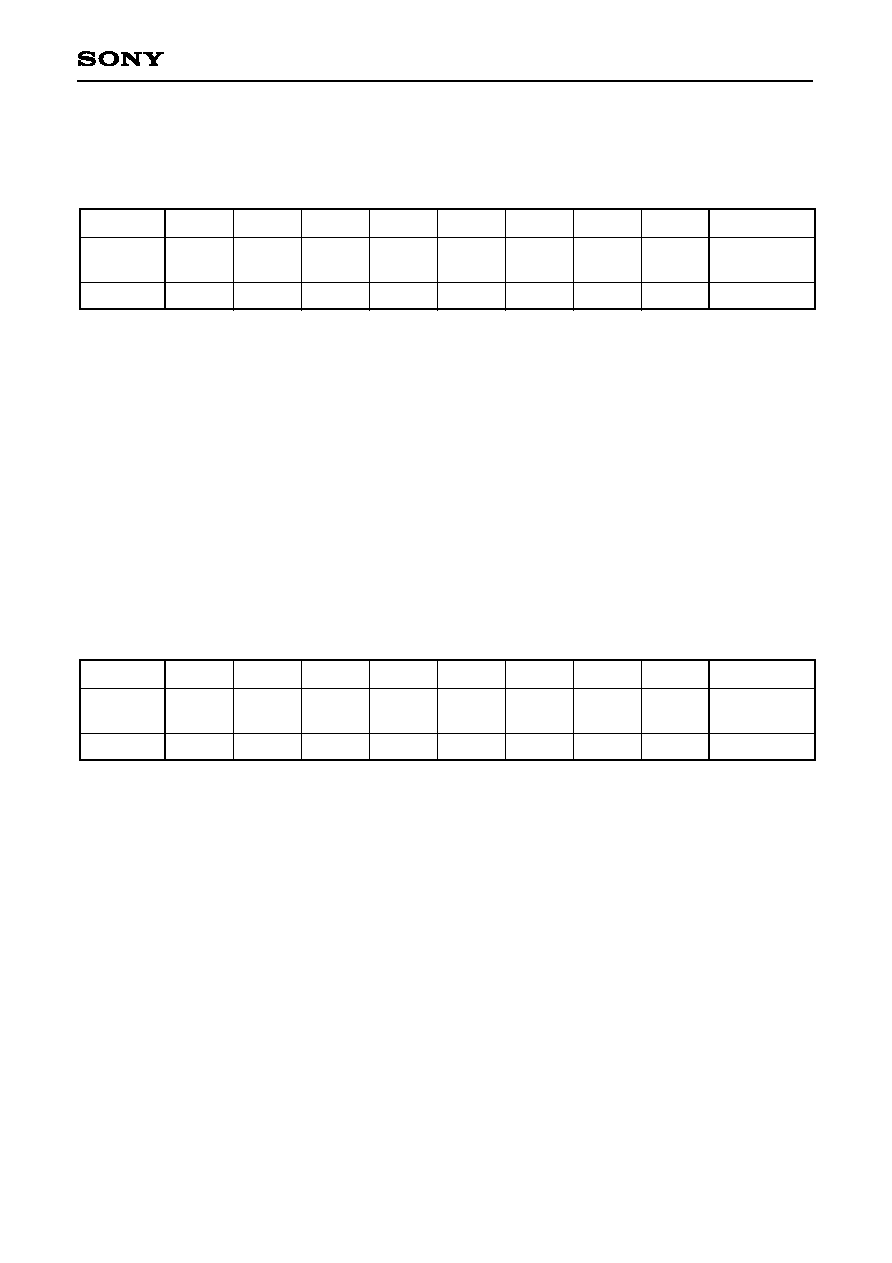

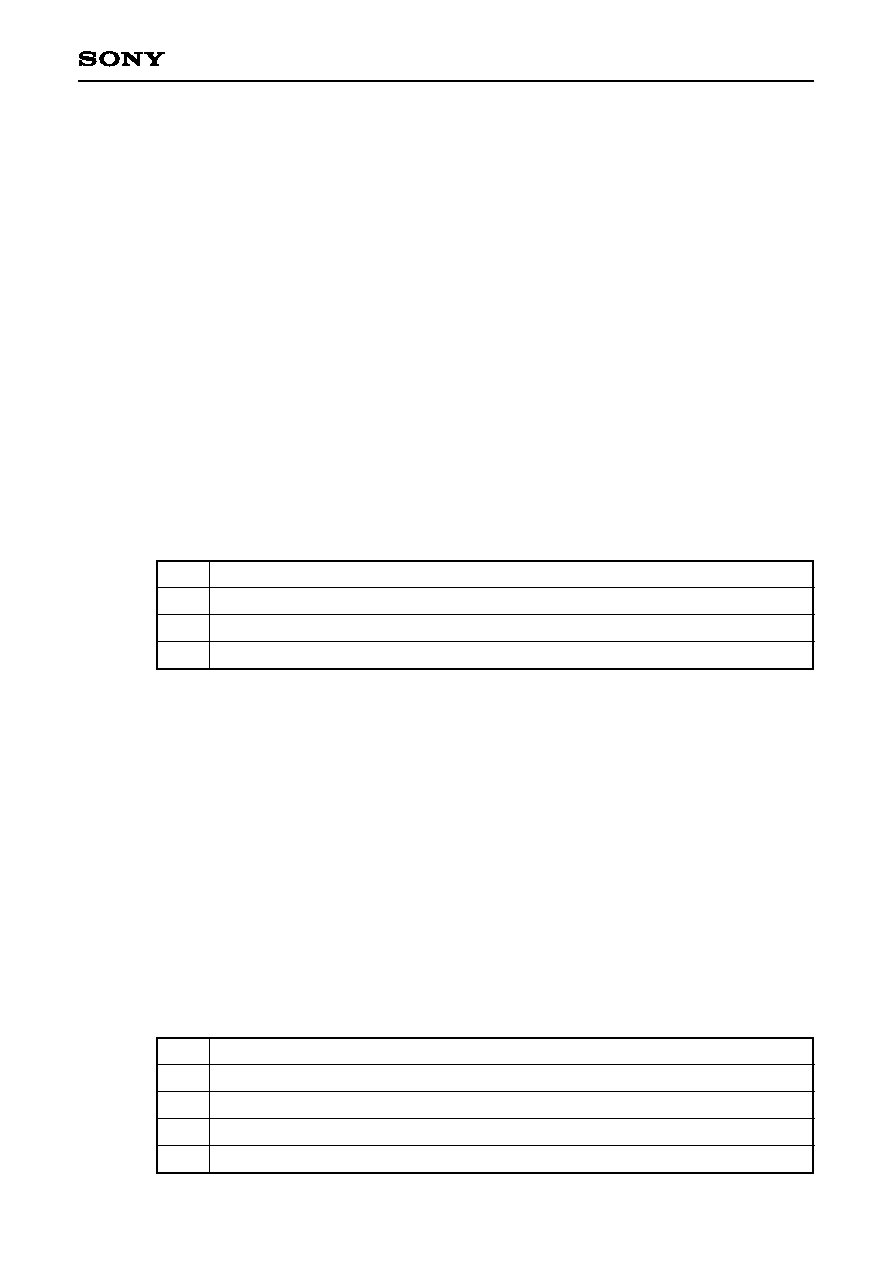

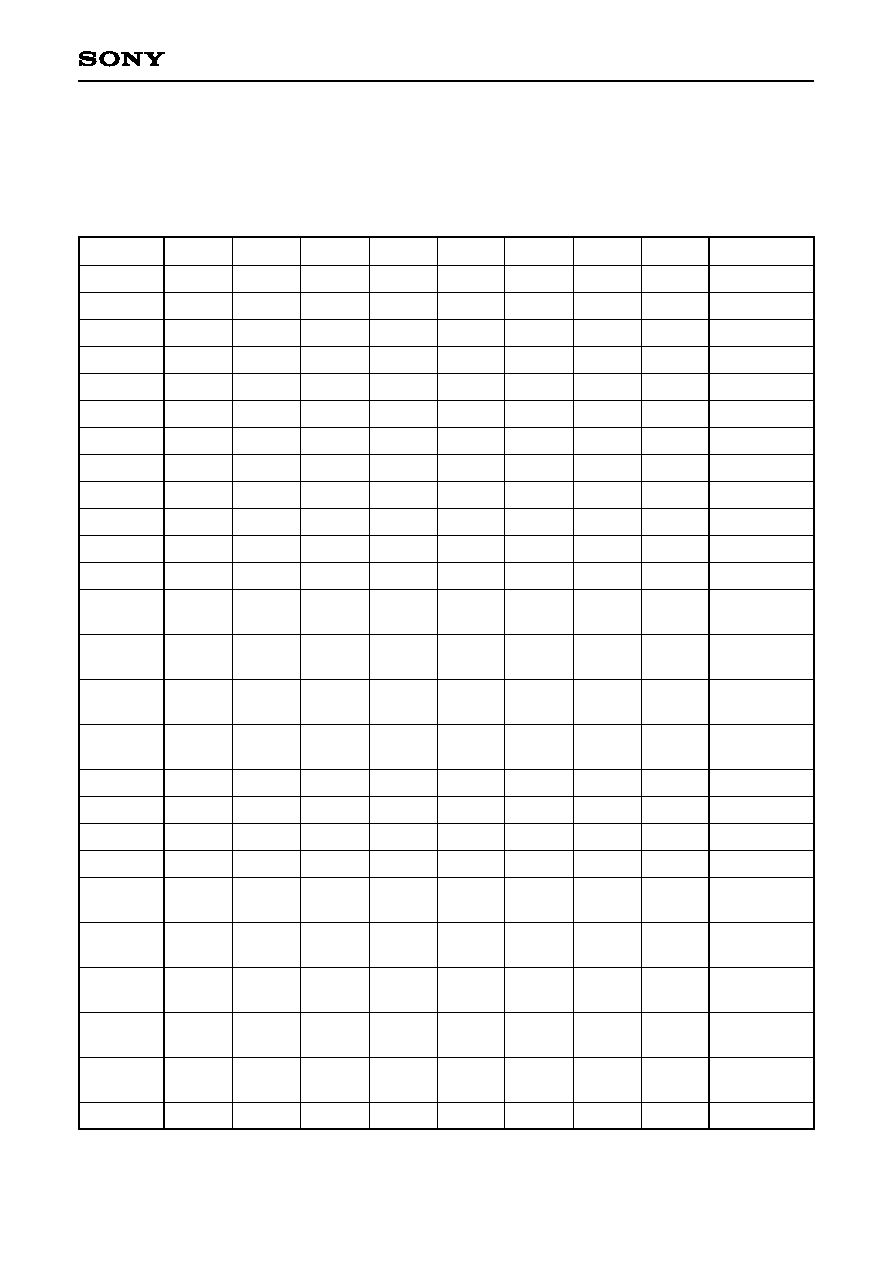

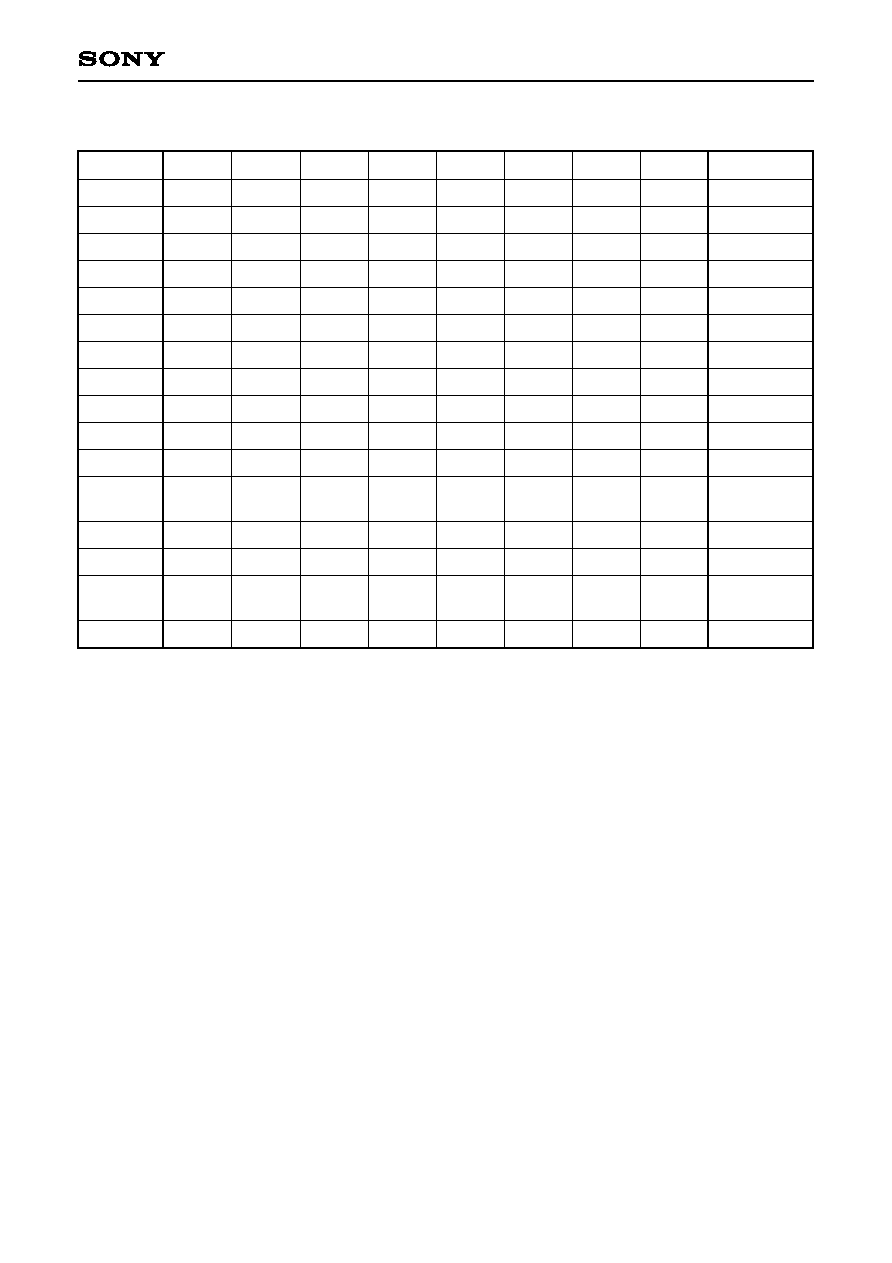

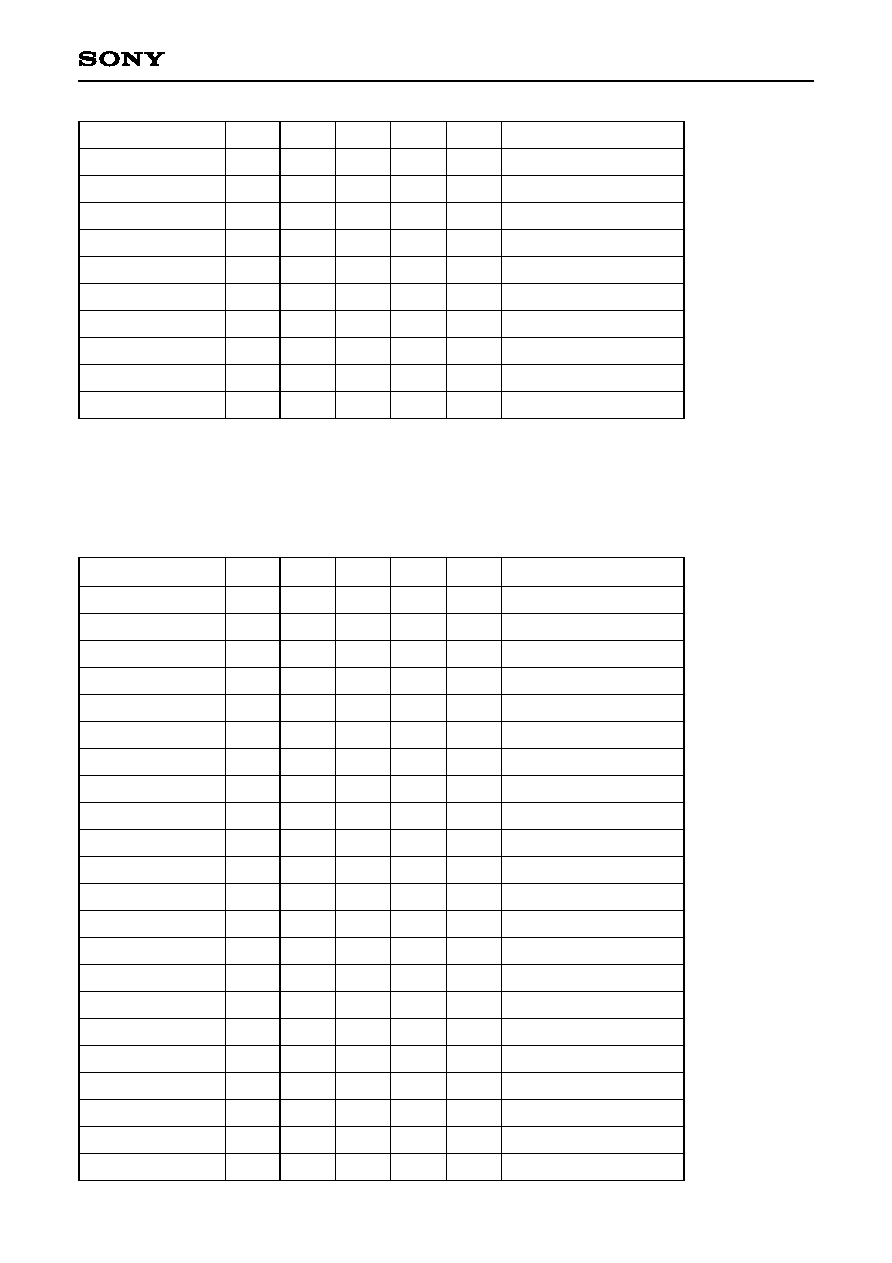

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

--

--

I/O

--

I/O

--

--

I/O

--

I/O

I/O

--

--

--

I/O

--

I/O

--

I/O

--

--

I/O

--

I/O

--

I/O

--

--

I/O

I/O

--

--

--

--

I/O

I/O

--

--

Negative

--

Negative

--

--

Negative

--

Negative

Negative

--

--

--

Negative

--

Negative

--

Negative

--

--

Negative

--

Negative

--

Negative

--

--

Negative

Negative

--

--

--

--

Negative

Negative

Power

Power

SCSI I/F

Power

SCSI I/F

Power

Power

SCSI I/F

Power

SCSI I/F

SCSI I/F

Power

Power

Power

SCSI I/F

Power

SCSI I/F

Power

SCSI I/F

Power

Power

SCSI I/F

Power

SCSI I/F

Power

SCSI I/F

Power

Power

SCSI I/F

SCSI I/F

Power

Power

Power

Power

SCSI I/F

SCSI I/F

V

SS

V

DD

SCSI data bus bit 0

V

SS

SCSI data bus bit 1

V

SS

V

DD

SCSI data bus bit 2

V

SS

SCSI data bus bit 3

SCSI data bus bit 4

V

SS

V

SS

V

DD

SCSI data bus bit 5

V

SS

SCSI data bus bit 6

V

SS

SCSI data bus bit 7

V

SS

V

DD

SCSI data bus parity

V

SS

SCSI control bus XATN signal

V

SS

SCSI control bus XBSY signal

V

SS

V

DD

SCSI control bus XACK signal

SCSI control bus XRST signal

V

SS

V

SS

V

DD

V

SS

SCSI control bus XMSG signal

SCSI control bus XSEL signal

V

SS

V

DD

XDB0

V

SS

XDB1

V

SS

V

DD

XDB2

V

SS

XDB3

XDB4

V

SS

V

SS

V

DD

XDB5

V

SS

XDB6

V

SS

XDB7

V

SS

V

DD

XDBP

V

SS

XATN

V

SS

XBSY

V

SS

V

DD

XACK

XRST

V

SS

V

SS

V

DD

V

SS

XMSG

XSEL

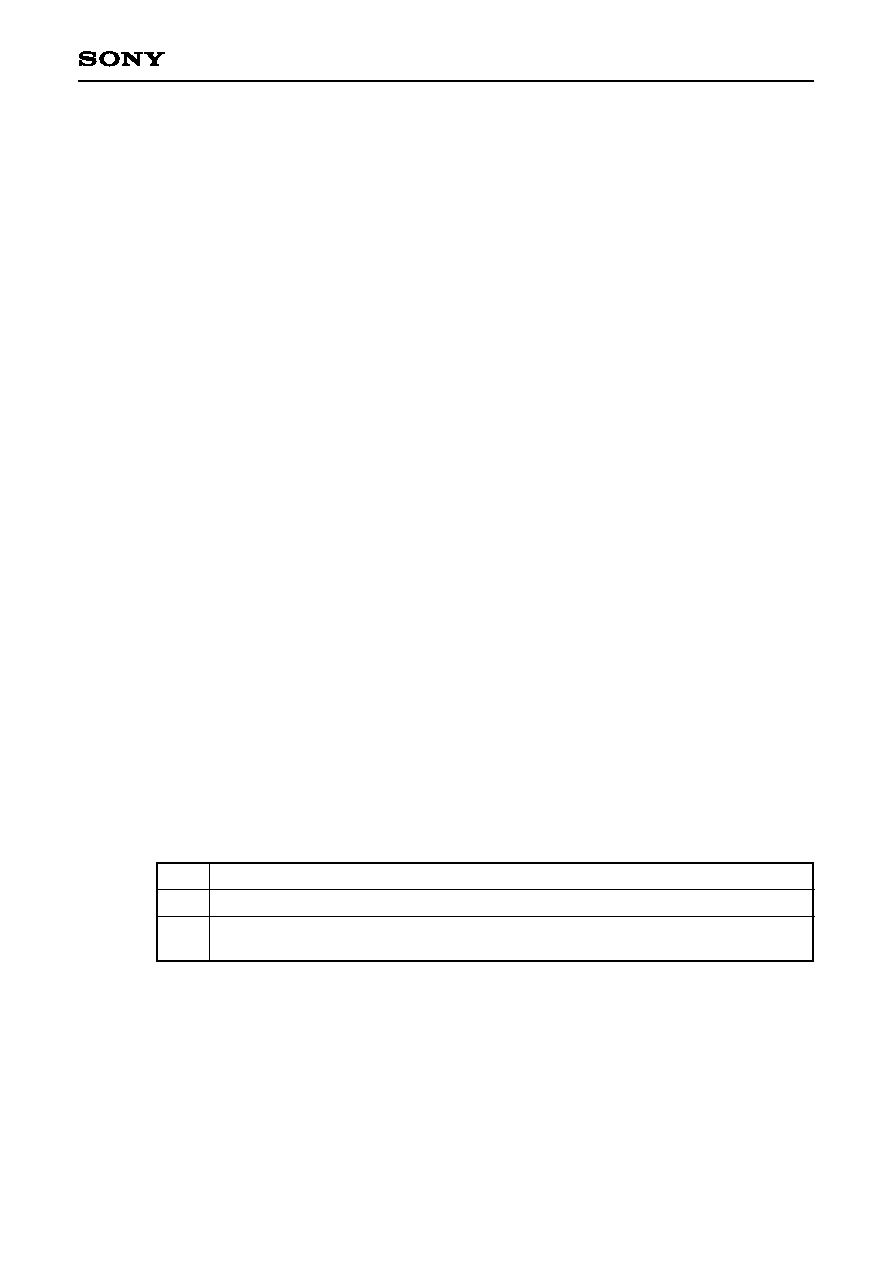

Symbol

I/O

Logic

Classification

Description

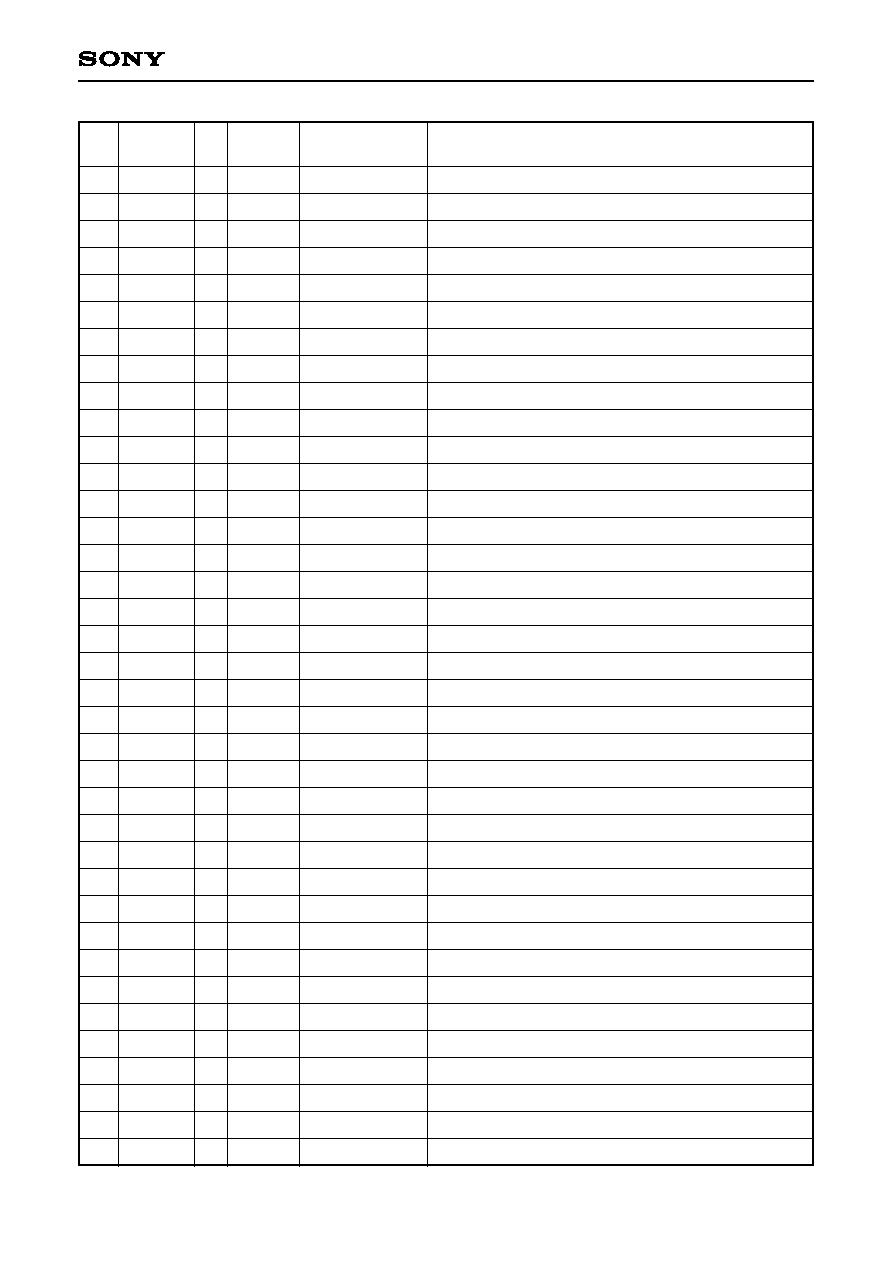

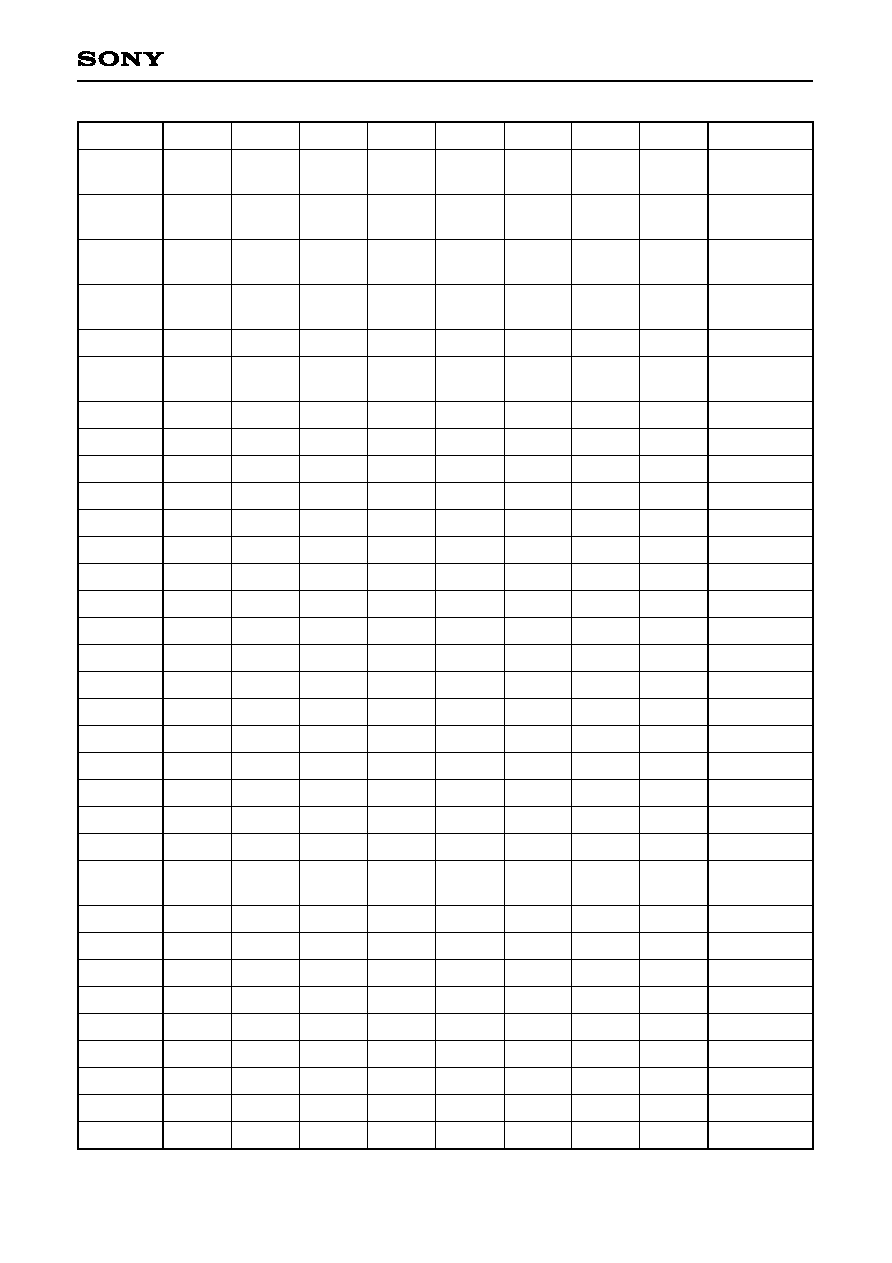

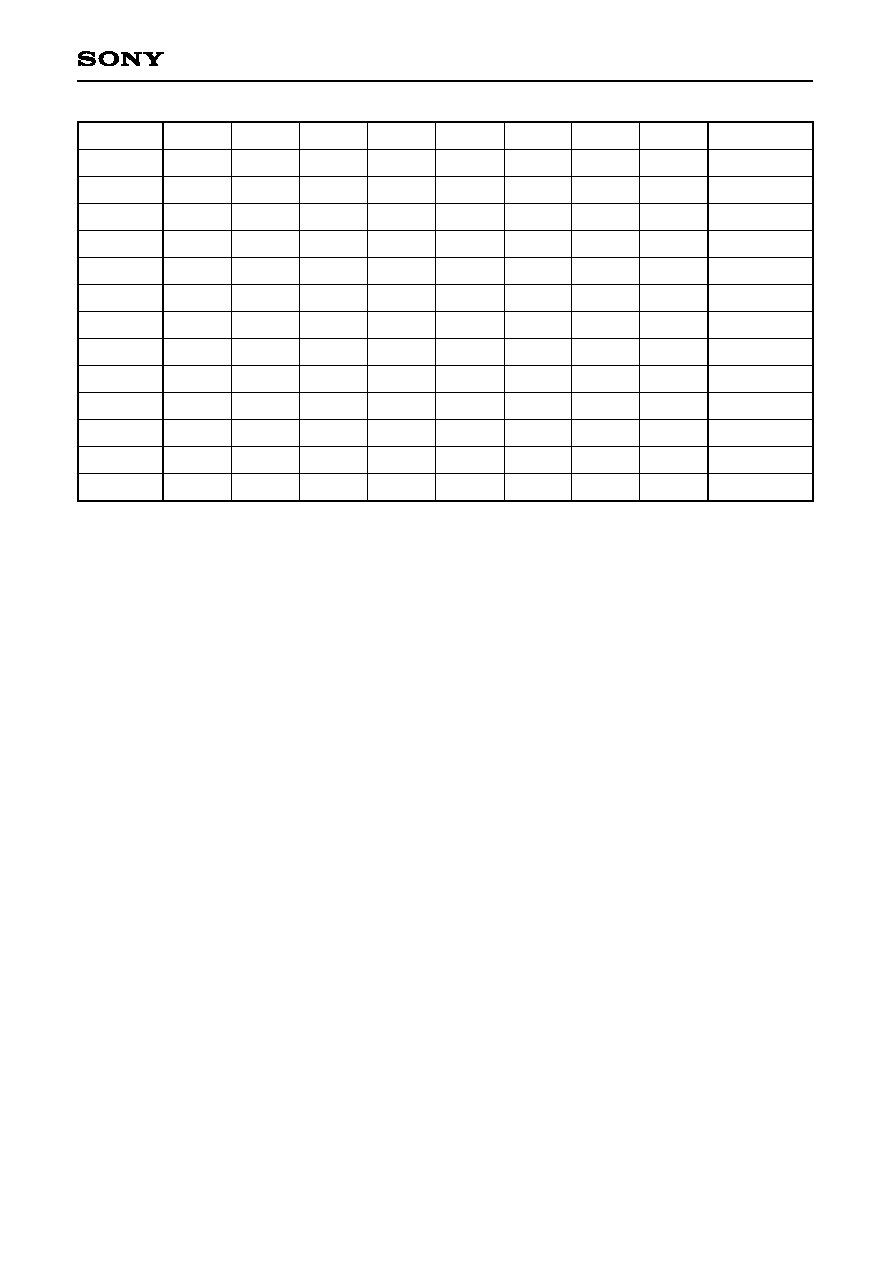

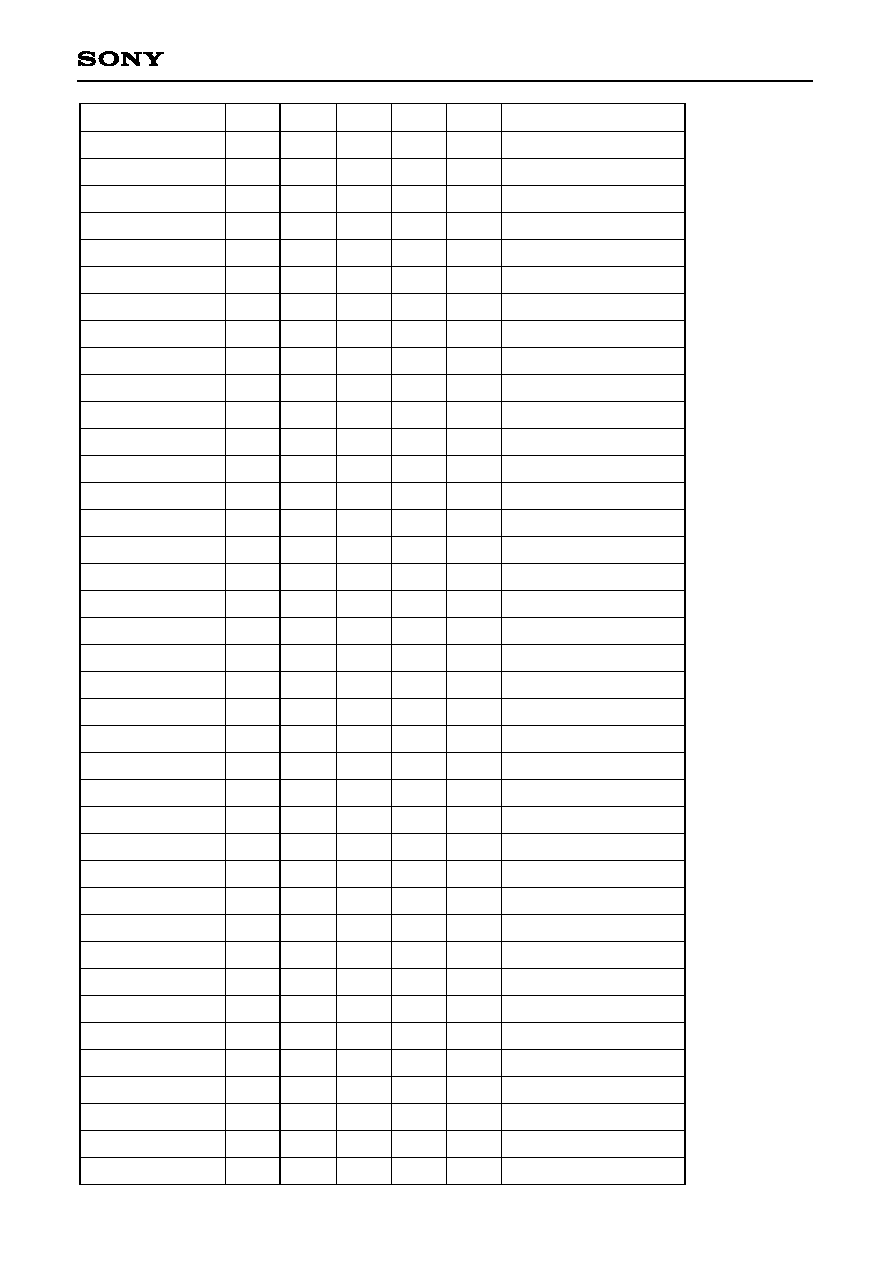

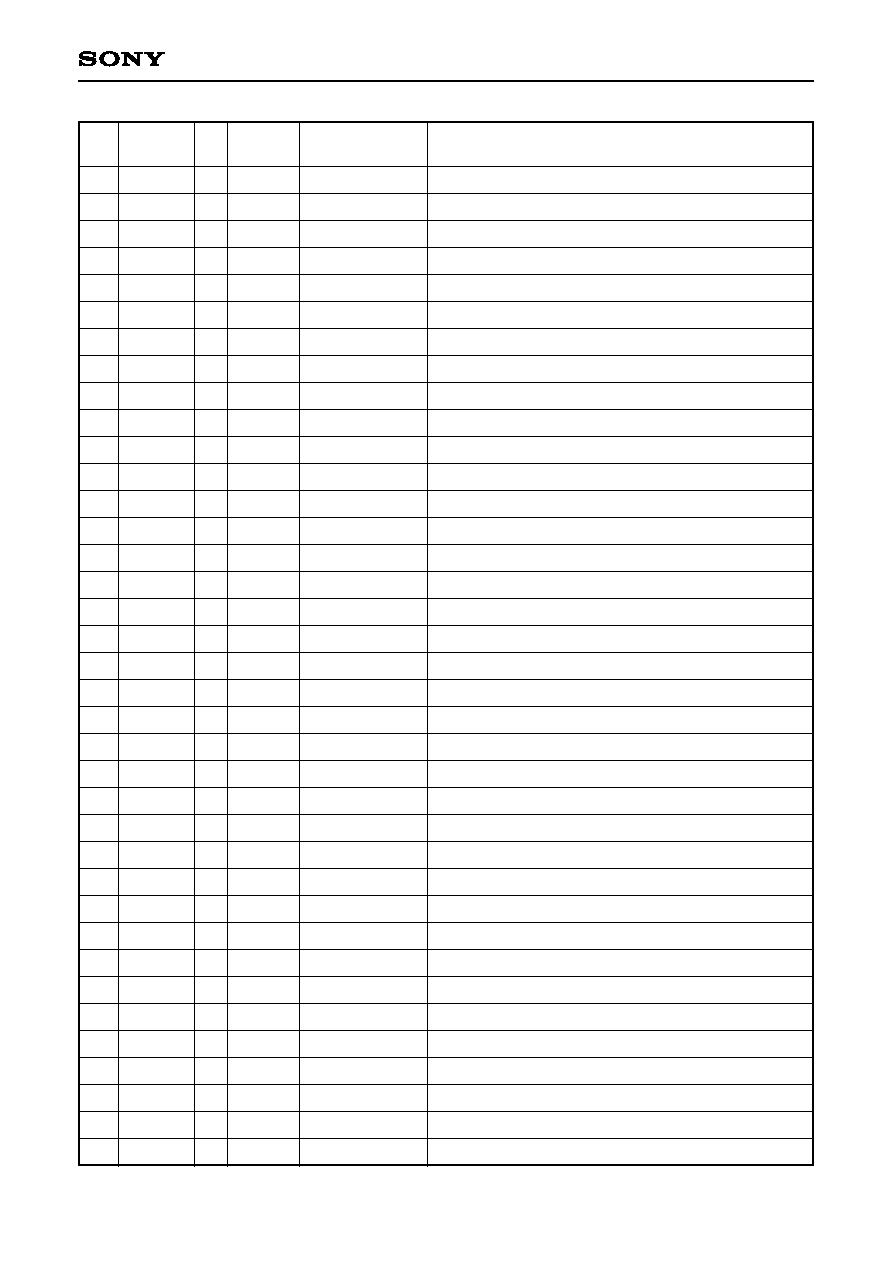

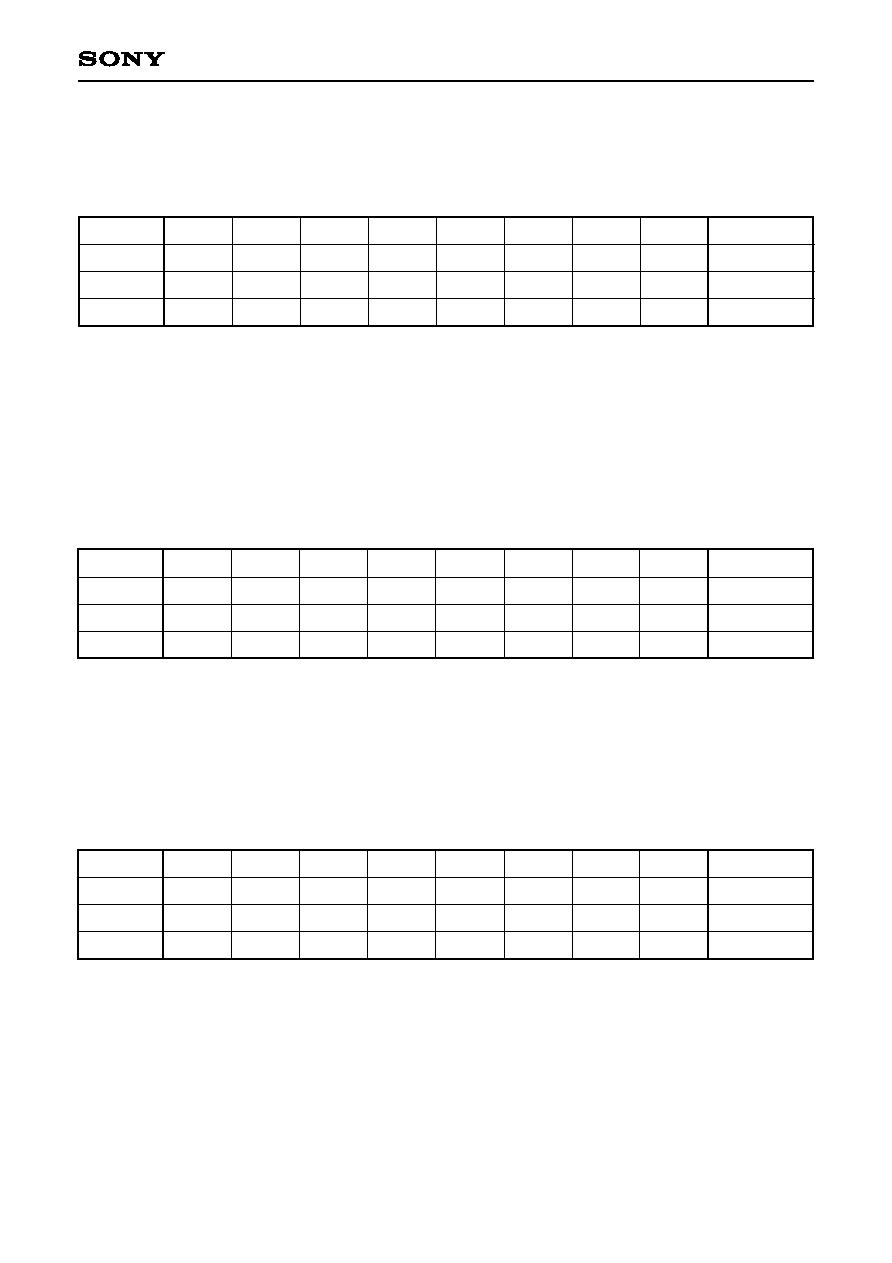

≠ 6 ≠

CXD1818R

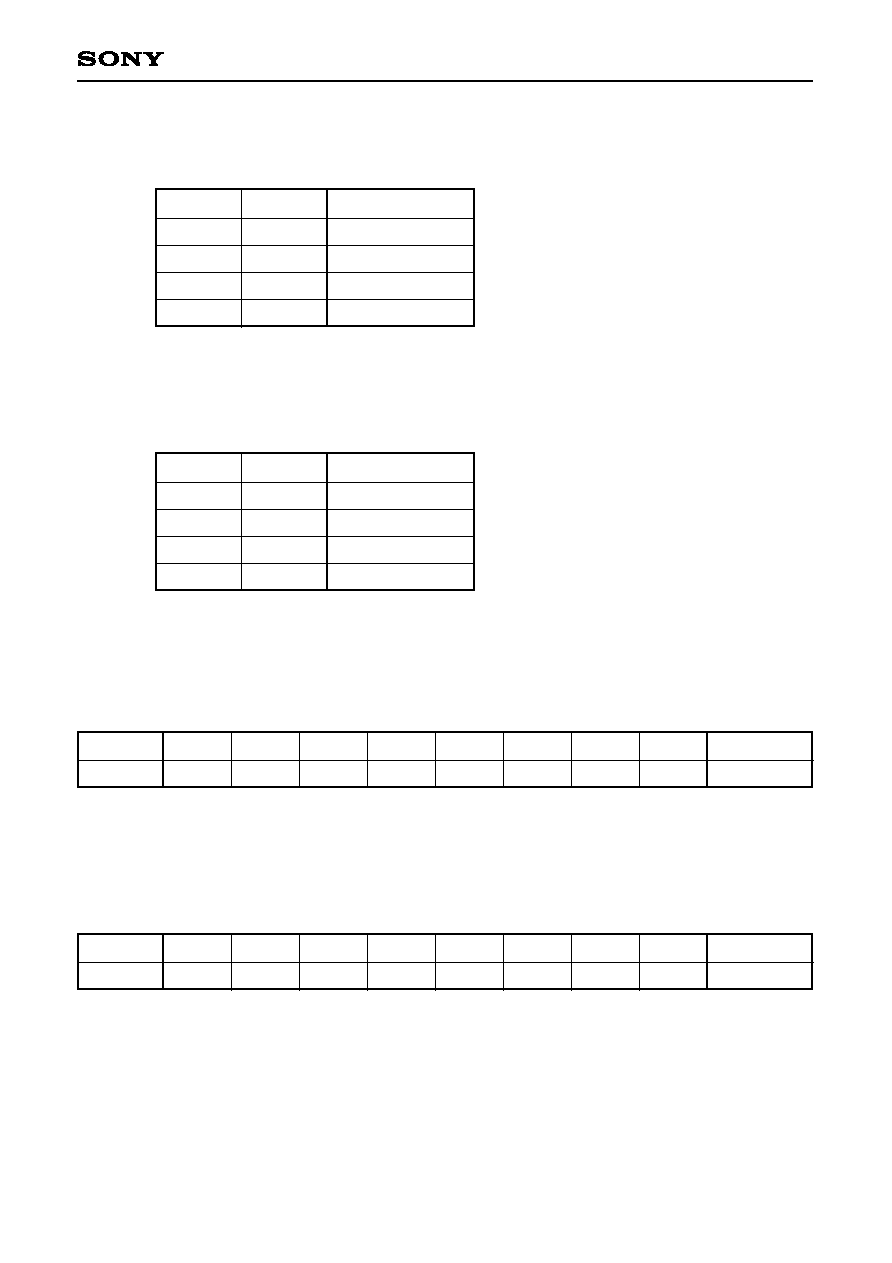

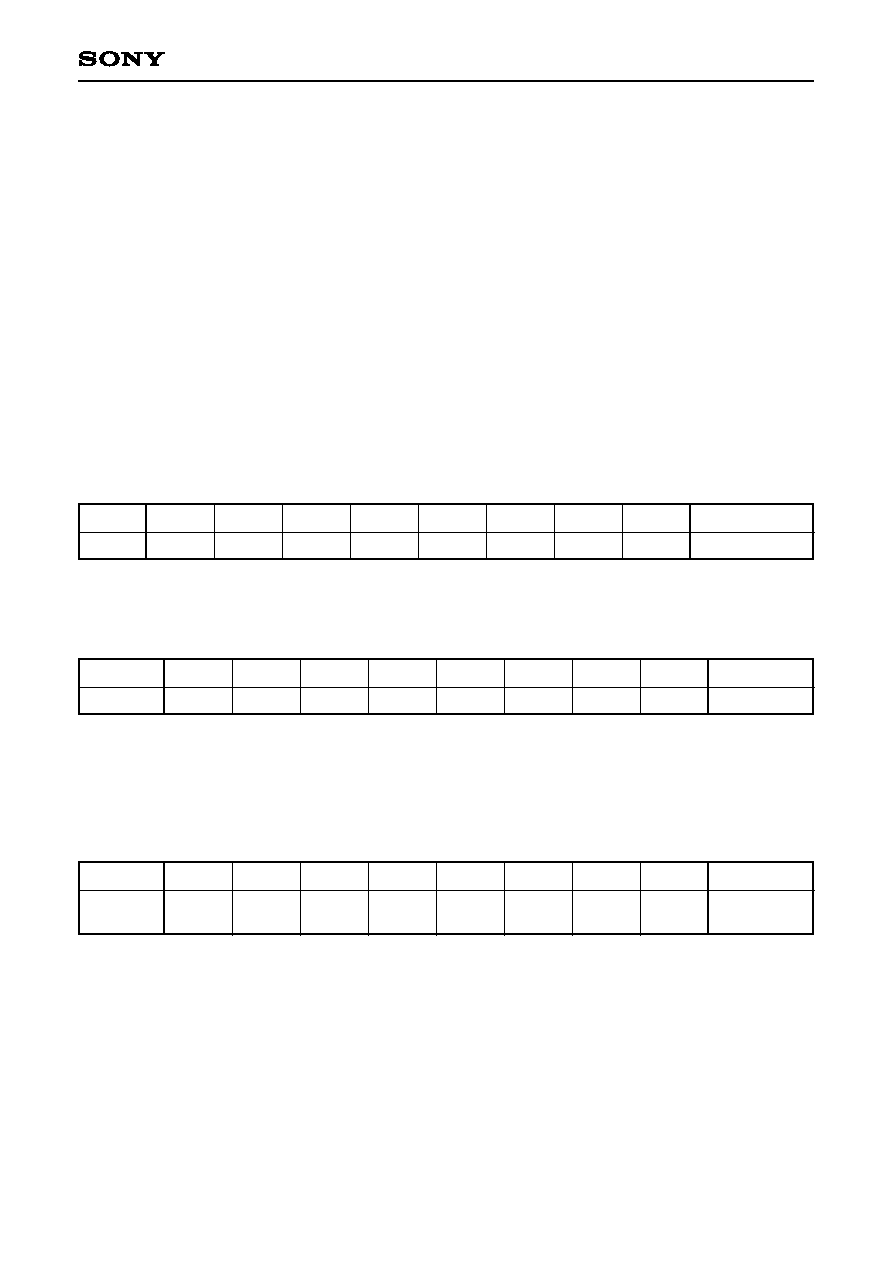

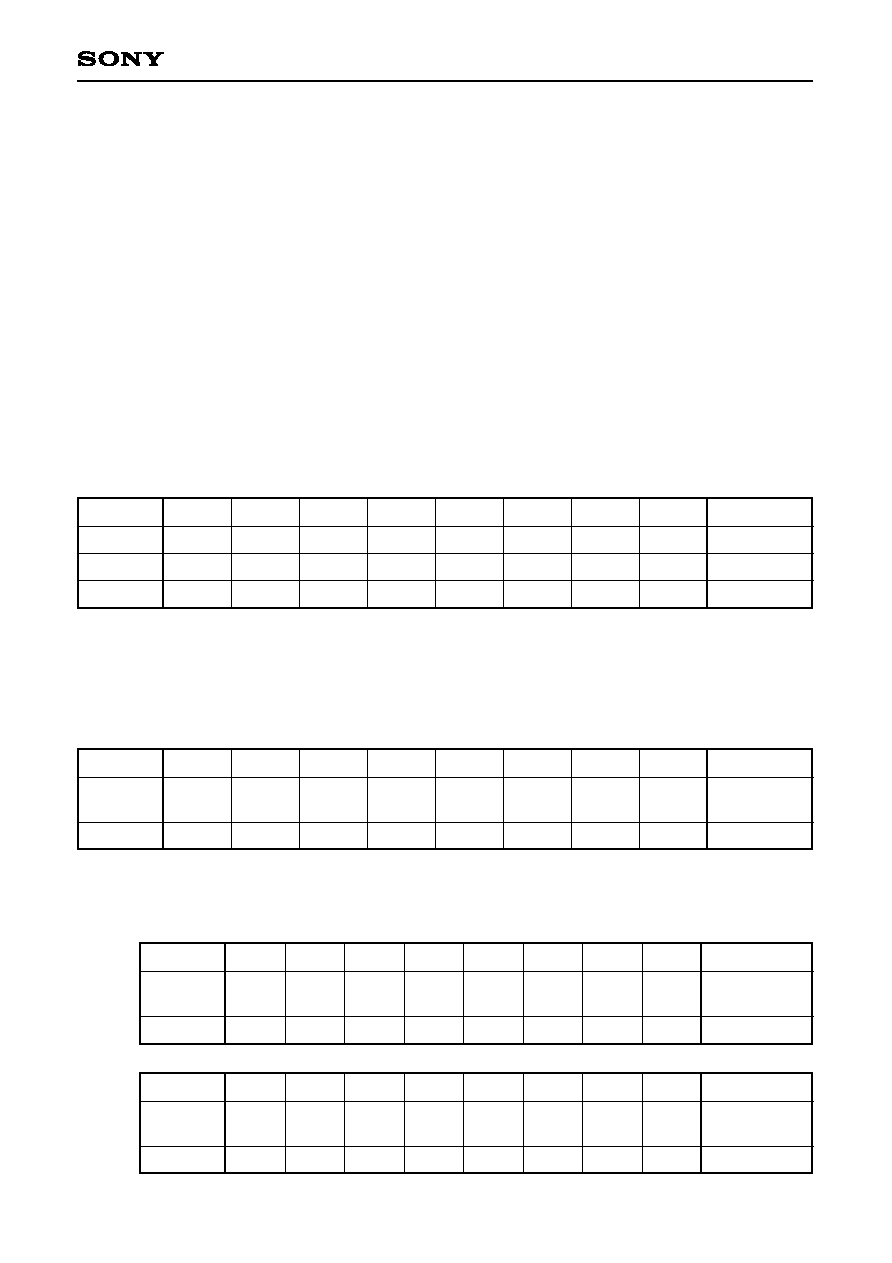

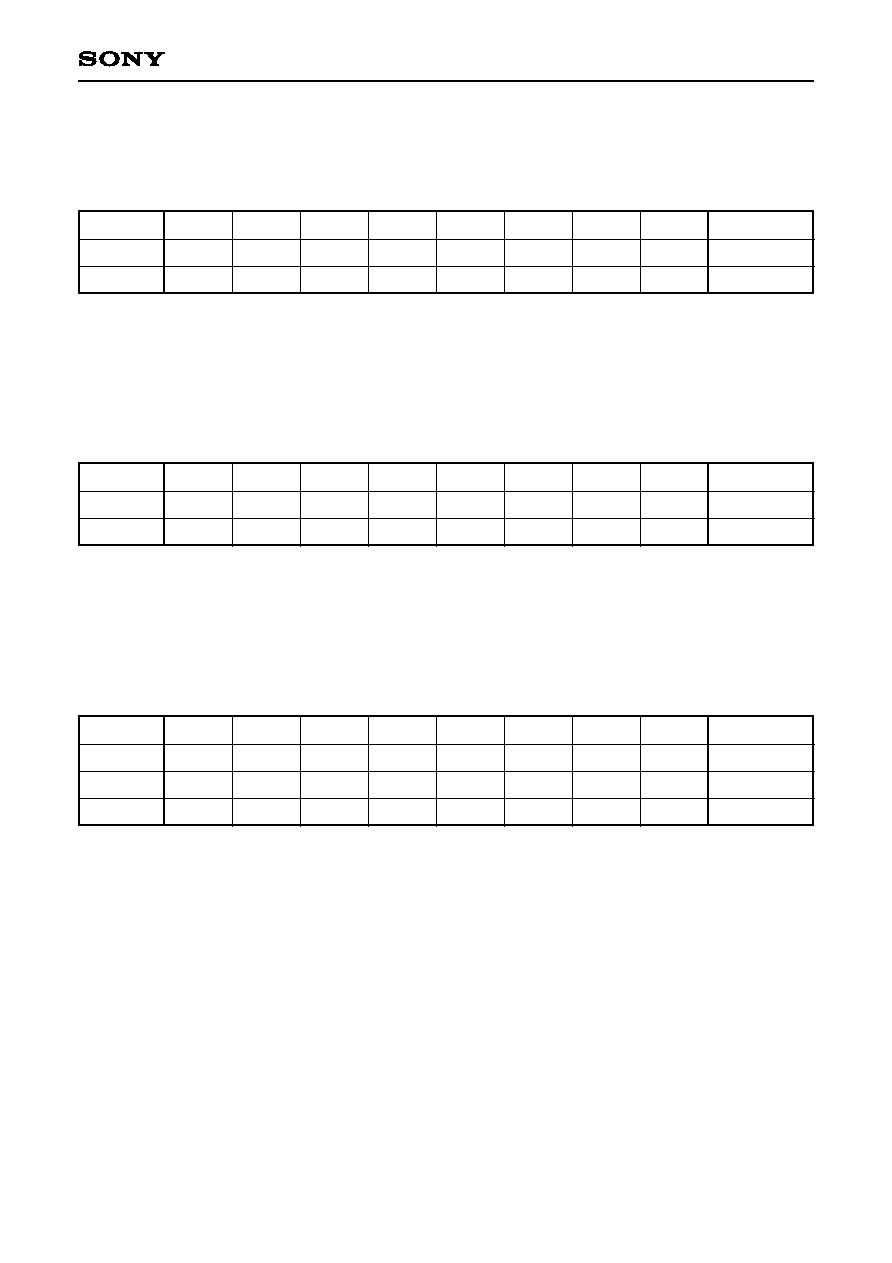

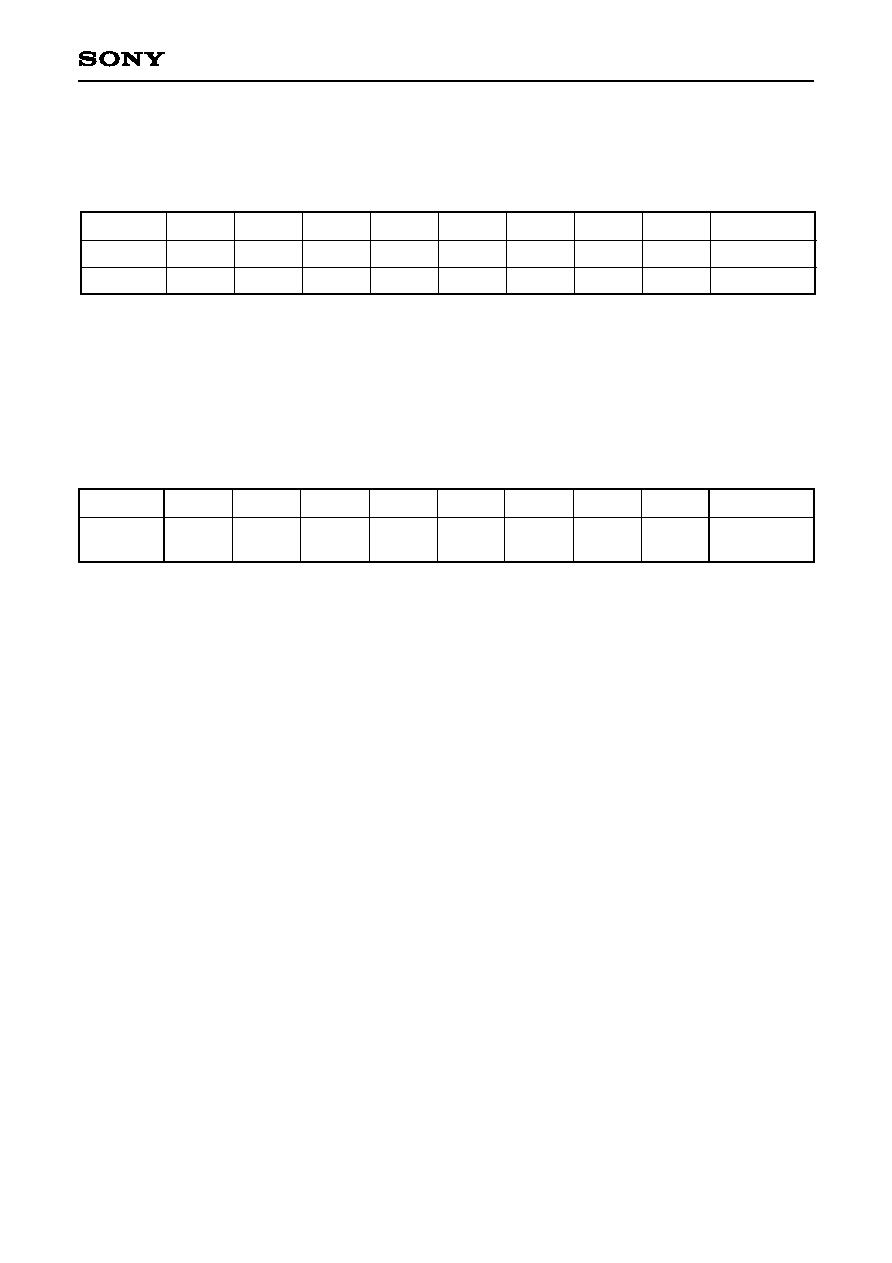

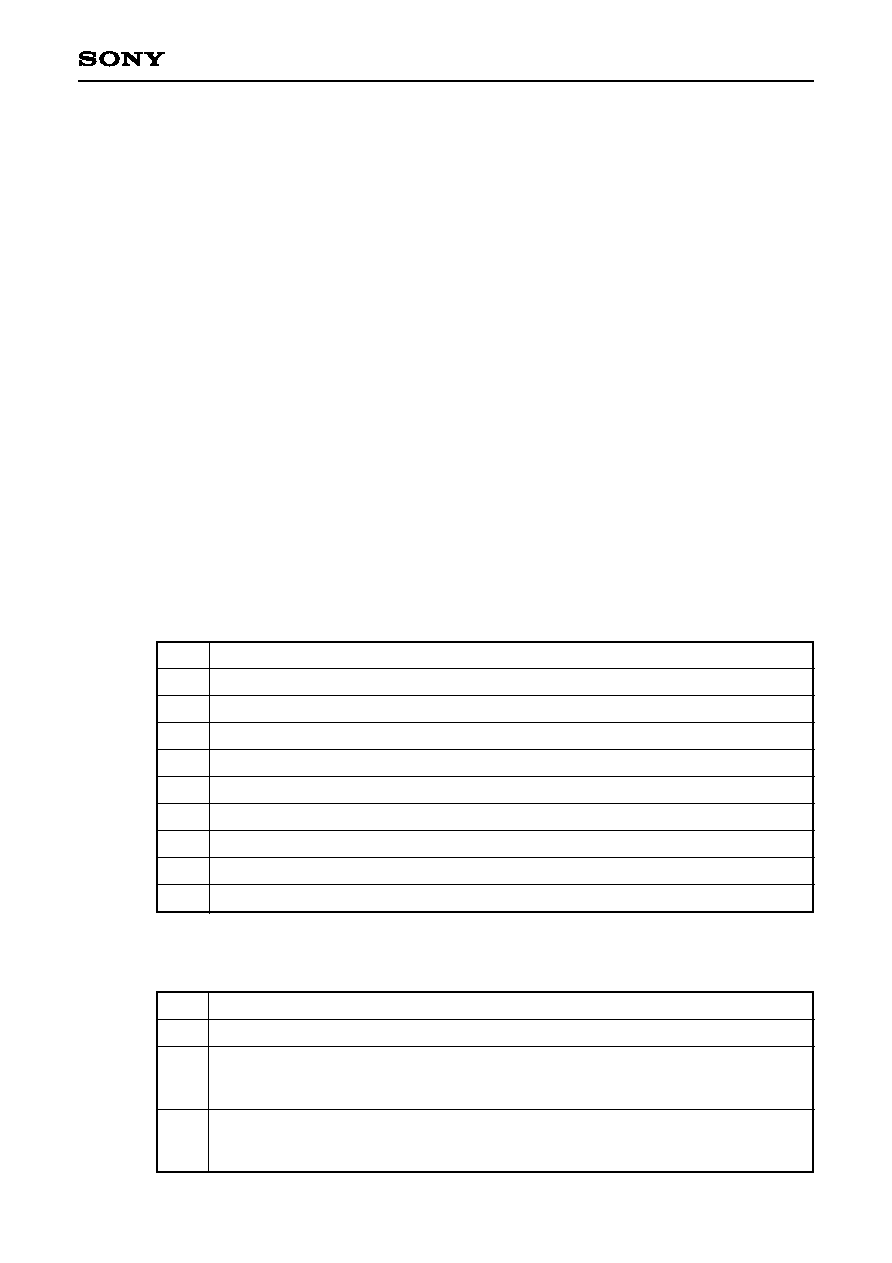

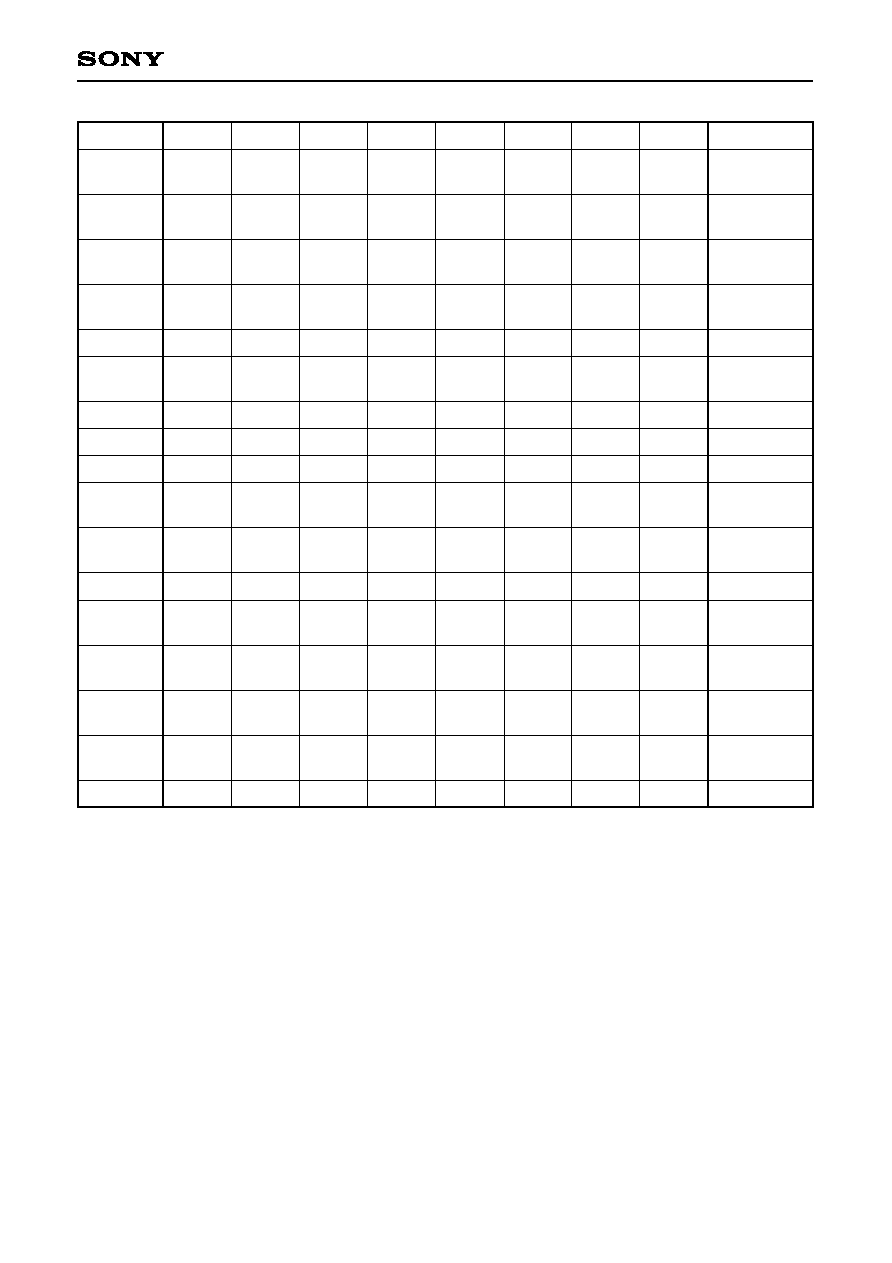

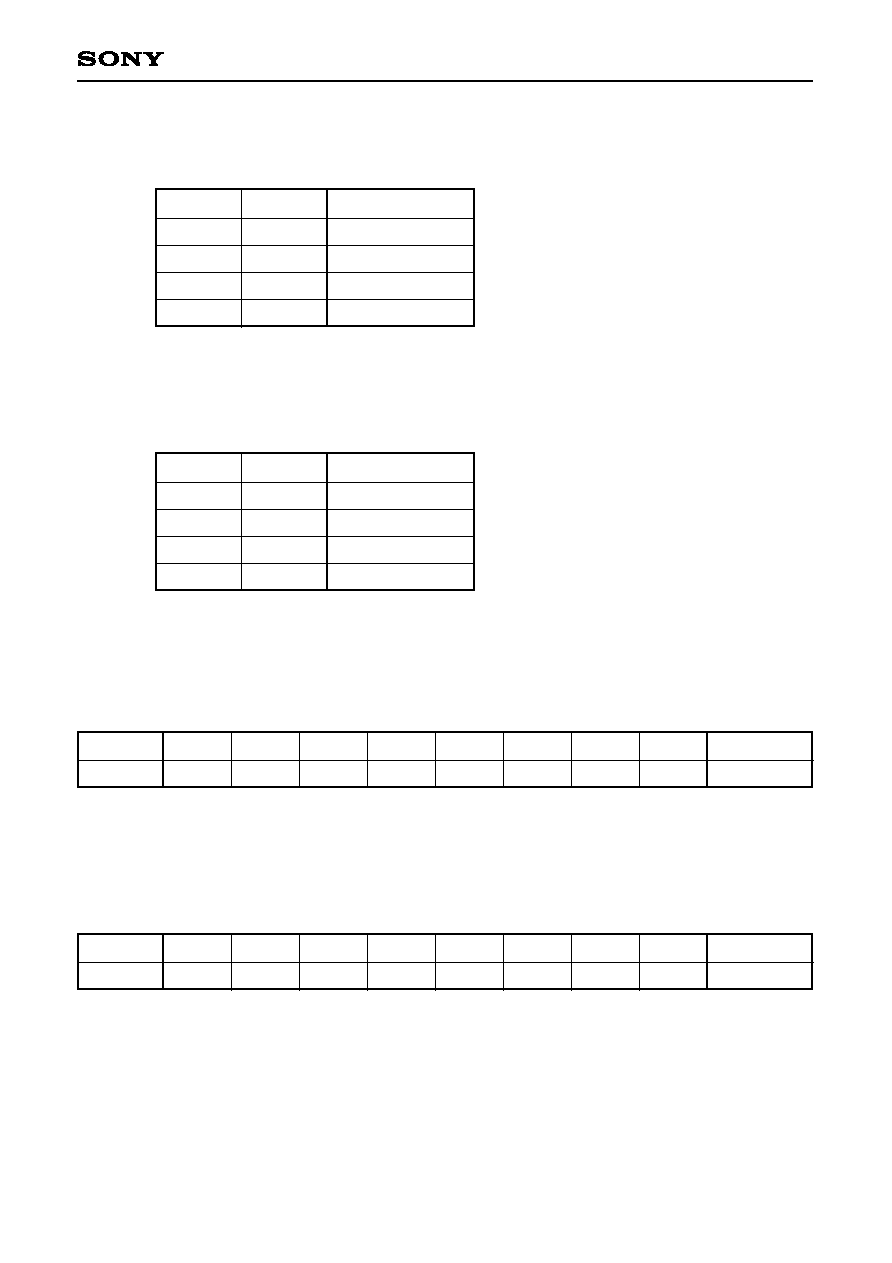

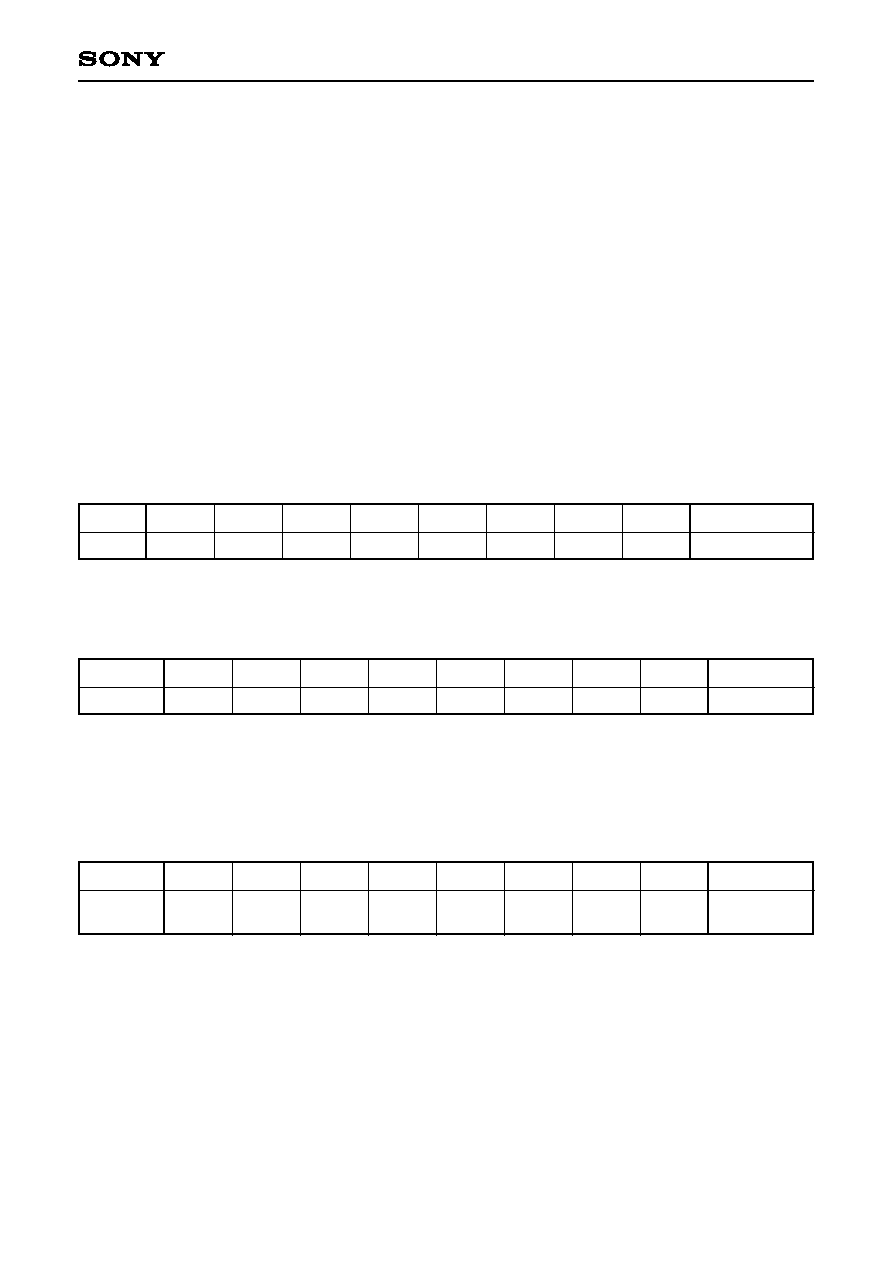

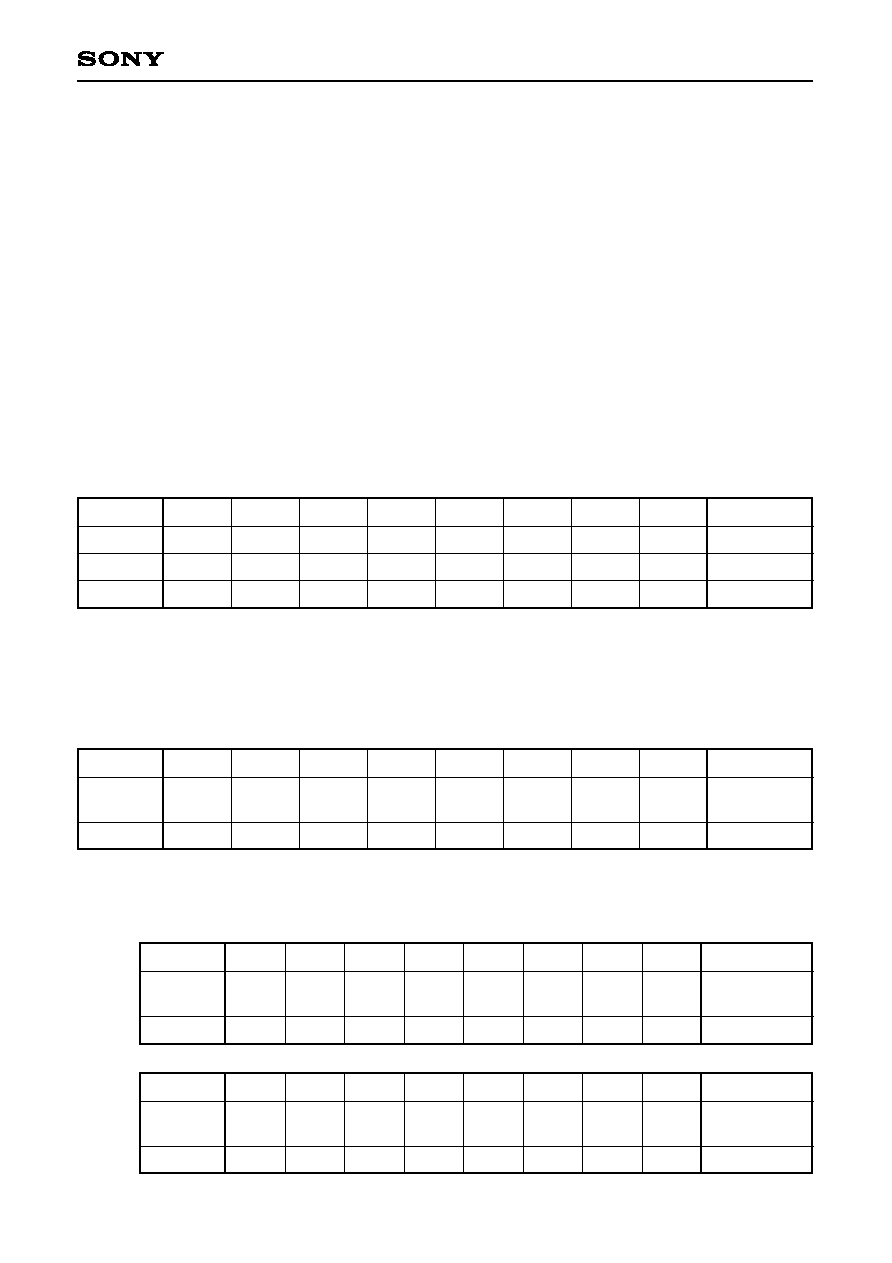

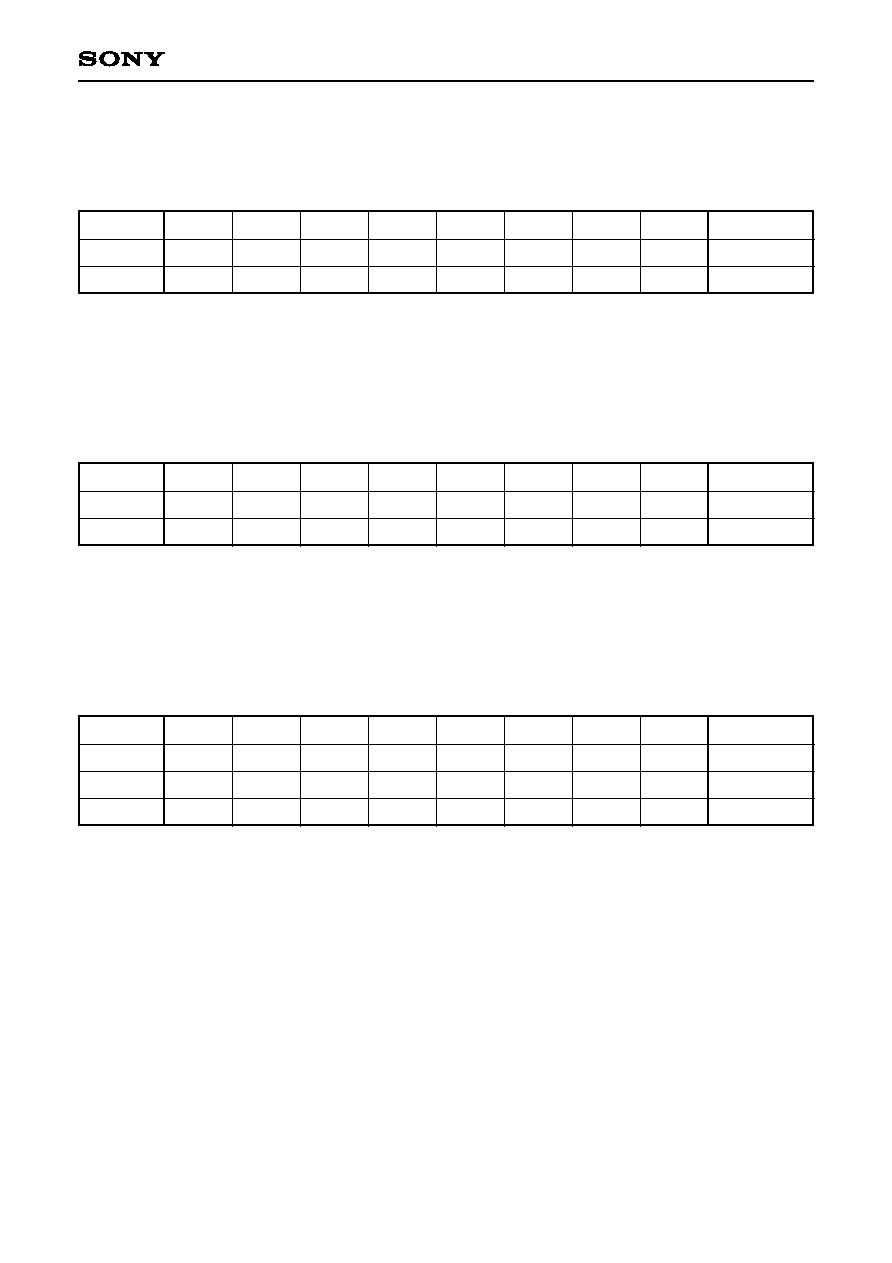

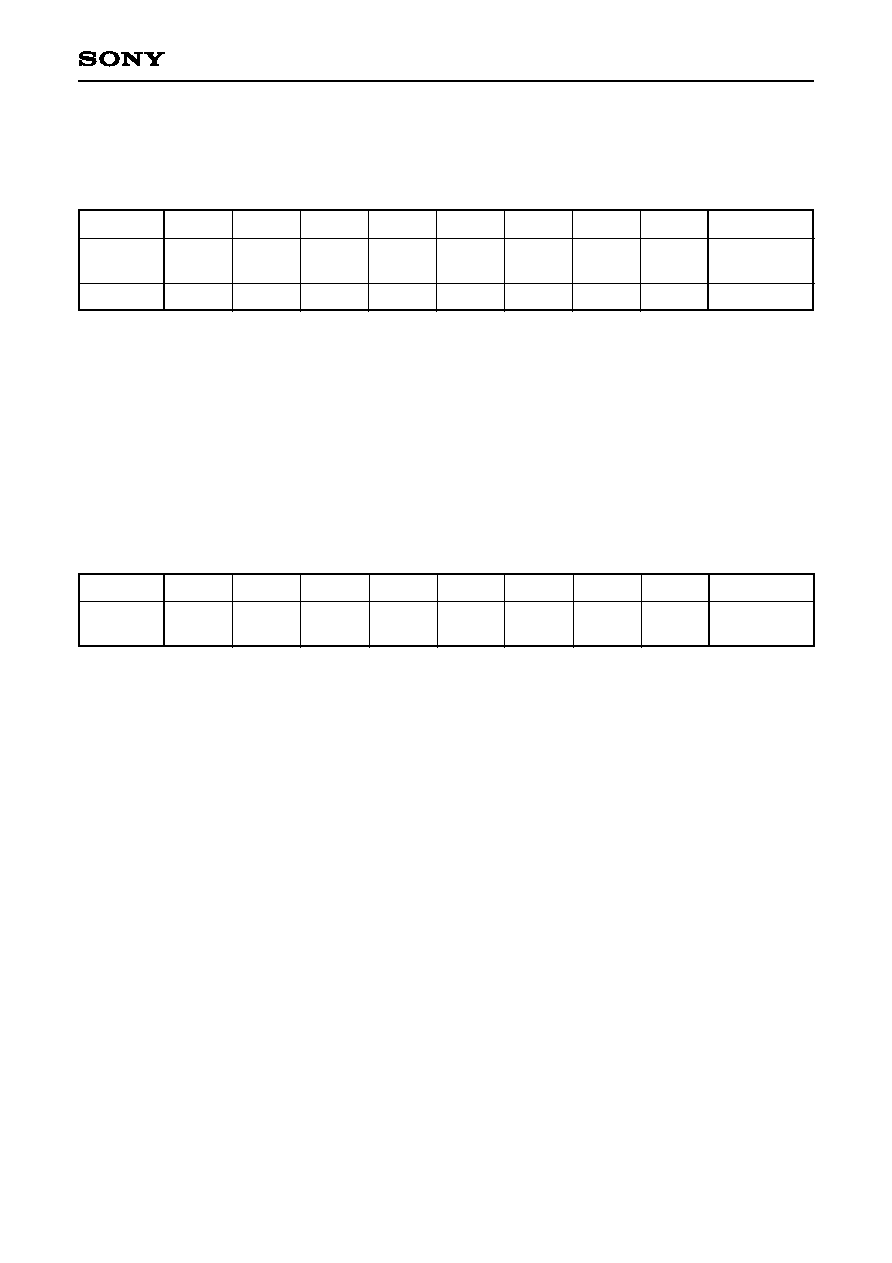

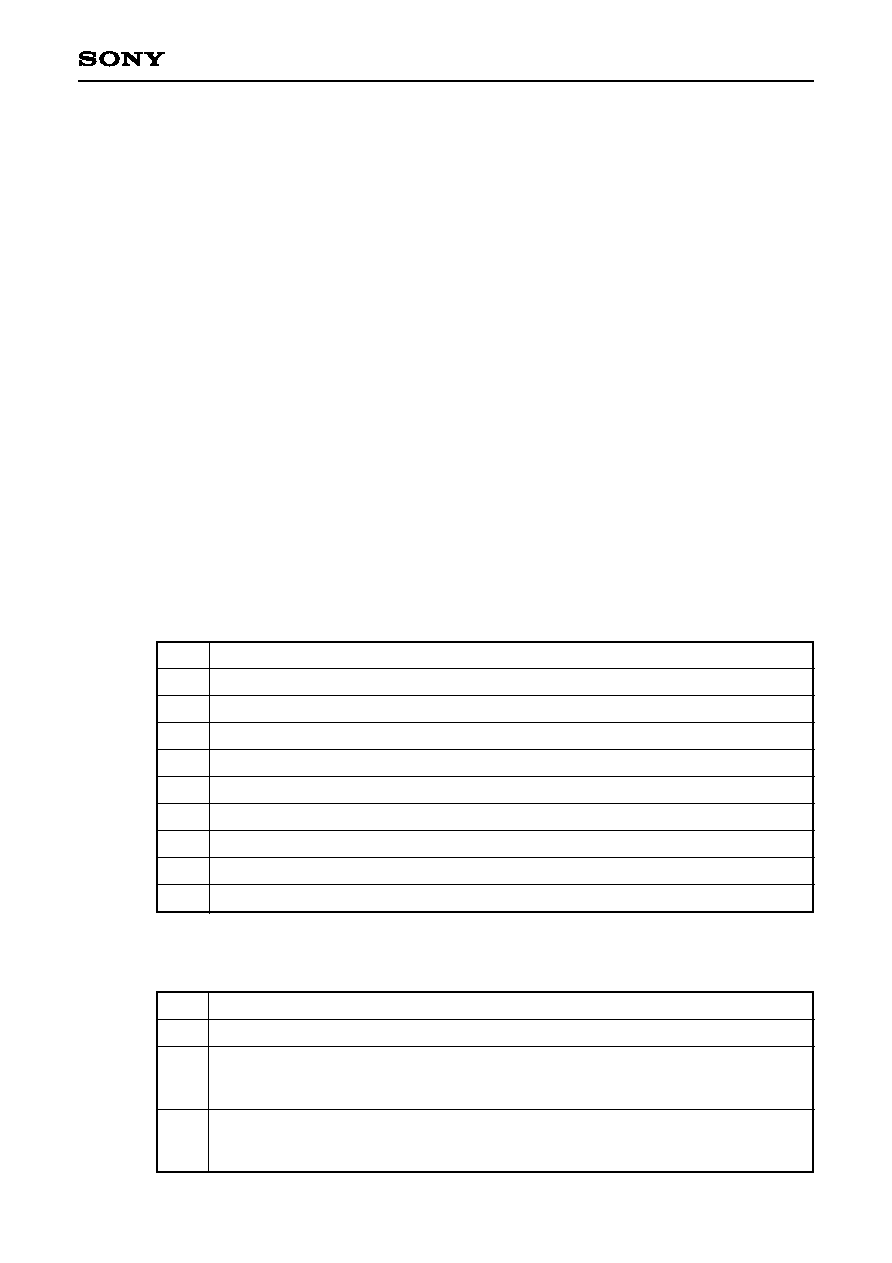

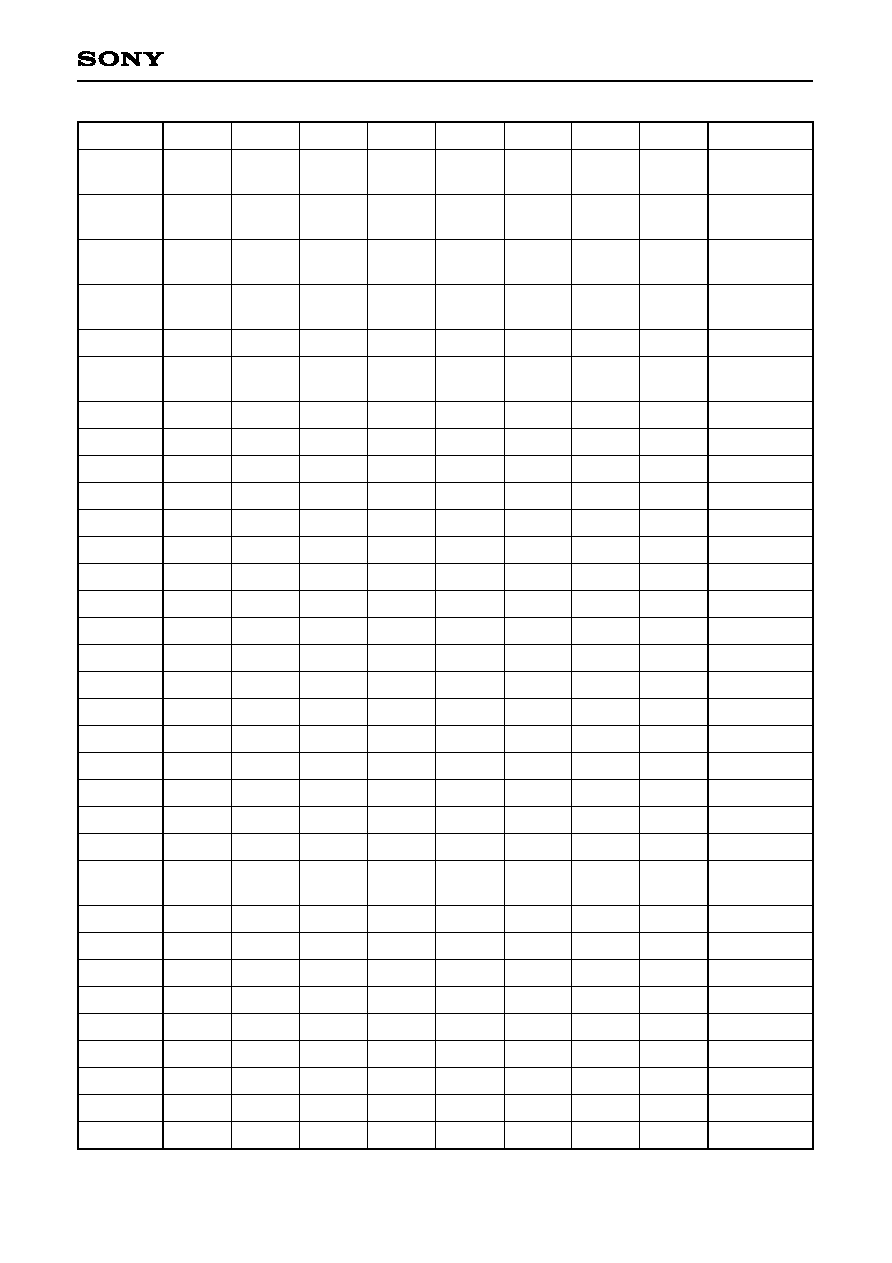

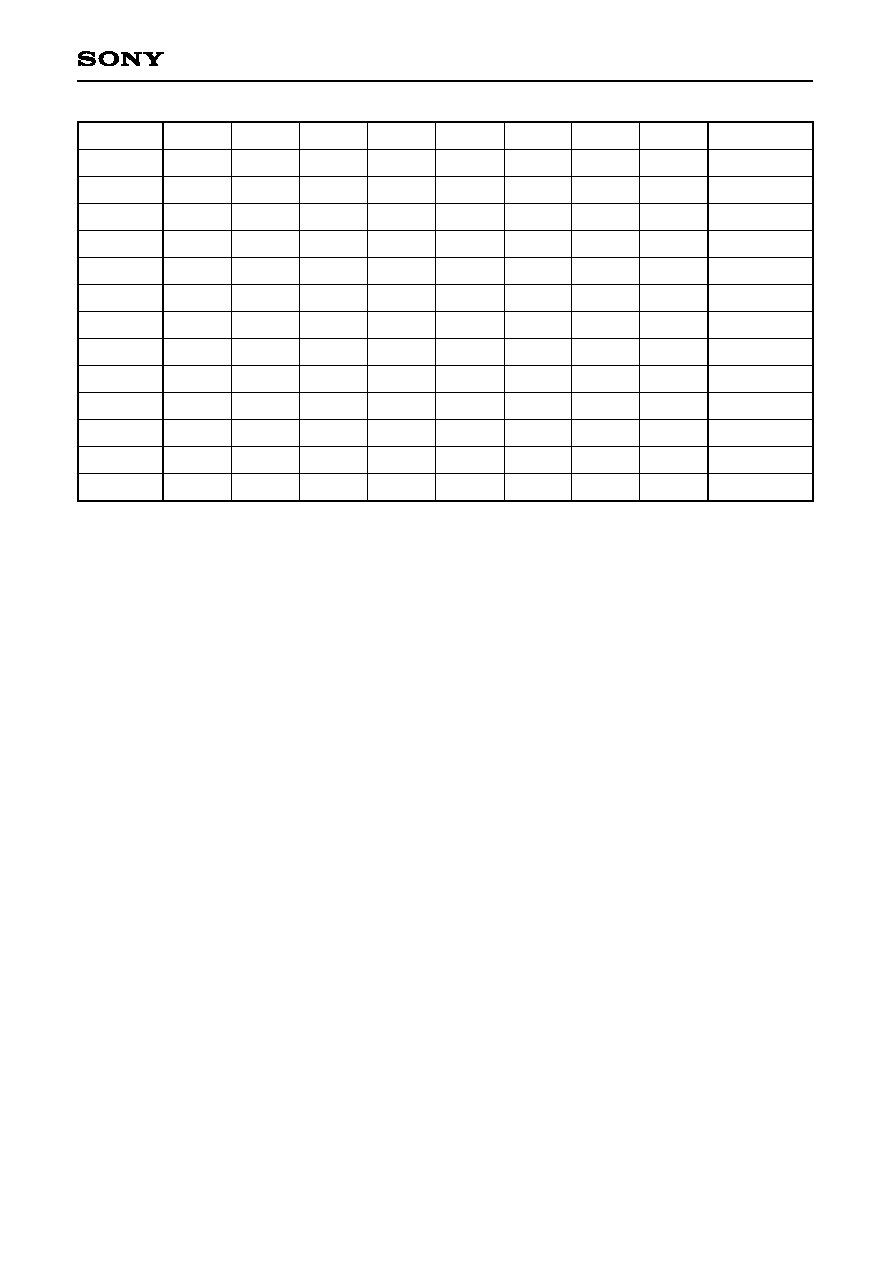

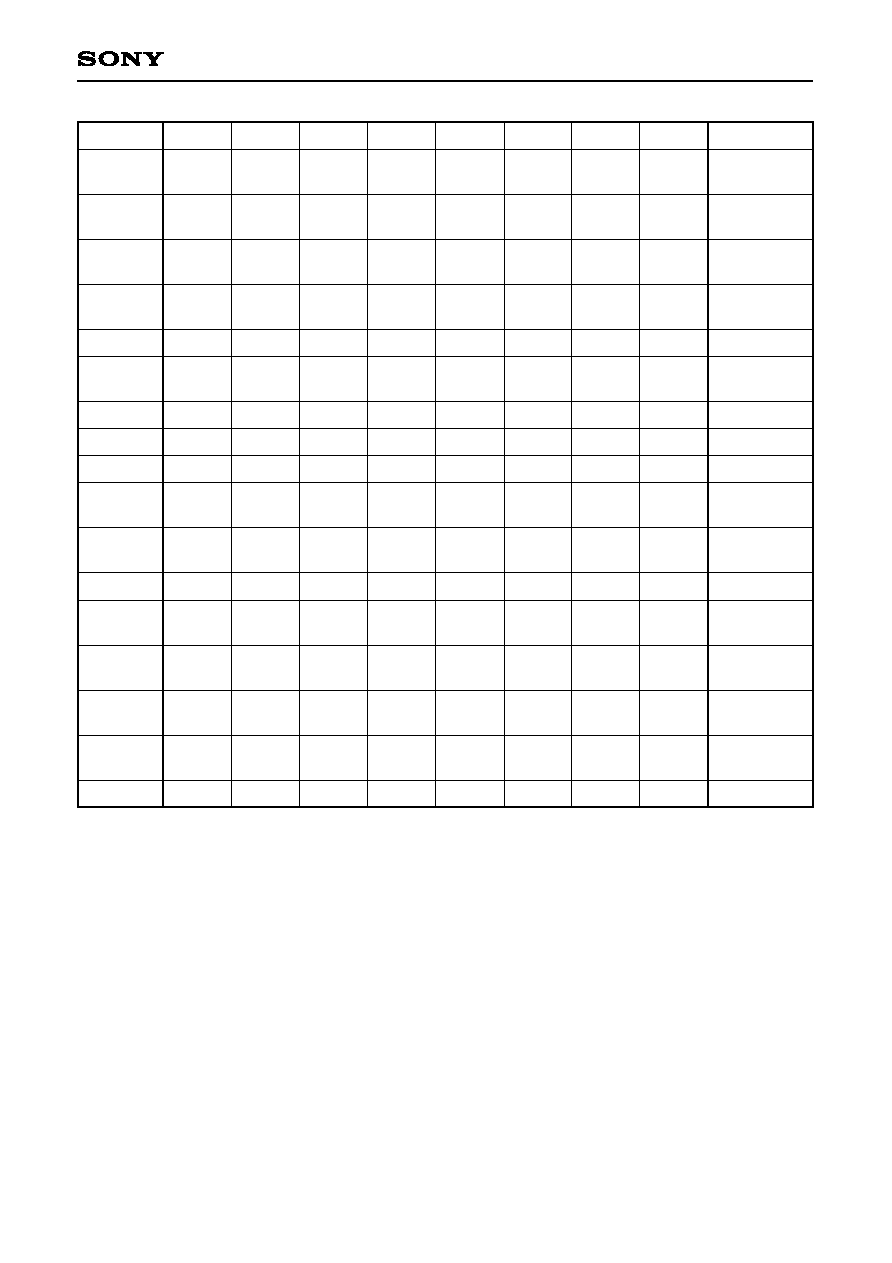

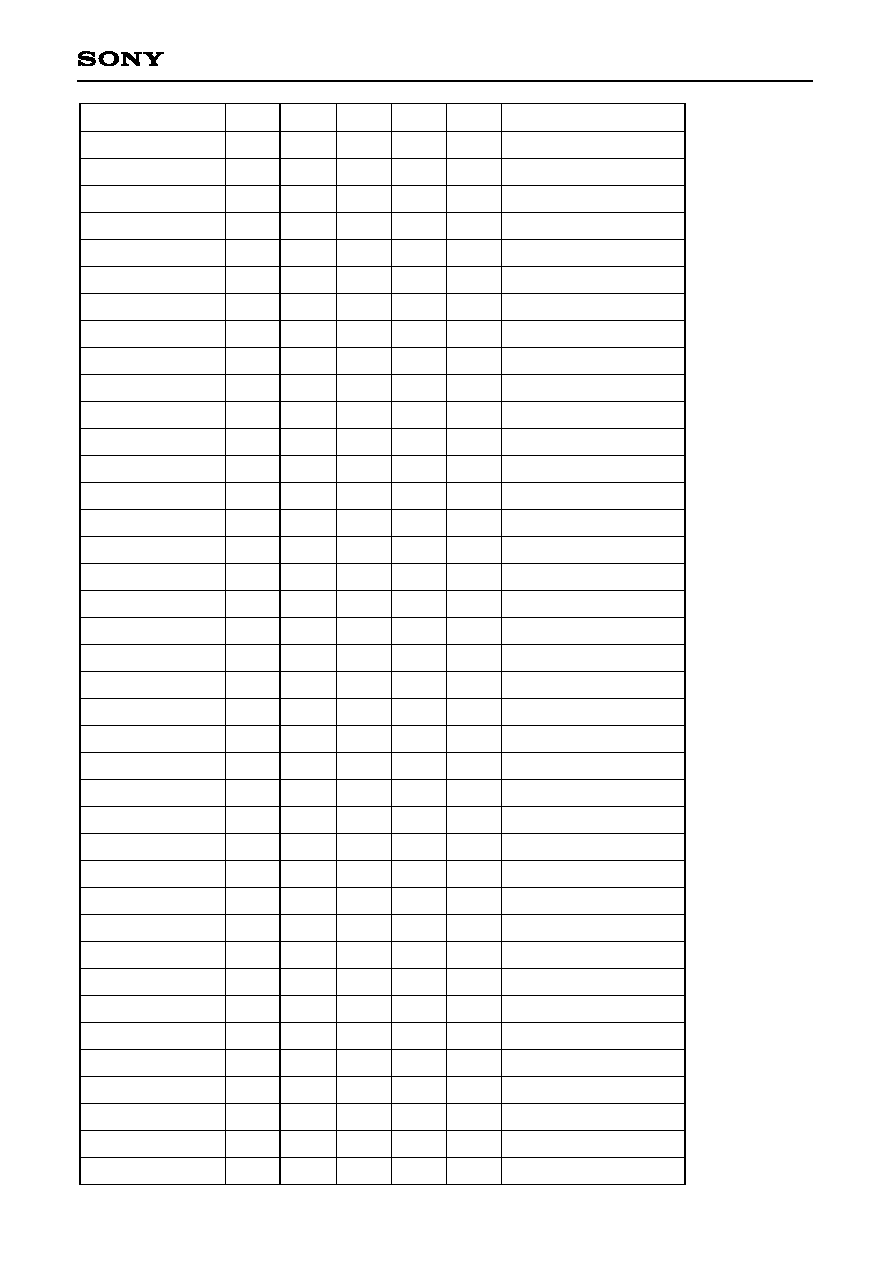

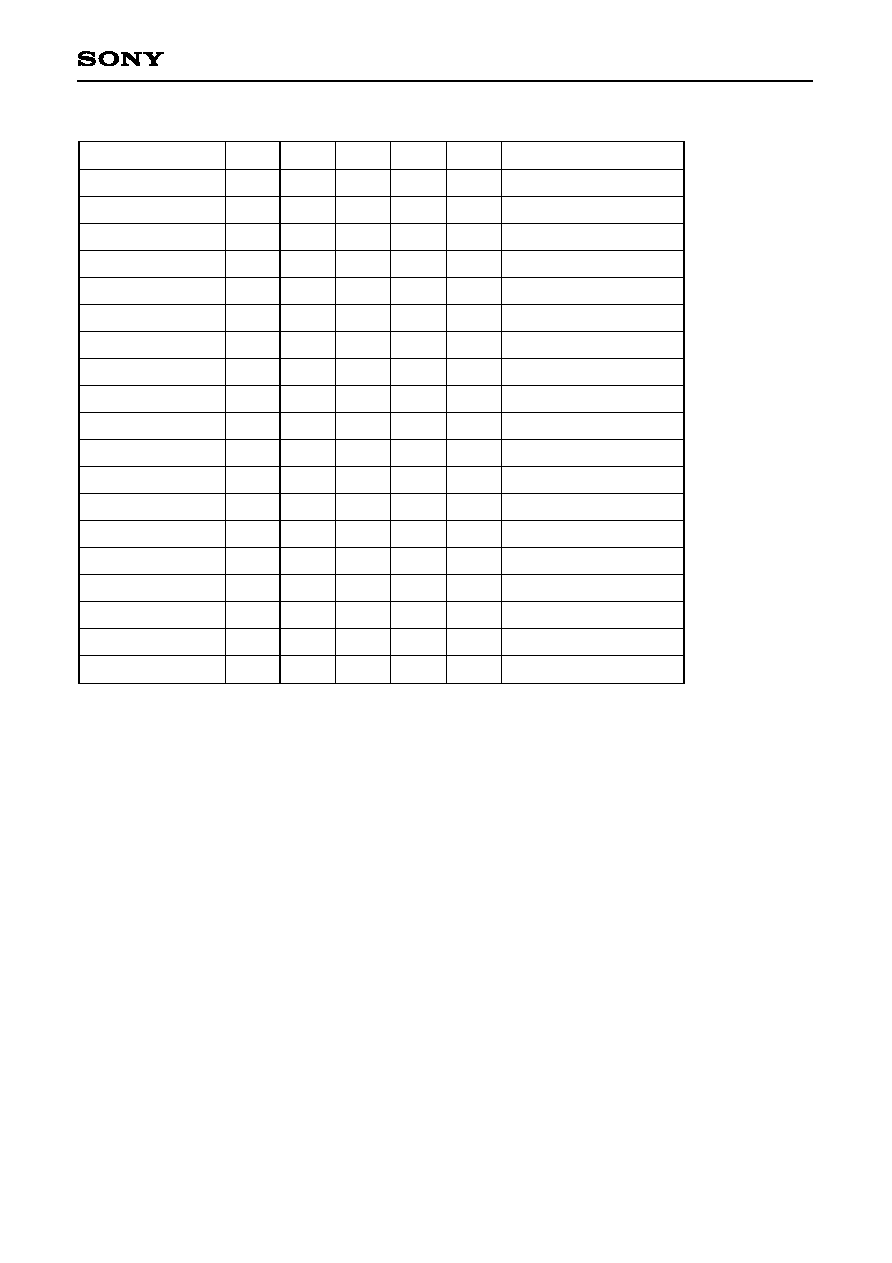

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

--

--

I/O

--

I/O

--

I/O

O

I

--

--

O

I

O

--

--

I

O

O

O

O

O

O

O

--

O

O

O

O

O

O

O

--

--

I/O

I/O

I/O

--

--

Negative

--

Negative

--

Negative

--

--

--

--

Negative

--

Negative

Negative

Negative

Negative

--

--

Power

Power

SCSI I/F

Power

SCSI I/F

Power

SCSI I/F

VCO Charge Pump Out

VCO Control

Analog Power

Analog Power

System I/F

System I/F

System I/F

Power

Power

System I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

Power

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

Power

Power

BufMem I/F

BufMem I/F

BufMem I/F

V

SS

V

DD

SCSI control bus XCD signal

V

SS

SCSI control bus XREQ signal

V

SS

SCSI control bus XIO signal

Multiplier VCO charge pump output

Multiplier VCO control voltage input

Analog V

SS

Analog V

DD

Crystal oscillation circuit output

Crystal oscillation circuit input

Clock output

V

SS

V

DD

CXD1818R reset signal

Address bus output bit 0 to buffer memory

Address bus output bit 1 to buffer memory

Address bus output bit 2 to buffer memory

Address bus output bit 3 to buffer memory

Address bus output bit 4 to buffer memory

Address bus output bit 5 to buffer memory

Address bus output bit 6 to buffer memory

V

SS

Address bus output bit 7 to buffer memory

Address bus output bit 8 to buffer memory

Address bus output bit 9 to buffer memory

Buffer memory RAS (Row Address Strobe) signal

Buffer memory CAS (Column Address Strobe) signal

Buffer memory CAS (Column Address Strobe) signal

Data write strobe signal to buffer memory

V

SS

V

DD

Buffer memory data bus bit 0

Buffer memory data bus bit 1

Buffer memory data bus bit 2

V

SS

V

DD

XCD

V

SS

XREQ

V

SS

XIO

CM1

AC

AV

SS

AV

DD

XTL2

XTL1

CLK

V

SS

V

DD

XRES

MA0

MA1

MA2

MA3

MA4

MA5

MA6

V

SS

MA7

MA8

MA9

XRAS

XUCAS

XLCAS

XMWR

V

SS

V

DD

MDB0

MDB1

MDB2

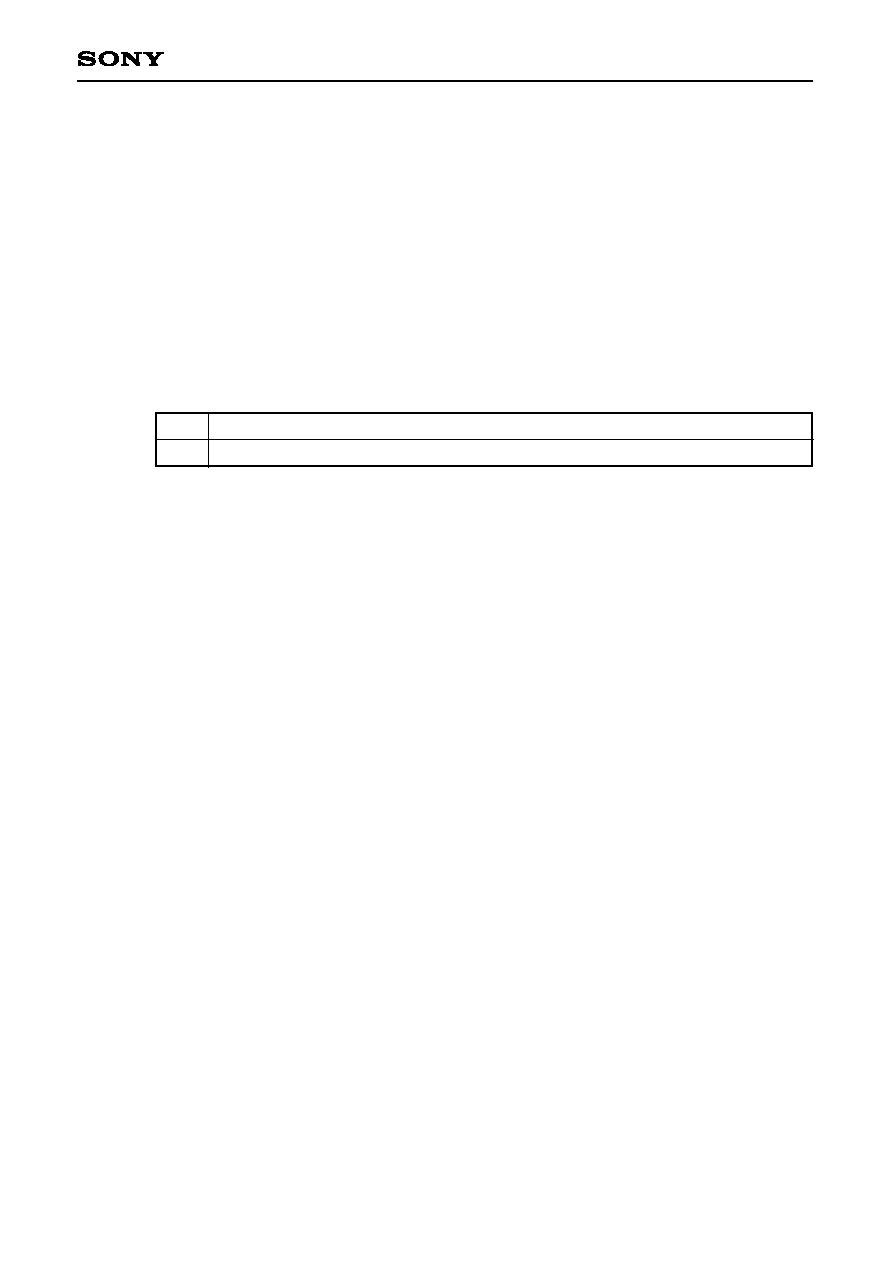

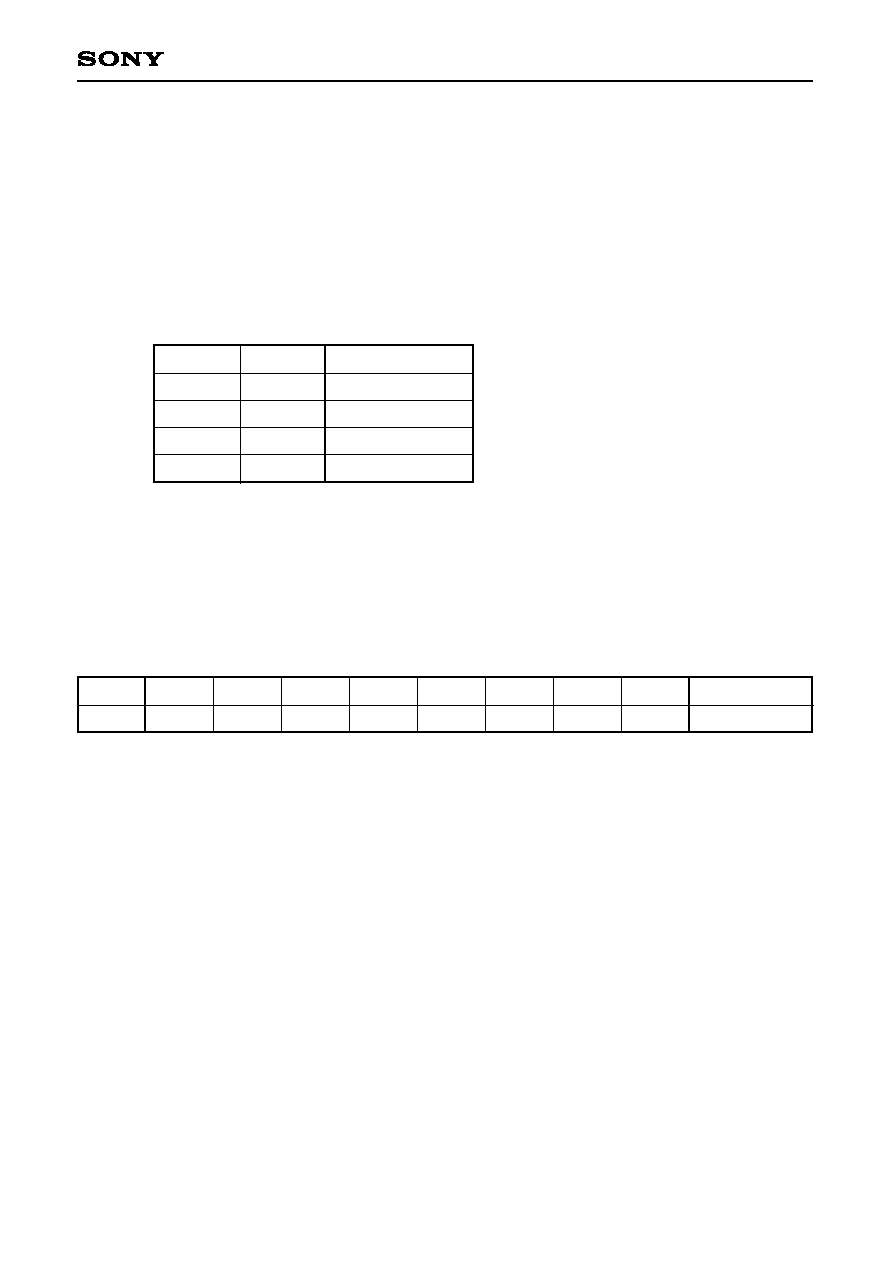

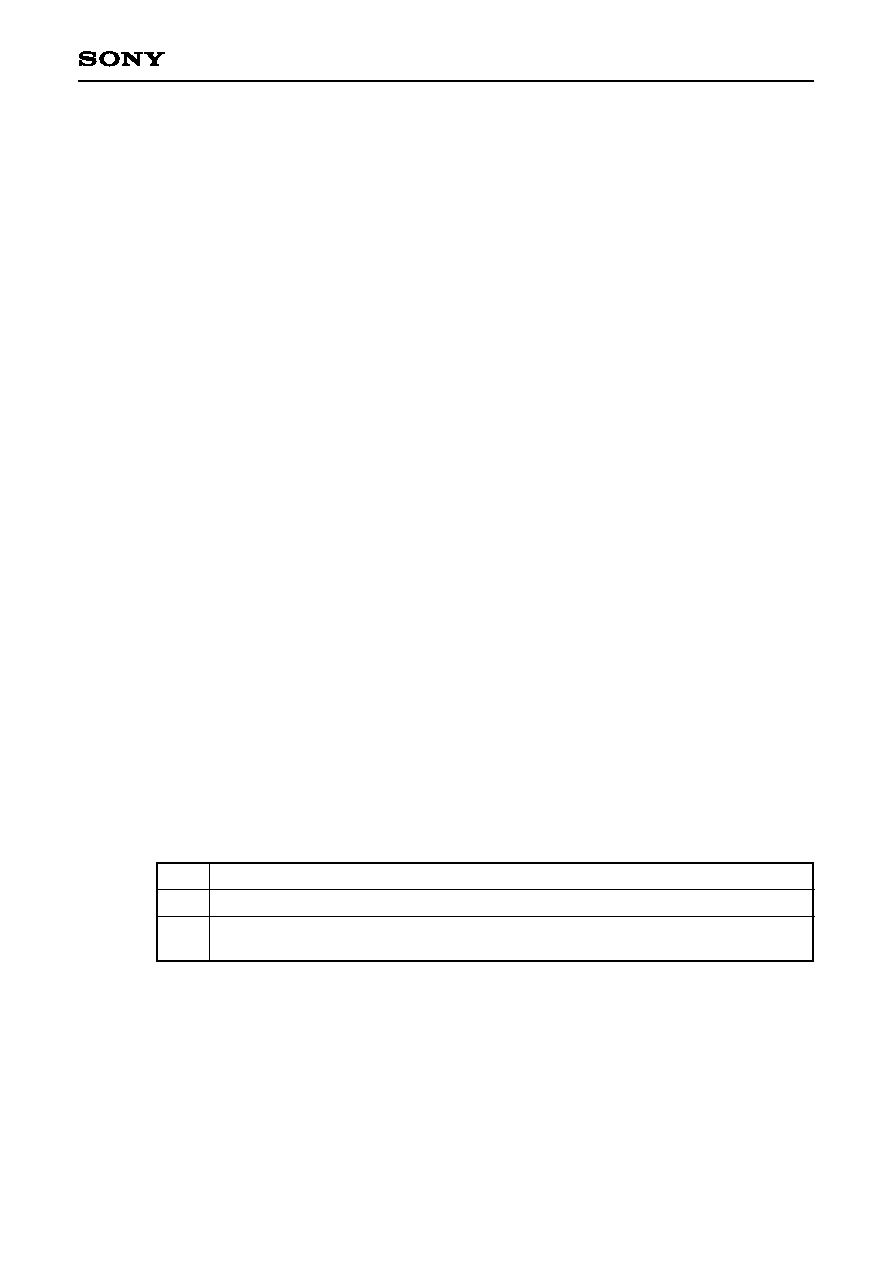

Pin

No.

Symbol

I/O

Logic

Classification

Description

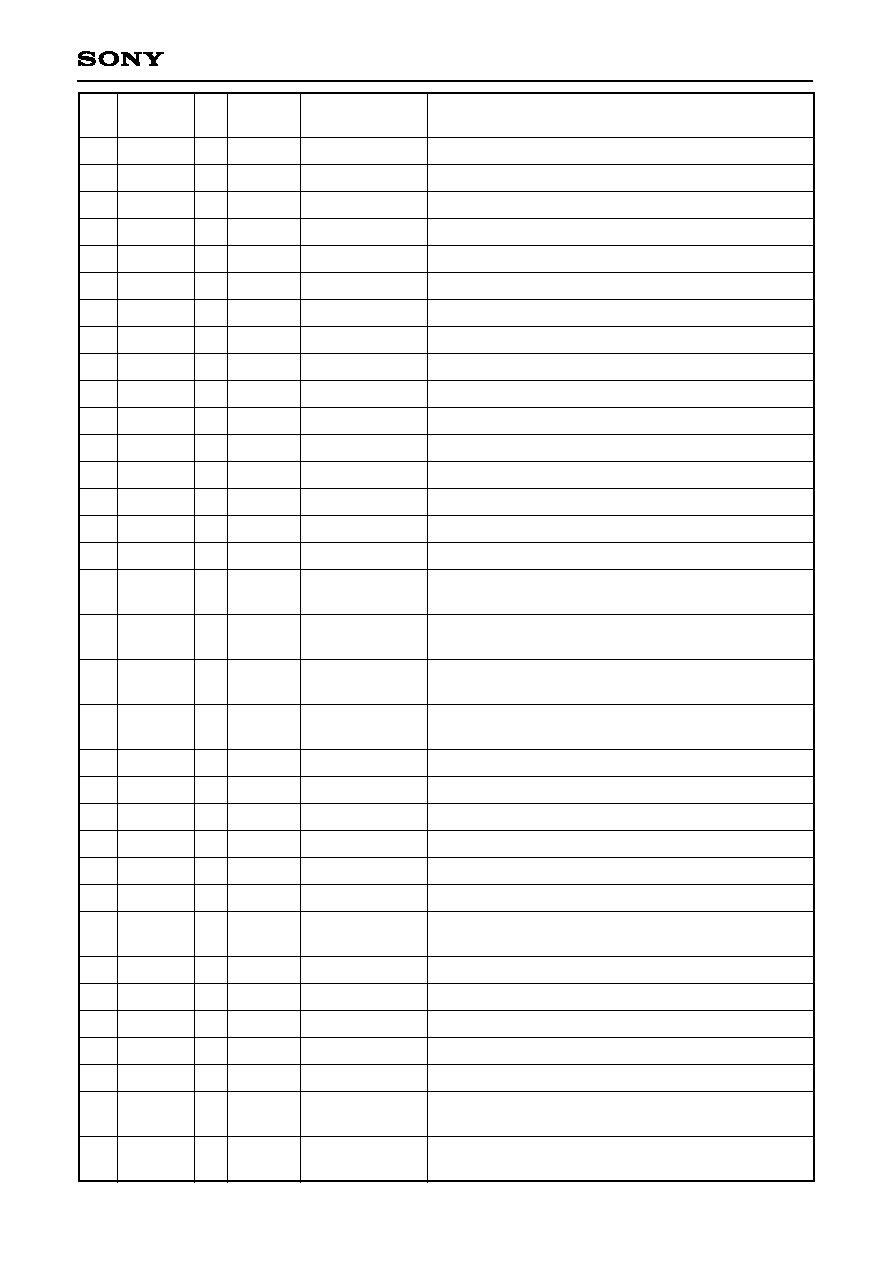

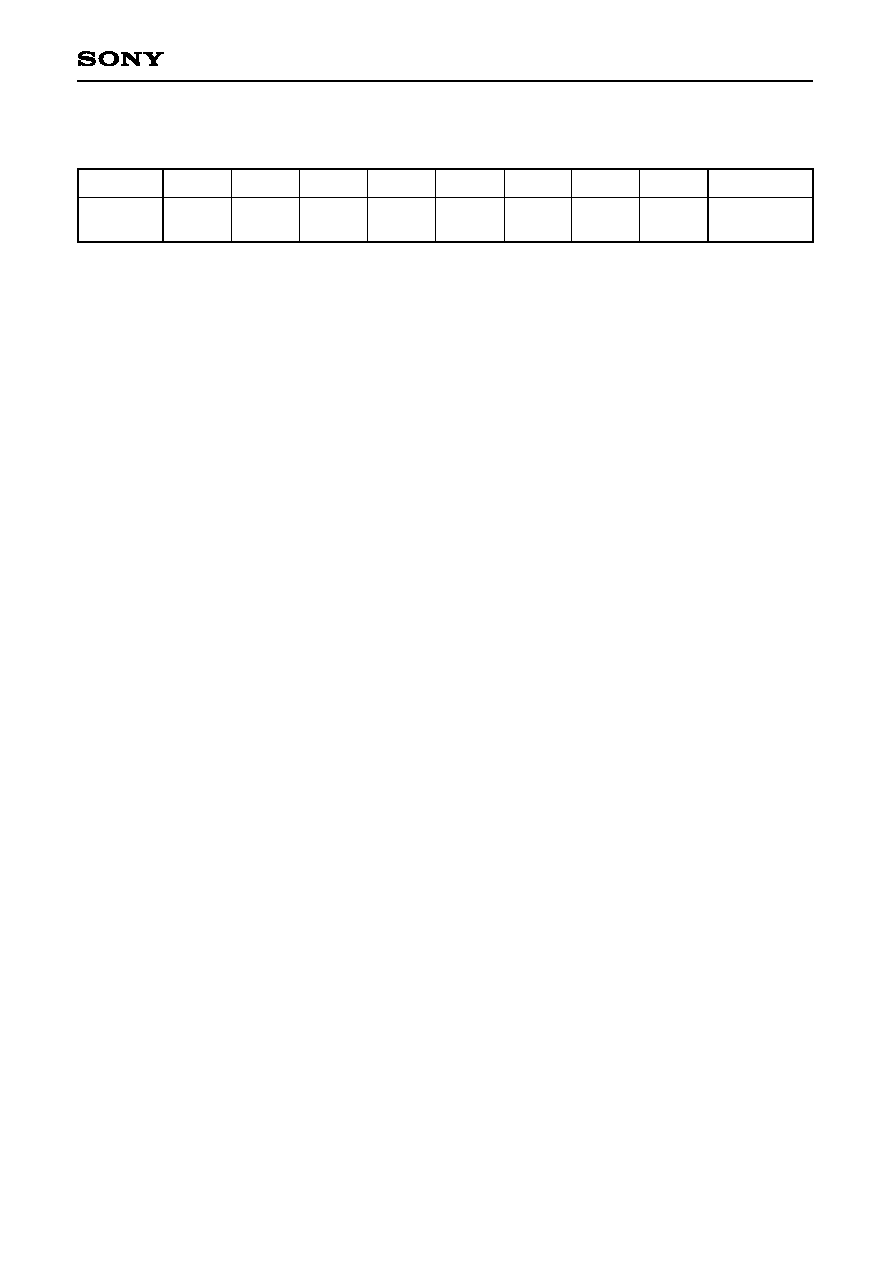

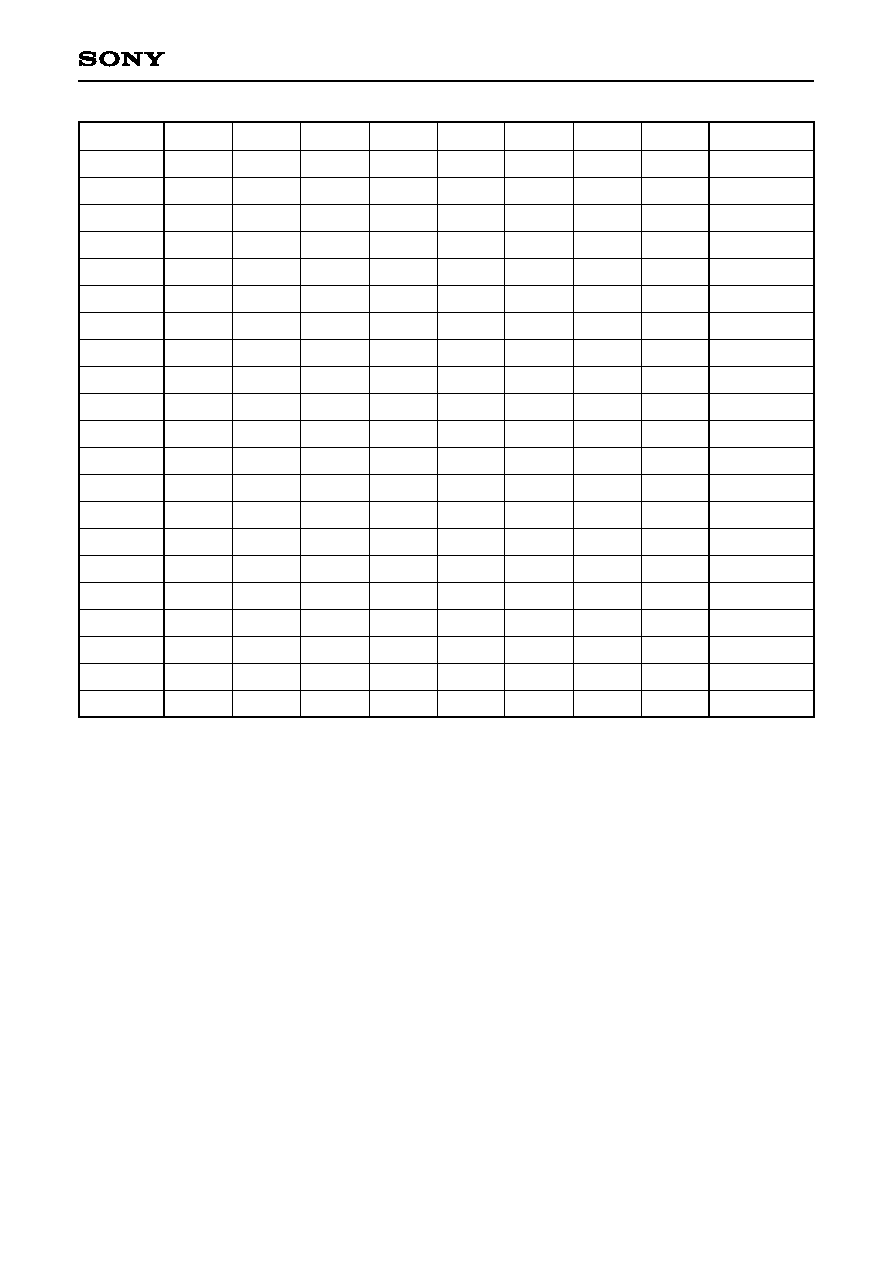

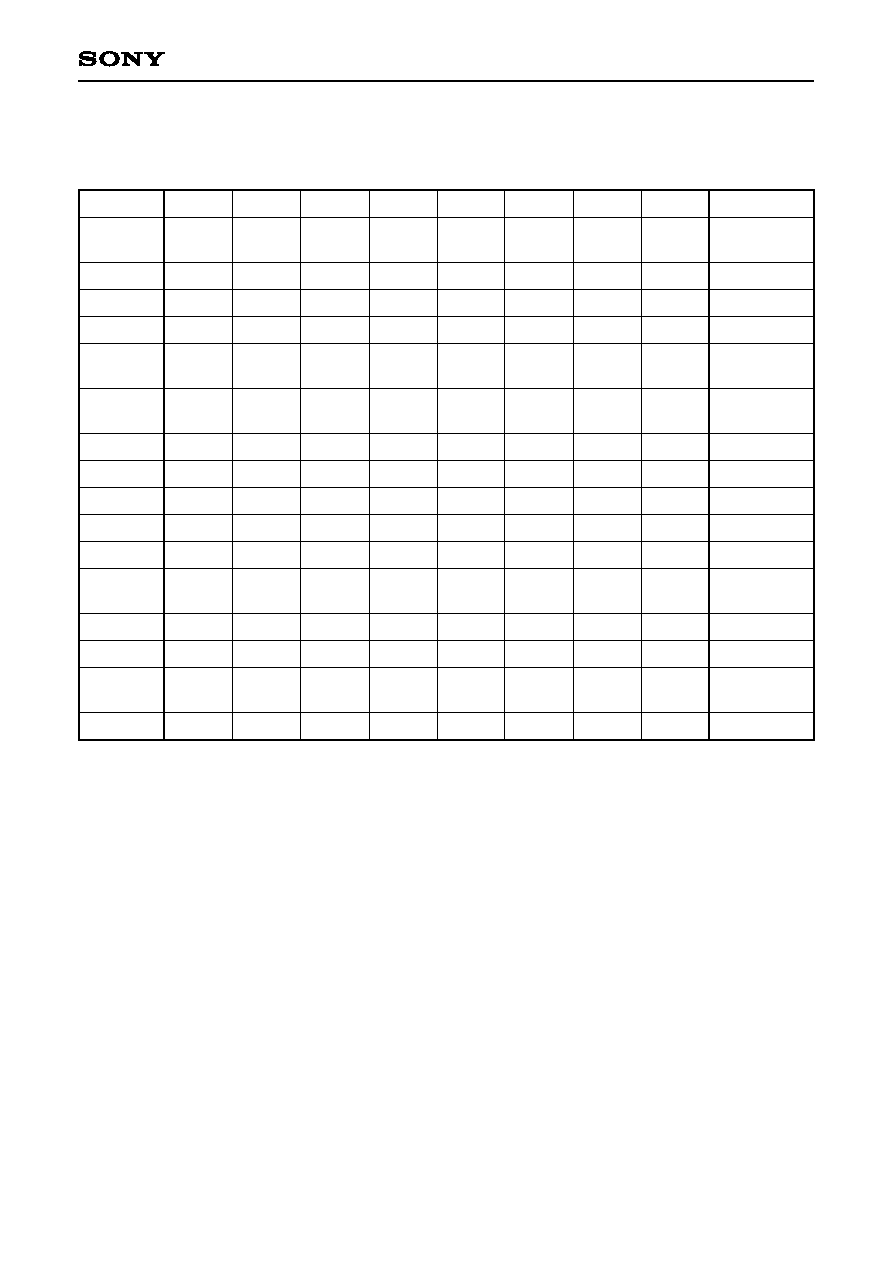

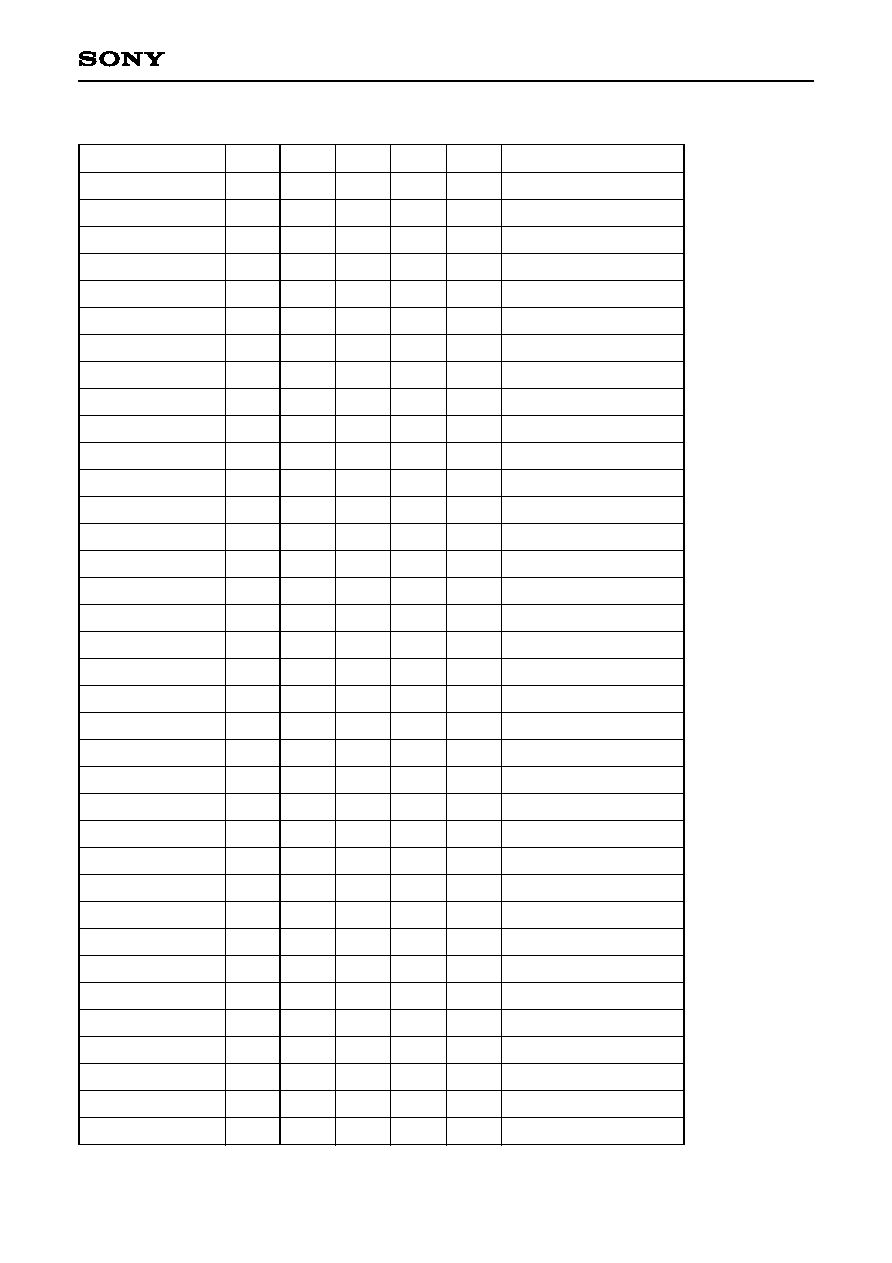

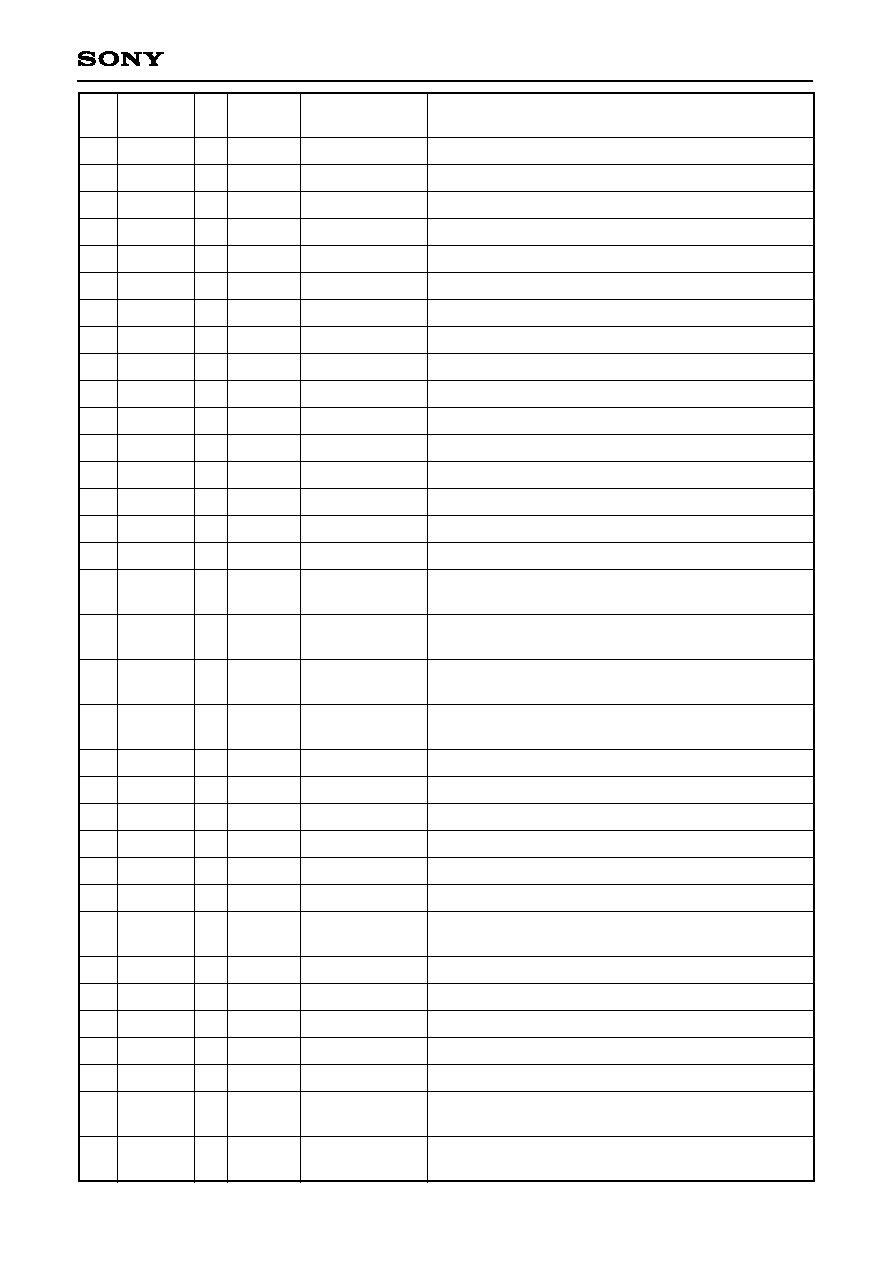

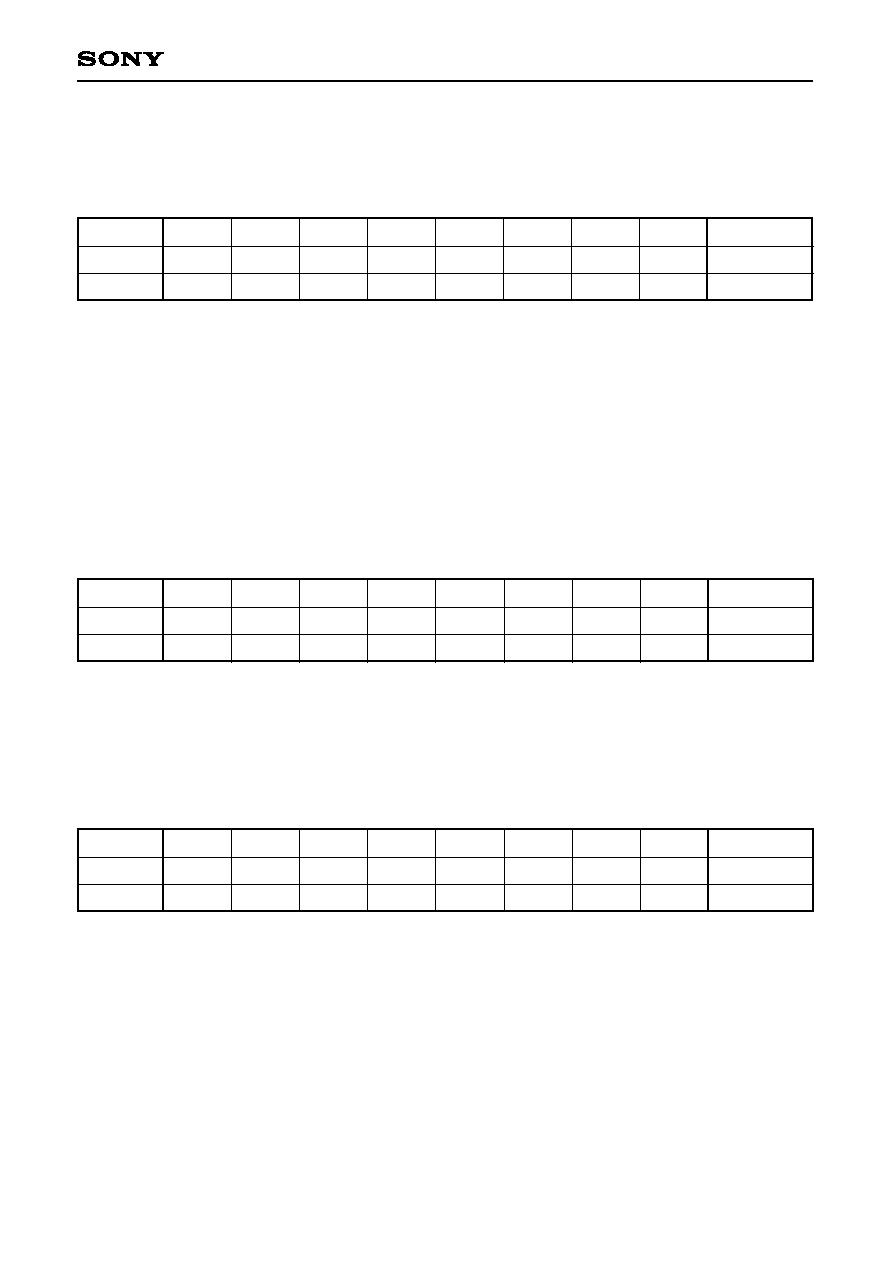

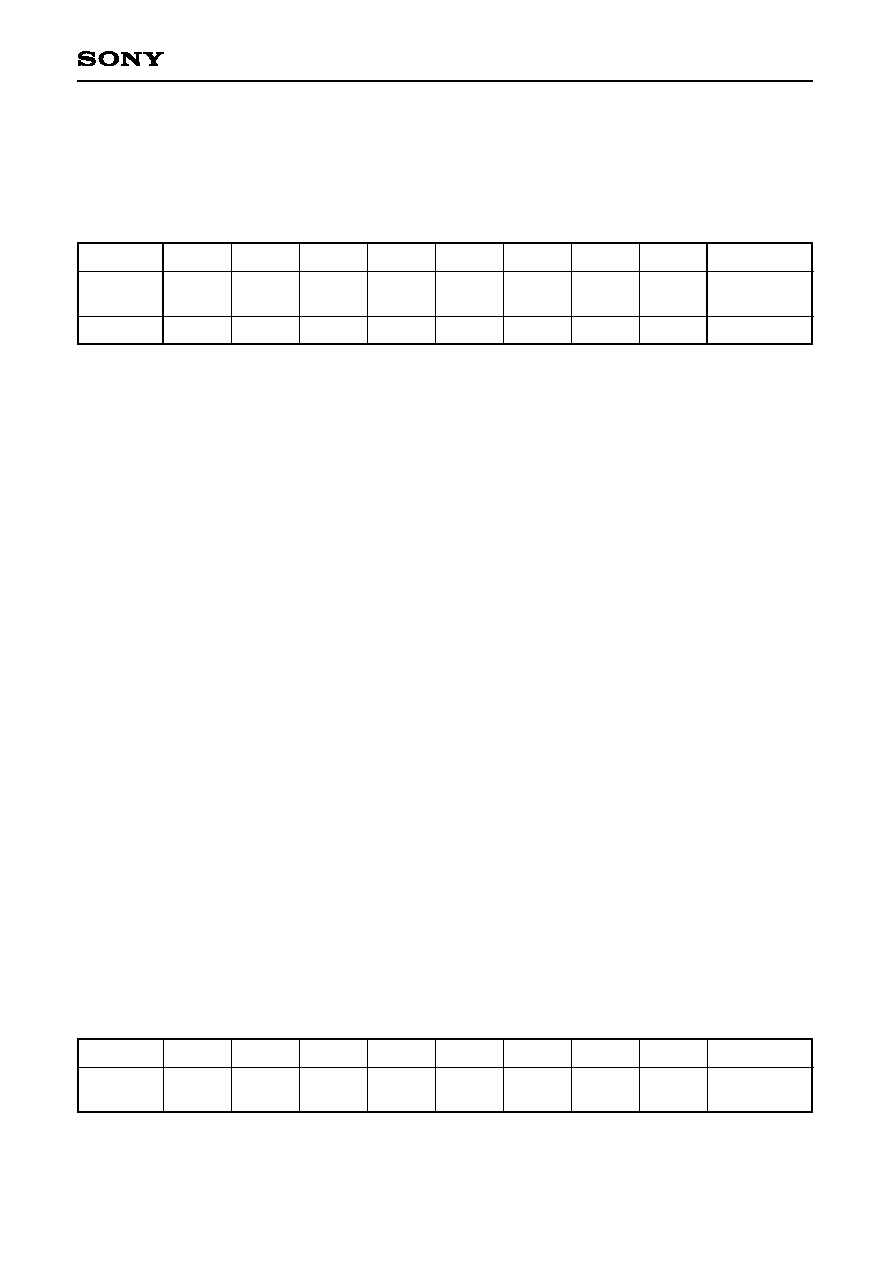

≠ 7 ≠

CXD1818R

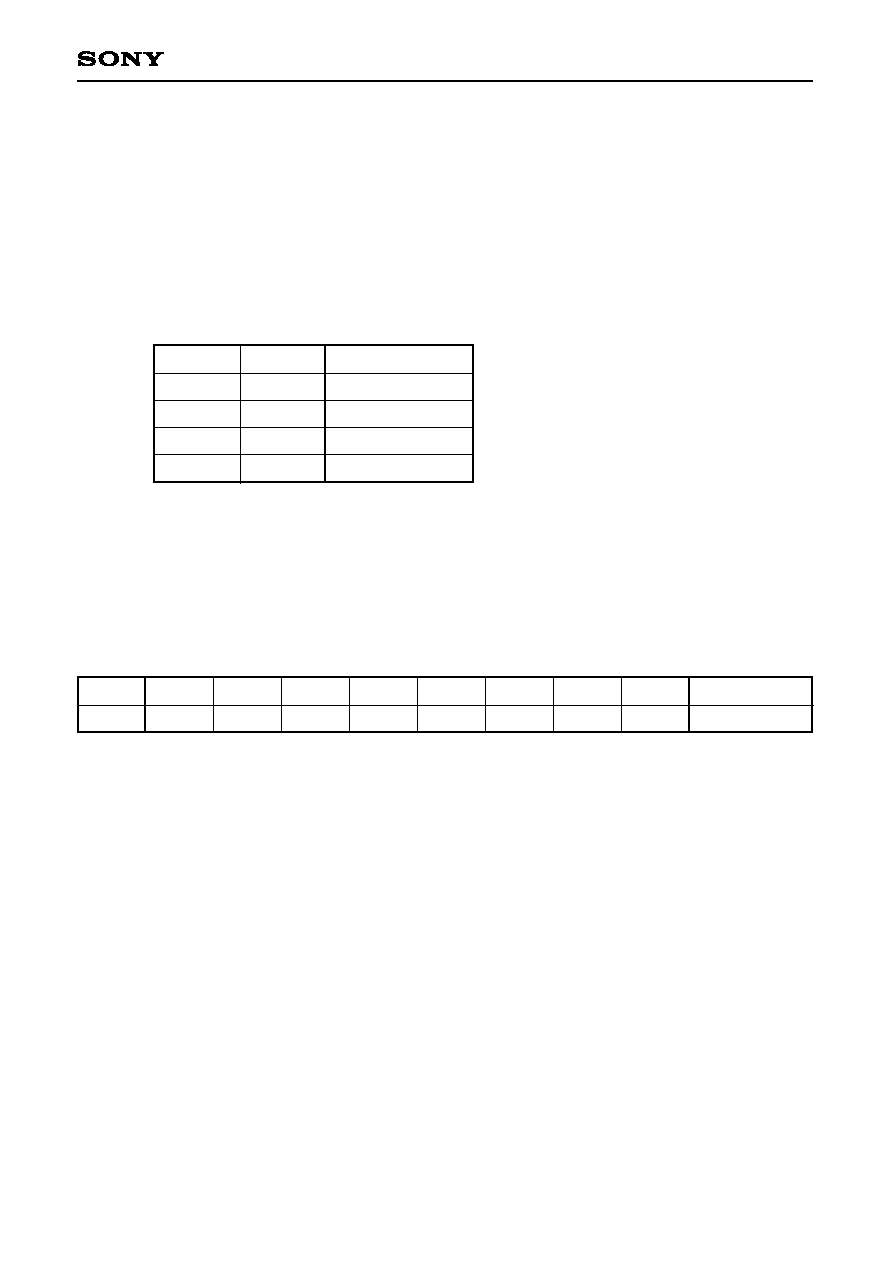

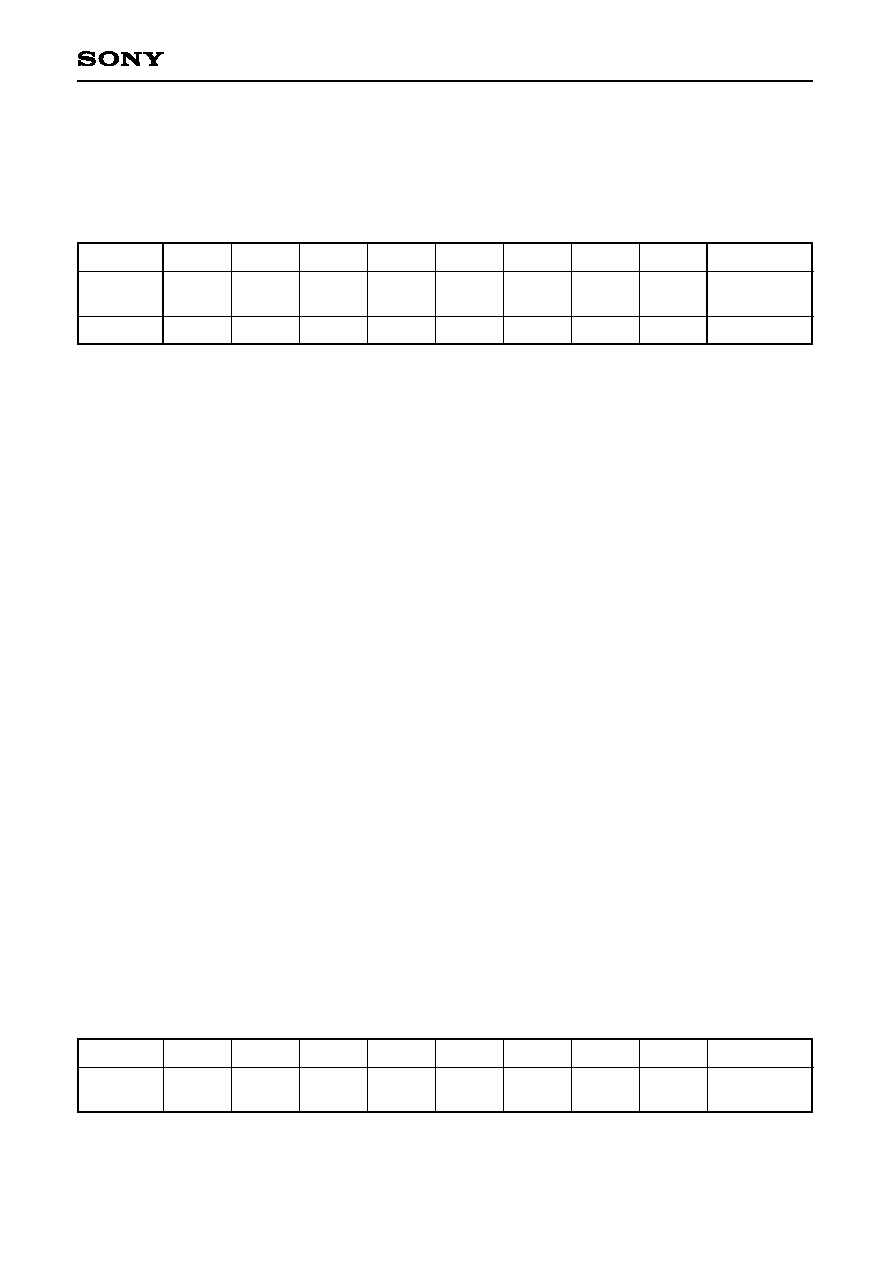

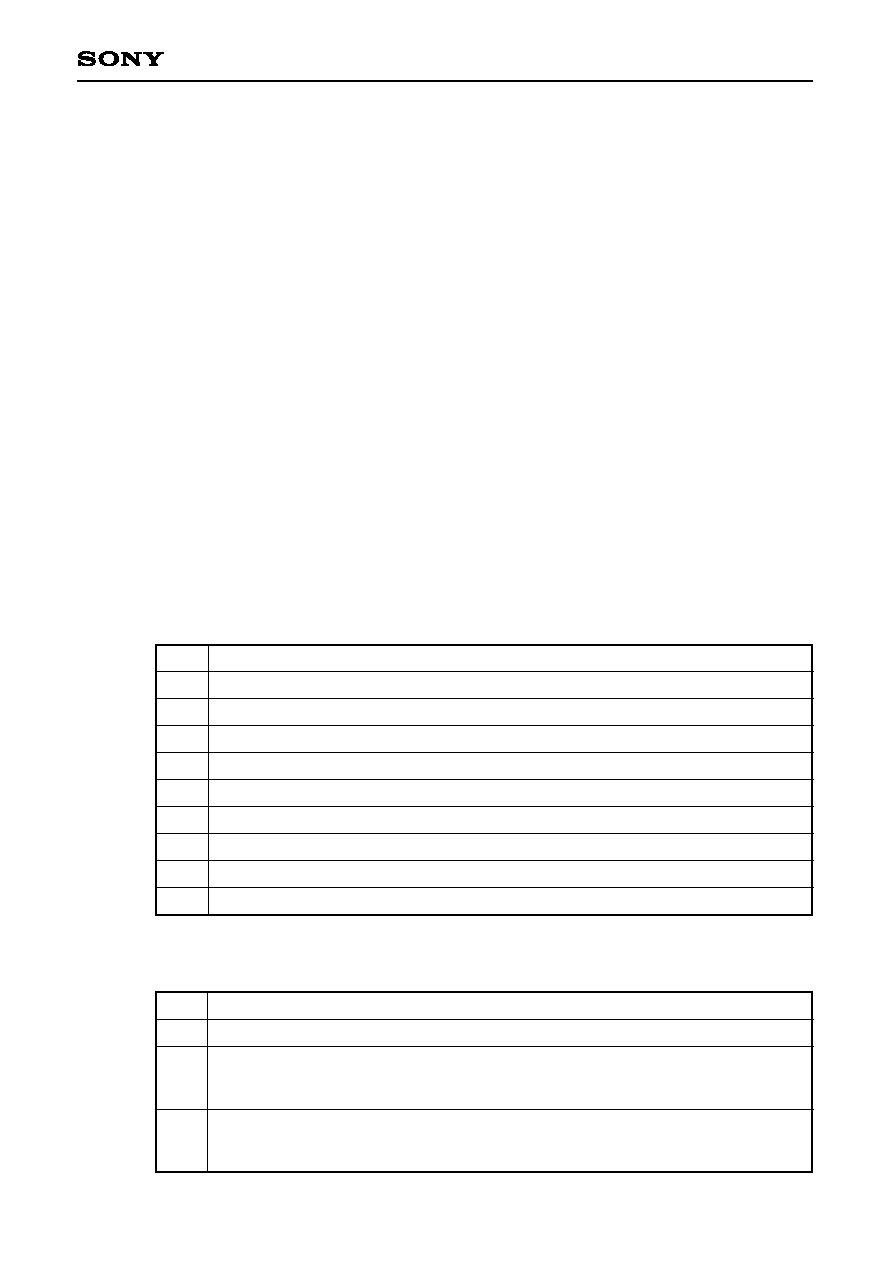

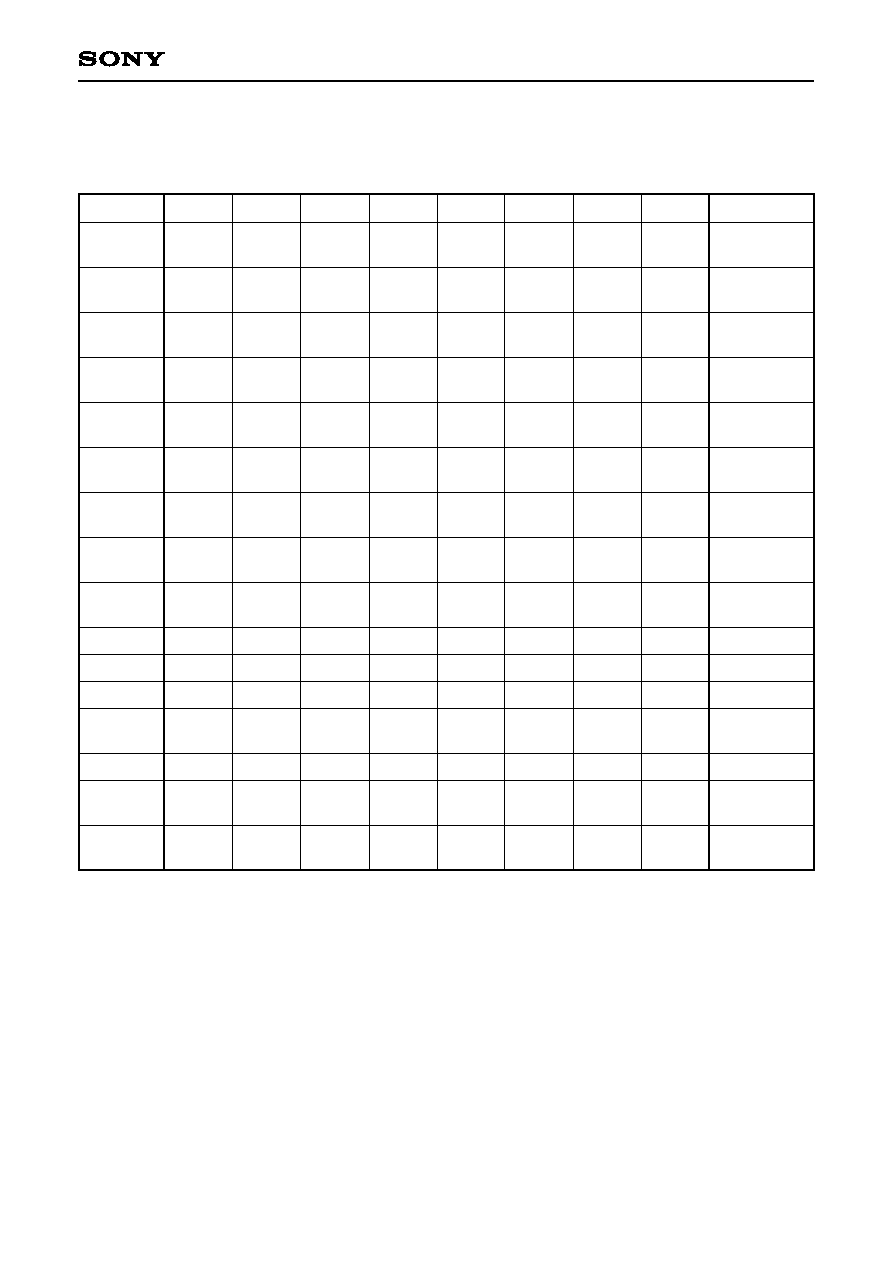

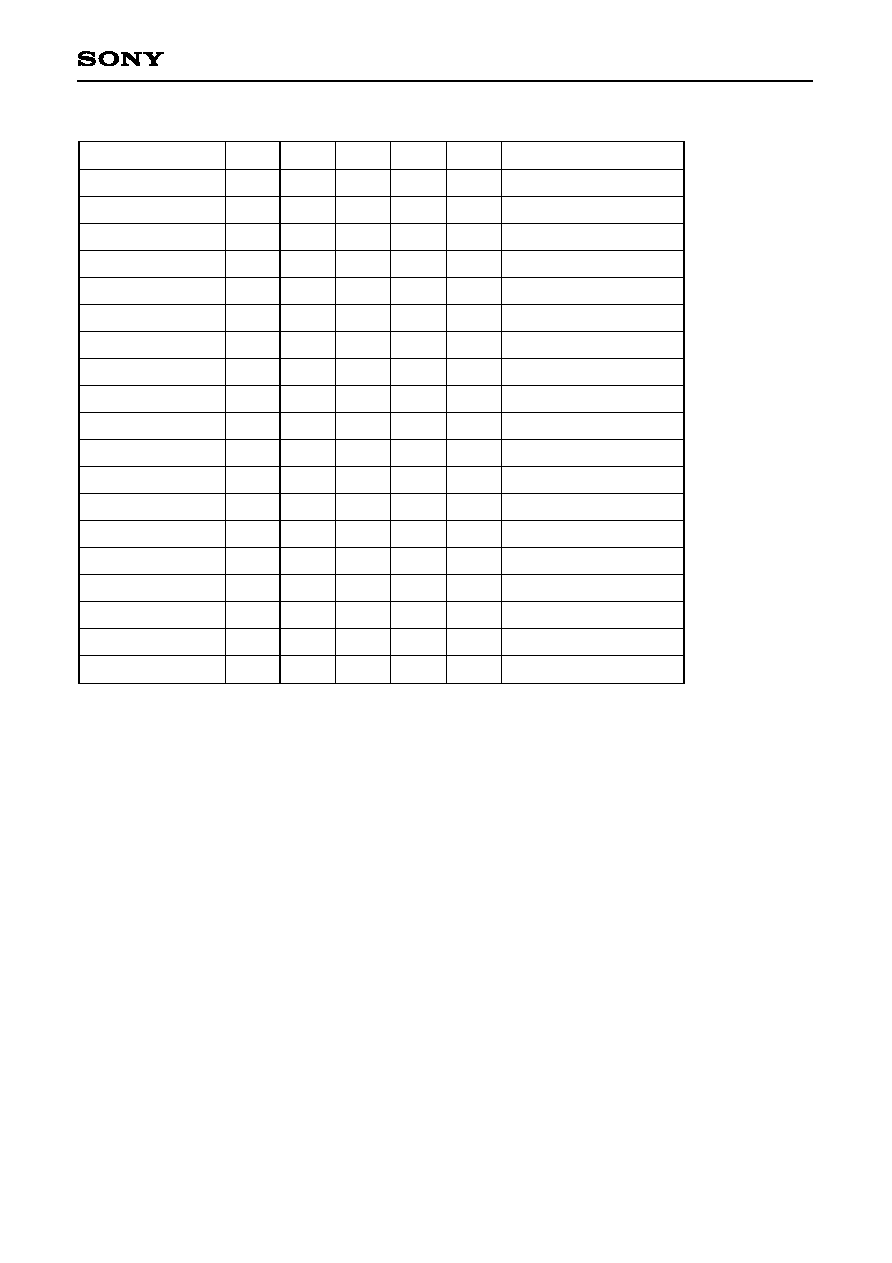

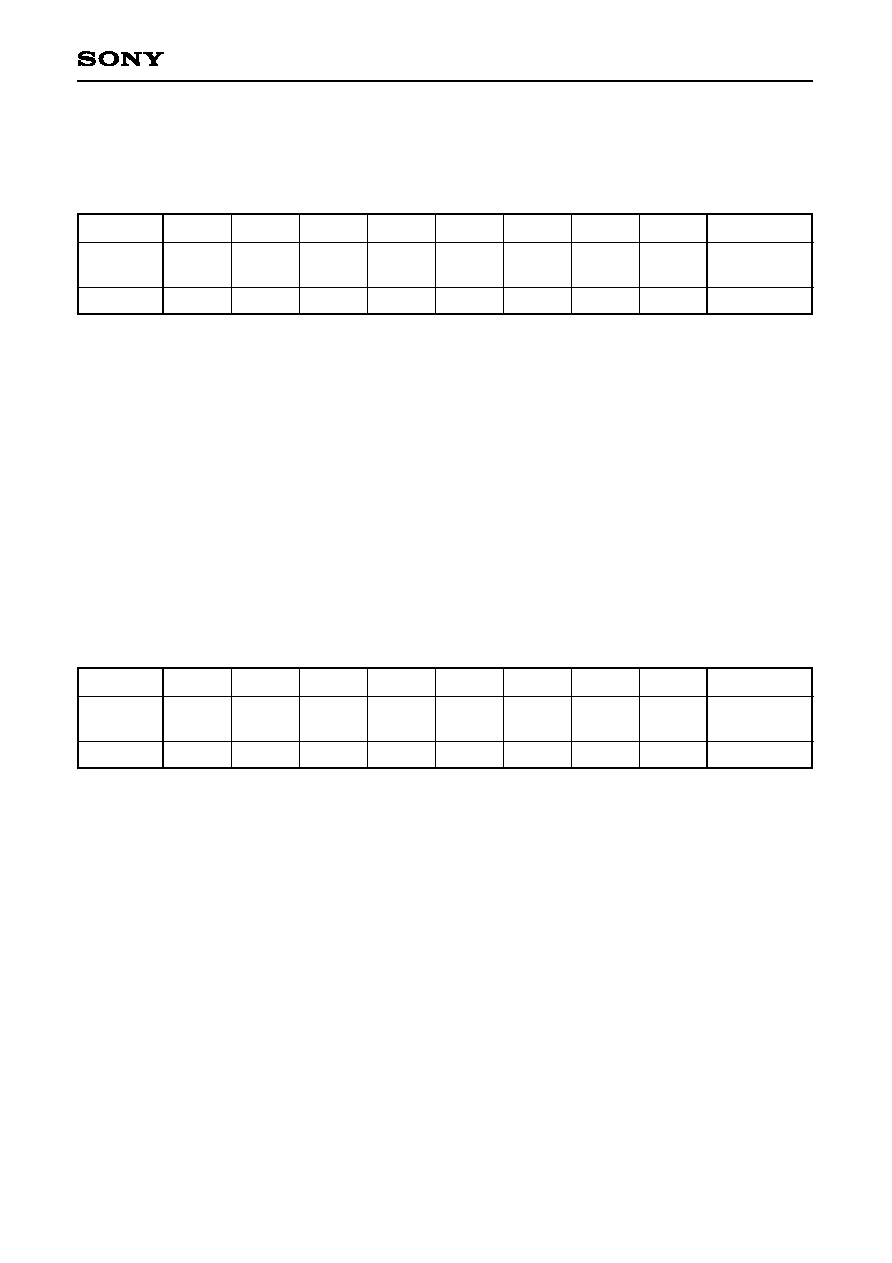

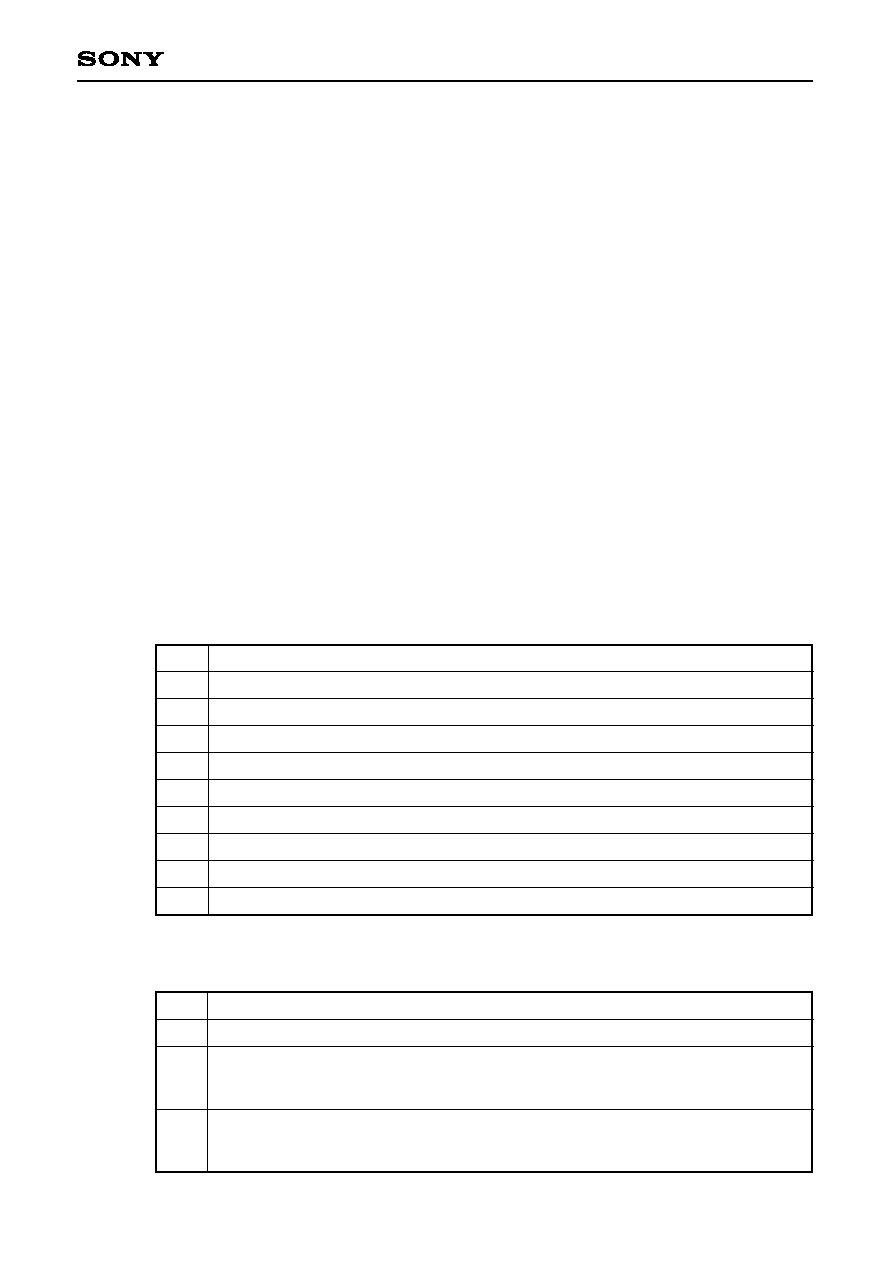

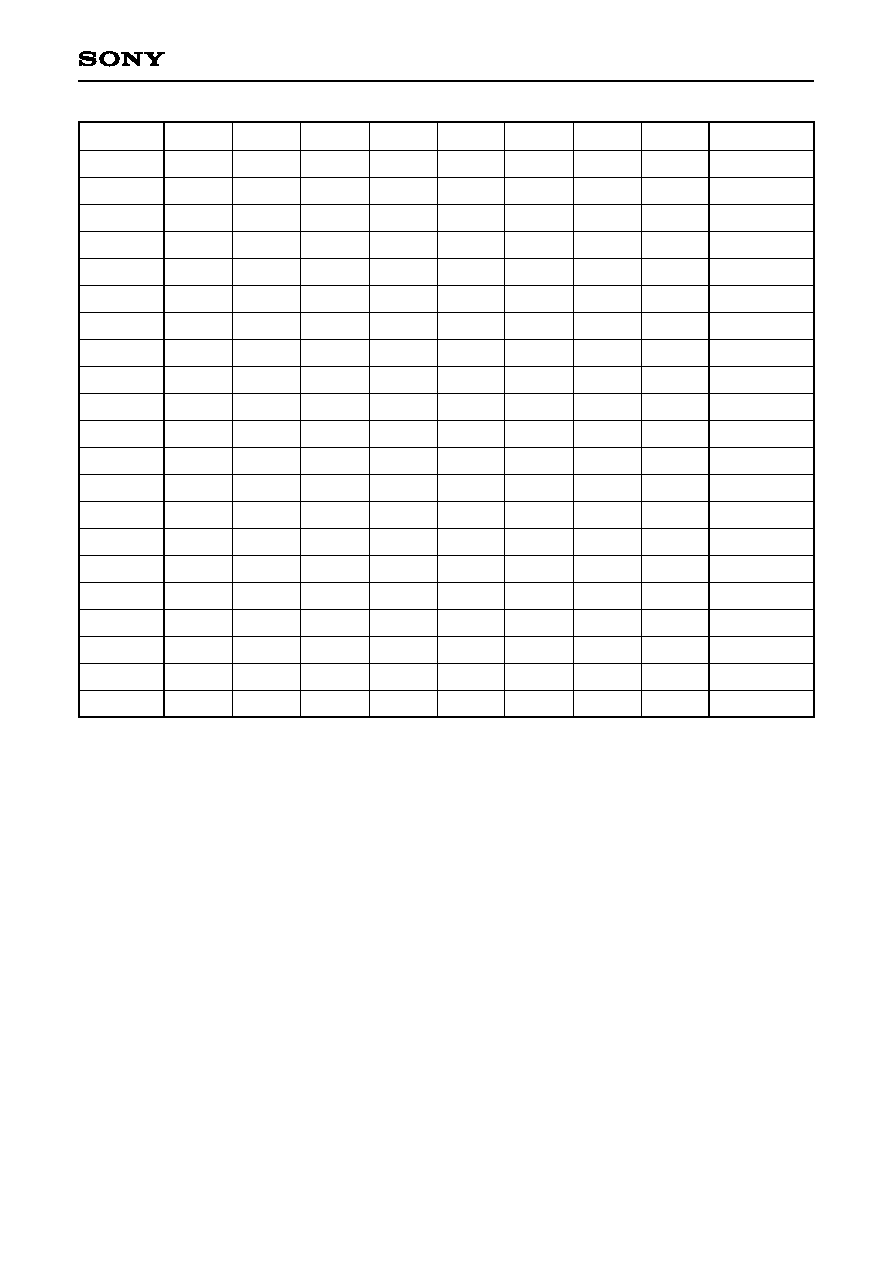

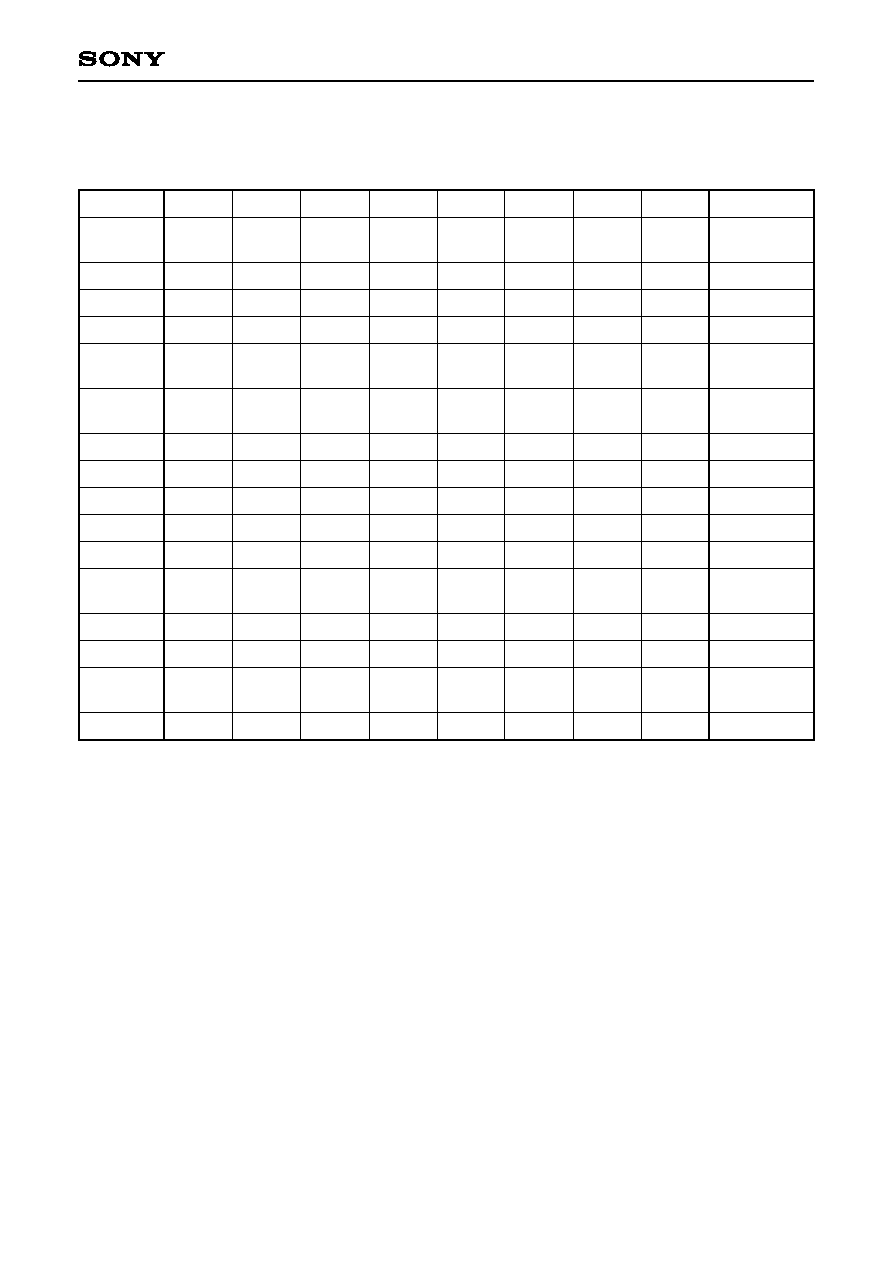

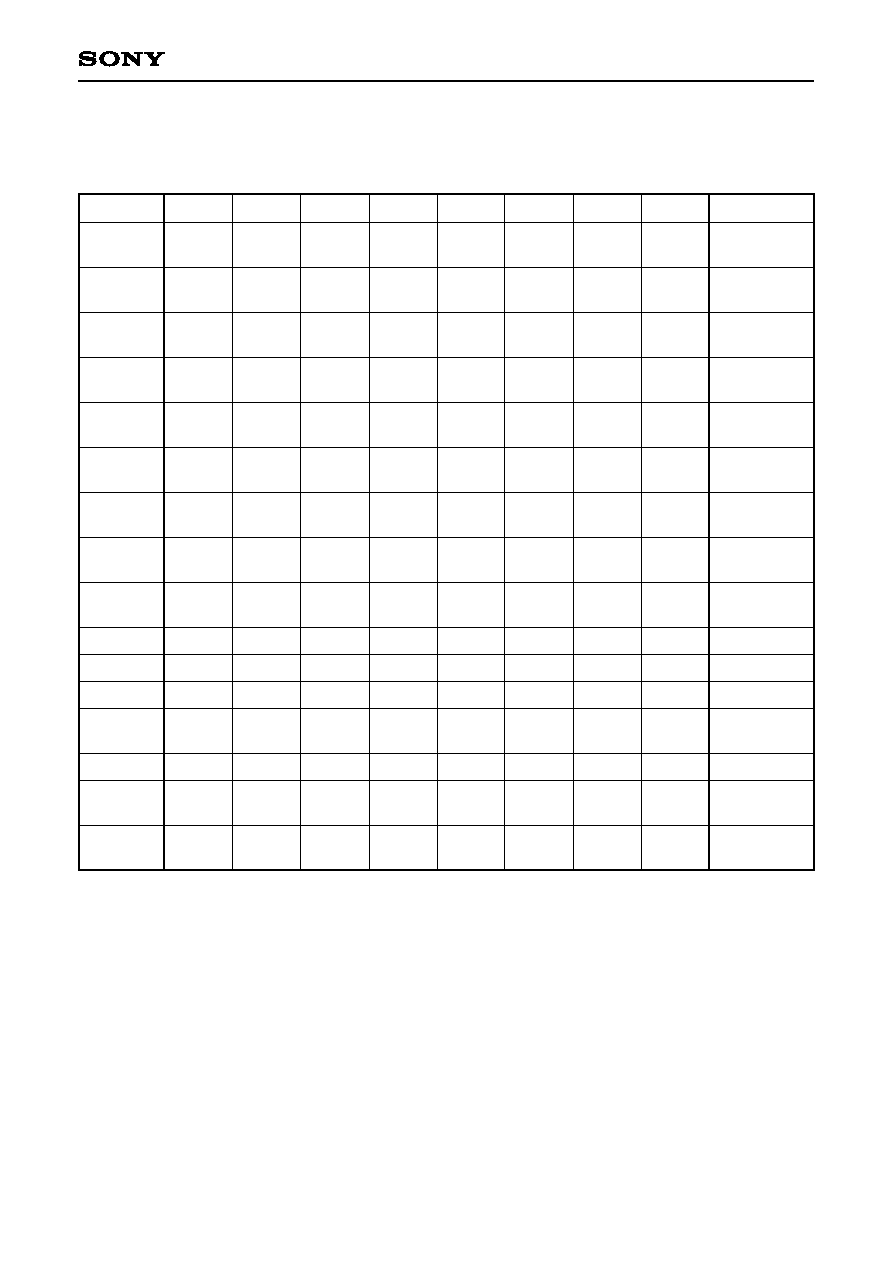

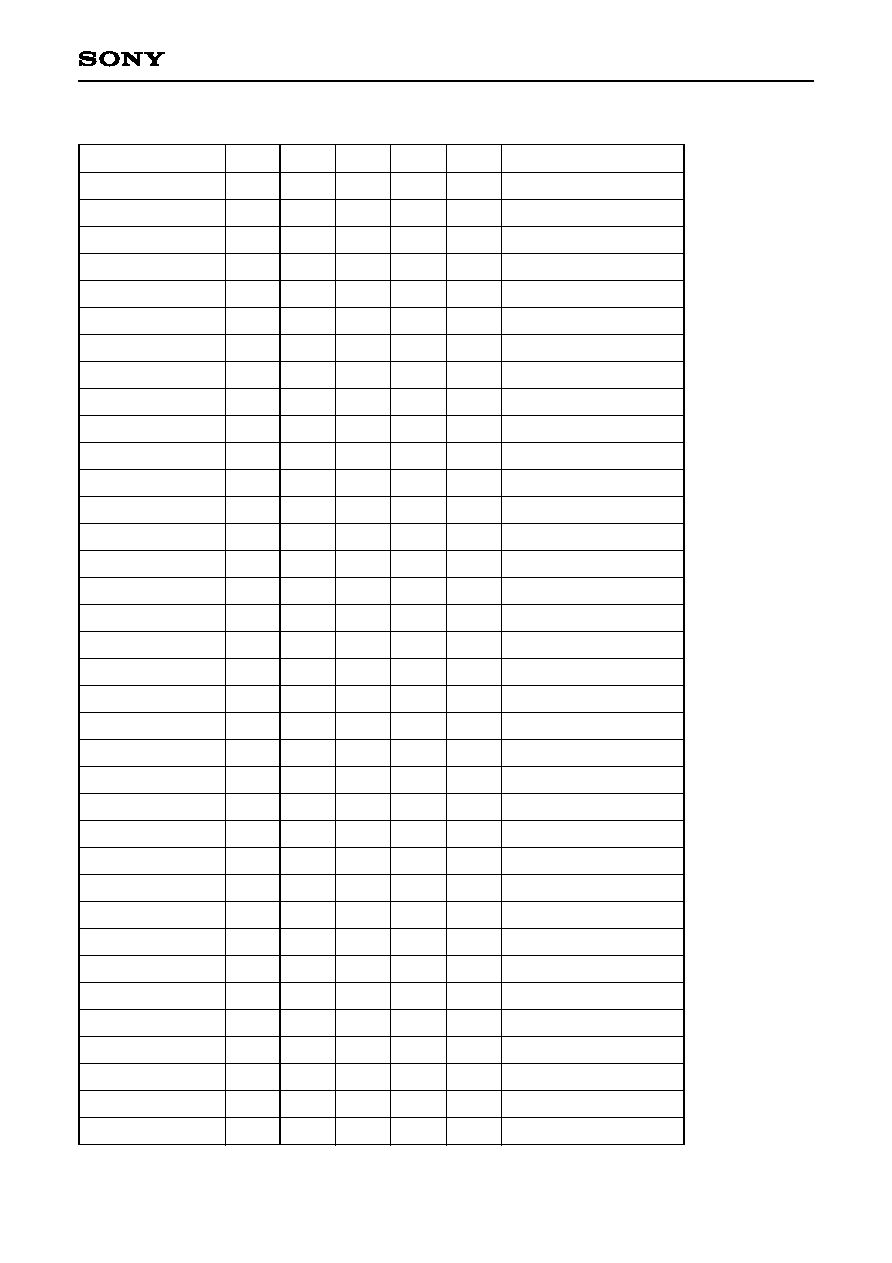

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

I/O

I/O

I/O

I/O

I/O

--

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

--

--

O

I

I

I

I

I

I

I

--

I

I

O

O

O

--

--

O

O

--

--

--

--

--

--

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

Power

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

BufMem I/F

Power

Power

CD DSP I/F

CD DSP I/F

CD DSP I/F

CD DSP I/F

CD DSP I/F

CD DSP I/F

CD DSP I/F

CD DSP I/F

Power

CD DSP I/F

CD DSP I/F

CD DSP I/F

CD DSP I/F

CD DSP I/F

Power

Power

CD DSP I/F

CD DSP I/F

Buffer memory data bus bit 3

Buffer memory data bus bit 4

Buffer memory data bus bit 5

Buffer memory data bus bit 6

Buffer memory data bus bit 7

V

SS

Buffer memory data bus bit 8

Buffer memory data bus bit 9

Buffer memory data bus bit 10

Buffer memory data bus bit 11

Buffer memory data bus bit 12

Buffer memory data bus bit 13

Buffer memory data bus bit 14

Buffer memory data bus bit 15

V

SS

V

DD

SBIN readout clock

(connected to the EXCK pin (Pin 65) of the CXD3000)

Subcode serial signal

(connected to the SBSO pin (Pin 64) of the CXD3000)

Subcode sync signal

(connected to the SCOR pin (Pin 63) of the CXD3000)

Write frame clock

(connected to the WFCK pin (Pin 62) of the CXD3000)

C2 pointer signal. Indicates that an error exists in MDAT.

Bit clock. MDAT strobe signal

Serial data stream from CD DSP

LR signal. Indicates MDAT left or right channel

V

SS

DSP crystal input

SCOR synchronized with DSP data output

(connected to the GRSCOR pin (Pin 113) of the CXD3000)

Serial data output from sub CPU to CD DSP

DATO latch signal. Latched at the rising edge.

DATO transfer clock

V

SS

V

DD

Bit clock

(connected to the BCKI pin (Pin 30) of the CXD3000)

Audio data output to DAC

(connected to the PCMDI pin (Pin 28) of the CXD3000)

MDB3

MDB4

MDB5

MDB6

MDB7

V

SS

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

V

SS

V

DD

EXCK

SBIN

SCOR

WFCK

C2PO

BCLK

MDAT

LRCK

V

SS

DSPCK

GSCR

DATO

XLAT

DSTB

V

SS

V

DD

BCKO

DACD

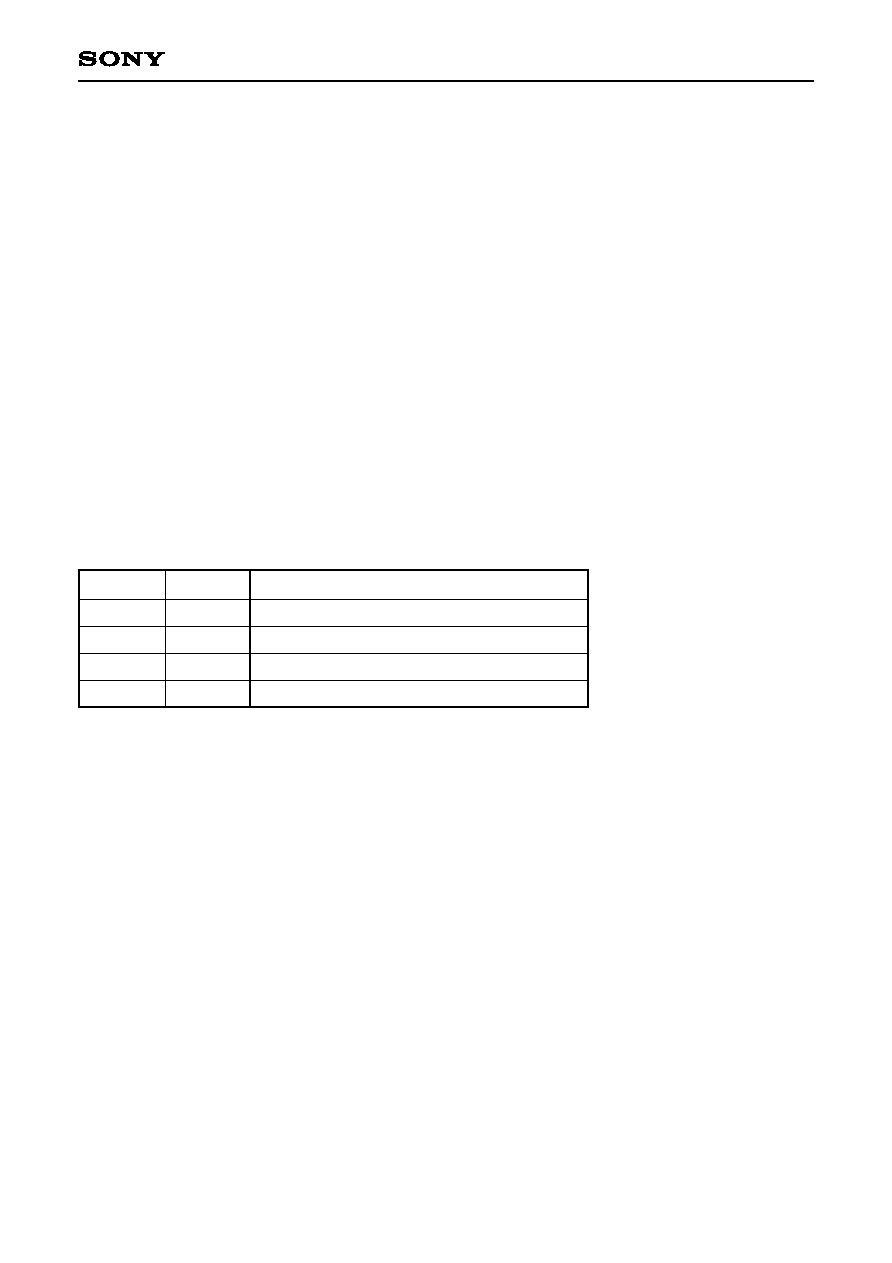

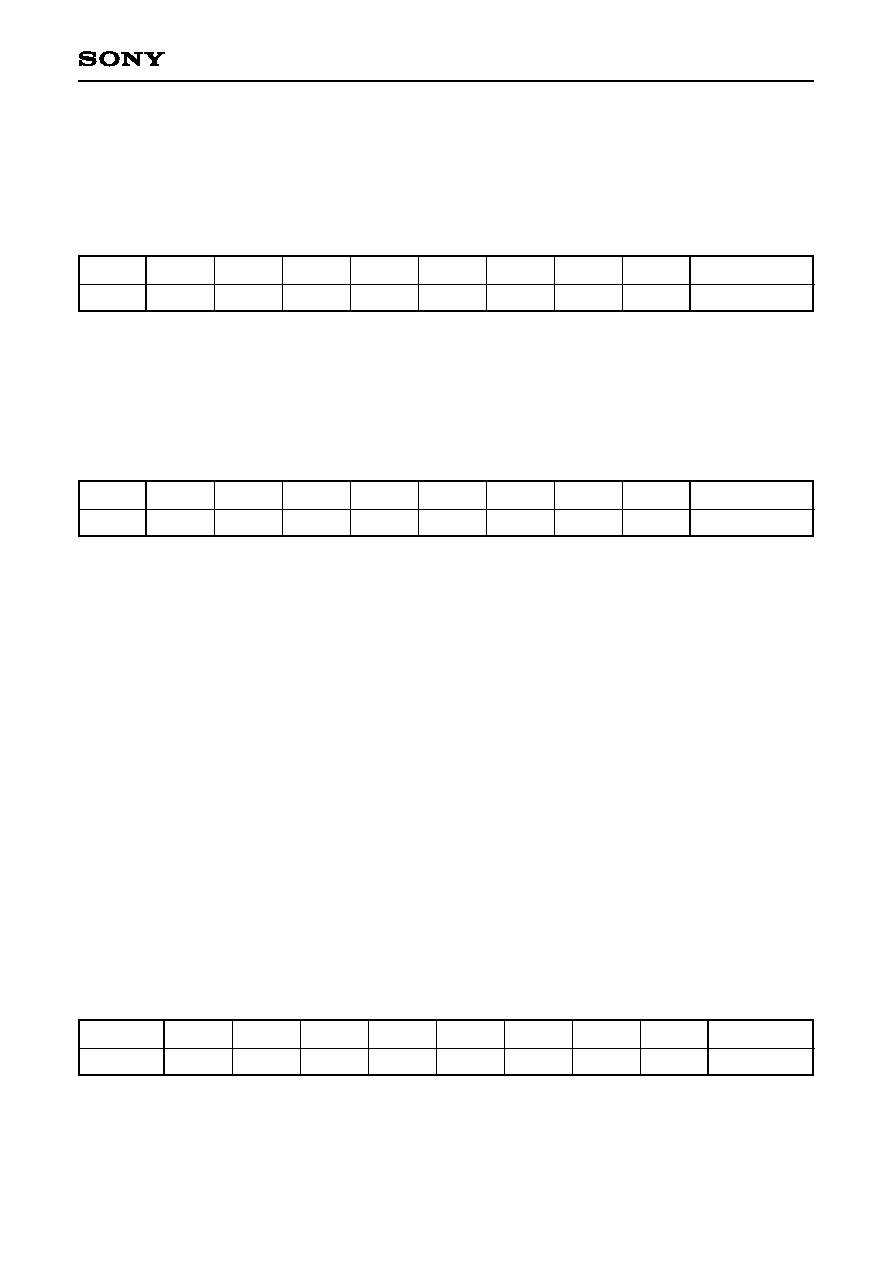

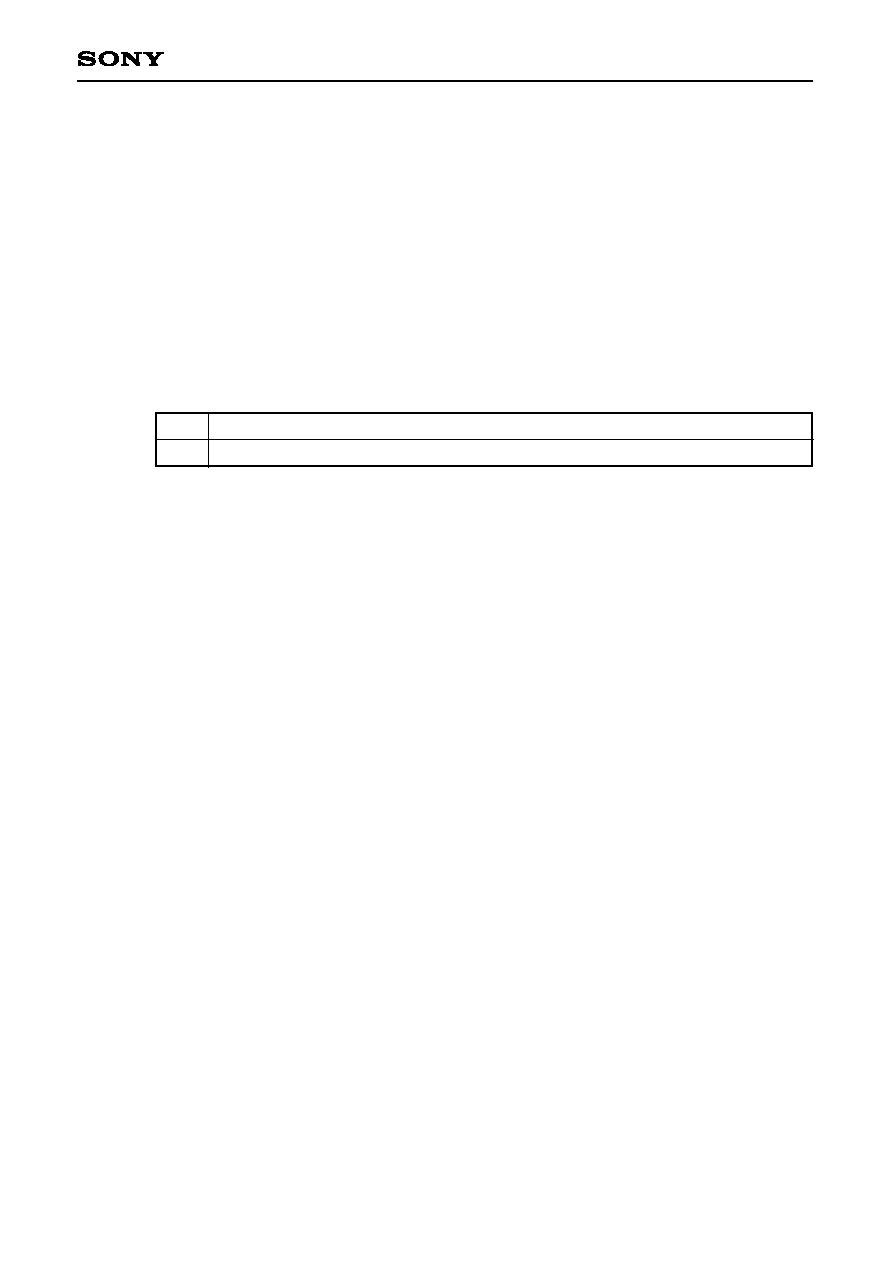

Pin

No.

Symbol

I/O

Logic

Classification

Description

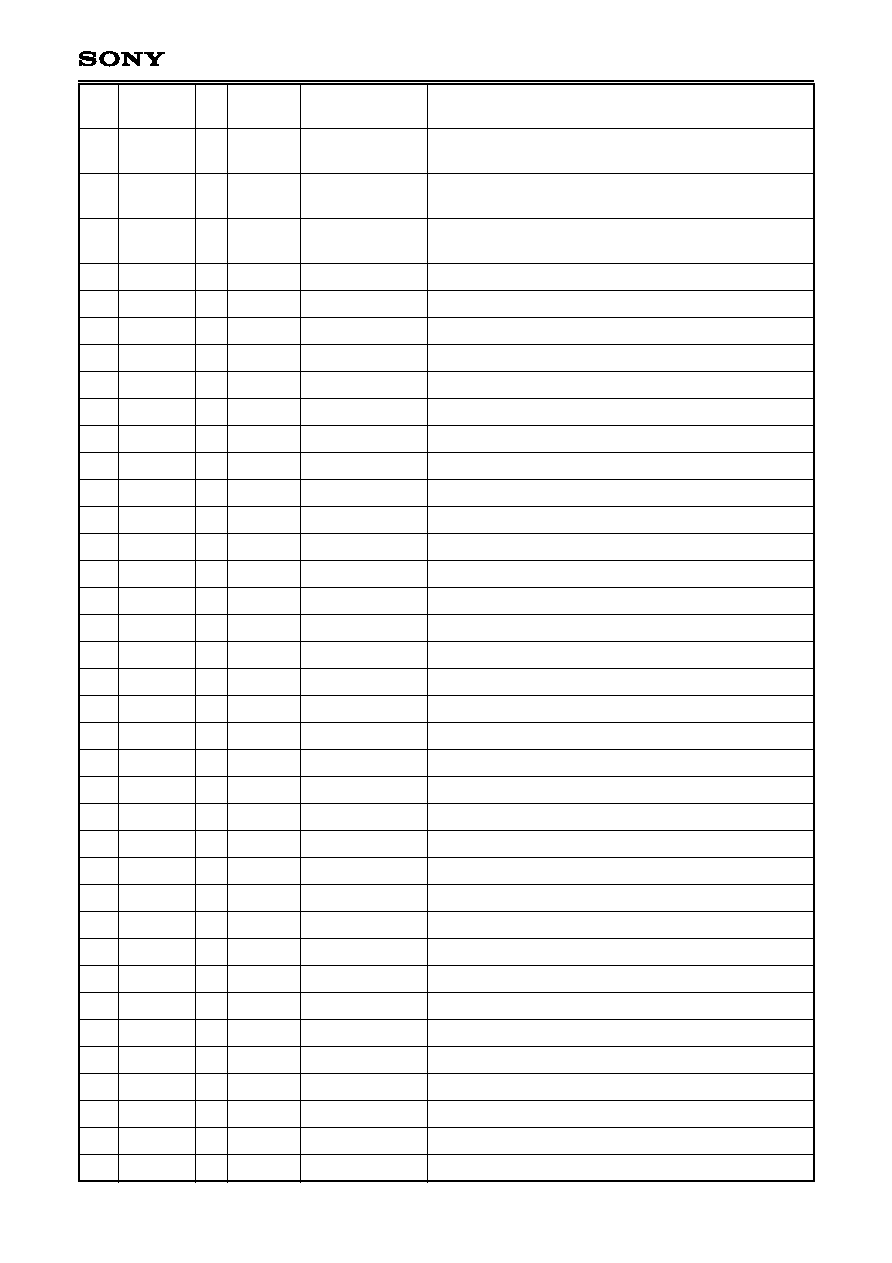

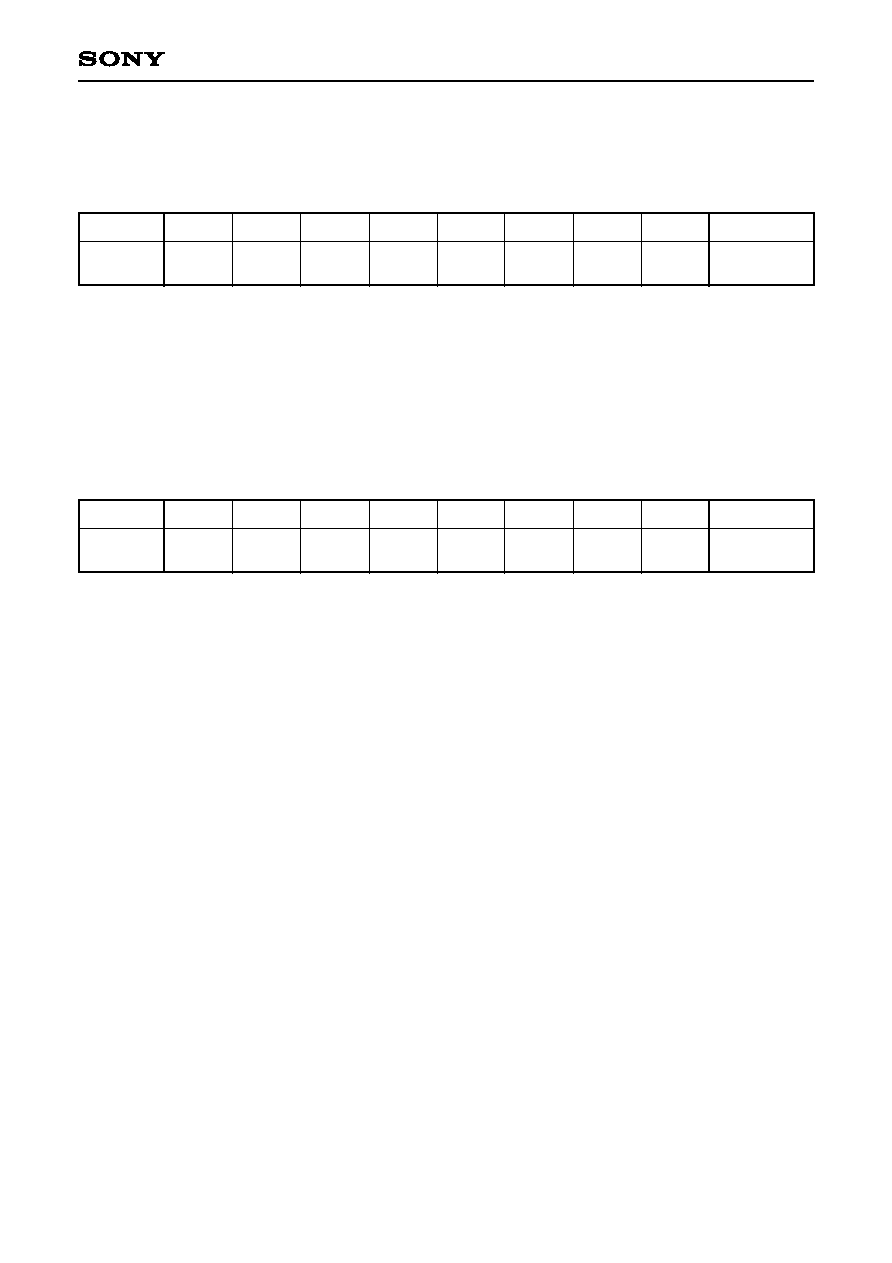

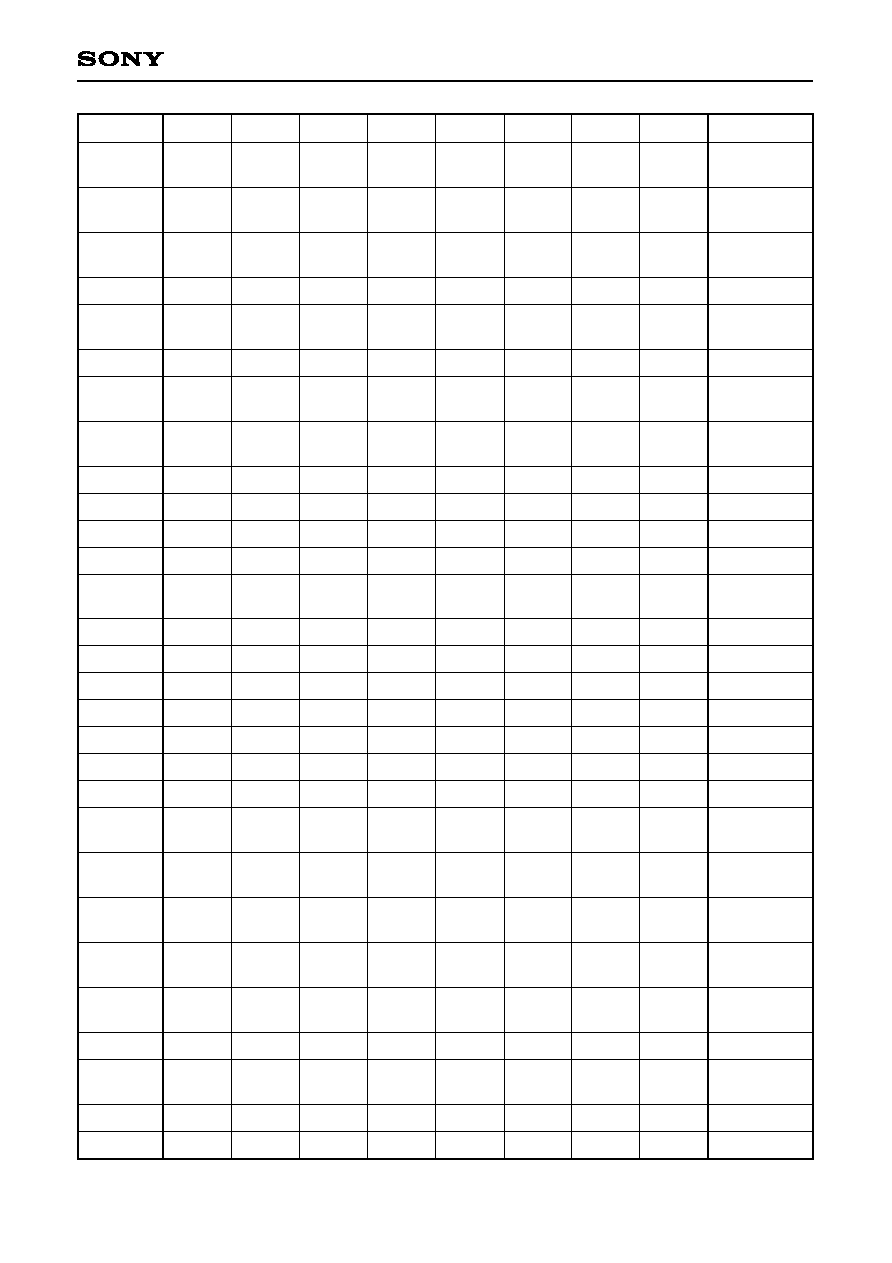

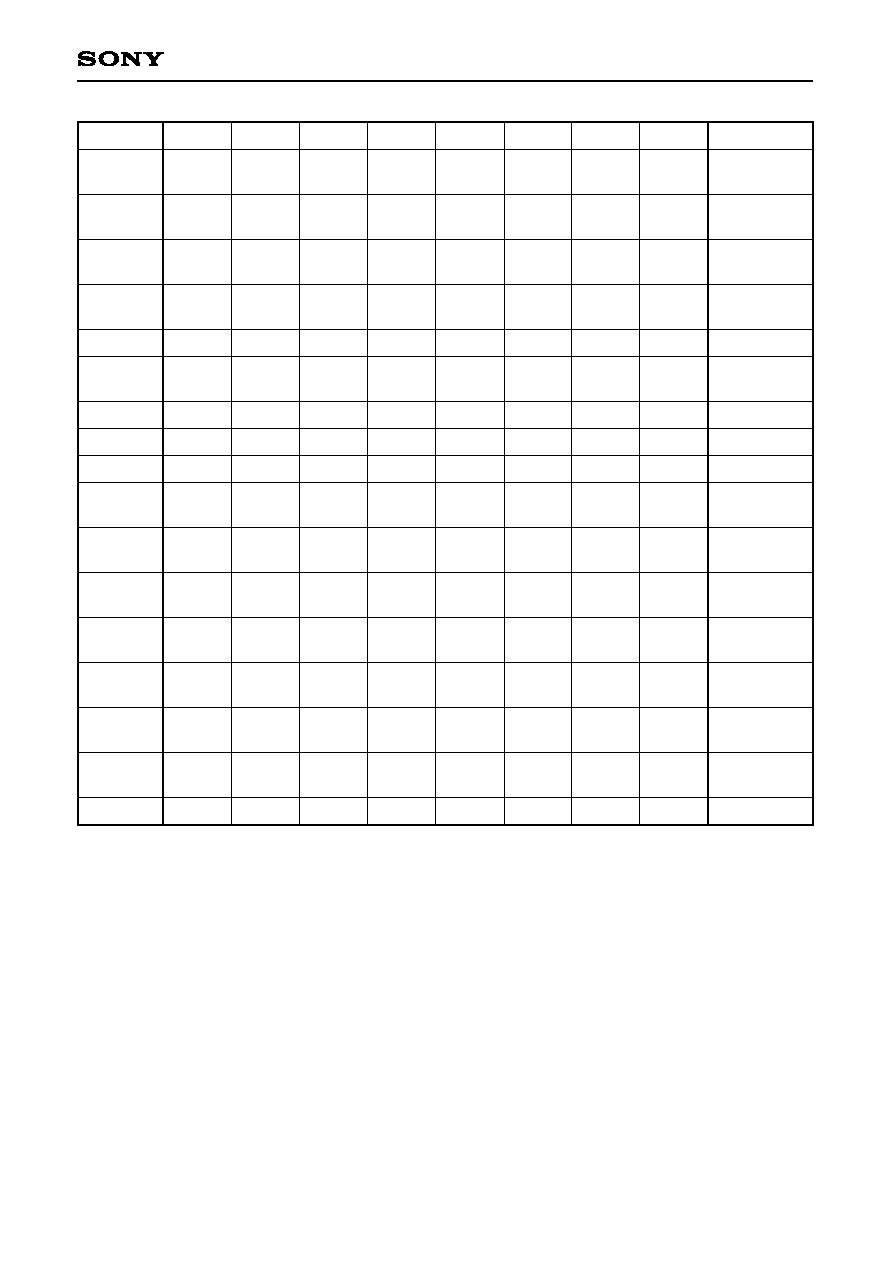

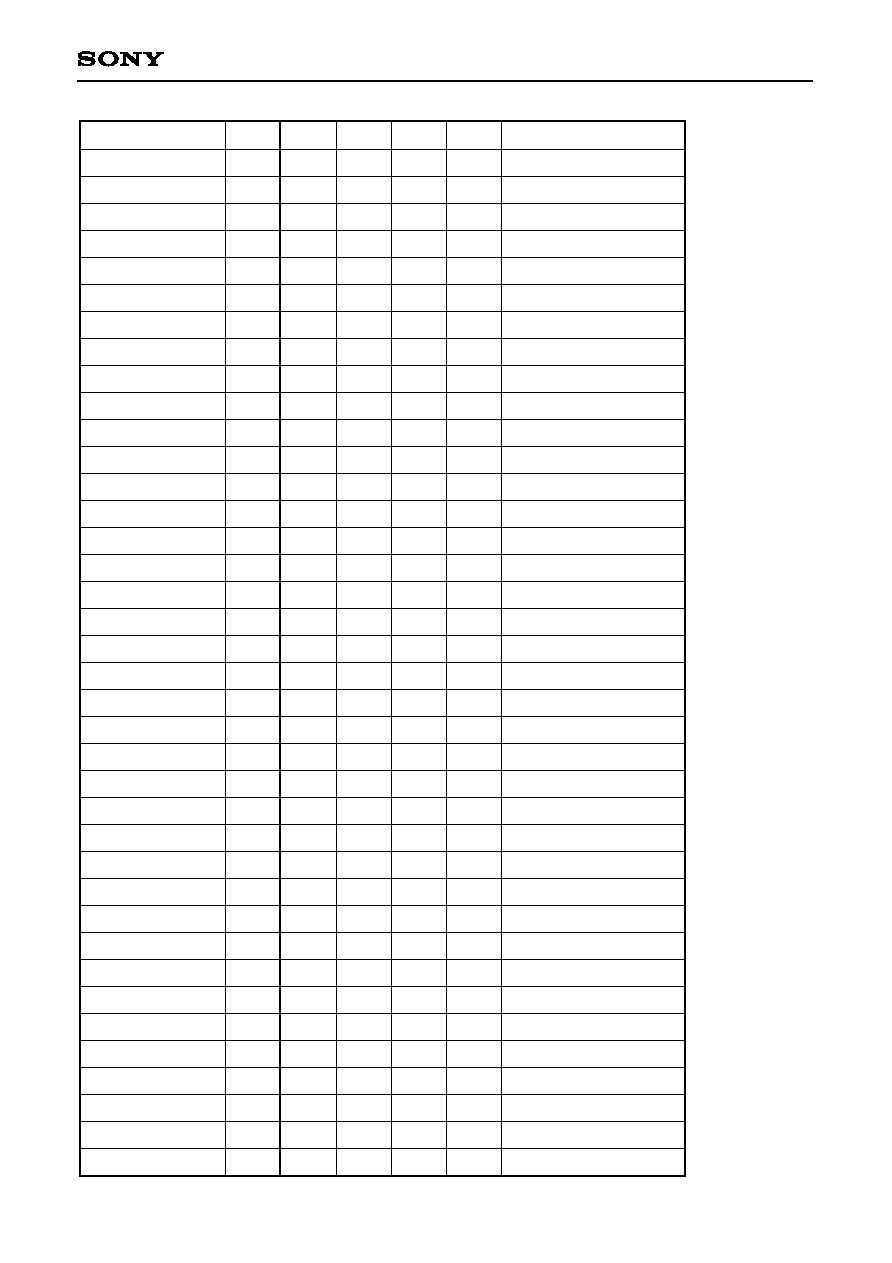

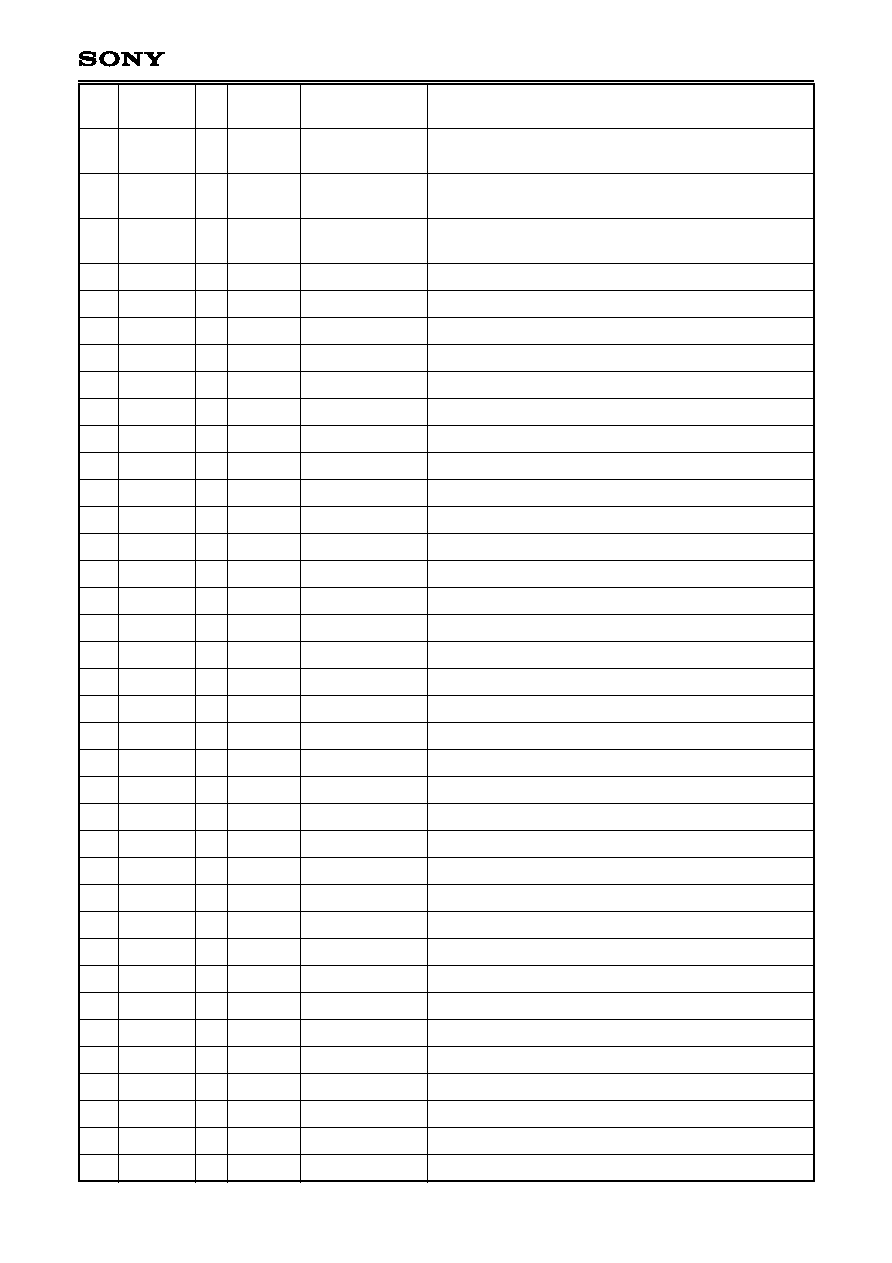

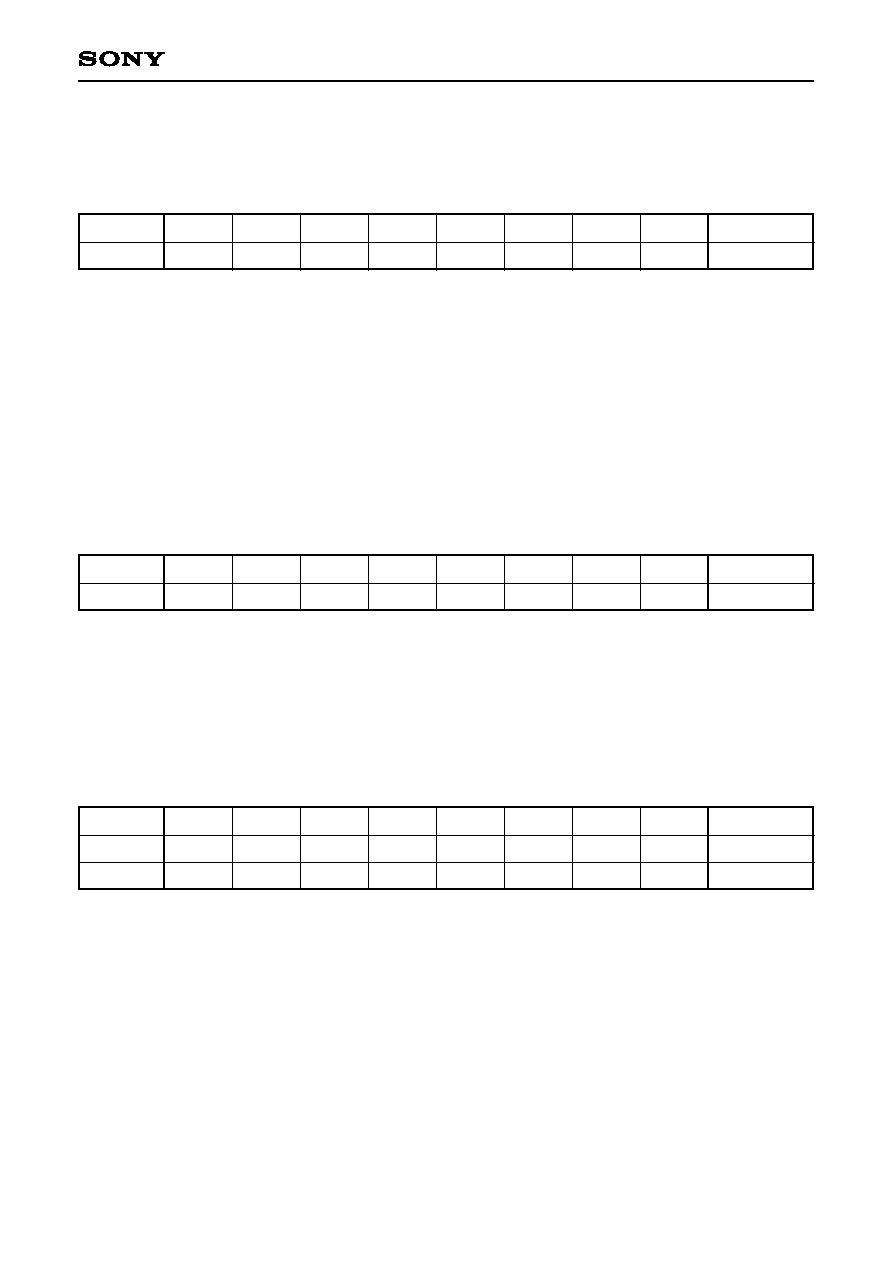

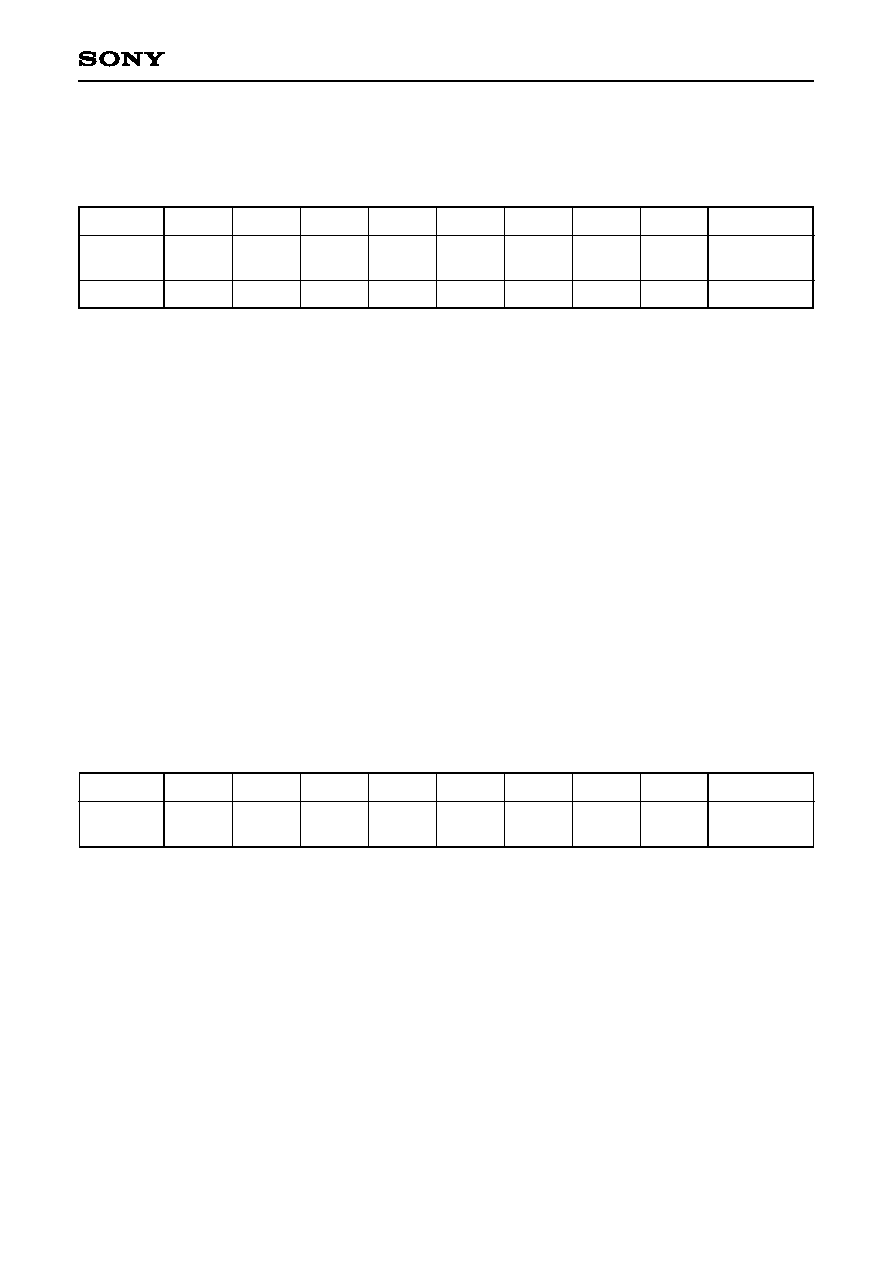

≠ 8 ≠

CXD1818R

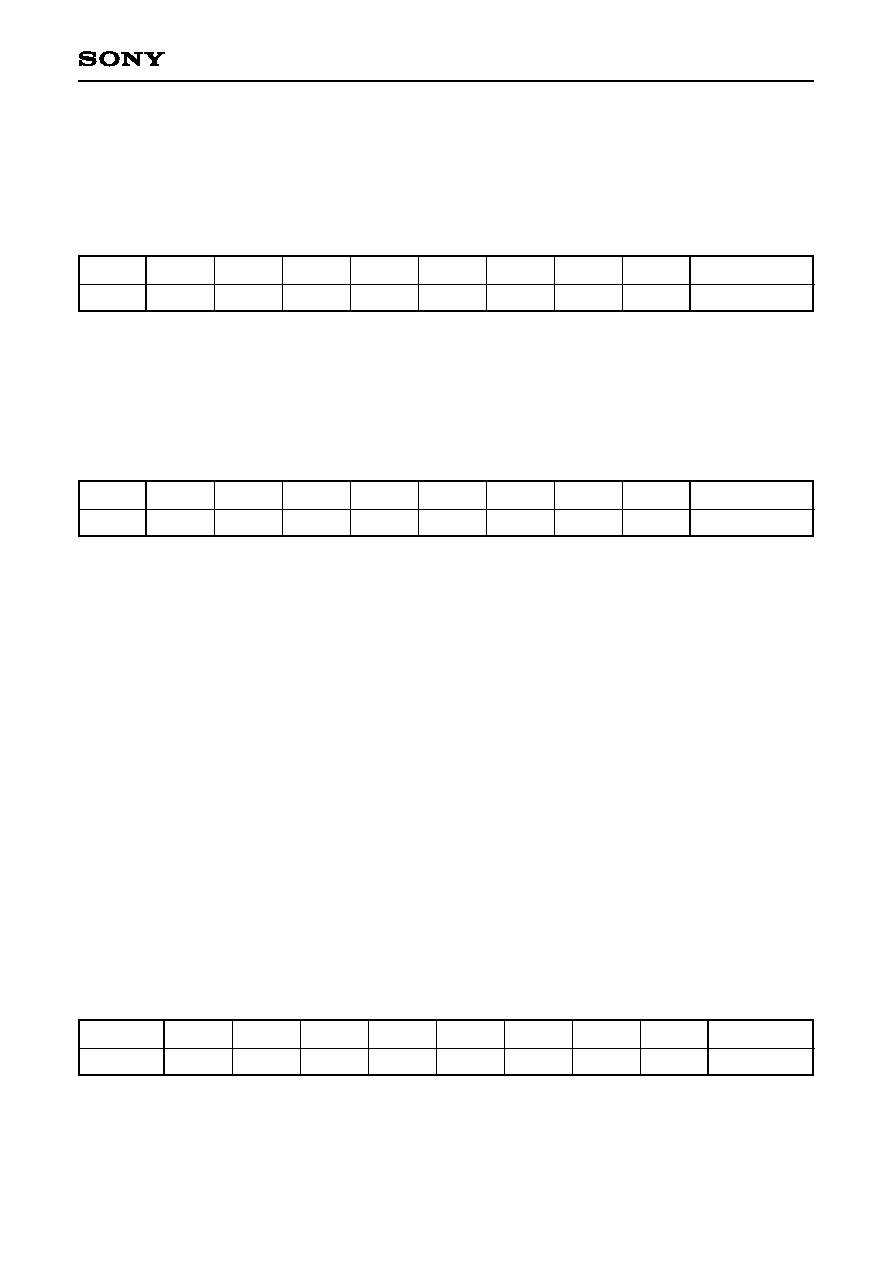

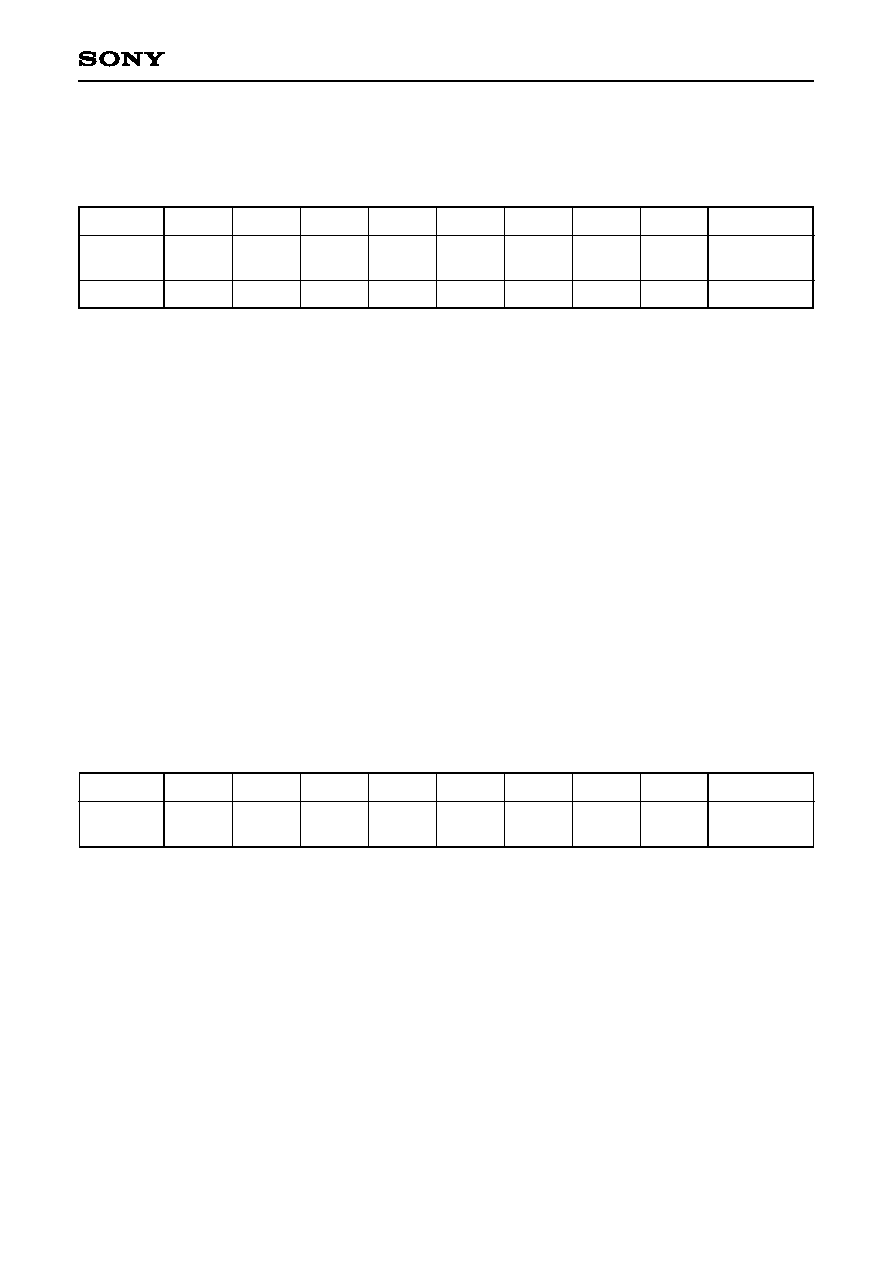

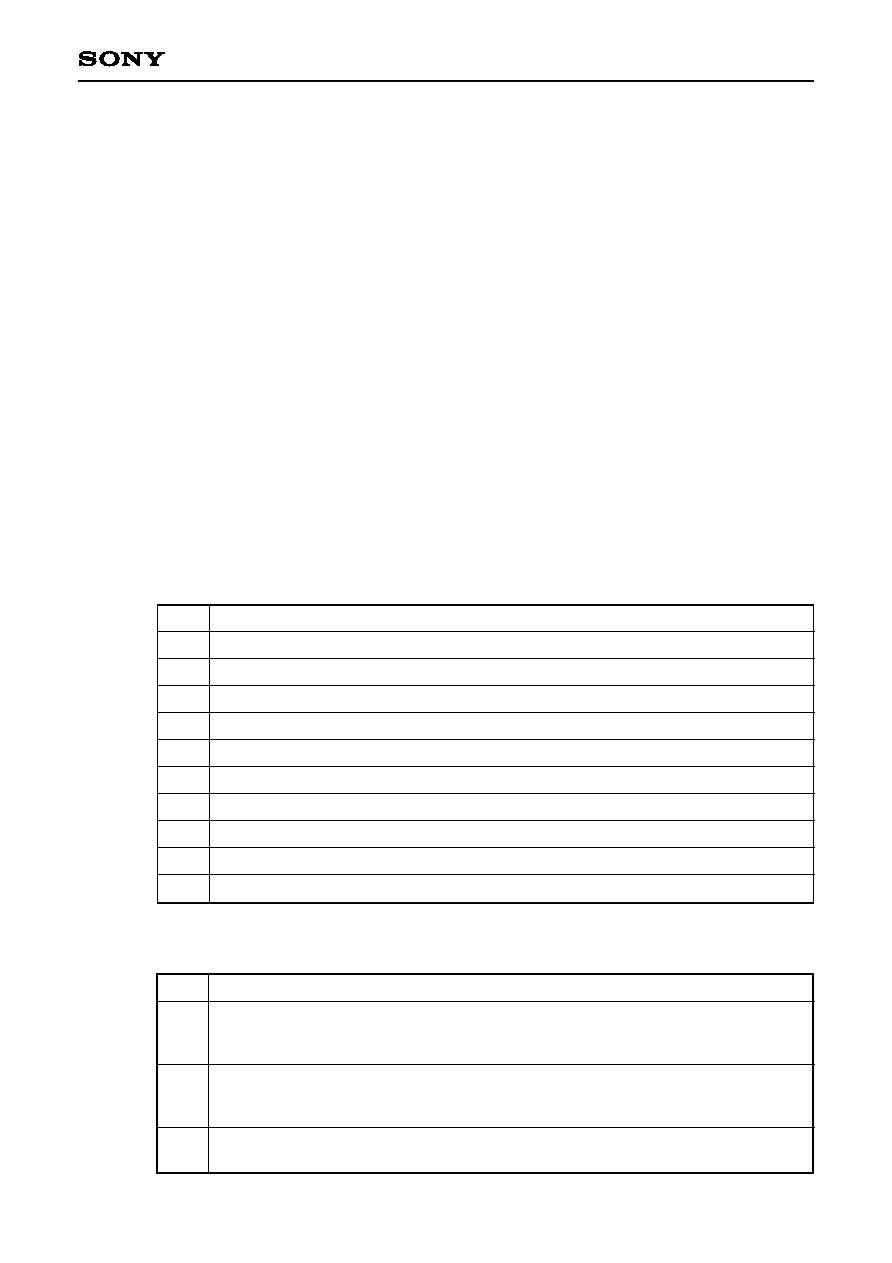

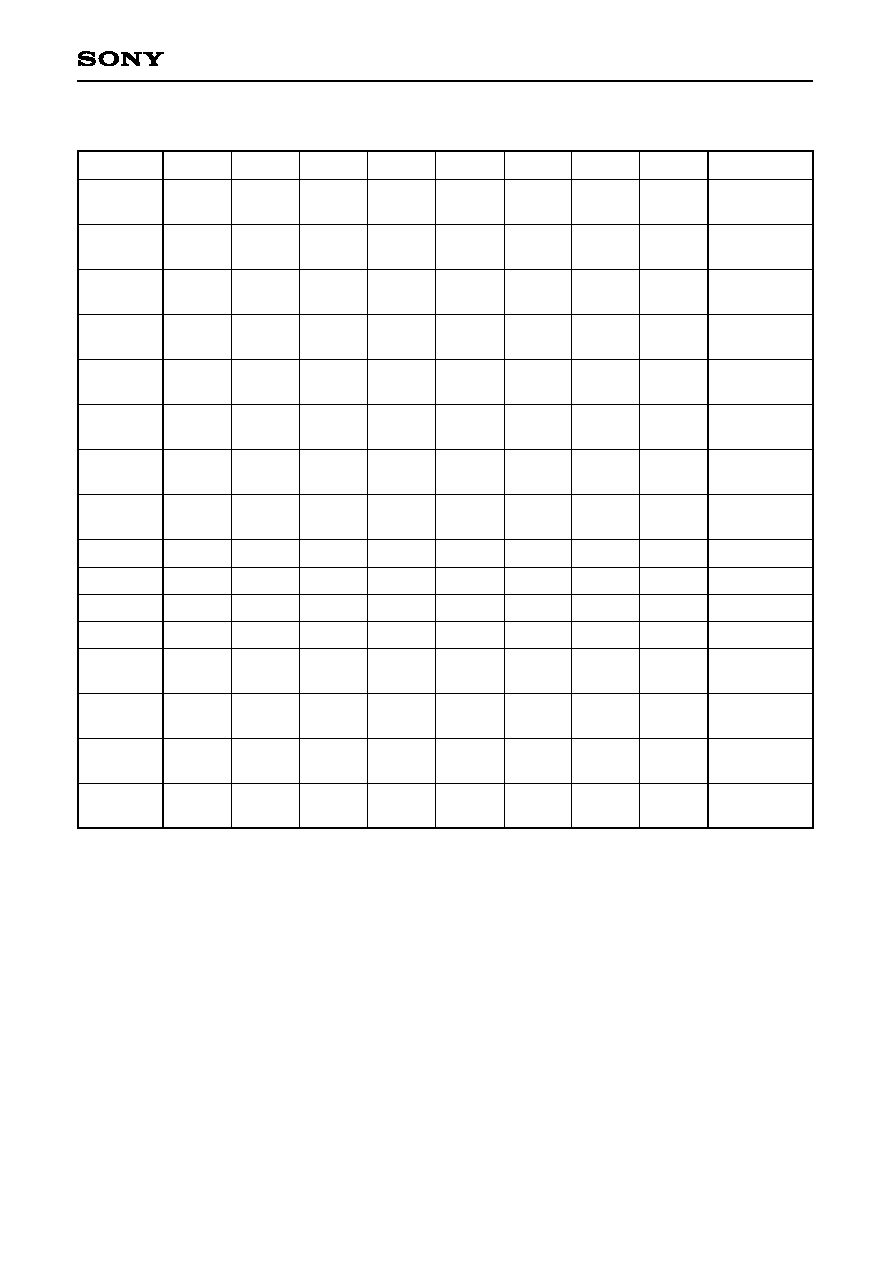

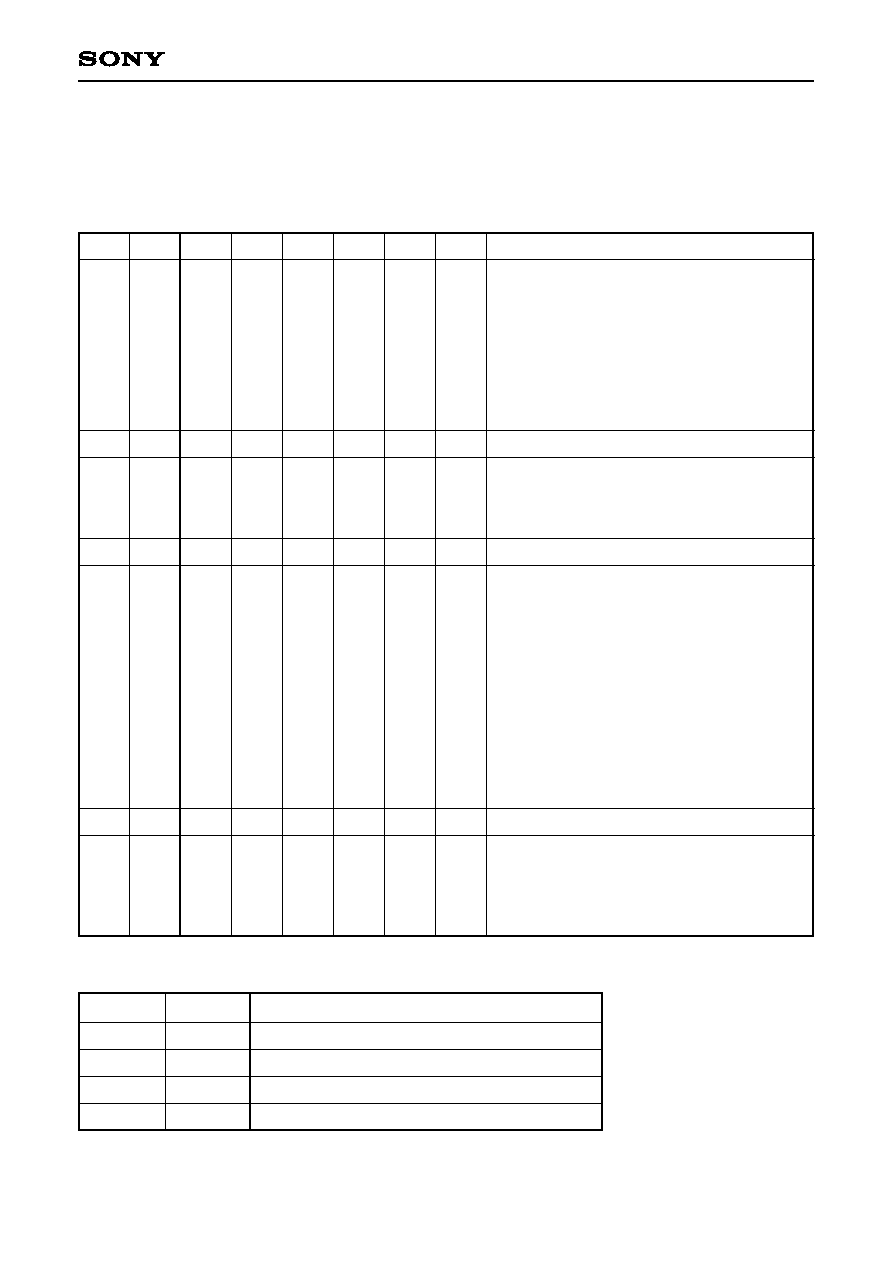

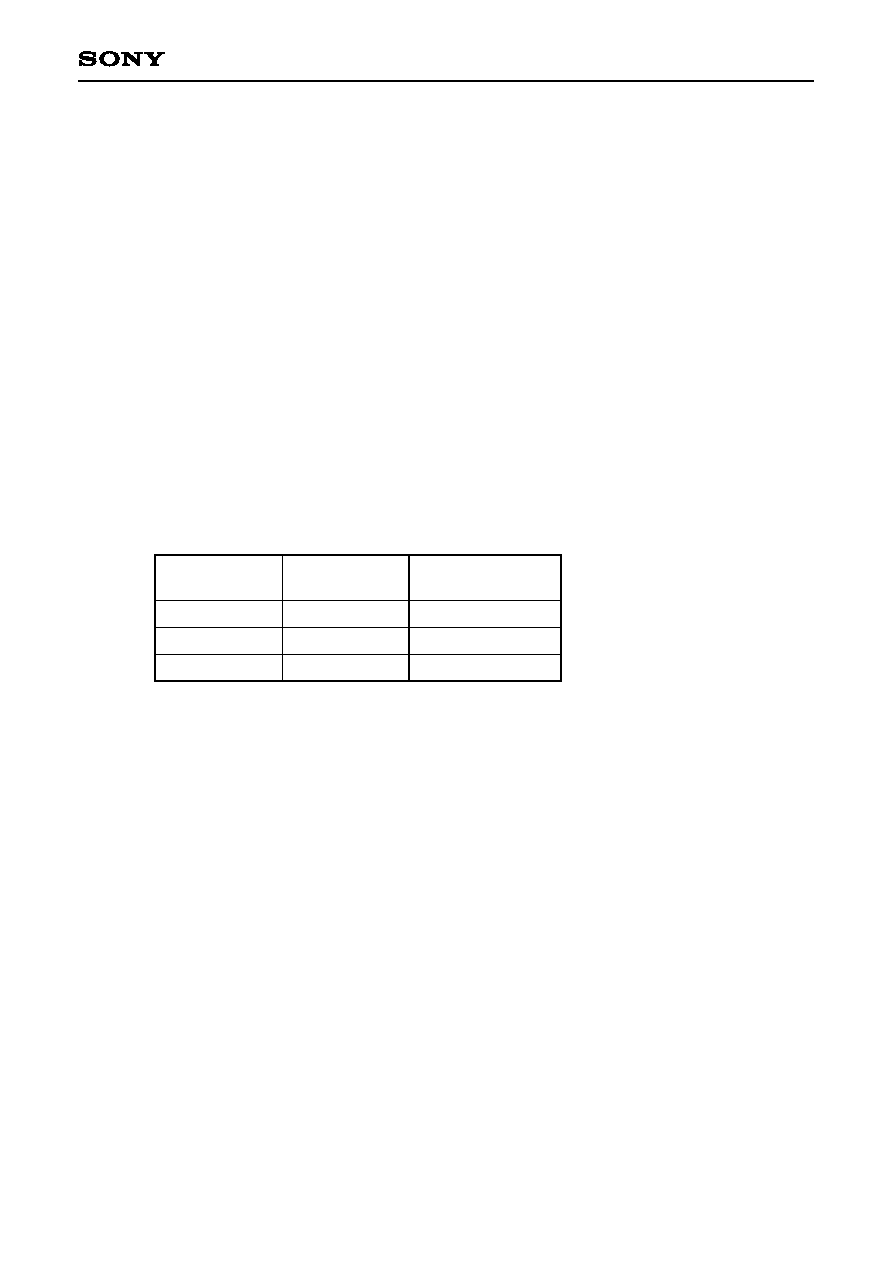

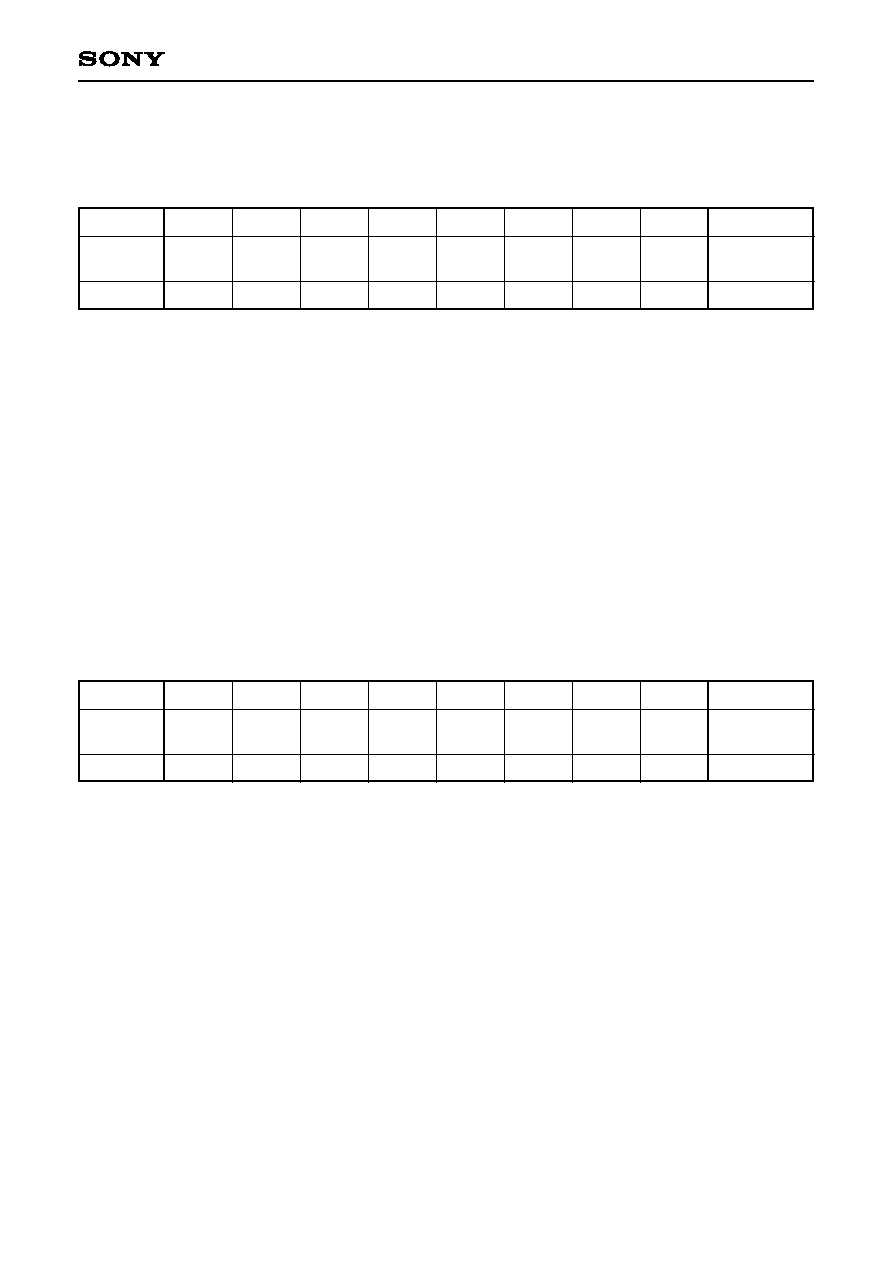

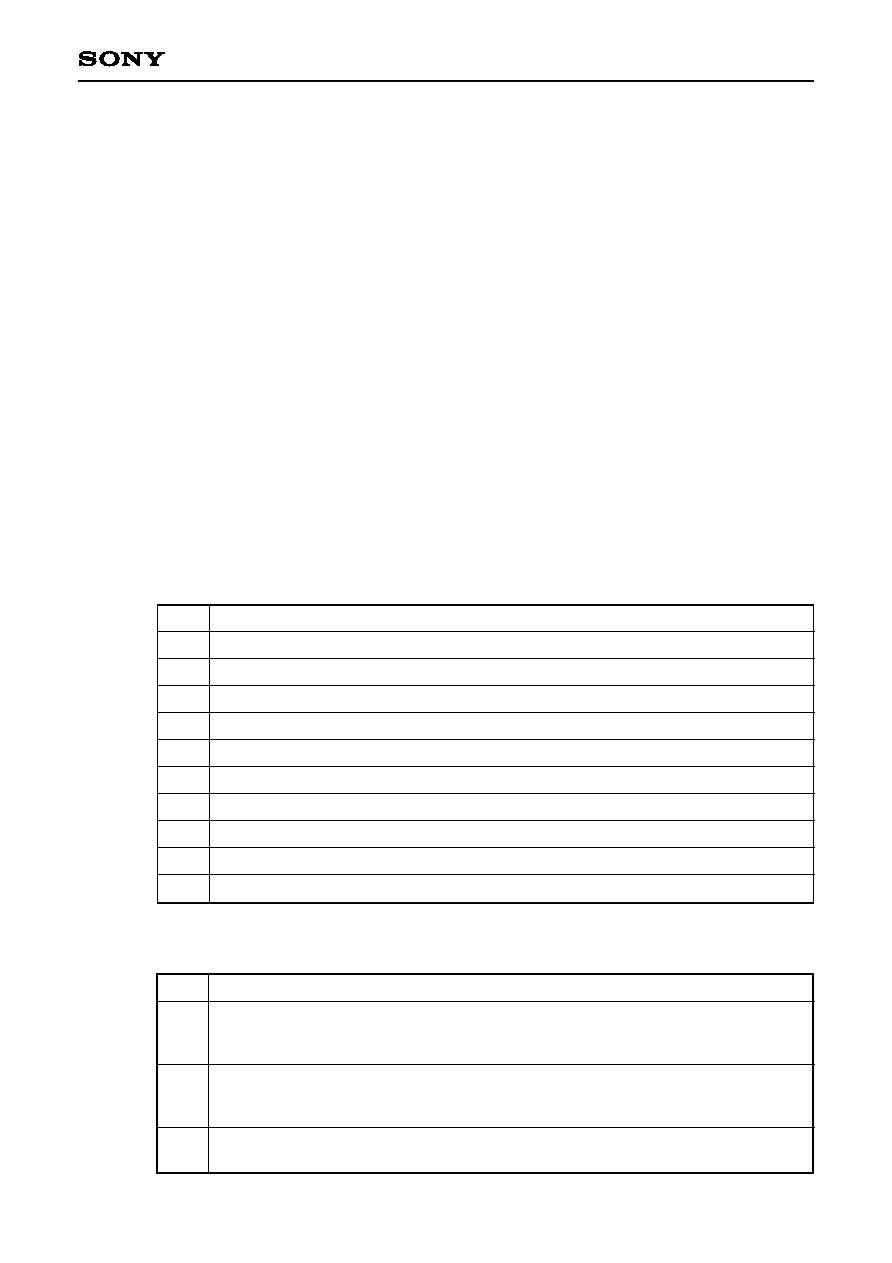

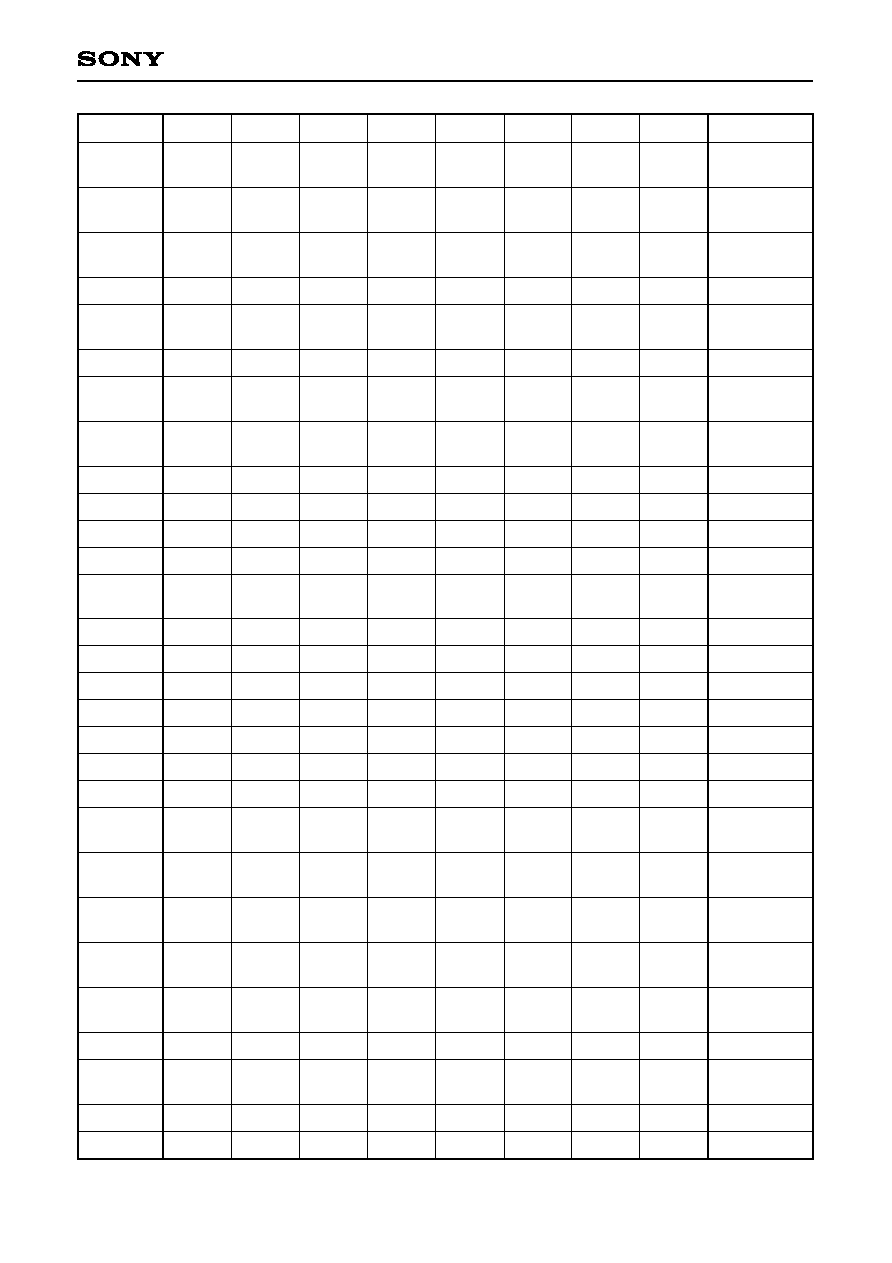

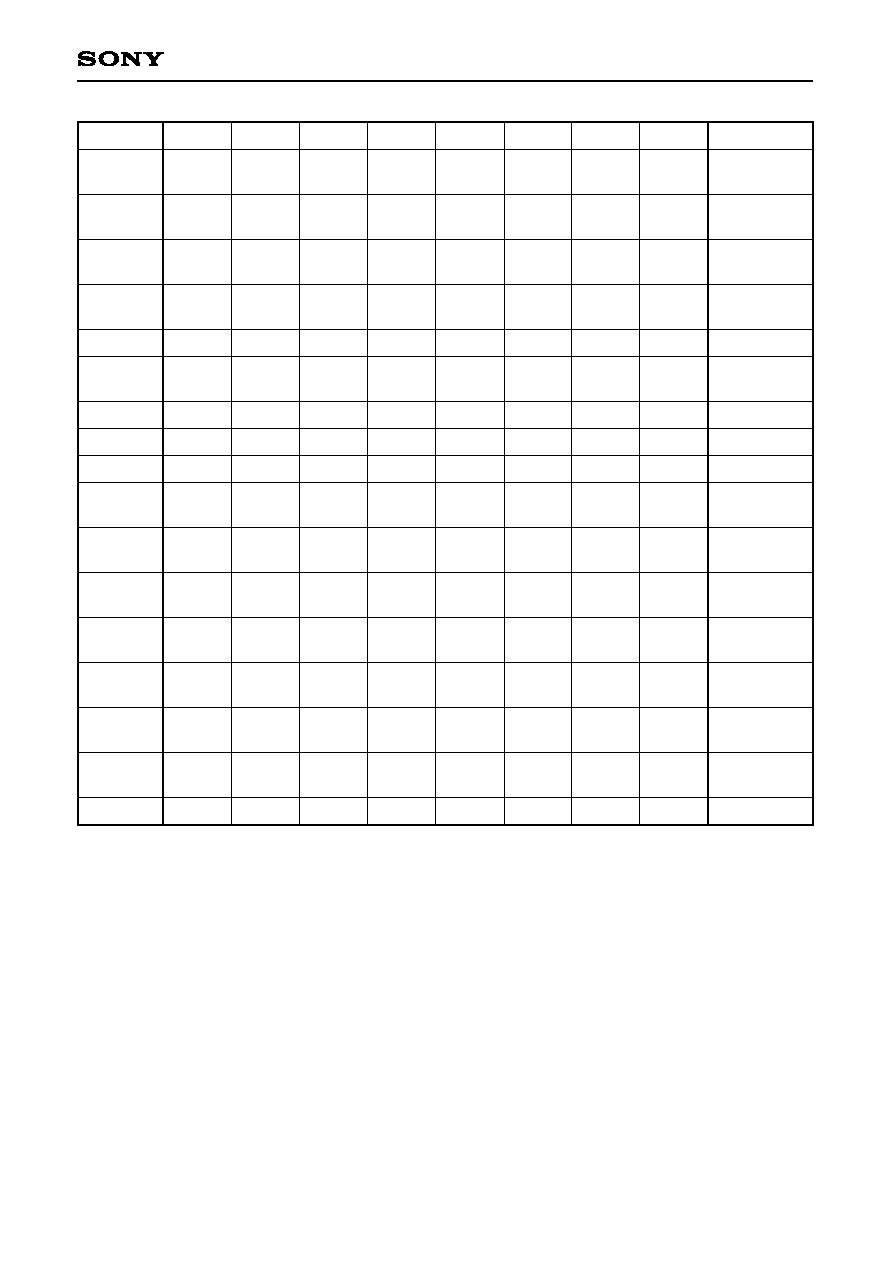

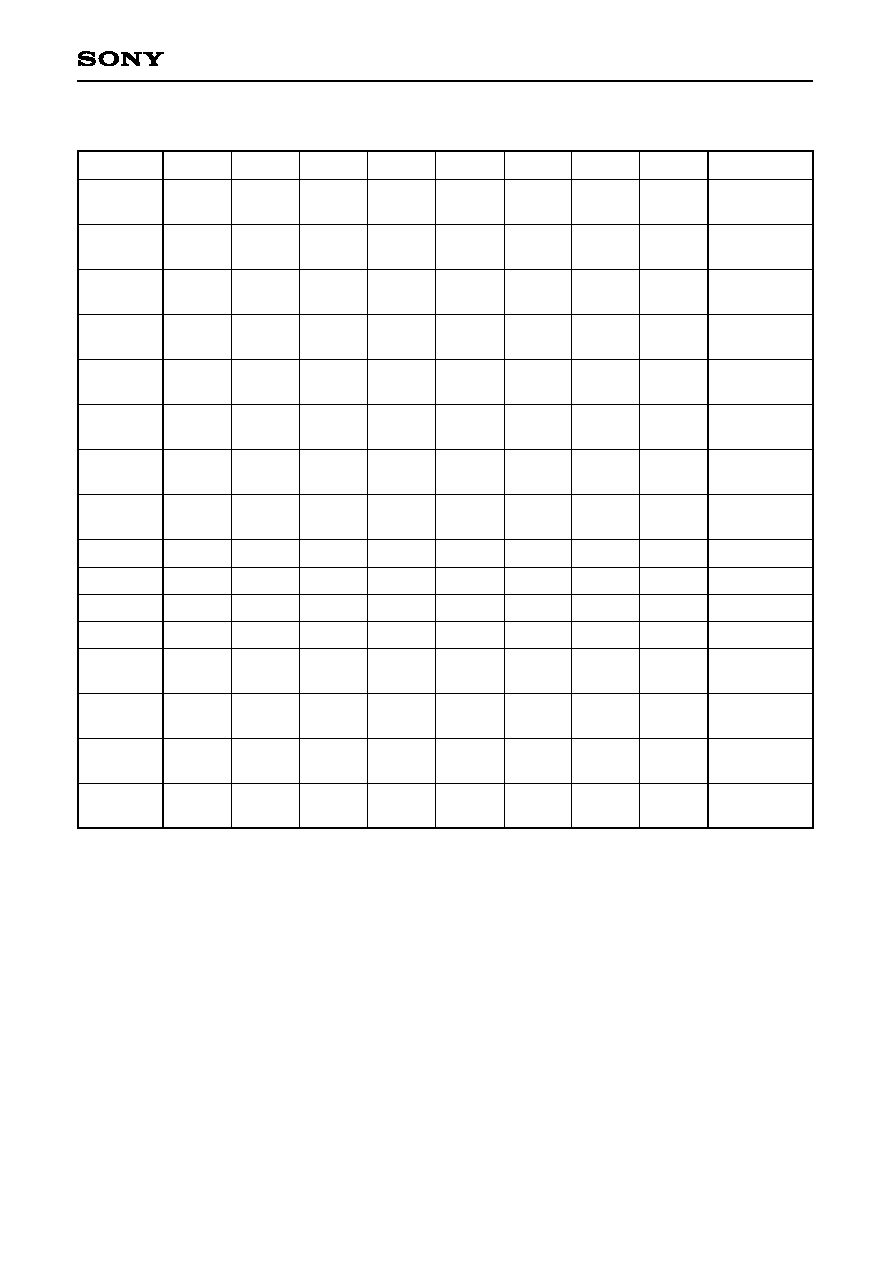

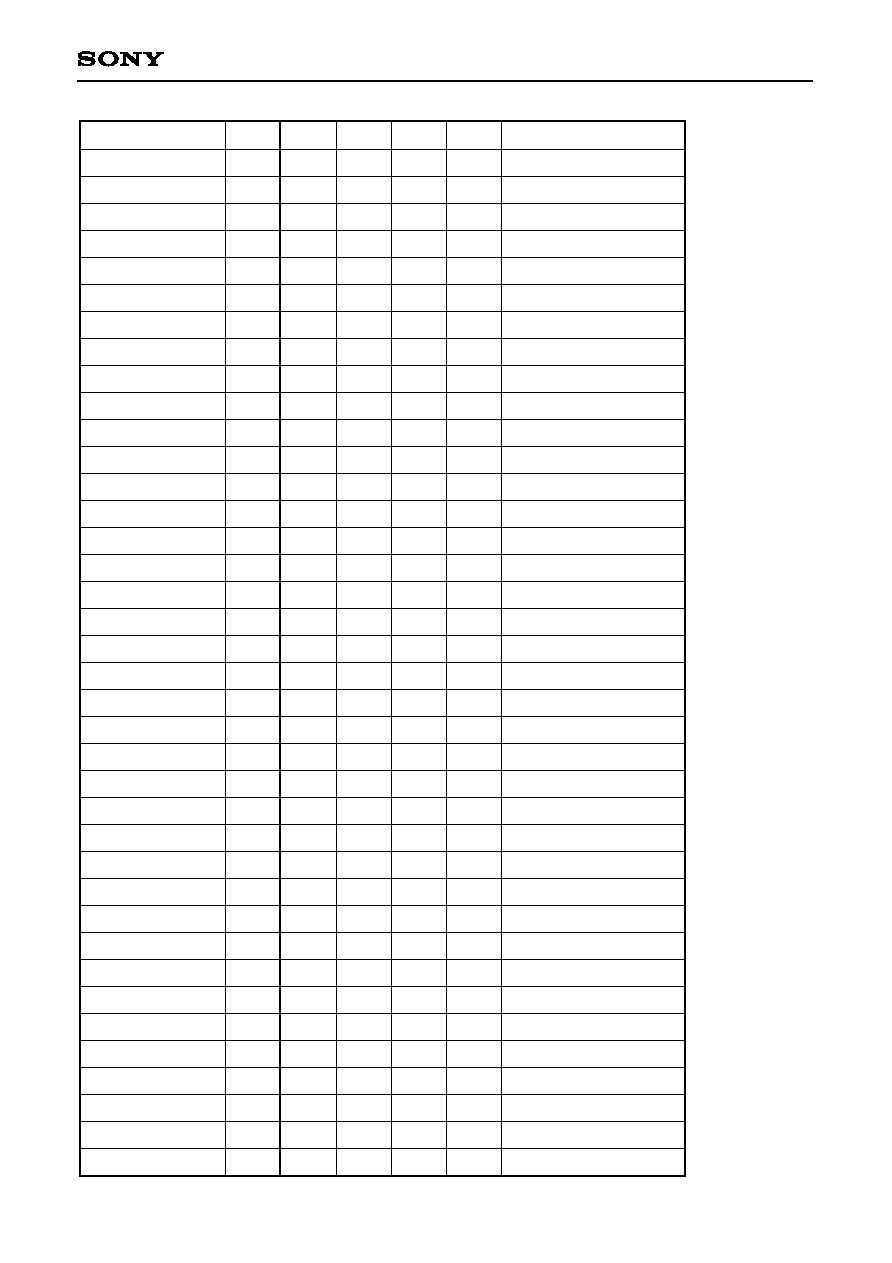

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

O

O

I

I

I

I

I

--

I

I

I

I

--

--

O

I

I

I

I

I

I

I

--

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

--

--

O

I

I

I

Negative

--

--

--

Negative

--

--

--

Selectable

Negative

Negative

Negative

CD DSP I/F

CD DSP I/F

CD DSP I/F

Test I/F

Test I/F

Test I/F

Test I/F

Power

Test I/F

Test I/F

Test I/F

Test I/F

Power

Power

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

Power

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

Power

Power

sub CPU I/F

sub CPU I/F

sub CPU I/F

sub CPU I/F

LR clock output to DAC

(connected to the LRCKI pin (Pin 26) of the CXD3000)

GRSCOR resynchronization output

(connected to the SCSY pin (Pin 68) of the CXD3000)

DSP RAM overflow input

(connected to the XROF pin (Pin 45) of the CXD3000)

Test pin 0

Test pin 1

Test pin 2

Test pin 3

V

SS

Test pin 4

Test pin 5

Test pin 6

Test pin 7

V

SS

V

SS

Wait signal for sub CPU buffer memory access

CXD1818R built-in register address bus bit 0

CXD1818R built-in register address bus bit 1

CXD1818R built-in register address bus bit 2

CXD1818R built-in register address bus bit 3

CXD1818R built-in register address bus bit 4

CXD1818R built-in register address bus bit 5

CXD1818R built-in register address bus bit 6

V

SS

Sub CPU data bus bit 0

Sub CPU data bus bit 1

Sub CPU data bus bit 2

Sub CPU data bus bit 3

Sub CPU data bus bit 4

Sub CPU data bus bit 5

Sub CPU data bus bit 6

Sub CPU data bus bit 7

V

SS

V

DD

Interrupt to sub CPU

CXD1818R chip select signal

CXD1818R built-in register write signal

CXD1818R built-in register read signal

LRCO

GRST

XROF

TST0

TST1

TST2

TST3

V

SS

TST4

TST5

TST6

TST7

V

SS

V

SS

XWAT

A0

A1

A2

A3

A4

A5

A6

V

SS

D0

D1

D2

D3

D4

D5

D6

D7

V

SS

V

DD

INT

XCS

XWR

XRD

Pin

No.

Symbol

I/O

Logic

Classification

Description

≠ 9 ≠

CXD1818R

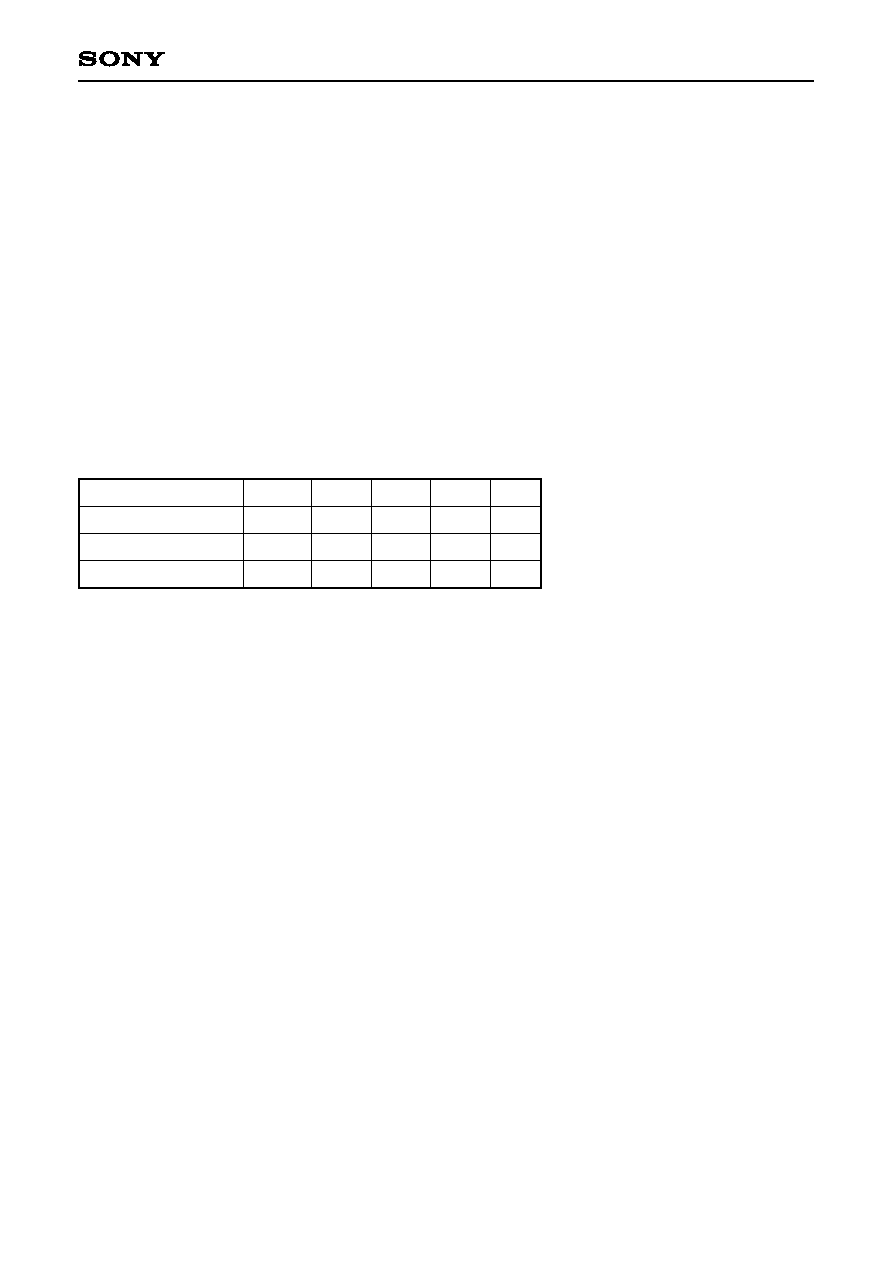

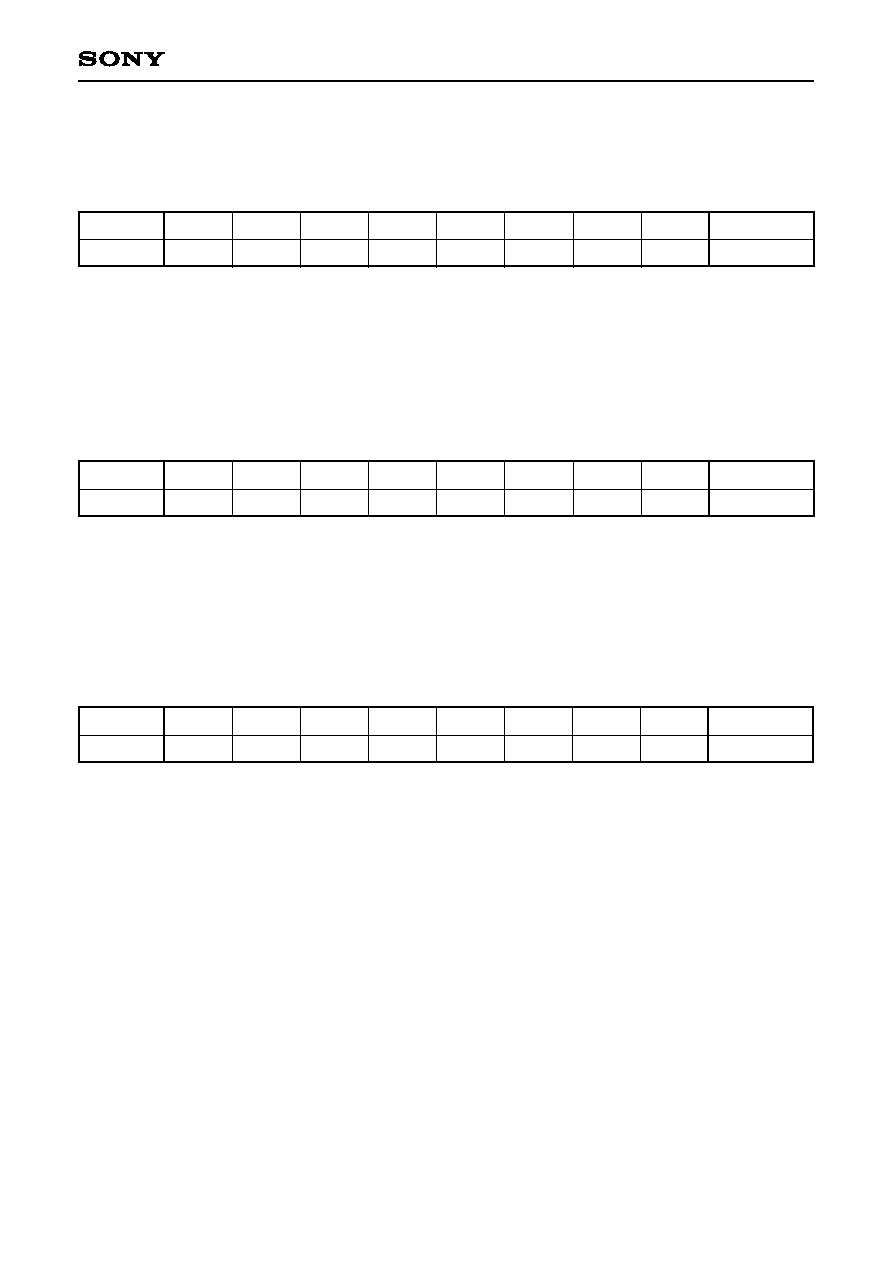

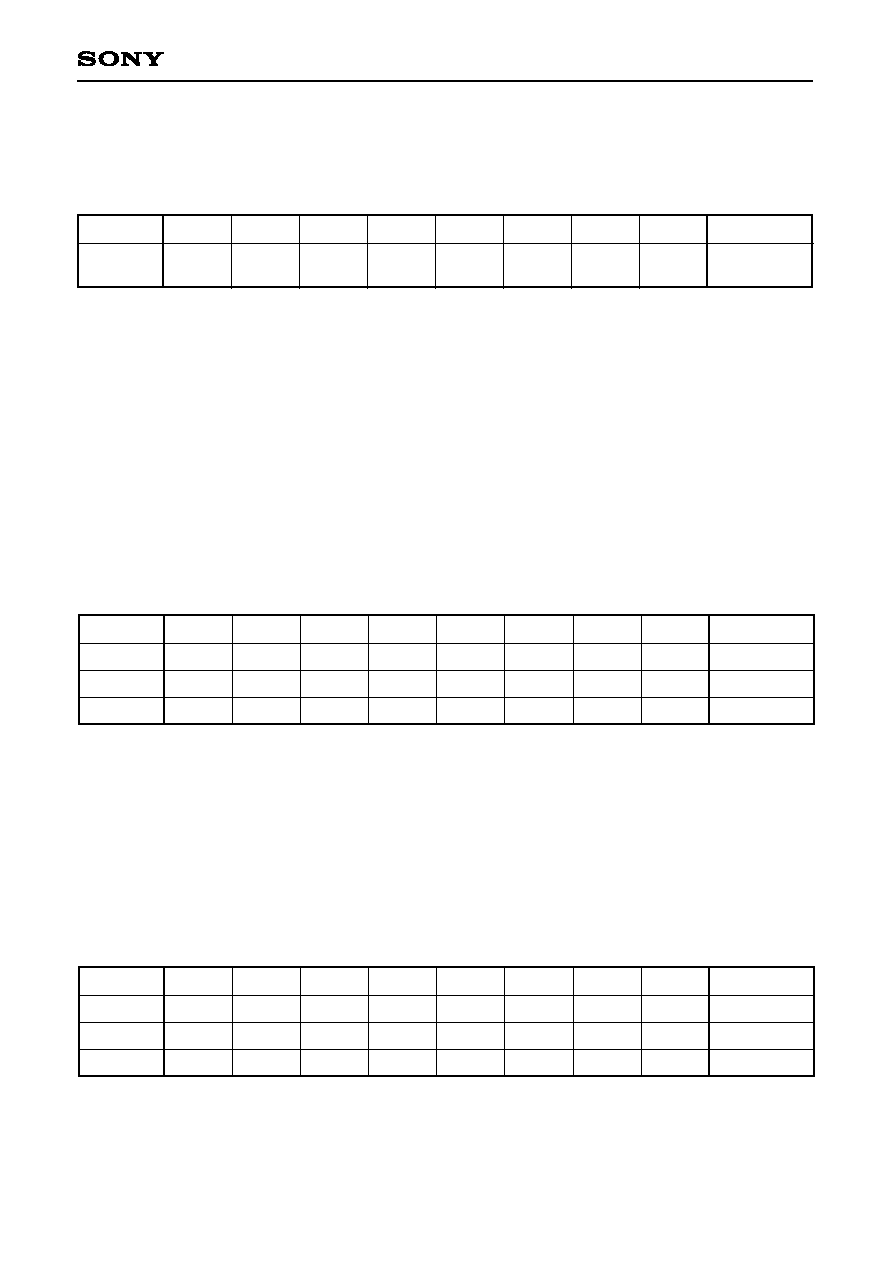

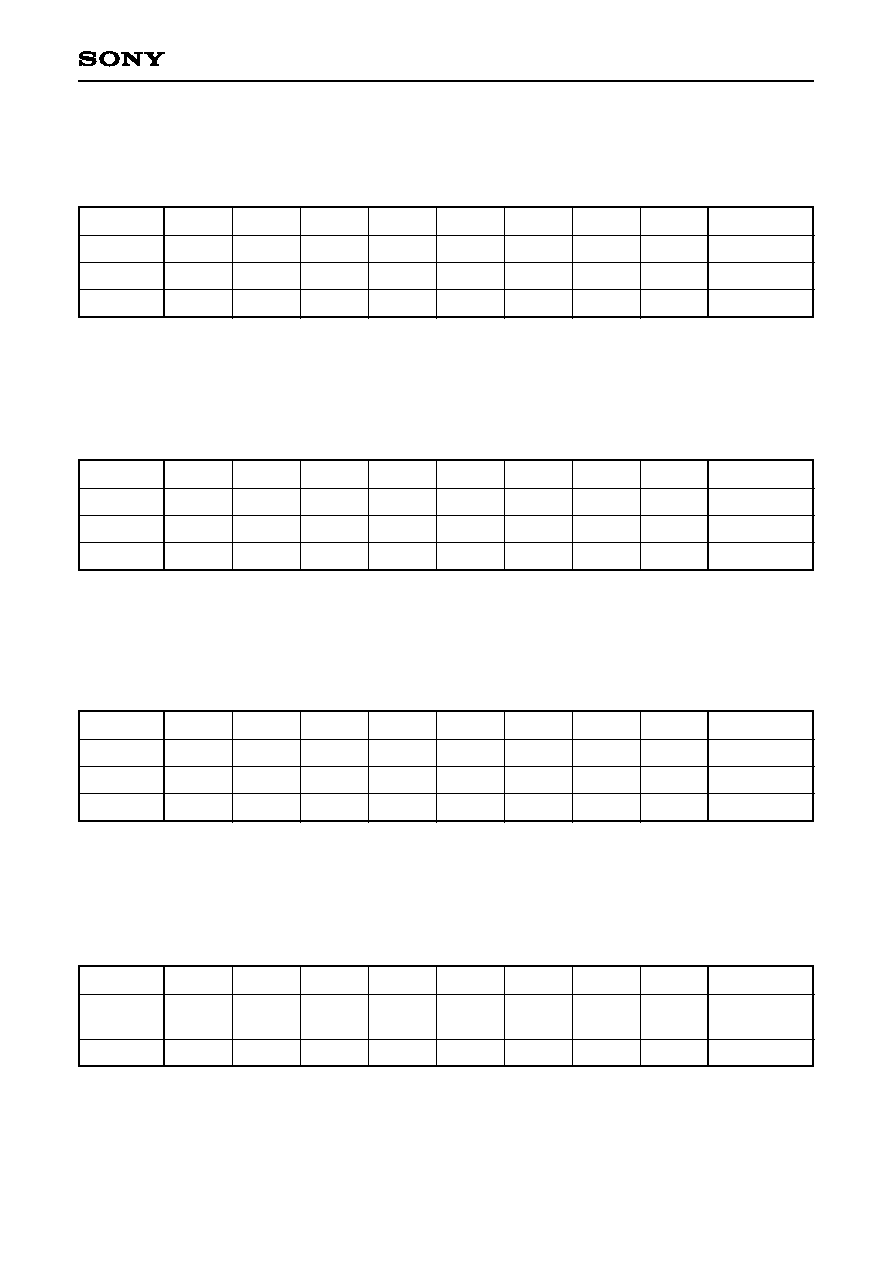

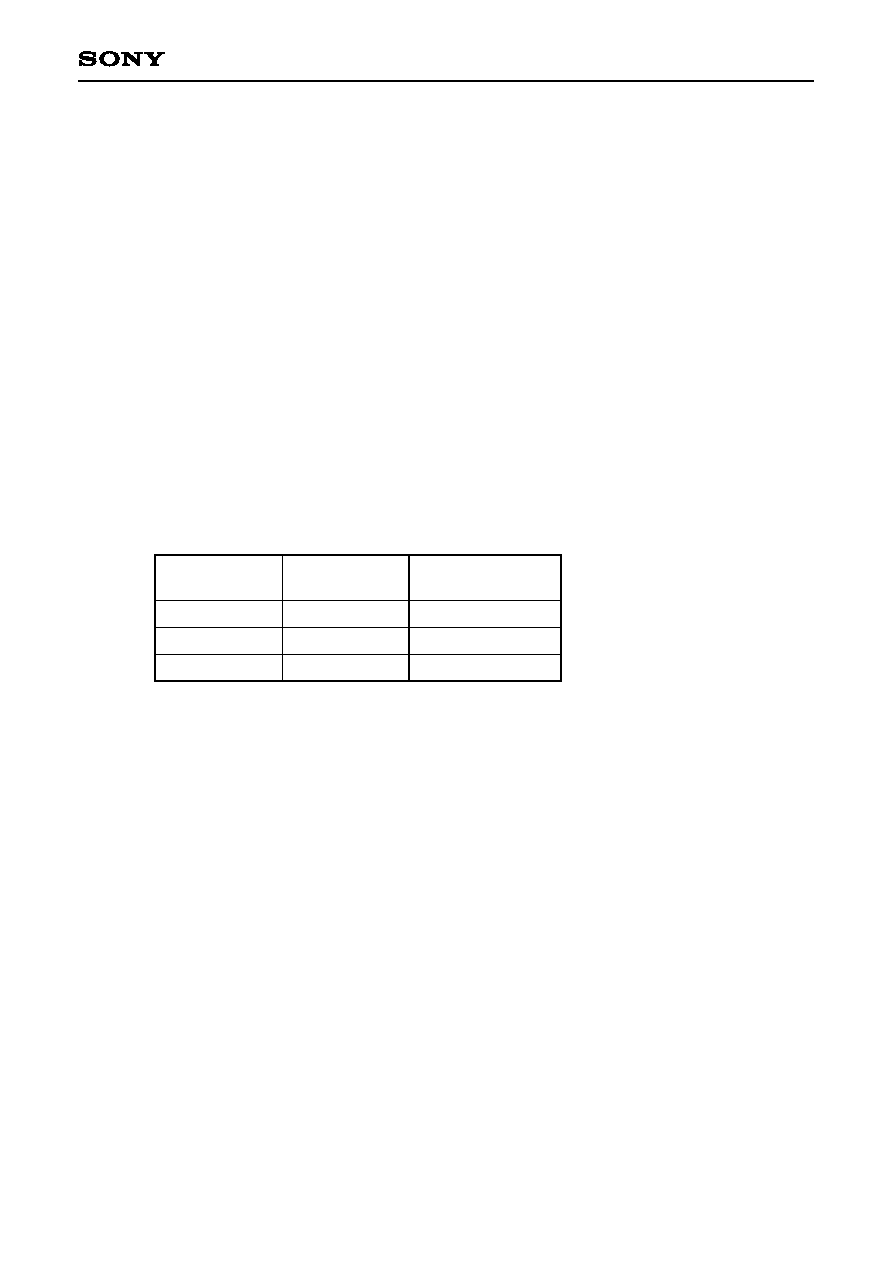

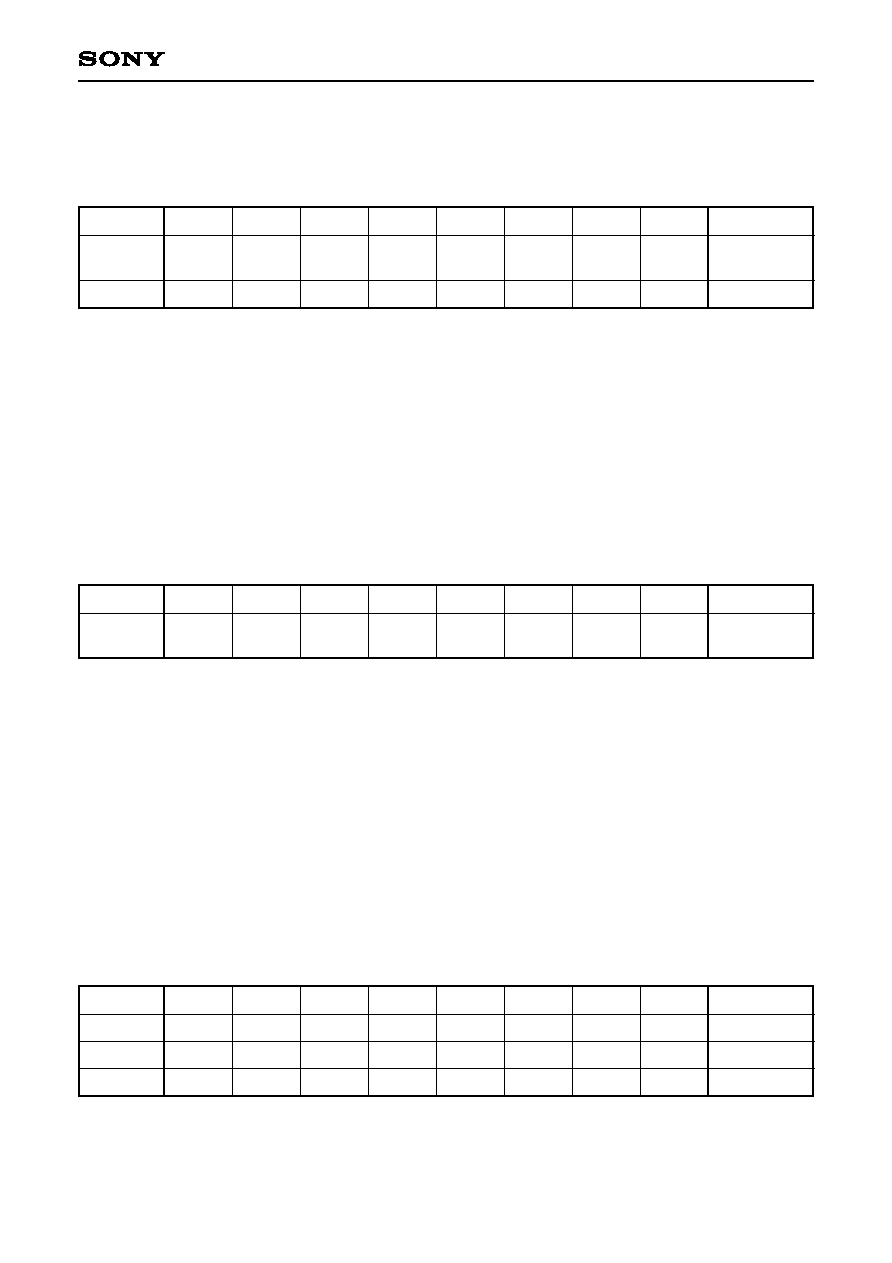

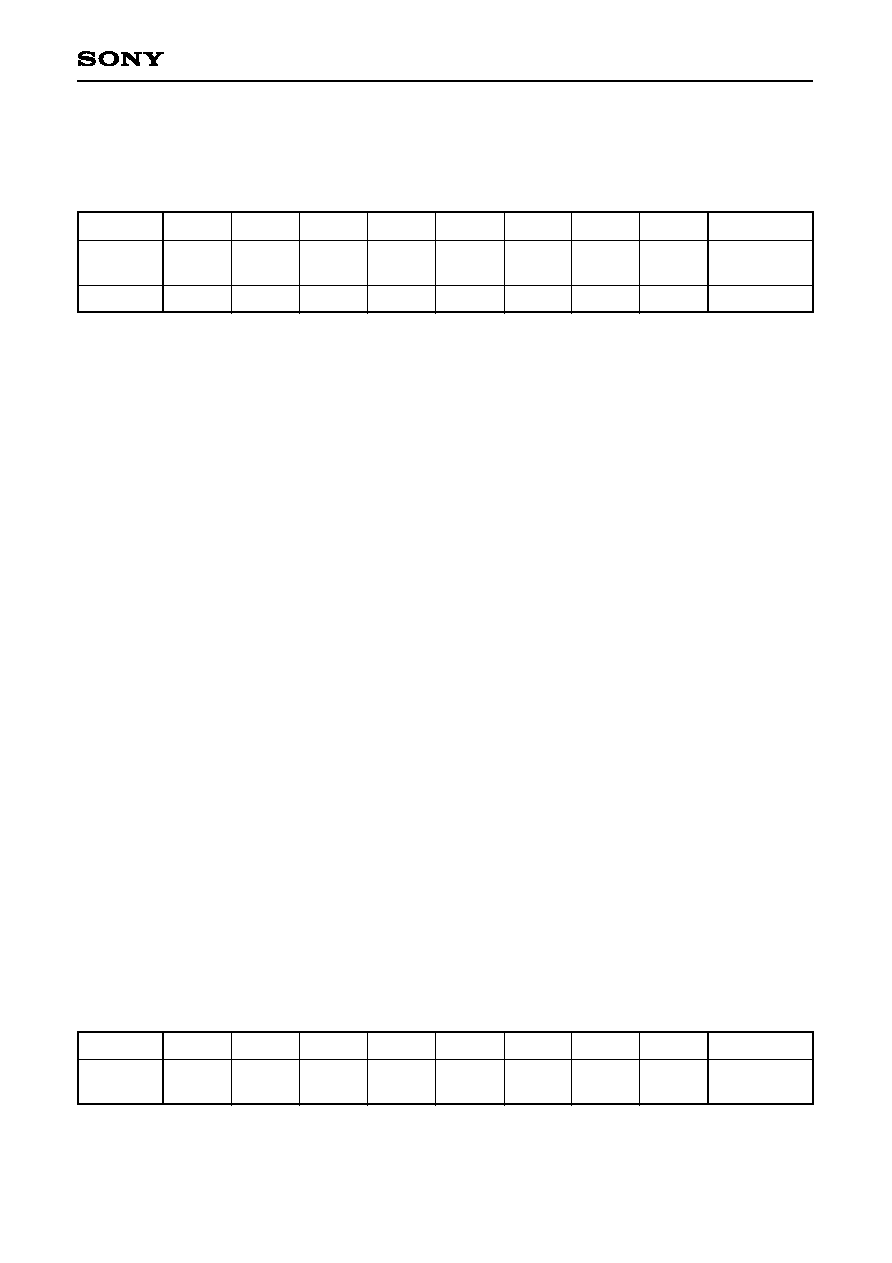

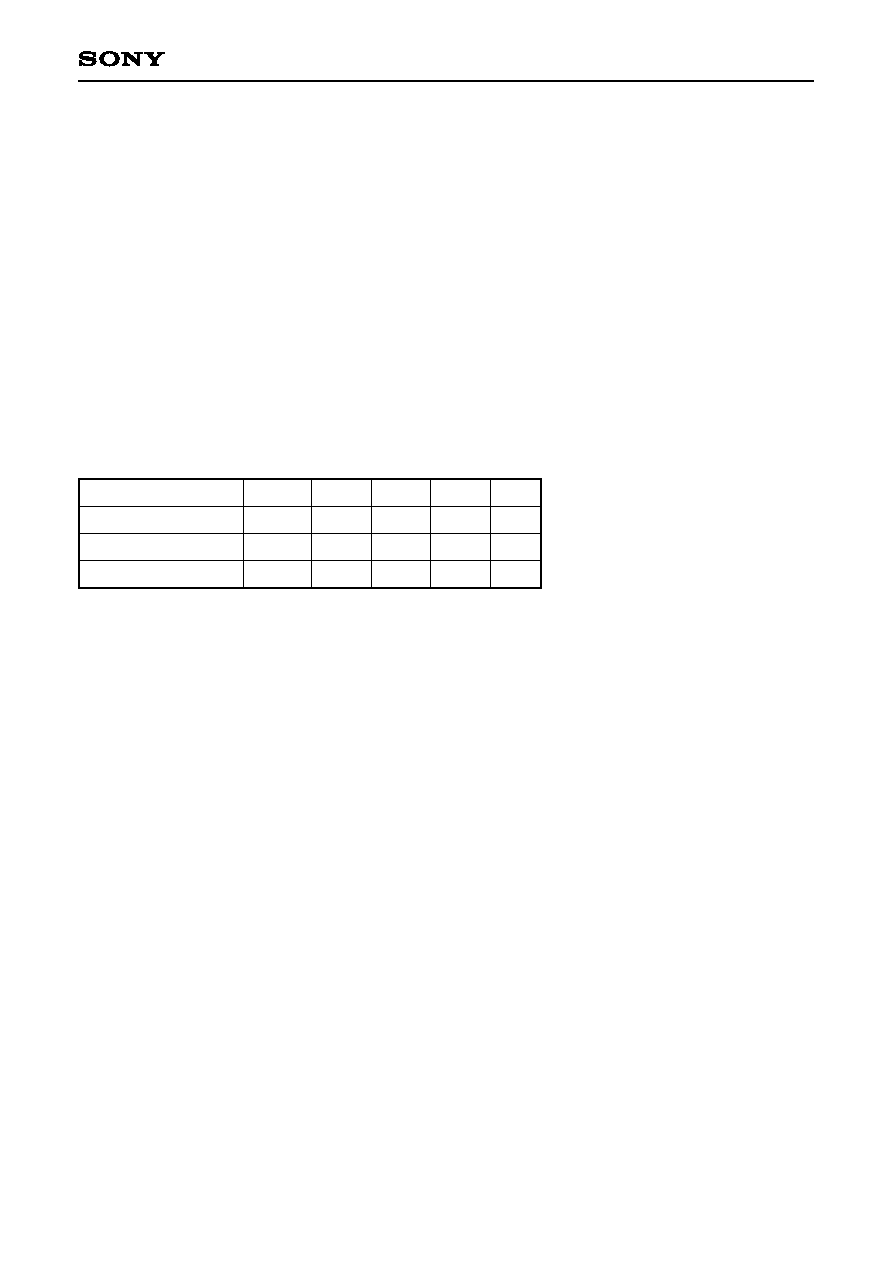

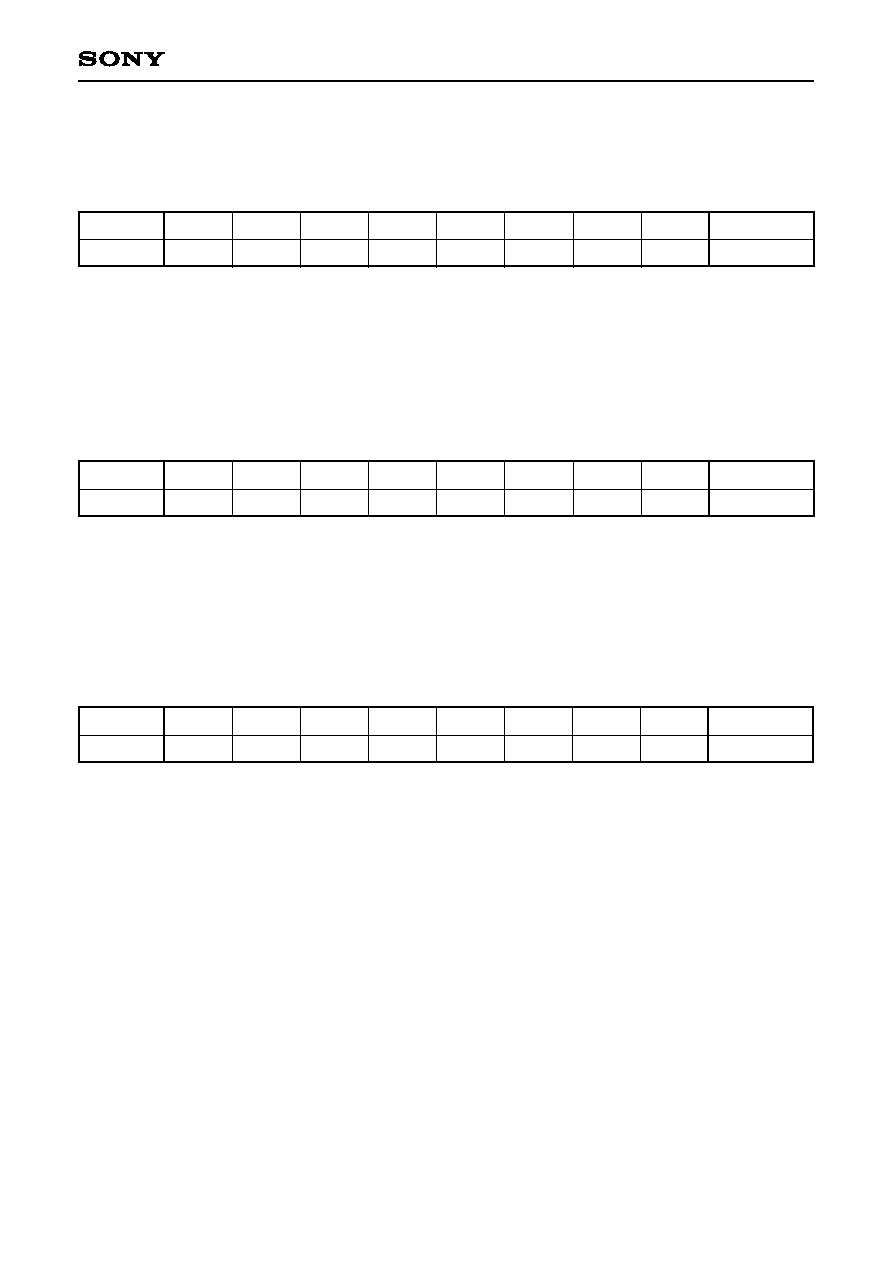

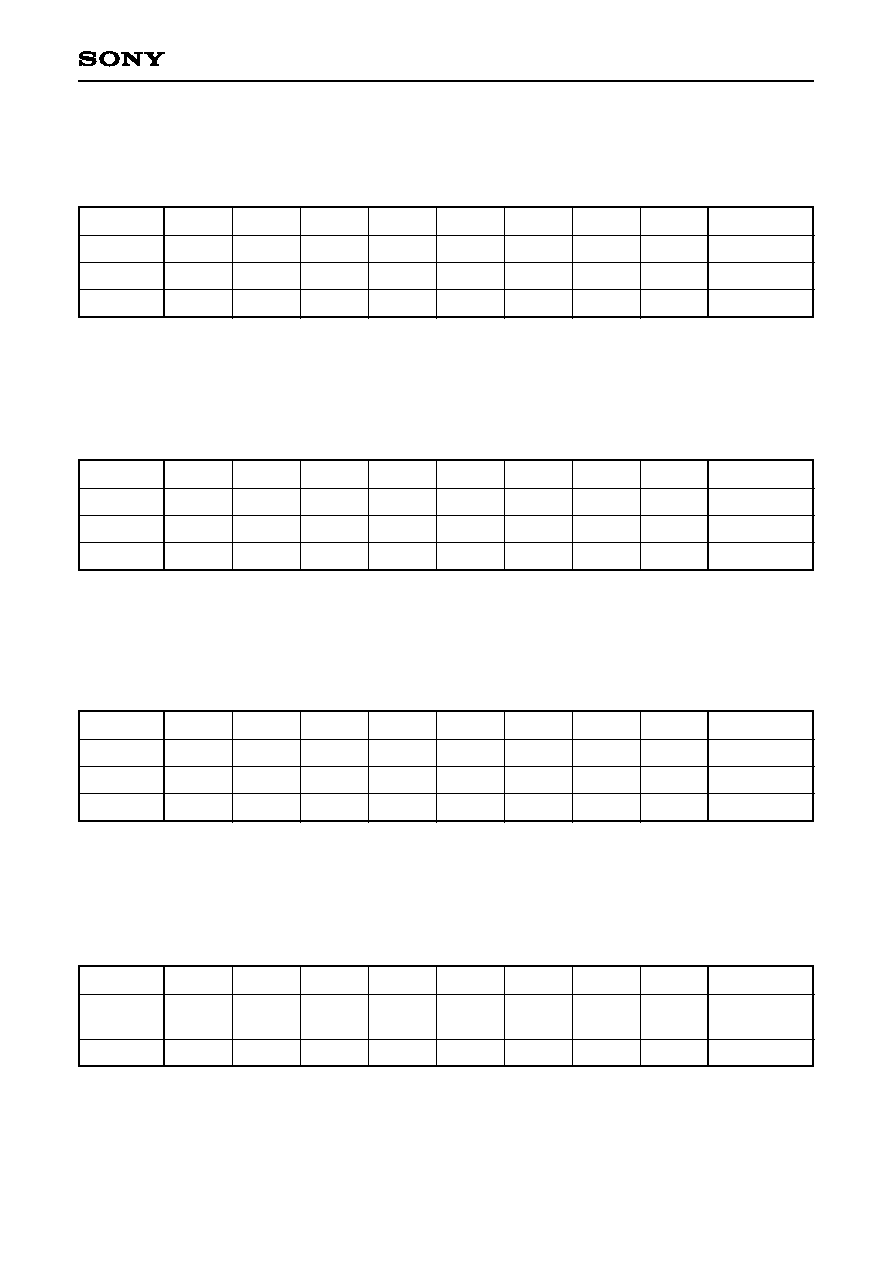

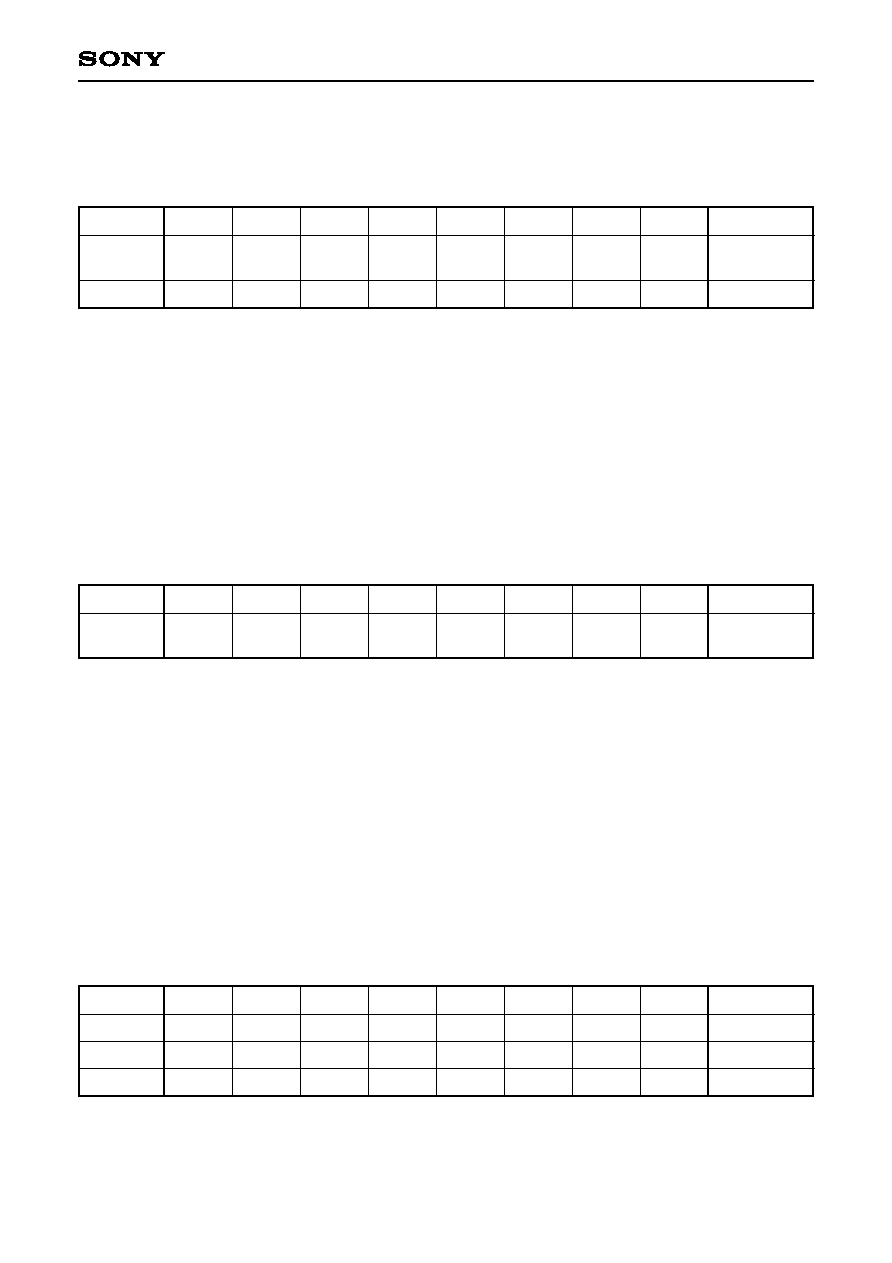

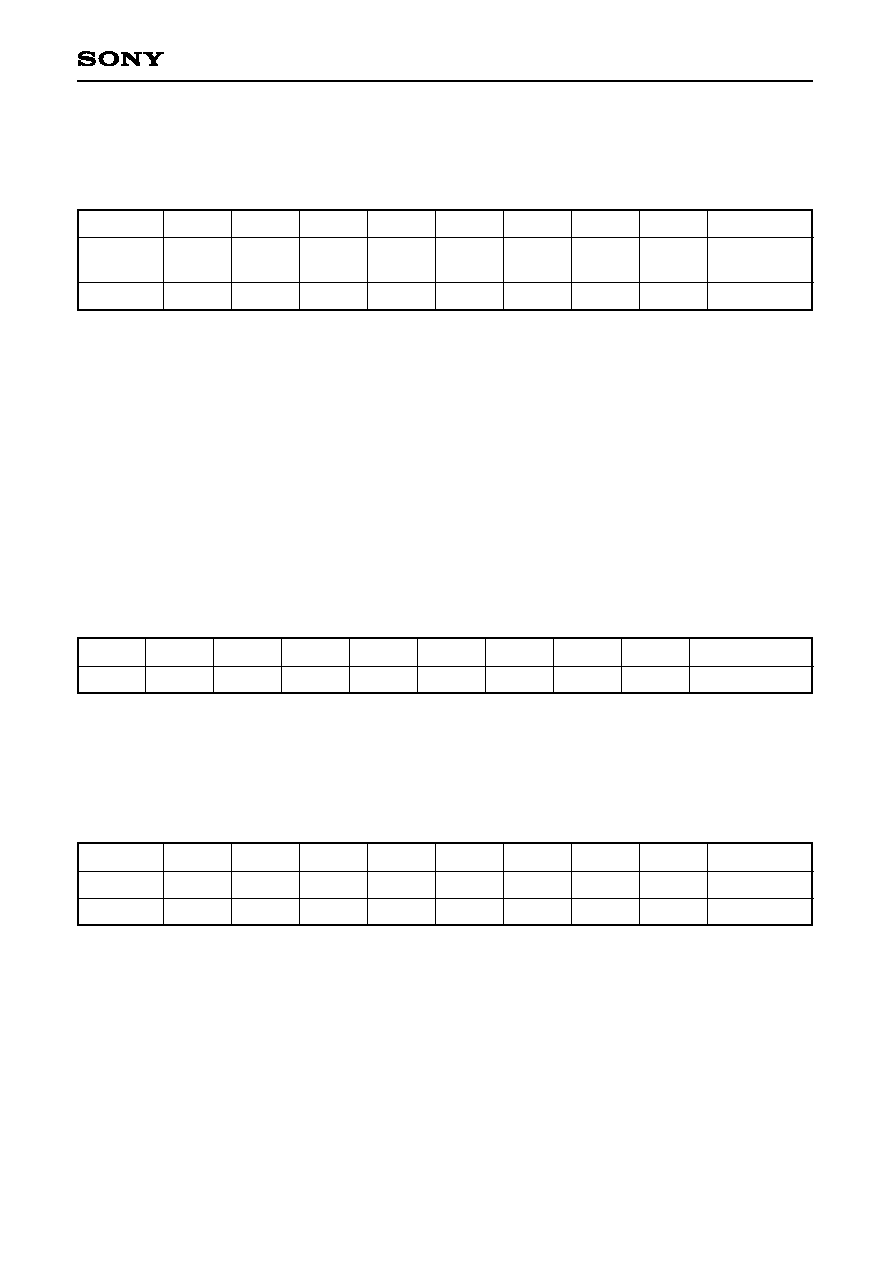

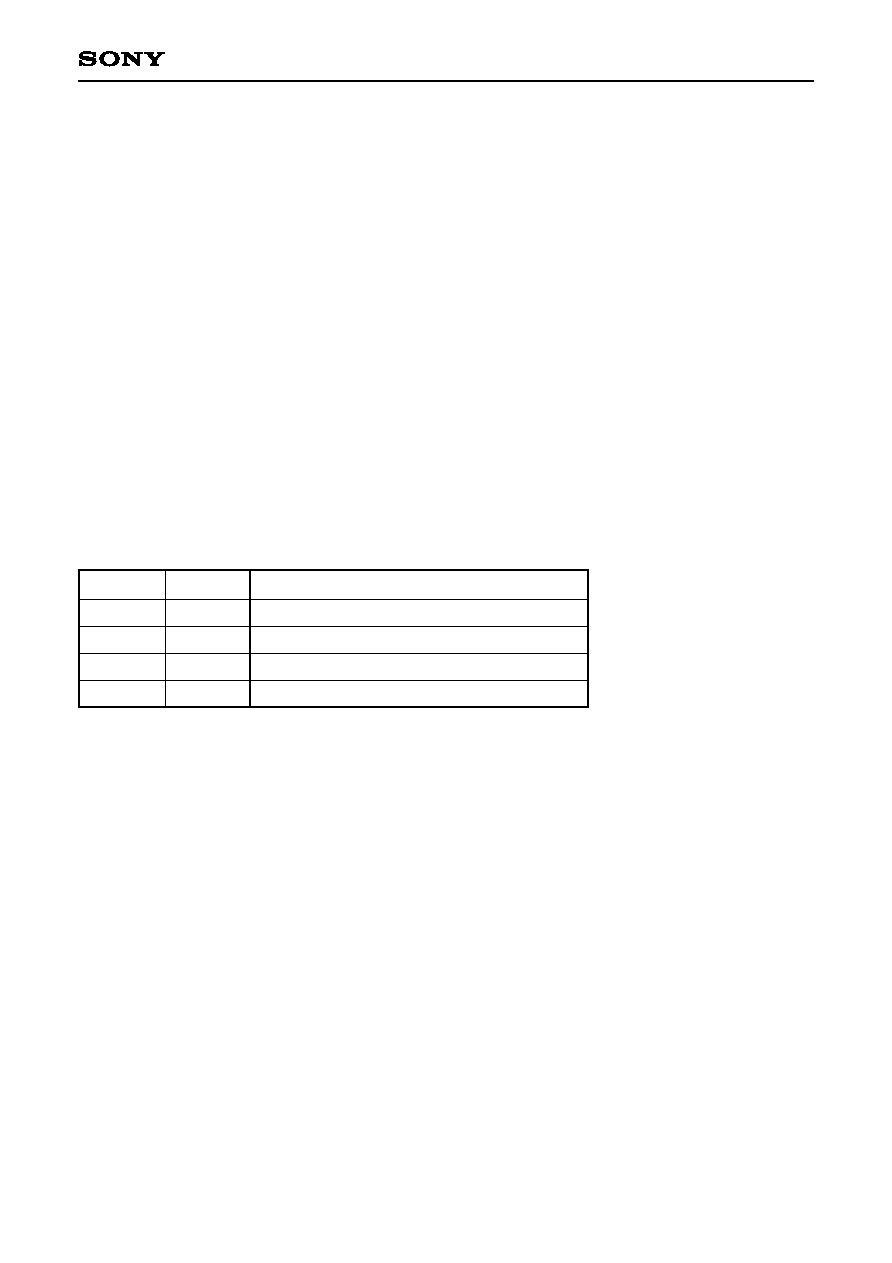

Electrical Characteristics

(V

DD

= 5V ± 10%, V

SS

= 0V, Topr = ≠20 to +75∞C)

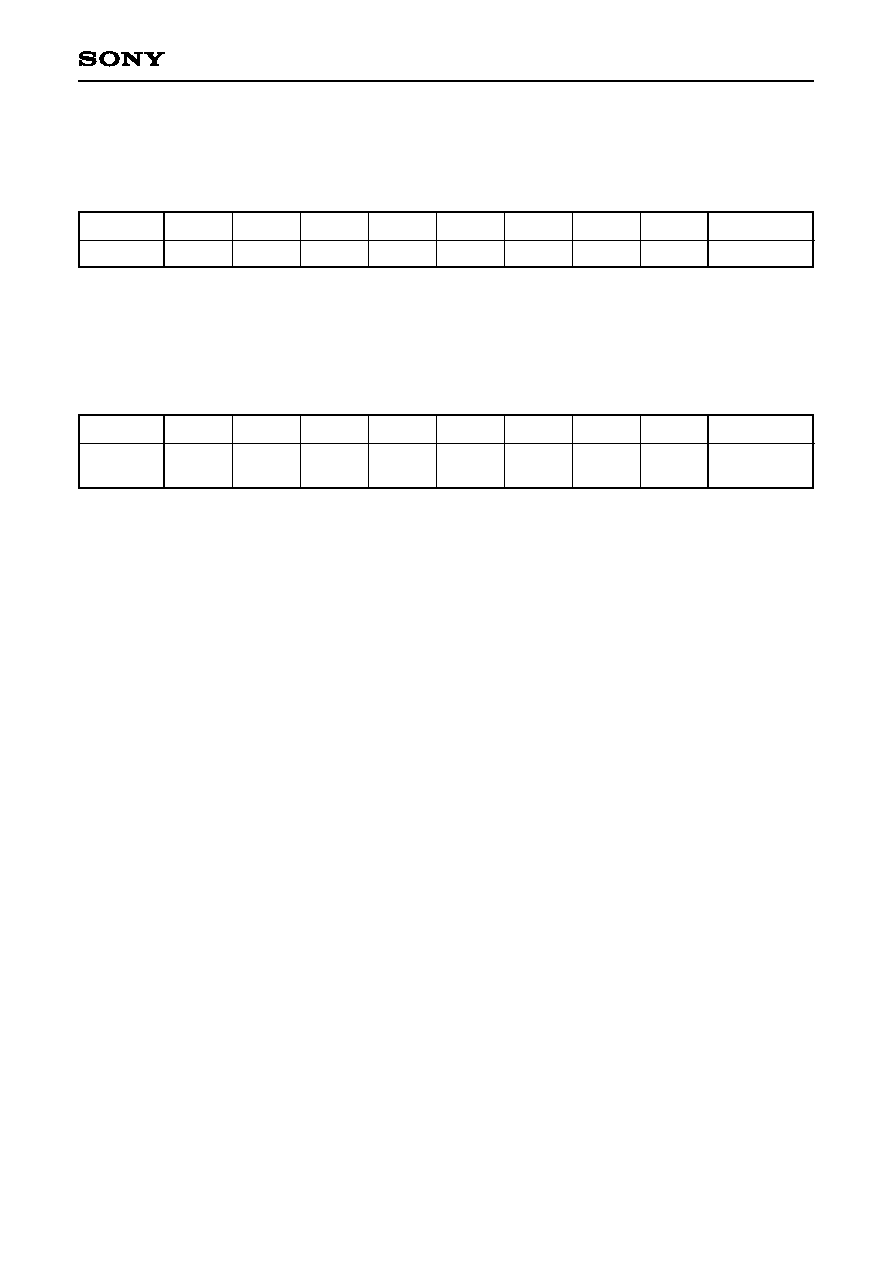

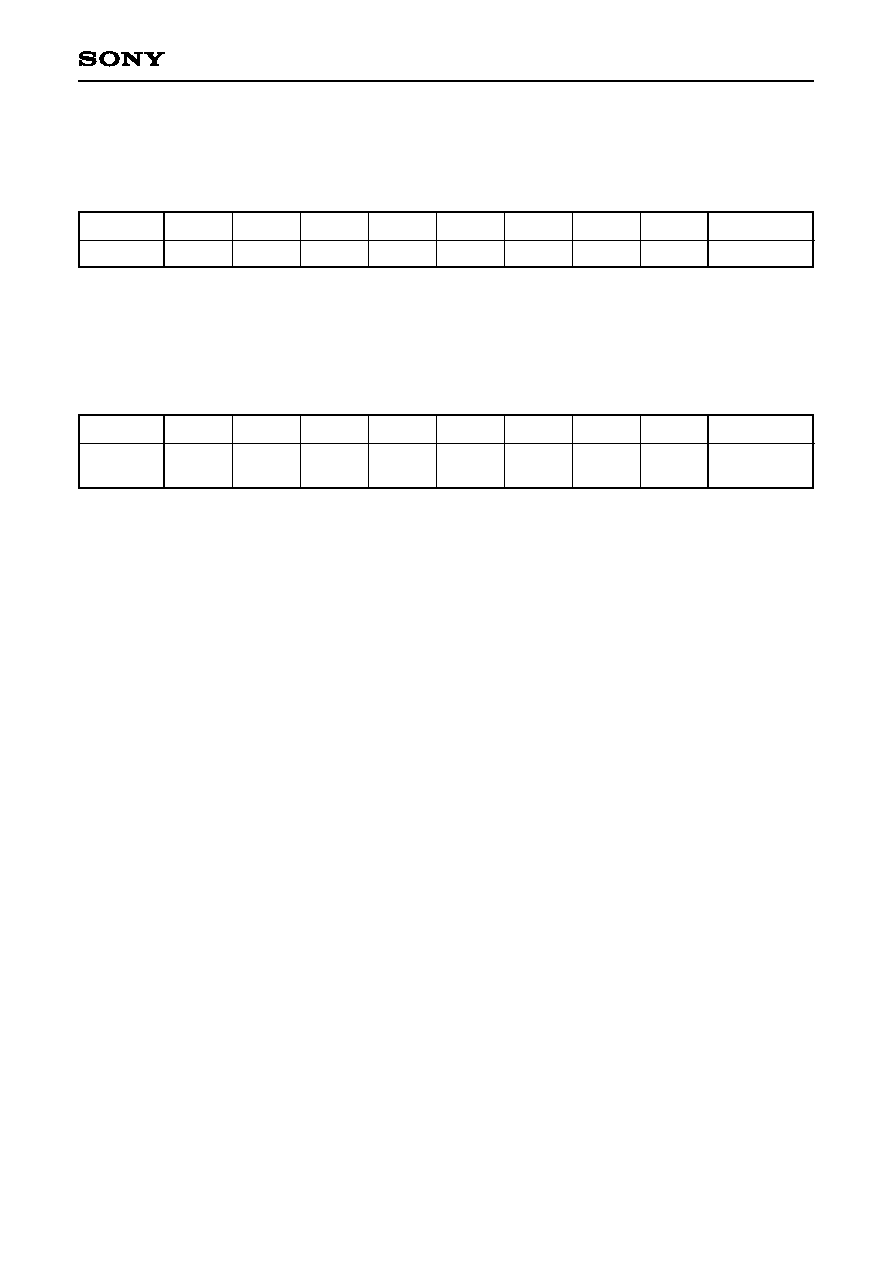

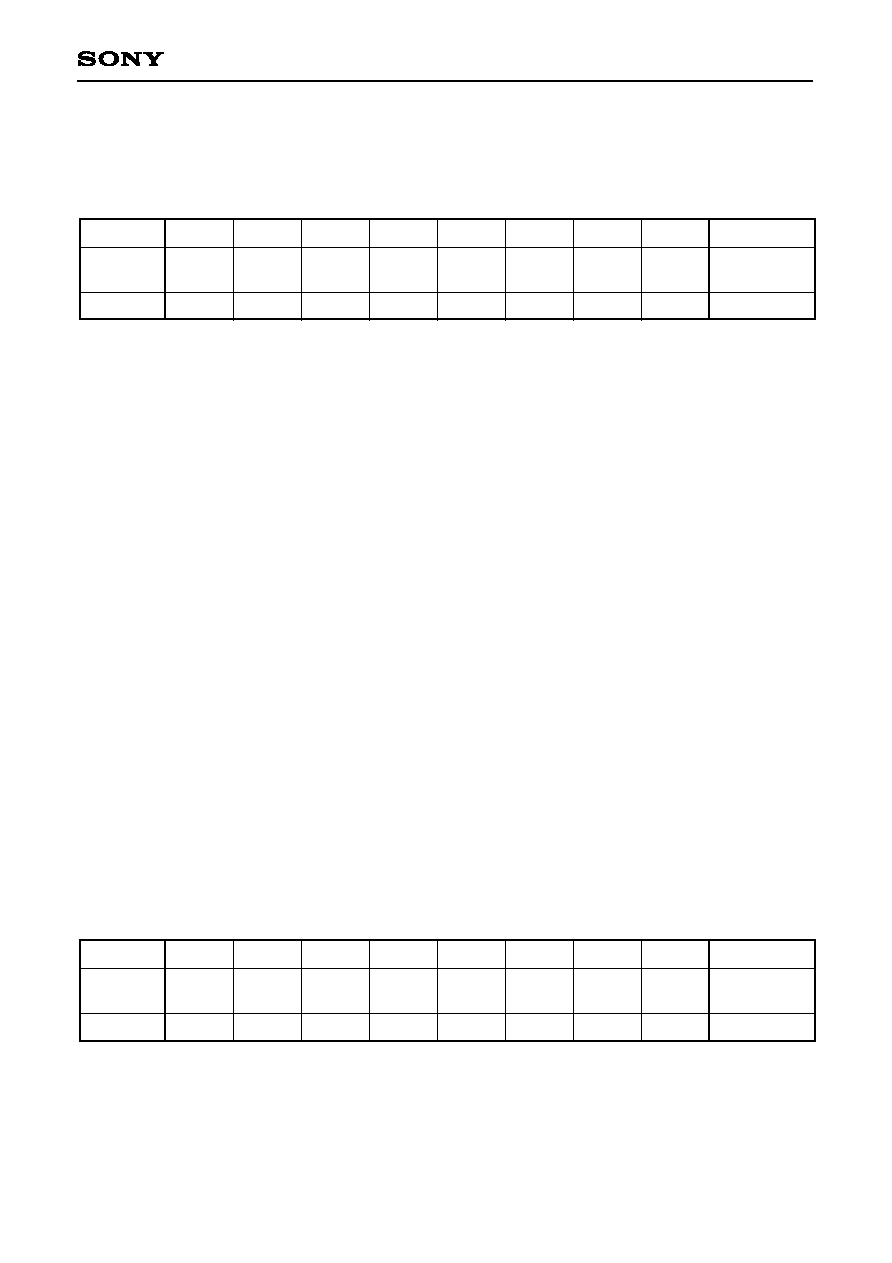

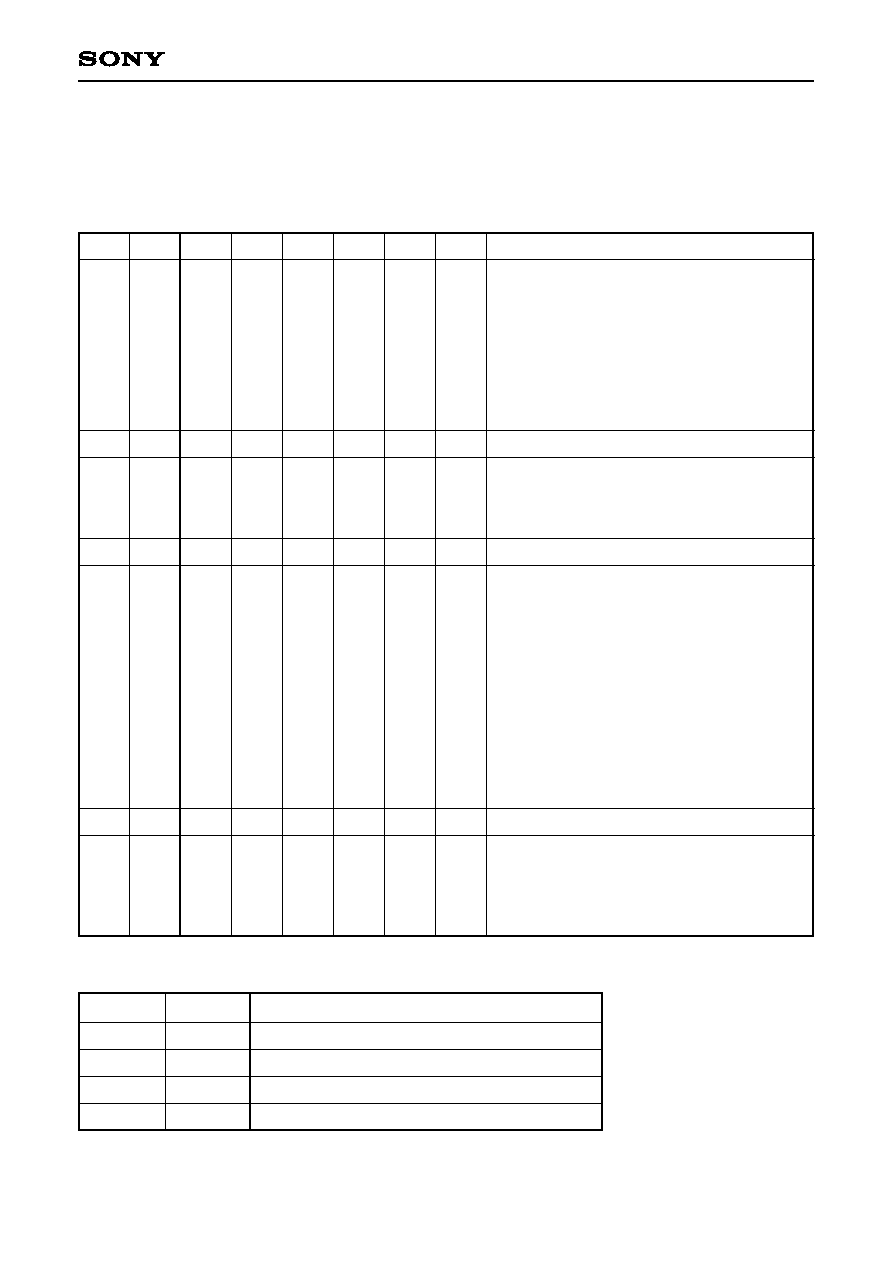

Item

TTL input level pin

High level input voltage

TTL input level pin

Low level input voltage

CMOS input level pin

High level input voltage

CMOS input level pin

Low level input voltage

CMOS Schmitt input level pin

High level input voltage

CMOS Schmitt input level pin

Low level input voltage

CMOS Schmitt input level pin

Input voltage hysteresis

TTL Schmitt input level pin

High level input voltage

TTL Schmitt input level pin

Low level input voltage

TTL Schmitt input level pin

Input voltage hysteresis

SCSI Schmitt input level pin

High level input voltage

SCSI Schmitt input level pin

Low level input voltage

SCSI Schmitt input level pin

Input voltage hysteresis

Bidirectional pin with pull-up resistor

Input current

Input voltage

High level output voltage

High level output voltage

SCSI high level output voltage

Low level output voltage

SCSI low level output voltage

Input leakage current

Oscillation cell high level input voltage

Oscillation cell low level input voltage

Oscillation cell logic threshold value

Oscillation cell feedback resistance value

Oscillation cell high level output voltage

Oscillation cell low level output voltage

V

IH1

V

IL1

V

IH2

V

IL2

V

IH4

V

IL4

V

IH4

≠ V

IL4

V

IH5

V

IL5

V

IH5

≠ V

IL4

V

IHS

V

ILS

V

IHTS

≠ V

ILTS

I

IL3

V

IN6

V

OH1

V

OH2

V

OHS

V

OL1

V

OLS

I

I1

V

IH4

V

IL4

LV

TH

R

FB

V

OH3

V

OL3

V

IN

= 0V

Analog input

I

OH

= ≠2mA

I

OH

= ≠6mA

I

OL

= 4mA

I

OL

= 48mA

V

IN

= V

SS

or V

DD

V

IN

= V

SS

or V

DD

I

OH

= ≠12mA

I

OL

= 12mA

2.2

0.7V

DD

0.8V

DD

2.2V

2.2V

≠40

V

SS

V

DD

≠ 0.8

V

DD

≠ 0.8

2.5

≠10

0.7V

DD

250k

0.5V

DD

0.6

0.4

0.4

≠100

0.5V

DD

1M

0.8

0.3V

DD

0.2V

DD

0.8V

0.8V

≠240

V

DD

3.7

0.4

0.5

10

0.3V

DD

2.5M

0.5V

DD

V

V

V

V

V

V

V

V

V

V

V

V

V

µA

V

V

V

V

V

V

µA

V

V

V

V

V

1

1

2

2

3

3

3

4

4

4

11

11

11

5

13

6

7

12

8

11

9

10

Symbol

Conditions

Min.

Typ.

Max.

Unit

Applicable

pins

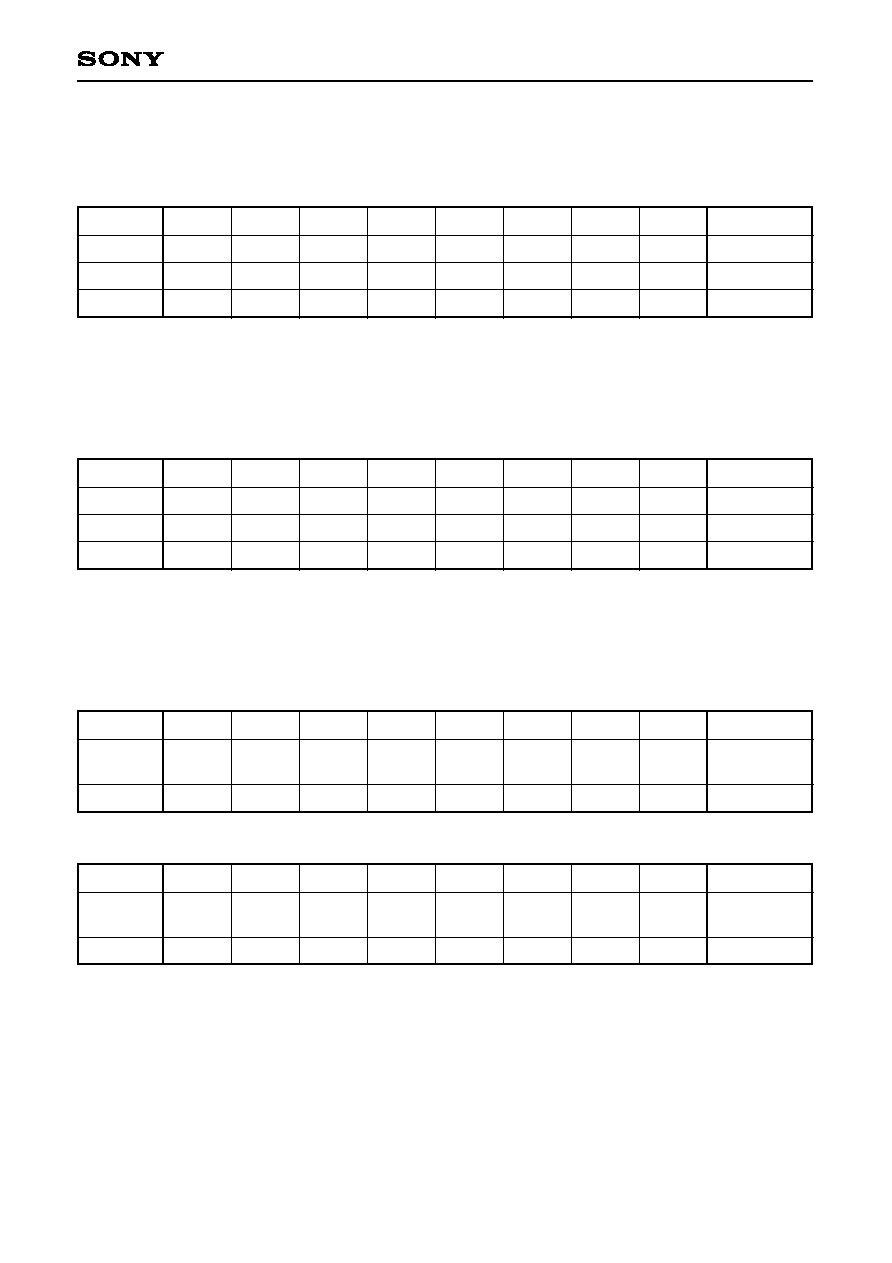

≠ 10 ≠

CXD1818R

1

D7 to 0, MDBF to 0, MDAT, LRCK, C2PO, SBIN, SCOR, WFCK, XROF

2

GRST, DACD, LRCK, BCKO, TST7 to 0

3

XRES

4

A6 to 0, XWR, XRD, XCS, BCLK, DSPCK, GSCR

5

D7 to 0, MDBF to 0

6

All output pins except XTL2, XRAS, XUCAS, XLCAS, XMWR and CLK

7

XRAS, XUCAS, XLCAS, XMWR, CLK, CM1

8

All output pins except XTL2

9

All input pins except

5

and XTL1

10

Input: XTL1, Output: XTL2

11

XRST, XBSY, XSEL, XATN, XMSG, XCD, XIO, XREQ, XACK, XDBP, XDB7 to 0

12

XREQ, XACK, XDBP and XDB7 to 0 when active negation is ON

13

AC

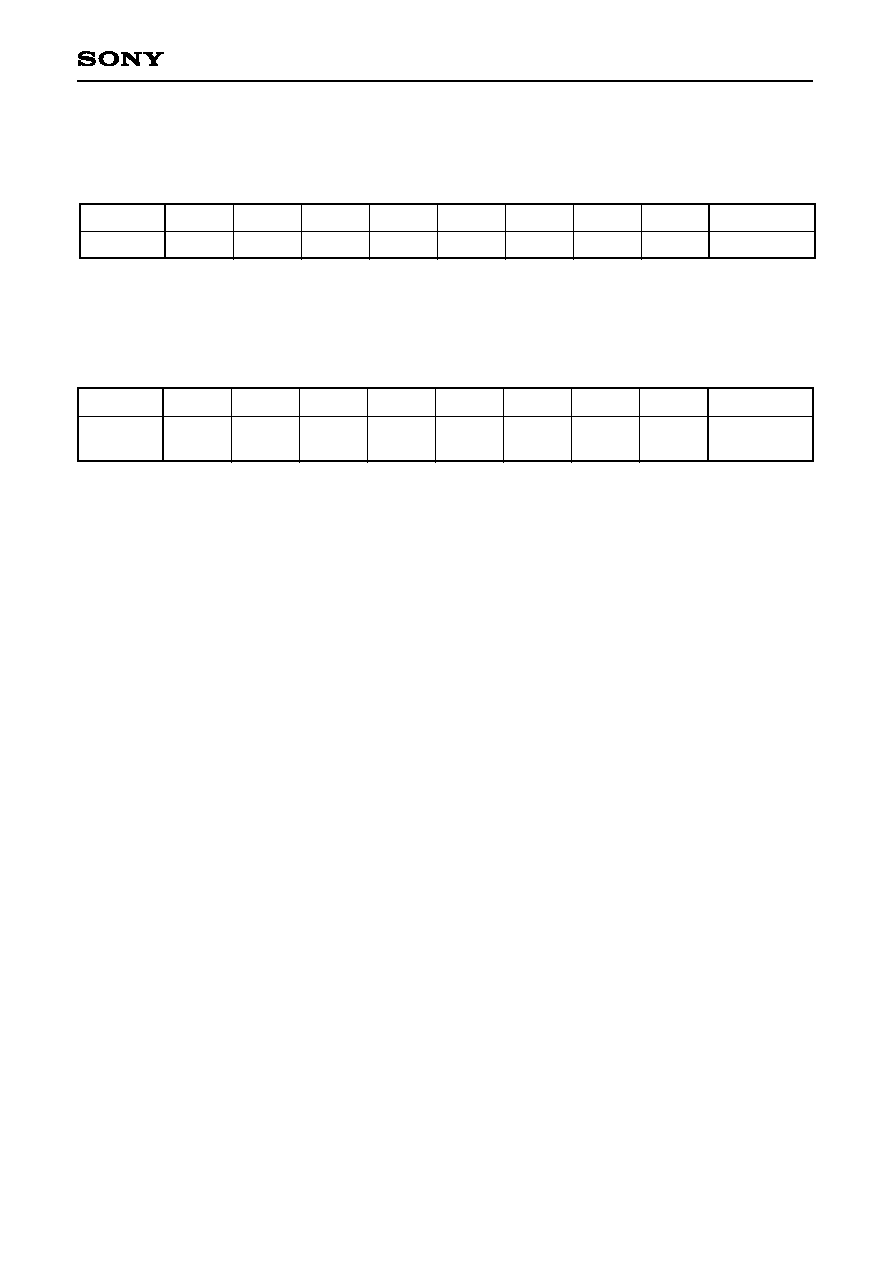

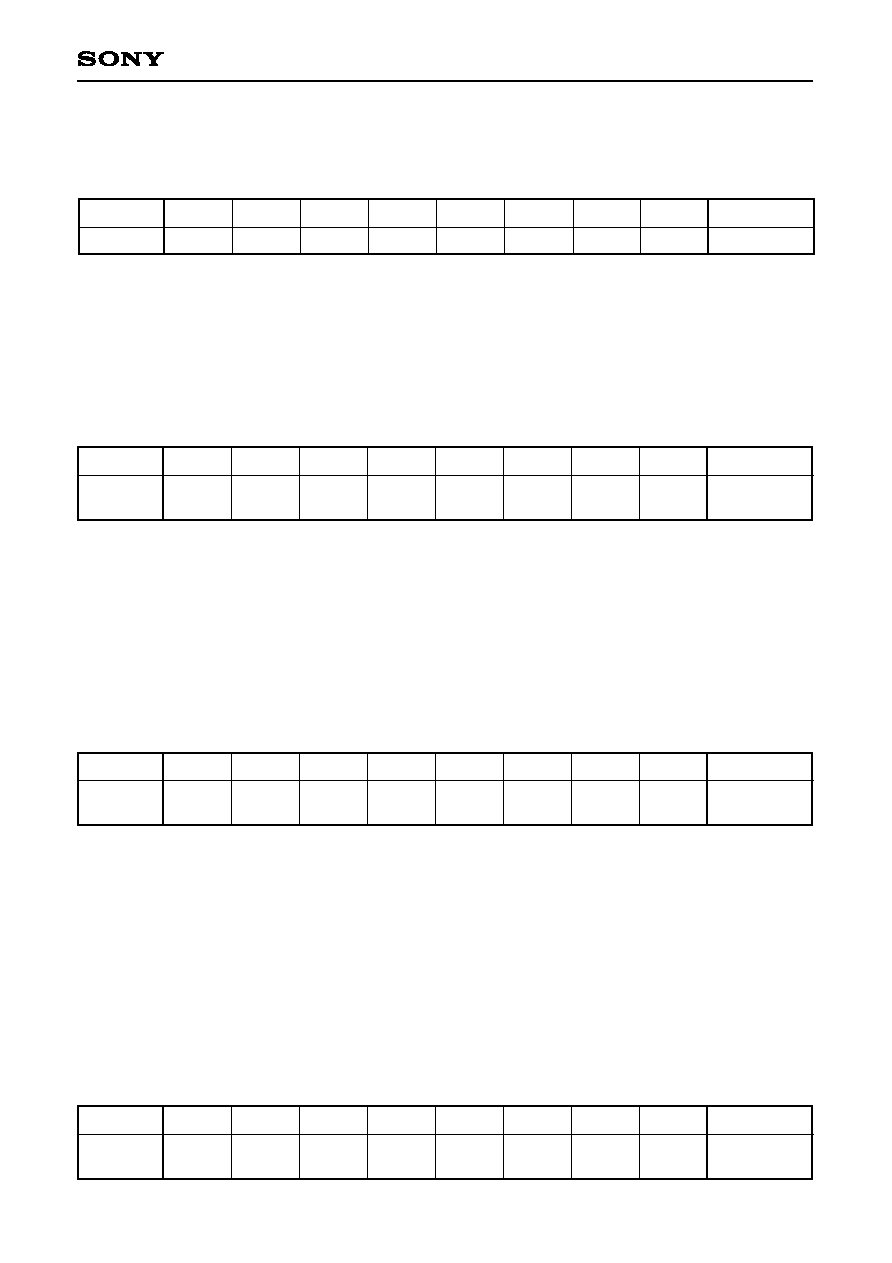

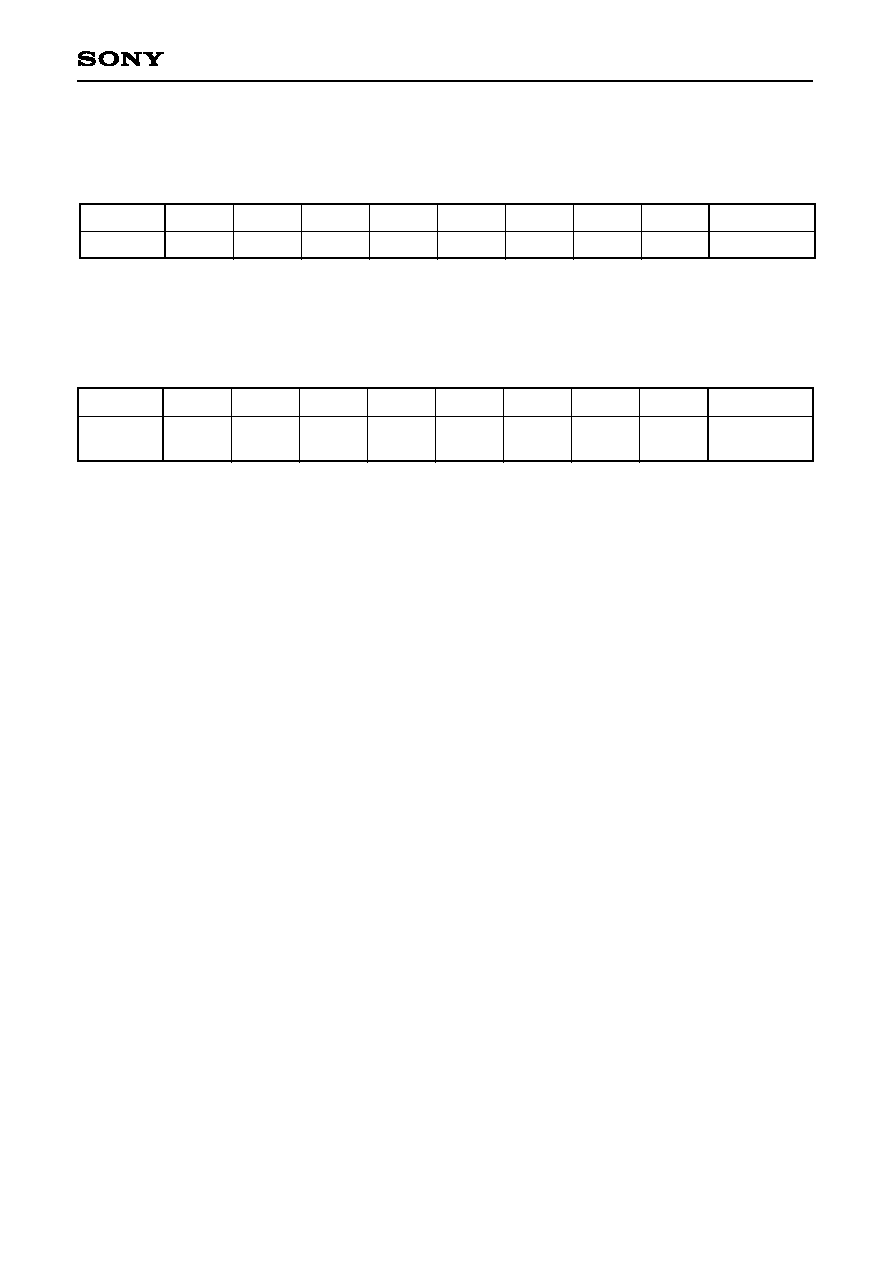

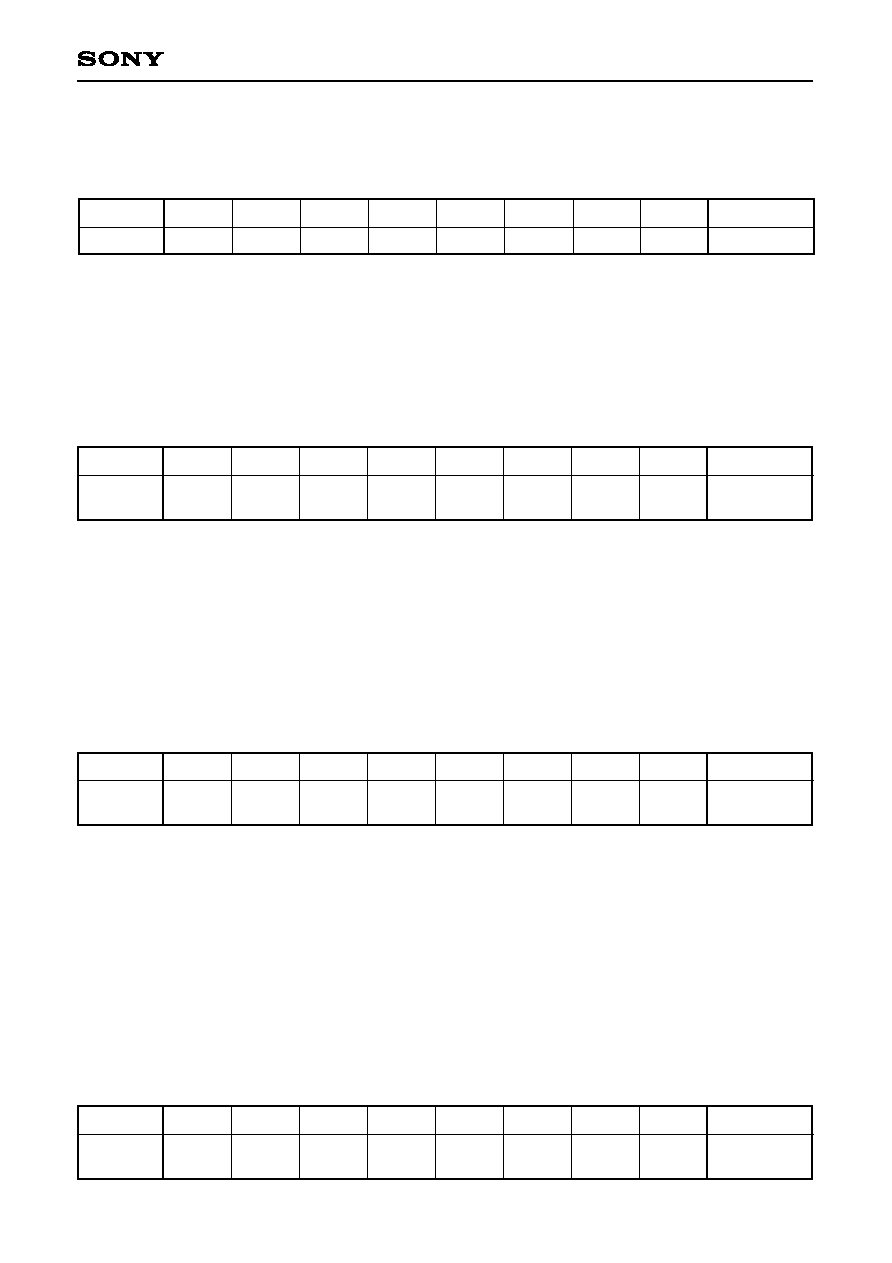

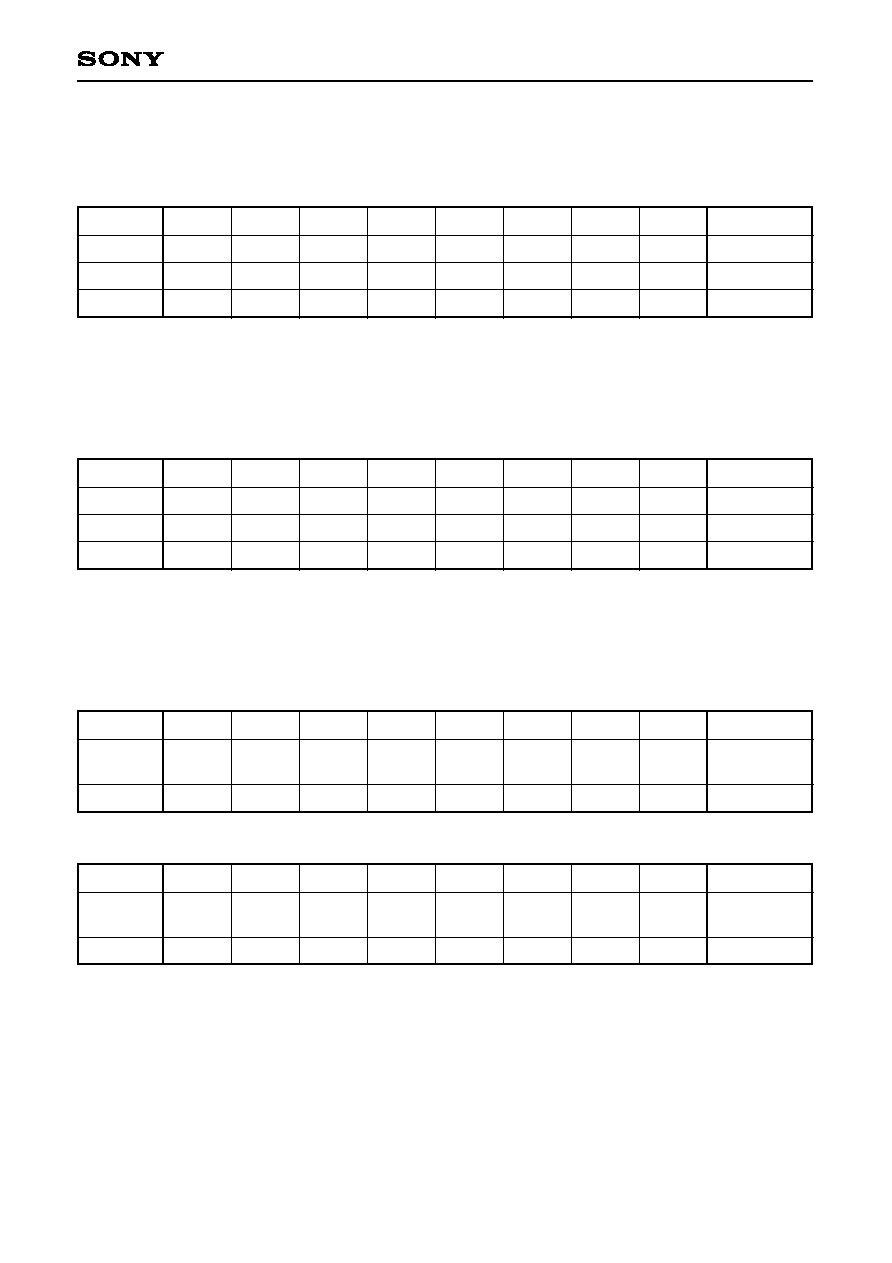

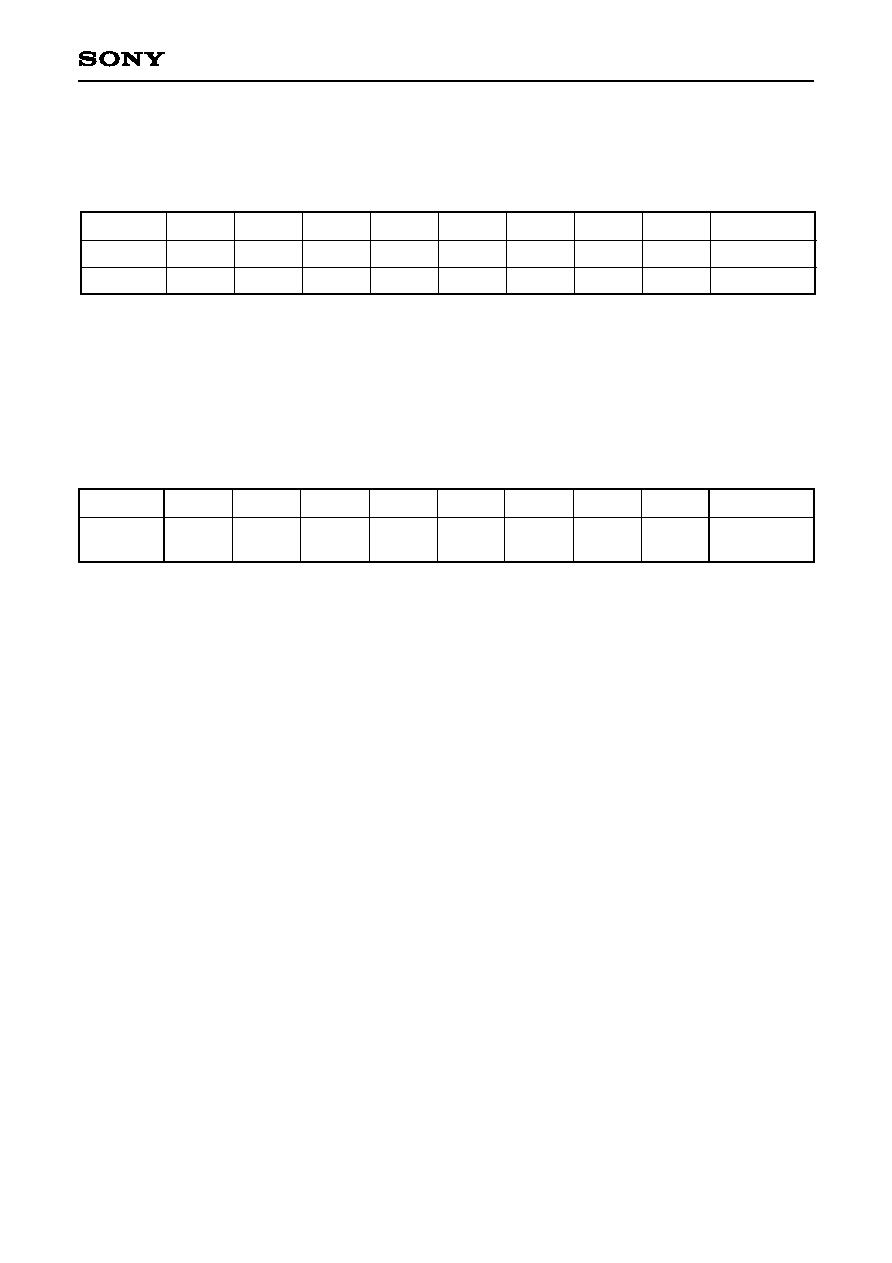

I/O Capacitance

(V

DD

= V

I

= 0V, f = 1MHz)

Item

Input capacitance

Output capacitance

I/O capacitance

C

IN

C

OUT

C

I/O

9

11

11

pF

pF

pF

Symbol

Min.

Typ.

Max.

Unit

≠ 11 ≠

CXD1818R

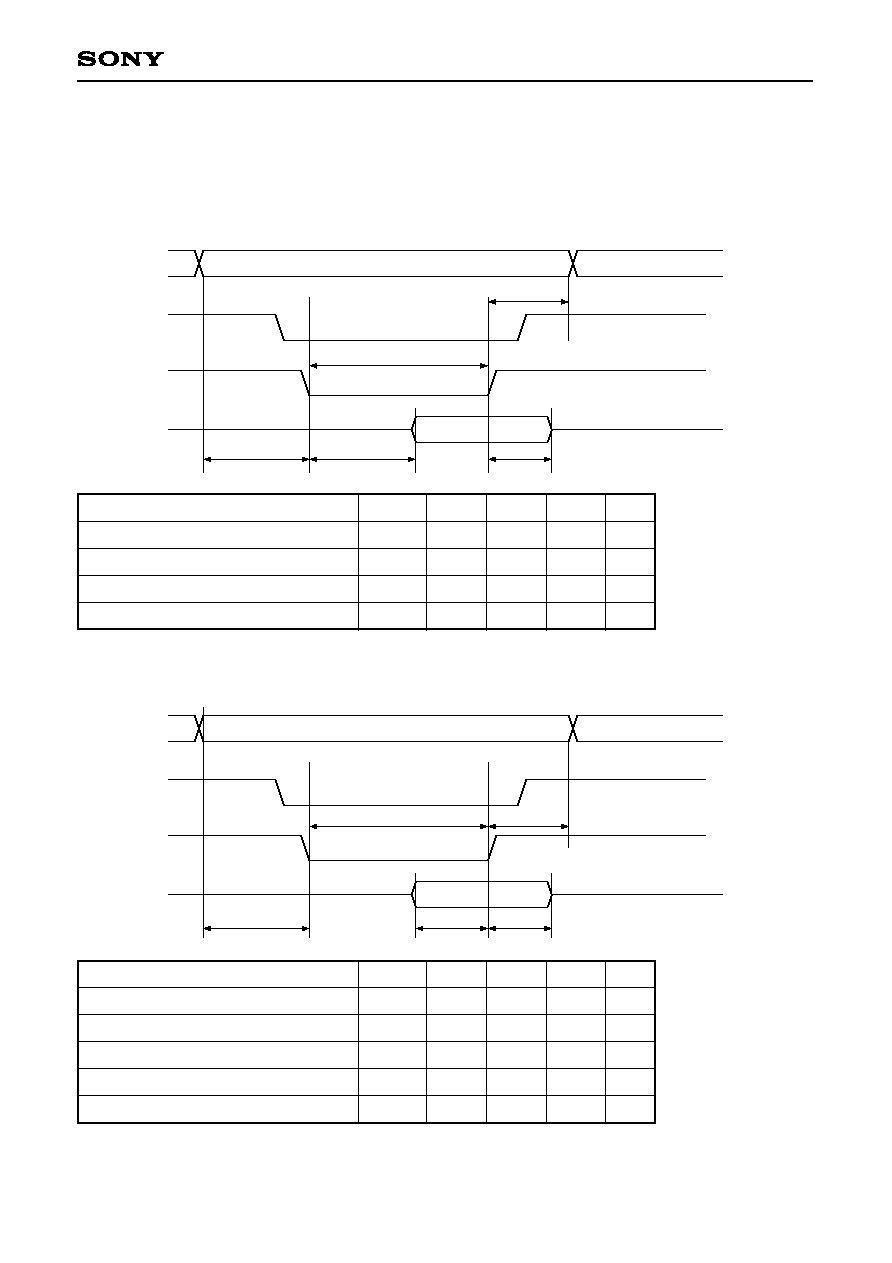

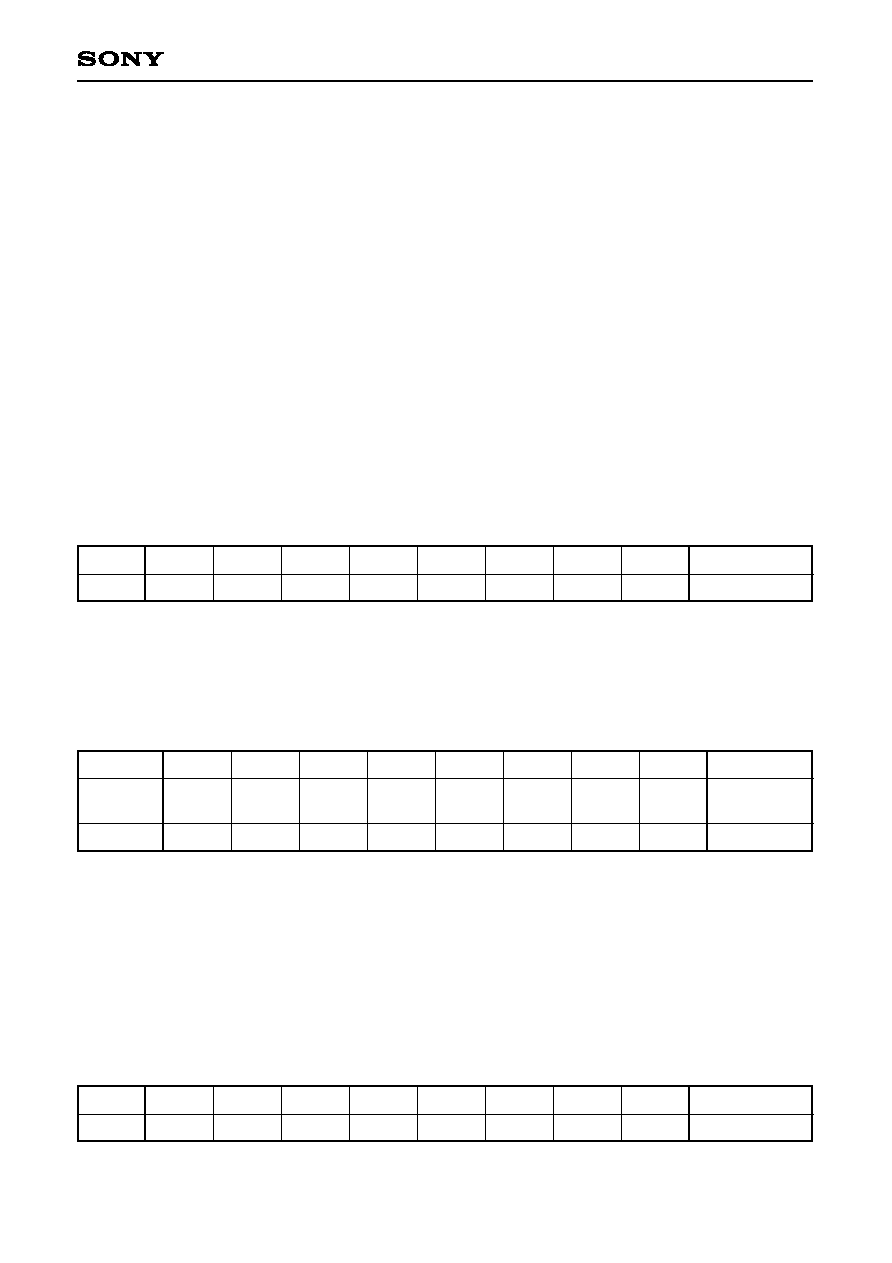

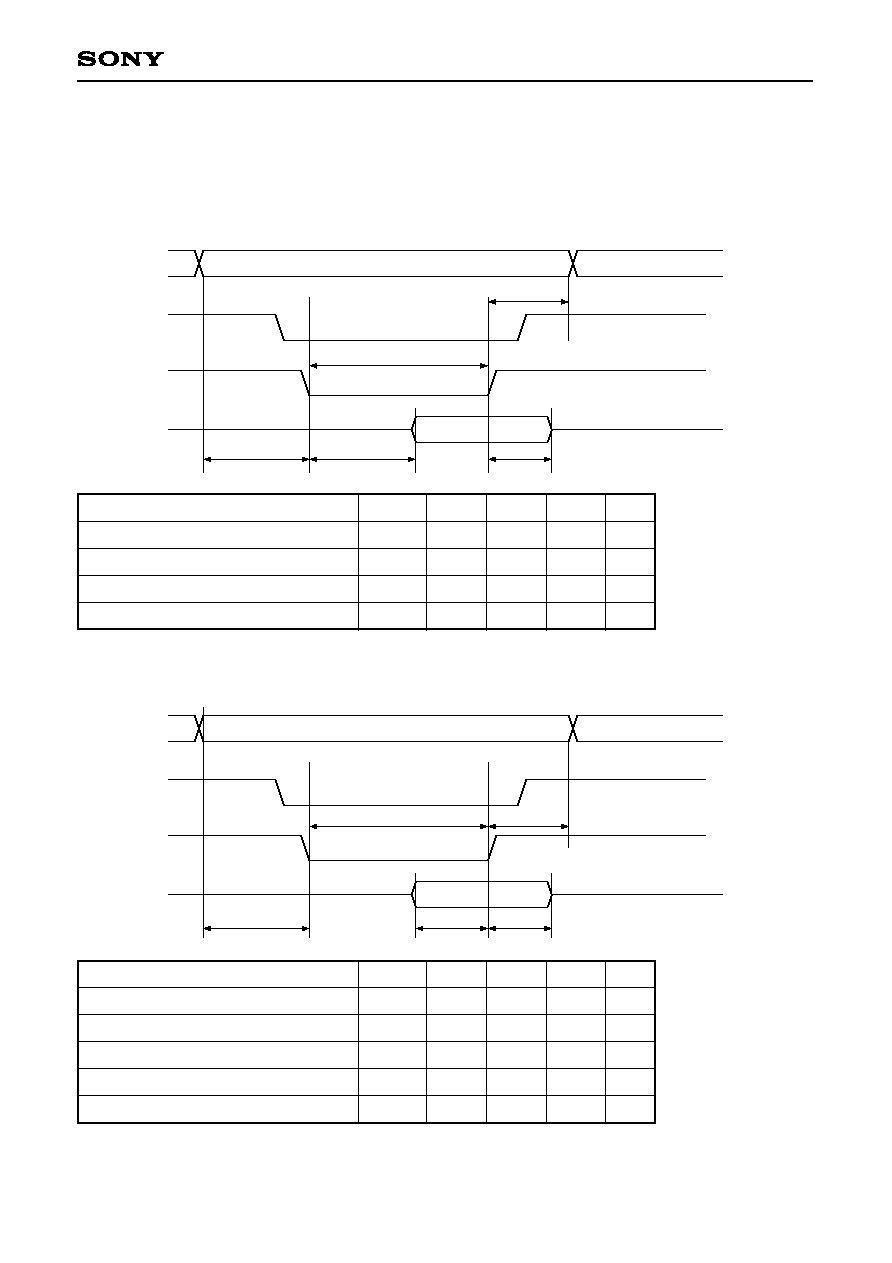

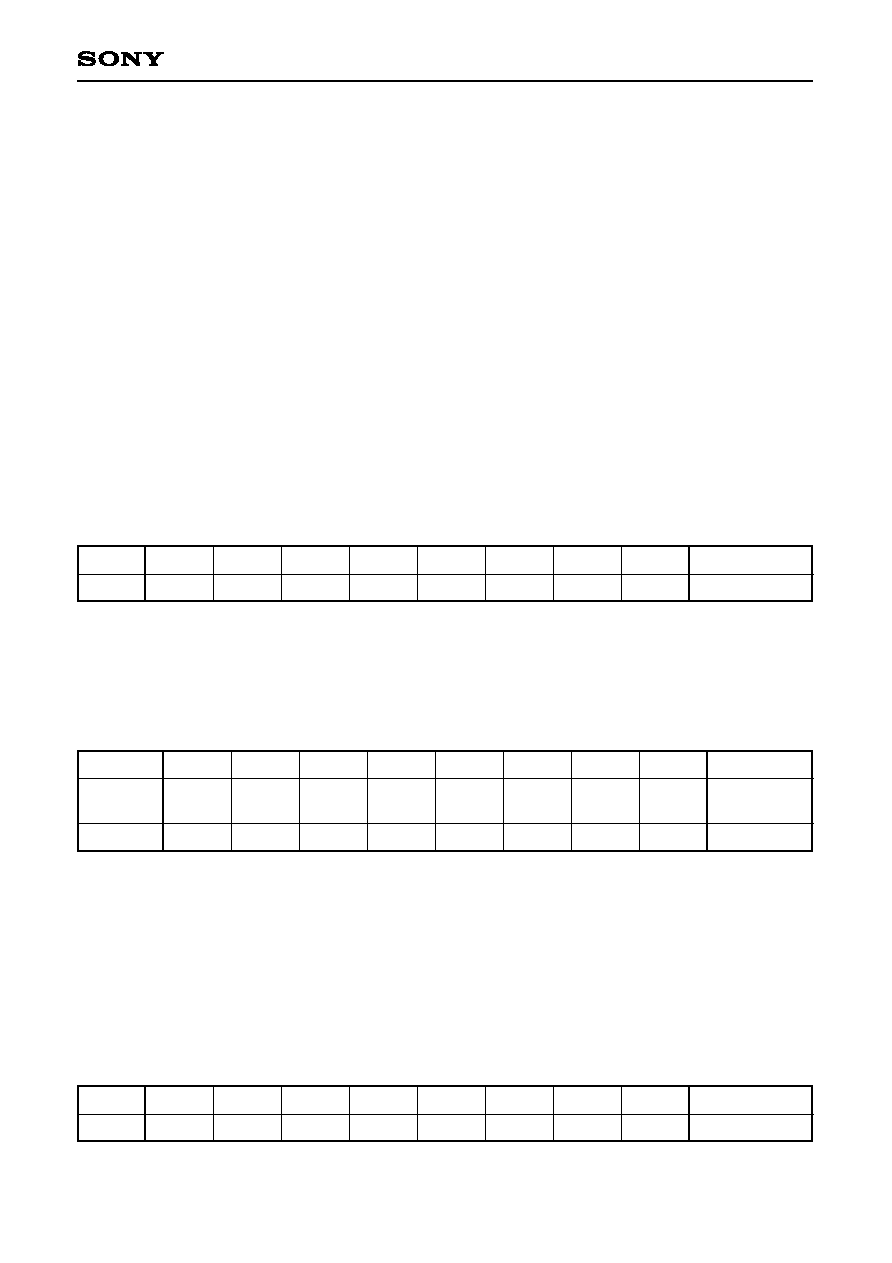

AC Characteristics

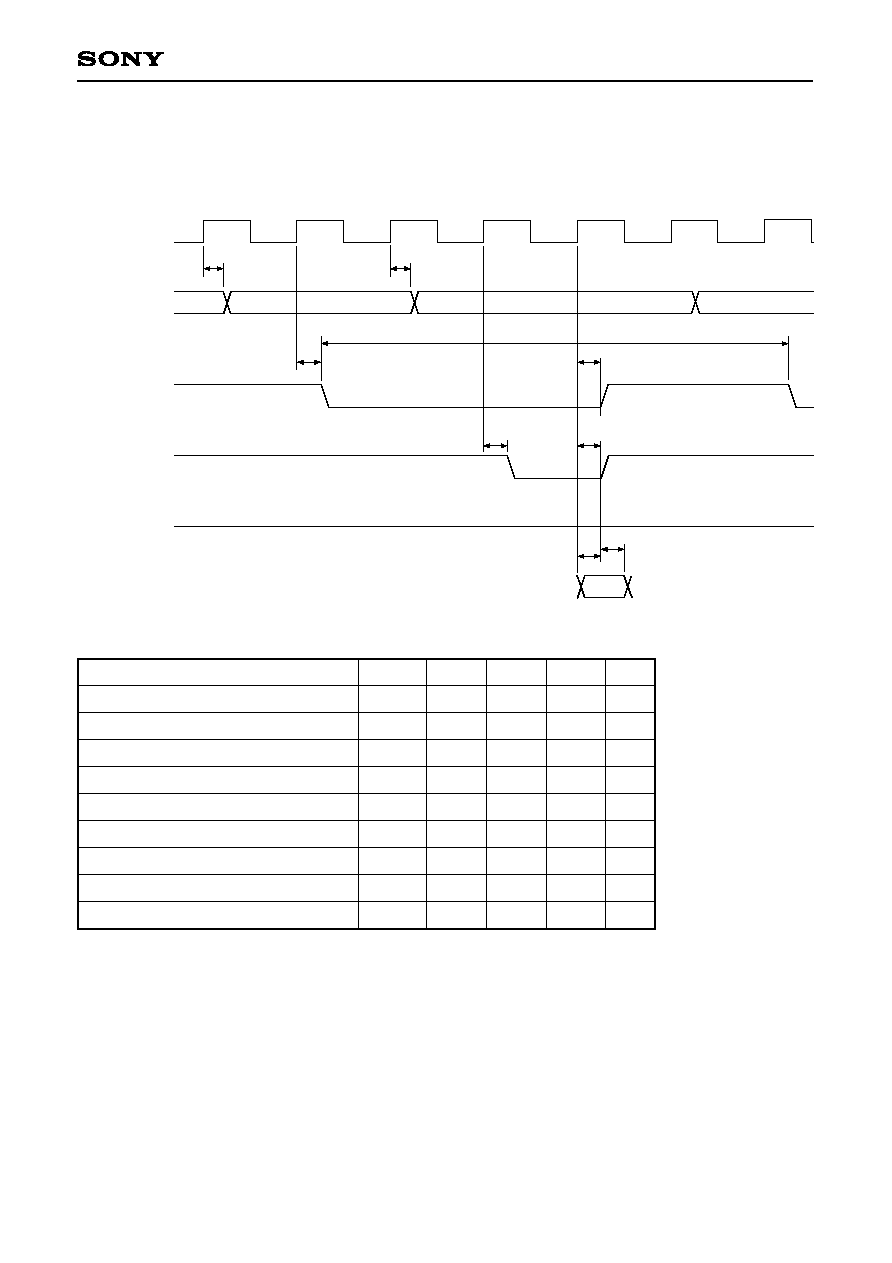

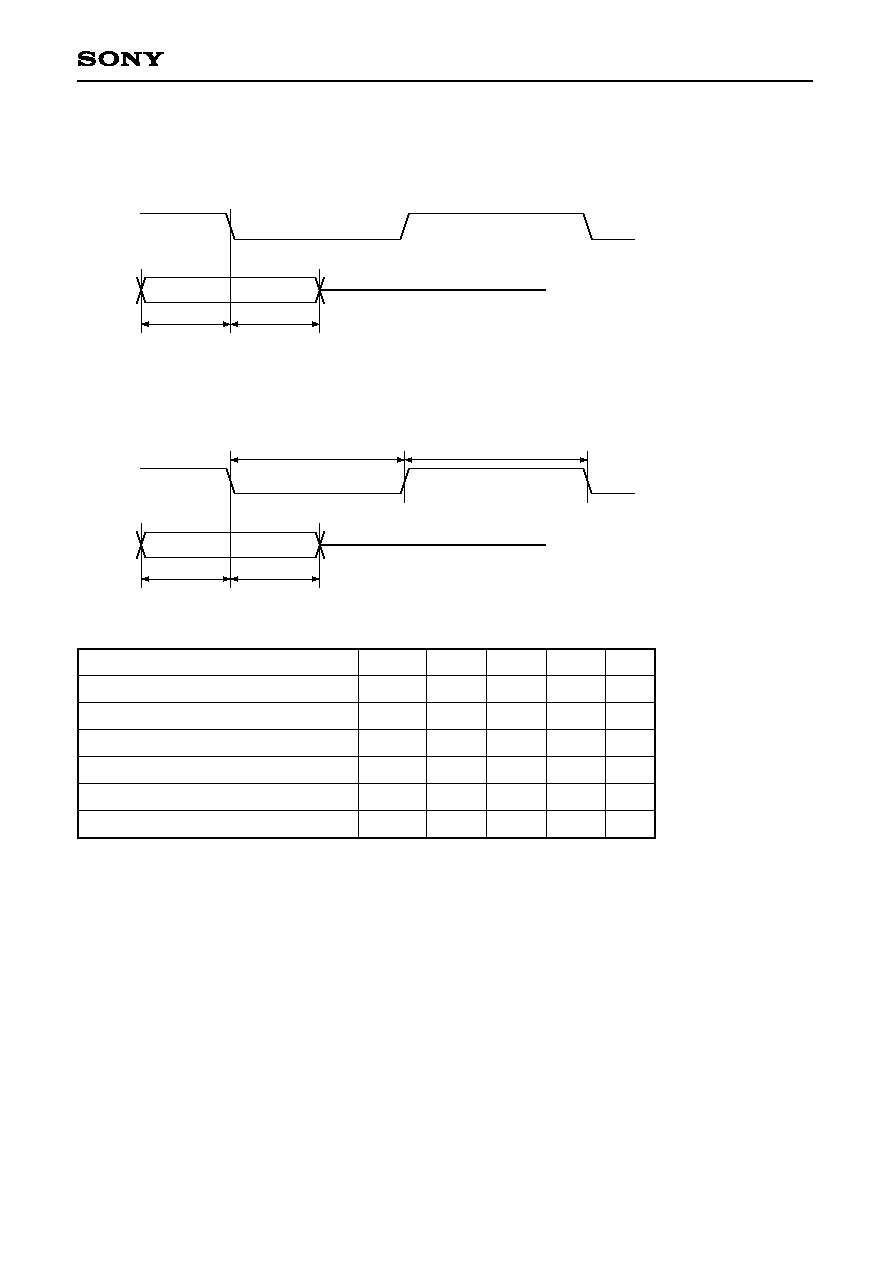

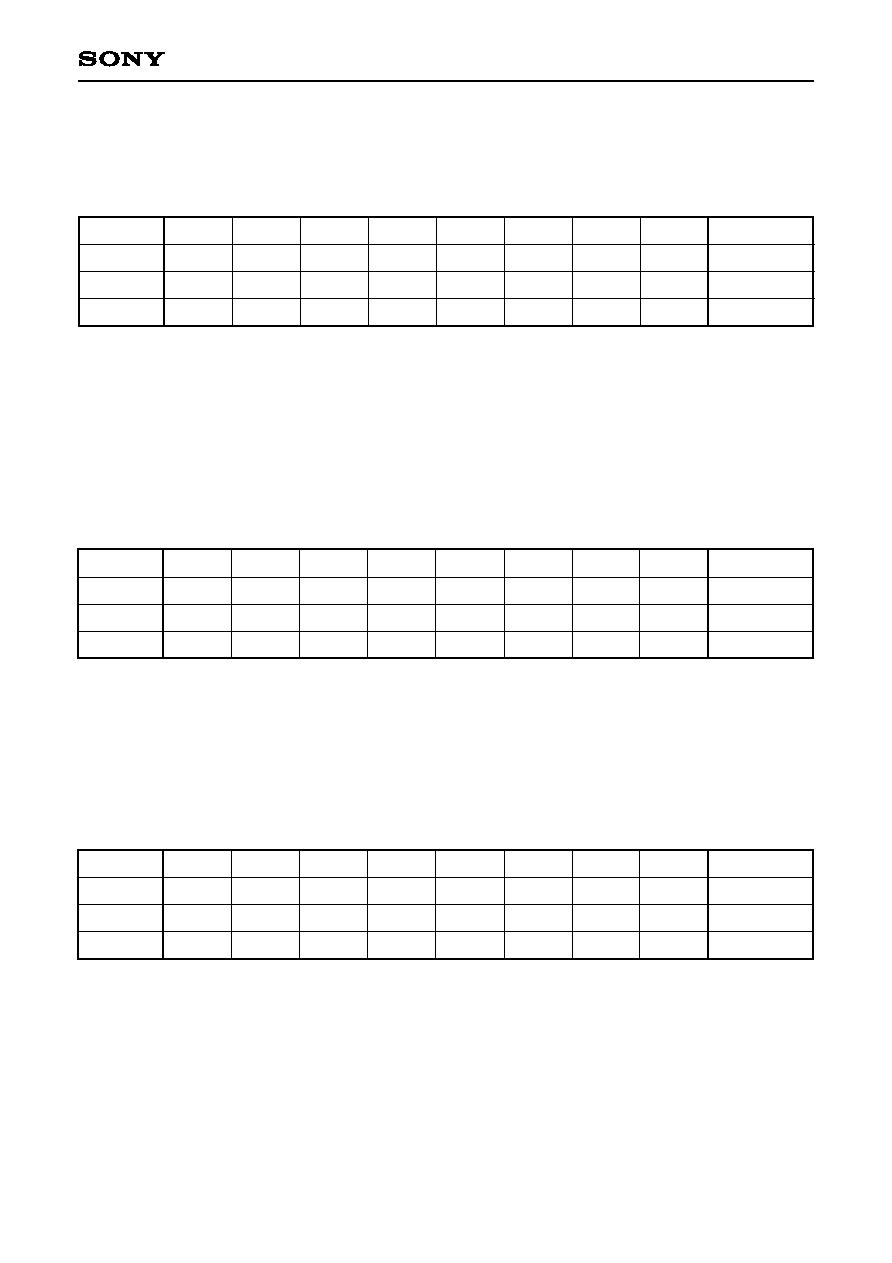

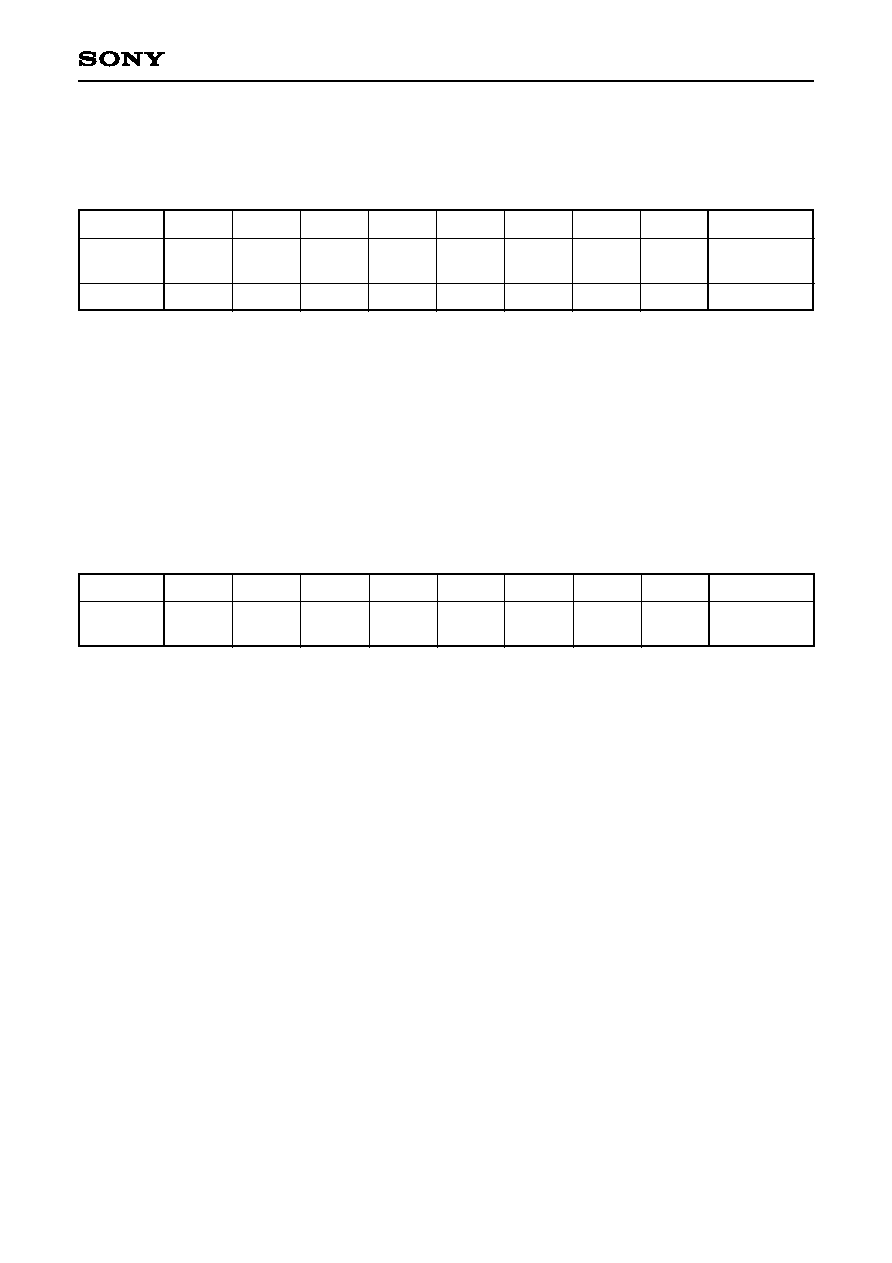

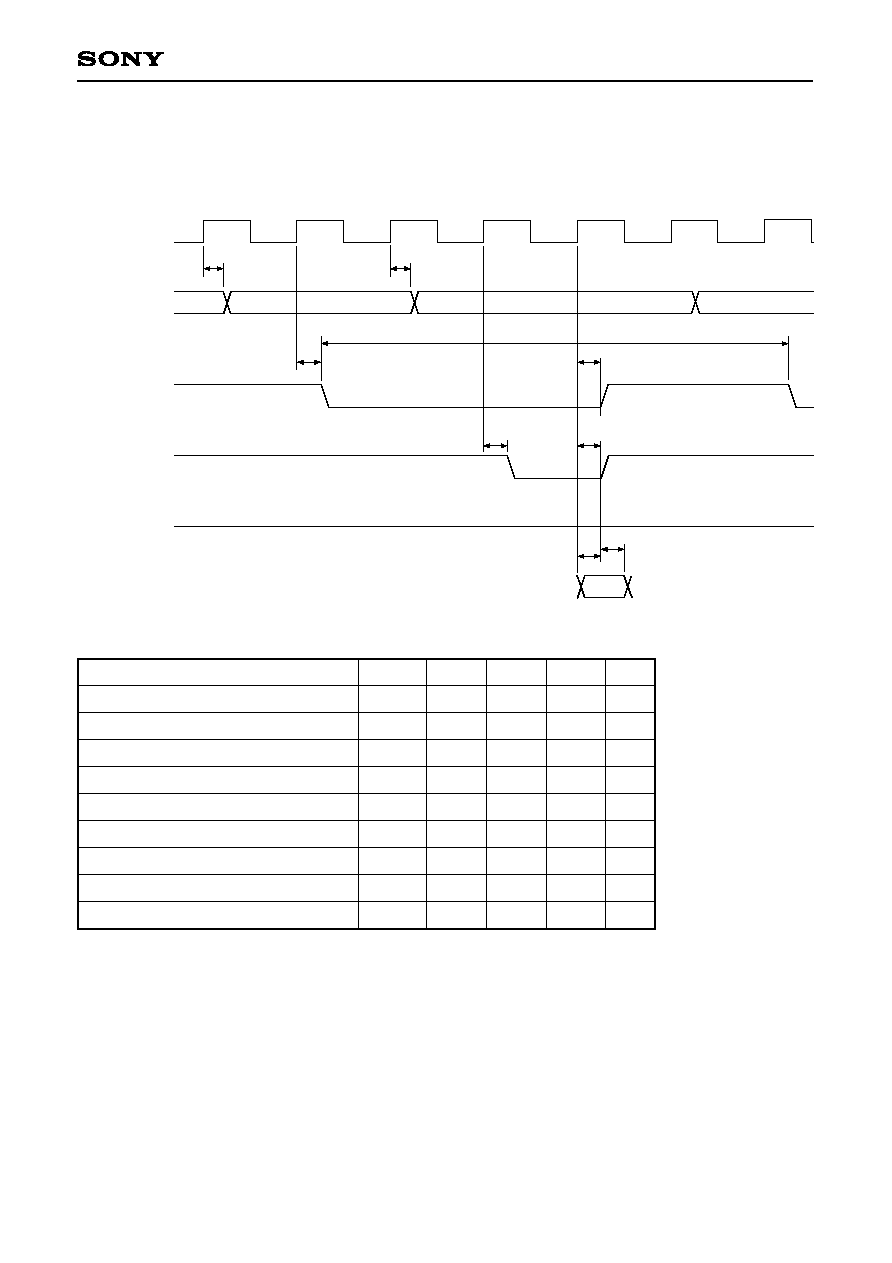

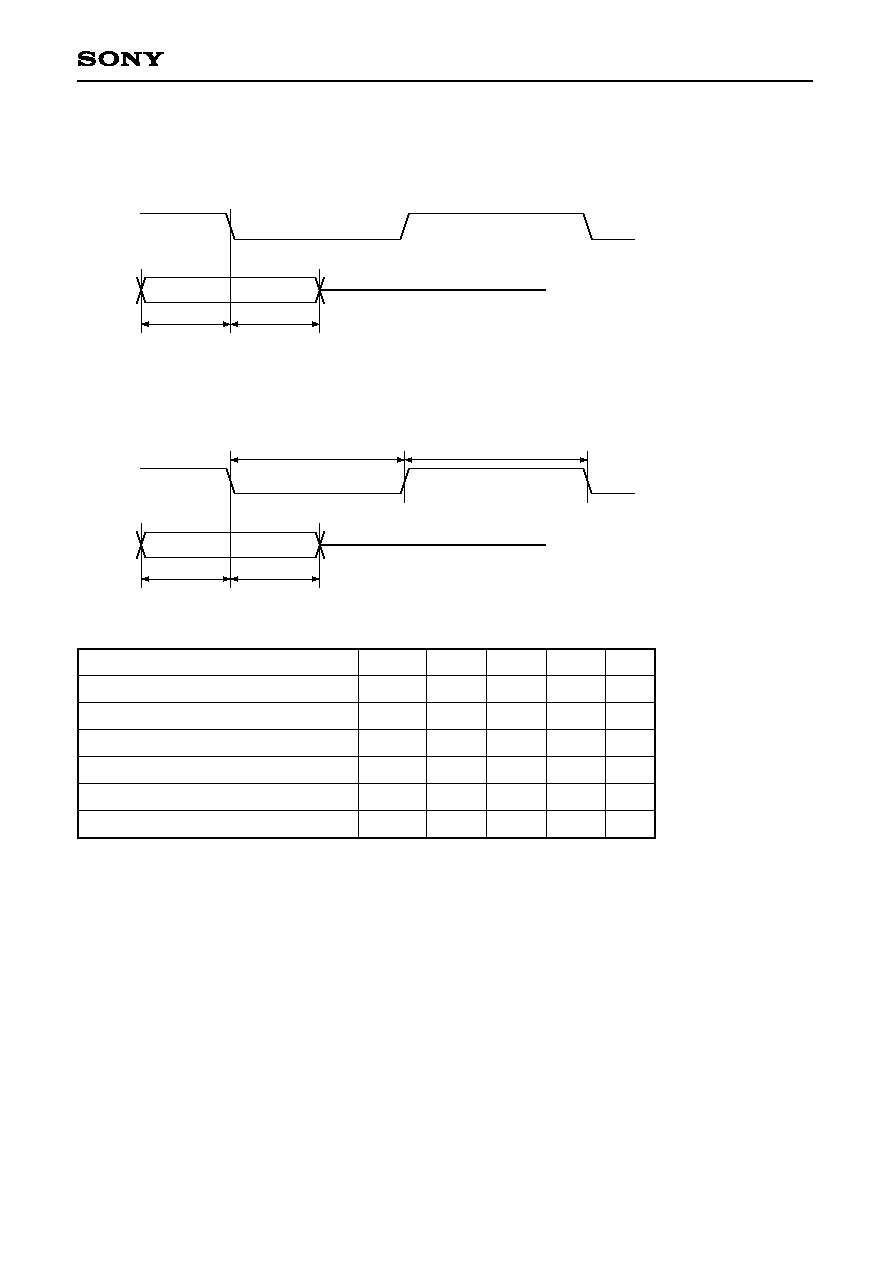

1. Sub CPU Interface (Output Load = 50pF)

(1) Read

Tsar

Thar

A6 to 0

XCS

XRD

D7 to 0

Tdrd

Tfrd

Trrl

Item

Address setup time (for XCS & XRD

)

Address hold time (for XCS & XRD

)

Data delay time (for XCS & XRD

)

Data float time (for XCS & XRD

)

Tsar

Thar

Tdrd

Tfrd

10

10

0

35

15

ns

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

Tsaw

Thwa

A6 to 0

XCS

XWR

D7 to 0

Tsdw

Thdw

Twwl

Item

Address setup time (for XCS & XWR

)

Address hold time (for XCS & XWR

)

Data setup time (for XCS & XWR

)

Data hold time (for XCS & XWR

)

Low level XWR pulse width

Tsaw

Thaw

Tsdw

Thdw

Twwl

20

10

20

10

30

ns

ns

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

(2) Write

≠ 12 ≠

CXD1818R

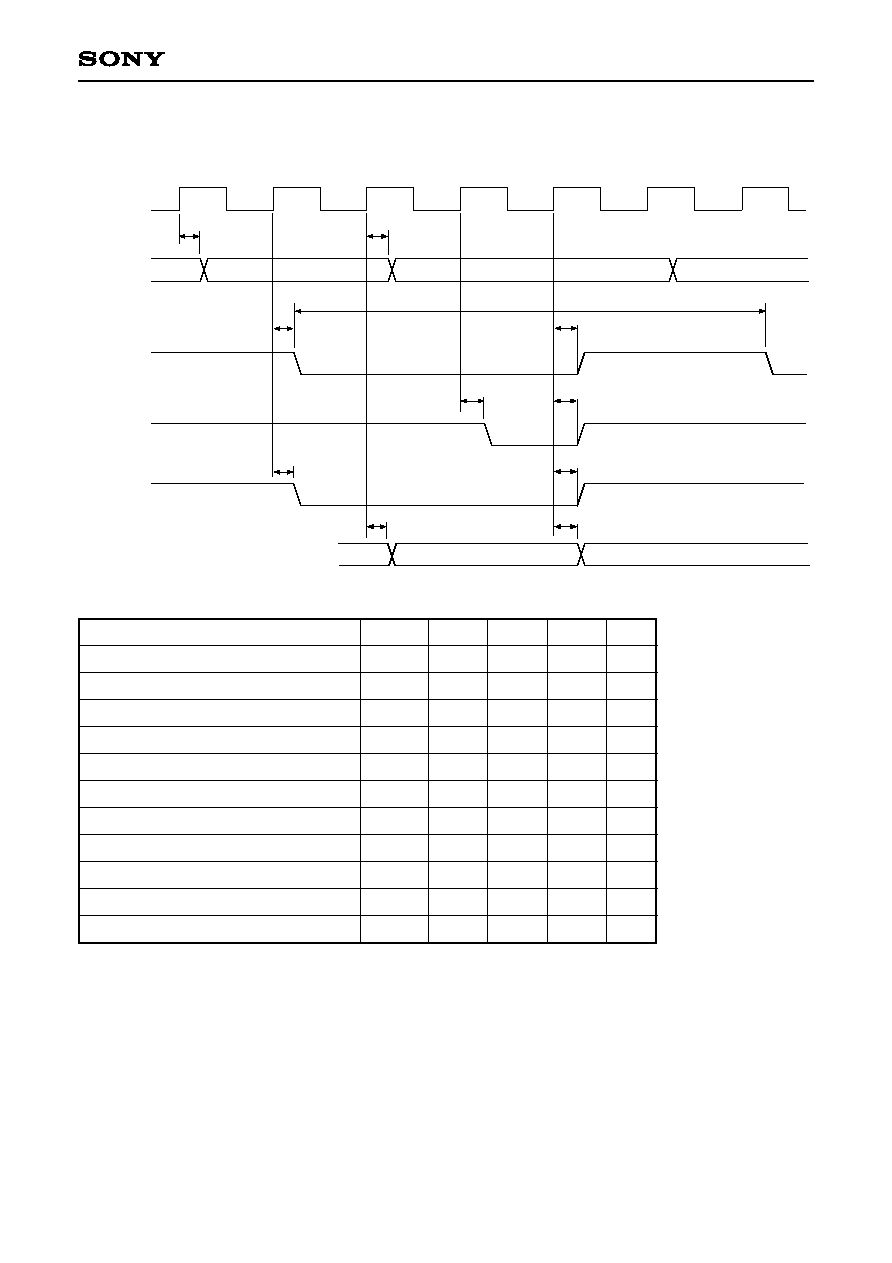

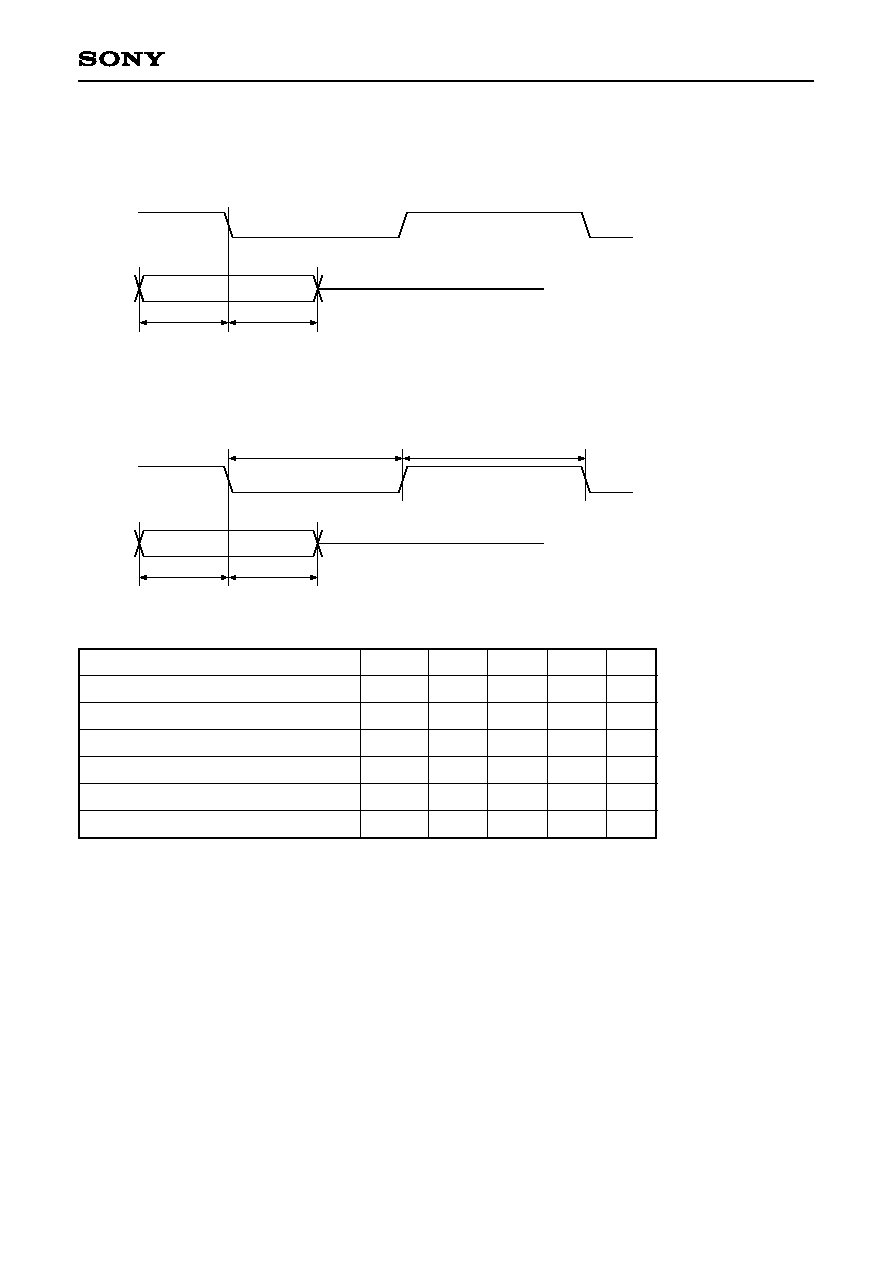

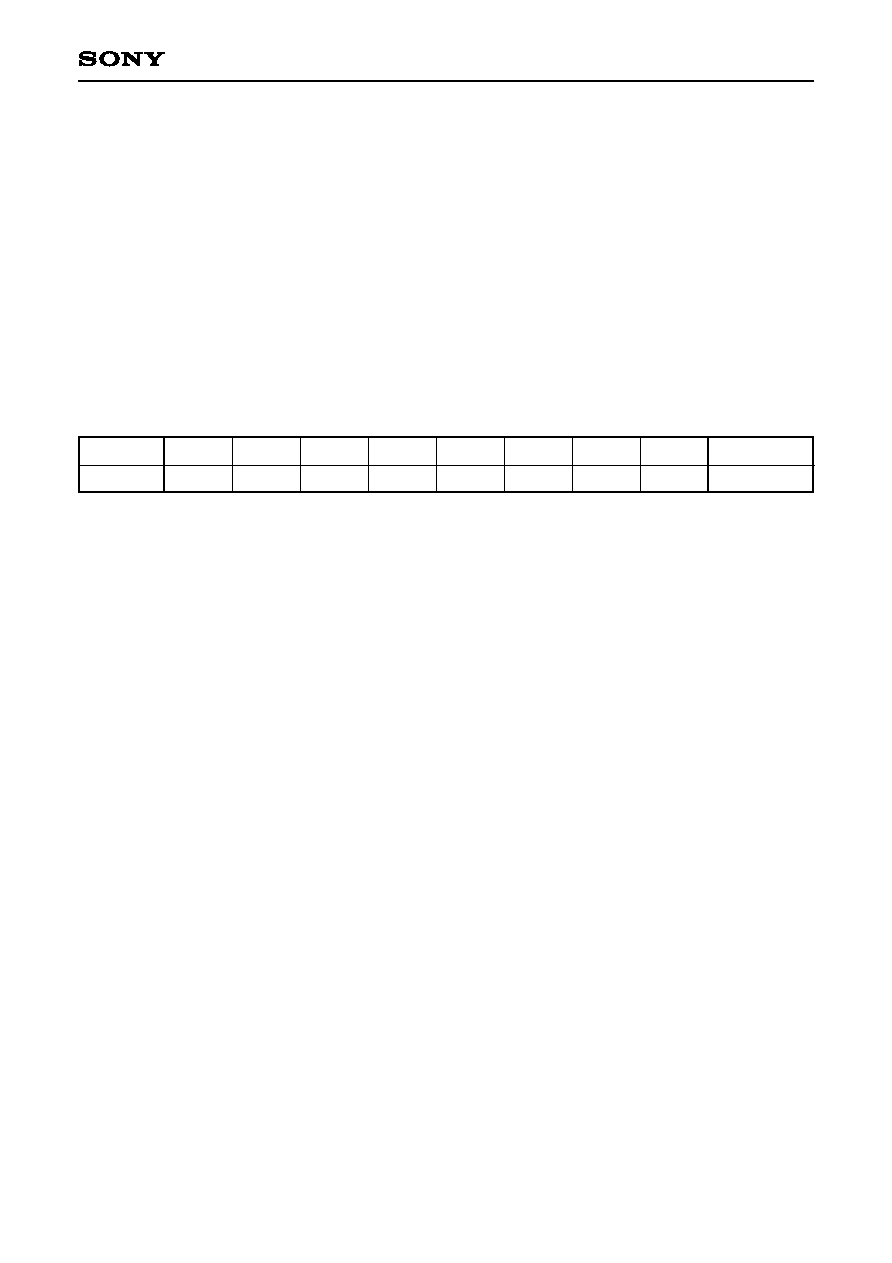

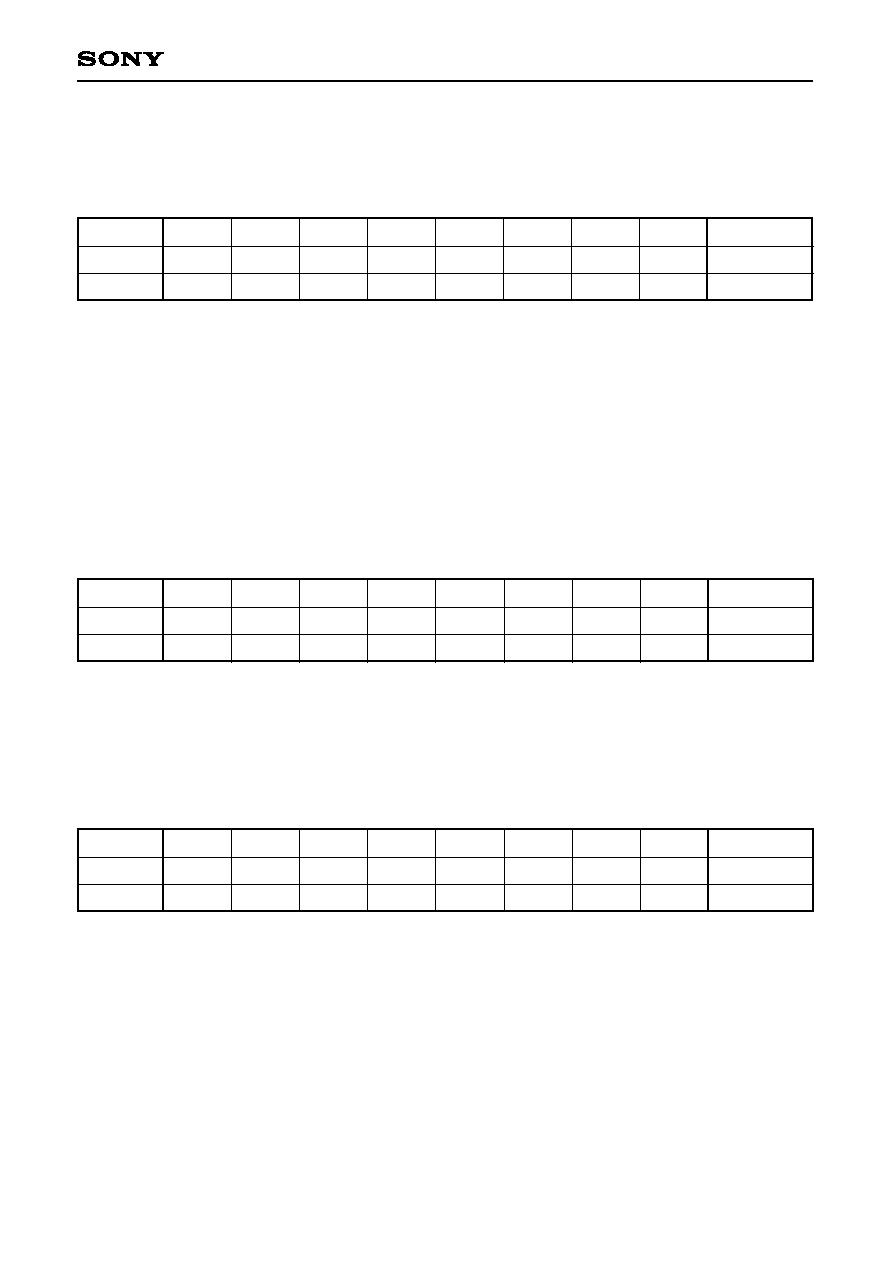

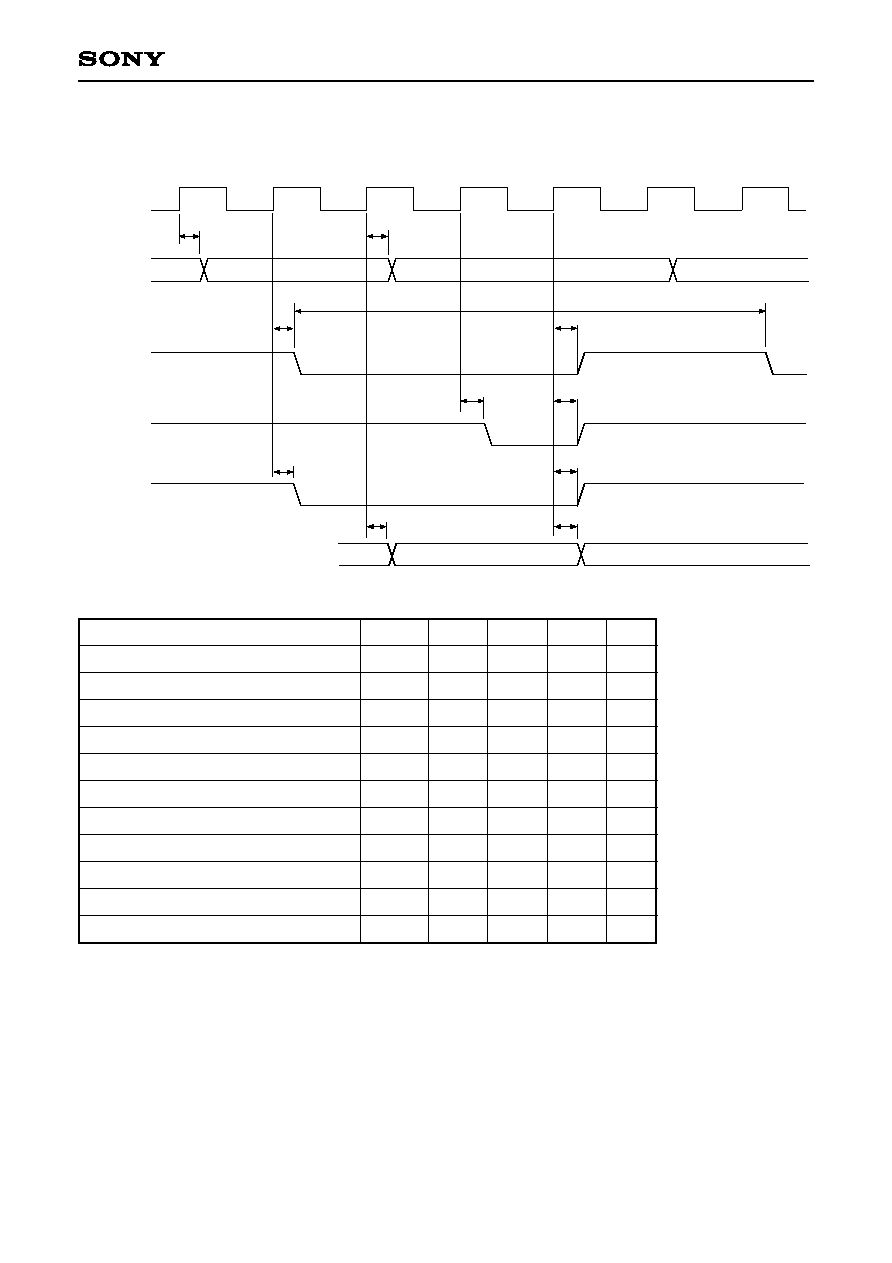

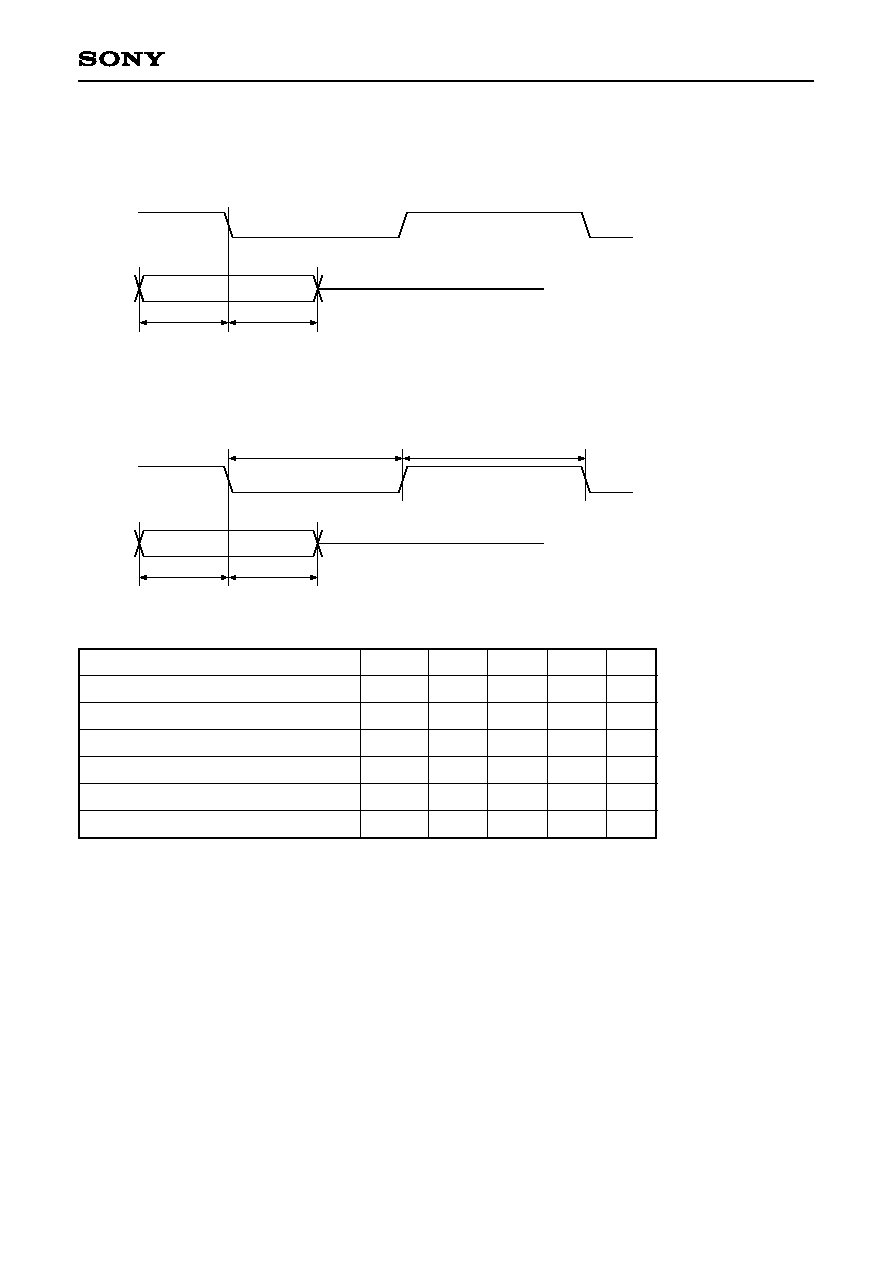

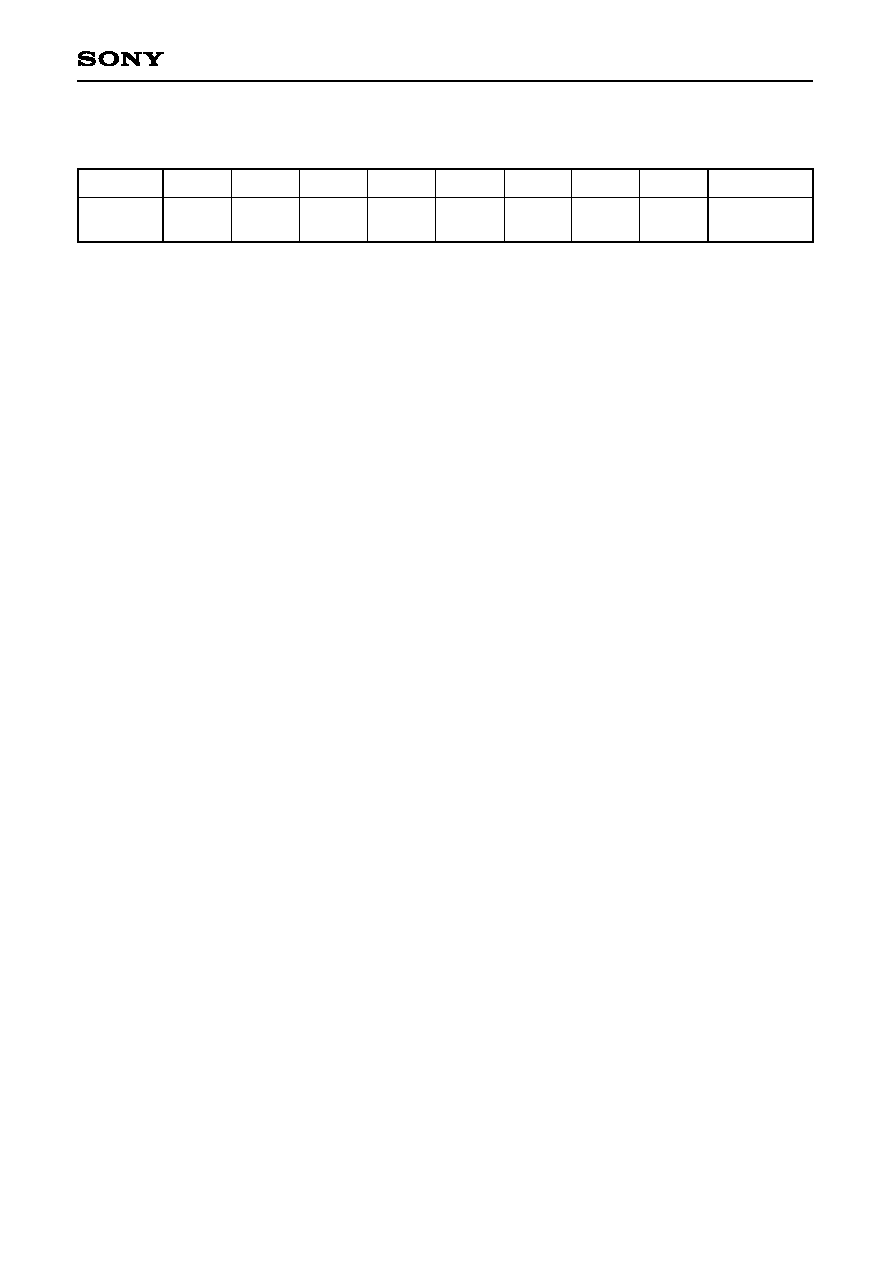

2. CD DSP Interface

BCKRED = "H"

Tbck

Tbck

Tsb1

Thb1

Tsb2

Thb2

BCLK

DATA

LRCK

C2PO

BCKRED = "L"

Tbck

Tbck

Tsb1

Thb1

Tsb2

Thb2

BCLK

DATA

LRCK

C2PO

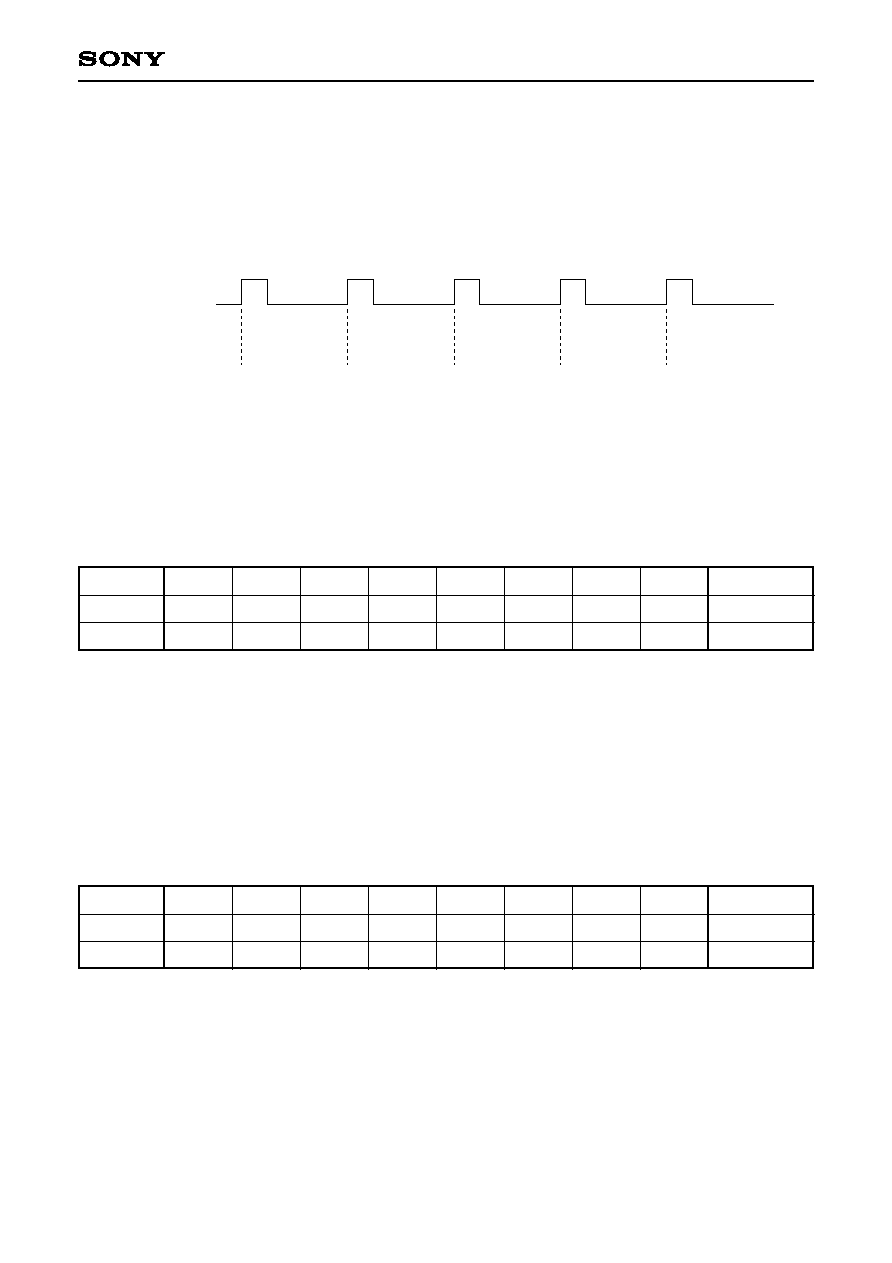

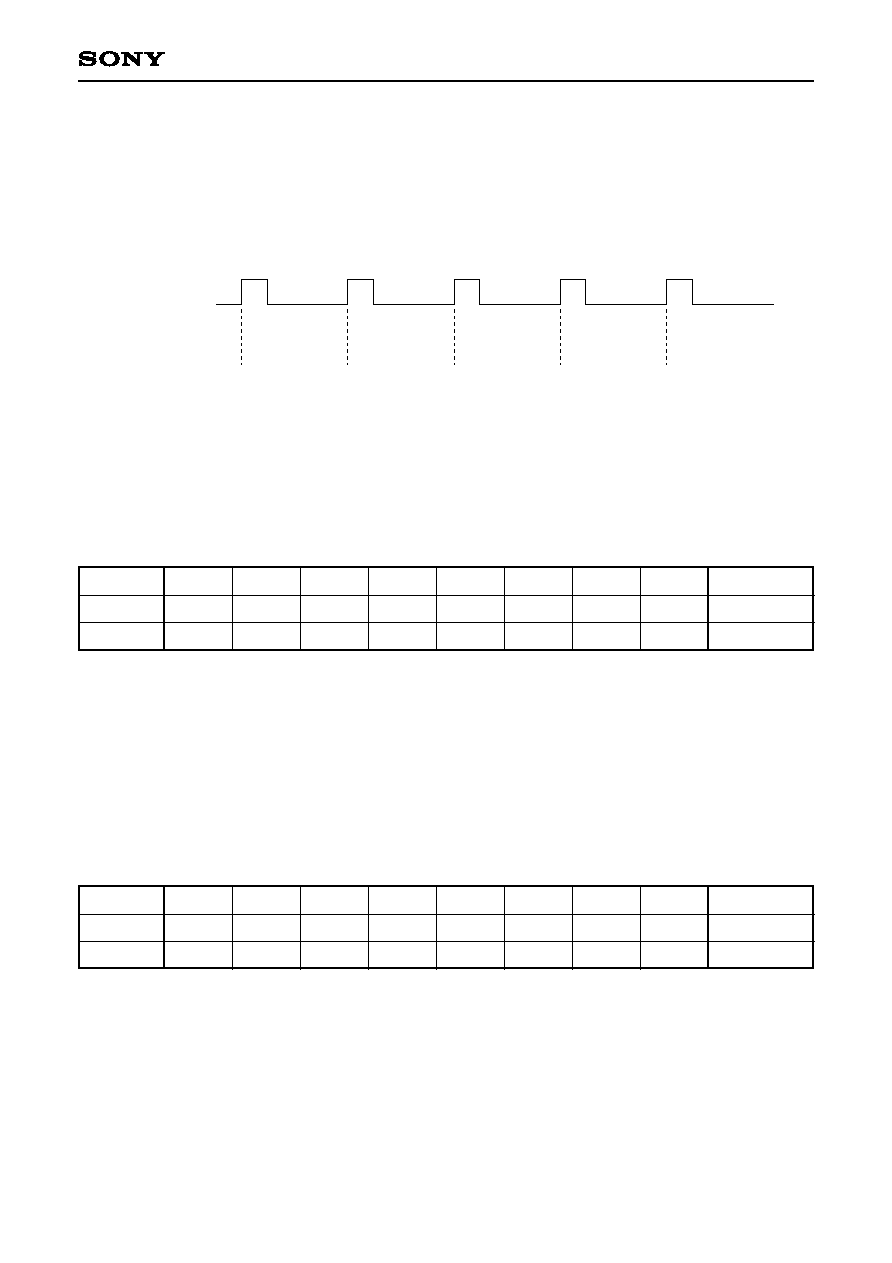

Item

BCLK frequency

BCLK pulse width

DATA setup time (for BCLK)

DATA hold time (for BCLK)

LRCK, C2PO setup time (for BCLK)

LRCK, C2PO hold time (for BCLK)

Fbck

Tbck

Tsb1

Thb1

Tsb2

Thb2

19

10

10

10

10

26

MHz

ns

ns

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

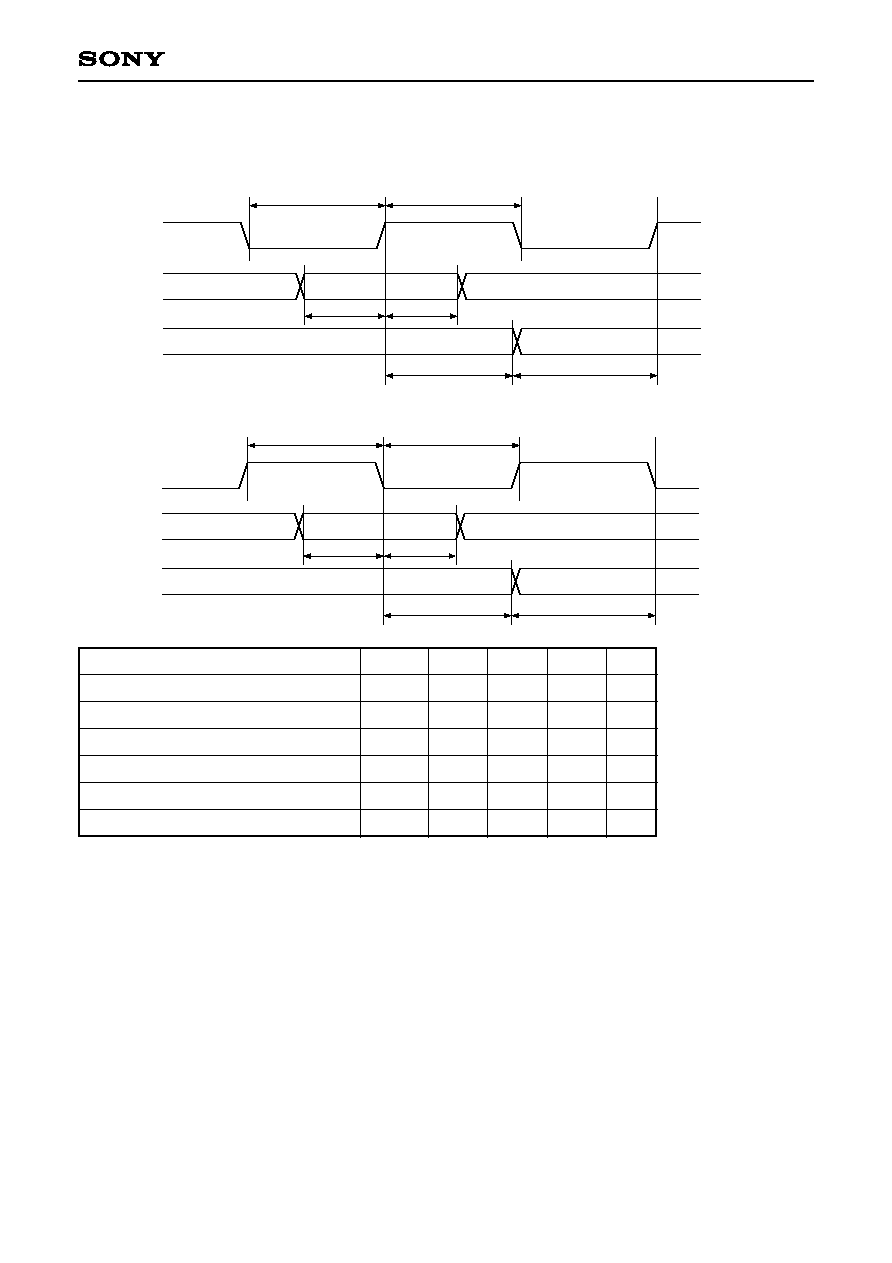

≠ 13 ≠

CXD1818R

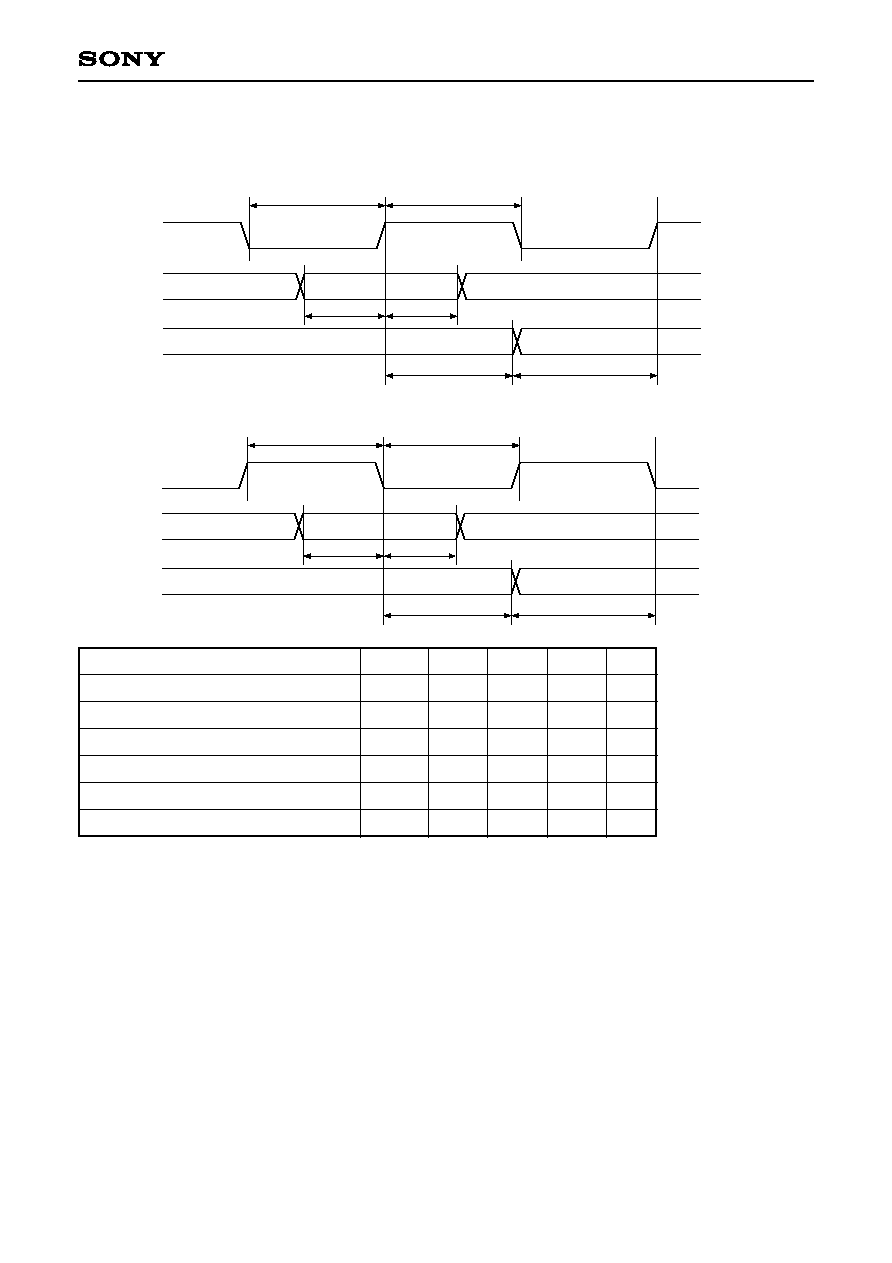

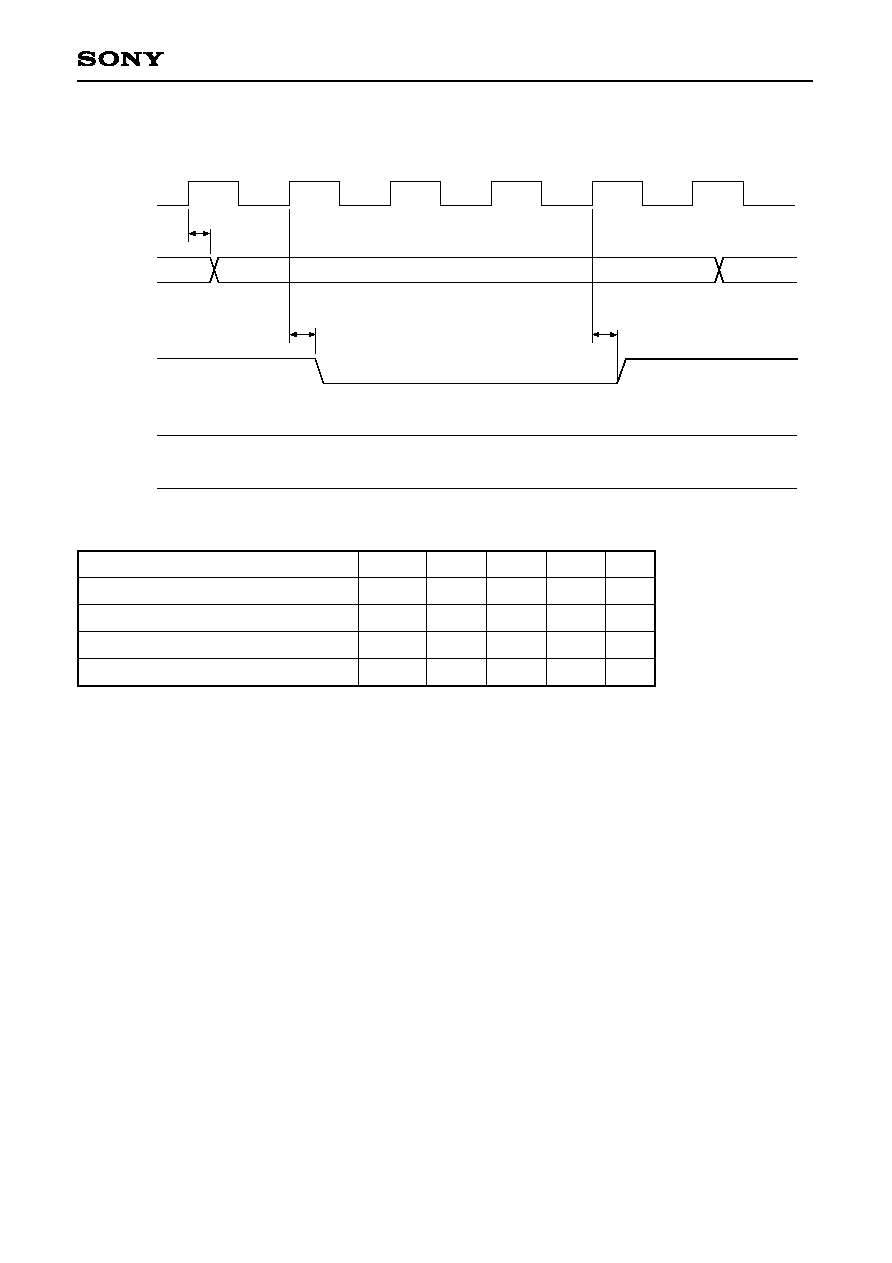

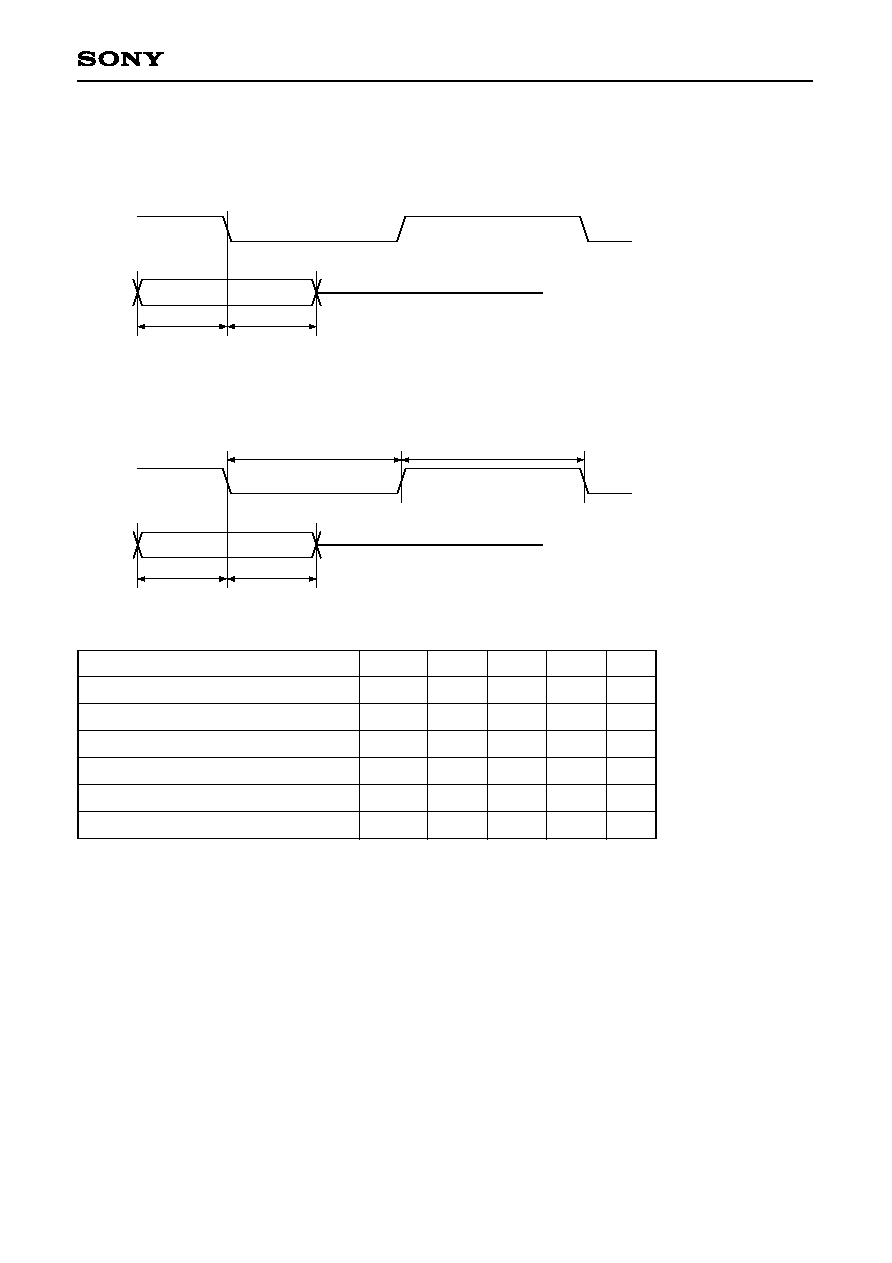

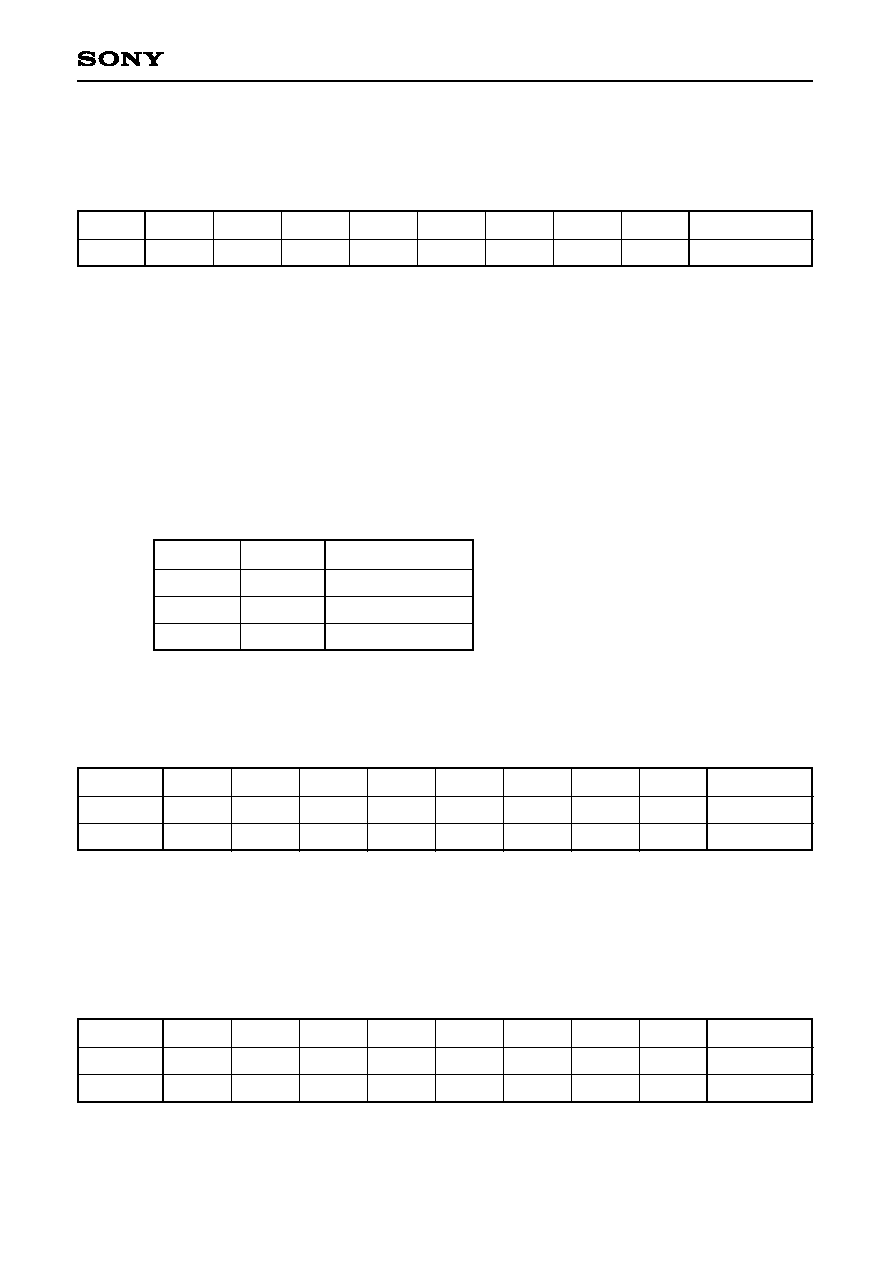

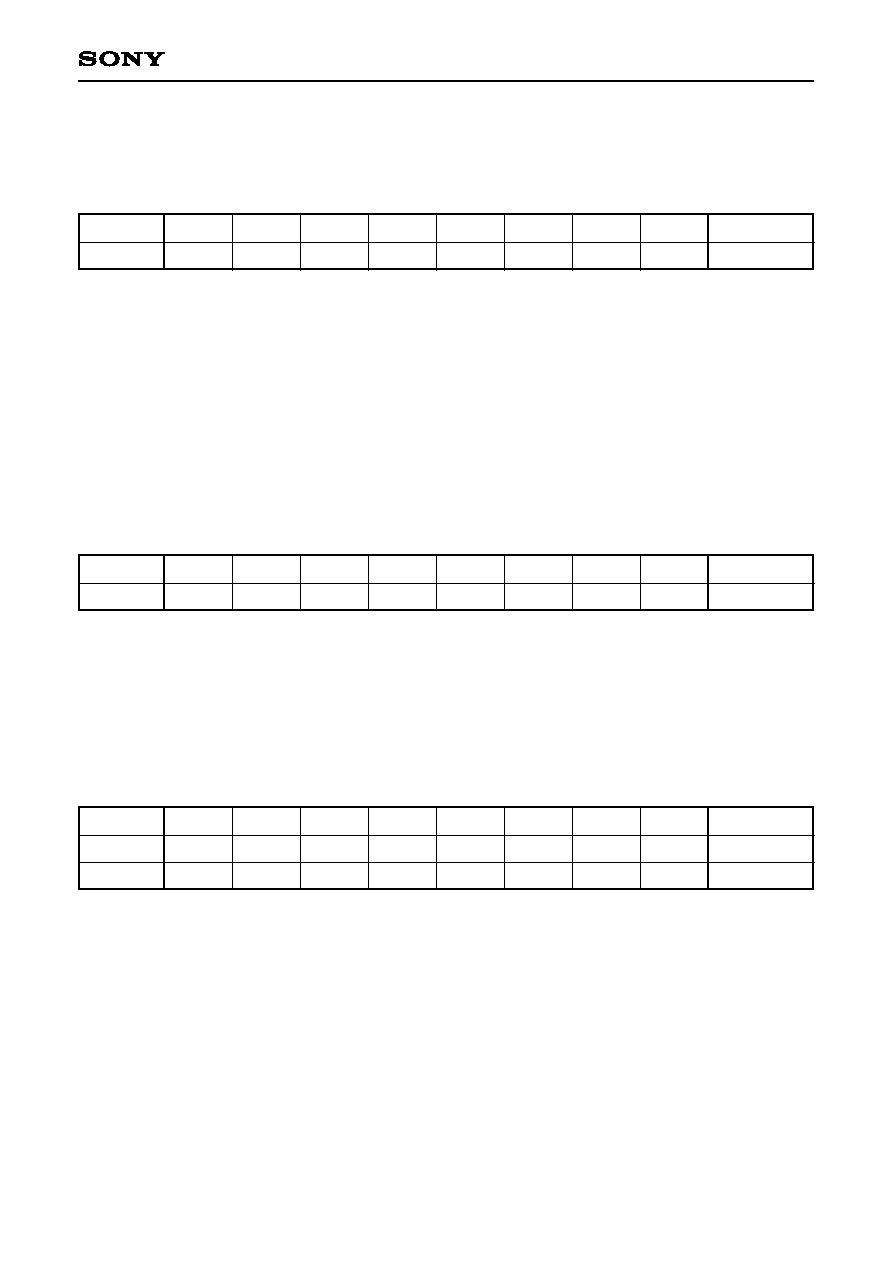

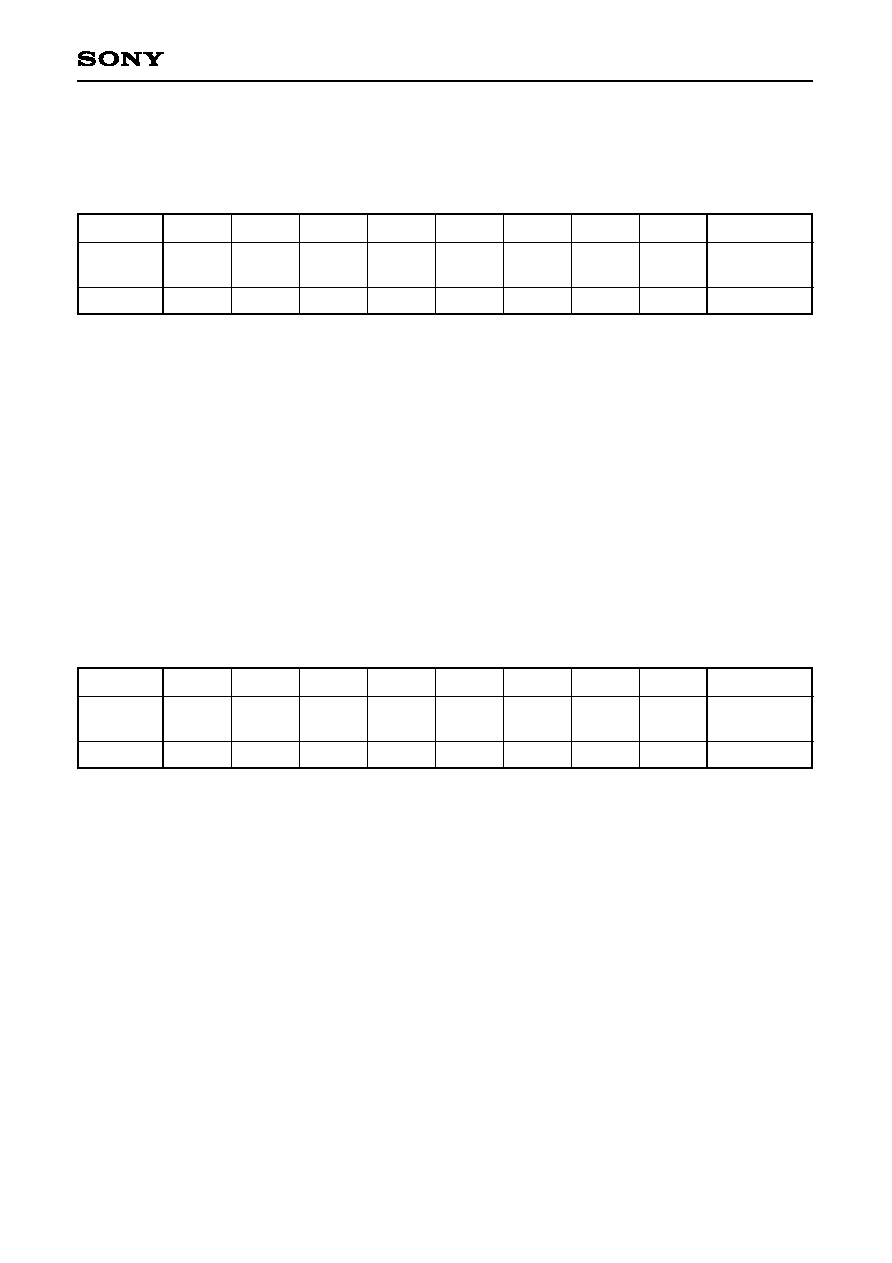

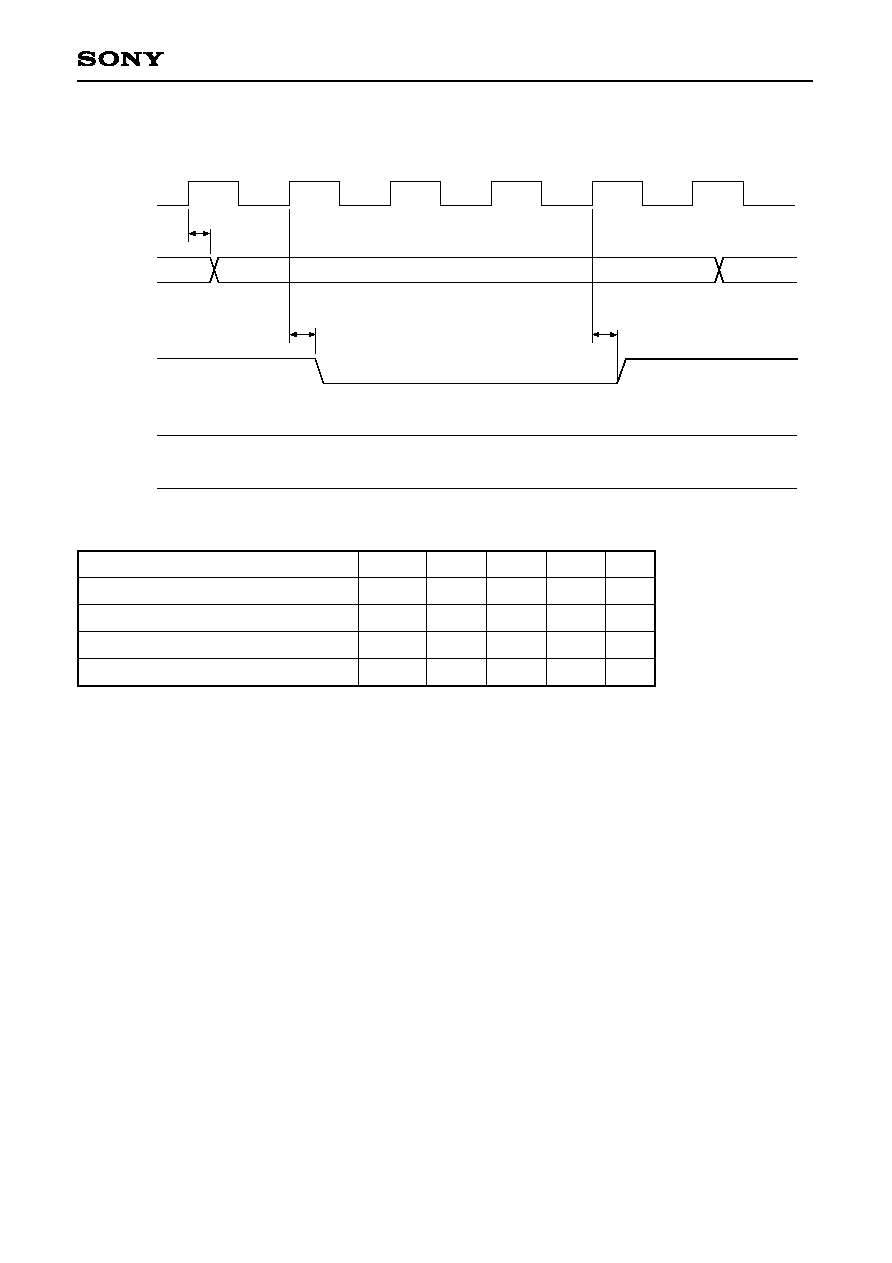

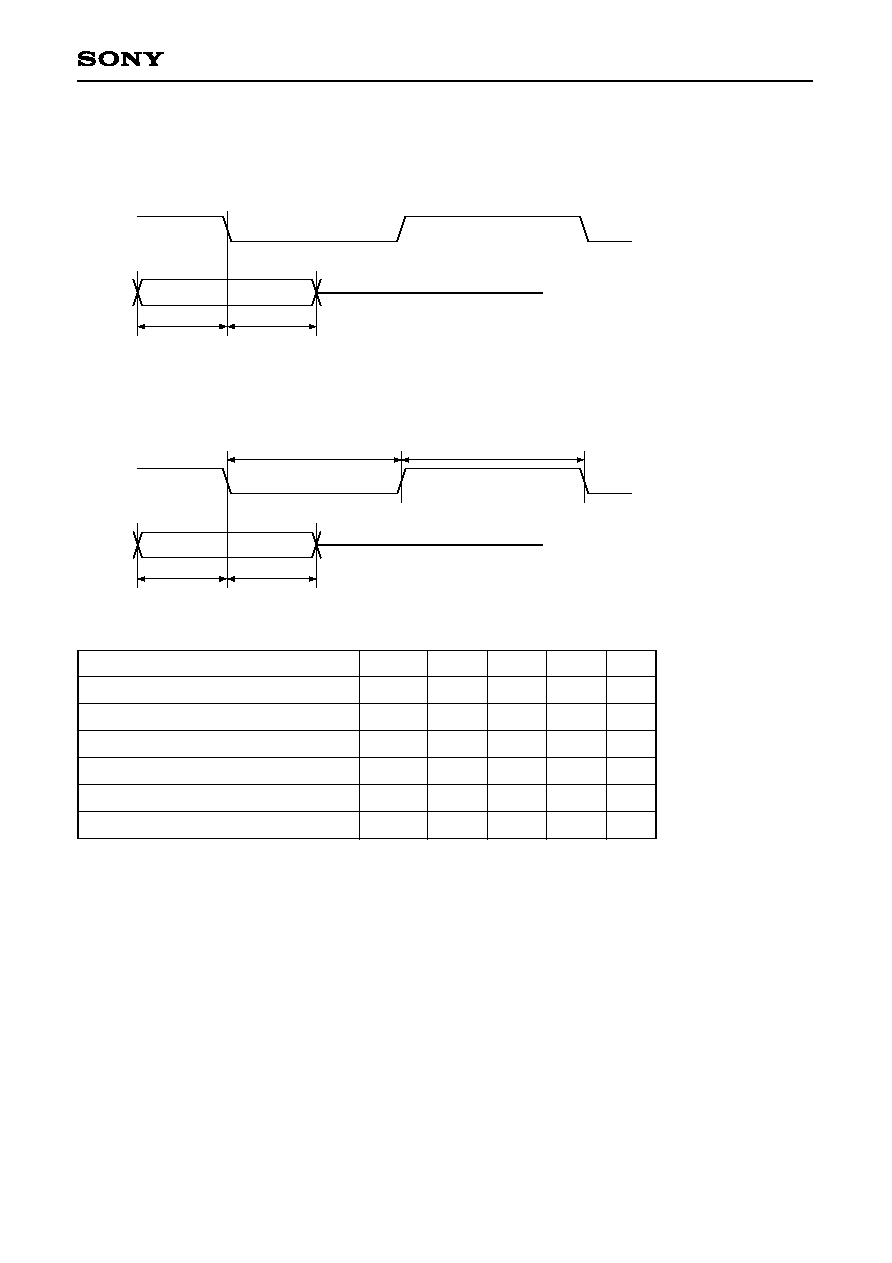

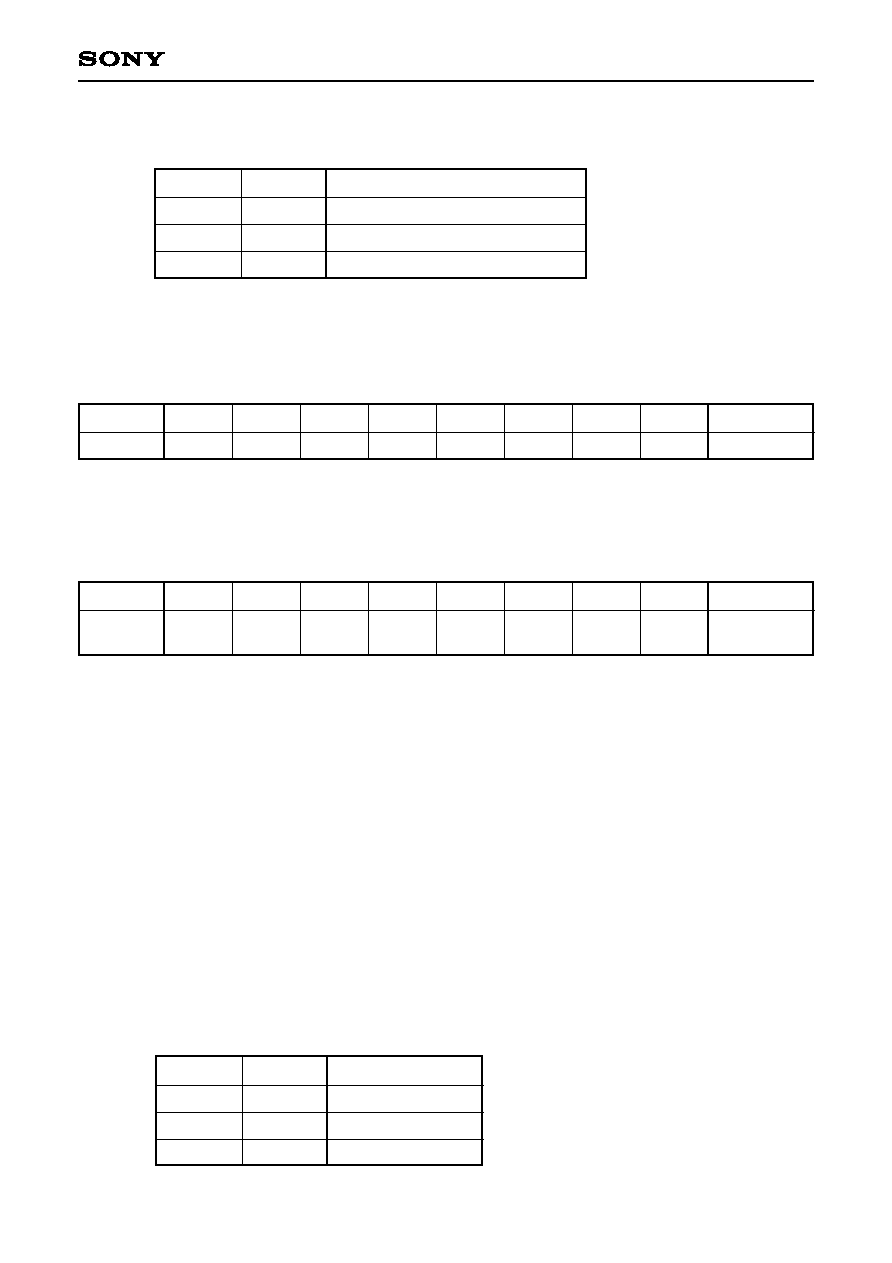

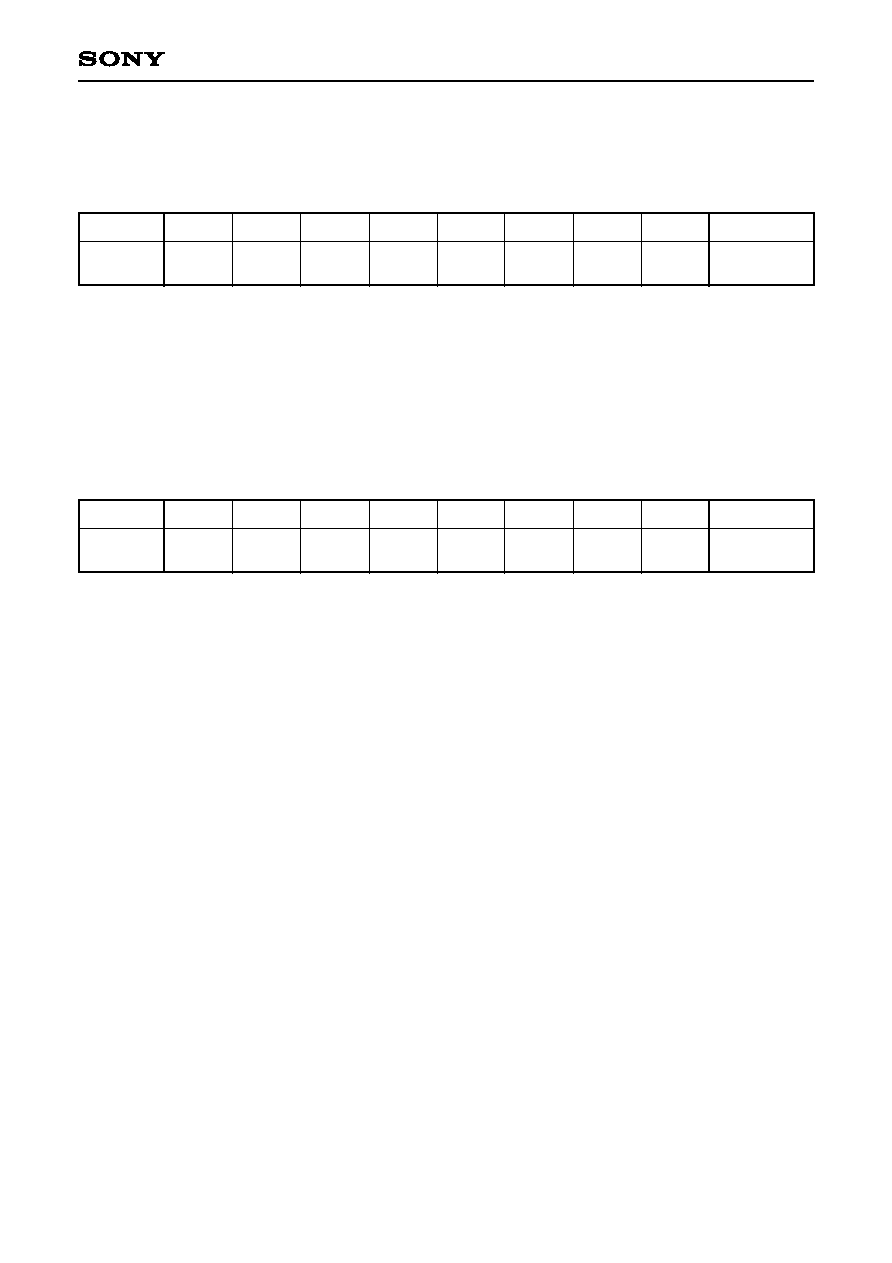

3. DRAM Interface (Output Load = 30pF)

(1) Read

Tma0

iCLK

Tma1

Trasl

Trash

Trc

Tcasl

Tcash

Tmdrs

Tmdrh

"H"

MA9 to 0

XRAS

XUCAS

XLCAS

XMWR

MDBF to 0

Item

Random read/write cycle time

Address delay time (for XTL2

)

Address delay time (for XTL2

)

XRAS

delay time (for XTL2

)

XRAS

delay time (for XTL2

)

XCAS

delay time (for XTL2

)

XCAS

delay time (for XTL2

)

Data setup time (for XTL2

)

Data hold time (for XCAS

)

Trc

Tma0

Tma1

Trasl

Trash

Tcasl

Tcash

Tmdrs

Tmdrh

5Tw

13

11

6

6

7

6

2

0

24

22

12

11

14

12

4

45

41

23

20

25

22

6

ns

ns

ns

ns

ns

ns

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

≠ 14 ≠

CXD1818R

(2) Write

Tma0

iCLK

Tma1

Trasl

Trash

Trc

Tcash

Tcasl

Tmdws

MA9 to 0

XRAS

XUCAS

XLCAS

XMWR

MDBF to 0

Tmwrh

Tmwrl

Tmdwh

Item

Random read/write cycle time

Address delay time (for XTL2

)

Address delay time (for XTL2

)

XRAS

delay time (for XTL2

)

XRAS

delay time (for XTL2

)

XCAS

delay time (for XTL2

)

XCAS

delay time (for XTL2

)

XMWR

delay time (for XTL2

)

XMWR

delay time (for XTL2

)

Data setup time (for XTL2

)

Data hold time (for XTL2

)

Trc

Tma0

Tma1

Trasl

Trash

Tcasl

Tcash

Tmwrl

Tmwrh

Tmdws

Tmdwh

5Tw

13

11

6

6

7

6

7

6

14

7

24

22

12

11

14

12

14

11

28

14

45

41

23

20

25

22

25

21

51

26

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

≠ 15 ≠

CXD1818R

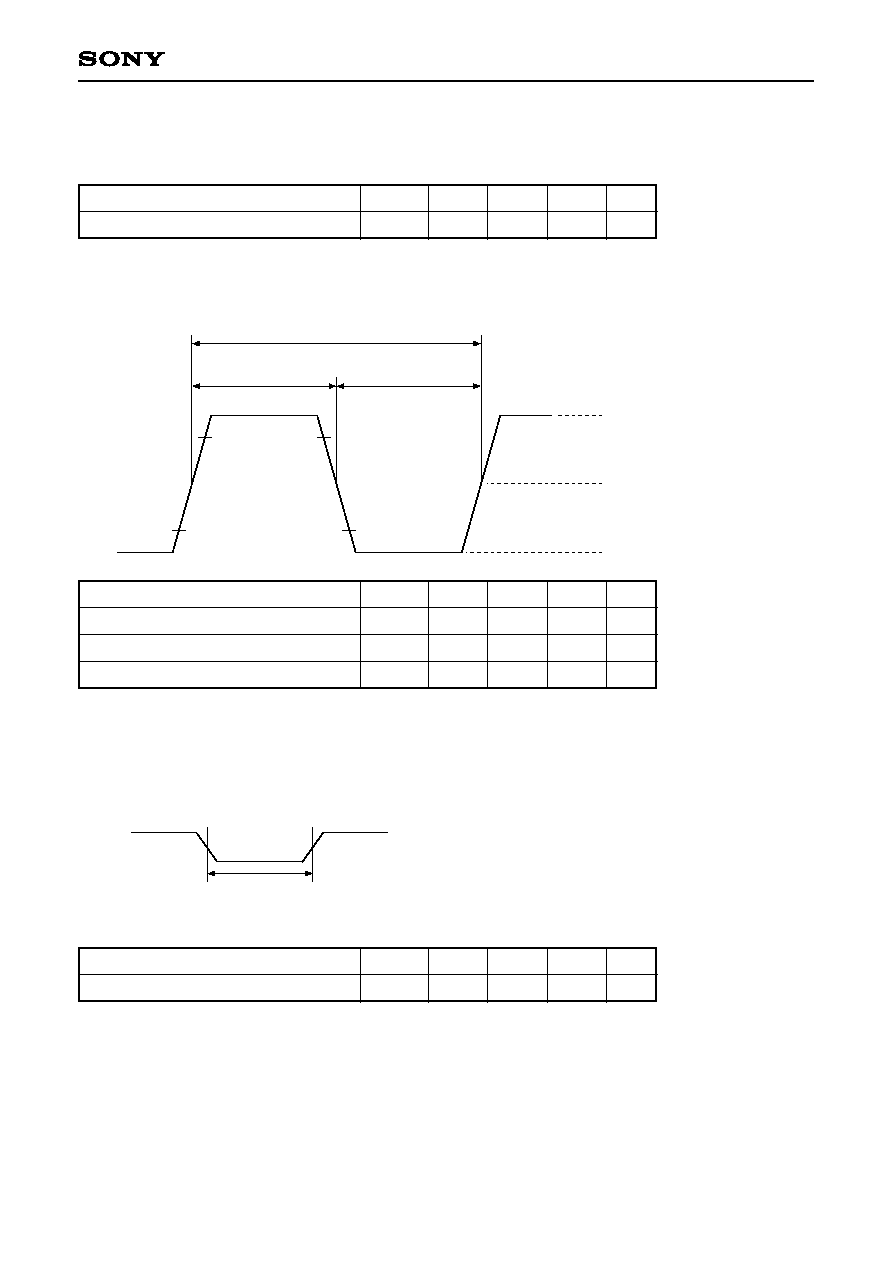

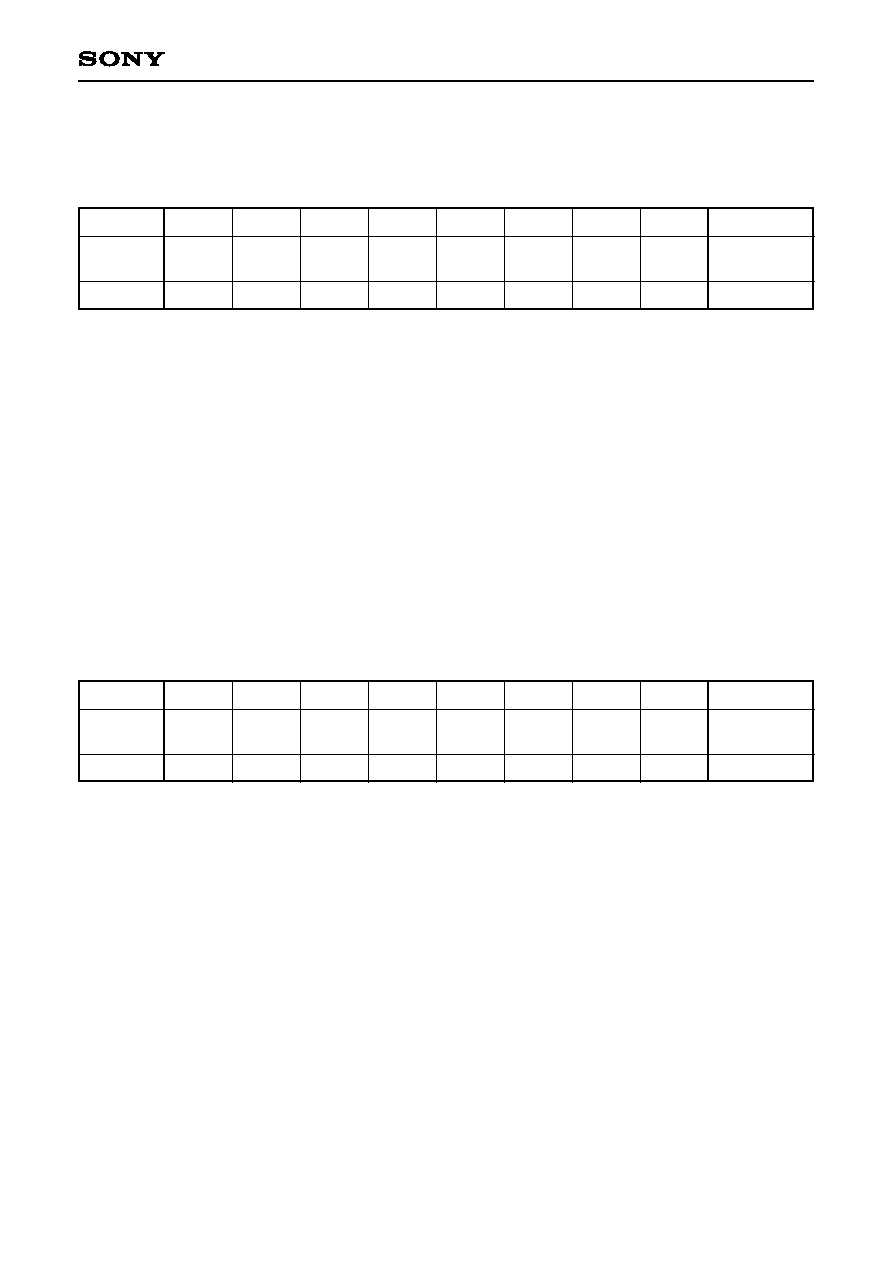

(3) Refresh (RAS only refresh)

Tma0

iCLK

Trasl

Trash

MA9 to 0

XRAS

XUCAS

XLCAS

XMWR

"H"

"H"

Item

Random read/write cycle time

Address delay time (for XTL2

)

XRAS

delay time (for XTL2

)

XRAS

delay time (for XTL2

)

Trc

Tma0

Trasl

Trash

5Tw

12

6

6

24

12

11

43

23

20

ns

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

≠ 16 ≠

CXD1818R

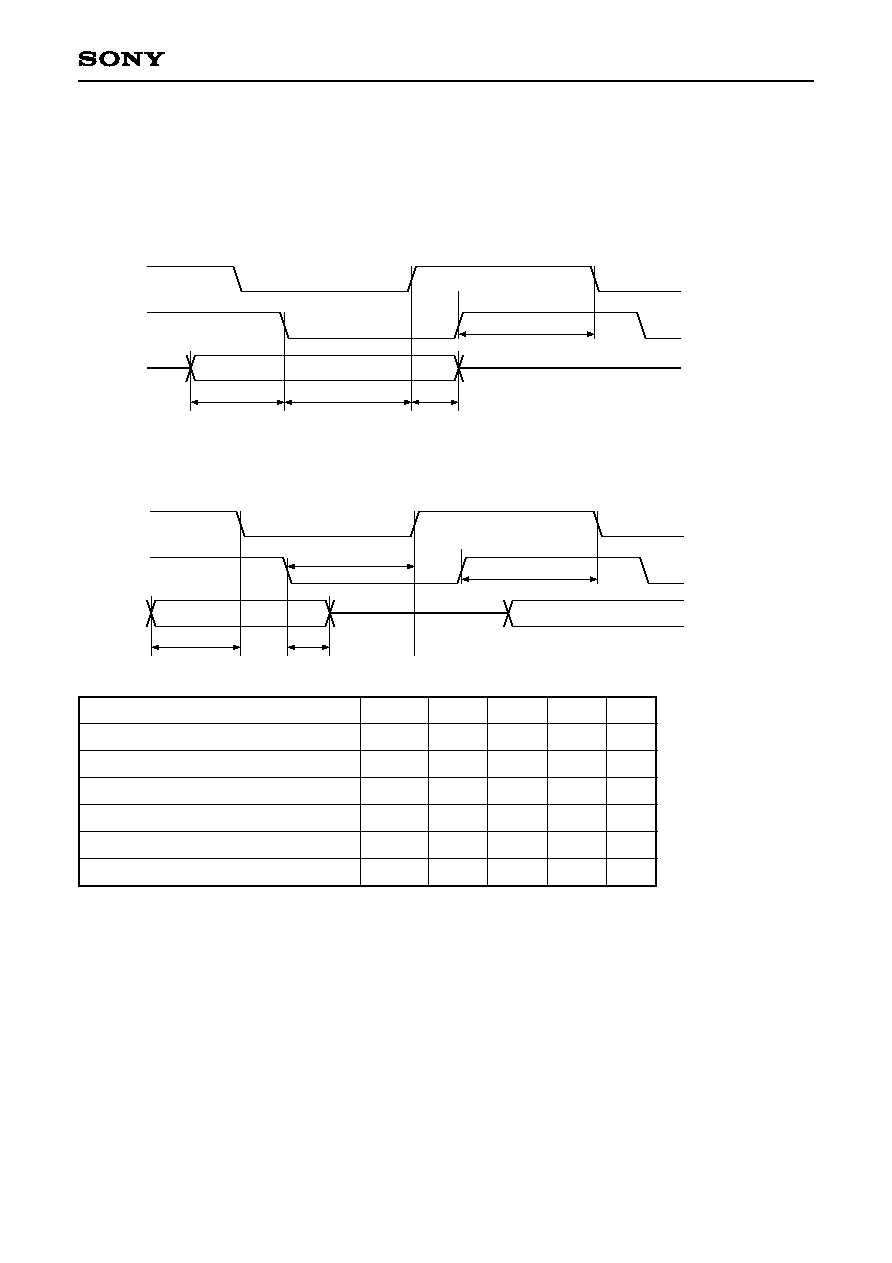

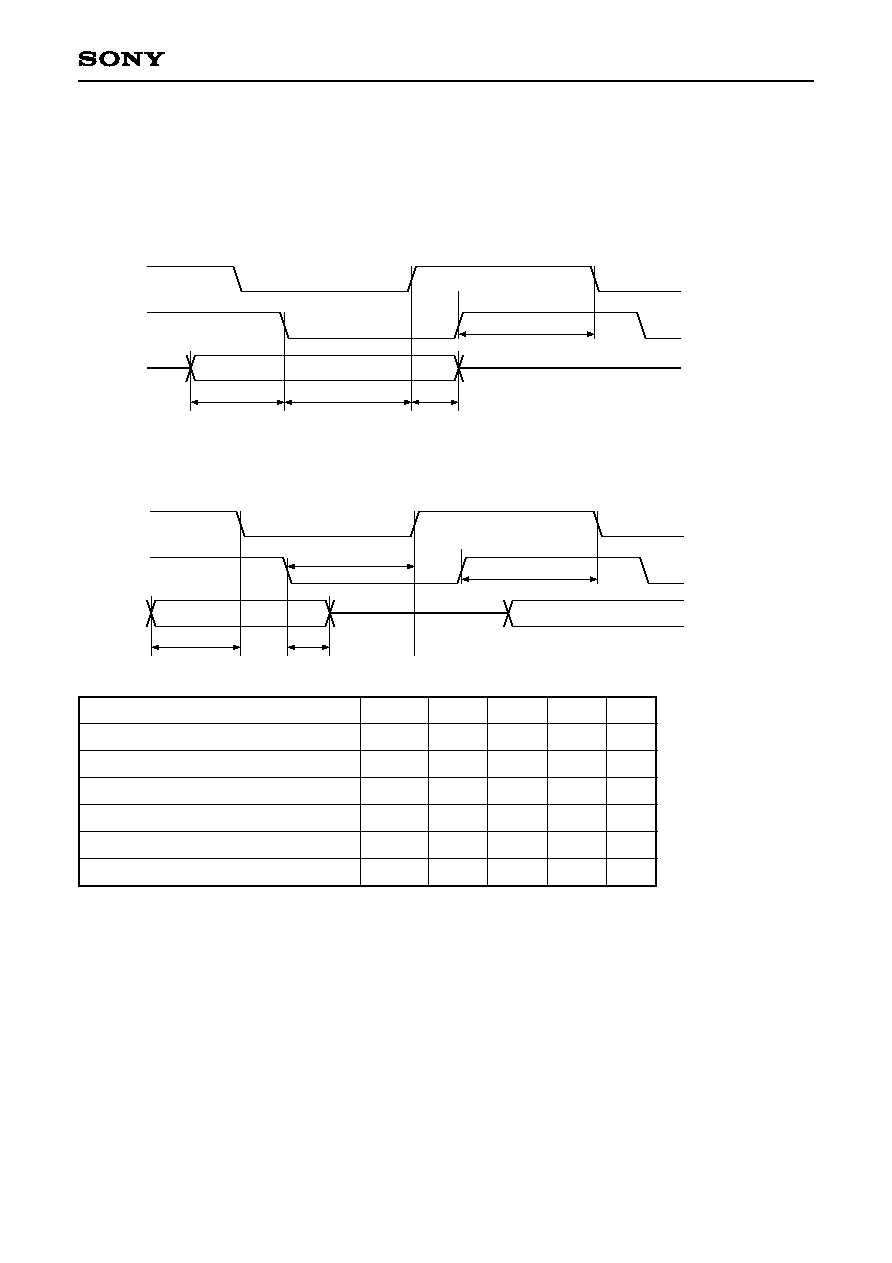

4. SCSI Interface

(1) SCSI asynchronous transfer timing

When receiving: Initiator

Target

Taads

Tardh

XREQ

XACK

XDB

Taaarnd

Taanrad

When transmitting: Target

Initiator

Tards

XREQ

XACK

XDB

Taadh

Taanrad

Taaarnd

Item

XDB setup time (for XACK

)

XDB hold time (for XREQ

)

XDB setup time (for XREQ

)

XDB hold time (for XREQ

)

XREQ rise delay time (for XACK

)

XREQ fall time (for XACK

)

Taads

Tardh

Tards

Taadh

Taaarnd

Taanrad

15

0

30

60

30

30

70

85

ns

ns

ns

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

≠ 17 ≠

CXD1818R

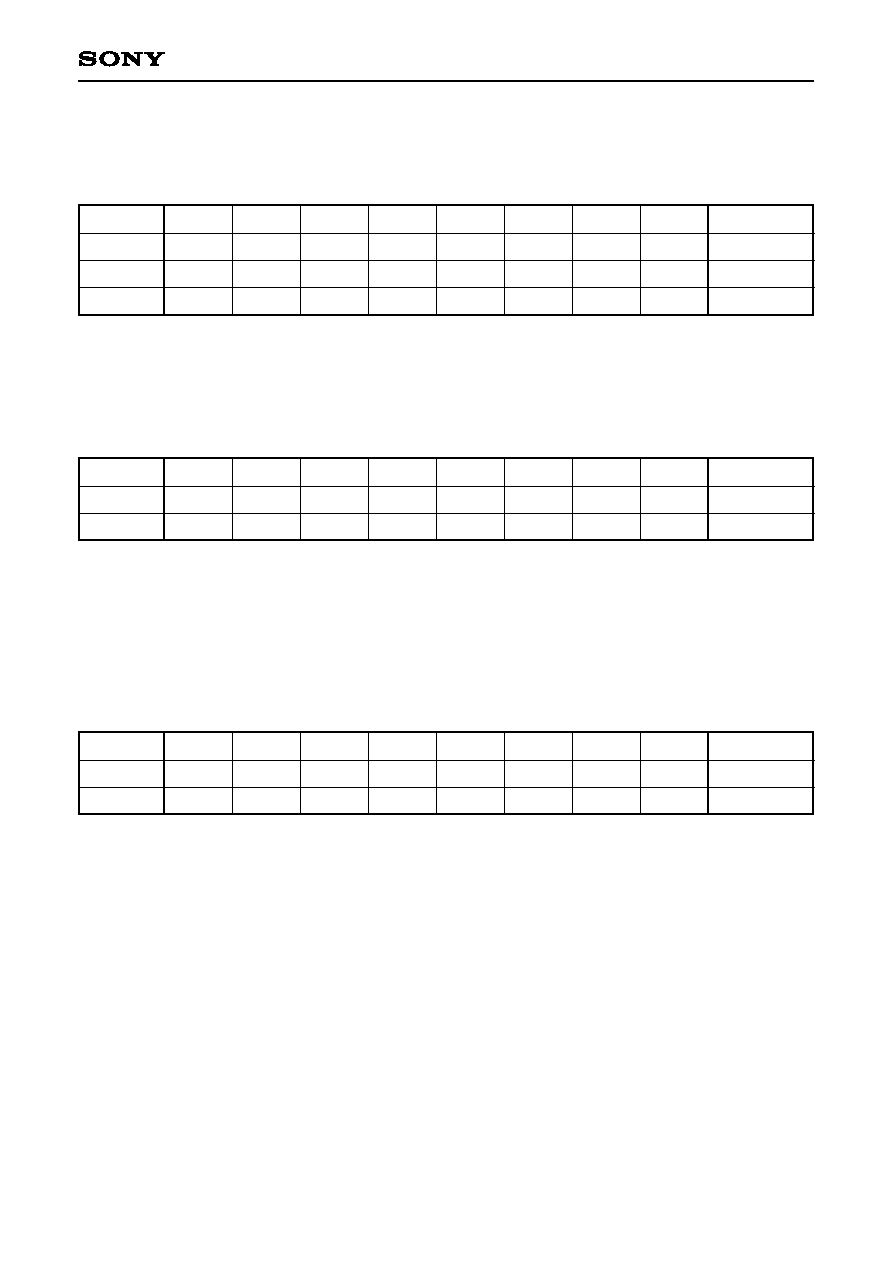

(2) SCSI synchronous transfer timing

When receiving: Initiator

Target

Tnads

XACK

XDB

Tnadh

When transmitting: Target

Initiator

Tnrds

XREQ

XDB

Tnrdh

Tnrap

Tnrnp

Item

XDB setup time (for XACK

)

XDB hold time (for XACK

)

XDB setup time (for XREQ

)

XDB hold time (for XREQ

)

XREQ assert time

XREQ negate time

Tnads

Tnadh

Tnrds

Tnrdh

Tnrap

Tnrnp

15

10

80

105

90

110

ns

ns

ns

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

≠ 18 ≠

CXD1818R

(3) Fast SCSI synchronous transfer timing

When receiving: Initiator

Target

Tfads

XACK

XDB

Tfadh

When transmitting: Target

Initiator

Tfrds

XREQ

XDB

Tfrdh

Tfrap

Tfrnp

Item

XDB setup time (for XACK

)

XDB hold time (for XACK

)

XDB setup time (for XREQ

)

XDB hold time (for XREQ

)

XREQ assert time

XREQ negate time

Tfads

Tfadh

Tfrds

Tfrdh

Tfrap

Tfrnp

15

10

55

55

40

60

ns

ns

ns

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

≠ 19 ≠

CXD1818R

(4) SCSI synchronous transfer (Ultra) timing

When receiving: Initiator

Target

Tuads

XACK

XDB

Tuadh

When transmitting: Target

Initiator

Turds

XREQ

XDB

Turdh

Turap

Turnp

Item

XDB setup time (for XACK

)

XDB hold time (for XACK

)

XDB setup time (for XREQ

)

XDB hold time (for XREQ

)

XREQ assert time

XREQ negate time

Tuads

Tuadh

Turds

Turdh

Turap

Turnp

15

10

11.5

16.5

15

30

ns

ns

ns

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

≠ 20 ≠

CXD1818R

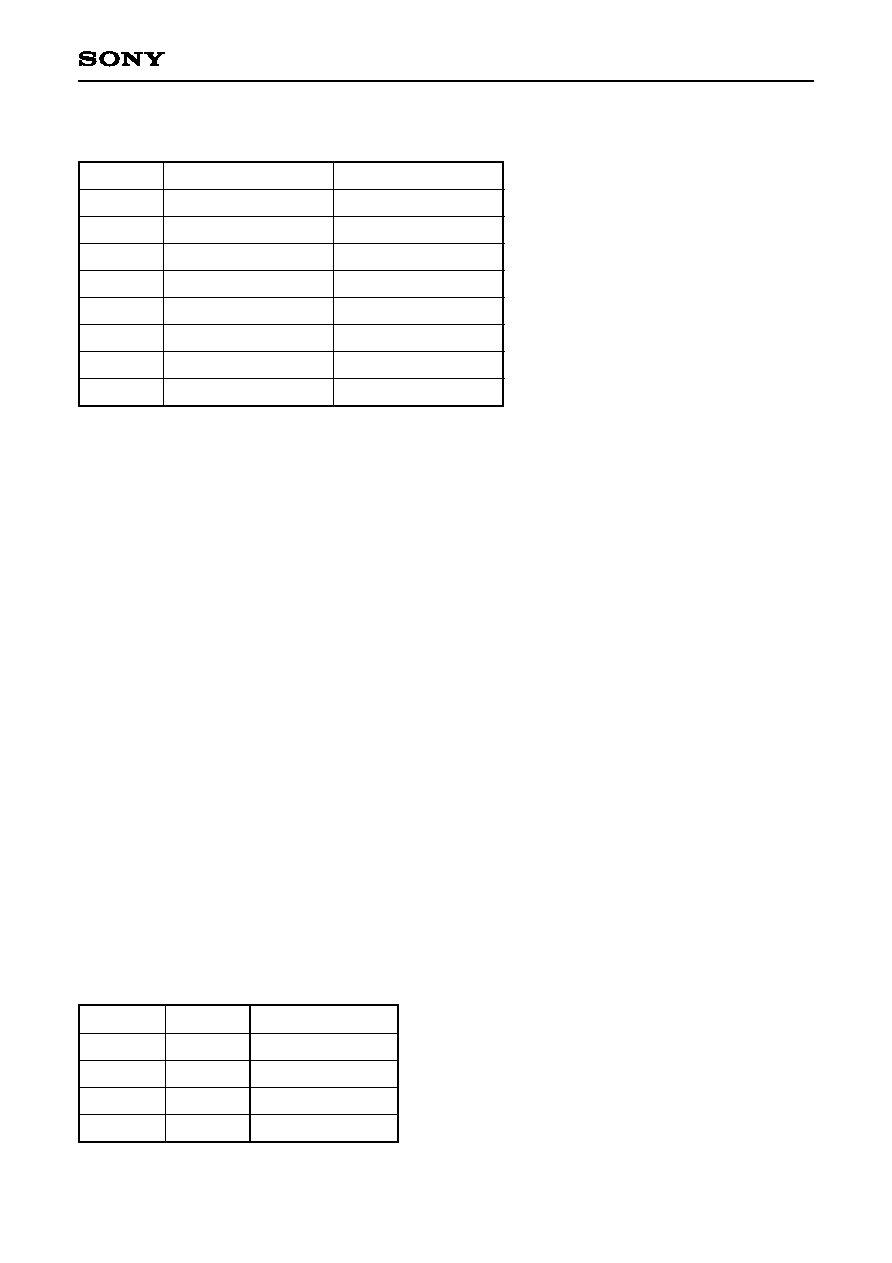

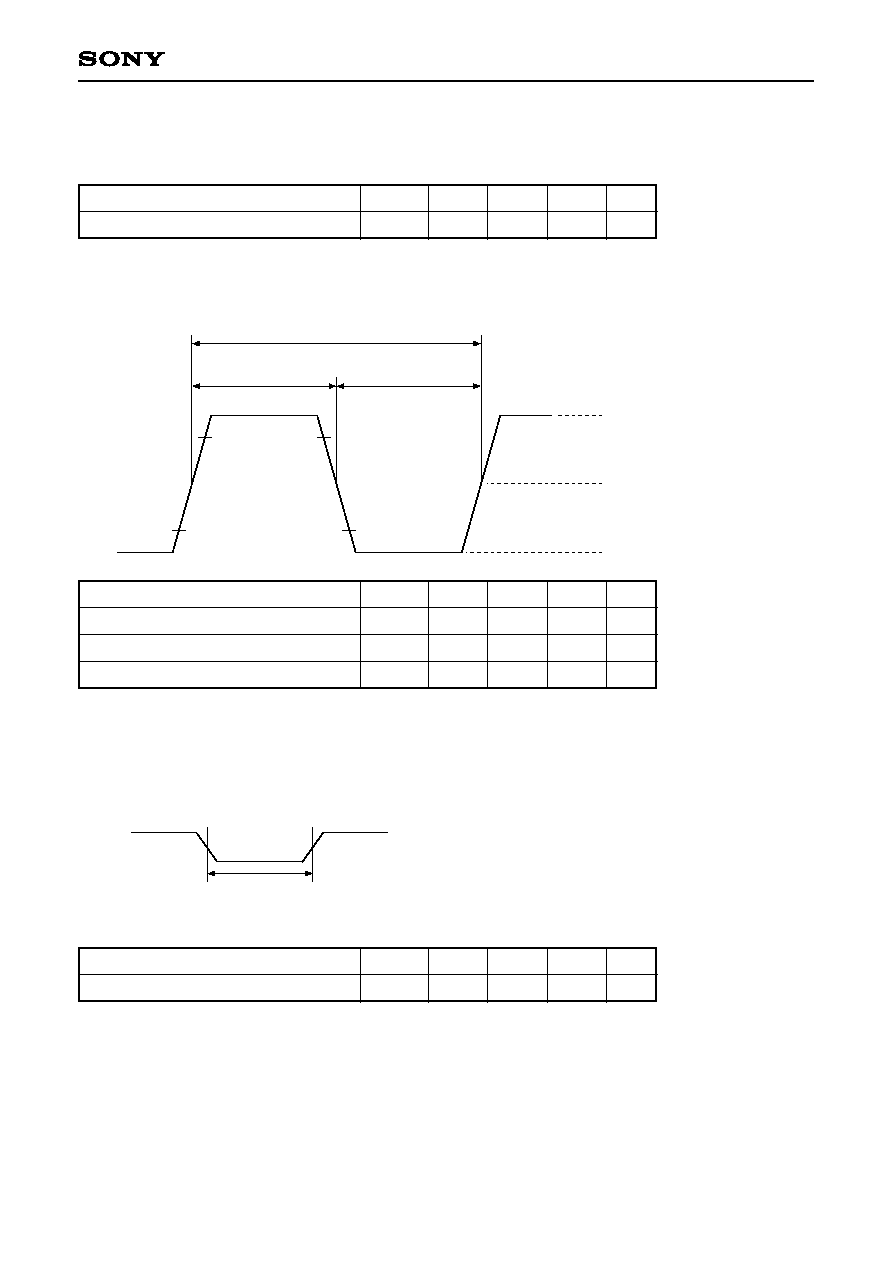

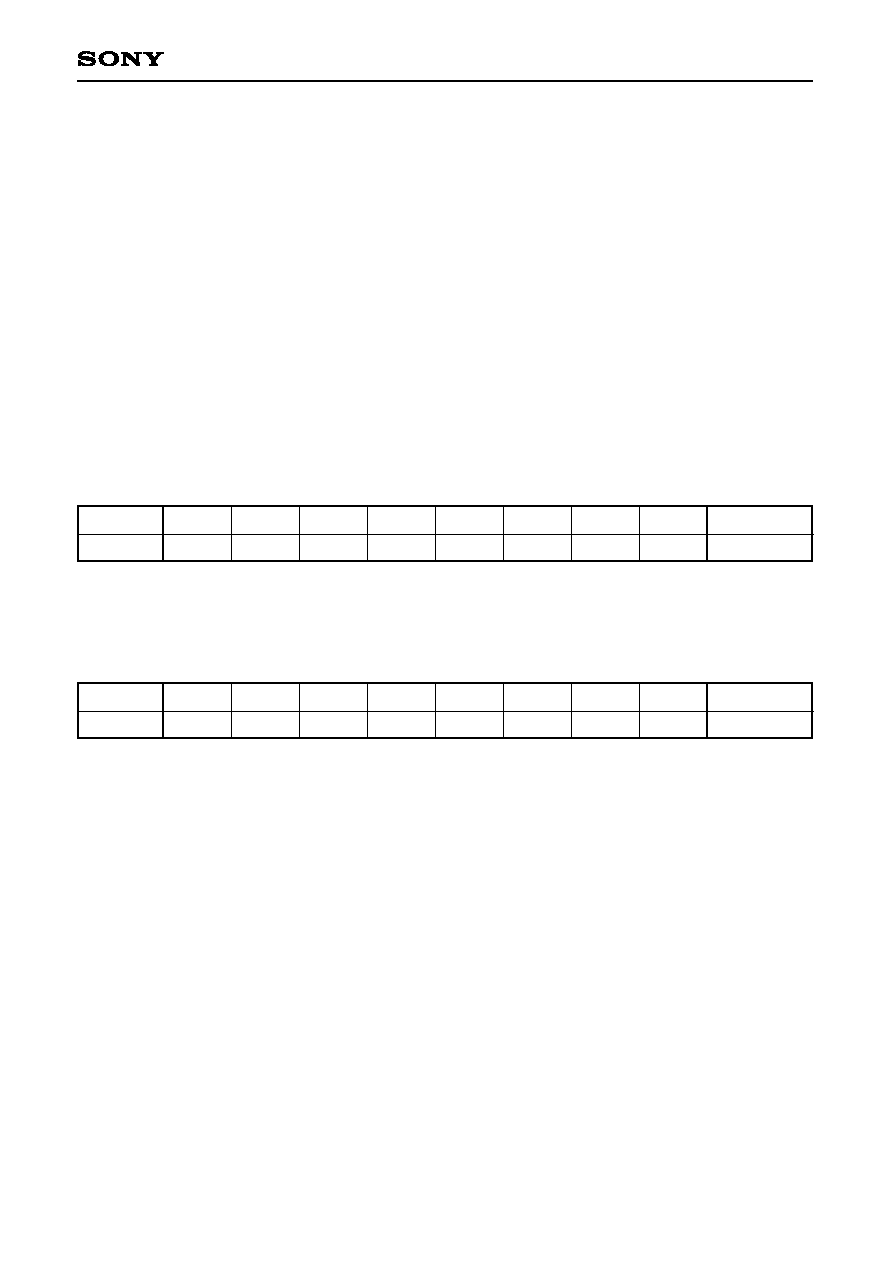

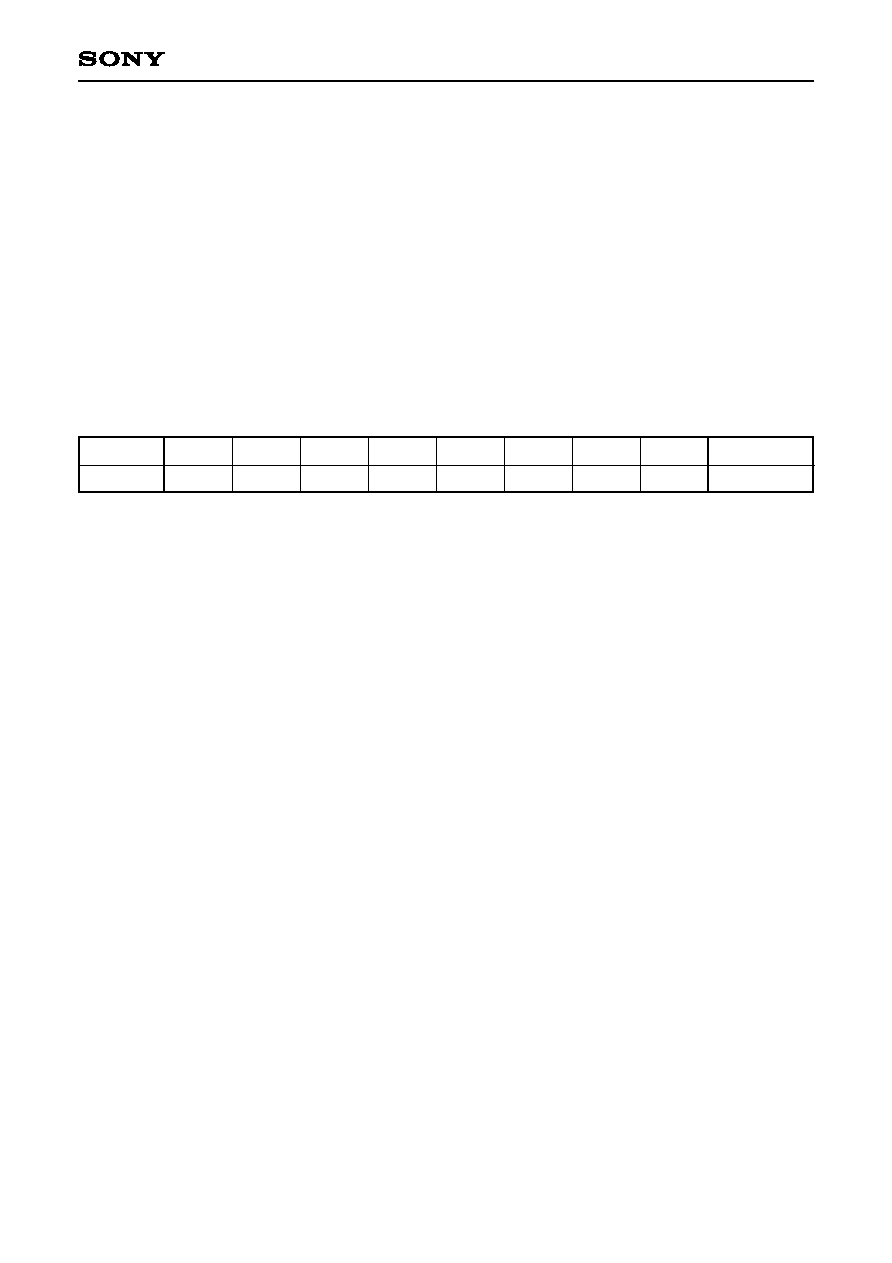

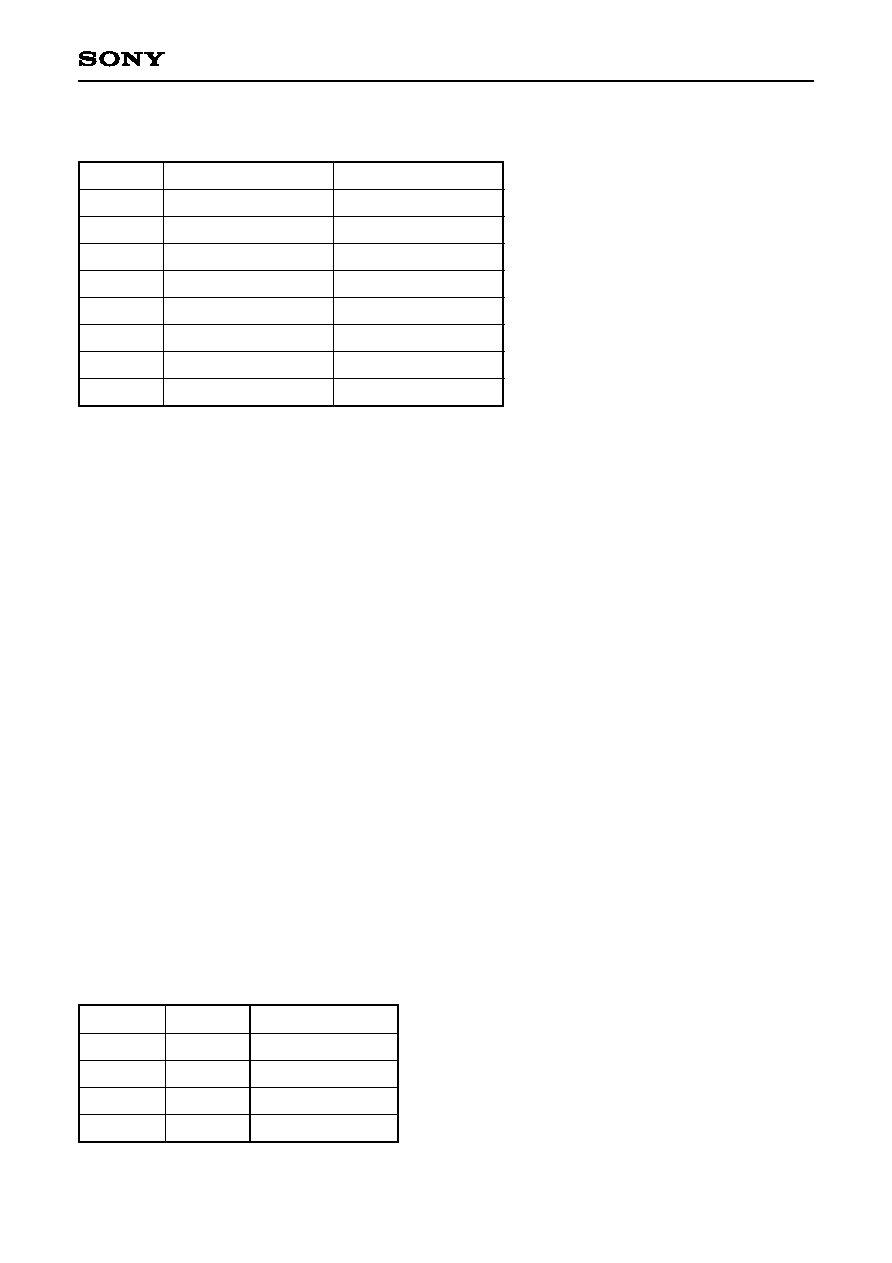

5. XTL1 and XTL2 Pins

(1) When using self-excited oscillation

Item

Oscillation frequency

Fmax

40.0

MHz

Symbol

Min.

Typ.

Max.

Unit

XRES Pin

Reset to IC

Item

XRES "L" hold time

Trs

100

ns

Symbol

Min.

Typ.

Max.

Unit

Vihx

Twlx

Twhx

Tw

V

DD

/2

Vilx

(2) When inputting a pulse to the XTL1 pin

Item

High level pulse width

Low level pulse width

Pulse cycle

Twhx

Twhx

Tw

10

10

25

ns

ns

ns

Symbol

Min.

Typ.

Max.

Unit

Trs

≠ 21 ≠

CXD1818R

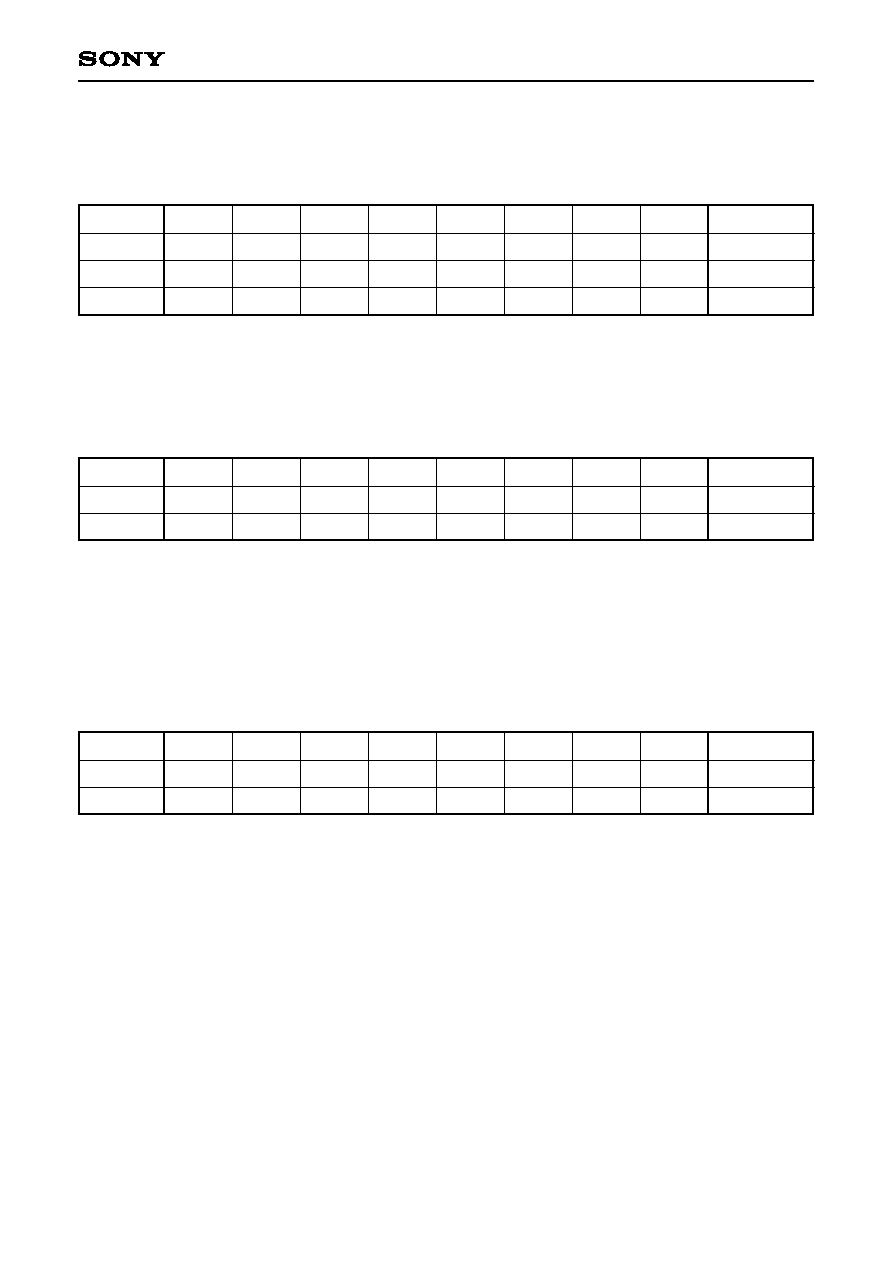

Contents

[1] Description of Registers ........................................................................................................................... 22

1-1. Description of Decoder Block Registers ............................................................................................... 22

1-2. Description of SCSI2 Controller Block Registers.................................................................................. 51

1-3. Common Registers ............................................................................................................................... 66

[2] Description of SCSI Controller Block Commands ................................................................................. 77

2-1. Precautions when Executing Commands ............................................................................................. 78

2-2. Category 00 Commands....................................................................................................................... 78

2-3. Category 01 Commands....................................................................................................................... 83

2-4. Category 10 Commands....................................................................................................................... 85

2-5. Category 11 Commands....................................................................................................................... 88

[3] Appendix A................................................................................................................................................. 93

3-1. List of CD-ROM Decoder Block Registers............................................................................................ 93

3-2. List of SCSI Controller Block Registers ................................................................................................ 99

3-3. List of Common Registers .................................................................................................................. 103

3-4. Register Reset Conditions .................................................................................................................. 105

[4] Appendix B............................................................................................................................................... 111

4-1. Summary of SCSI Controller Block Commands ................................................................................. 111

≠ 22 ≠

CXD1818R

[1] Description of Registers

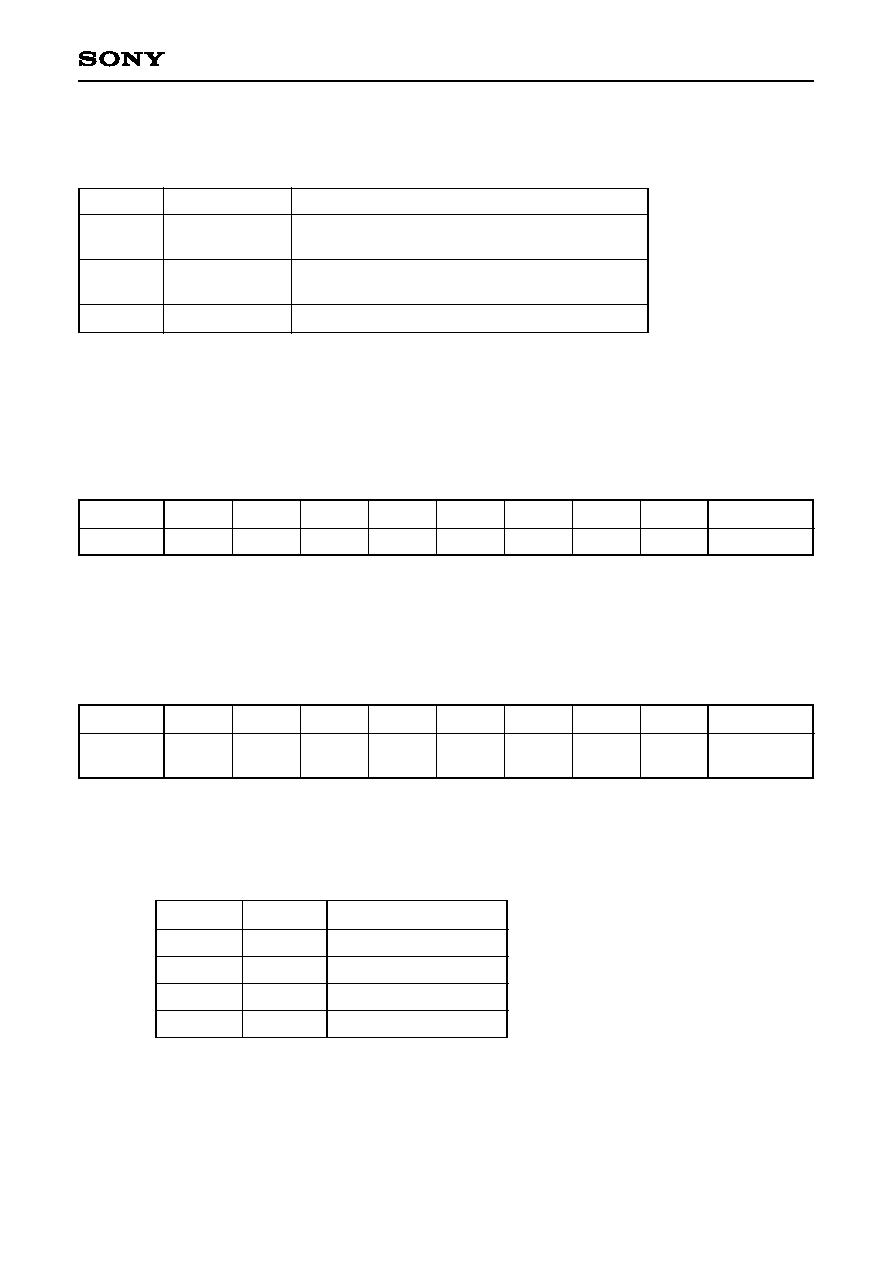

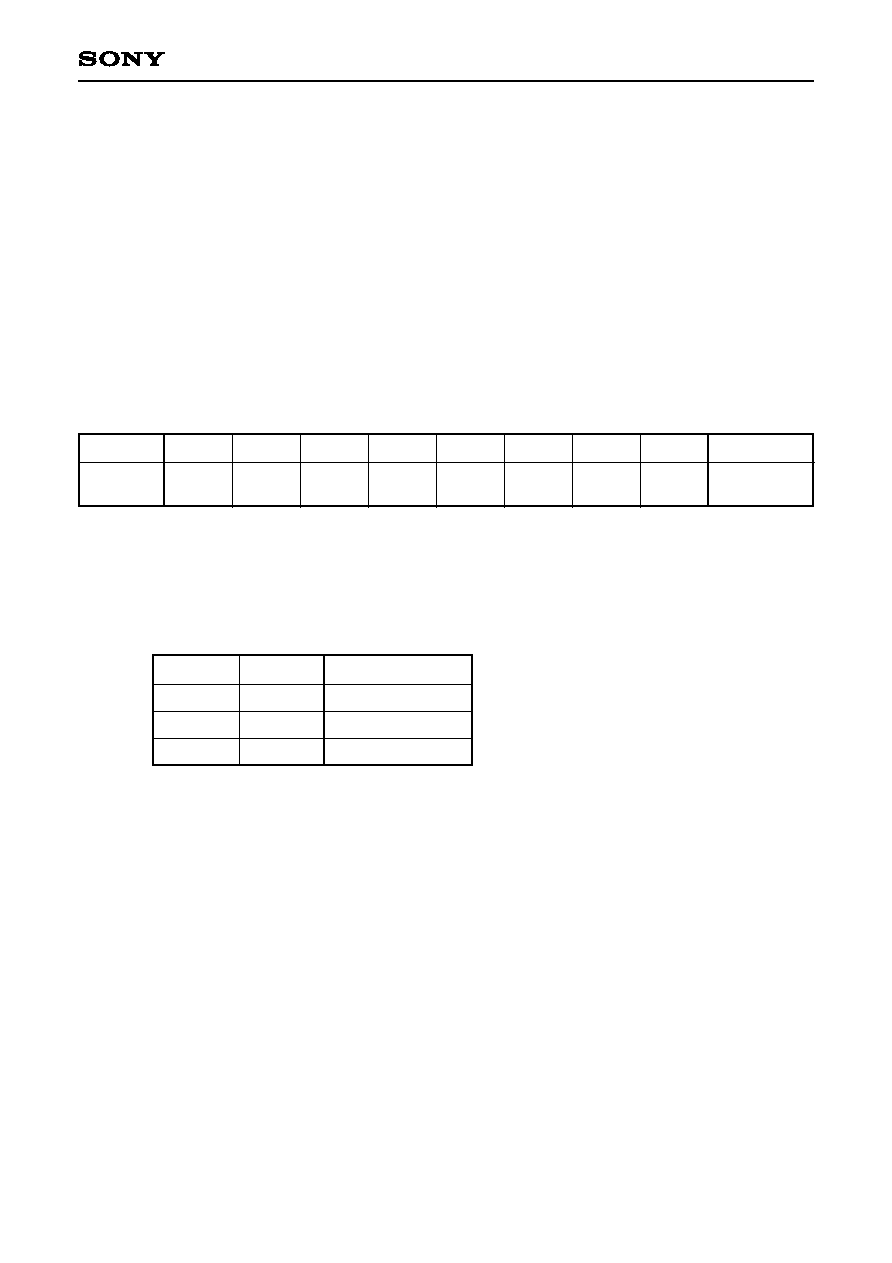

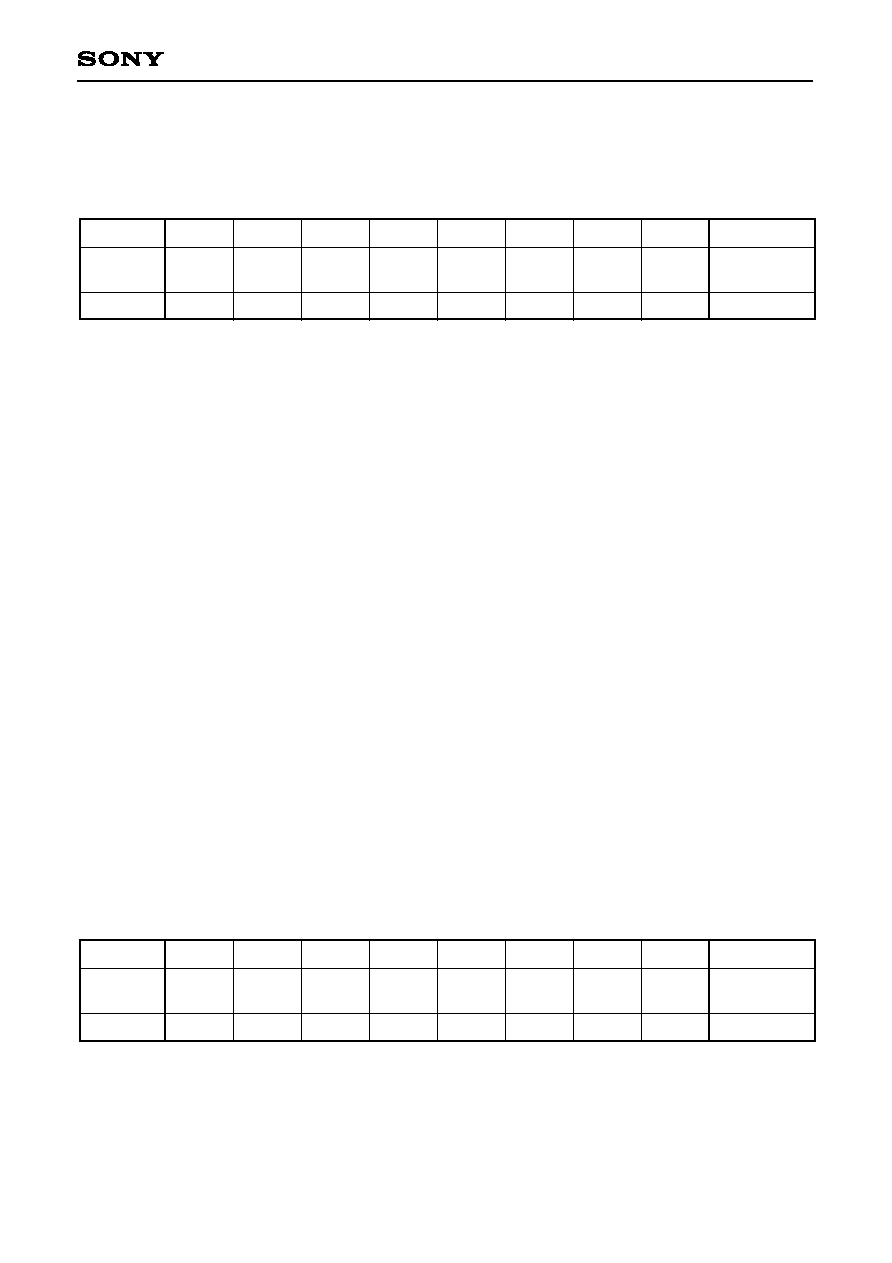

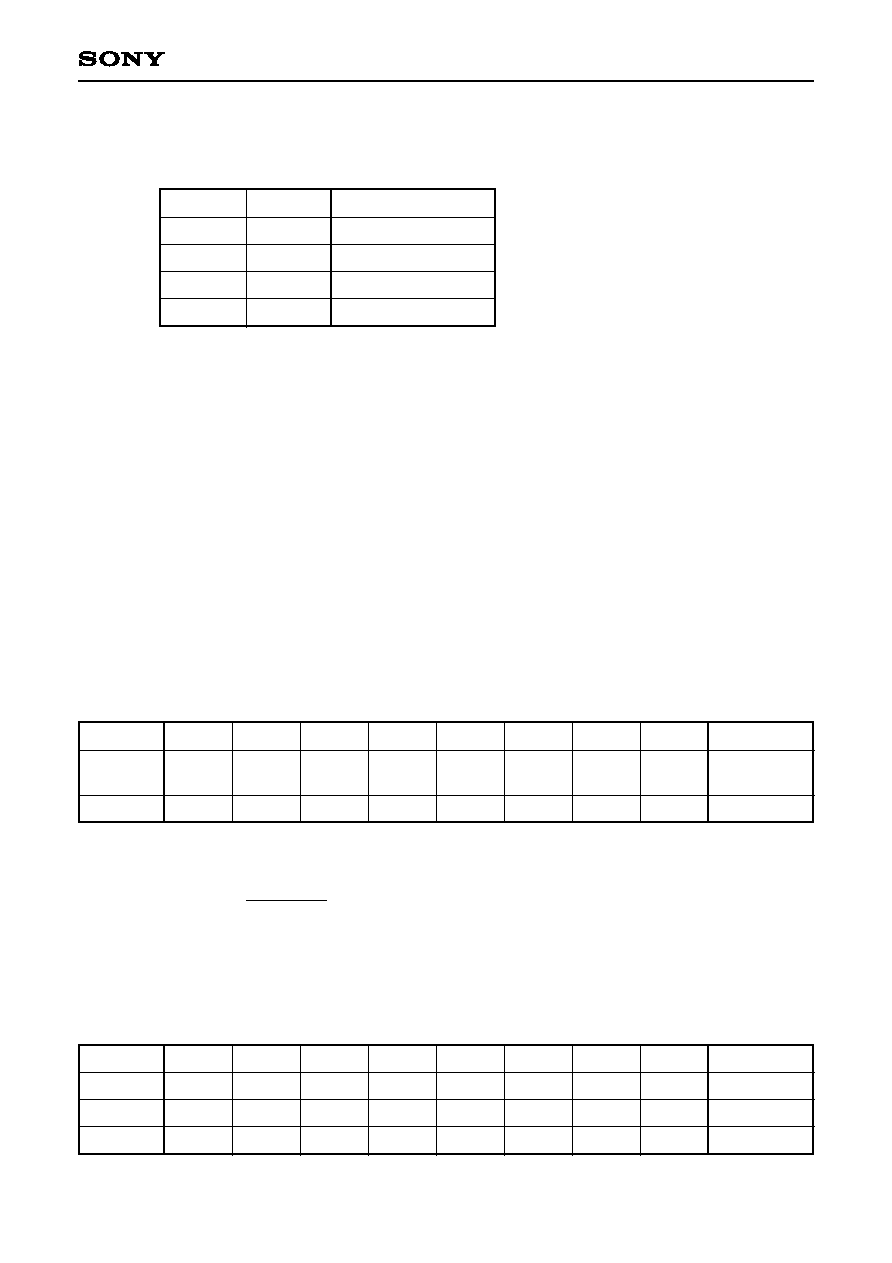

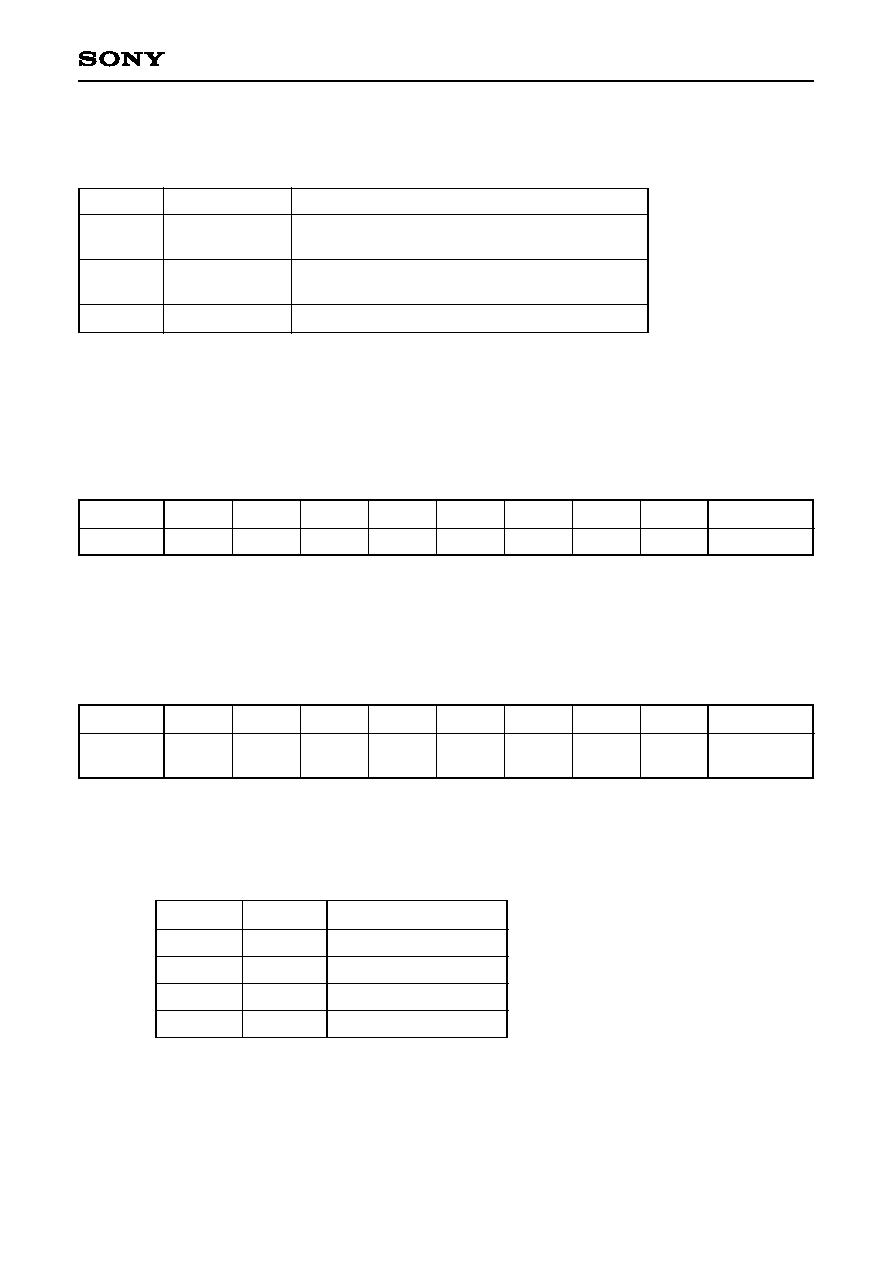

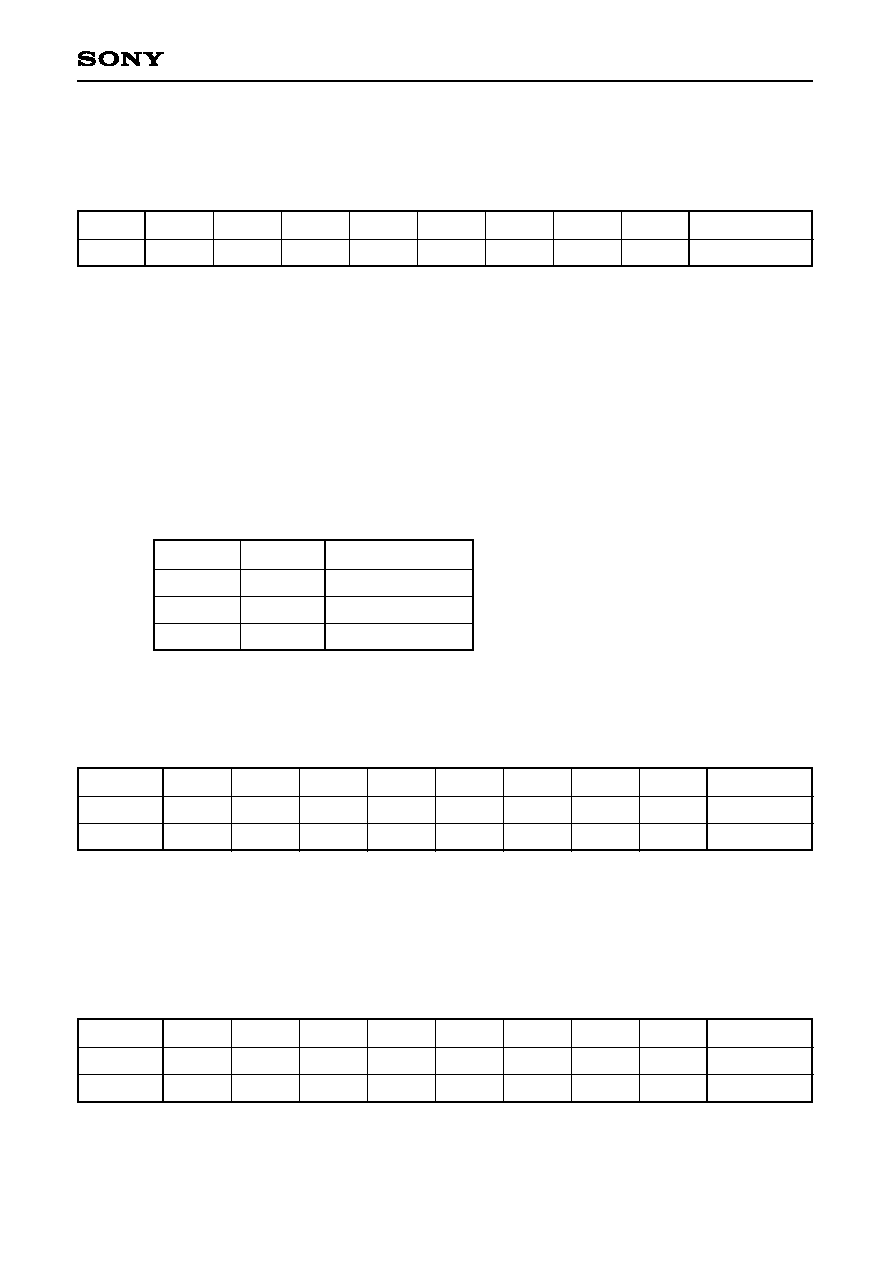

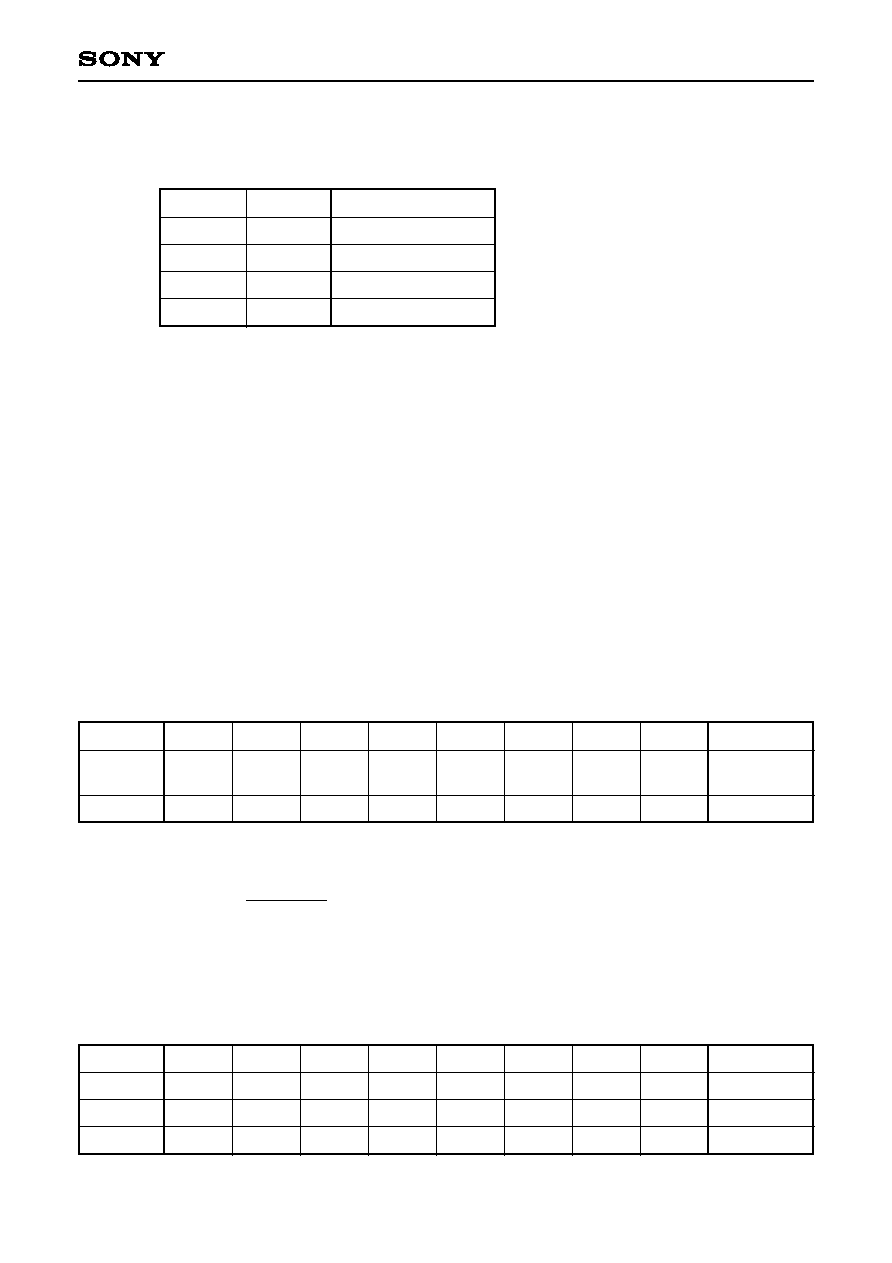

The CXD1818R's register address area is allotted as shown in the table below.

Address

00h to 4Fh

50h to 6Fh

70h to 7Fh

0xx xxxx

100 xxxx

101 xxxx

110 xxxx

111 xxxx

CD-ROM decoder block

SCSI2 interface block

CD-ROM decoder/SCSI2 interface common block

Description

1-1. Description of Decoder Block Registers

1-1-1. 00h

(1) RAWMIN (raw minute) register (read)

RAWMIN (raw minute) register

00h (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

REWMIN

The Header Minute byte for the sector being sent from the CD DSP while DECINT is active can be read from

this register. A difference of two sectors exists between the RAWxxx and BFxxx registers during the write-only

and real-time correction modes.

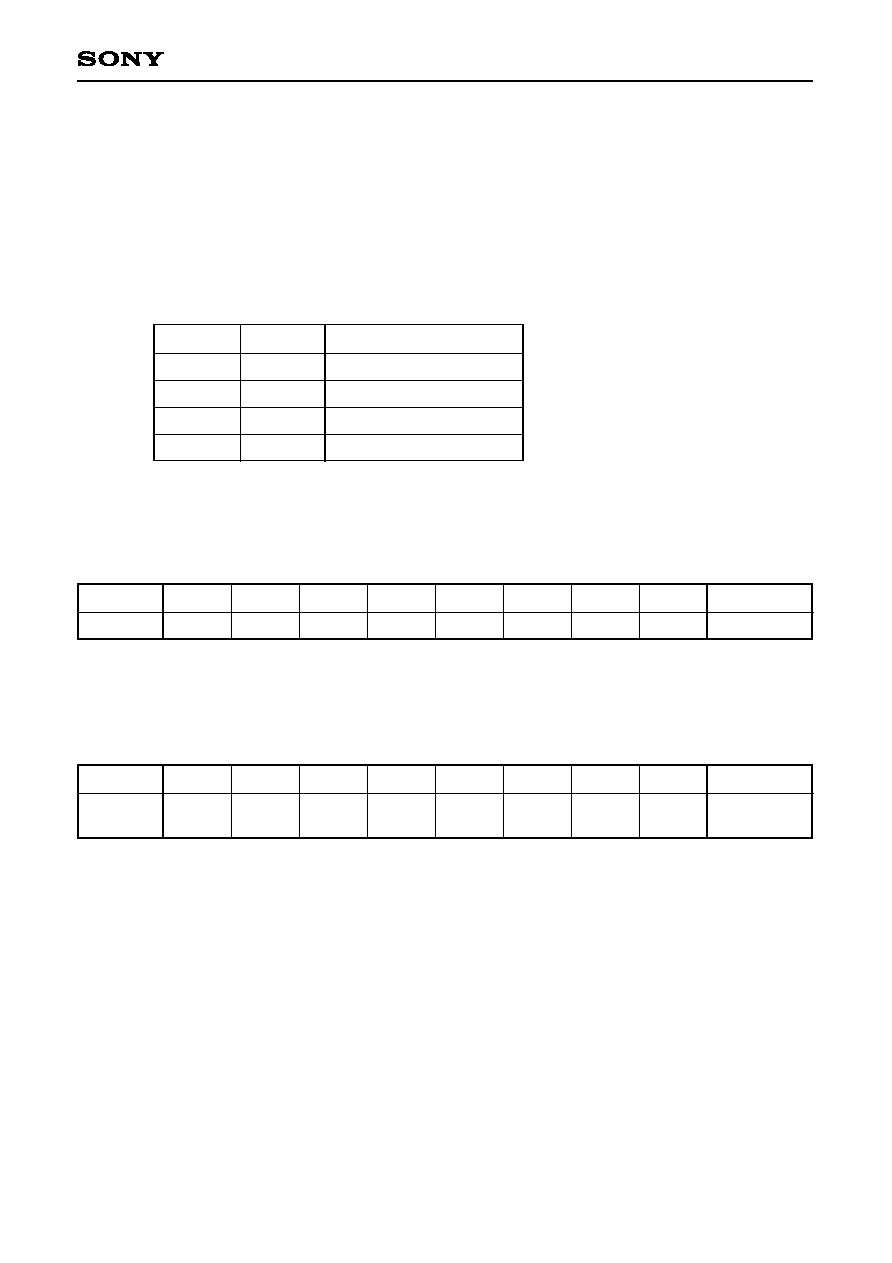

(2) CONFIG0 (configuration 0) register (write)

CONFIG0 (configuration 0) register

00h (W)

CINT

POL

RAM

SIZE1

RAM

SIZE0

RAM8

BITW

RAM2

CAS

"L"

CLK

SEL1

CLK

SEL0

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

CONFIG0

bit 7:

CINTPOL (sub CPU interrupt polarity)

High: The INT pin becomes active high. When the register is inactive, it goes low.

Low: The INT pin becomes active low. When the register is inactive, it goes to high impedance.

bits 6, 5:

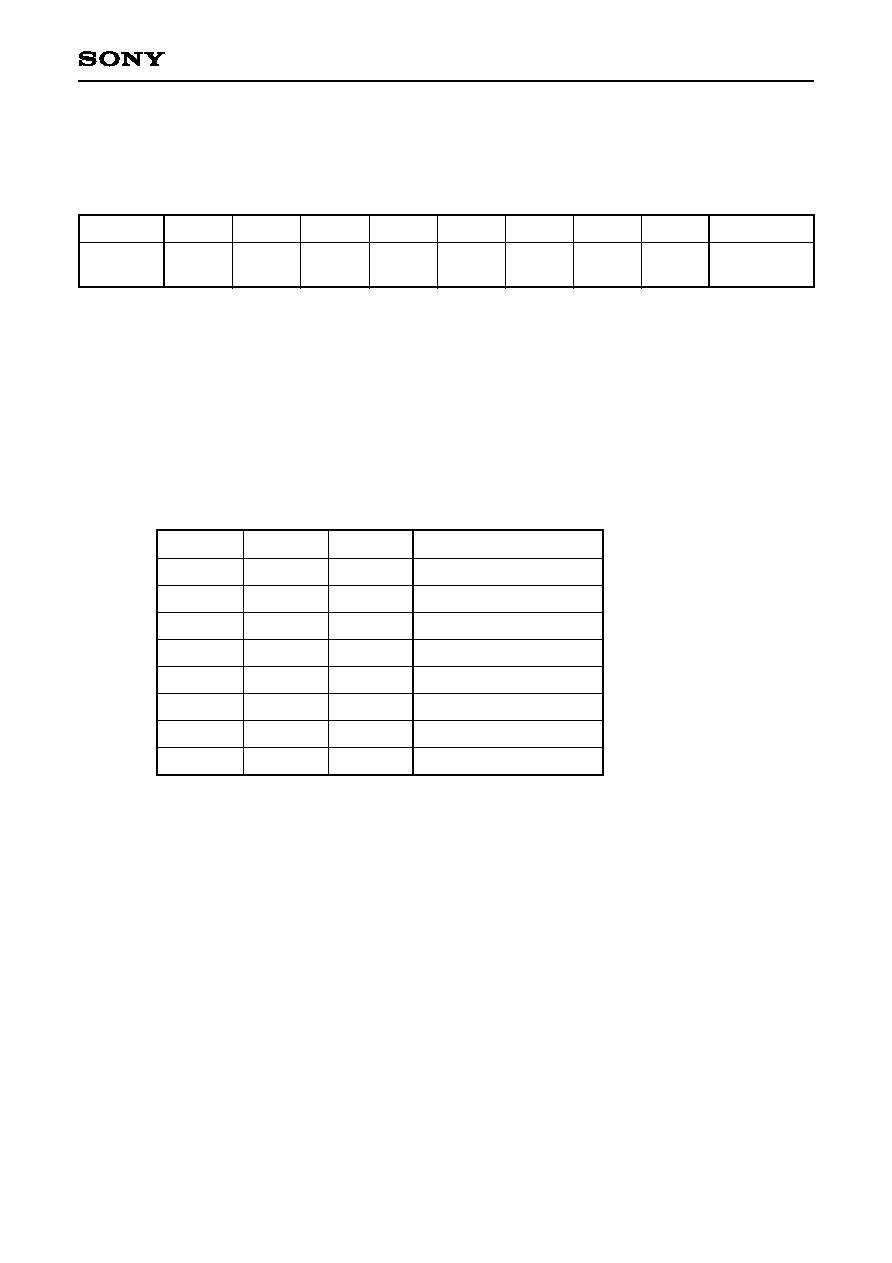

RAMSIZE1, 0 (DRAM size 1, 0)

Set these bits according to the total size of the DRAM connected to this IC.

RAMSIZE1

"L"

"L"

"H"

"H"

"L"

"H"

"L"

"H"

1M bits

2M bits

4M bits

8M bits

RAMSIZE0

DRAM total size

bit 4:

RAM8BITW (DRAM 8-bit wide)

This bit is set according to the bit width of the DRAM data bus to be connected.

High: Set this bit high when the DRAM to be connected has the 8-bit width.

Low: Set this bit low when the DRAM to be connected has the 16-bit width.

(Set low when two 8-bit width DRAMs are connected in parallel.)

≠ 23 ≠

CXD1818R

bit 3:

RAM2CAS (DRAM 2 CAS)

When the DRAM bus width is 16 bits, set this bit according to the number of CAS and WE signals.

When the DRAM bus width is 8 bits, this bit has no meaning.

High: Set this bit high when the IC is connected to a DRAM with 2 CAS signals and 1 WE signal.

Low: Set this bit low when the IC is connected to a DRAM with 1 CAS signal and 2 WE signals.

bit 2:

RESERVED

Normally set low.

bits 1, 0:

CLKSEL1, 0 (CLK select 1, 0)

These bits determine the clock frequency output from the CLK pin.

CLKSEL1

"L"

"L"

"H"

"H"

"L"

"H"

"L"

"H"

Fixed to high

Same frequency as XTL1

1/2 of XTL1

RESERVED

CLKSEL0

Clock frequency

1-1-2. 01h

(1) RAWSEC (raw second) register (read)

RAWSEC (raw second) register

01h (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

RAWSEC

The Header Second byte for the sector being sent from the CD DSP while DECINT is active can be read from

this register.

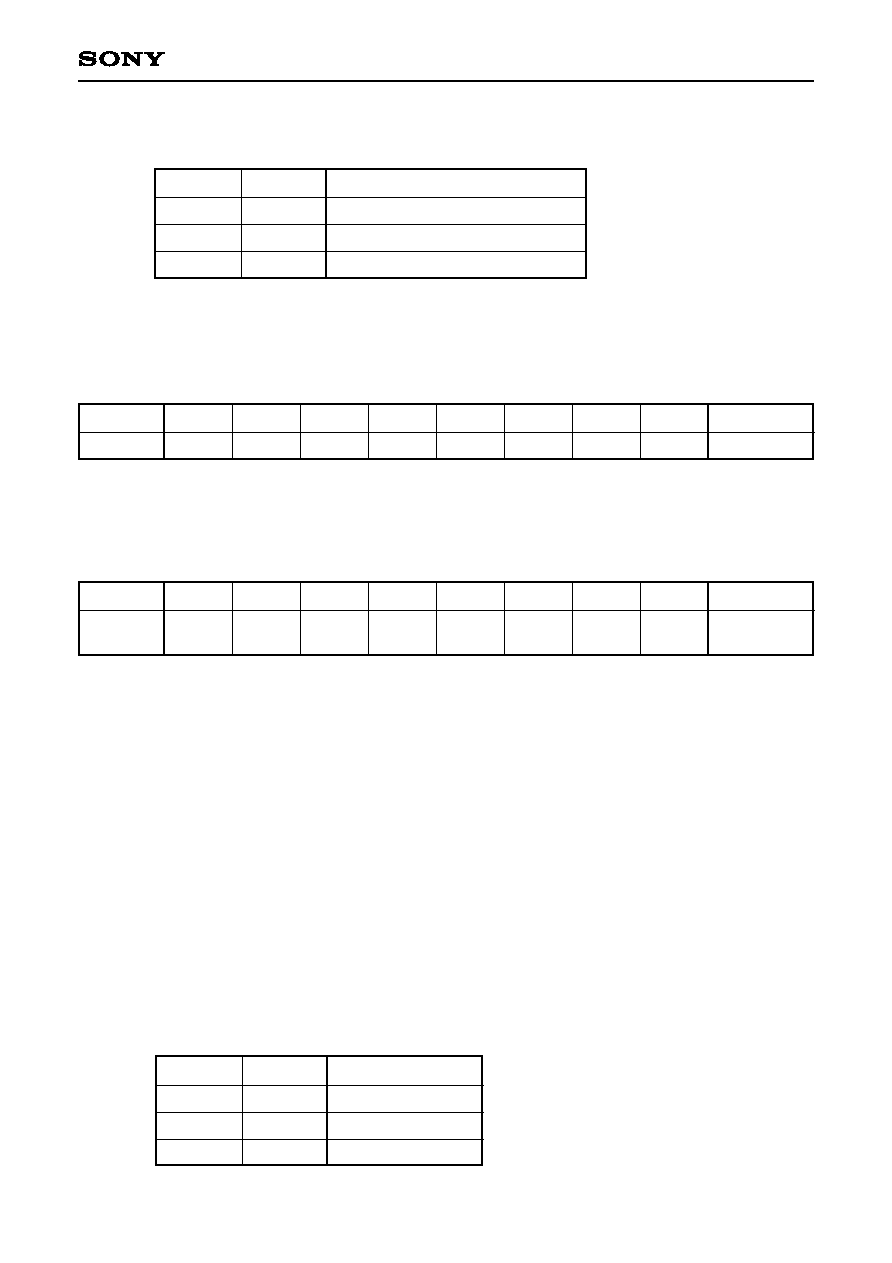

(2) CONFIG1 (configuration 1) register (write)

CONFIG1 (configuration 1) register

01h (W)

SW

OPEN

SYC

NGC2

SYC

NGC1

SYC

NGC0

DCK

SEL

"L"

SBC

ECC1

SBC

ECC0

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

CONFIG1

bit 7:

SWOPEN (sync window open)

High: The Sync mark detection window opens. In this case, the IC's internal Sync protection circuit

is disabled.

Low: The Sync mark detection window is controlled by the IC's internal Sync protection circuit.

bits 6 to 4: SYCNGC2 to 0 (sync NG count 2 to 0)

The Sync mark detection window opens once the number of Sync marks specified by these bits is

inserted. Setting a value of 1h or less for these bits is prohibited. (After a reset, these bits are set to

2h.)

bit 3:

DCKSEL (Dsp Clock Select)

High: DSPCLK 16.9344MHz

Low: DSPCLK 33.8688MHz

bit 2:

RESERVED

Normally set low.

≠ 24 ≠

CXD1818R

BCKMD1

"L"

"L"

"H"

"L"

"H"

"X"

16BCLKs/WCLK

24BCLKs/WCLK

32BCLKs/WCLK

BCKMD0

bits 1, 0:

SBCECC1, 0 (subcode ECC 1, 0)

These two bits specify the error correction method when decoding the subcode.

SBECC1

"X"

"L"

"H"

"L"

"H"

"H"

Error correction not performed.

Single error correction performed.

Double error correction performed.

SBECC0

Subcode error correction

1-1-3. 02h

(1) RAWBLK (raw block) register (read)

RAWBLK (raw block) register

02h (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

RAWBLK

The Header Block byte for the sector being sent from the CD DSP while DECINT is active can be read from

this register.

(2) DSPIF (DSP interface) register (write)

DSPIF (DSP interface) register

02h (W)

C2PO

L1st

LCH

LOW

BCK

RED

BCKL

MD1

BCKL

MD0

LSB

1st

"L"

BFSH

DFSL

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

DSPIF

This register controls the connection mode with the CD DSP. After the IC is reset, the sub CPU sets this

register according to the CD DSP to be connected.

bit 7:

C2PL1ST (C2PO lower byte first)

High: When two bytes of data are input, C2PO inputs the lower byte first followed by the upper byte.

Low: When two bytes of data are input, C2PO inputs the upper byte first followed by the lower byte.

Here, "upper byte" means the upper 8 bits including MSB from the CD DSP and "lower byte"

means the lower 8 bits including LSB from the CD DSP. For example, the Header minute

byte is the lower byte and the second byte, the upper byte.

bit 6:

LCHLOW (Lch low)

High: When LRCK is low, determined to be the left channel data.

Low: When LRCK is high, determined to be the right channel data.

bit 5:

BCKRED (BLCK rising edge)

High: Data is strobed at the rising edge of BCLK.

Low: Data is strobed at the falling edge of BCLK.

bits 4, 3:

BCKMD1, 0 (BCLK mode 1, 0)

These bits are set according to the number of clocks output for BCLK during 1/2 LCLK cycle by the

CD digital signal processing LSI (CD DSP).

≠ 25 ≠

CXD1818R

bit 2:

LSB1ST (LSB first)

High: Connected with the CD DSP which outputs data with LSB first.

Low: Connected with the CD DSP which outputs data with MSB first.

bit 1:

RESERVED

Normally set low.

Any change to the bits in this register must be made in the decoder disable status. (After the IC is

reset, the address is 28h.)

bit 0:

BFSHDFSL (buffering subheader flag select)

High: The Sub Headers written two times are compared and, if they do not match, the result

reports an error to bits 3 to 0 of BFHDRFLG.

Low: When the C2PO of the Sub Headers written two times are both high, that reports an error to

the bits 3 to 0 of BFHDRFLG.

1-1-4. 03h

(1) RAWMD (raw mode) register (read)

RAWMD (raw mode) register

03h (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

RAWMD

The Header Mode byte for the sector being sent from the CD DSP while DECINT is active can be read from

this register.

(2) RFINTVL (refresh interval) register (write)

RFINTVL (refresh interval) register

03h (W)

b7

b6

b5

b4

b3

b2

b1

b0

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

RFINTVL

This register determines the refresh interval. The refresh interval is RFINTVL

◊

4

◊

TW. Here, TW represents

the XTL1 clock frequency. Note that this IC performs RAS only refresh.

≠ 26 ≠

CXD1818R

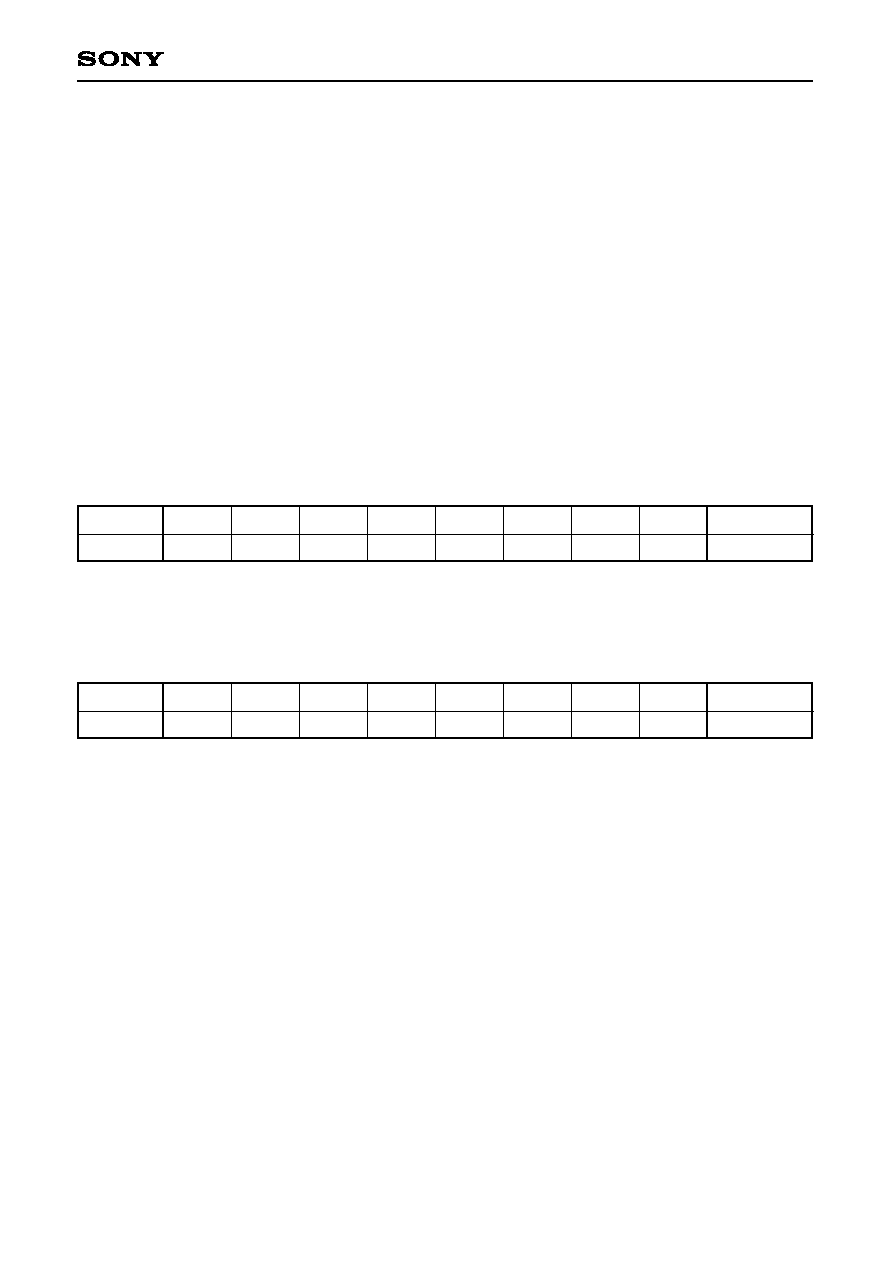

bits 7, 6:

DSTBSL1, 0

These bits determine the frequency of the DSTB and XLAT clocks used for passing data (DATO) to

the CD DSP. The sub CPU sets these bits according to the frequency of the clock on the XTL1 pin.

(The maximum frequency for DSTB is 1MHz.)

DSTBDL1

0

0

1

1

0

1

0

1

1/24 of XTL1

1/32 of XTL1

1/48 of XTL1

1/64 of XTL1

DSTBDL0

Frequency

bit 5:

DISXLAT (disable XLAT output)

High: After the contents of the DSPCMD register are transferred to the DSP, a latch pulse is not

output from the XLAT pin. In this case, the sub CPU uses DSPCMDLT (bit 0 of the

CHPCTL0 register) to output a latch pulse from the XLAT pin at the appropriate time.

Low: After the contents of the DSPCMD register are transferred to the DSP, a latch pulse is output

from the XLAT pin.

bits 4, 3:

XFRBYT1, 0 (transfer command byte length 1,0)

These bits determine the number of bytes in the command data (DSPCMD register) to be

transferred to the CD DSP. The relationship between the settings and the number of transferred

bytes is shown in the following table.

XFRBYT1

"L"

"L"

"H"

"H"

"L"

"H"

"L"

"H"

Prohibited

1

2

3

XFRBYT0

Number of transferred bytes

1-1-5. 04h

(1) BFMIN (buffer minute) register (read)

BFMIN (buffer minute) register

04h (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

BFMIN

During the execution of a write-only or real-time error correction command and after execution of a repeat

correction command, the Header Minute byte of the current sector can be read from this register. This register

is invalid when the decoder is disabled or a monitor-only command is being executed.

(2) DSPCTL (DSP control) register (write)

DSPCTL (DSP control) register

04h (W)

DSTB

SL1

DSTB

SL0

DIS

XLAT

XFR

BYT1

XFR

BYT0

FAST

DSTB

EXCK

SEL1

EXCK

SEL0

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

DSPCTL

≠ 27 ≠

CXD1818R

bit 1:

EXCKSEL1

bit 0:

EXCKSEL0

These bits determine the frequency of the EXCK clock that is used to get the subcode from the CD

DSP. The sub CPU sets these bits according to the clock frequency on the XTL1 pin and the

playback speed.

05h (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

BFSEC

During the execution of a write-only or real-time error correction command and after execution of a repeat

correction command, the Header Second byte of the current sector can be read from this register. This register

is invalid when the decoder is disabled or a monitor-only command is being executed.

(2) DSPCMD (DSP command) register (write)

DSPCMD (DSP command) register

05h (W)

b7

b6

b5

b4

b3

b2

b1

b0

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

DSPCMD

The data to be serially transferred to the CD DSP is written in this register. This register is a three-byte LIFO

(last-in, first-out) register.

bits 2:

FASTDSTB

When this bit is high, it is possible to make the frequencies faster of the DSTB, DATO and XLAT

outputs to the CD DSP set in DSTBSL1 and 0 (DSPCTL bits 7 and 6).

DSTBSL1

0

0

1

1

0

1

0

1

1/48 of XTL1

1/16 of XTL1

1/8 of XTL1

1/4 of XTL1

DSTBSL0

Frequency

EXCKSEL1

"L"

"L"

"H"

"H"

"L"

"H"

"L"

"H"

1/32 of XTL1

1/16 of XTL1

1/8 of XTL1

Prohibited

EXCKSEL0

EXCK clock

1-1-6. 05h

(1) BFSEC (buffer second) register (read)

BFSEC (buffer second) register

≠ 28 ≠

CXD1818R

1-1-7. 06h

(1) BFHDRBLK (buffer header block) register (read)

BFHDRBLK (buffer block) register

06h (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

BFHDRBLK

During the execution of a write-only or real-time error correction command and after execution of a repeat

correction command, the Header Block byte of the current sector can be read from this register. This register is

invalid when the decoder is disabled or a monitor-only command is being executed.

(2) CONFIG2 (configuration 2) register (write)

CONFIG2 (configuration 2) register

06h (W)

DLAR

NWMS

SBAI

TMSL

"L"

LRSEL

MMC

CSCT

ASET

EDCT

OECC

ASCON

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

CONFIG2

bit 7:

DLARNWMS (DLARA renewal mode select)

This bit is valid only when ATDLRNEW (DECCTL0 bit 0) = high.

High: DLARA is incremented when the data transfer to the host is completed for one sector.

Low: When the data transfer to the host is completed for one sector, DLARA is renewed in the

written area of that sector like before.

bit 6:

SBAITMSL (subcode buffering area increment timing select)

High: The internal subcode buffering area is incremented when the 1st pack of data is loaded and

de-interleaved.

Low: The internal subcode buffering area is incremented when the subcode sync is detected and

inserted.

bit 5:

RESERVED

Always set low.

bit 4:

LRSEL (LRCK select)

This bit is valid only with the CD-DA and ESP commands.

High: Data buffering is triggered by the falling edge of LRCK.

Low: Data buffering is triggered by the rising edge of LRCK.

bit 3:

MMC (multi media command)

High: Block error flag transfer appears as two bytes.

Low: Block error flag transfer appears as one byte like before.

bit 2:

CSCTASET (current sector area set)

High: When BFARA is set, CSCTARA is also set to that value.

Low: CSCTARA cannot be set.

bit 1:

EDCTOECC (EDC to ECC)

High: When ASCON (CONFIG2 bit 0) = high and the sector contains a C2PO or the EDC

calculation results are NG in the write only mode, error correction is started automatically.

bit 0:

ASCON (asynchronous correction on)

When error correction finishes, if the next buffered sector has not been corrected, error correction

continues.

Setting this bit and "Real-time correction mode (DECCTL1 (17h) bits 5 to 3 = "011")" results in

the same functions as the conventional "Asynchronous correction mode (DECCTL1 (17h) bits 5

to 3 = "100")". In addition, this bit can also be used during "Write only mode (DECCTL1 (17h)

bits 5 to 3 = "010")".

≠ 29 ≠

CXD1818R

07h (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

BFMD

During the execution of a write-only or real-time error correction command and after execution of a repeat

correction command, the Header Mode byte of the current sector can be read from this register. This register is

invalid when the decoder is disabled or a monitor-only command is being executed.

(2) DMACTL (DMA control) register (write)

DMACTL (DMA control) register

1-1-8. 07h

(1) BFMD (buffer mode) register (read)

BFMD (buffer mode) register

07h (W)

HCAS

CYCS

DMA

CYC4

DRQ

PRS

DRQ

PRS2

HWKR

QDIS

EDOD

RAM

EDCF

FEN

ECAS

CYCS

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

DMACTL

bit 7:

HCASCYCS

High: DMA for data transfer to the host is performed in the page mode with a minimum 8 CAS

cycles.

Low: DMA for data transfer to the host is performed in the page mode with a minimum 4 CAS

cycles.

bit 6:

DMACYC4 (DMA cycle 4)

High: The basic number of access clocks to the buffer is 4 clocks.

Low: The basic number of access clocks to the buffer is 5 clocks.

bit 5:

DRQPRS (DSP data write request priority select)

High: DMA for writing DSP data to the buffer has priority over refresh operation.

Low: Refresh operation has priority over DMA for writing DSP data to the buffer like before.

bit 4:

DRQPRS2 (DSP data write request priority 2)

High: DMA for buffering DSP data is performed preceeding DMA for host transfer.

Low: As usual.

bit 3:

HWKRQDIS (host DMA weak request disable)

High: (during send data commands via the buffer)

DMA from the buffer to the FIFO does not start unless there is 8 bytes or more of space in

the FIFO.

(during receive data commands via the buffer)

DMA from the FIFO to the buffer does not start until 8 bytes or more or the last data are

written to the FIFO.

Low: (during send data commands via the buffer)

DMA from the buffer to the FIFO starts if there is space in the FIFO.

(during receive data commands via the buffer)

DMA from the FIFO to the buffer starts as soon as data is written to the FIFO.

Setting this bit high reduces the number of times DMA is executed for the host. (because the

page mode is always used)

bit 2:

EDODRAM

High: Buffer access is performed in the EDO DRAM mode.

Low: Buffer access is performed in the normal DRAM mode.

bit 1:

EDCFFEN

High: EDC calculations are performed using the page mode and the FIFO.

Low: EDC calculations are performed by the conventional method.

bit 0:

ECASCYCS

This bit is valid only when EDCFFEN (DMACTL bit 1) = high.

High: DMA for EDC calculations is performed in the page mode with a minimum 8 CAS cycles.

Low: DMA for EDC calculations is performed in the page mode with a minimum 4 CAS cycles.

≠ 30 ≠

CXD1818R

1-1-11. 0Ah

(1) BFSUBM (buffer sub mode) register (read)

BFSUBM (buffer sub mode) register

0Ah (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

BFSUBM

During the execution of a write-only or real-time error correction command and after execution of a repeat

correction command, the Sub Header Sub Mode byte of the current sector can be read from this register. This

register is invalid when the decoder is disabled or a monitor-only command is being executed.

1-1-9. 08h

(1) BFFILE (buffer file) register (read)

BFFILE (buffer file) register

08h (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

BFFILE

During the execution of a write-only or real-time error correction command and after execution of a repeat

correction command, the Sub Header File byte of the current sector can be read from this register. This

register is invalid when the decoder is disabled or a monitor-only command is being executed.

1-1-10. 09h

(1) BFCHAN (buffer channel) register (read)

BFCHAN (buffer channel) register

09h (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

BFCHAN

During the execution of a write-only or real-time error correction command and after execution of a repeat

correction command, the Sub Header Channel byte of the current sector can be read from this register. This

register is invalid when the decoder is disabled or a monitor-only command is being executed.

≠ 31 ≠

CXD1818R

1-1-13. 0Ch

(1) RAWHDRFLG (raw header flag) register (read)

RAWHDRFLG (raw header flag) register

0Ch (R)

MIN

SEC

BLO

CK

MODE

CDR

DTEN

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

RAWHDR

This register indicates the C2PO value for the RAWHDR register.

bit 7:

Minute

bit 6:

Second

bit 5:

Block

bit 4:

Mode

bit 3 to 1:

RESERVED

bit 0:

CD-R Mode Detect Enable

(2) CDRMOD (CD-R mode) register (write)

CDRMOD (CD-R mode) register

bit 0:

CDRDTEN (CD-R mode detect enable)

High: The CDRINT status results when the decoder is operating in the monitor-only, write-only,

real-time correction or asynchronous correction mode if either of the conditions below is met.

(1) Bits 7 to 5 of the Raw Mode byte are not "000".

(2) The error flag of the Raw Mode byte is not established. (Values after processing by

setting of MDBYTCTL (DECCTL0 bit 2))

Low: The CD-R Mode byte is not detected.

1-1-14. 0Dh

(1) BFHDRFLG (buffer header flag) register (read)

BFHDRFLG (buffer header flag) register

0Dh (R)

MIN

SEC

BLO

CK

MODE

FILE

CHAN

SUB

MODE

DATA

TYPE

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

BFHDRFLG

0Ch (W)

CDR

DTEN

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

CDRMODE

0Bh (R)

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

BFDTYP

During the execution of a write-only or real-time error correction command and after execution of a repeat

correction command, the Sub Header Data Type byte of the current sector can be read from this register. This

register is invalid when the decoder is disabled or a monitor-only command is being executed.

1-1-12. 0Bh

(1) BFDTYP (buffer data type) register (read)

BFDTYP (buffer data type) register

≠ 32 ≠

CXD1818R

This register shows the error status of each byte in the BFHDR and BFSHDR registers. High means an error.

bit 7:

Minute

bit 6:

Second

bit 5:

Block

bit 4:

Mode

bit 3:

File

bit 2:

Channel

bit 1:

Submode

bit 0:

Data Type

1-1-15. 0Eh

(1) DECSTS0 (decoder status 0) register (read)

DECSTS0 (decoder status 0) register

0Eh (R)

SHRTSCT NOSYNC CORINH ERINBLK CORDONE EDCNG ECCNG TGTNTMET

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

DECSTS0

bit 7:

SHRTSCT (short sector)

Indicates that the Sync mark interval was less than 2351 bytes since the previous DECINT. This

sector does not remain in the buffer memory.

bit 6:

NOSYNC

Indicates that the Sync mark was inserted because one was not detected in the prescribed position

for the current sector.

bit 5:

CORINH (correction inhibit)

This is high if the current sector Mode and Form could not be determined when the AUTODIST bit

of the DECCTL register is set high. ECC or EDC is not executed in this sector. The CORINH bit is

invalid when AUTODIST is set low. It is high in any of the conditions below when the AUTODIST bit

is set high.

(1) When an error was found in the Mode byte.

(2) When the Mode byte is a value other than 01h or 02h.

(3) When the Mode byte is 02h and the C2 pointer is high in the Submode byte.

bit 4:

ERINBLK (erasure in block)

When the decoder is operating in the monitor-only, write-only or real-time mode which prohibits

erasure correction, this indicates that at least a 1-byte error flag (C2PO) has been raised in the

data excluding the Sync mark from the current sector CD DSP.

bit 3:

CORDONE (correction done)

Indicates that there is an error corrected byte in the current sector.

bit 2:

EDCNG

Indicates that an error was found in the current sector through an EDC check.

bit 1:

ECCNG

Indicates that an uncorrectable error was found somewhere between the Header byte and the

Parity byte in the current sector. (Bit 1 = don't care in the Mode2, Form2 sectors.)

bit 0:

TGTNTMET (target not met)

Indicates that the current sector address and the target address in the TGTMNT, TGTSEC, and

TGTBLK registers do not match. The error pointer is not referenced in this instance.

≠ 33 ≠

CXD1818R

1-1-16. 0Fh

(1) DECSTS1 (decoder status 1) register (read)

DECSTS1 (decoder status 1) register

0Fh (R)

CMDFM

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

DECSTS1

bit 7:

CMDFM

Results of comparing the value set in INTCOND1 bits 1 and 0 to DECSTS1 bits 1 and 0 (CMODE,

CFORM) of CSCTARA.

High: The values did not match.

Low: The values matched.

bits 6 to 3: RESERVED

bit 2:

EDCALL0 (EDC all 0)

This is high when there are no error flags in all the 4 EDC parity bytes of the current sector and

their values are all 00h.

bit 1:

CMODE (correction mode)

bit 0:

CFORM (correction form)

These bits indicate the Mode and Form of the current sector the decoder has discriminated to

correct errors when the decoder is operating in the real-time correction or repeat correction mode.

CFORM

"X"

"L"

"H"

"L"

"H"

"H"

MODE1

MODE2, FORM1

MODE2, FORM2

CMODE

1-1-17. 10h, 11h

(1) LSTARA-H, L (last area-high, low) register (read/write)

LSTARA-H, L (last area-high, low) register

10h (R/W)

11h (R/W)

b7

b6

b5

b4

b3

b2

b1

b8

b0

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

LSTARA-H

LSTARA-L

This register specifies the last order area. Set bits 7 to 1 of the LSTARA-H register low when writing in this

register.

1-1-18. 12h, 13h

(1) LHADR-H, L (last HADR-high, low) register (read/write)

LHADR-H, L (last HADR-high, low) register

12h (R/W)

13h (R/W)

b7

b6

b5

b4

b3

b2

b1

b8

b0

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

LHADR-H

LHADR-L

When host automatic transfer mode is disabled, this register specifies the upper limit for HADRC (the upper 9

bits); for the subcode buffering command, this register specifies the upper limit for the address (upper 9 bits).

The lower 11 bits are 7FFh. Set bits 7 to 1 of the LHADR-H register low when writing in this register.

≠ 34 ≠

CXD1818R

1-1-19. 14h

(1) XFRFMT0 (transfer format 0) register (read/write)

XFRFMT0 (transfer format 0) register

14h (R/W)

1024

XFR

512

XFR

SYNC

HEAD

ER

SBHE

ADER

USER

DATA

PARI

TY

AUTO

XFR

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

XFRFMT0

The transfer format for automatic data transfer is determined by this register. Before starting to transfer each

sector, this IC reads the value of the SCTINF register written in the buffer memory. The buffer memory data is

transferred to the host according to the read values and those in the XFRFMT1 and 0 registers. The

Mode/Form of bits 3 to 1 depends on the values of bits 2 and 1 in the SCTINF register.

Regarding Mode2 in the Yellow Book, don't care the Form2 (bit 2) of the SCTINF register. Set bits 3 to 1 of the

XFRFMT0 register high to transfer 2336 bytes of user data.

bit 7:

1024XFR

When this bit is set high, the user data (2048 bytes) is divided into 1024-byte blocks for

transmission. In this case, set bits 6 to 1 in the XFRFMT0 register and bits 7 to 0 in the XFRFMT1

register low. In other words, the Sync mark, Header, Sub Header, and Parity bytes, as well as the

block error flag, byte error flag, and subcode cannot be sent to the host. This transfer mode is not

supported for Mode2/Form2 sectors.

bit 6:

512XFR (512 bytes transfer mode)

When this bit is set high, the user data (2048 bytes) is divided into 512-byte blocks for

transmission. In this case, set bit 7 and bits 5 to 1 in the XFRFMT0 register and bits 7 to 0 in the

XFRFMT1 register low. In other words, the Sync mark, Header, Sub Header, and Parity bytes, as

well as the block error flag, byte error flag, and subcode cannot be sent to the host. This transfer

mode is not supported for Mode2/Form2 sectors.

bit 5:

SYNC

High: Sync marks are transferred to the host.

Low: Sync marks are not transferred to the host.

bit 4:

HEADER

High: The four Header bytes are transferred to the host.

Low: The four Header bytes are not transferred to the host.

bit 3:

SBHEADER

High: Mode1: This bit has no meaning.

Mode2: The eight Sub Header bytes are transferred to the host.

Low: The bytes indicated above are not transferred to the host.

bit 2:

USERDATA (user data)

High: Mode1 and Mode2/Form1: User data (2048 bytes) is transferred to the host.

Mode2/Form2:

User data (2324 bytes) is transferred to the host.

Low: The bytes indicated above are not transferred to the host.

bit 1:

PARITY

High: Mode1: The EDC, ECC parity bytes and the eight 00h bytes, for a total of 288 bytes, are

transferred to the host.

Mode2/Form1: The 280 EDC and ECC parity bytes are transferred to the host.

Mode2/Form2: The four reserved bytes (at the end of the sector) are transferred to the host.

Low: The bytes indicated above are not transferred to the host.

bit 0:

AUTOXFR

Set this bit high when operating in automatic transfer mode. Set this bit low when operating in

manual transfer mode. For CD-DA data, set 3Fh in this register when operating in automatic

transfer mode.

≠ 35 ≠

CXD1818R

1-1-20. 15h

(1) XFRFMT1 (transfer format 1) register (read/write)

XFRFMT1 (transfer format 1) register

15h (R/W)

ENBL

KEFL

BLKE

FLSL

ENBY

TFBT

BYTE

FLSL

ENSB

CBT

ALL

SBC

SBCE

STS

ZA

SQEF

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

XFRFMT1

bit 7:

ENBLKEFL (enable block error flag)

High: The block error flag (1 byte) is transferred to the host.

Low: The byte indicated above is not transferred to the host.

bit 6:

BLKEFLSL (block error flag select)

This bit is valid only when ENBLKEFL is high.

High: The value (one byte) written in the BLKESTS register by the sub CPU is transferred to the

host as the block error flag.

Low: The OR value of each bit in the byte error flag is transferred to the host as the block error flag.

bit 5:

ENBYTFBT (enable byte error flag buffering & transfer)

If this bit is set high, the operations described below are performed. If this bit is set low, the

operations described below are not performed.

(1) The byte error flag is buffered during execution of a write-only, real-time error correction, and

CD-DA command.

(2) When host automatic transfer mode is enabled (the AUTOXFR bit (bit 0) of the XFRFMT0

register is high), the byte error flag is transferred to the host.

The ENBYTFBT and BYTEFLSL bits are valid only when the USERDATA bit (bit 2) of the

XFRFMT0 register is high.

bit 4:

BYTEFLSL (byte error flag select)

This bit is valid only when ENBYTFBT is high. When this bit is set high, the value of BYTERSTS

(the byte error status register, described later) is written in the byte error flag area of the buffer

memory. Setting the BLKEFLSL bit low and the BYTEFLSL bit high at the same time is prohibited.

If this bit is set low, the value of C2PO from the CD DSP is written in the byte error flag area.

bit 3:

ENSBCBT (enable subcode buffering & transfer)

If this bit is set high, the operations described below are performed. If this bit is set low, the

operations described below are not performed.

(1) All subcodes or subcode-Q is buffered while the decoder executes CD-DA commands.

(2) When host automatic transfer mode is enabled (the AUTOXFR bit (bit 0) of the XFRFMT0

register is high), all subcodes or subcode-Q is transferred to the host.

Note that buffering the CD-ROM data and the subcodes or subcode-Q at the same time is not

supported.

bit 2:

ALLSBC (all subcode/subcode-Q)

This determines whether to buffer and transfer all subcodes or subcode-Q to the host when

ENSBCBT is high.

High: All subcodes

Low: Subcode-Q

≠ 36 ≠

CXD1818R

bit 1:

SBCESTS (subcode error status)

This

bit is valid only when ENSBCBT is high.

High: The value (one byte) written in the SBCESTS register by the sub CPU is transferred to the host.

Low: The byte indicated above is not transferred to the host.

bit 0:

ZASQEF (zero after subcode-Q error flag)

This bit is valid only when ENSBCBT and SBCESTS are both high. (This bit is valid only when

subcode-Q and the subcode error flag are transferred to the host.)

High: Five 00h bytes in addition to the subcode-Q error flag are transferred to the host.

Low: Five 00h bytes are not added to the subcode-Q error flag.

1-1-21. 16h

(1) DECCTL0 (decoder control 0) register (read/write)

DECCTL0 (decoder control 0) register

16h (R/W)

AUTO

DIST

MODE

SEL

FORM

SEL

ATTG

TMET

ENFM

2EDC

MDBY

TCTL

EN

DLA

ATDL

RNEW

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

DECCTL0

bit 7:

AUTODIST (auto distinction)

High: Errors are corrected according to the Mode byte and the Form bit read from the drive.

Low: Errors are corrected according to the MODESEL and FORMSEL bits (bits 6 and 5).

bit 6:

MODESEL (mode select)

bit 5:

FORMSEL (form select)

When AUTODIST is low, the sector is corrected in the Mode or Form indicated in the table below.

MODESEL

"L"

"H"

"H"

"L"

"L"

"H"

MODE1

MODE2, FORM1

MODE2, FORM2

FORMSEL

bit 4:

ATTGTMET (auto target met)

When this bit is high, the processing for TGTMET and INCTGT (CHPCTL0 bits 6 and 5) can be

performed inside of this IC, which was performed by the sub CPU formerly.

bit 3:

ENFM2EDC (enable Form2 EDC check)

High: EDC check for Form2 is enabled.Low: EDC check for Form2 is disabled. The EDCNG bit of

the DECSTS0 register goes low.

bit 2:

MDBYTCTL (mode byte control)

High: Even if there are data other than "0" in the upper six bits of the Mode byte in the Header, an

error does not result. Set this bit high when playing back discs such as CD-ROM.

Low: If the upper six bits of the Mode byte in the Header are not "000000", an error results.

≠ 37 ≠

CXD1818R

bit 1:

ENDLA (enable drive last area (address))

High: DLAR (Drive Last Area) is enabled. While the decoder is executing a write-only command,

real-time error correction command, or CD-DA command, if buffering of the buffer memory

area specified by DLAR is completed, the DRVOVRN (drive overrun) status results. Buffer-

write of subsequent sectors is then interrupted.

Also, while the decoder is executing a subcode buffering command, if data is written in the

buffer memory address specified by SLADR, the DRVOVRN (Drive Overrun) status results.

Buffer-write of subsequent sectors is then interrupted.

Low: DLAR (Drive Last Area) and SLADR are disabled when this is set low.

bit 0:

ATDLRNEW (auto DLARA renewal)

High: When the data transfer to the host is completed for one sector, DLARA is renewed in the

written area of the sector.

Low: DLARA is renewed by the sub CPU.

≠ 38 ≠

CXD1818R

1-1-22. 17h

(1) DECCTL1 (decoder control 1) register (read/write)

DECCTL1 (decoder control 1) register

17h (R/W)

ENSB

QRD

ESPB

CKMD

DEC

CMD2

DEC

CMD1

DEC

CMD0

ATW

SCTI

NTCR

CT1

NTCR

CT0

Adr.

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Reg.

DECCTL1

bit 7:

ENSBQRD (enable subcode-Q read)

The subcode is fetched from the DSP and the subcode-Q CRC check is performed. The sub CPU

can read the subcode-Q from the SUBQ register. Subcode decoding (de-interleave, error

correction) is performed.

bit 6:

ESPBCKMD (ESP BCLK mode)

The CD DSP sets this bit according to how many BCLK clocks are output during the LRCK/2 cycle.

(for ESP and CD-DA)

High: 16 BCLKs/WCLK

Low: 24 BCLKs/WCLK

bits 5 to 3: DECCMD2 to 0 (decoder commands 2 to 0)

DECCMD2

"L"

"L"

"L"

"L"

"H"

"H"

"H"

"H"

"L"

"L"

"H"

"H"

"L"

"L"

"H"

"H"

DECCMD1

"L"

"H"

"L"

"H"

"L"

"H"

"L"

"H"

DECCMD0

DECODER Disable

Monitor-only

Write-only

Real-time correction

Asynchronous correction

Subcode buffering

ESP mode

CD-DA

Decoder command

bit 2:

ATWSCTI (auto write sector information)

When this bit is high, the SCTINF, BLKESTS and BYTESTS registers are set and writing to the

buffer memory is performed automatically.

The values of SCTINF, BLKESTS and BYTESTS, set automatically, are shown below.

SCTINF bit 7 to 3 = `00000' b

bit 2 = Current sector CMODE (DECSTS1 bit 1)

bit 1 = Current sector CFORM (DECSTS1 bit 0)

bit 0 = `1' (transferred to the host)

BLKESTS = `00' h

BYTESTS = `00' h

bits 1 to 0: NTCRCT2 to 0 (number of times of correction)

This determines the number of times where error correction is performed when operating in

asynchronous correction mode. (1 to 4 times)

≠ 39 ≠

CXD1818R

1-1-23. 18h

(1) XFRSTS (data transfer status) register (read)

XFRSTS (data transfer status) register

18h (R)

REV#

2

REV#

1

REV#

0

CMDO

BUSY

CBFW

RRDY

CBFR

DRDY

Adr.

bit7

bit6