| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXD2719Q | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

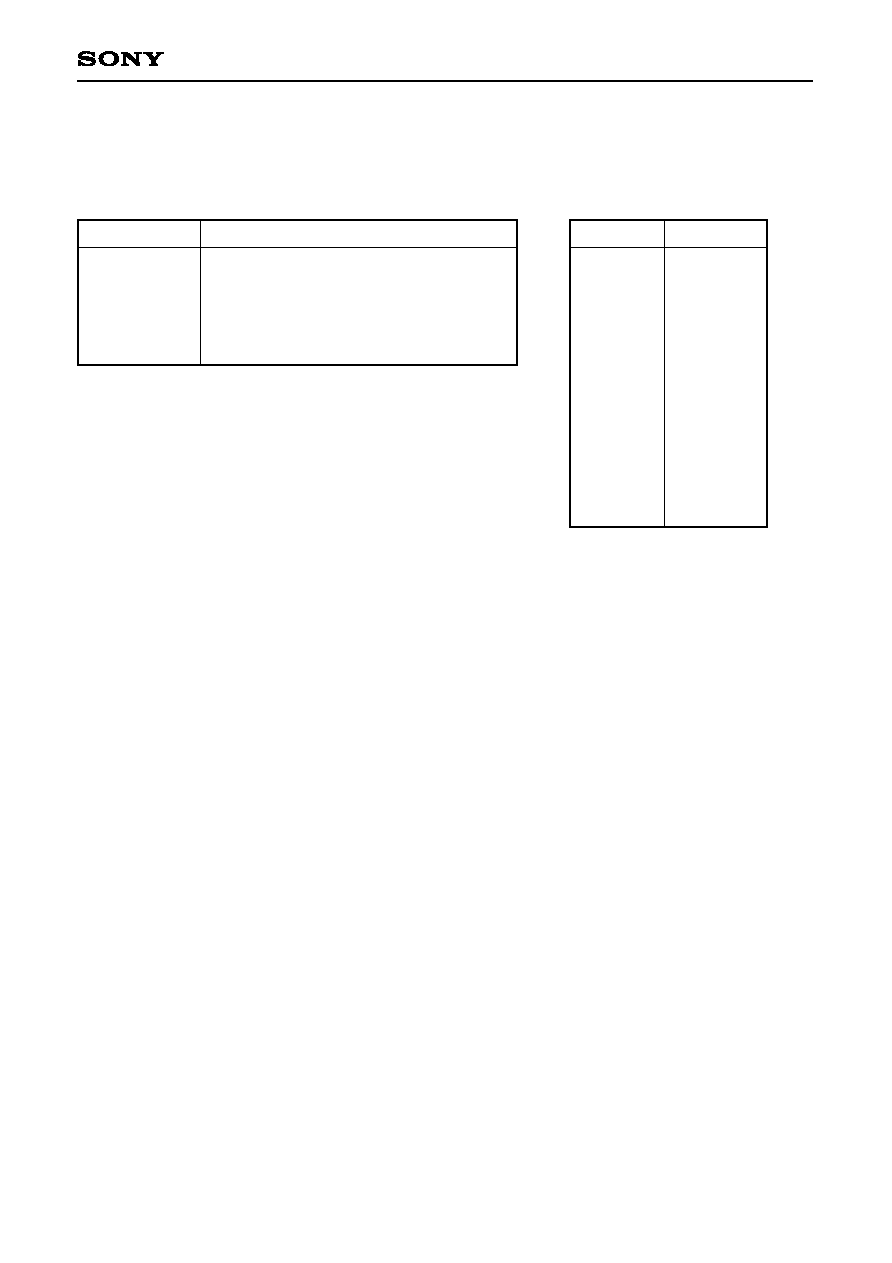

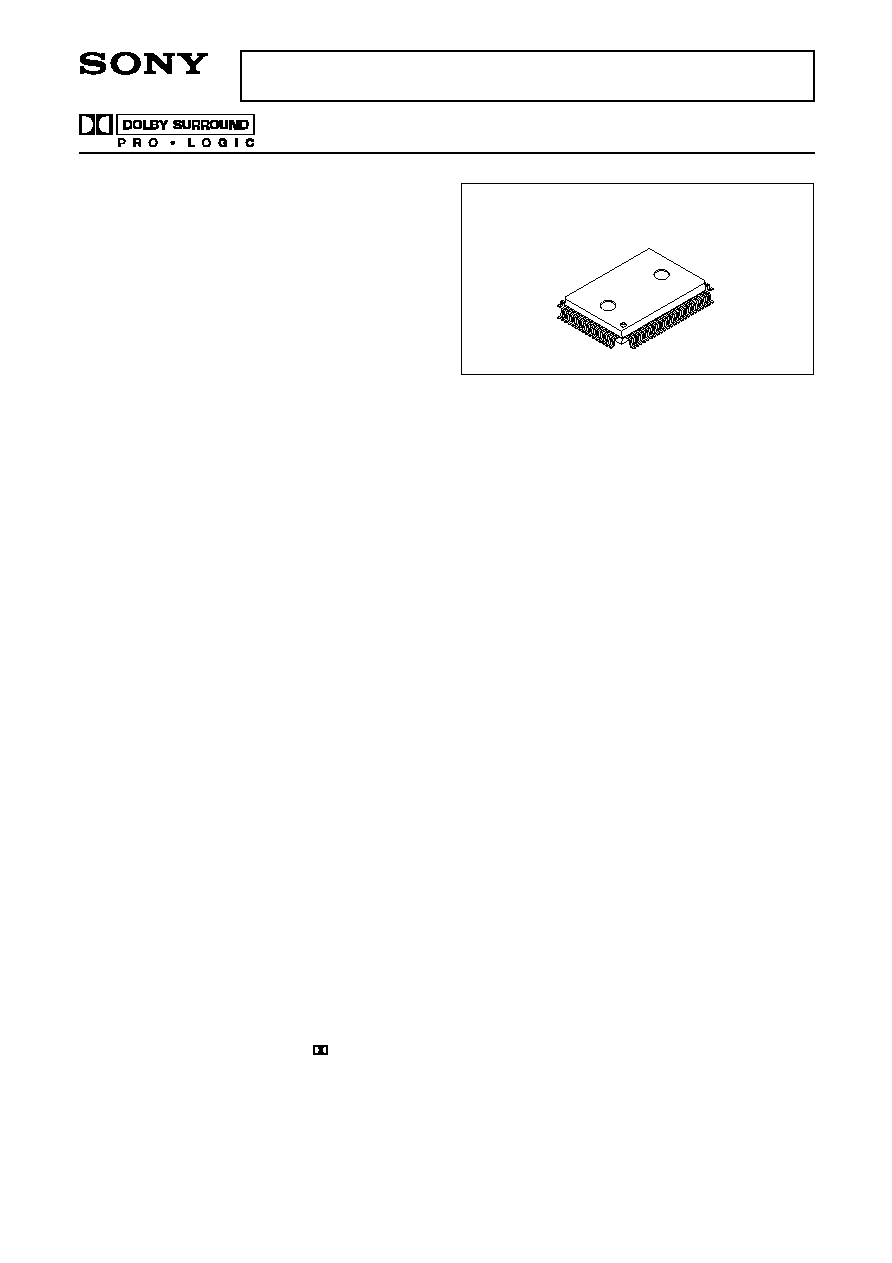

Single-Chip Dolby Pro Logic Surround Decoder

Description

The CXD2719Q is a CMOS LSI developed for

Dolby Pro Logic Surround. A SRAM for short delay

and AD/DA converters are built in, and all functions

necessary for Dolby Pro Logic Surround such as an

adaptive matrix, a passive decoder including BNR,

auto input balance, a noise sequencer and center

channel mode control are contained on a single

chip.

Features

∑ Dolby Pro Logic Surround decoding with a single

chip

∑ 2-channel 1-bit AD converter, decimation filter and

prefilter operational amplifier

∑ 4-channel 1-bit DA converter, oversampling filter

and post filter

∑ Analog switch for DSP bypass

∑ Analog electronic attenuator (+1.5 to ≠29.5dB) for

center/surround channel trim

∑ 24K-bit SRAM for short delay

∑ No separation or other variance for digital

processing

∑ External parts reduced by incorporating analog

circuits

Functions

∑ Adaptive matrix

∑ Center channel mode control

(Normal/Phantom/Wide)

∑ Dolby 3 Stereo

∑ Auto input balance control (ON/OFF)

∑ Noise sequencer

∑ Variable delay time (0 to 34.8ms)

∑ 7 kHz low-pass filter (12dB/Oct)

∑ Modified Dolby B-type NR

∑ Simple SFC function

∑ SFC mode

∑ DSP bypass mode (L, R-channel through)

Structure

Silicon gate CMOS

Applications

Equipment having Dolby Pro Logic Surround

function such as AV amplifiers, receivers and

compact music systems

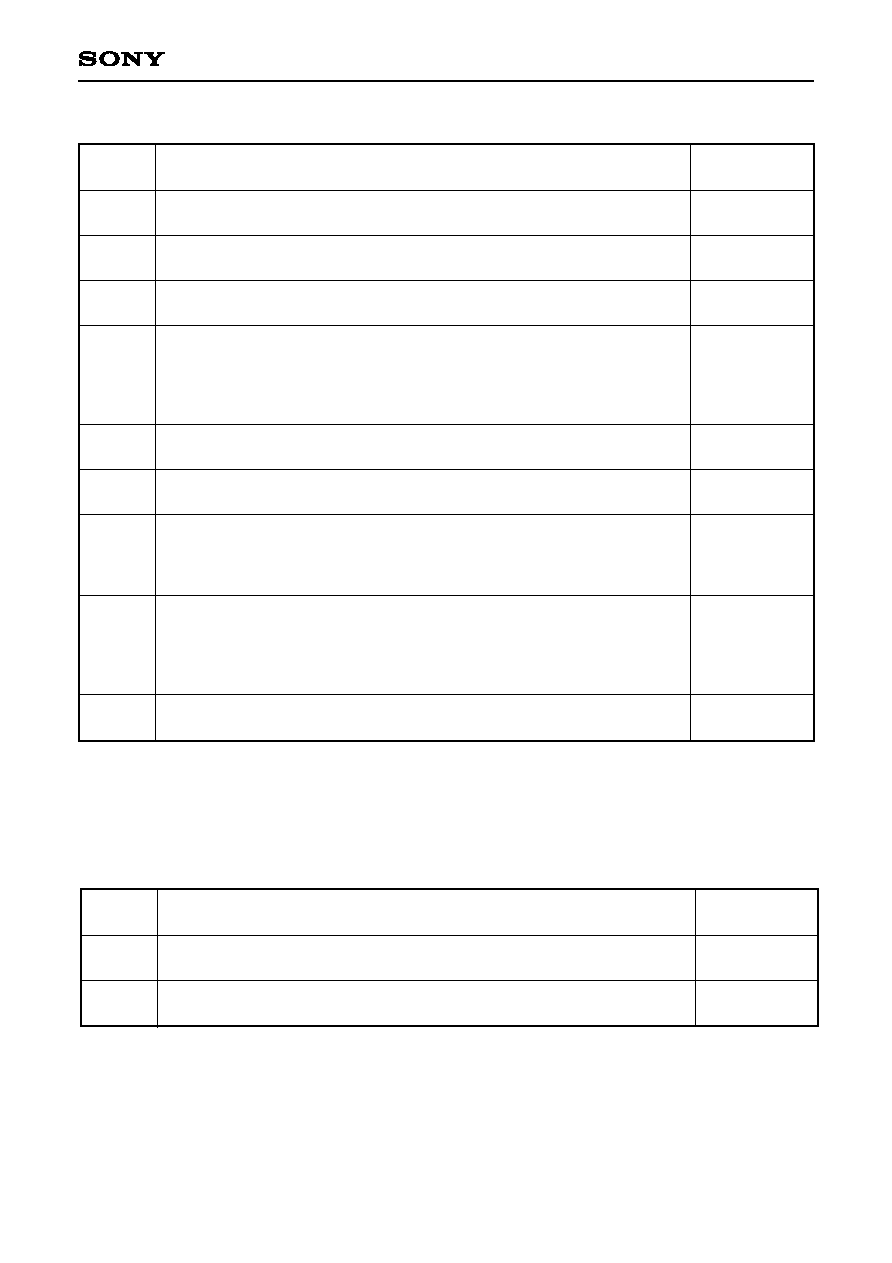

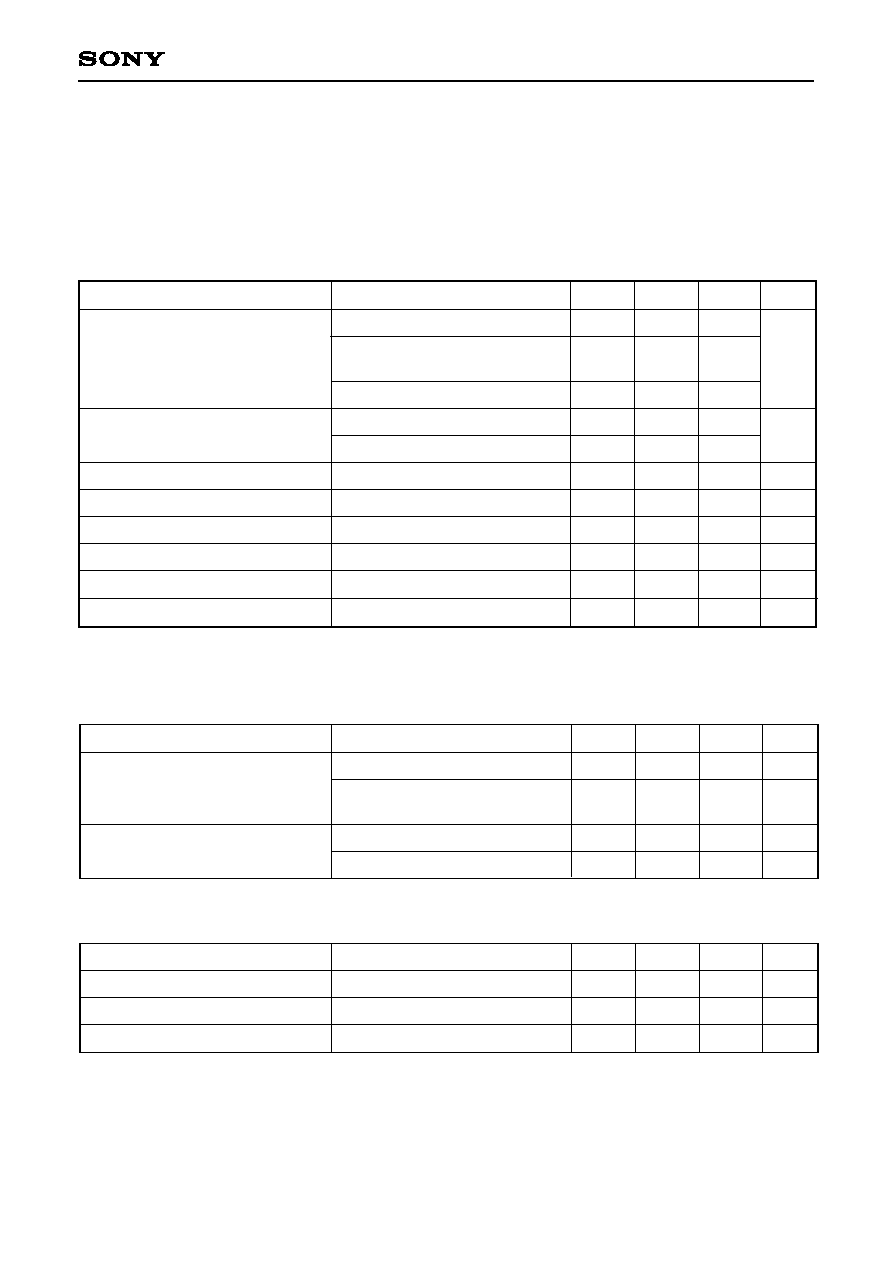

Absolute Maximum Ratings (Ta = 25∞C, V

SS

= 0V)

∑ Supply voltage

V

DD

V

SS

≠ 0.5 to +7.0

V

∑ Input voltage

V

I

V

SS

≠ 0.5 to V

DD

+ 0.5

V

∑ Output voltage

V

O

V

SS

≠ 0.5 to V

DD

+ 0.5

V

∑ Operating temperature

Topr

≠20 to +70

∞C

∑ Storage temperature

Tstg

≠55 to +150

∞C

Recommended Operating Conditions

∑ Supply voltage

V

DD

Analog system

4.75 to 5.25 (5.0 typ.)

V

Digital system

4.50 to 5.25 (5.0 typ.)

V

∑ Operating temperature

Ta

≠20 to +70

∞C

Input/Output Capacitance

∑ Input capacitance C

IN

9 (max.)

pF

∑ Output capacitance C

OUT

11 (max.)

pF

∑ Input/output capacitance

C

I/O

11 (max.)

pF

Measurement conditions: V

DD

= V

I

= 0V, F = 1MHz

Maximum Current Consumption

(Ta = 25∞C, V

DD

= 5.25V)

∑ Digital/analog block total: 166.7mA

Dolby level

∑ During analog input: 200 to 300mVrms

∑ During digital input: ≠20dBFS

Analog characteristics

Pro Logic ON: Dolby level = 300mVrms

Prefilter gain = ≠3.52dB

∑ S/N: L, Rch = 80dB, C, Sch = 72dB

∑ THD + N: L, Rch = 0.015%, C, Sch = 0.03%

All values for typ.

≠ 1 ≠

E98944-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

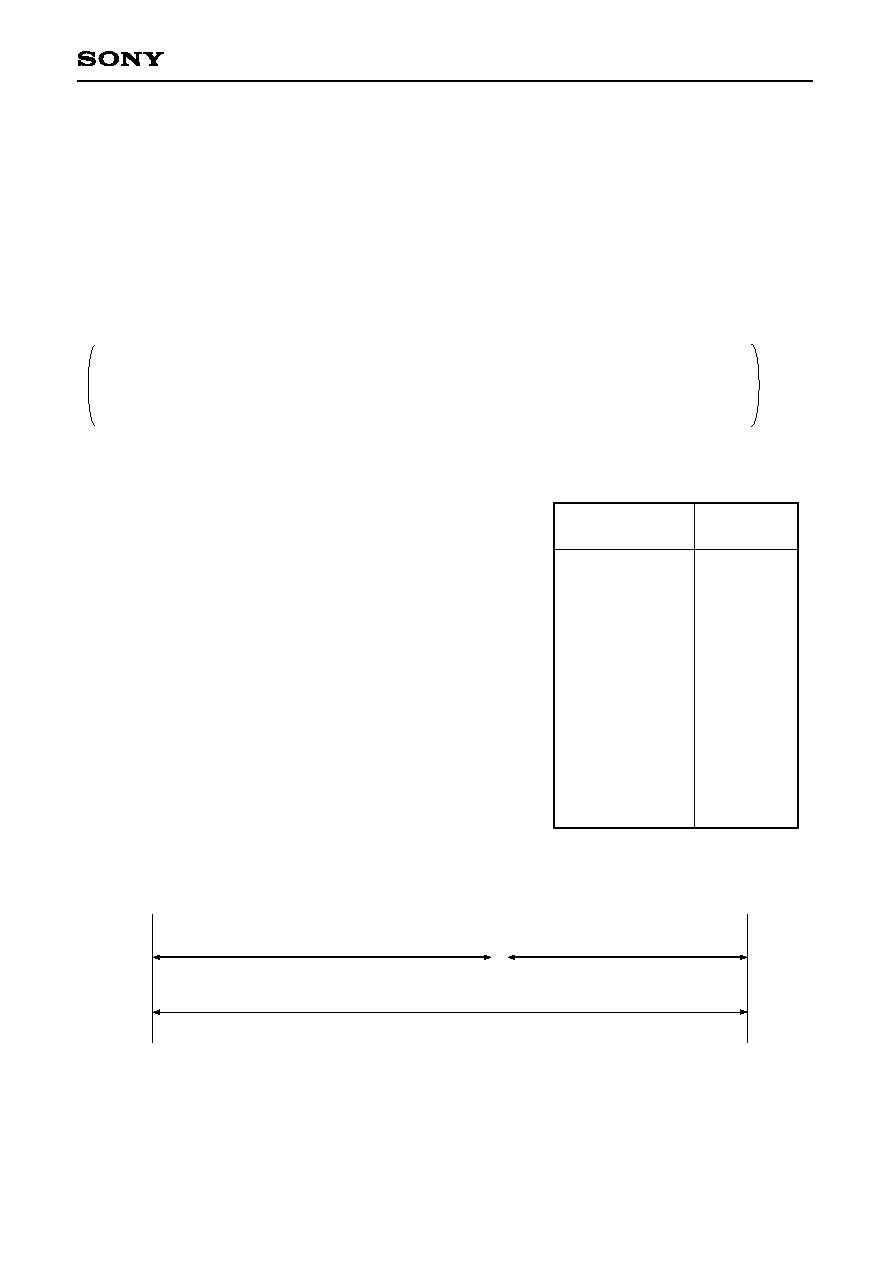

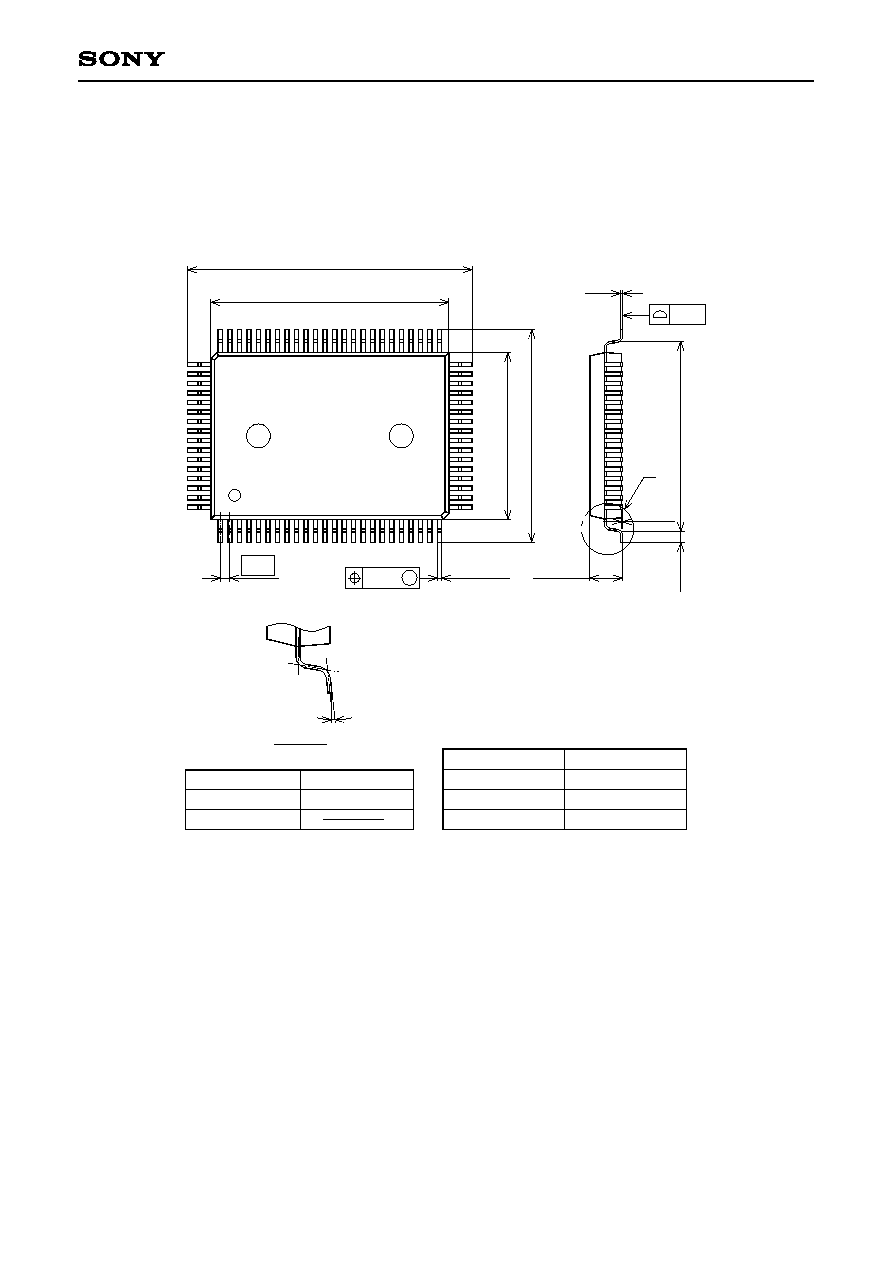

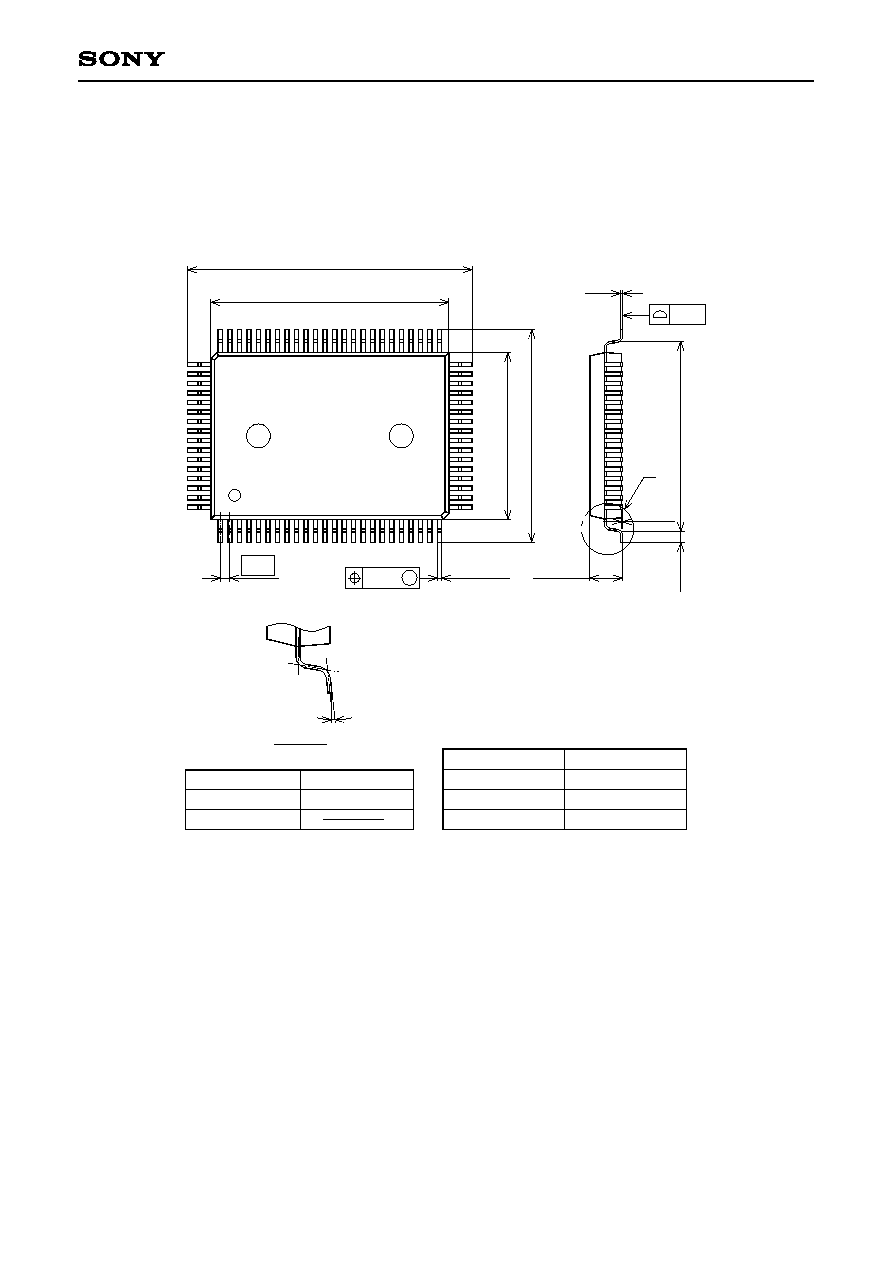

CXD2719Q

80 pin QFP (Plastic)

This device is available only to parties obtaining the license from Dolby Laboratories Licensing Corporation.

"Dolby", the double-D symbol and "Pro Logic" are trademarks of Dolby Laboratories Licensing Corporation.

≠ 2 ≠

CXD2719Q

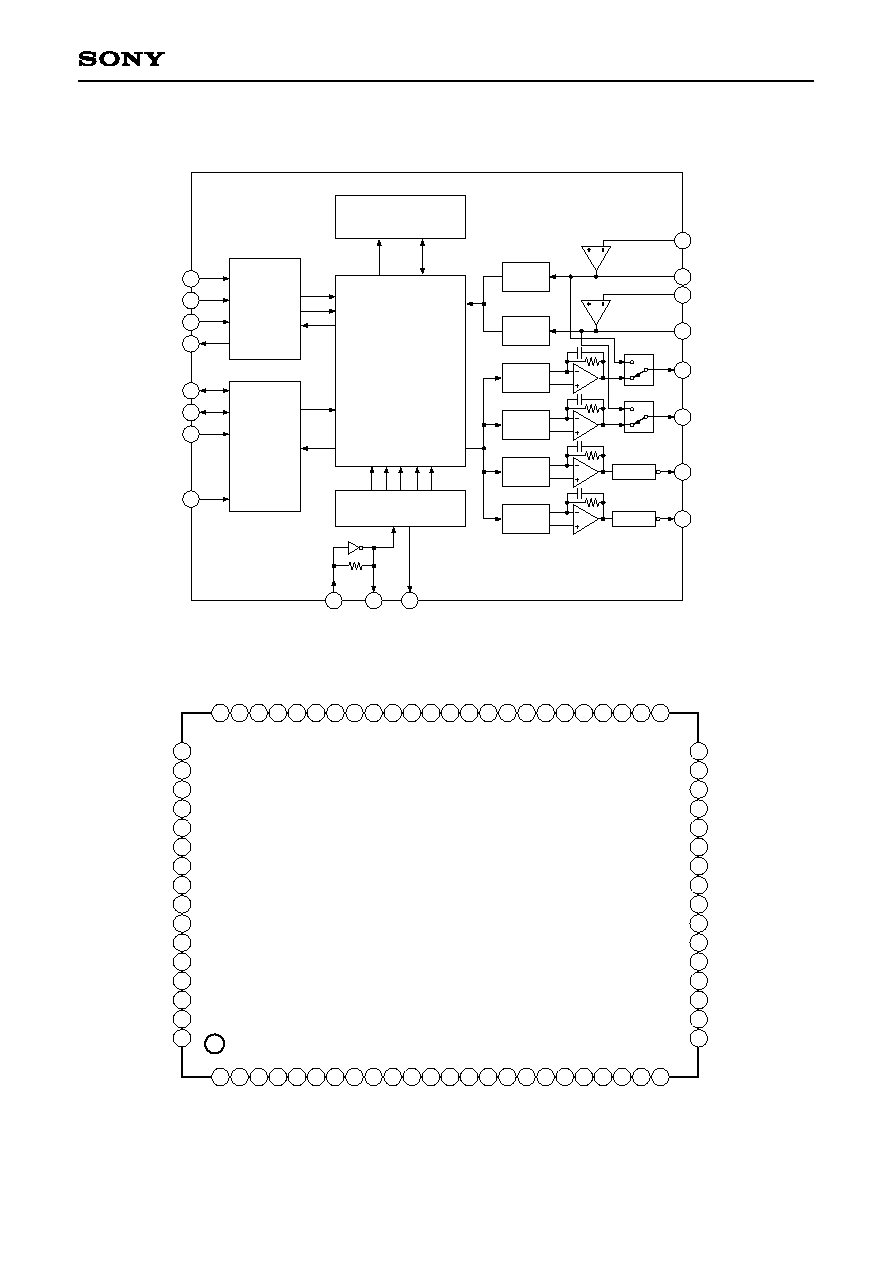

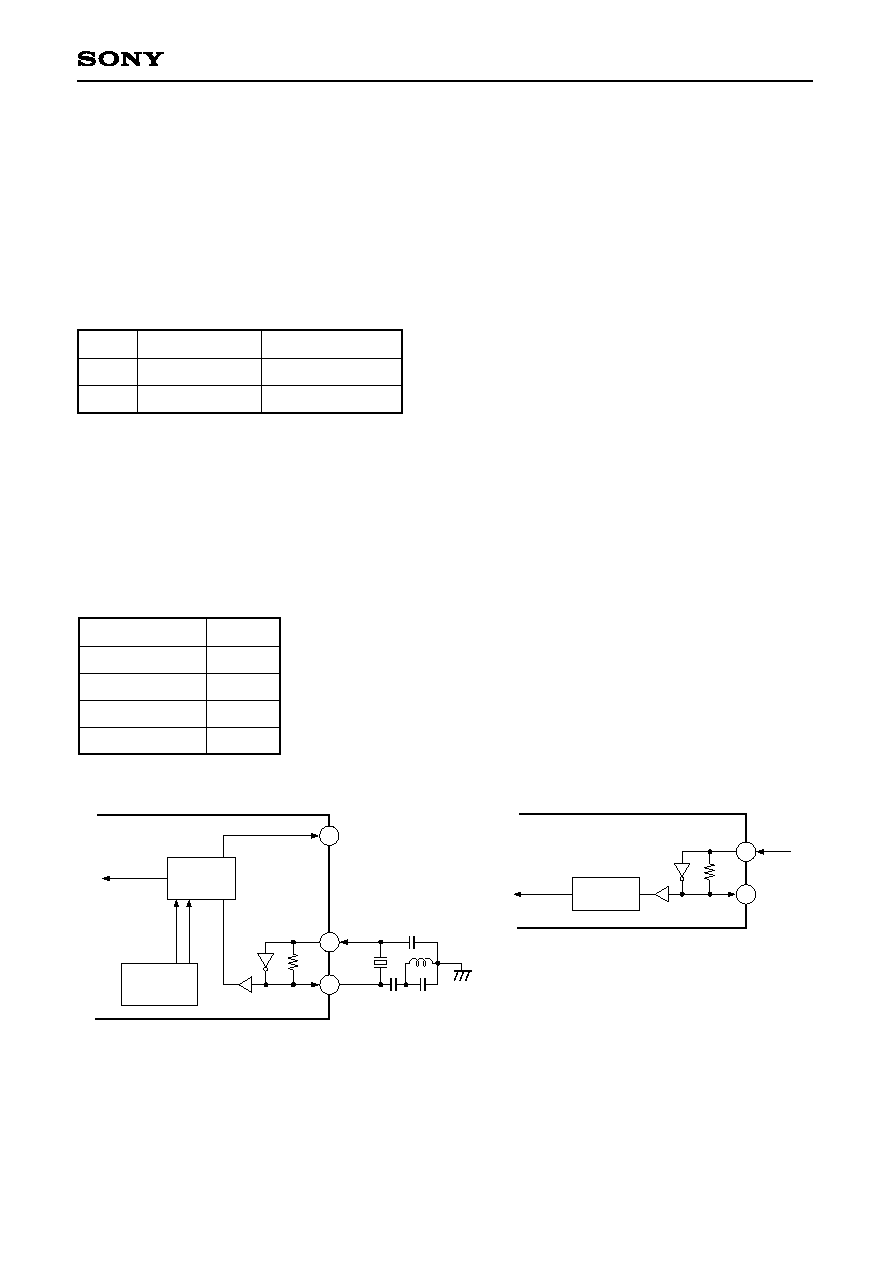

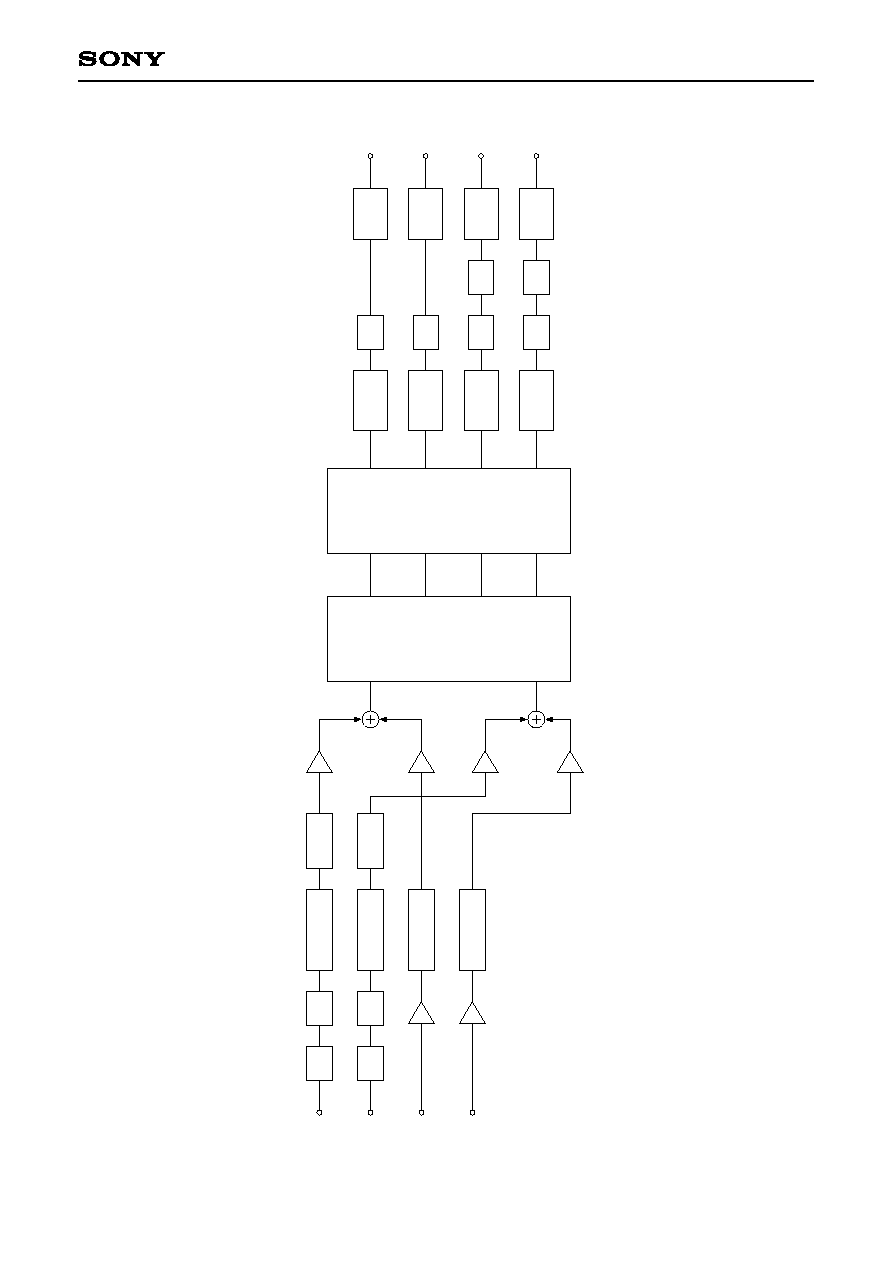

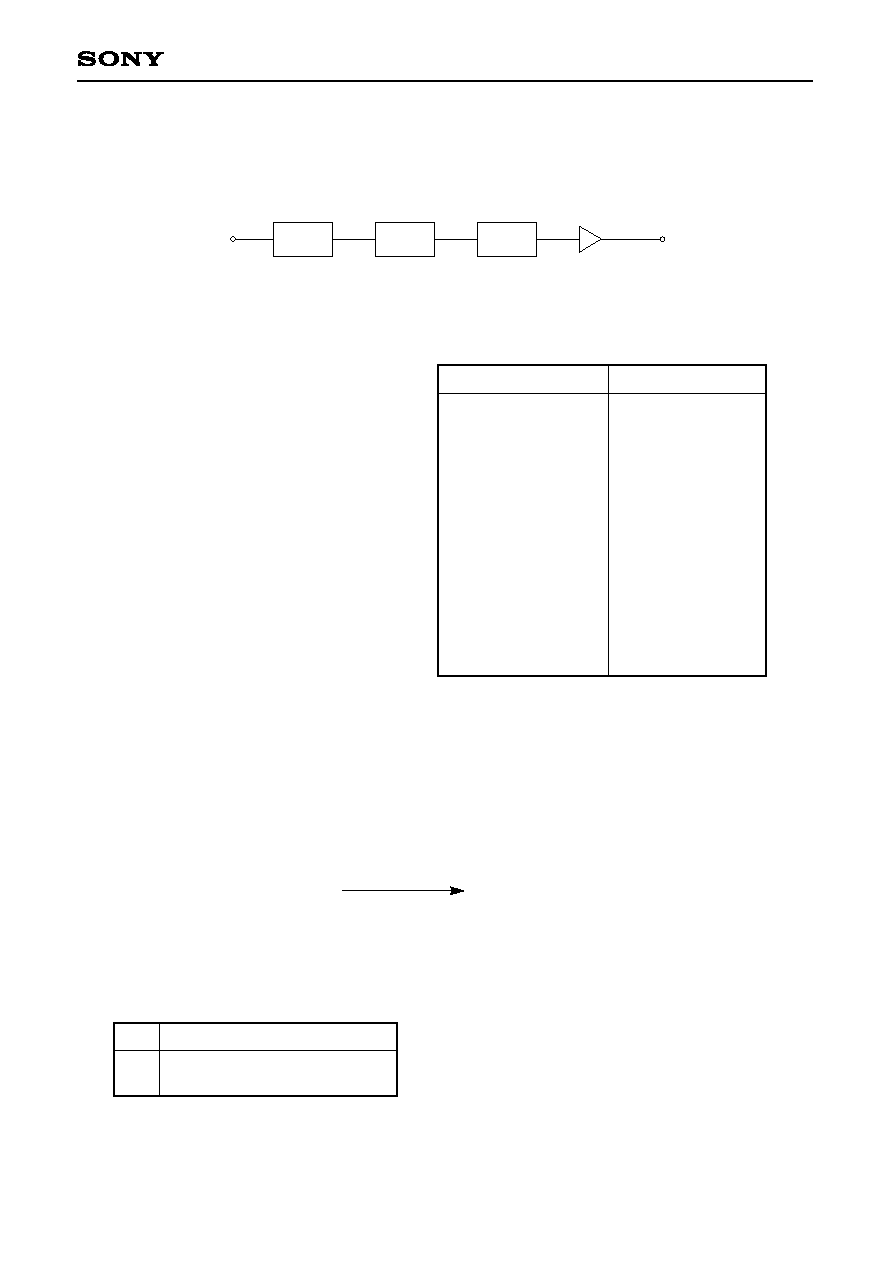

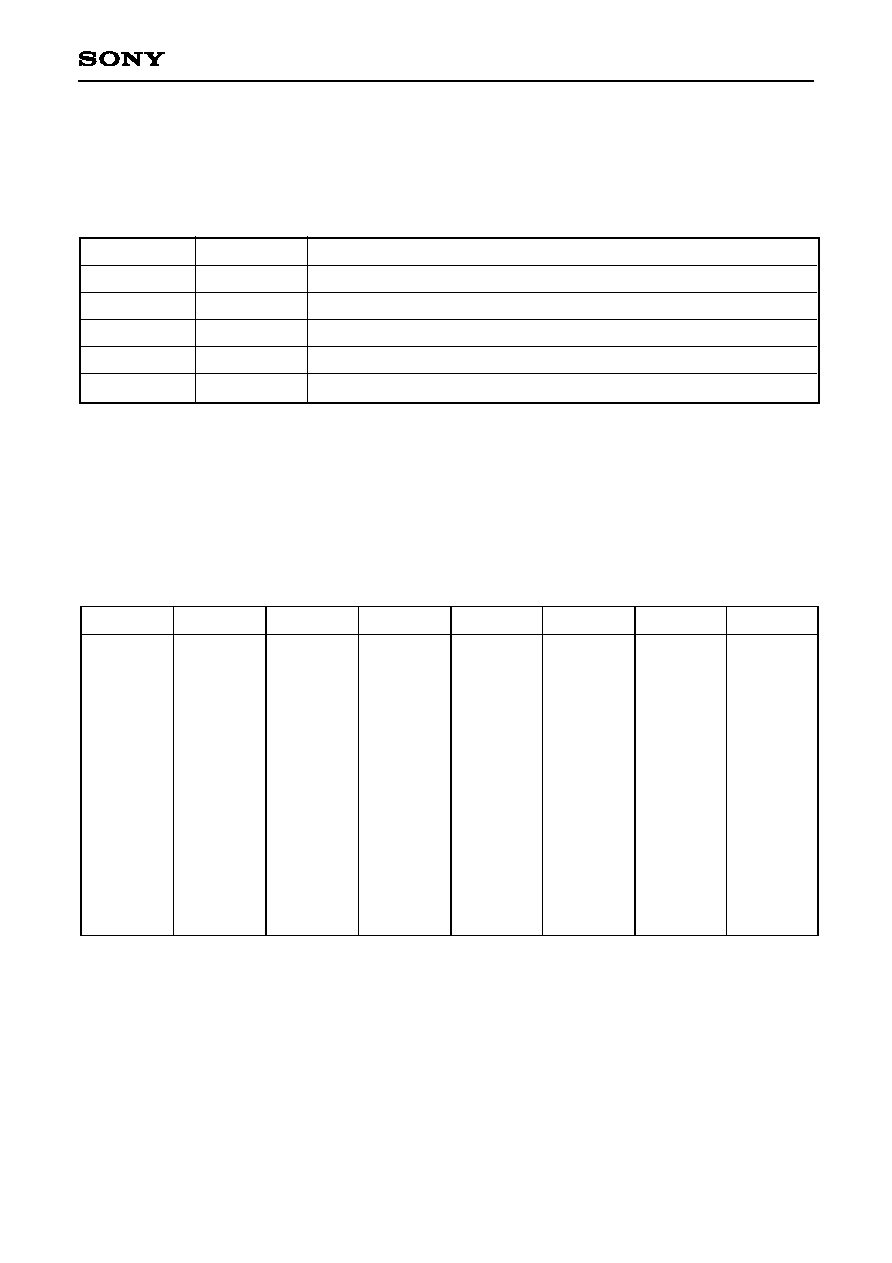

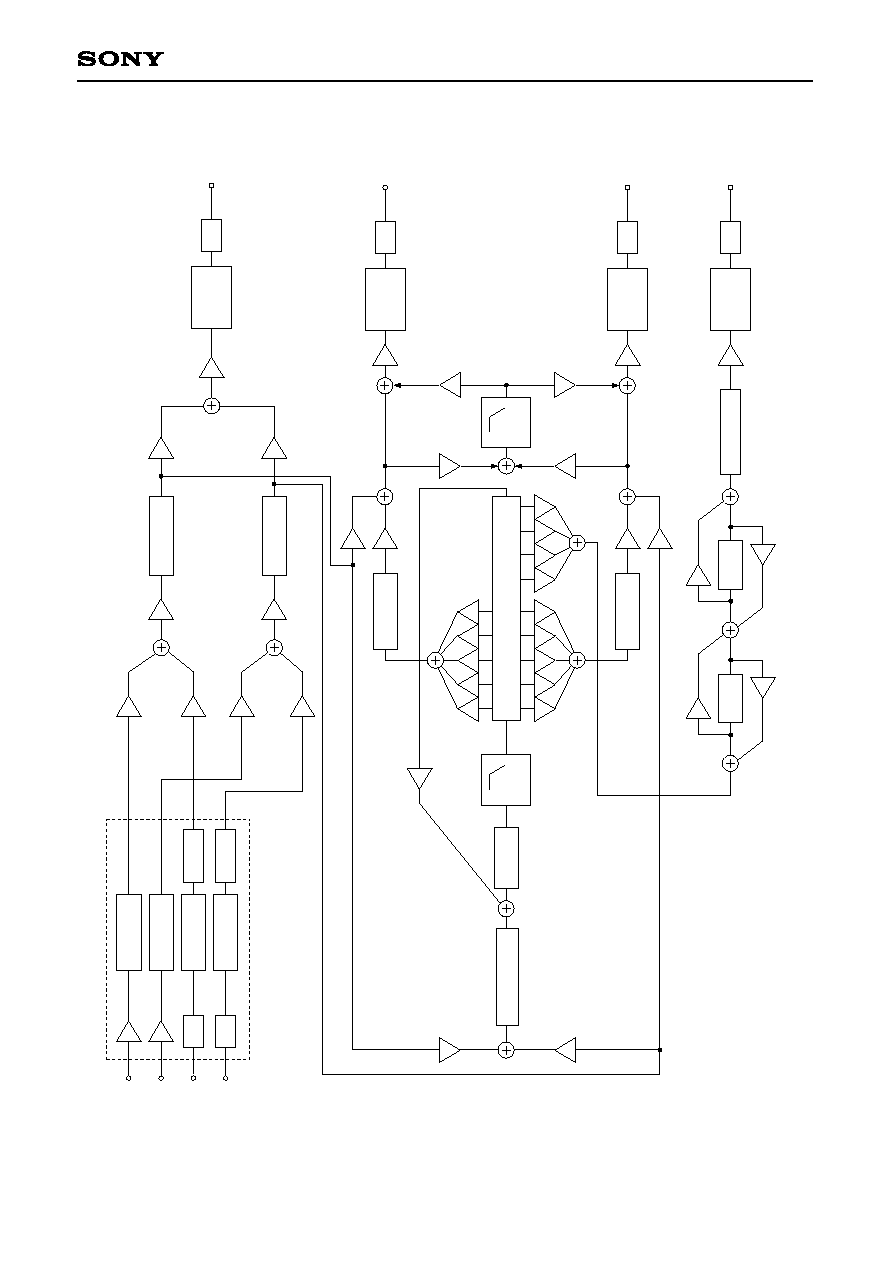

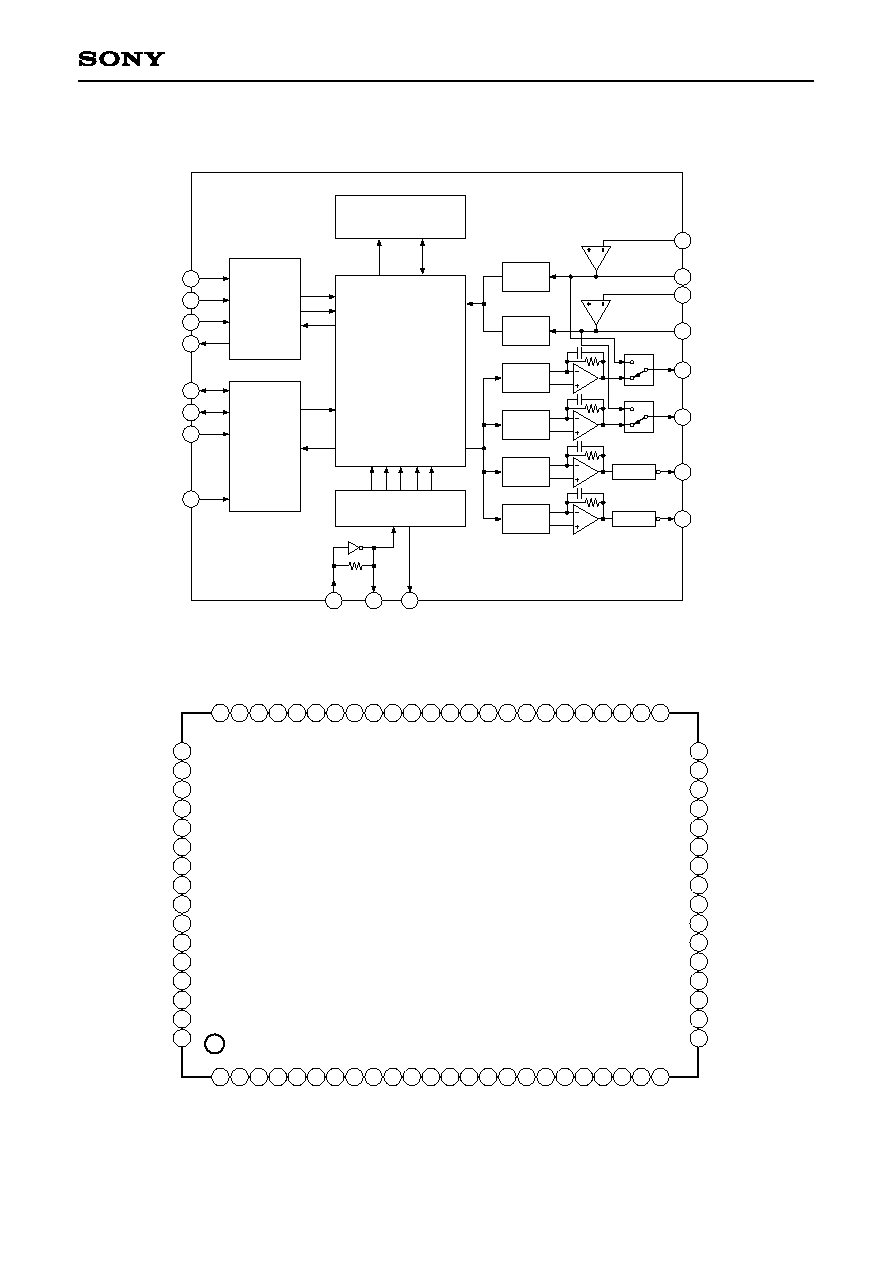

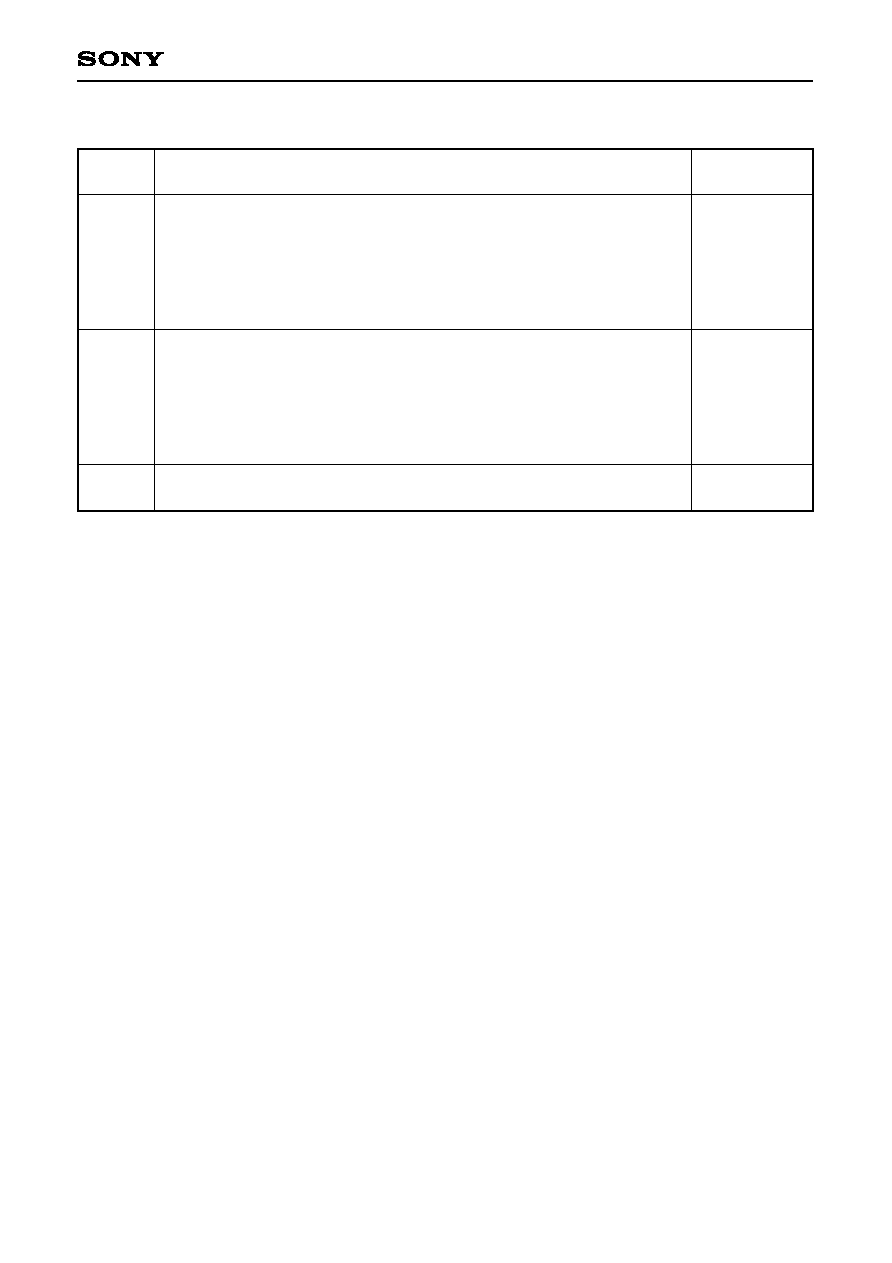

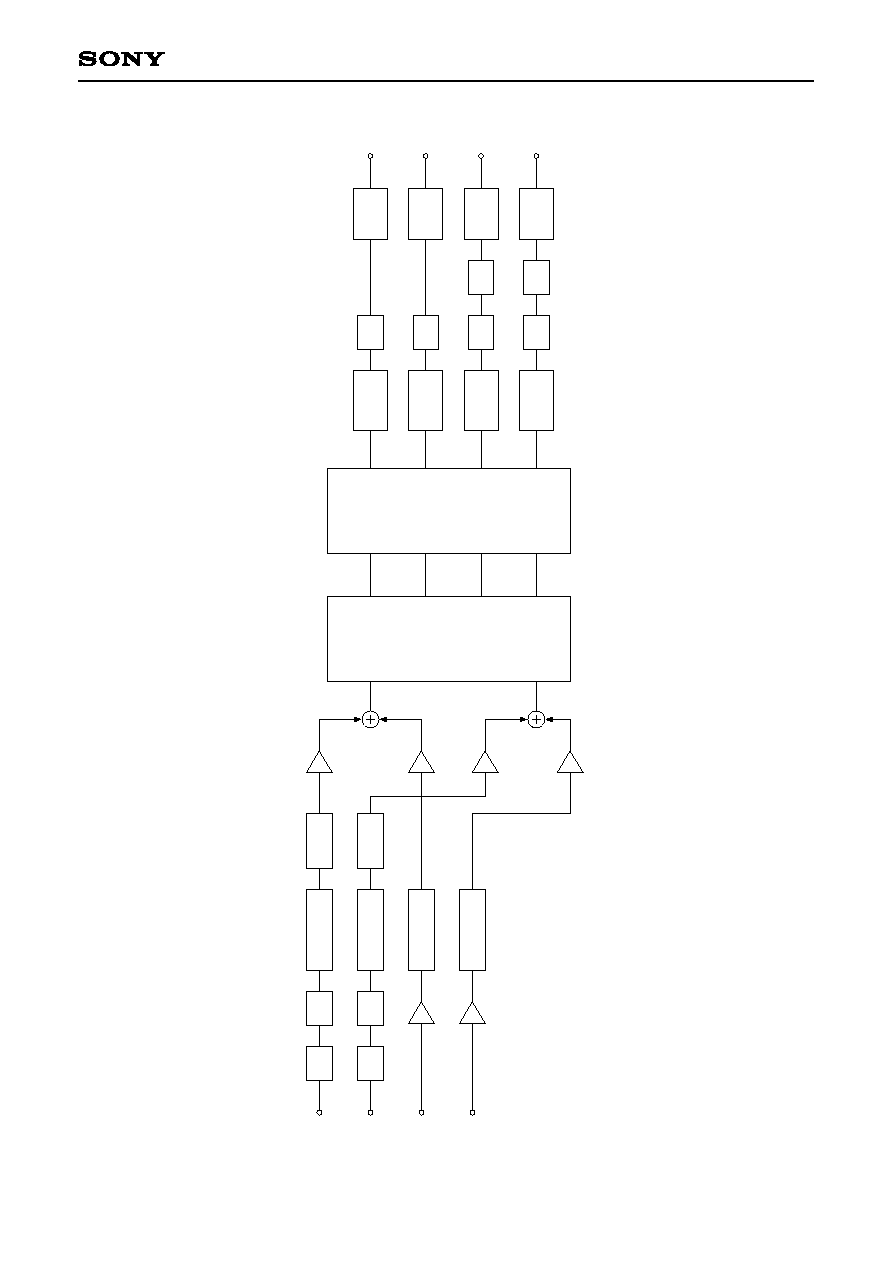

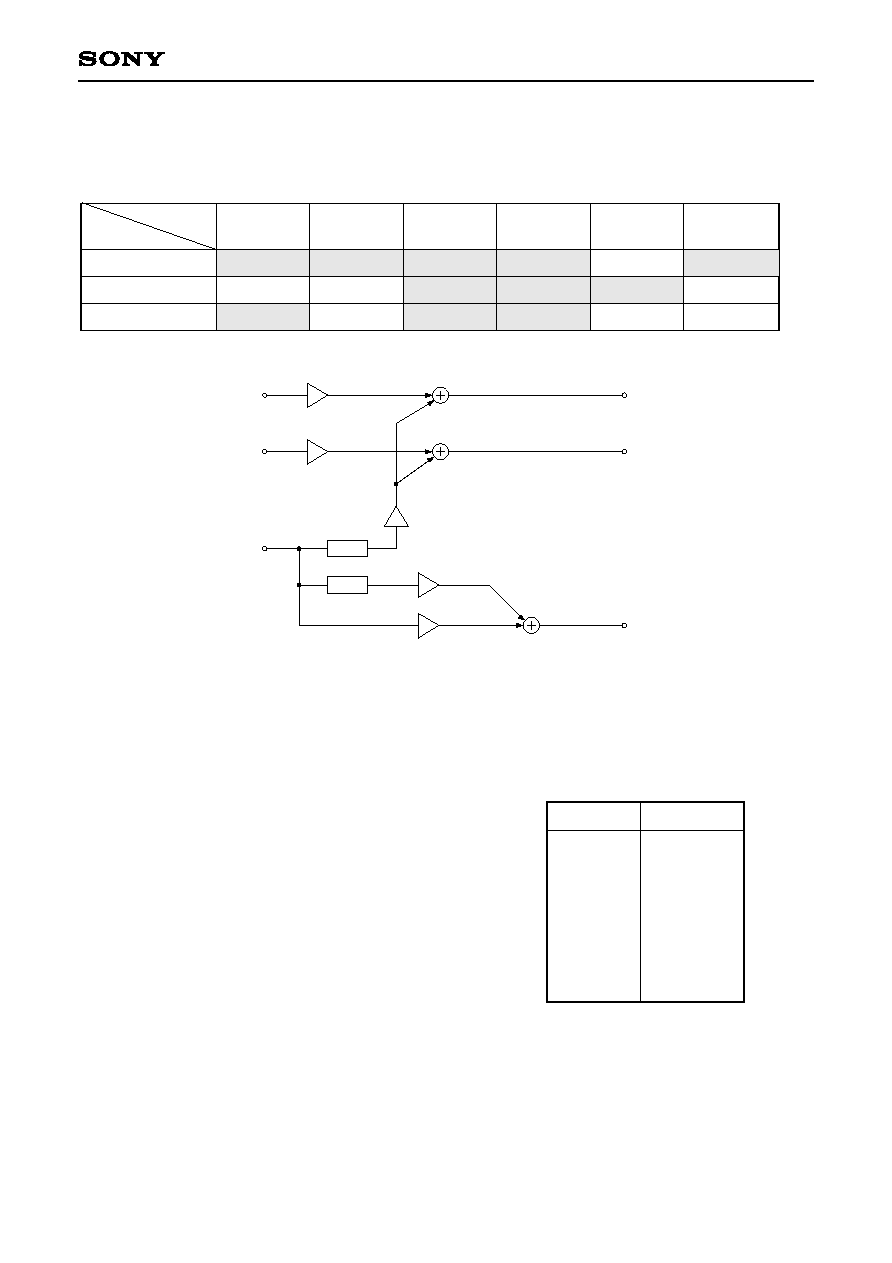

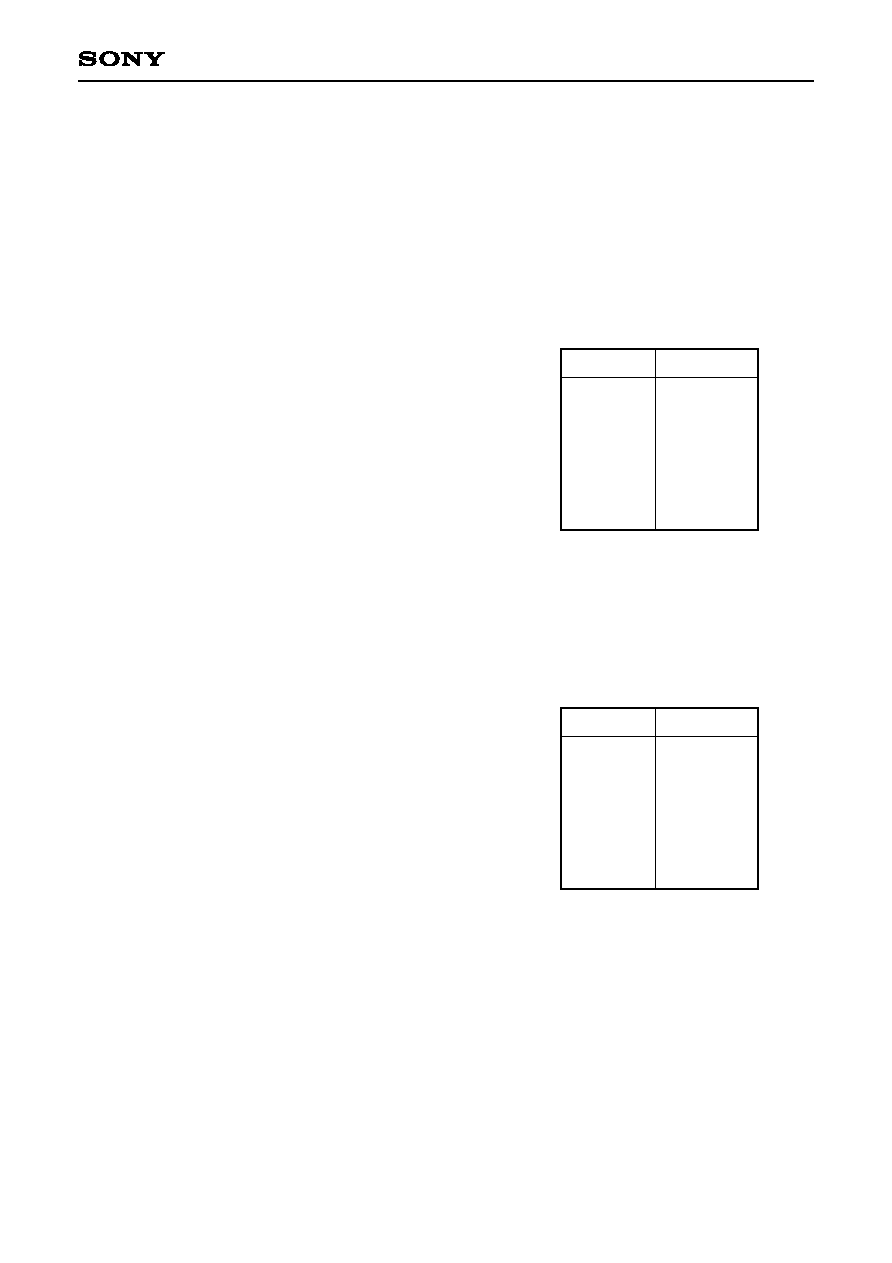

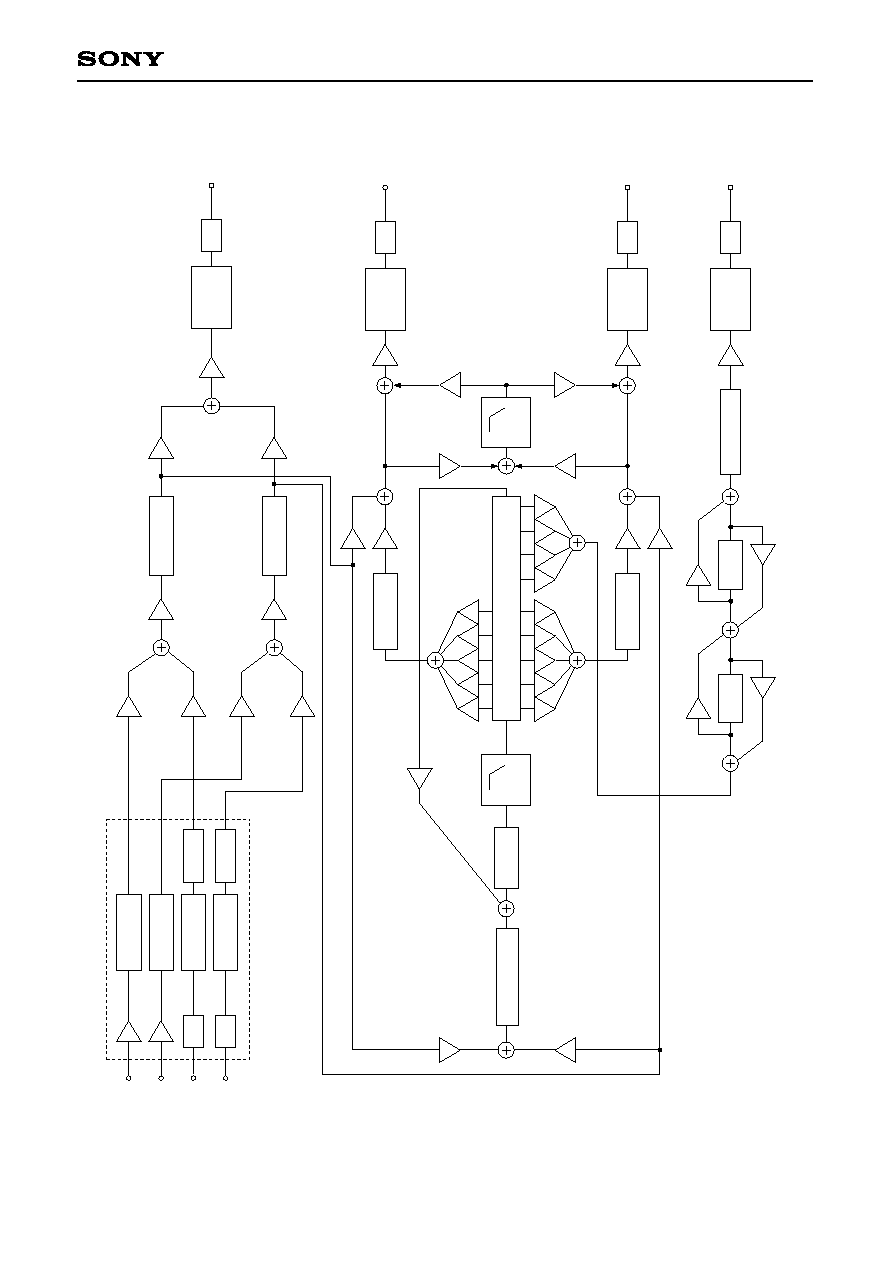

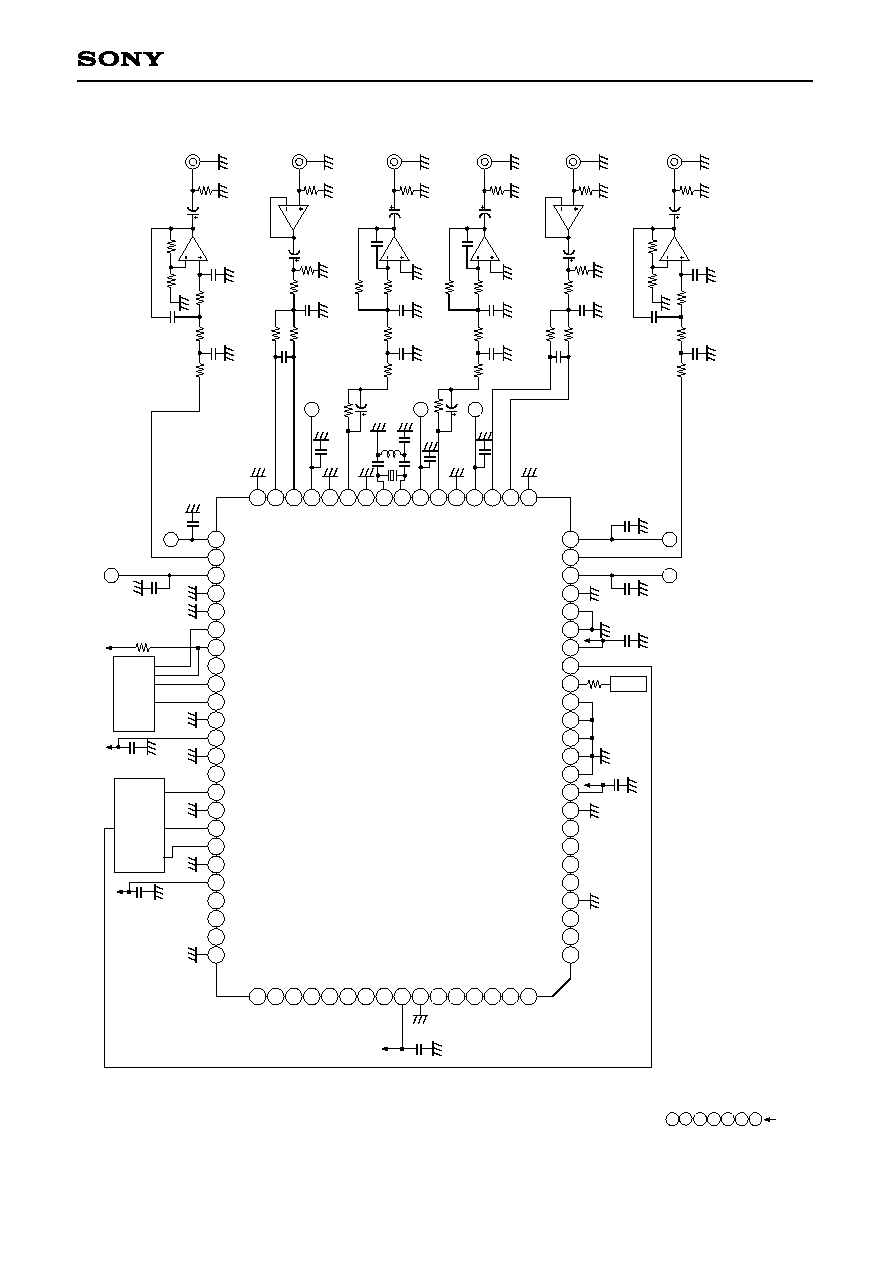

Block Diagram

XSOUT

XCOUT

ROUT

LOUT

LO2

RIN

LO1

LIN

17

23

30

35

32

42

57

58

DAC1

DAC2

DAC3

DAC4

Trim Vol

Trim Vol

ADC2

ADC1

Analog SW

Analog SW

DSP

24K bit DELAY RAM

CLOCK GENERATOR

/TIMING CIRCUIT

MICRO-

COMPUTER

I/F

SERIAL

DATA

I/F

26

27

39

38

55

60

46

47

49

50

33

X

T

L

I

X

T

L

O

B

F

O

T

XMST

SI

BCK

REDY

XLAT

SCK

RVDT

LRCK

(Phase Inverted Output)

(Phase Inverted Output)

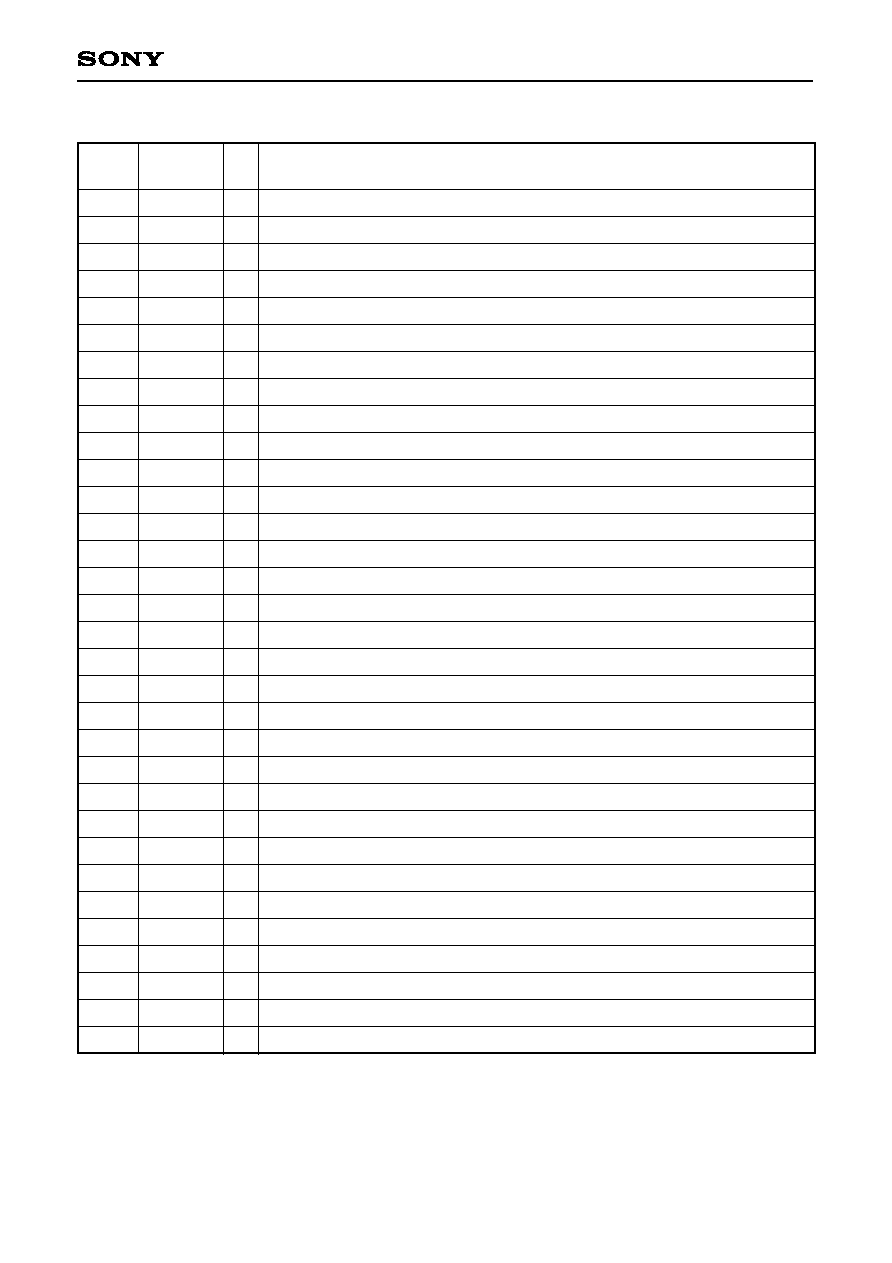

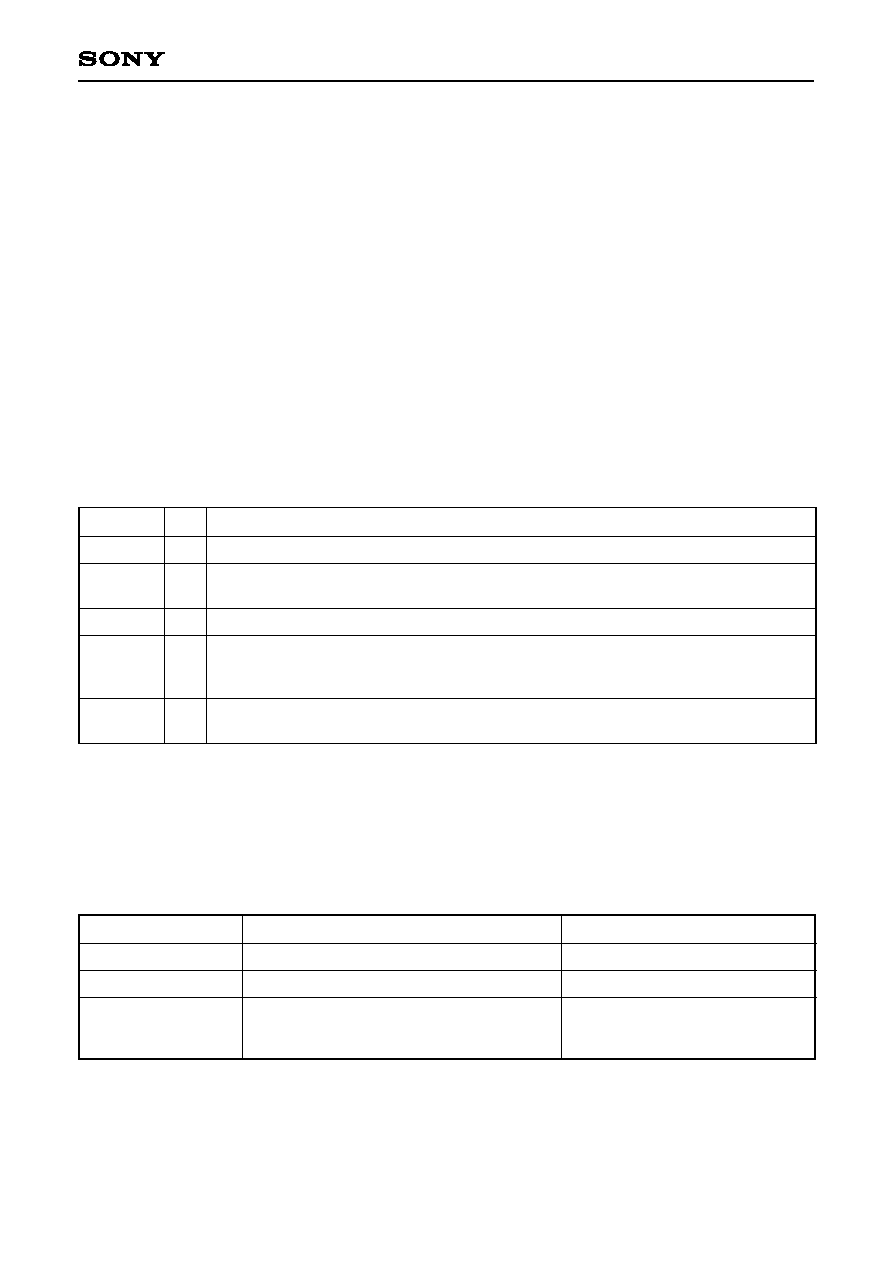

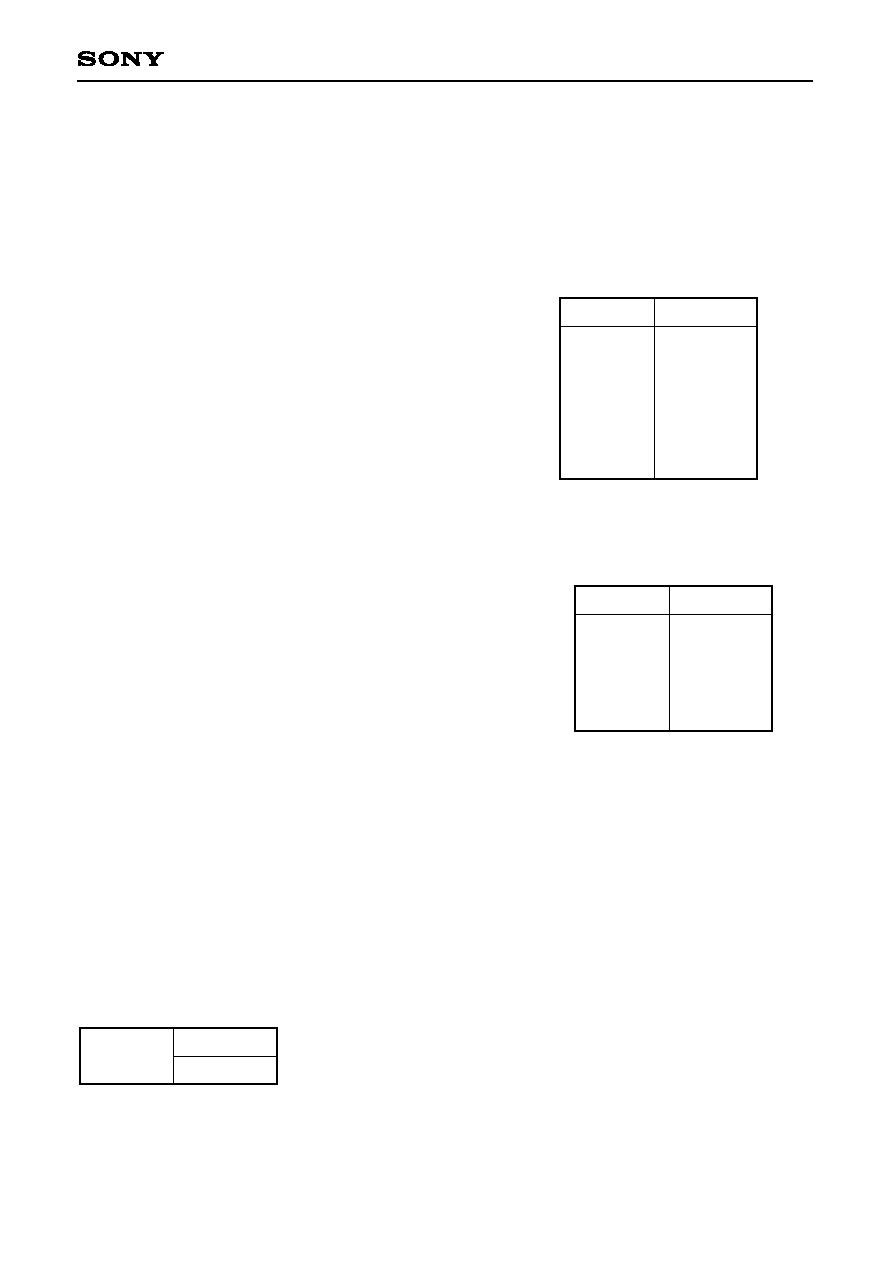

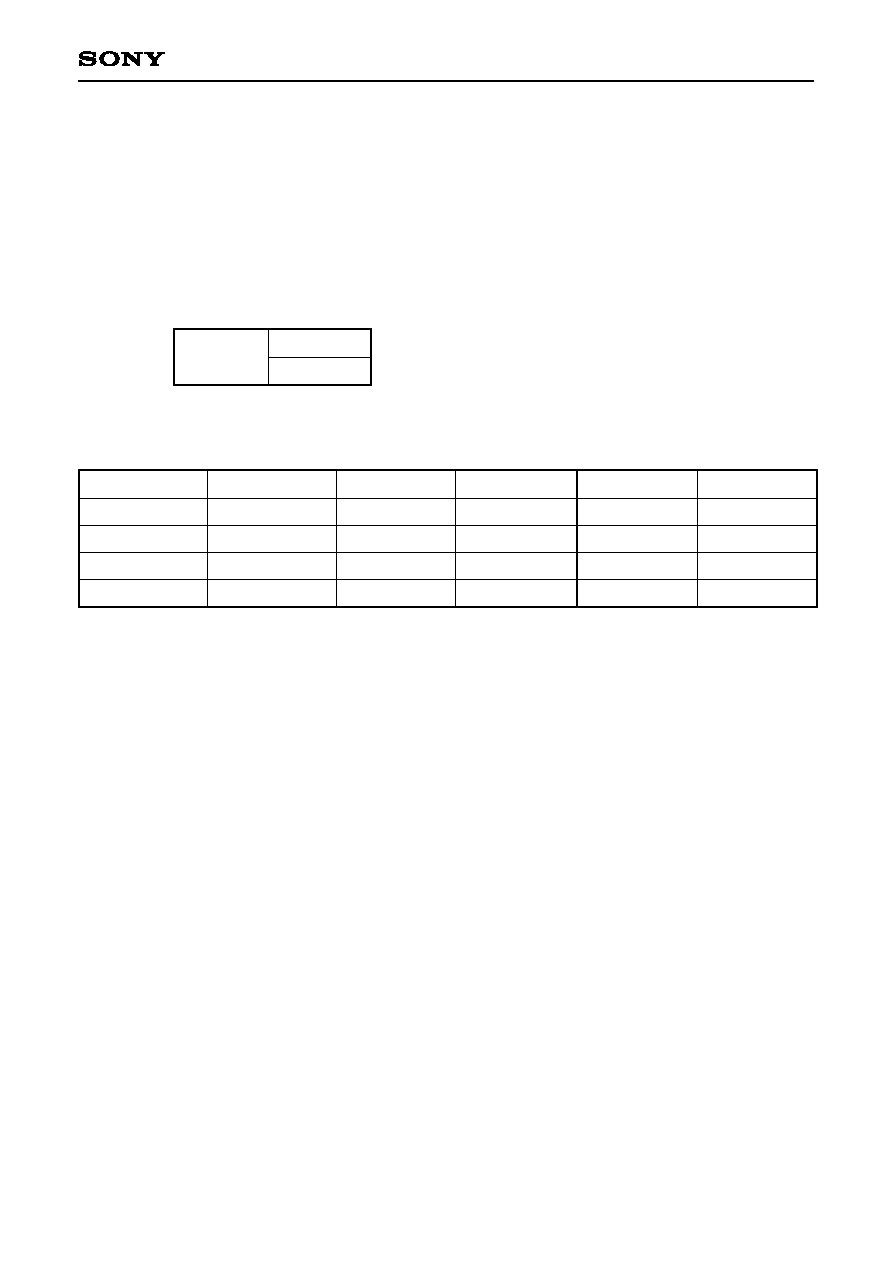

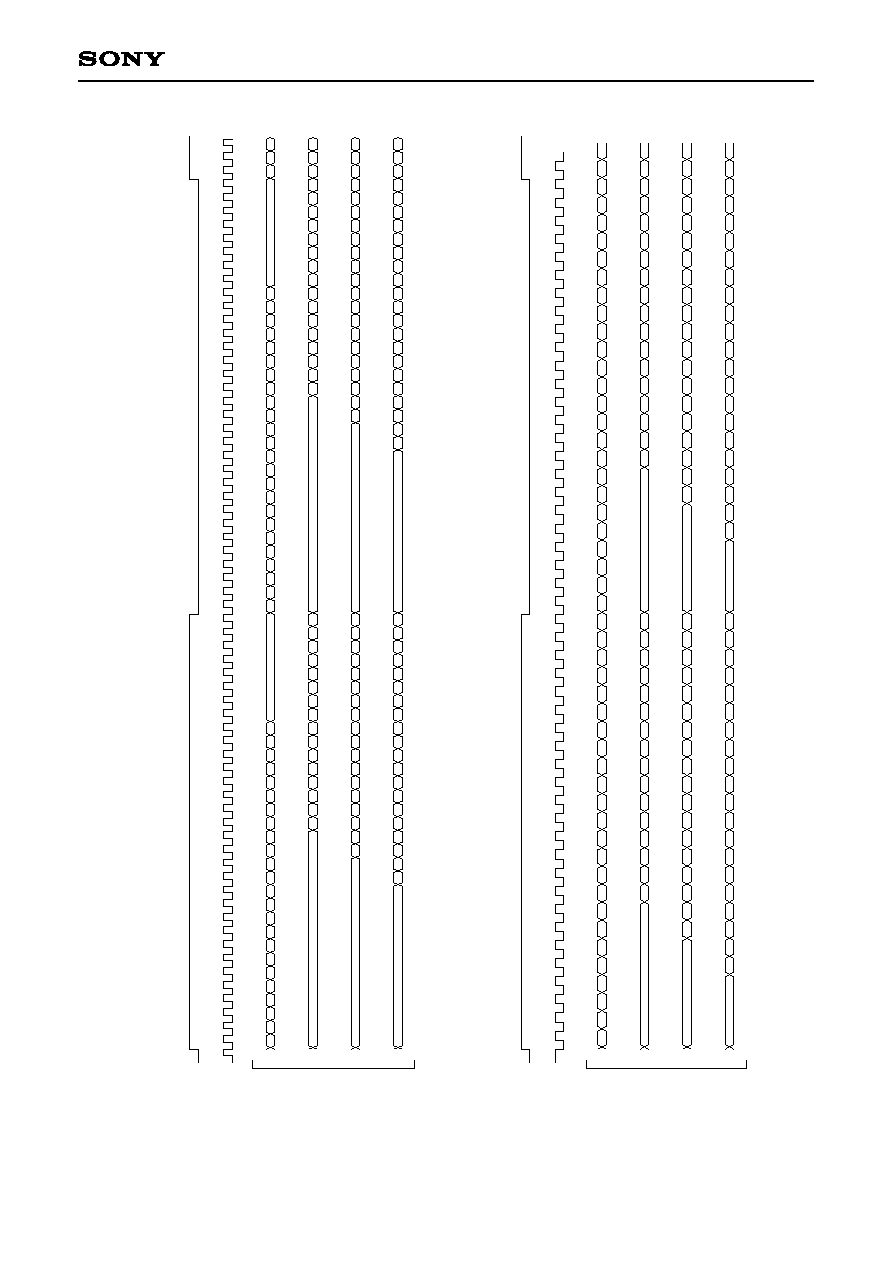

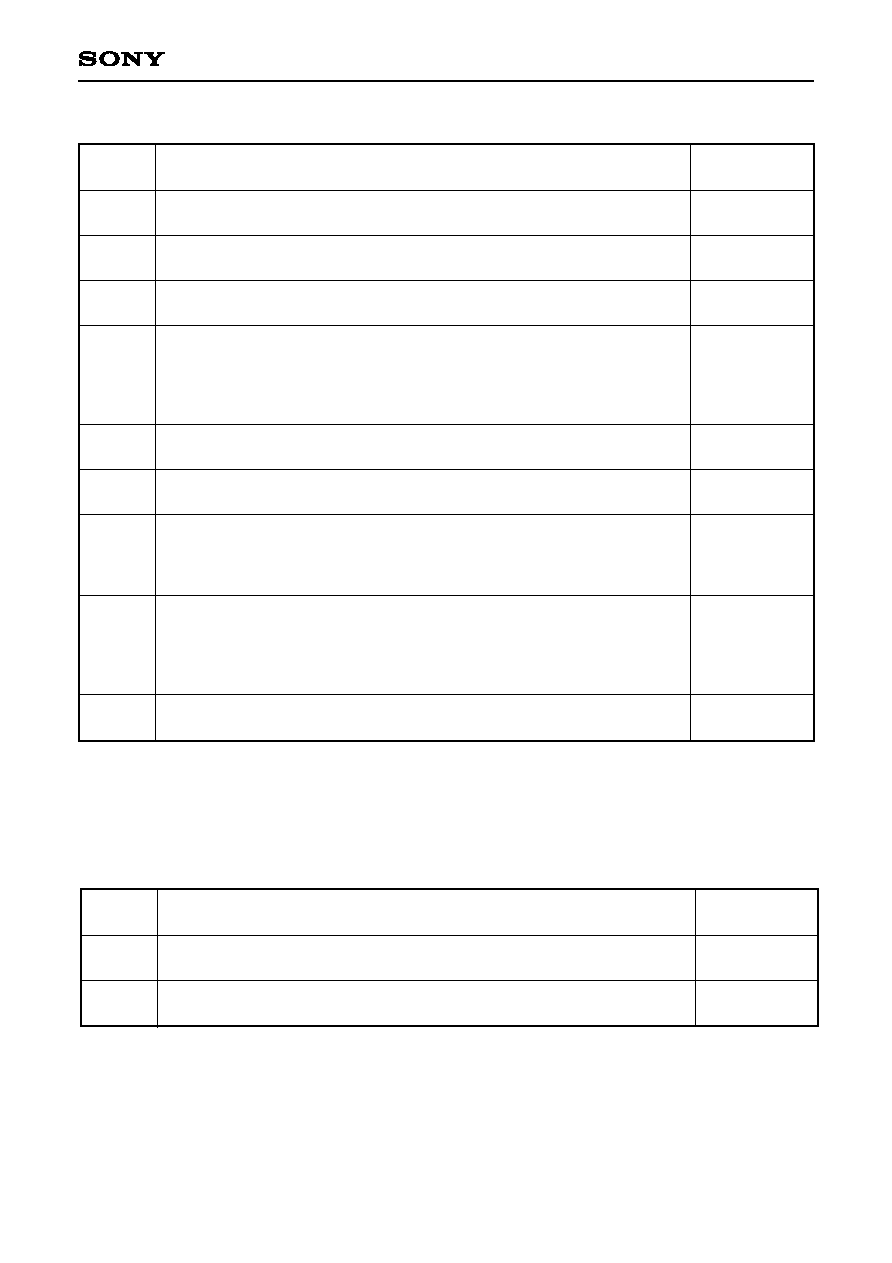

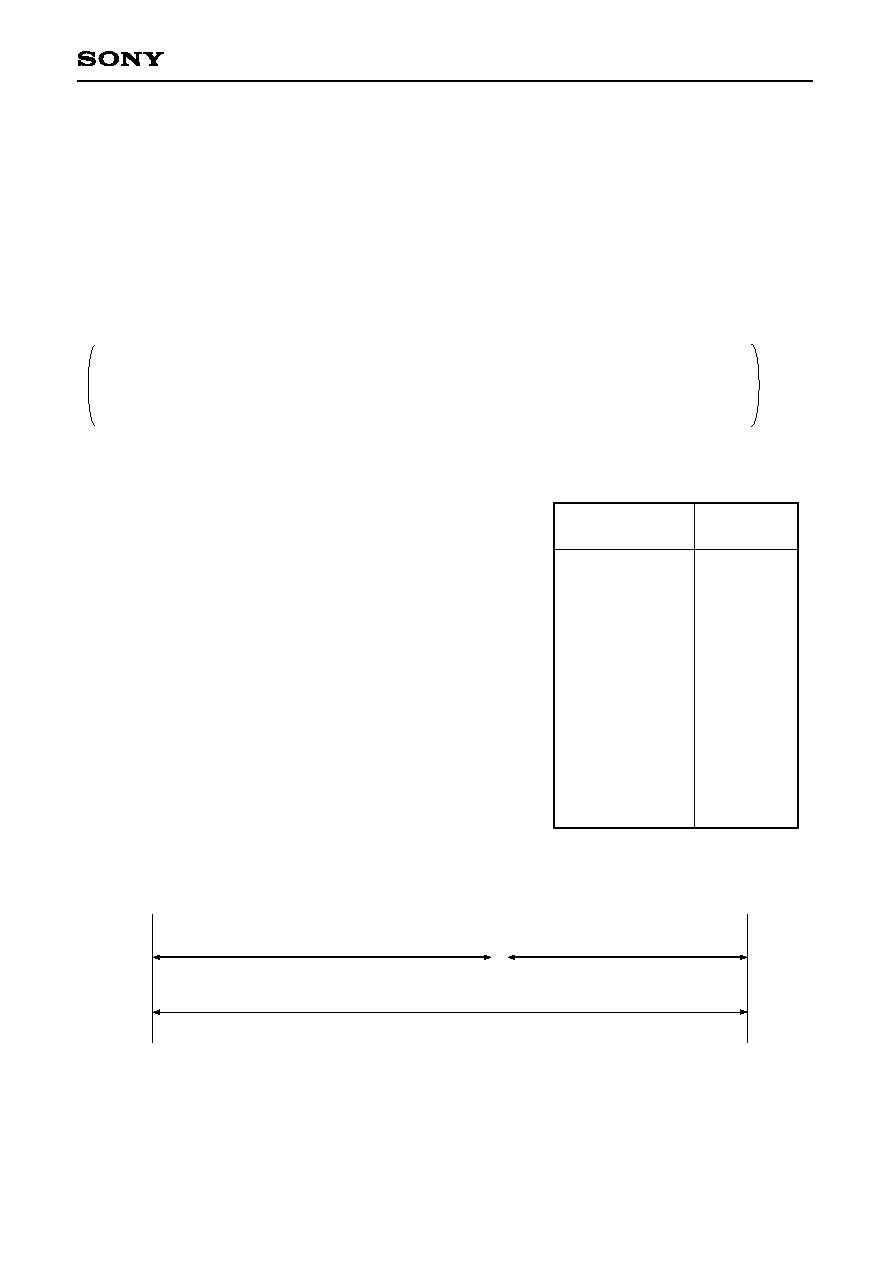

Pin Configuration

T

.

P

T

.

P

T

.

P

T

.

P

V

S

S

0

T

.

P

T

.

P

T

.

P

T

S

T

0

V

D

D

0

V

S

S

1

T

S

T

1

T

S

T

2

T

S

T

3

T

S

T

4

X

R

S

T

B

F

O

T

C

S

L

1

C

S

L

2

V

S

S

2

A

V

S

3

A

V

D

3

L

O

U

T

A

V

D

1

V

S

S

6

T

.

P

T

.

P

T

.

P

B

C

K

T

.

P

S

I

T

.

P

V

S

S

4

V

D

D

1

X

S

2

4

R

V

D

T

T

.

P

R

E

D

Y

S

C

K

V

S

S

3

A

V

S

4

A

V

D

4

R

O

U

T

A

V

D

2

AVS1

LO1

LIN

AVD5

AVS5

XCOUT

AVDX

XTLO

XTLI

AVSX

XSOUT

AVS6

AVD6

RIN

LO2

AVS2

X

L

A

T

V

S

S

5

L

R

C

K

X

M

S

T

1

4

5

6

7

8

9 10

2

3

11 12 13 14 15 16 17 18 19 20 21 22 23 24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

63

64

62

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

T.P

T.P

T.P

T.P

T.P

T.P

V

SS

7

V

DD

2

T.P

T.P

T.P

T.P

T.P

T.P

T.P

T.P

≠ 3 ≠

CXD2719Q

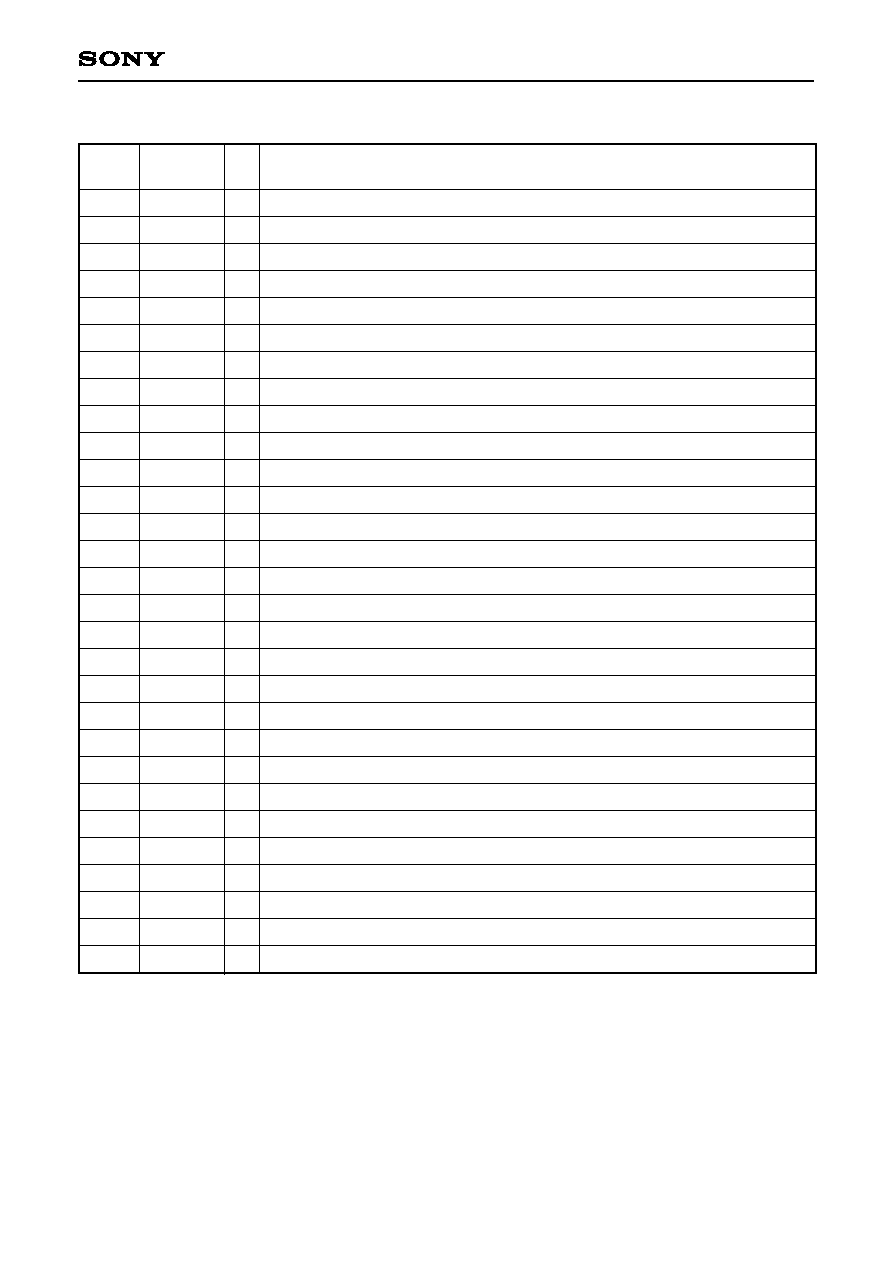

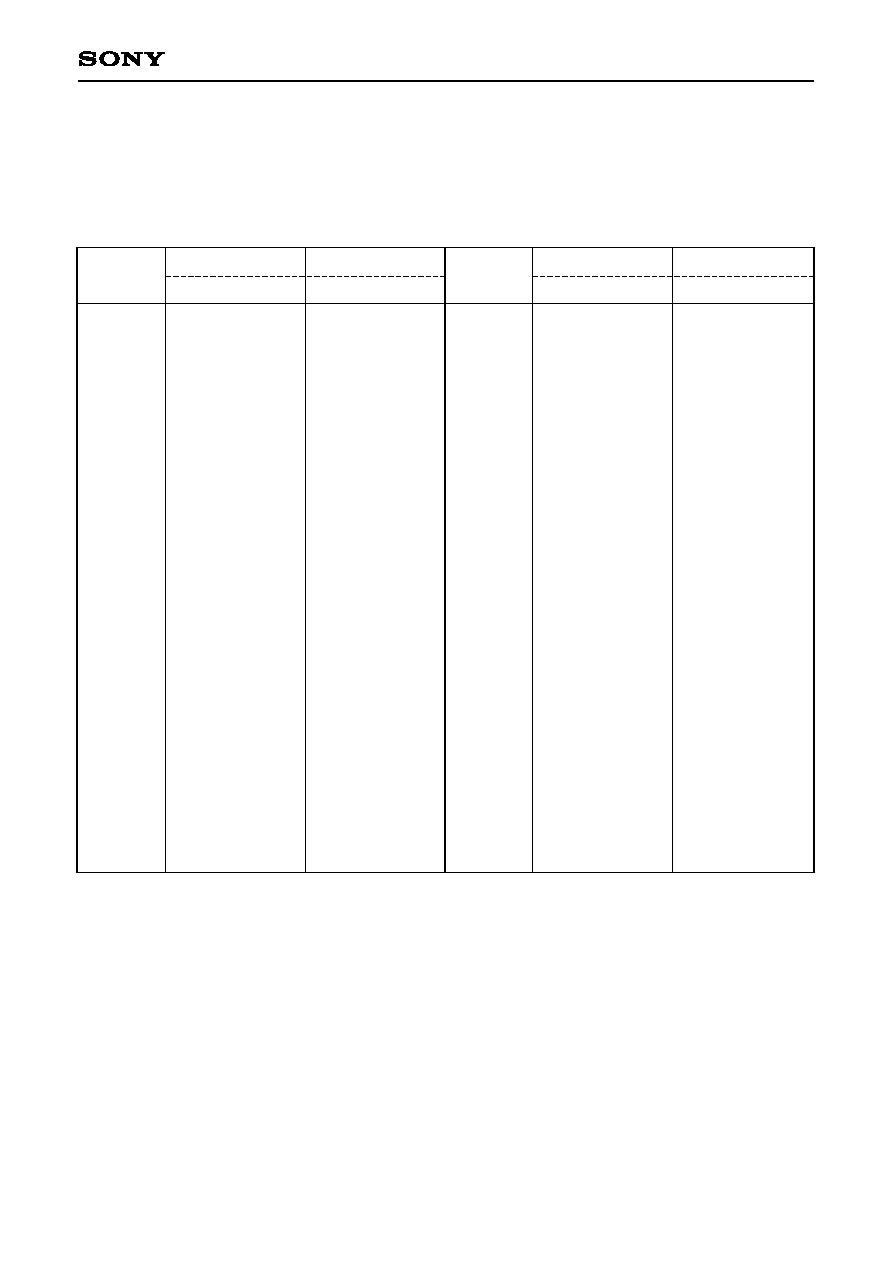

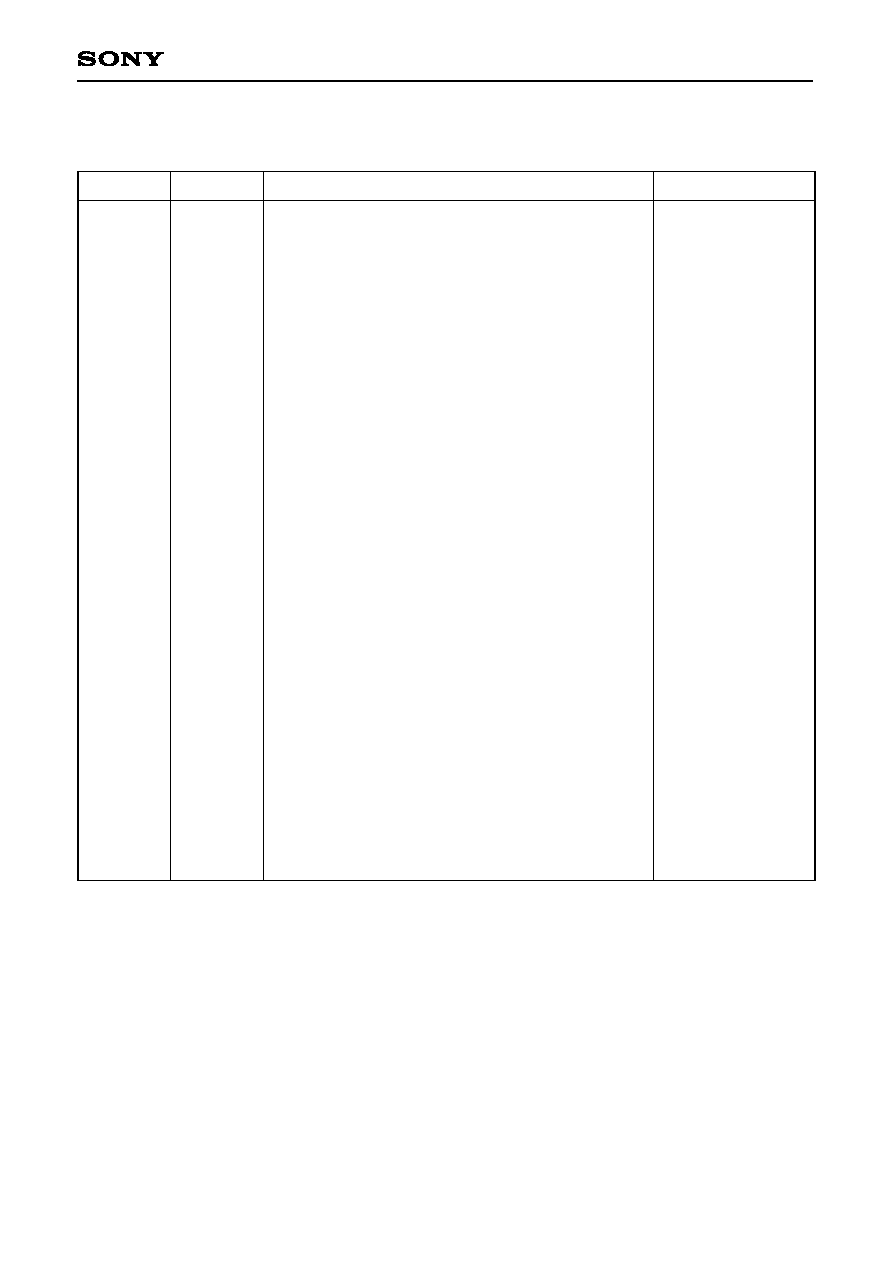

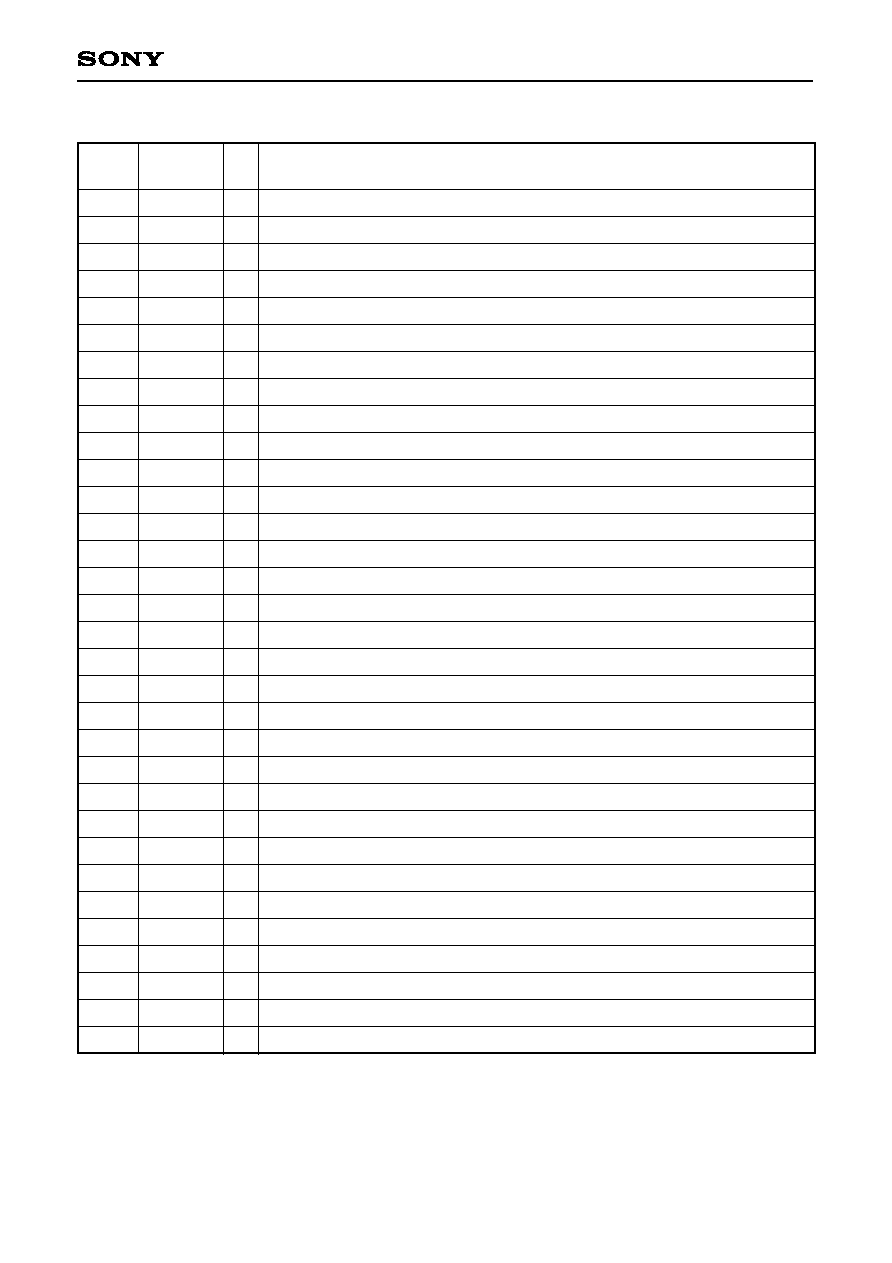

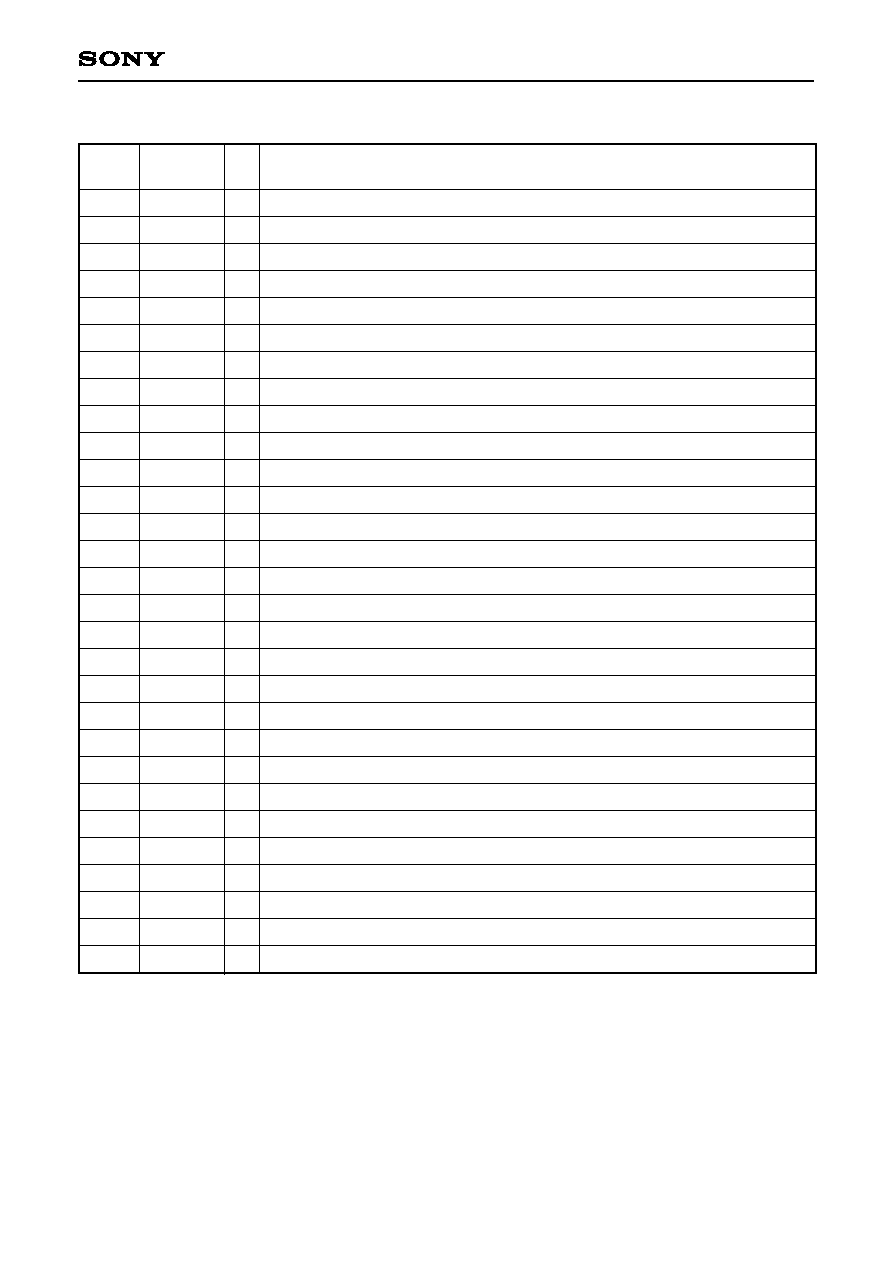

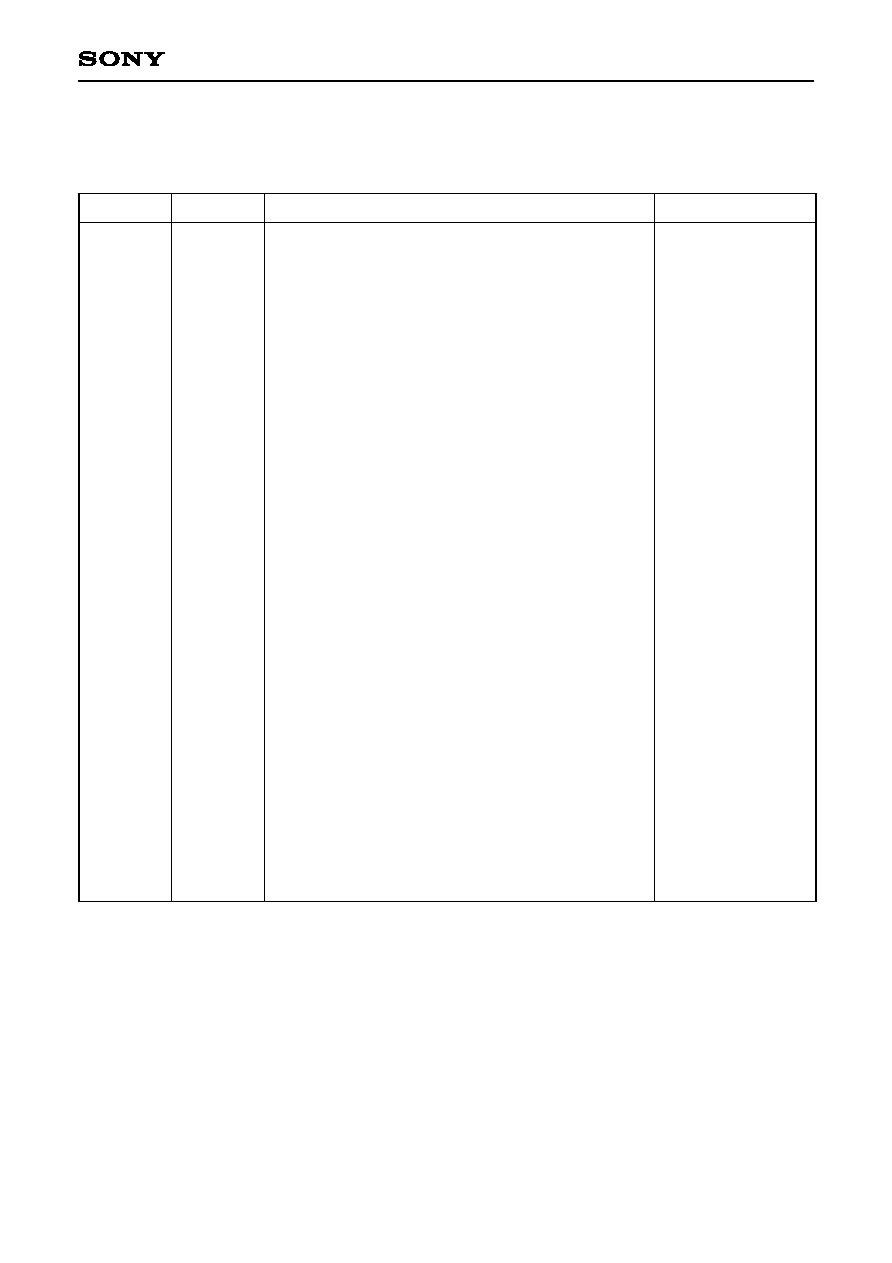

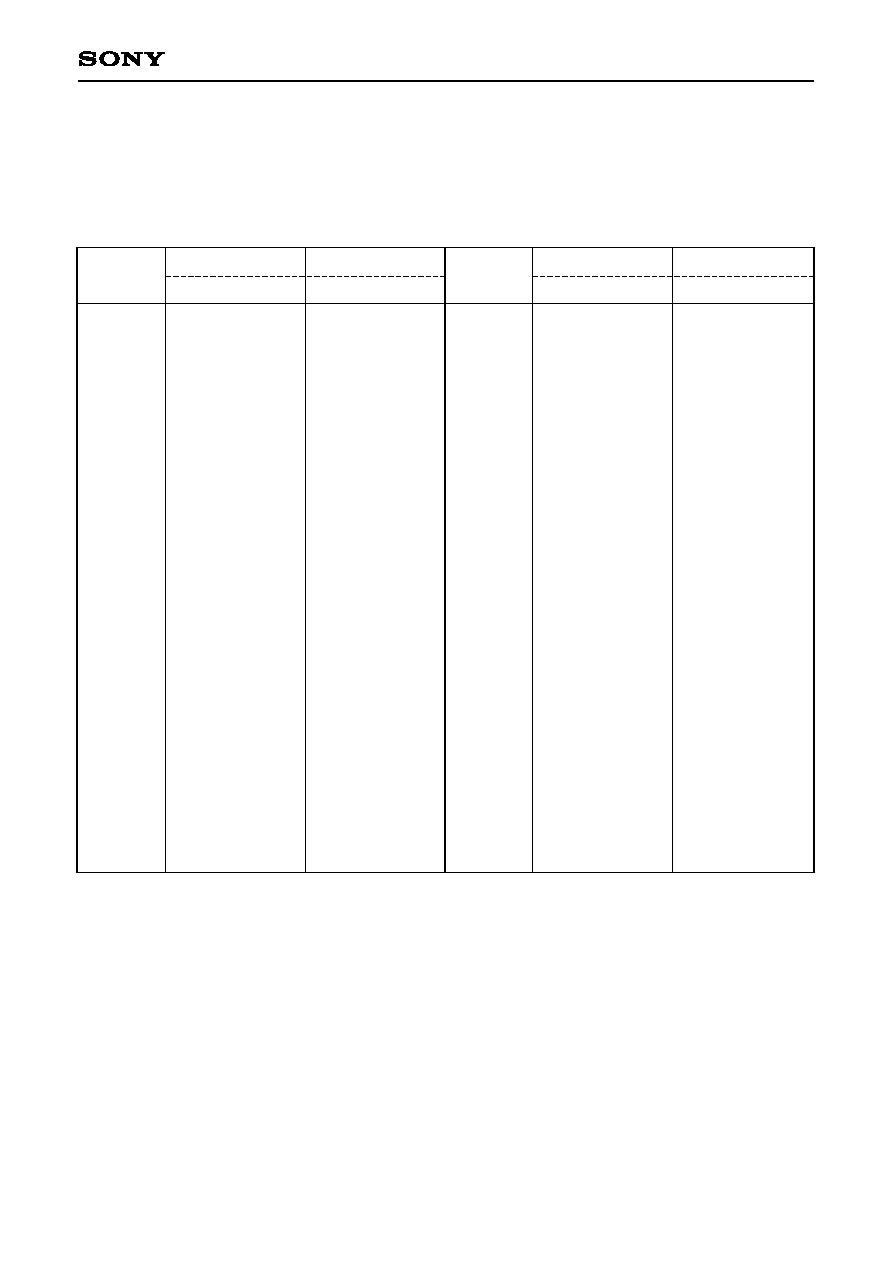

Pin Description

Notations in parentheses indicate the fixed pin connection status.

1 to 3

4

5 to 8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

T.P

V

SS

0

T.P

TST0

V

DD

0

V

SS

1

TST1

TST2

TST3

TST4

XRST

BFOT

CSL1

CSL2

V

SS

2

AVS3

AVD3

LOUT

AVD1

AVS1

LO1

LIN

AVD5

AVS5

XCOUT

AVDX

XTLO

XTLI

AVSX

XSOUT

AVS6

AVD6

O

--

O

I

--

--

I

I

I

I

I

O

I

I

--

--

--

O

--

--

O

I

--

--

O

--

O

I

--

O

--

--

Test monitor. Normally outputs Low.

(OPEN)

Digital GND.

(V

SS

)

Test monitor. Normally outputs Low.

(OPEN)

Test. Normally fixed Low.

(V

SS

)

Digital power supply.

(V

DD

)

Digital GND.

(V

SS

)

Test. Normally fixed Low.

(V

SS

)

Test. Normally fixed Low.

(V

SS

)

Test. Normally fixed Low.

(V

SS

)

Test. Normally fixed Low.

(V

SS

)

System reset input. Reset when Low.

Clock, frequency-division output. [384/768/256/512fs]

Test. Normally fixed High.

(V

DD

)

Test. Normally fixed Low.

(V

SS

)

Digital GND.

(V

SS

)

L-ch DA converter GND.

(AV

SS

)

L-ch DA converter power supply.

(AV

DD

)

L-ch DA converter output.

L-ch AD converter power supply.

(AV

DD

)

L-ch AD converter GND.

(AV

SS

)

L-ch AD converter LPF operational amplifier inverted output.

L-ch AD converter analog input.

C-ch DA converter power supply.

(AV

DD

)

C-ch DA converter GND.

(AV

SS

)

C-ch DA converter output.

Analog power supply for master clock.

(AV

DD

)

Crystal oscillator circuit output.

Crystal oscillator circuit input.

Analog GND for master clock.

(AV

SS

)

S-ch DA converter output.

S-ch DA converter GND.

(AV

SS

)

S-ch DA converter power supply.

(AV

DD

)

Pin No.

Symbol

I/O

Description

(OPEN): Open, (V

DD

): +5V digital power supply, (AV

DD

): +5V analog power supply,

(V

SS

): Digital GND, (AV

SS

): Analog GND

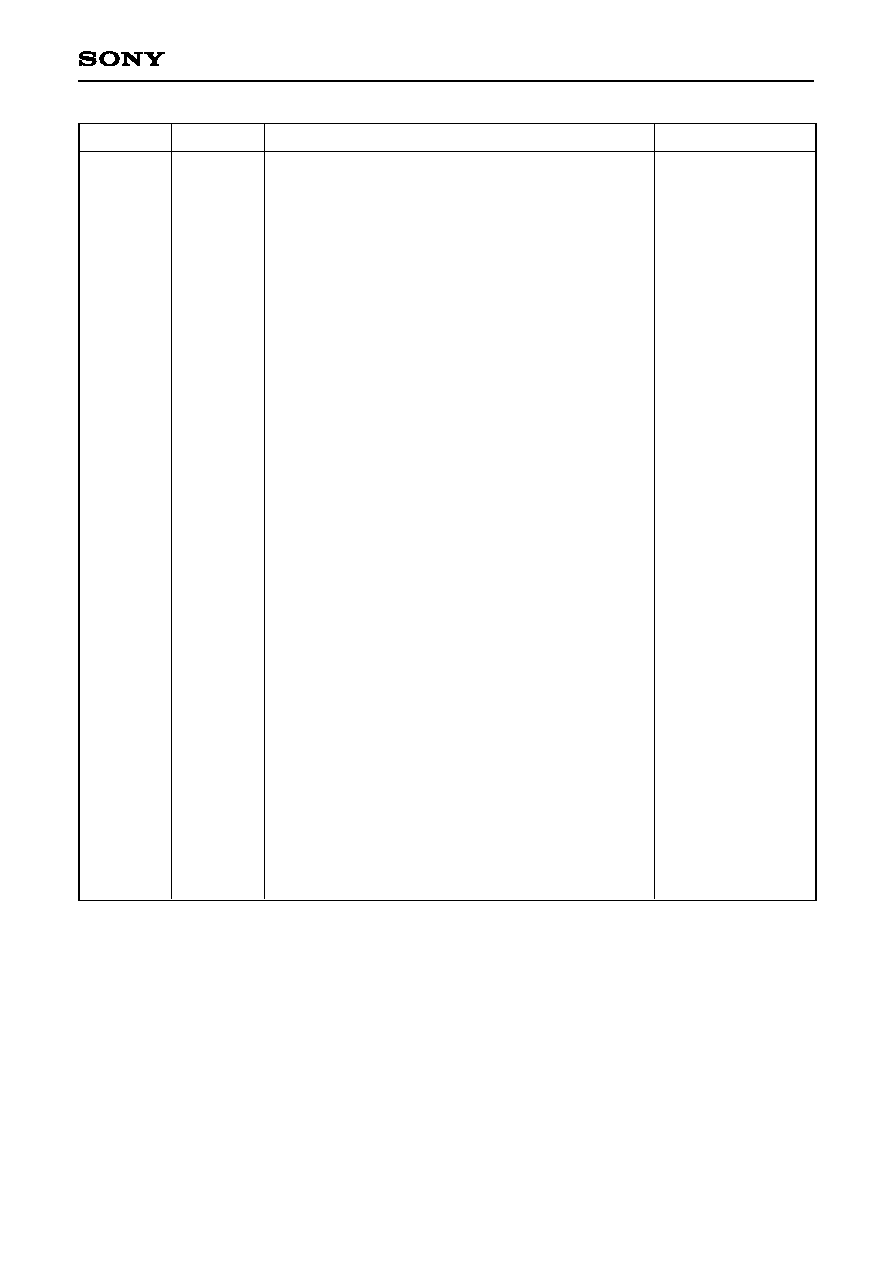

≠ 4 ≠

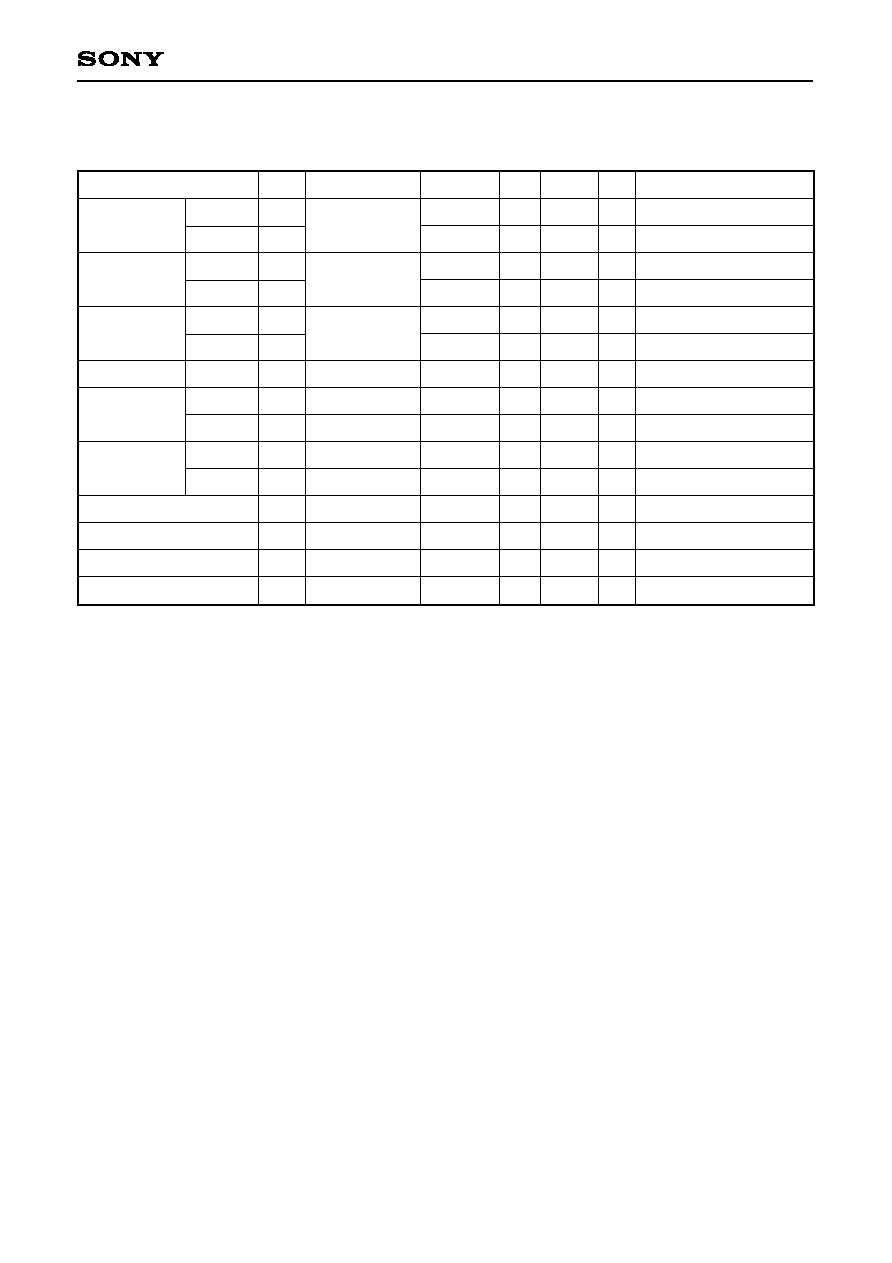

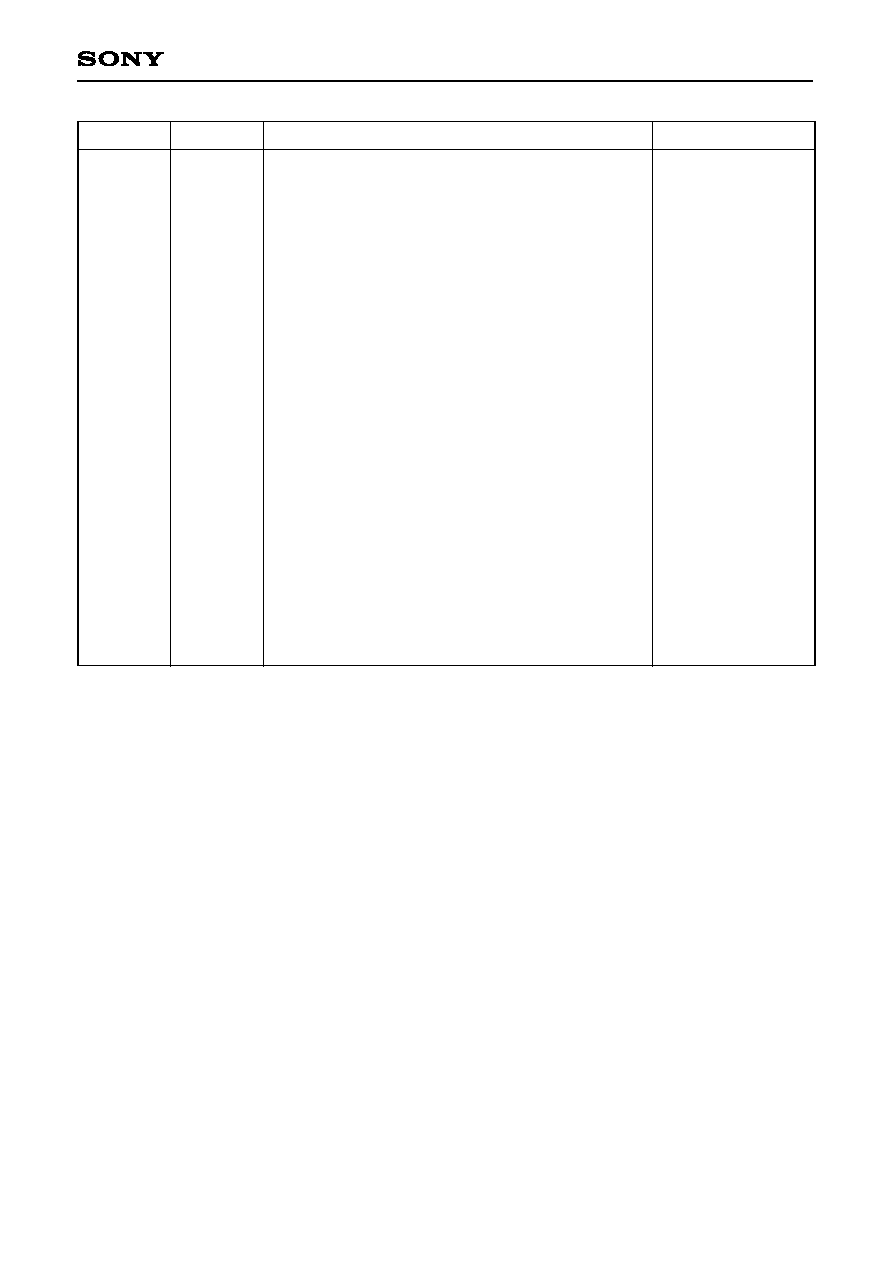

CXD2719Q

Notations in parentheses indicate the fixed pin connection status.

(OPEN): Open, (V

DD

): +5V digital power supply, (AV

DD

): +5V analog power supply,

(V

SS

): Digital GND, (AV

SS

): Analog GND

There are three digital and seven analog power supplies, but the power-on sequence is not specified.

Pin No.

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61 to 63

64

65 to 72

73

74

75 to 80

Symbol

RIN

LO2

AVS2

AVD2

ROUT

AVD4

AVS4

V

SS

3

SCK

REDY

T.P

XLAT

RVDT

XS24

V

DD

1

V

SS

4

T.P

SI

T.P

BCK

LRCK

V

SS

5

XMST

T.P

V

SS

6

T.P

V

DD

2

V

SS

7

T.P

I/O

I

O

--

--

O

--

--

--

I

O

O

I

I

I

--

--

O

I

I

I/O

I/O

--

I

O

--

O

--

--

O

Description

R-ch AD converter analog input.

R-ch AD converter LPF operational amplifier inverted output.

R-ch AD converter GND.

(AV

SS

)

R-ch AD converter power supply.

(AV

DD

)

R-ch DA converter output.

R-ch DA converter power supply. (AV

DD

)

R-ch DA converter GND.

(AV

SS

)

Digital GND.

(V

SS

)

Shift clock input for microcomputer interface.

Transfer enabling signal output for microcomputer interface. Transfer prohibited when Low.

Test monitor. Normally outputs Hi-Z.

(OPEN)

Latch input for microcomputer interface.

Data input for microcomputer interface.

Serial data 24-/32-bit slot selection. 24-bit slot when Low. (valid for slave mode)

Digital power supply.

(V

DD

)

Digital GND.

(V

SS

)

Test monitor. Normally outputs Low.

(OPEN)

1-sampling 2-channel serial data input.

Test input. Normally inputs Low.

(V

SS

)

Serial bit transfer clock for serial I/O data SI and SO.

Sampling frequency clock for serial I/O data SI and SO.

Digital GND.

(V

SS

)

BCK, LRCK master/slave mode switching input. Master mode when Low.

Test monitor. Normally outputs Low.

(OPEN)

Digital GND.

(V

SS

)

Test monitor. Normally outputs Low.

(OPEN)

Digital power supply.

(V

DD

)

Digital GND.

(V

SS

)

Test monitor. Normally outputs Low.

(OPEN)

≠ 5 ≠

CXD2719Q

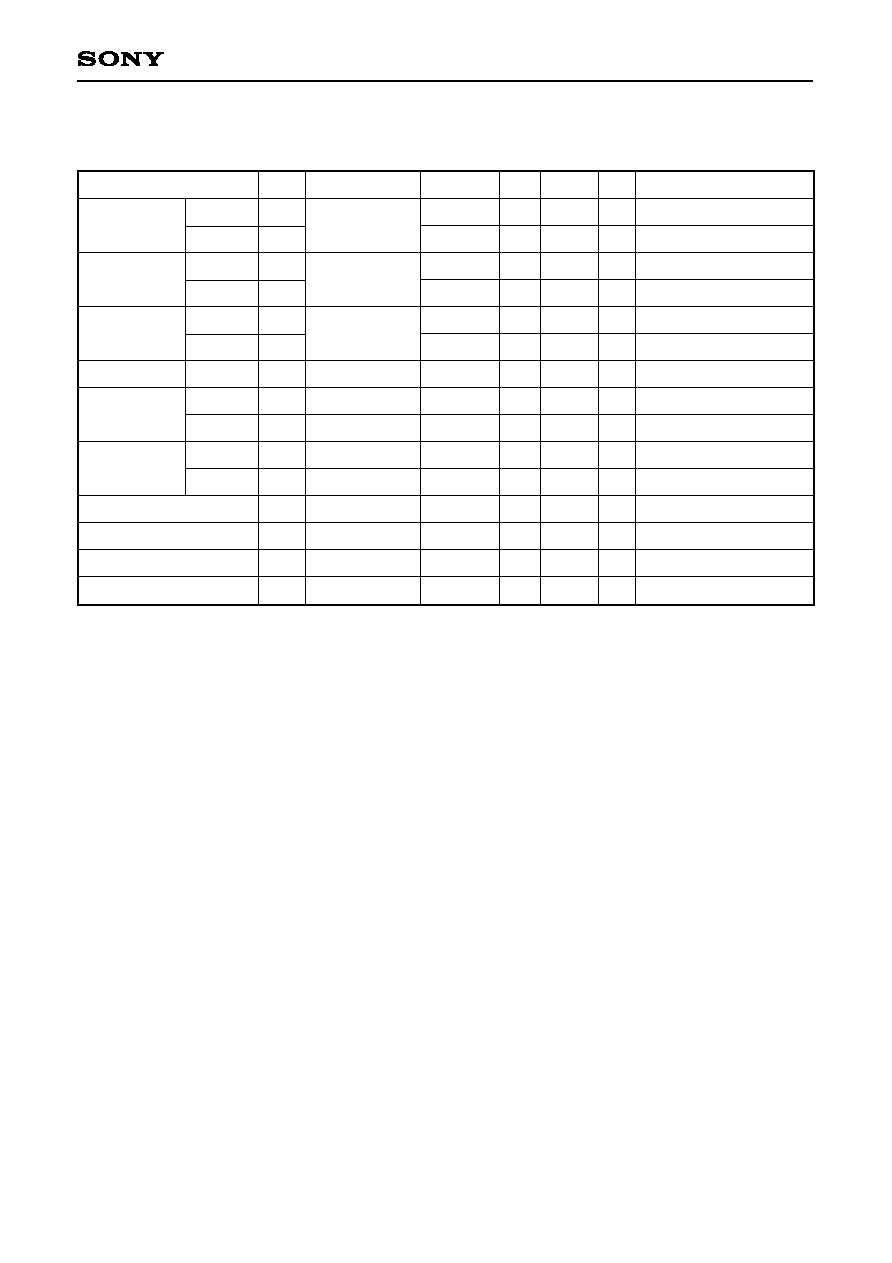

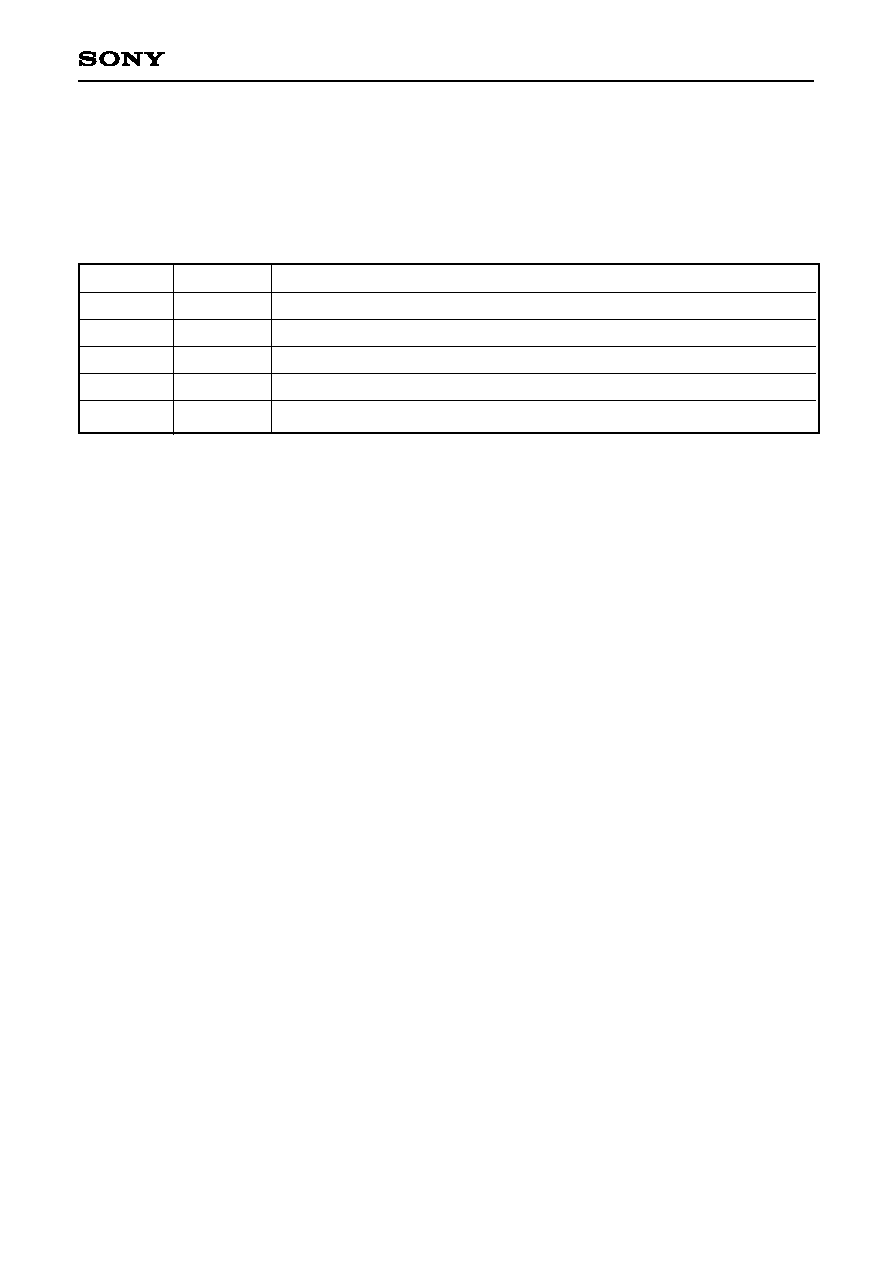

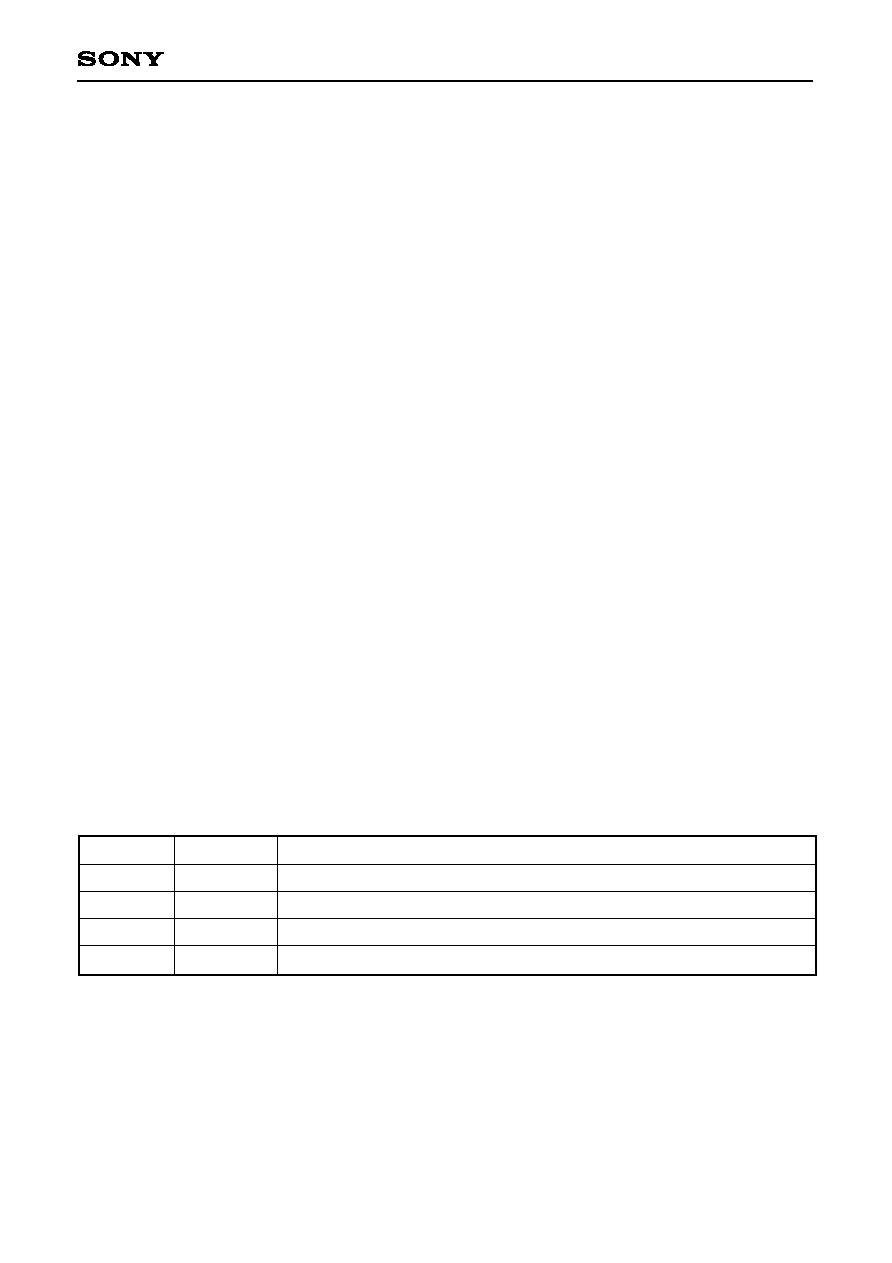

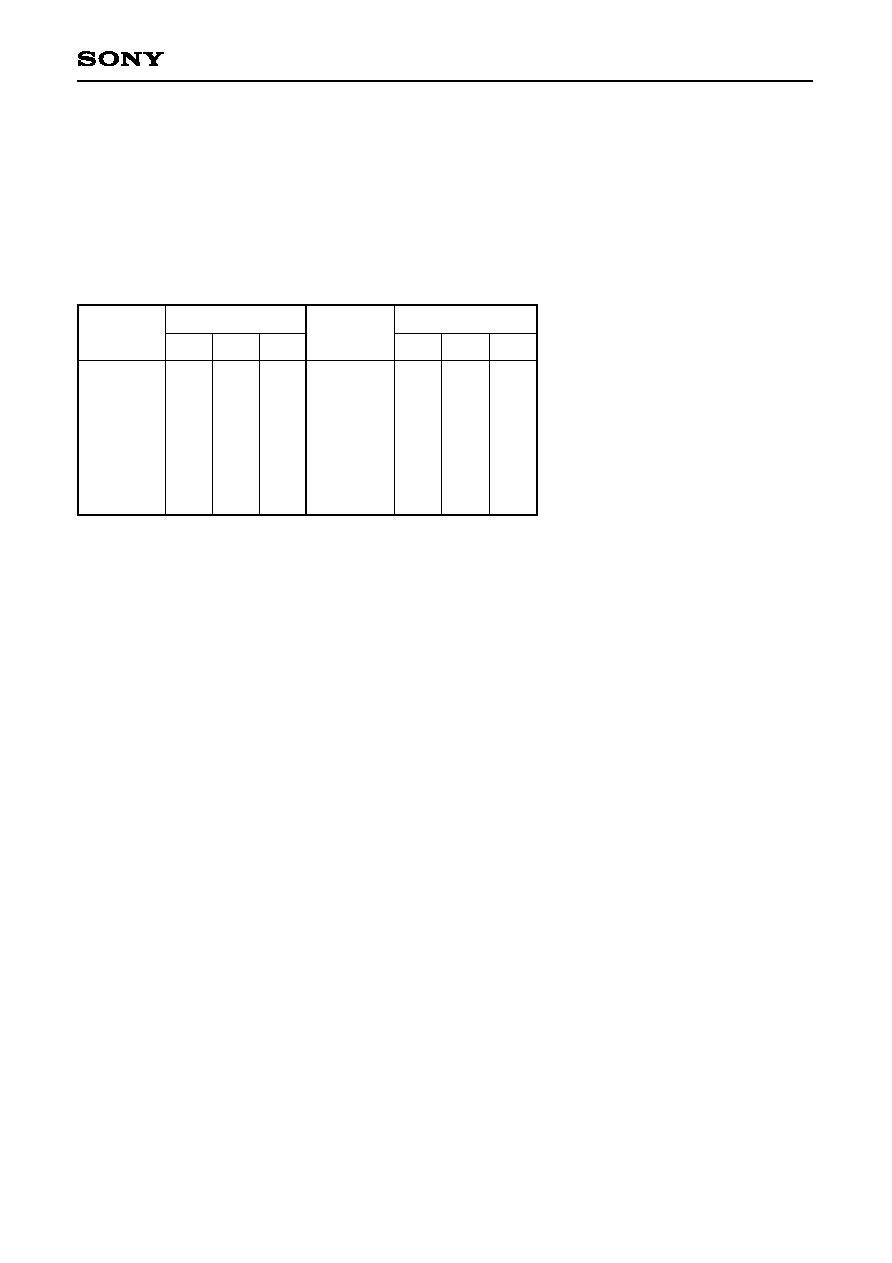

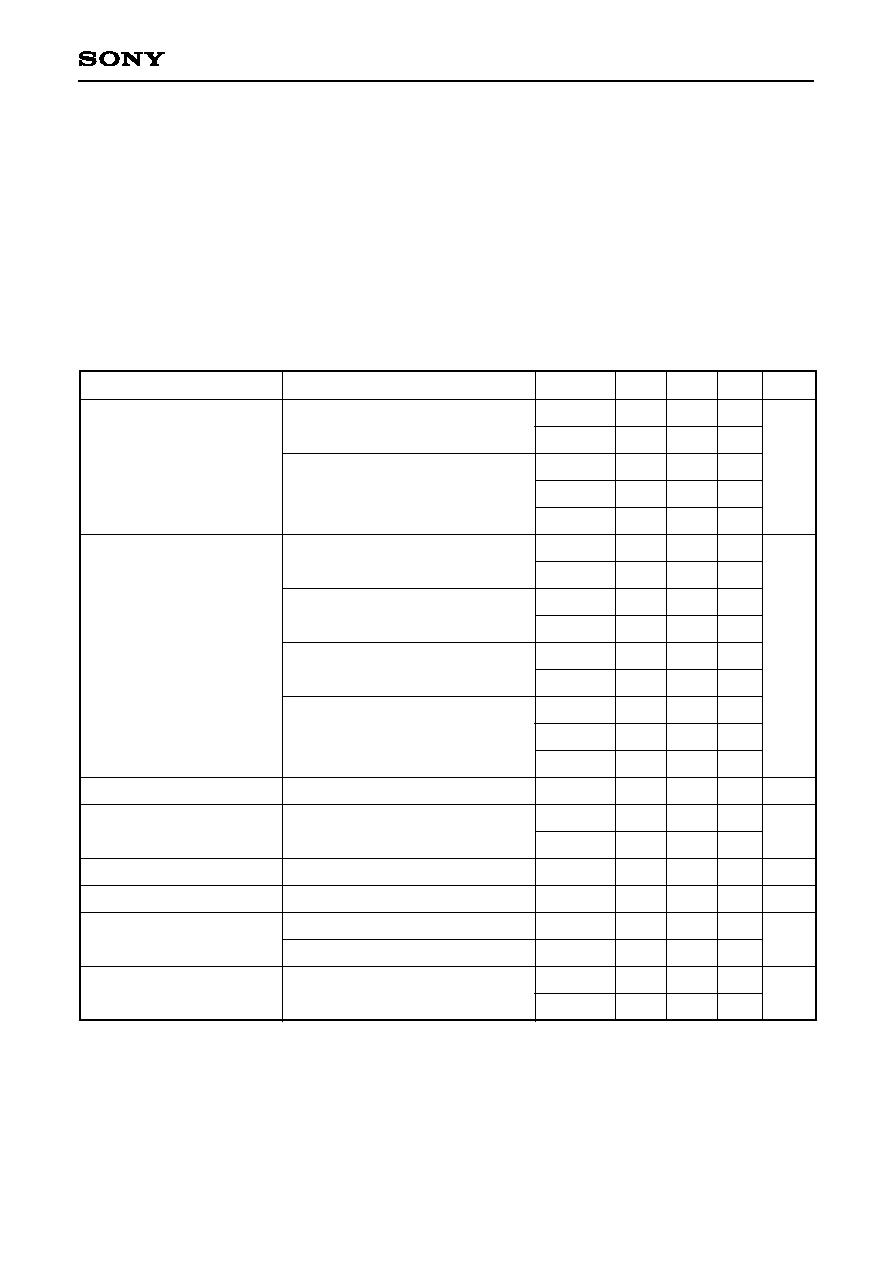

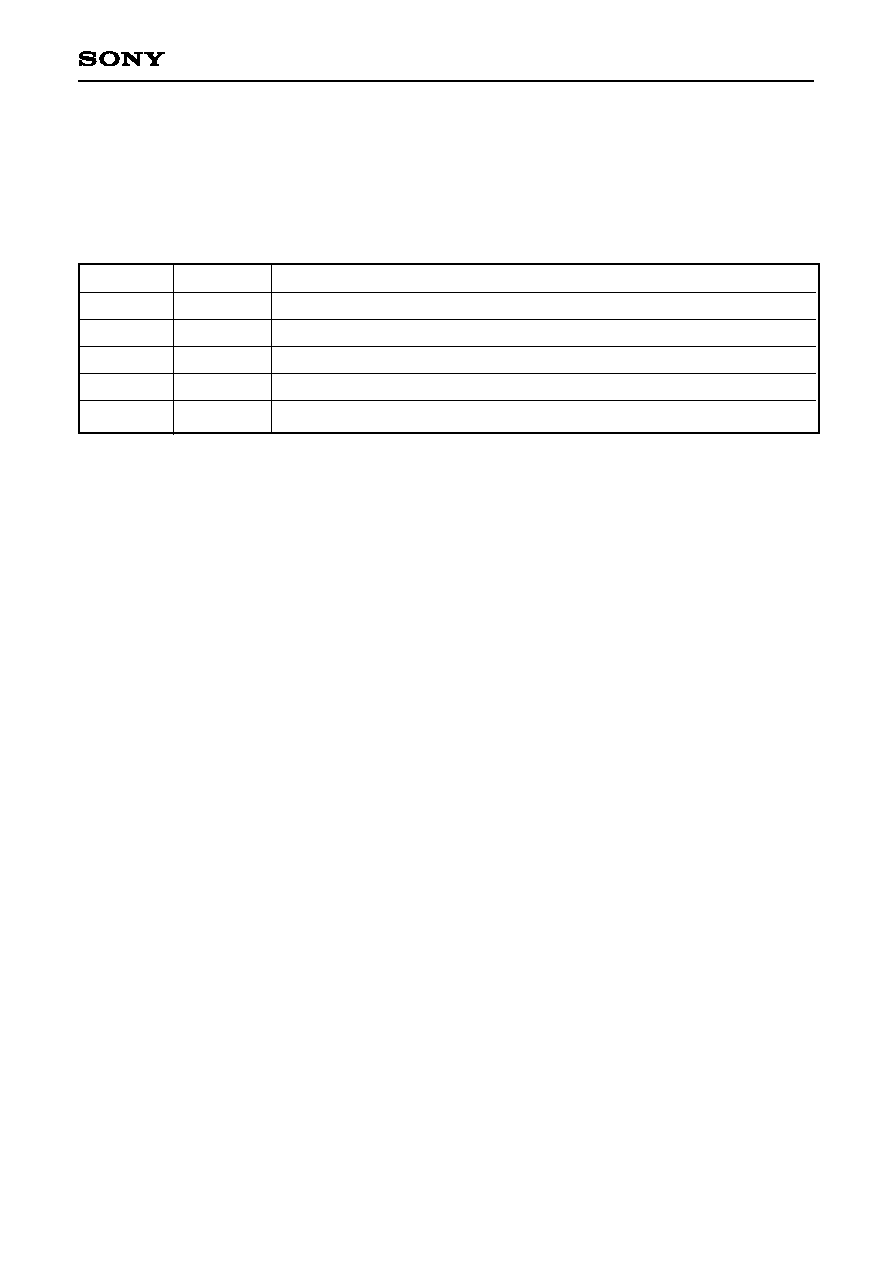

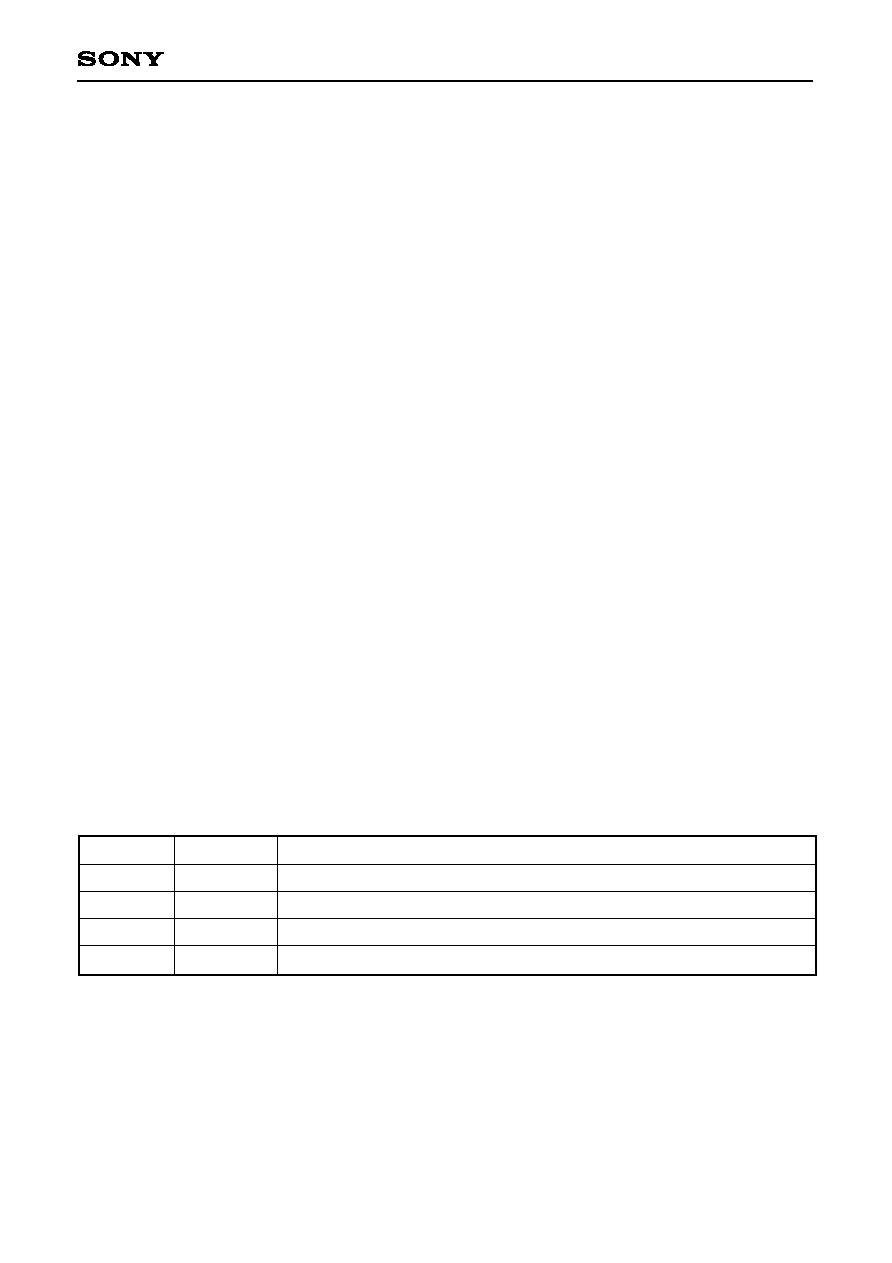

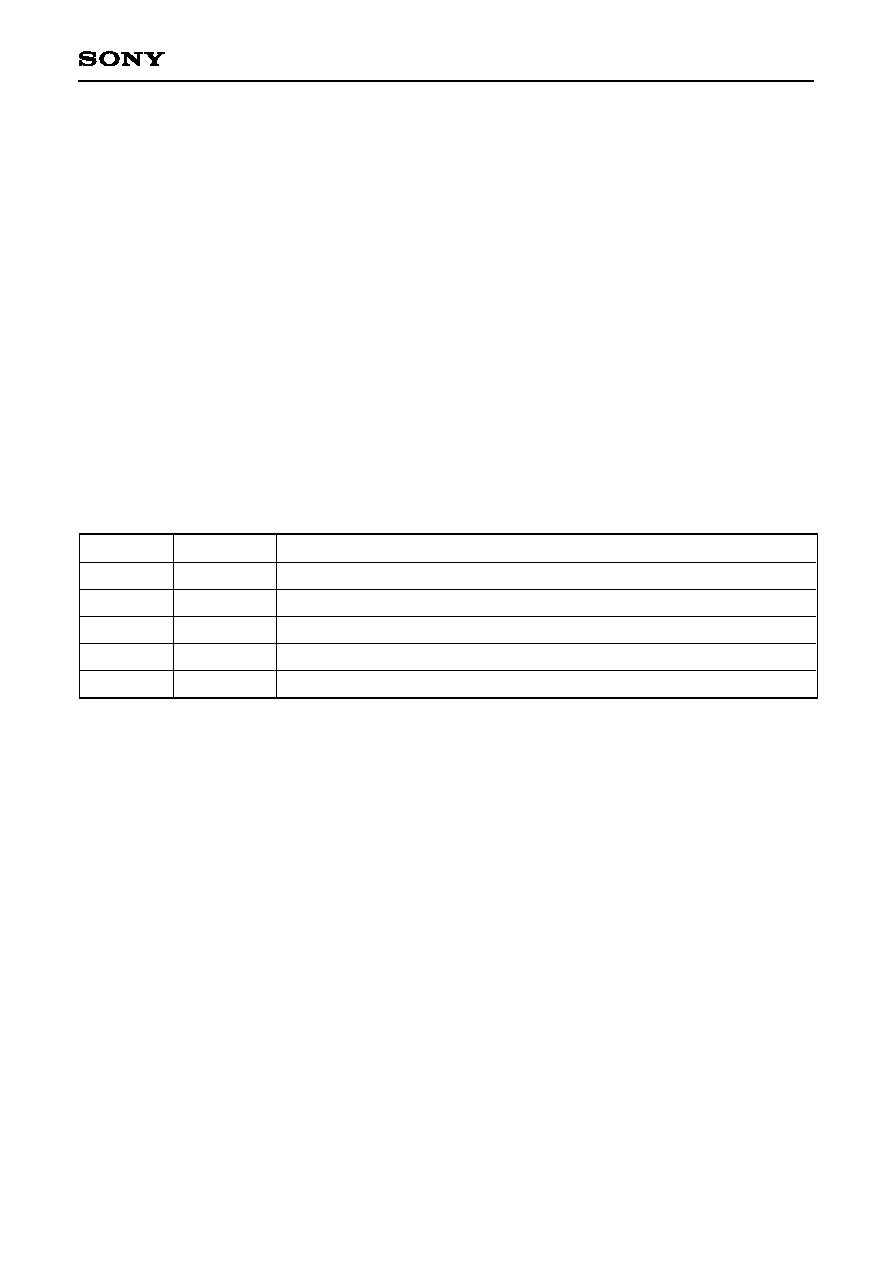

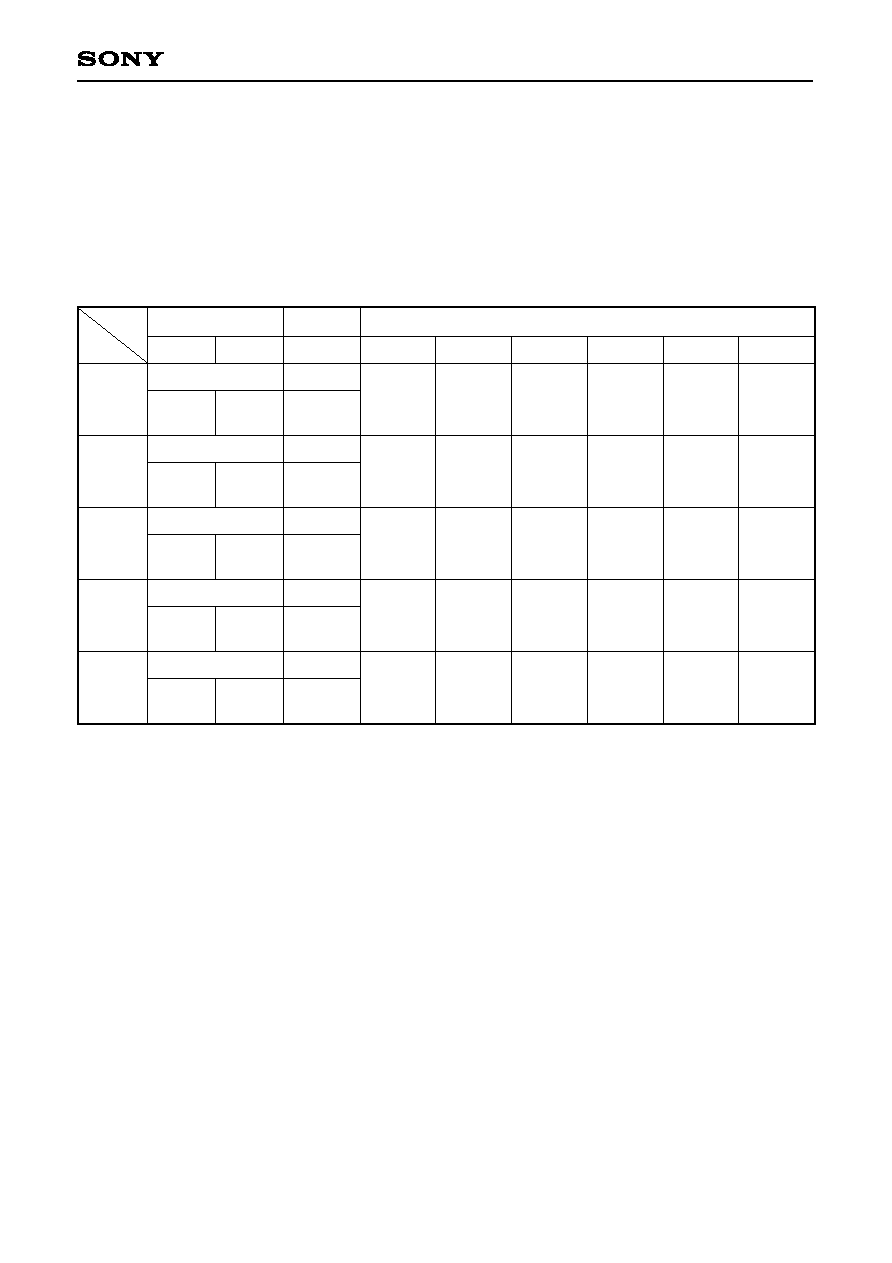

DC Characteristics

(AVD1 to 6 = AVDX = V

DD

0 to 2 = 5V ± 5%, AVS1 to 6 = AVSX = V

SS

0 to 7 = 0V, Ta = ≠20 to +70∞C)

Item

Symbol

Conditions

Min.

Max.

Unit

Applicable pins

Typ.

V

V

V

V

V

V

V

V

V

V

V

µA

µA

µA

1

,

2

,

7

1

,

2

,

7

5

5

3

,

6

3

,

6

4

8

,

9

8

,

9

,

10

11

11

1

,

5

,

7

2

,

3

,

6

9

,

10

Resistance between

7

and

11

High level

Low level

High level

Low level

High level

Low level

High level

Low level

High level

Low level

Input voltage

(1)

Input voltage

(2)

Input voltage

(3)

Input voltage (4)

Output voltage

(1)

Output voltage

(2)

Input leak current (1)

Input leak current (2)

Output leak current

Feedback resistance

V

IH

V

IL

V

IH

V

IL

V

IH

V

IL

V

IN

V

OH

V

OL

V

OH

V

OL

I

I

I

I

I

OZ

R

FB

CMOS input

Schmitt input

TTL input

Analog input

I

OH

= ≠2.0mA

I

OL

= 4.0mA

I

OH

= ≠12.0mA

I

OL

= 12.0mA

V

IH

= V

DD

, V

SS

V

IH

= V

DD

, V

SS

V

IH

= V

DD

, V

SS

0.7V

DD

0.8V

DD

2.2

V

SS

V

DD

≠ 0.8

V

DD

/2

≠10

≠40

≠40

250k

1M

0.3V

DD

0.2V

DD

0.8

V

DD

0.4

V

DD

/2

10

40

40

2.5M

1

CSL2, CSL1, TST0 to TST4, XMST

2

XLAT, RVDT, XS24, SCK

3

SI

4

LIN, RIN

5

XRST

6

During input to bidirectional pins BCK, LRCK

7

XTLI

8

During output from bidirectional pins BCK, LRCK

9

BFOT

10

REDY

11

XTLO

≠ 6 ≠

CXD2719Q

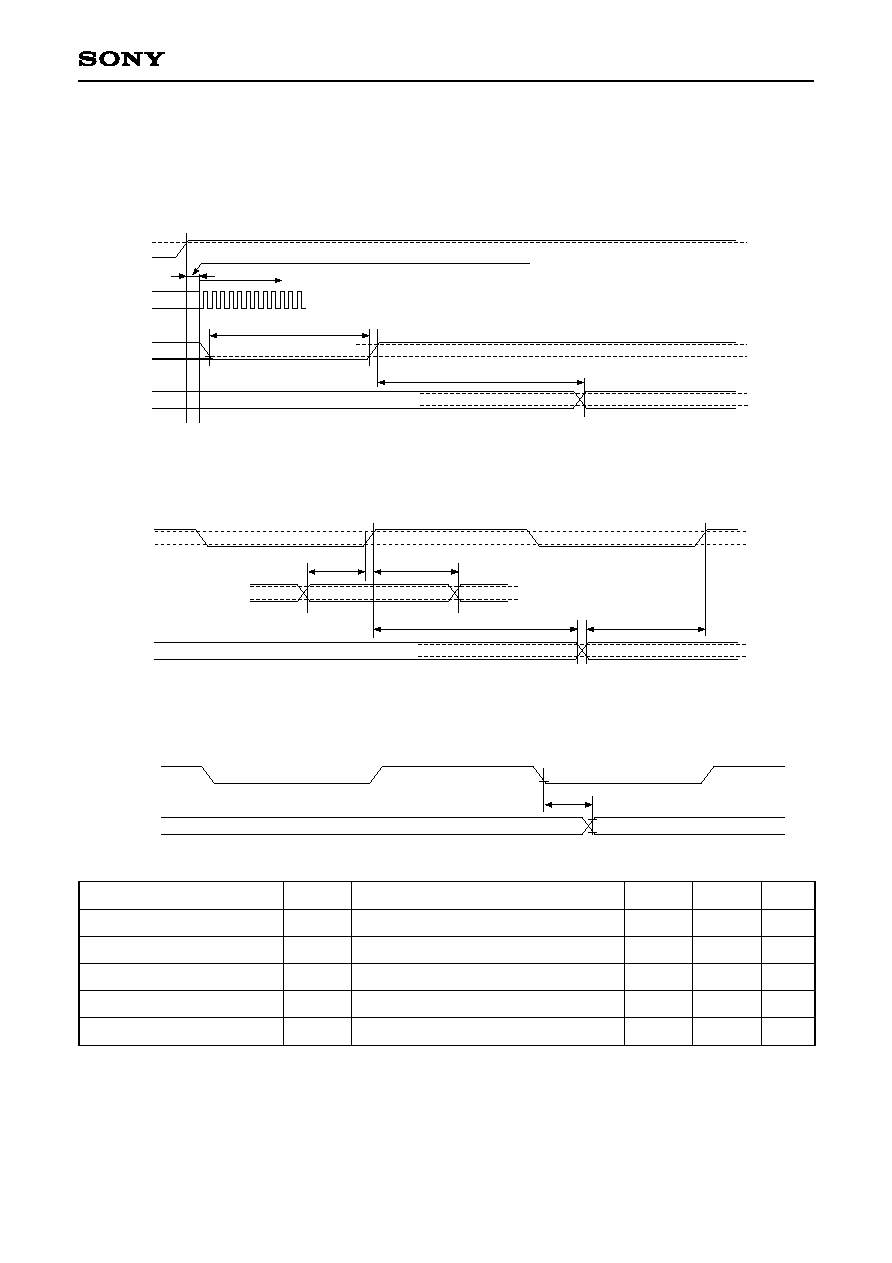

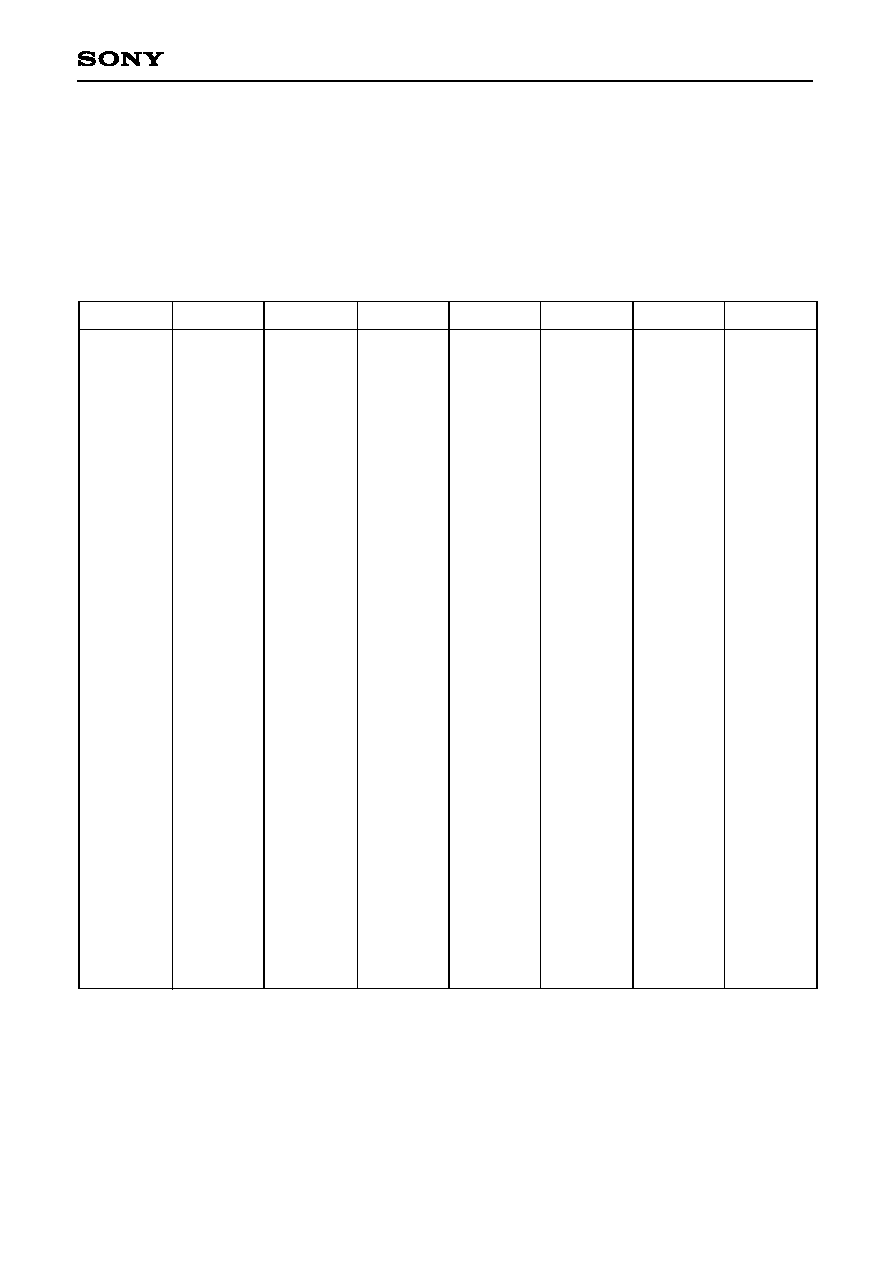

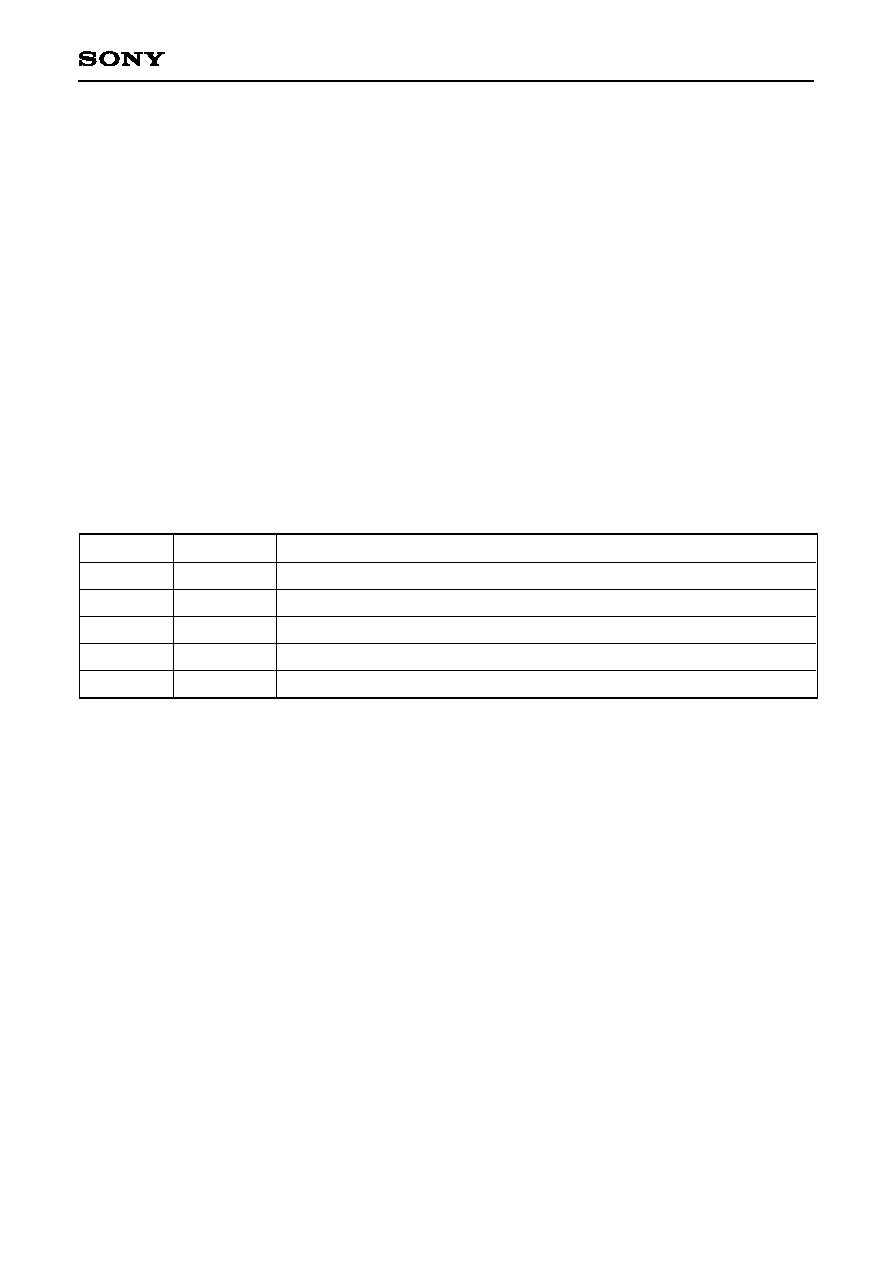

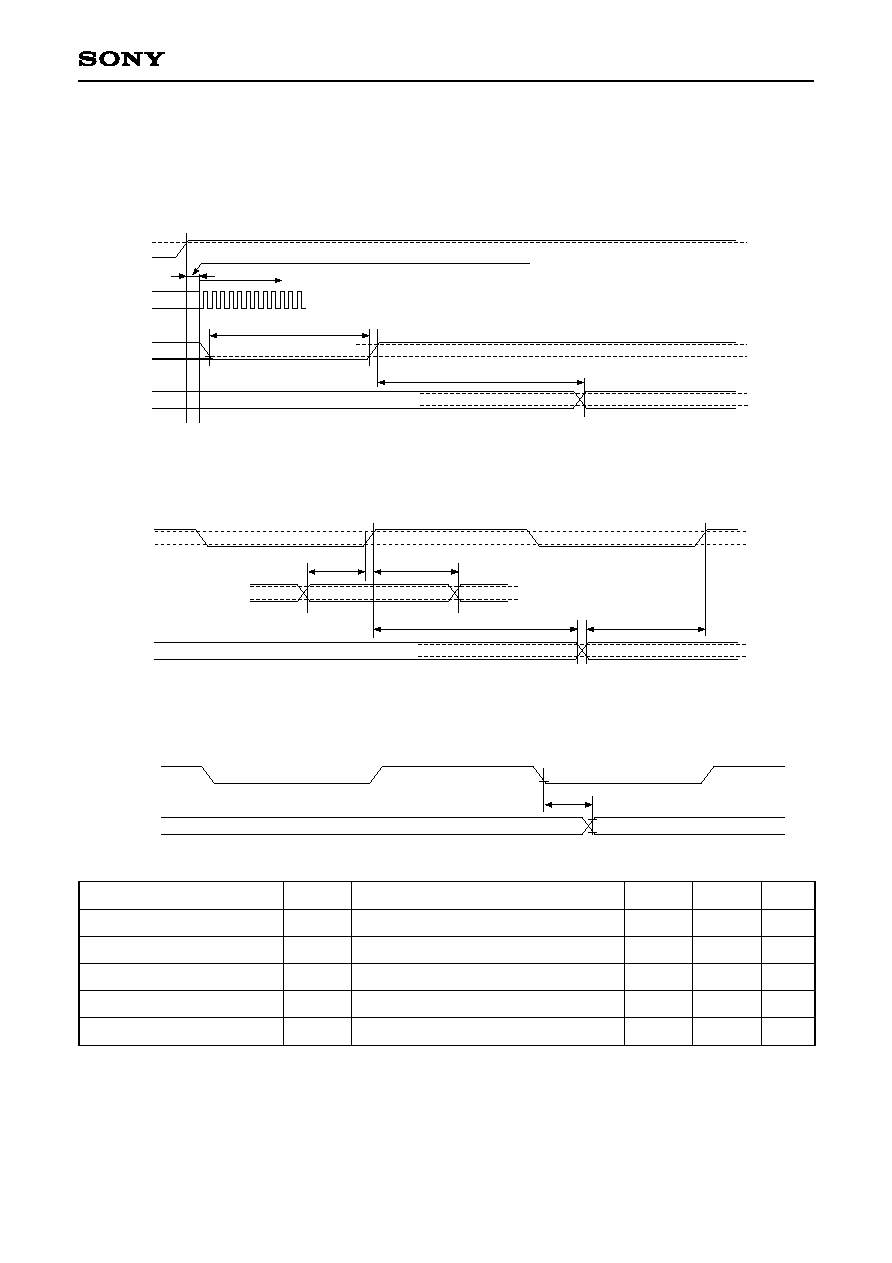

AC Characteristics

(AVD1 to 6 = AVDX = V

DD

0 to 2 = 5V ± 5%, AVS1 to 6 = AVDX = V

SS

0 to 7 = 0V, Ta = ≠20 to +70∞C)

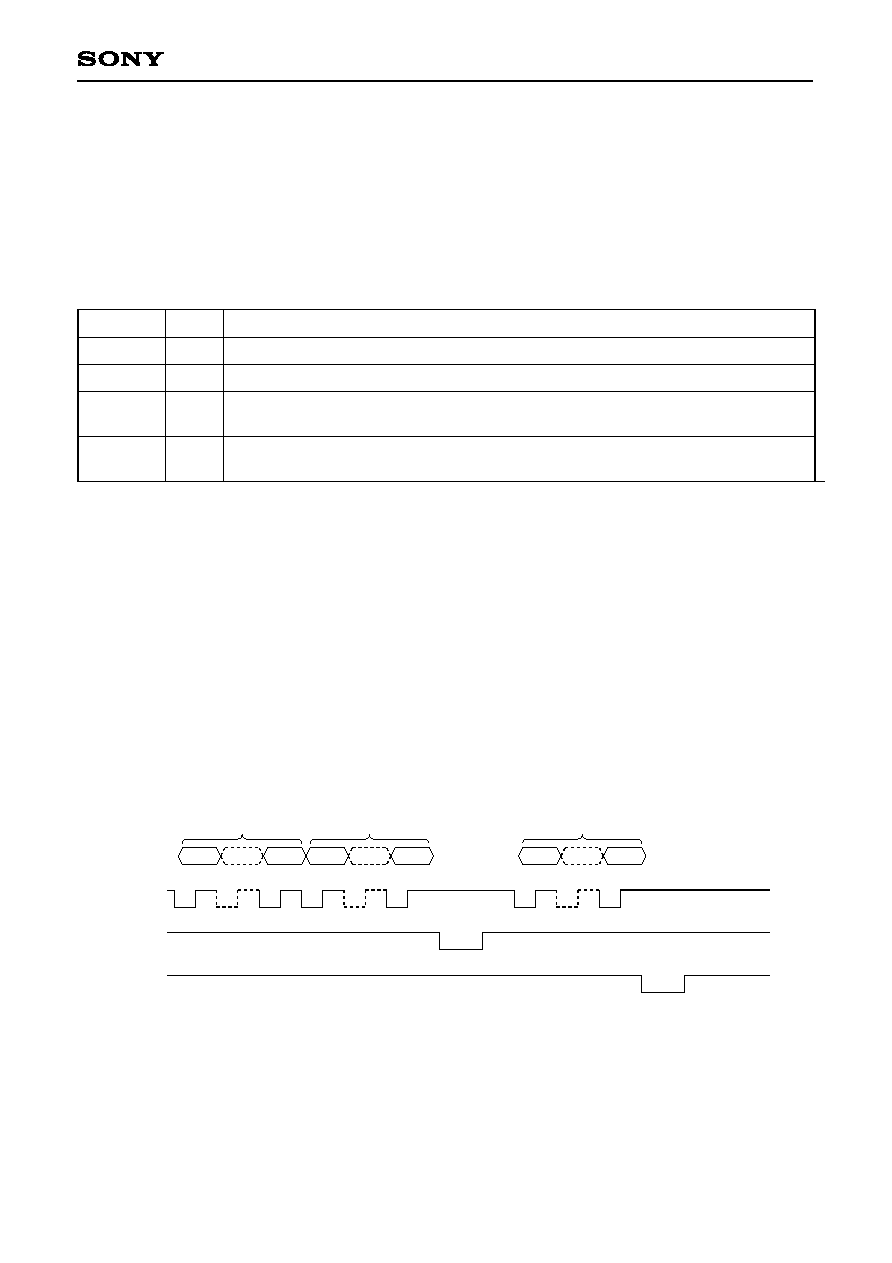

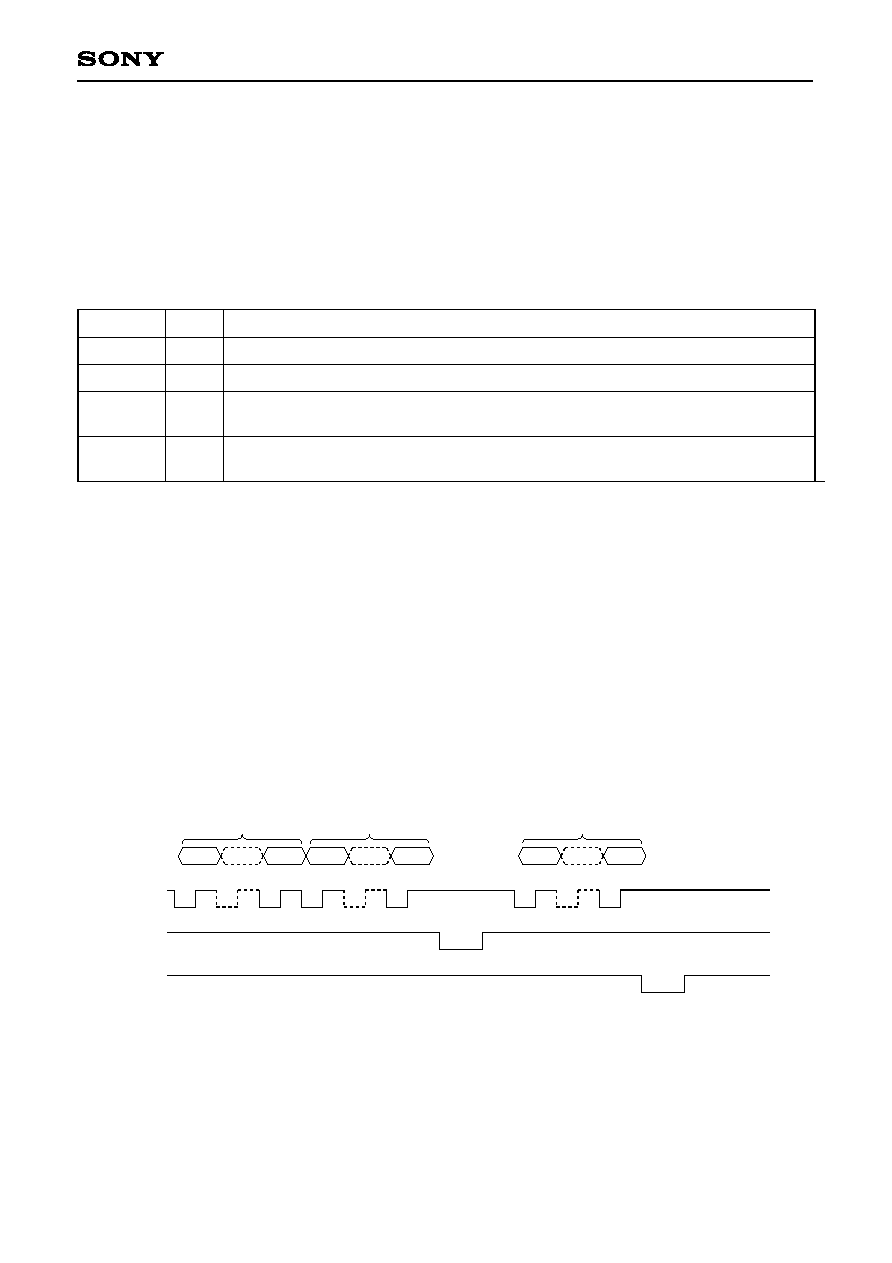

Input Timing from Power-on to Input Pin

∑∑∑∑∑

V

DD

XTLI

XRST

Input pins

0.7V

DD

0.3V

DD

1/fs or more

1/fs or more

Determined by the crystal and other external circuit conditions

Stable (clock applied correctly)

0.8V

DD

0.2V

DD

0.95V

DD

First input

BCK

SI

LRCK

tHLR

tSLR

0.7V

DD

0.3V

DD

0.7V

DD

0.3V

DD

tSSI

tHSI

0.7V

DD

0.3V

DD

BCK

LRCK

tDLR

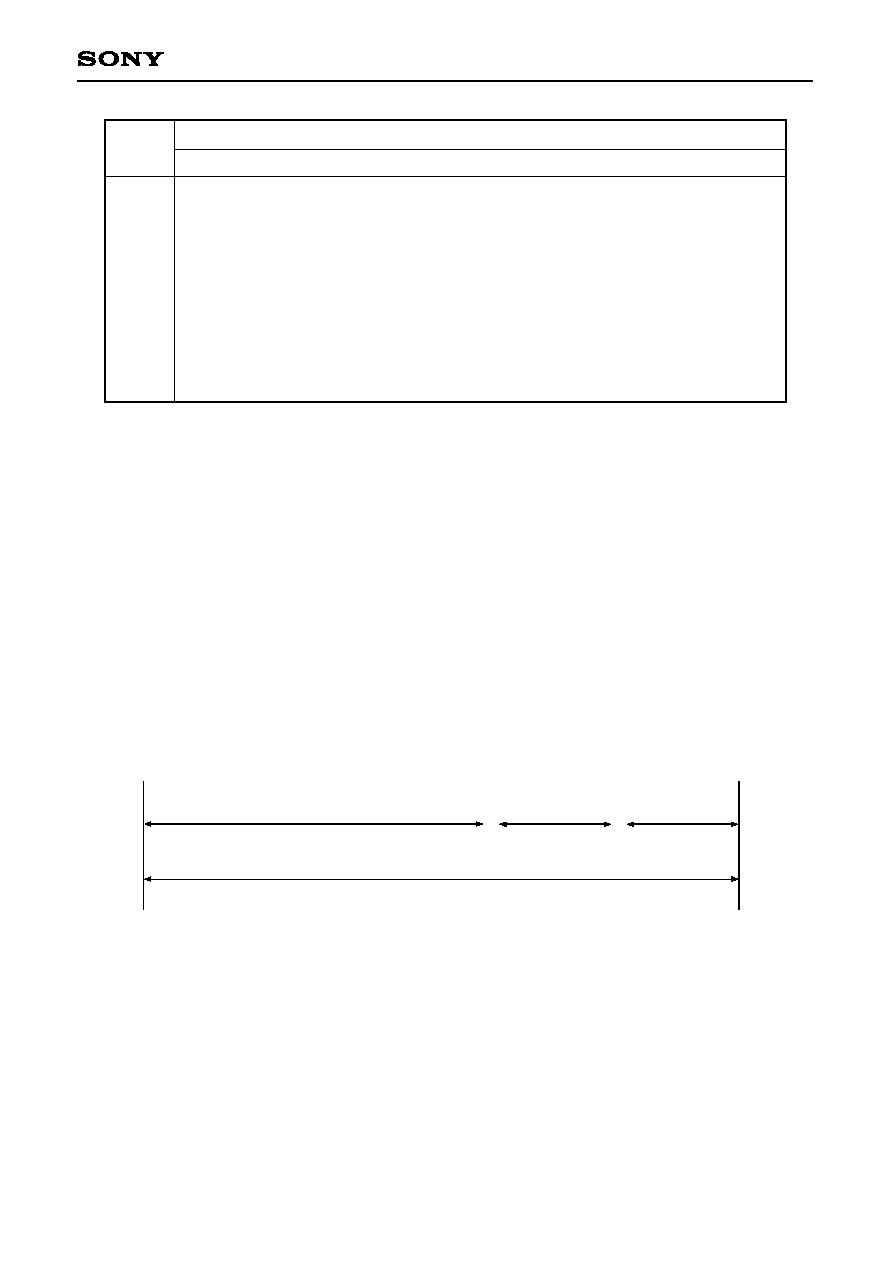

Serial Audio Interface Timing

[Slave mode]

[Master mode]

Item

SI setup time

SI hold time

LRCK setup time

LRCK hold time

LRCK delay time

Symbol

t

SSI

t

HSI

t

SLR

t

HLR

t

DLR

Conditions

Slave mode

Slave mode

Slave mode

Slave mode

Master mode, C

L

= 120pF

Min.

20

40

20

40

Max.

50

Unit

ns

ns

ns

ns

ns

≠ 7 ≠

CXD2719Q

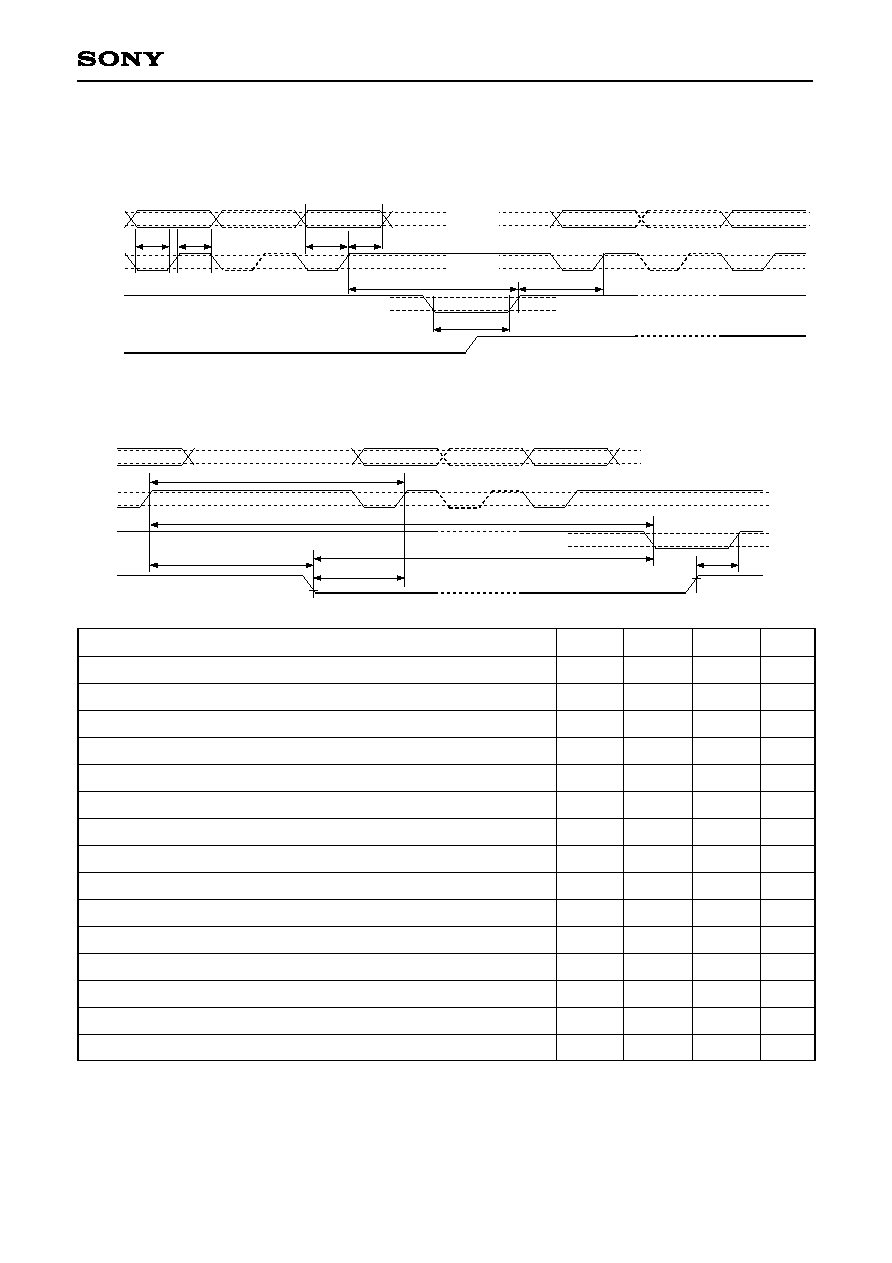

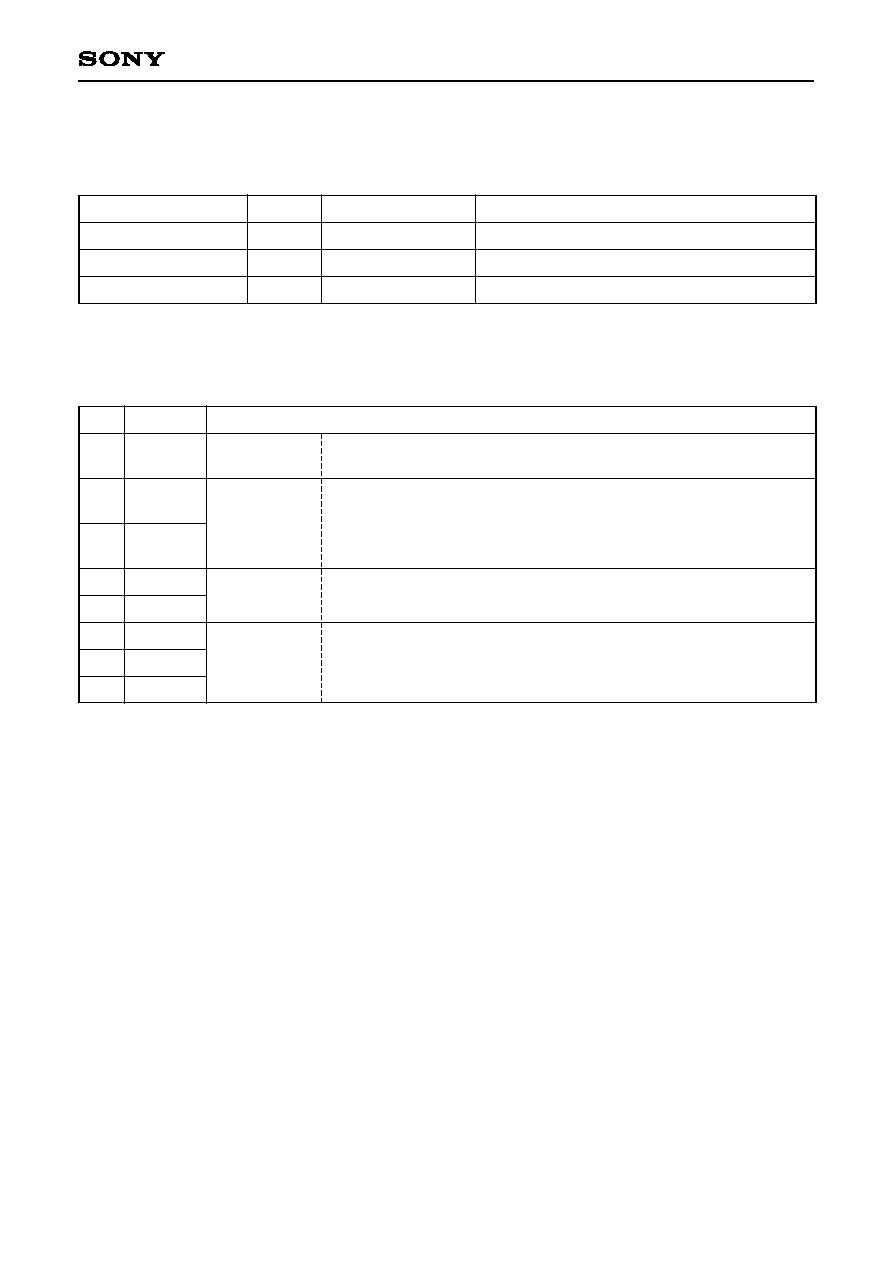

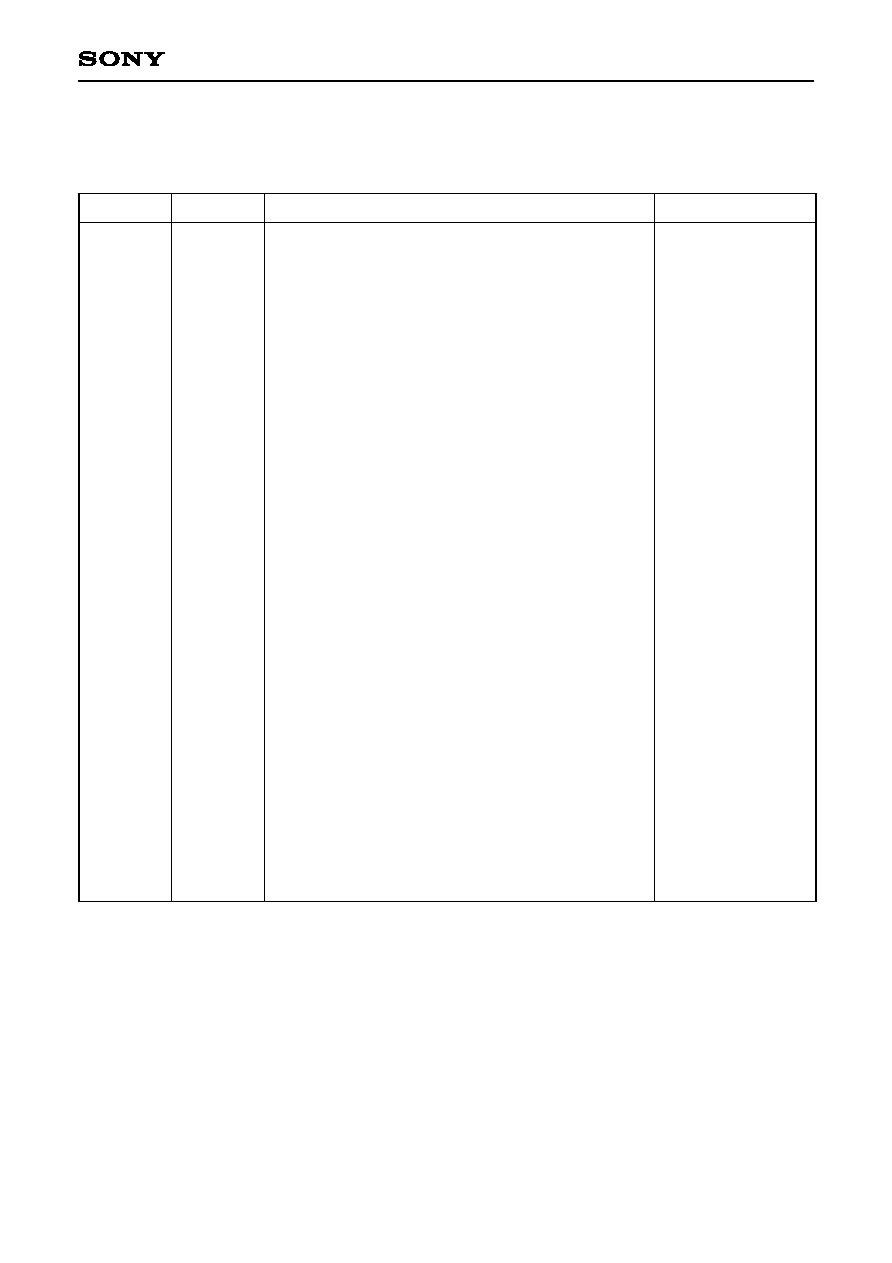

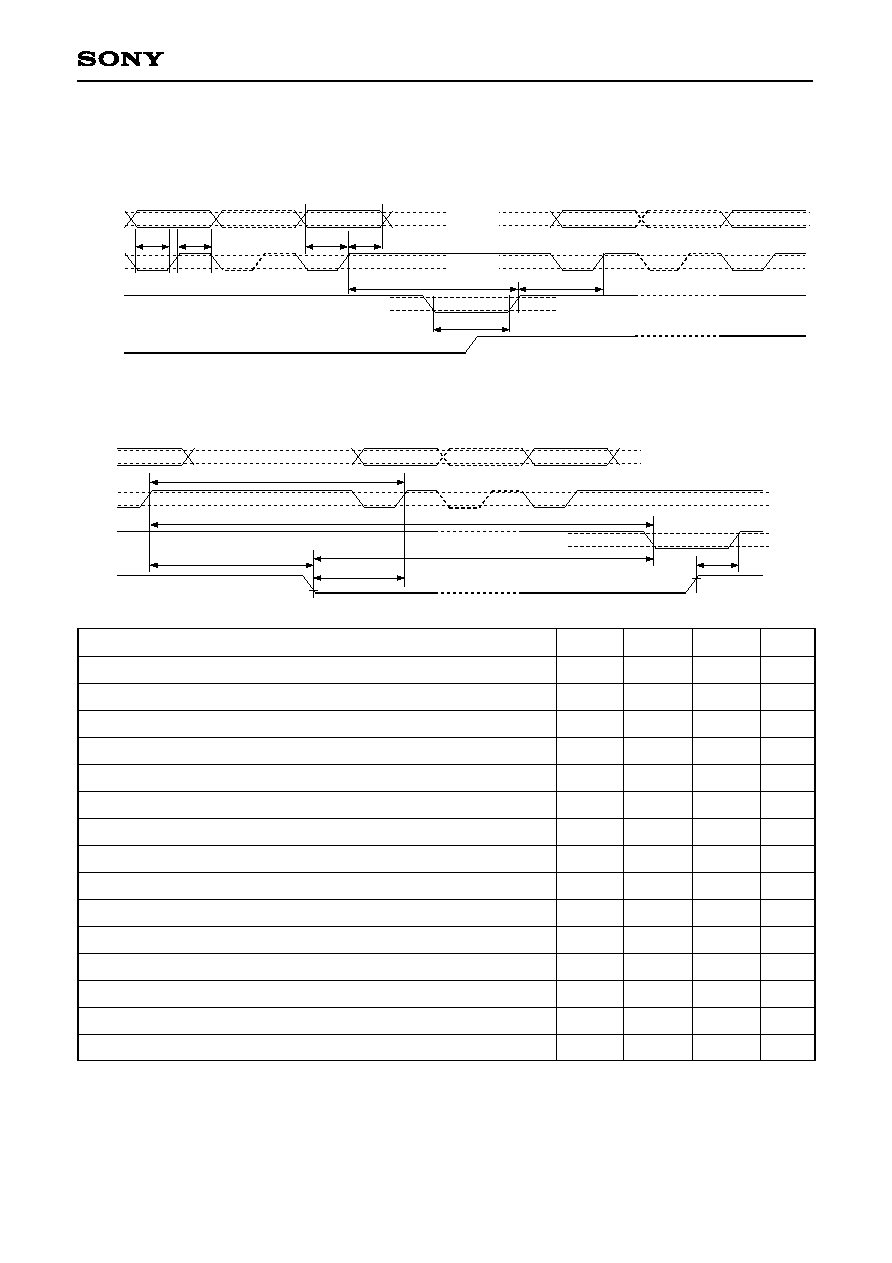

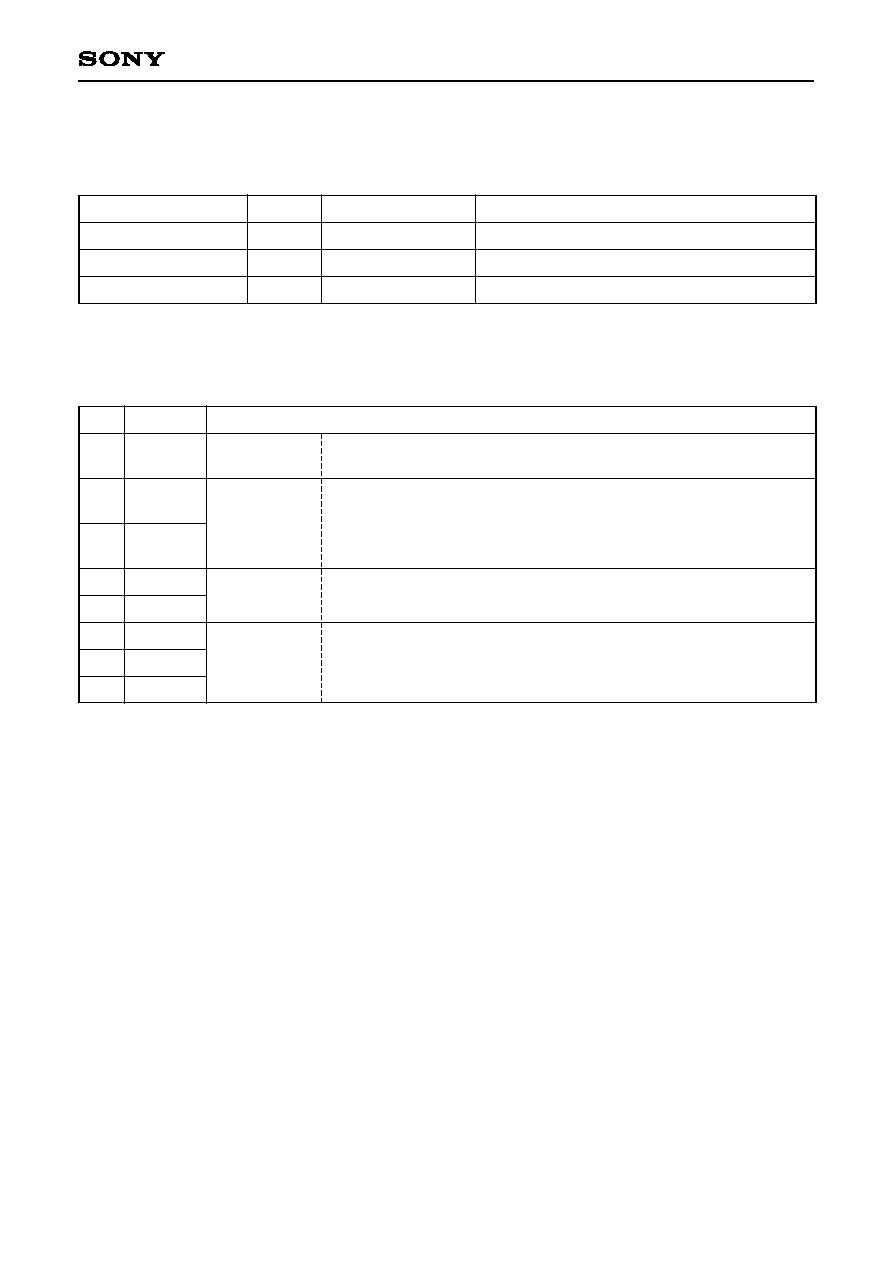

Microcomputer Interface Timing

Transfer timing for address section, transfer mode section and data section LSB

Transfer timing from data section MSB to address section and transfer mode section

Notes) 1. t is the cycle of 2/3 the clock frequency applied to the XTLI pin. (512fs)

2. The REDY pin is the value for C

L

= 60pF.

Item

RVDT data setup time relative to SCK rise

RVDT data hold time from SCK rise

SCK Low level width

SCK High level width

XLAT Low level width

XLAT High level width

SCK rise preceding time relative to XLAT rise

SCK rise wait time relative to XLAT rise

Delay time to REDY fall relative to SCK rise

REDY fall preceding time relative to SCK rise

REDY rise preceding time relative to XLAT rise

REDY rise preceding time relative to SCK fall

XLAT fall wait time relative to SCK rise

XLAT fall delay time relative to REDY fall

SCK rise wait time for next transfer

Symbol

tDS

tDH

tSWL

tSWH

tLWL

tLWH

tSLP

tLSD

tSBD

tBSP

tRLP

tRSDP

tSLD

tLDR

tSS

Min.

20

1t + 20

1t + 20

1t + 20

1t + 20

1t + 20

20

3t + 20

20

20

20

3t + 20

20

2t + 40

Max.

4t + 50

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

RVDT

SCK

tSWL

tSWH

tDS

tDH

Address LSB

Mode MSB

0.3V

DD

0.7V

DD

0.3V

DD

0.7V

DD

tSLP

tLSD

tLWL

0.3V

DD

0.7V

DD

XLAT

REDY

Data LSB

Data MSB

RVDT

SCK

XLAT

REDY

Mode MSB

0.3V

DD

0.7V

DD

Address LSB

Data MSB

tSS

tLDR

tSBD

tSLD

tBSP

0.3V

DD

0.7V

DD

tRLP

0.3V

DD

0.7V

DD

≠ 8 ≠

CXD2719Q

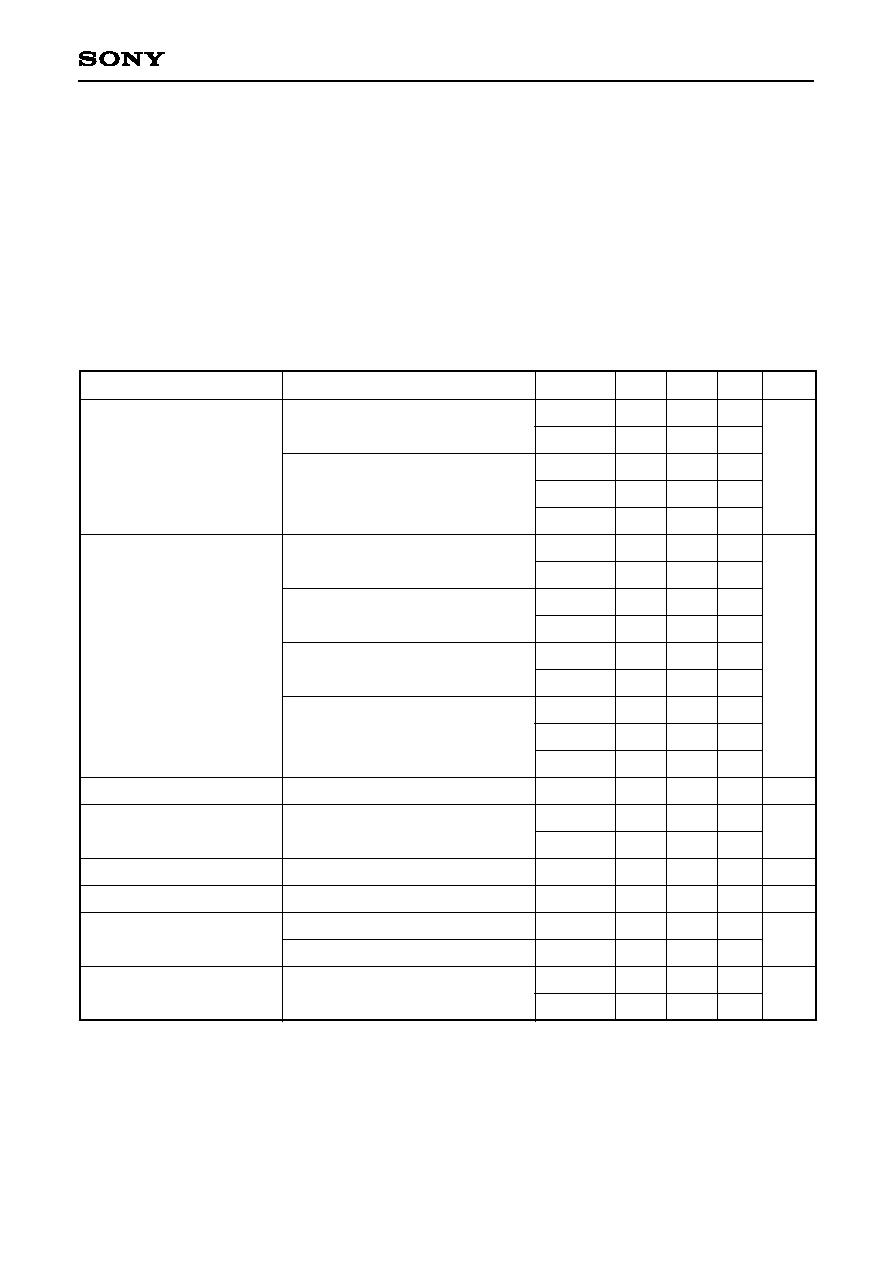

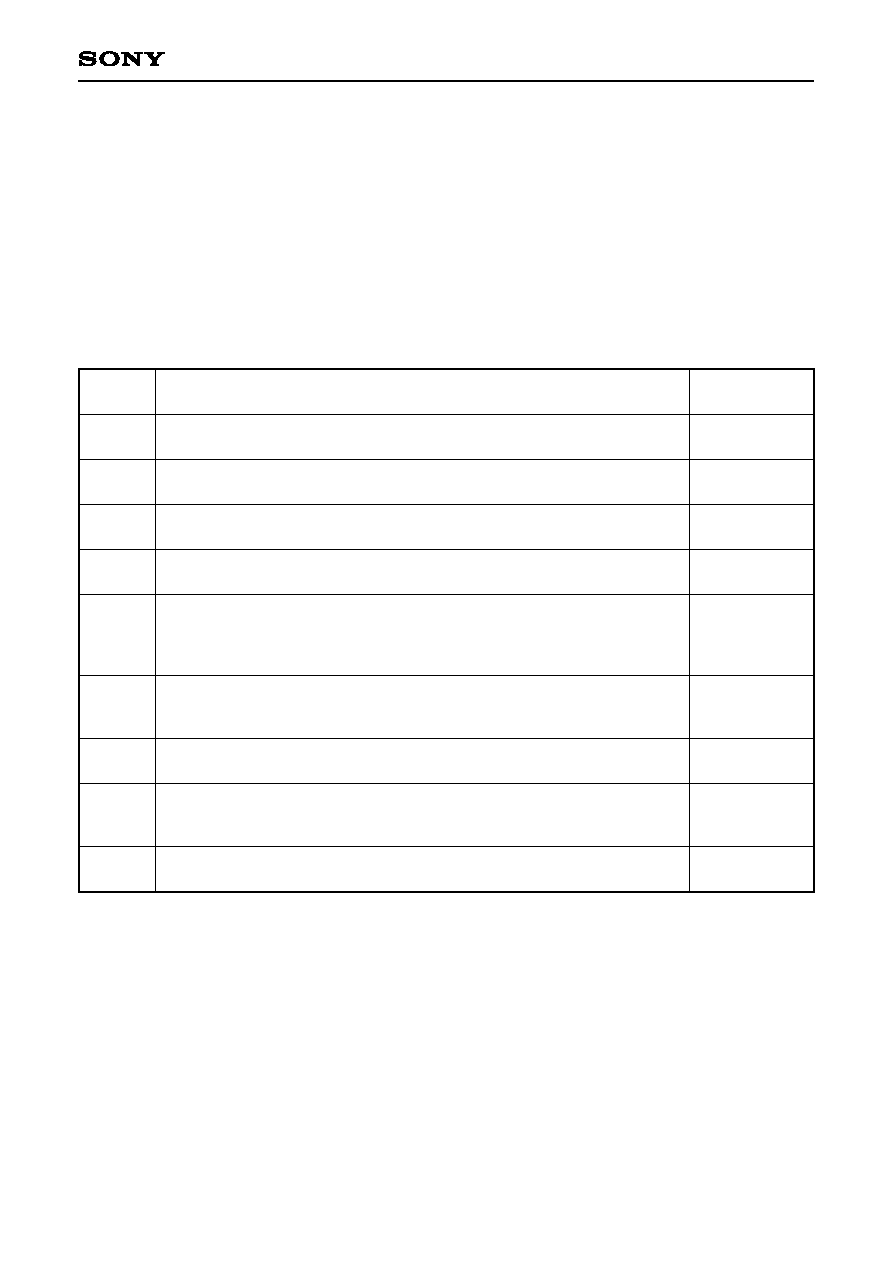

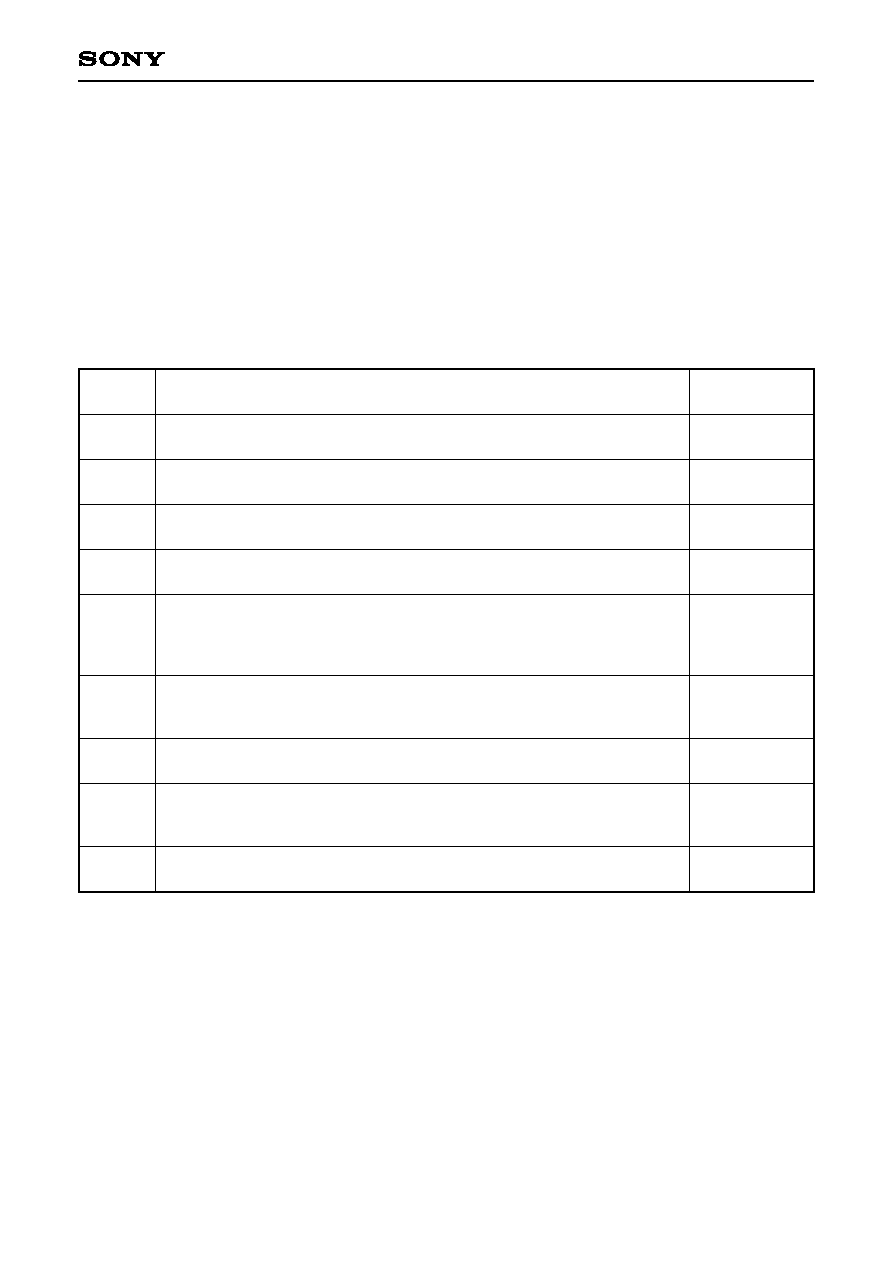

Analog Characteristics

(AVD0 to 6 = V

DD

0 to 2 = AVDX = 5.0V, AVS0 to 6 = V

SS

0 to 7 = AVSX = 0.0V, fs = 44.1kHz, Ta = 25∞C)

When Pro Logic mode is on, the input signal level while measuring the center (C) and surround (S) channels

should be ≠3dB smaller than the input level while measuring the left (L) and right (R) channels. Note that the C

channel is input in-phase to the L channel, and the S channel is input at reversed phase to the R channel.

The input level is the same for all measurement items when Pro Logic mode is off.

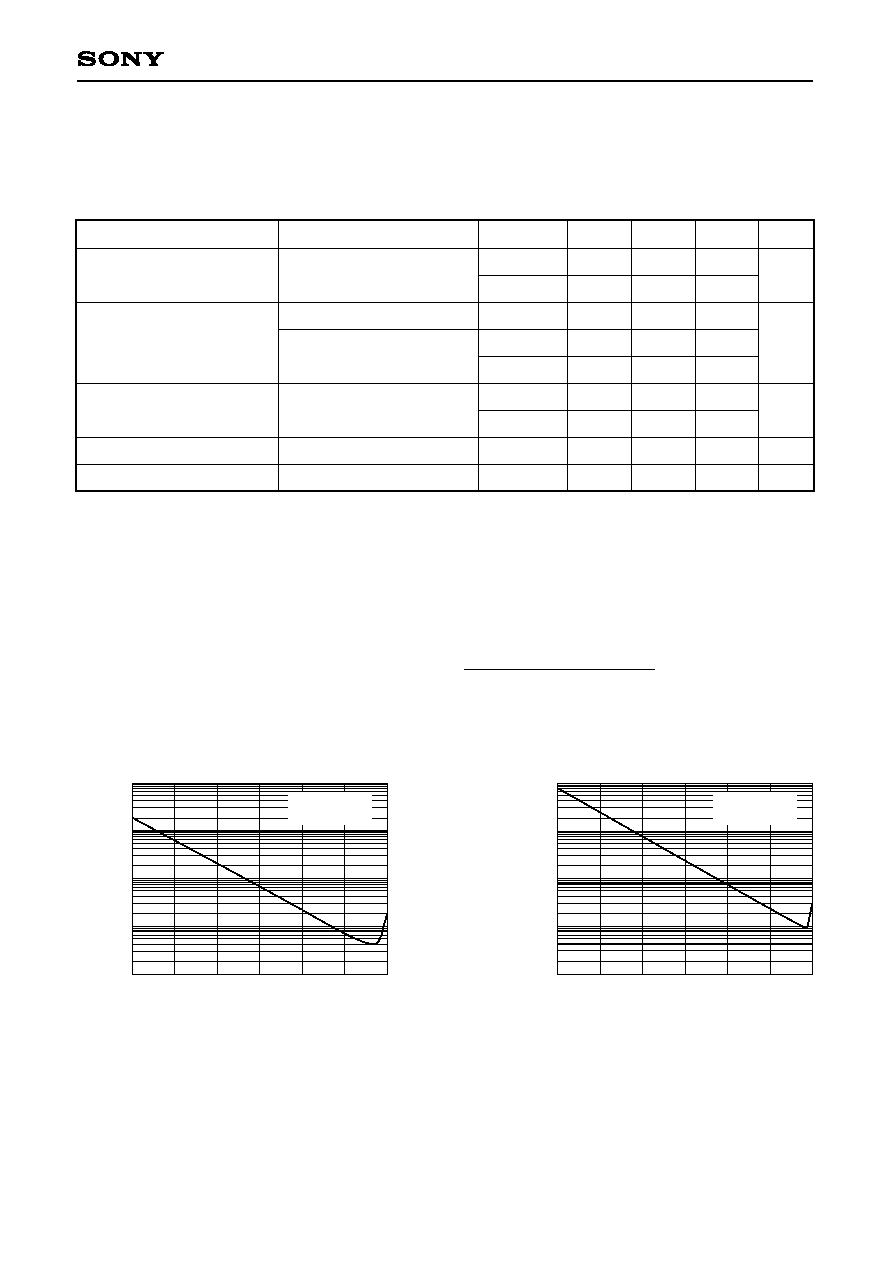

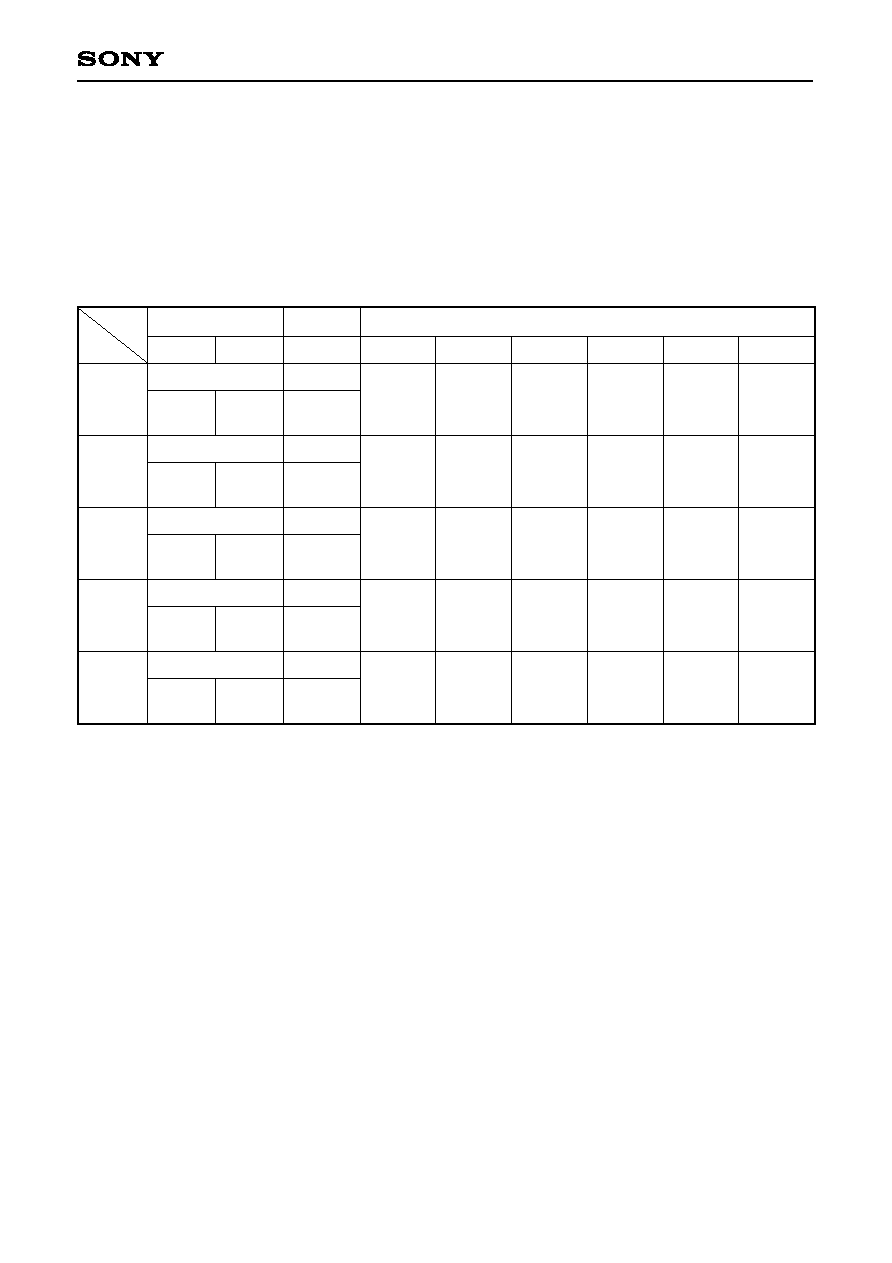

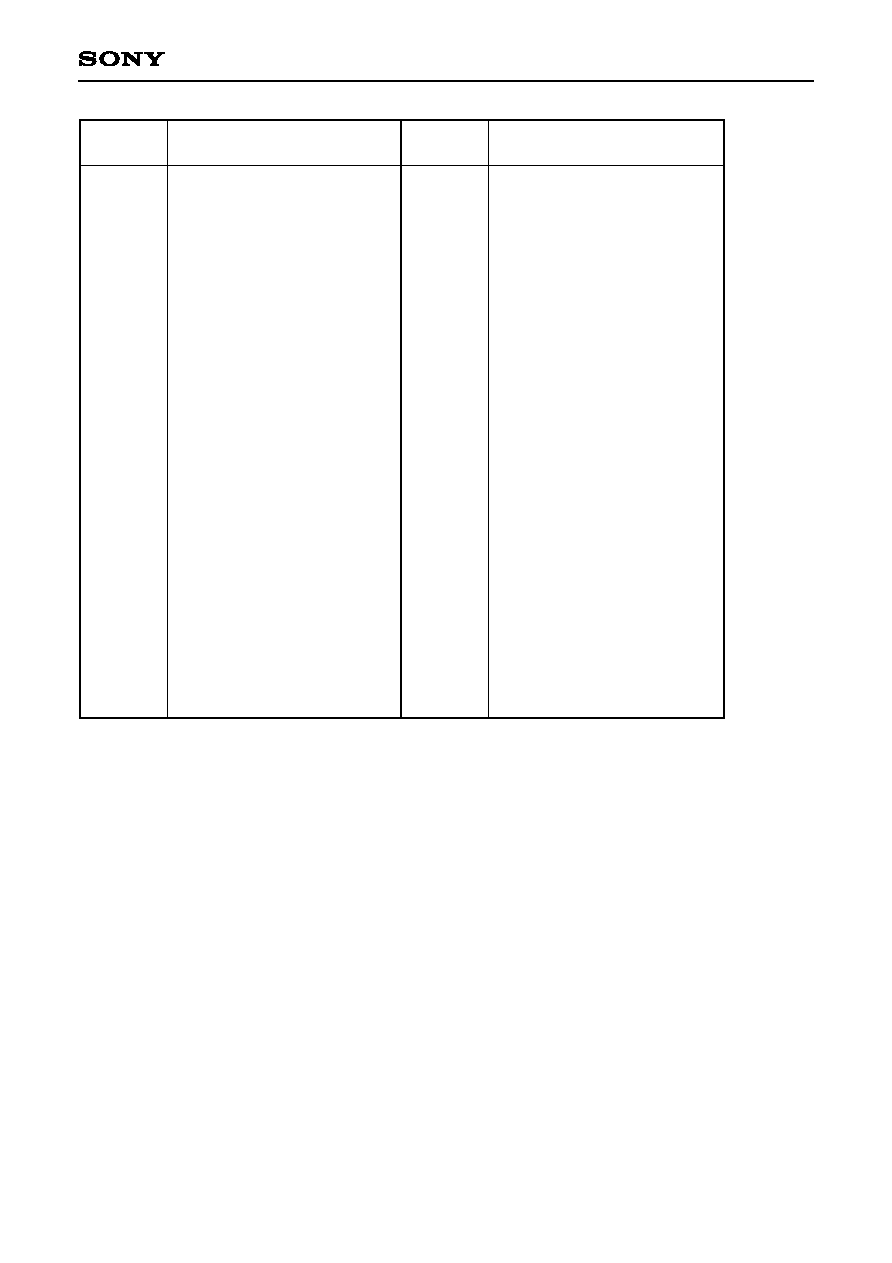

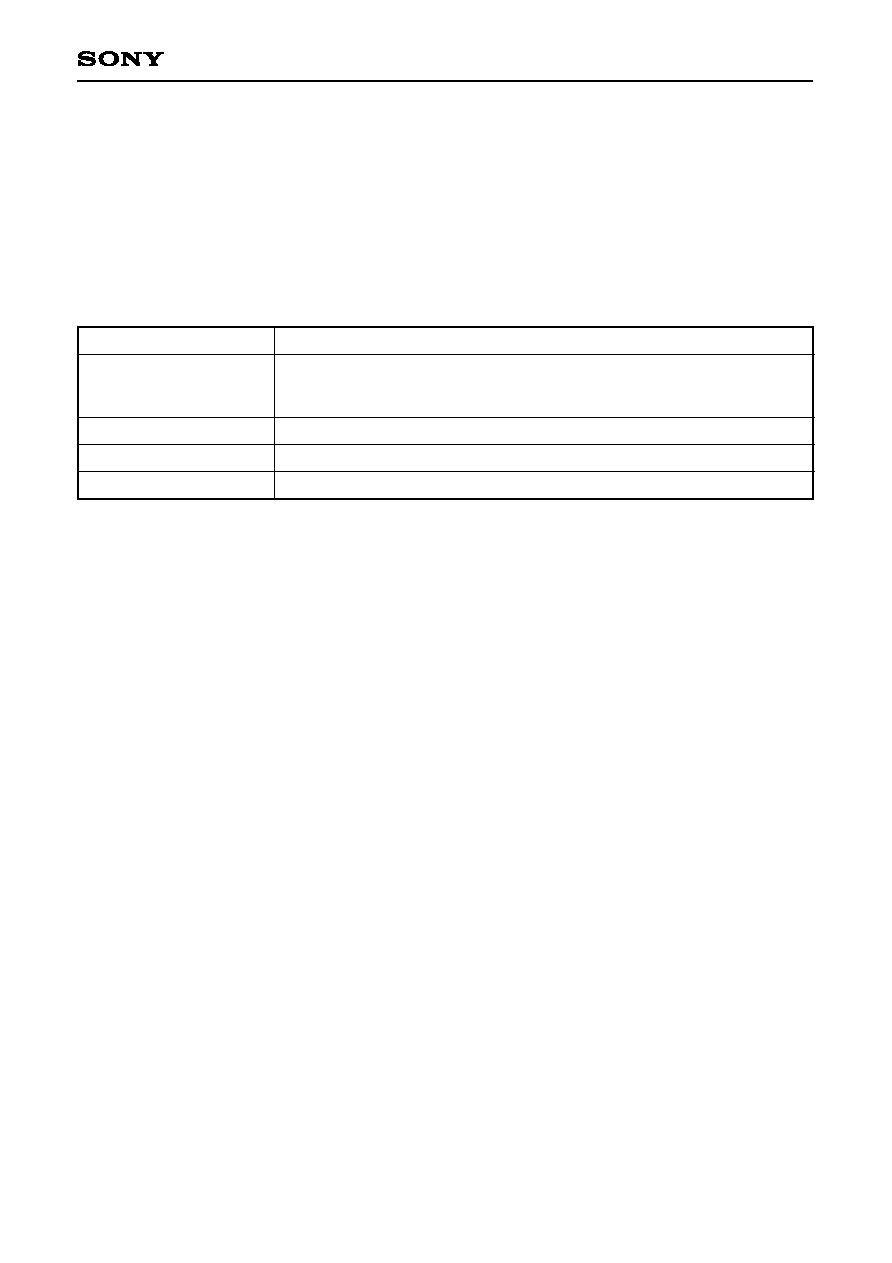

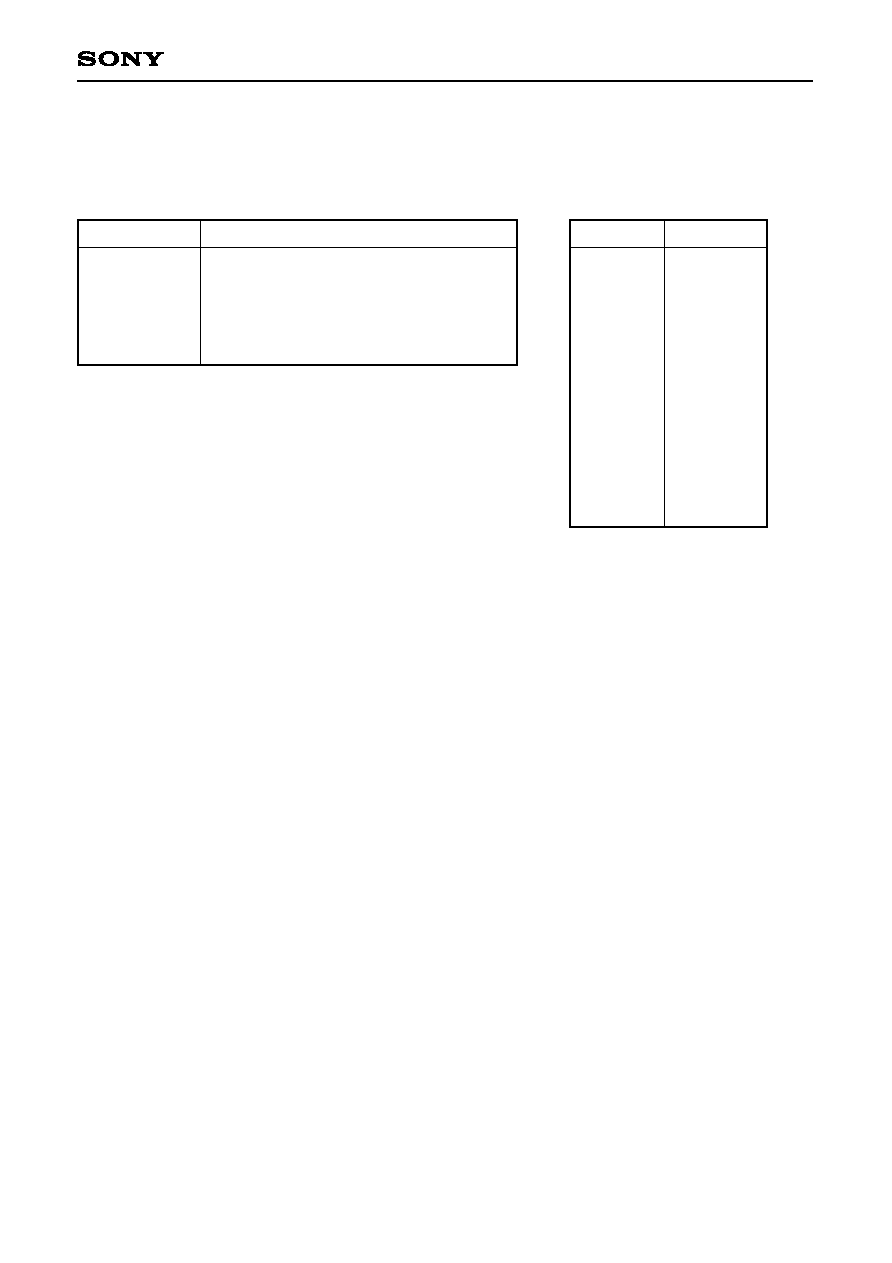

1. ADC + DAC Connection Total Characteristics

In addition to the ADC and DAC, the total characteristics include the prefilter with built-in operational amplifier,

built-in post filter, and trim volume. Use the analog I/O circuits in the Application Circuit for the measurement

circuit.

1-1. When Pro Logic mode is on

Unless otherwise specified, the measurement conditions are as given below.

∑ V

IN

(L, R) = 300mVrms, V

IN

(C, S) = 212mVrms (= 0dB)

∑ f

IN

= 1kHz

1

When V

IN

= 200mVrms (= ≠3.52dB), the S/N ratio is 3.52dB smaller than the values noted in the table above.

2

V

IN

(L, R) = 2.0Vrms, V

IN

(C, S) = 1.414Vrms

3

V

IN

(L, R) = 300mVrms, V

IN

(C, S) = 212mVrms

4

V

IN

(L, R) = 200mVrms, V

IN

(C, S) = 141mVrms

5

When the L and R channel gain deviation is 0.1dB or less for the ADC front-end prefilter output.

6

Includes the amplification (L/Rch...5.27dB, C/Sch...13.72dB) of the external amplifier.

7

The trim volume is set to 0dB.

L, R

C, S

L, R

C

S

L, R

C, S

L, R

C, S

L, R

C, S

L, R

C

S

L, R

C, S

(all)

(all)

L, R

C, S

7

70

65

25

25

250

80

72

60

56

64

0.04

0.007

0.015

0.03

0.02

0.04

0.12

0.18

0.04

16.5

60

40

280

±0.2

36

91

3.9

≠13.2

1.00

1.00

310

dB

%

dB

dB

Vrms

dB

mA

dB

S/N ratio

1

THD + N

Head room

Matrix rejection

Output level

Level difference between channels

Current consumption

Power supply rejection

ratio

6

CCIR/ARM filter

10Hz to 500kHz

10Hz to 20kHz

V

IN

= 16.5dB

2

10Hz to 20kHz

V

IN

= 0dB

3

10Hz to 20kHz

V

IN

= ≠3.52dB

4

10Hz to 500kHz

10Hz to 20kHz, THD + N = 1%

5

Analog system (including oscillator circuit)

Digital system

1mVrms, 100Hz sine wave

Channels

Min.

Typ.

Max.

Unit

Item

Measurement conditions

≠ 9 ≠

CXD2719Q

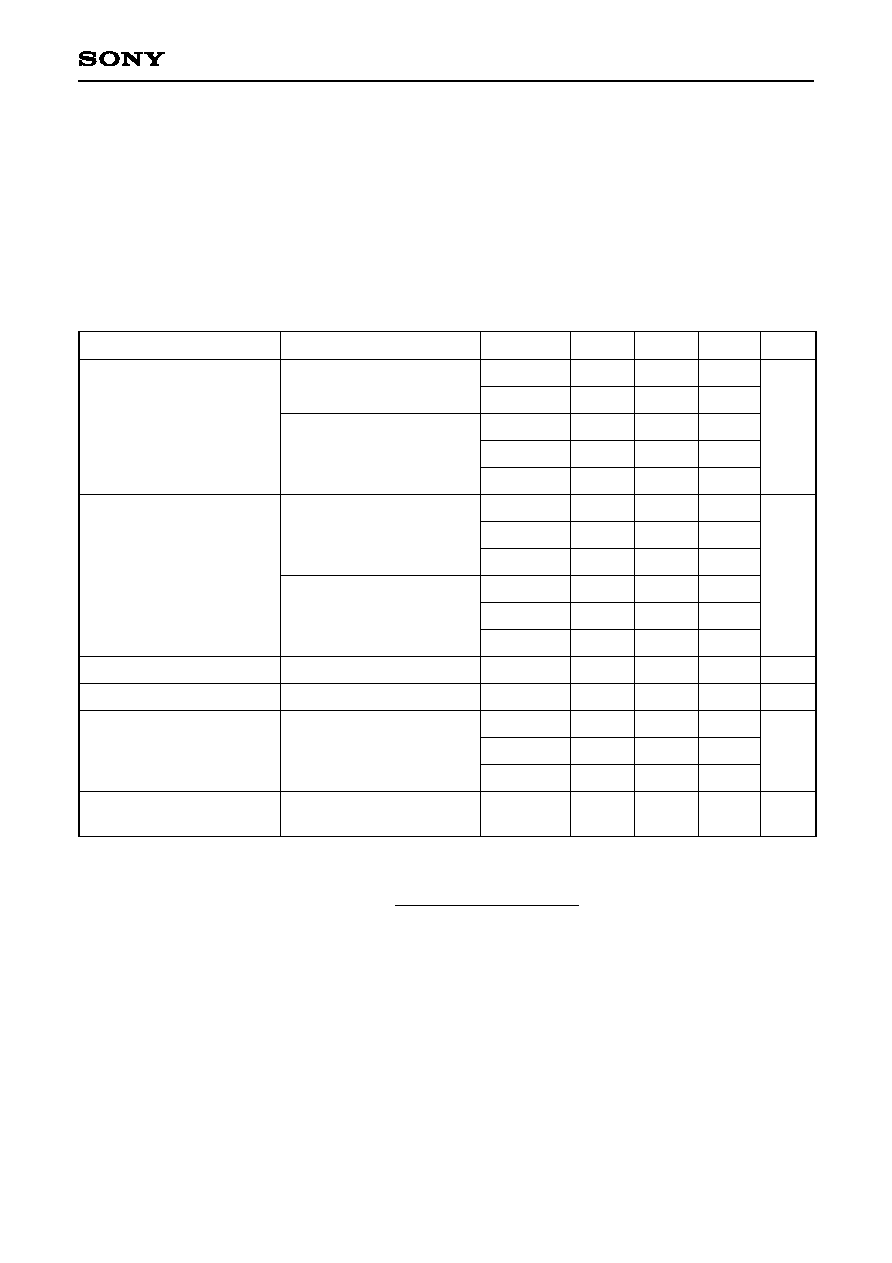

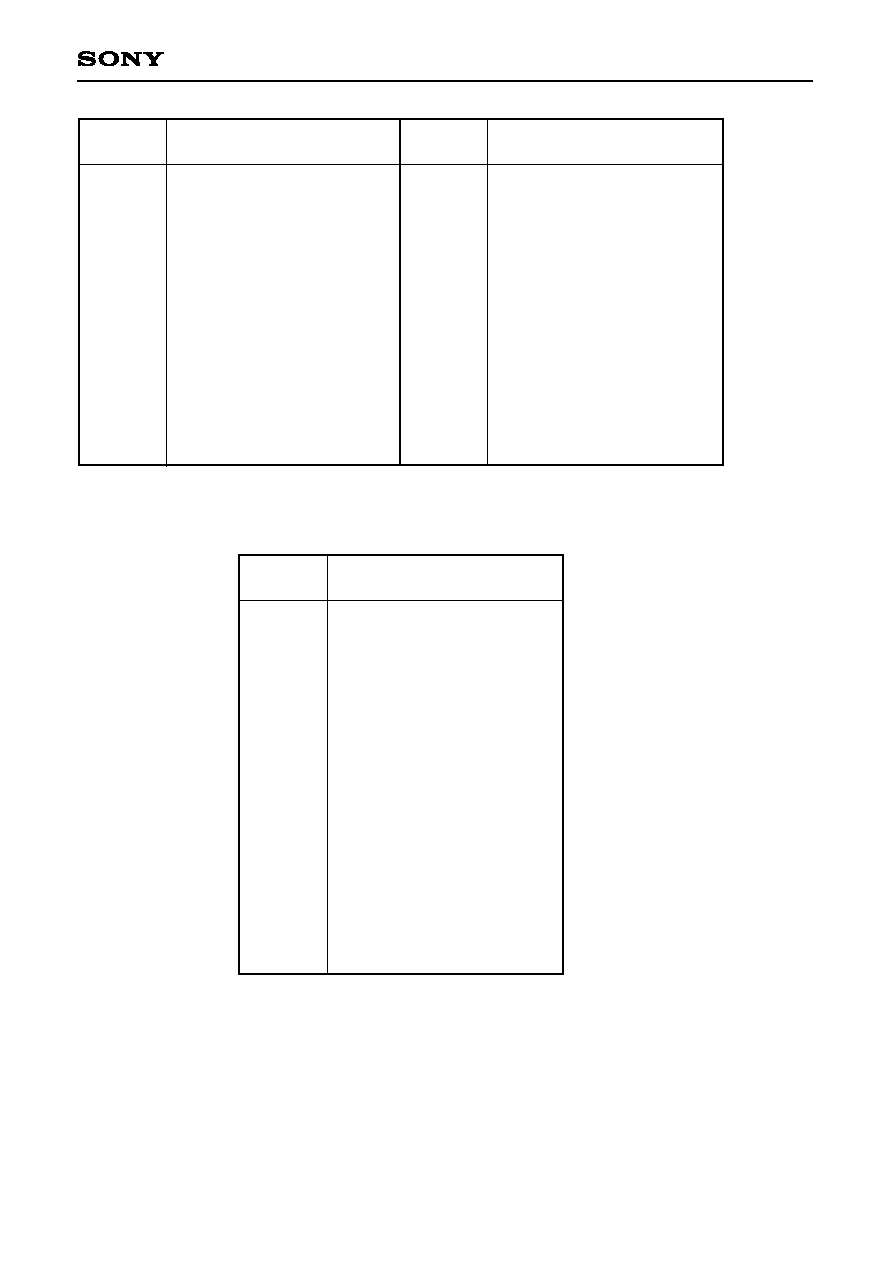

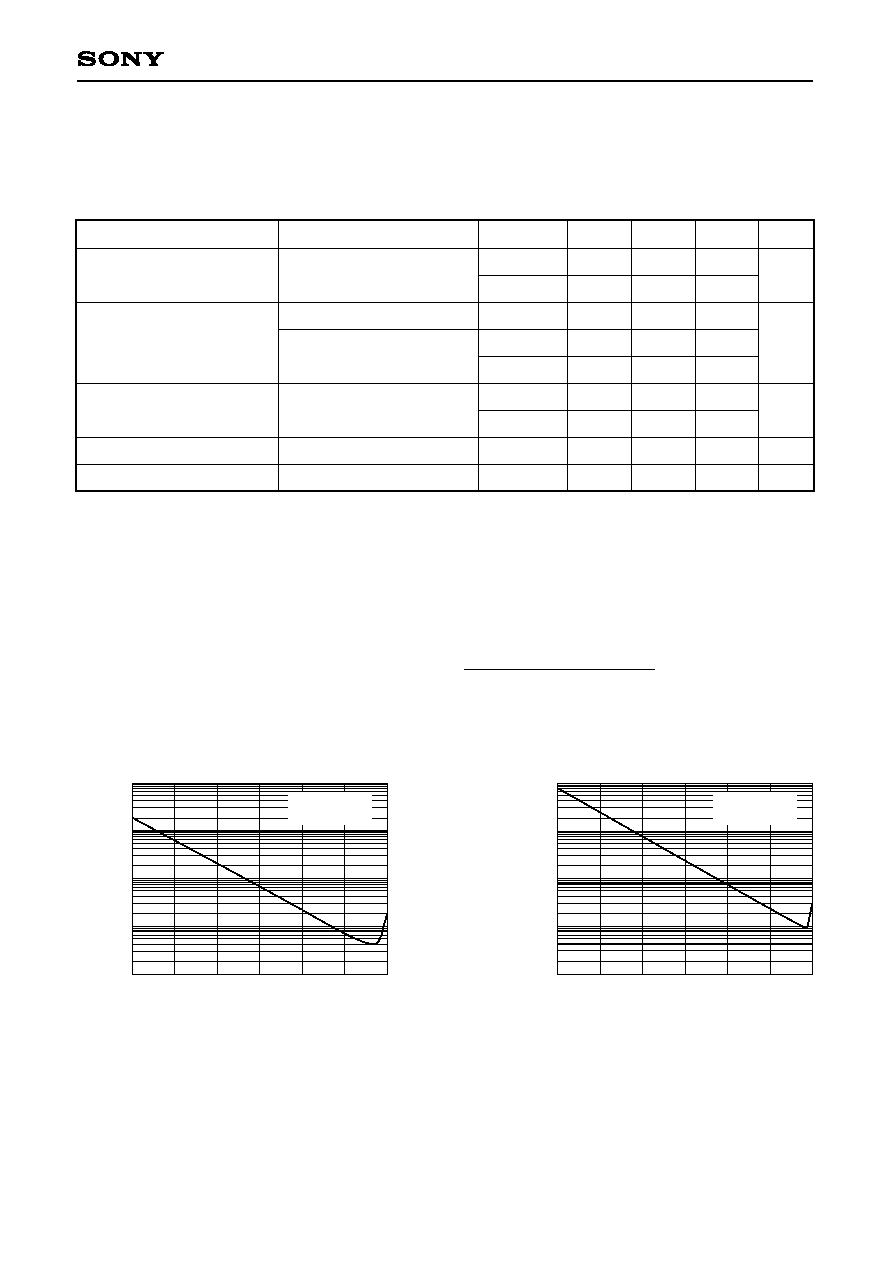

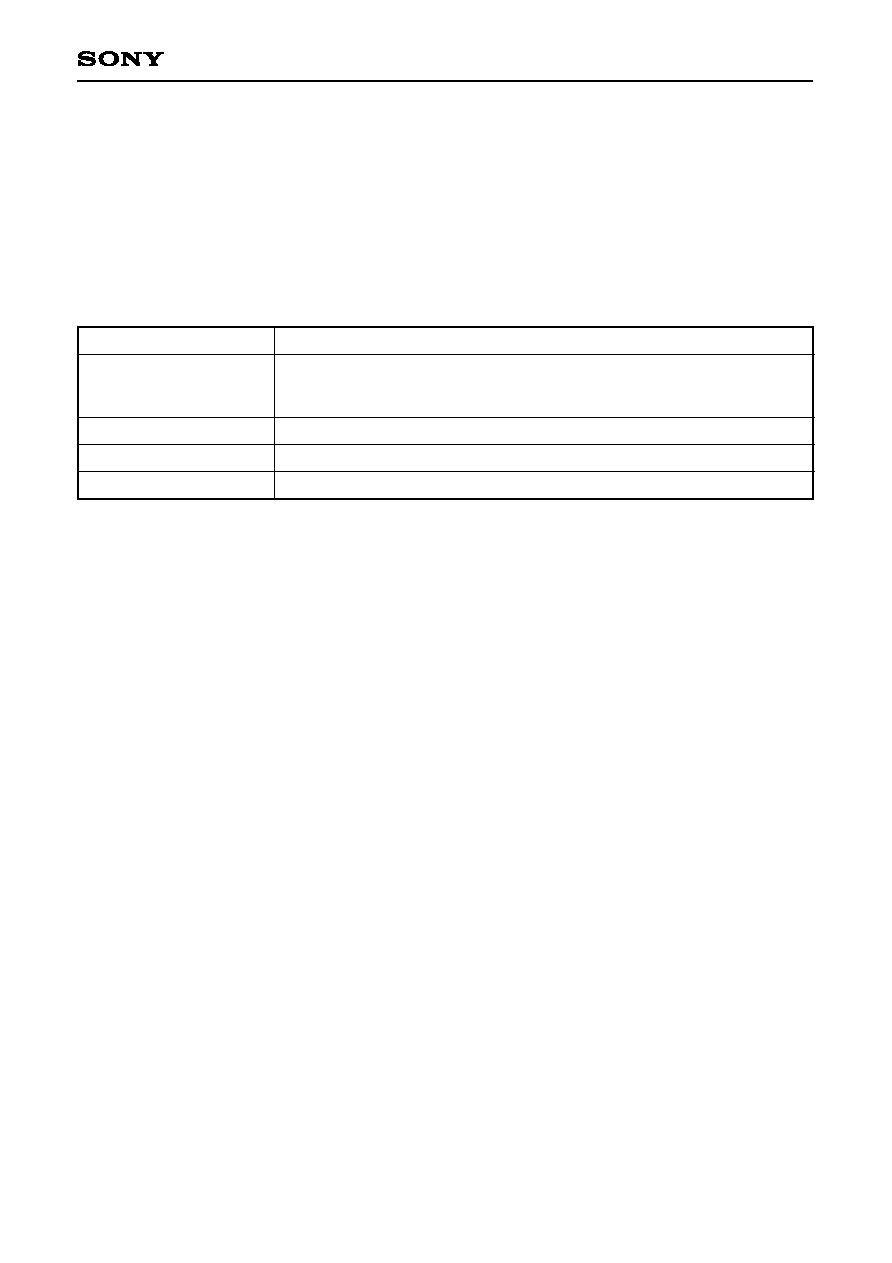

1-2. When Pro Logic mode is off

Unless otherwise specified, the measurement conditions are as given below.

∑ V

IN

(L, R, C, S) = 2.0Vrms (= 0dB)

∑ f

IN

= 1kHz

L, R

C, S

(all)

L, R

C, S

L, R

C, S

(all)

(all)

1.7

97

90

0.03

0.004

0.01

93

83

1.33

1.85

1.00

2.0

dB

%

dB

Vrms

Vrms

S/N ratio

THD + N

11

Dynamic range

12

ADC maximum input level

13

Output level

14

EIAJ

(with "A" weighting filter)

EIAJ (0dB)

EIAJ (≠3dB)

EIAJ (≠60dB)

(Full-scale output)

11

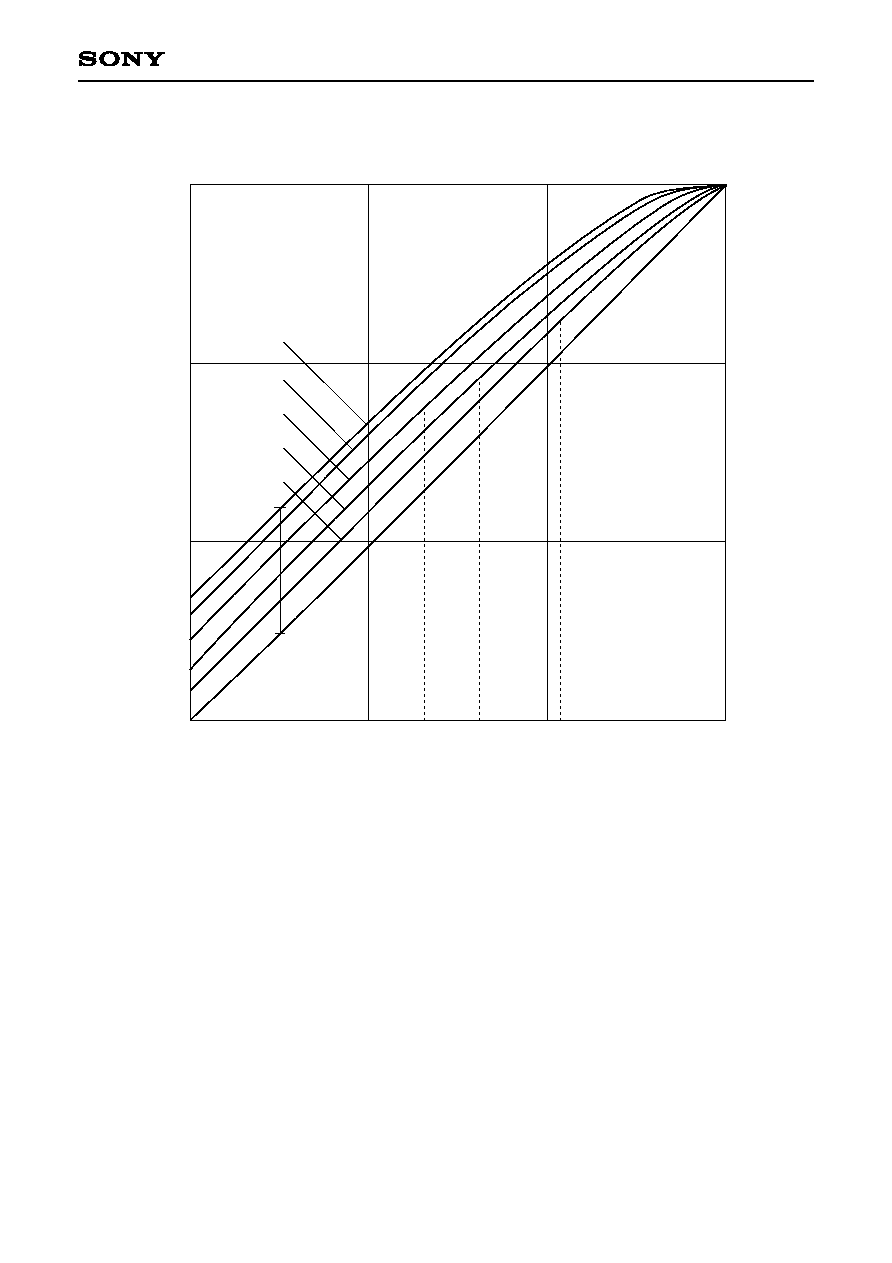

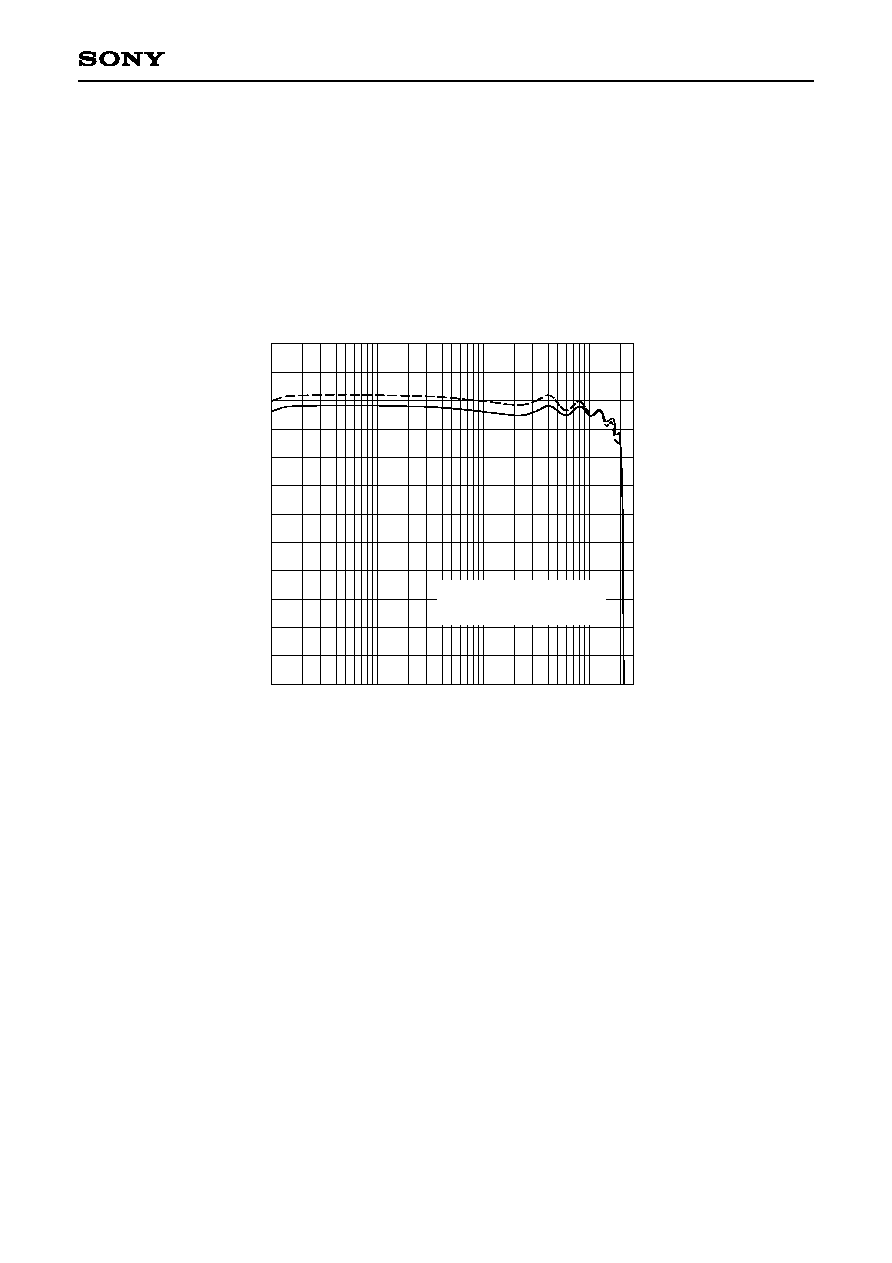

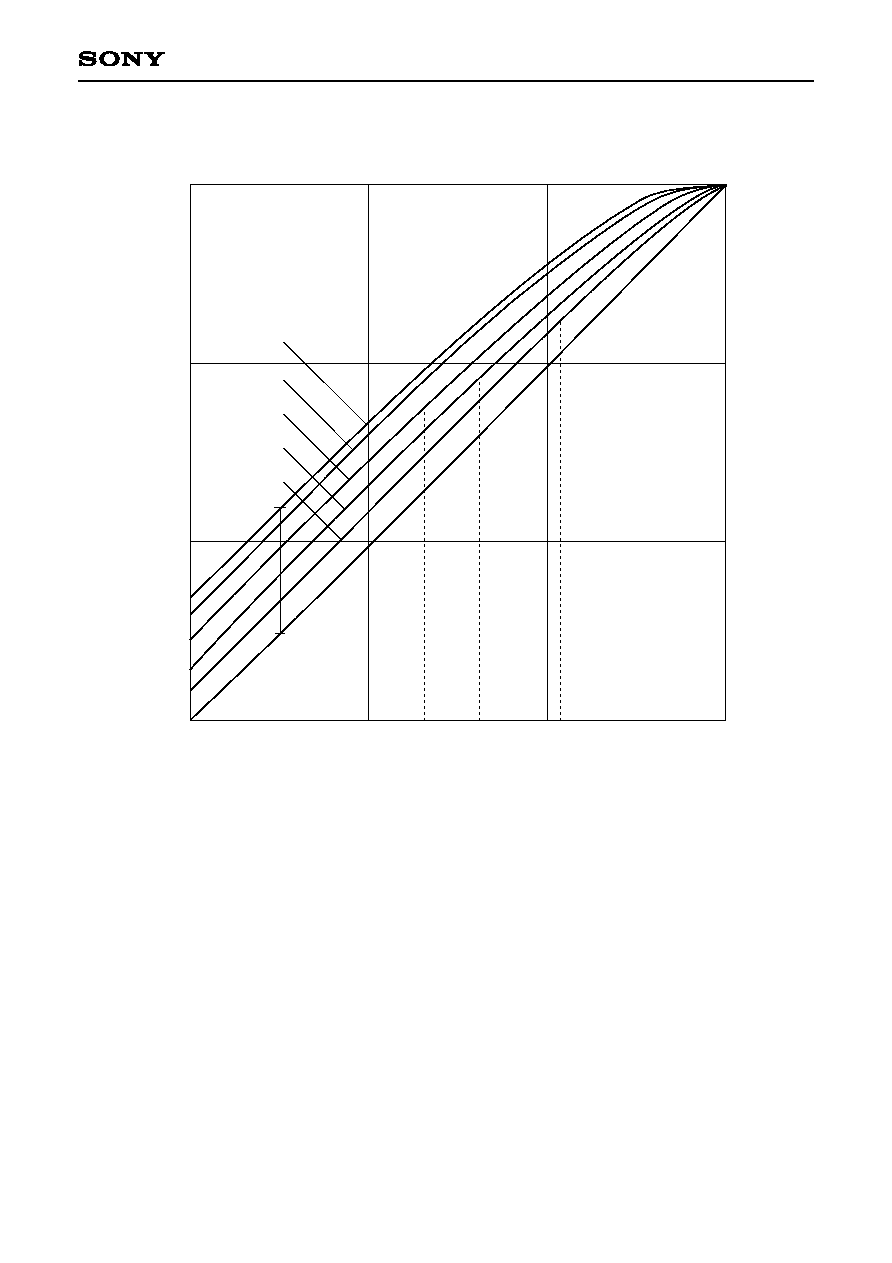

See Graphs 1a and 1b.

12

THD + N during ≠60 dB input

13

The analog input level at which the ADC outputs full scale varies according to supply voltage AVDn.

When supply voltage AVDn contains deviation, calculate the maximum input level from (Formula 1) below

and adjust the level with the ADC front-end prefilter, etc., so that the waveform is not clipped at the

minimum voltage.

ADC maximum input level [Vrms] = 1.33 [Vrms]

◊

(Formula 1)

14

Like the ADC, the DAC conversion gain also varies according to supply voltage AVDn. However, the DAC

has the reverse characteristics of the ADC, so the total gain between the ADC and DAC is constant.

Minimum supply voltage [V]

5.0 [V]

≠60

≠50

≠40

≠30

≠20

≠10

0

0.001

0.01

0.1

1

10

Graph 1a. L, R Channel Characteristics

Analog input level [dB]

T

H

D

+

N

[

%

]

0dB = 2Vrms

fin = 1kHz

≠60

≠50

≠40

≠30

≠20

≠10

0

0.001

0.01

0.1

1

10

Graph 1b. C, S Channel Characteristics

Analog input level [dB]

T

H

D

+

N

[

%

]

0dB = 2Vrms

fin = 1kHz

Channels

Min.

Typ.

Max.

Unit

Item

Measurement conditions

≠ 10 ≠

CXD2719Q

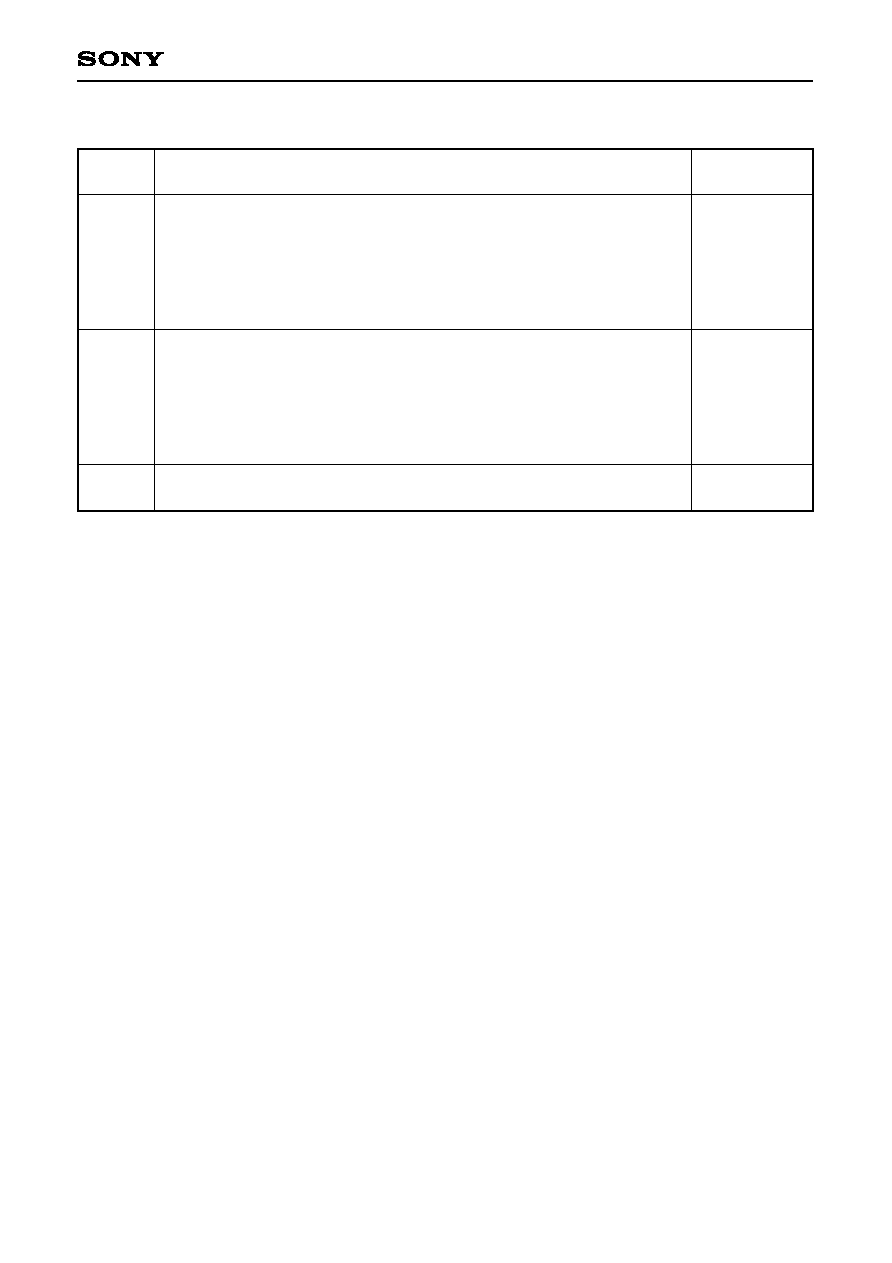

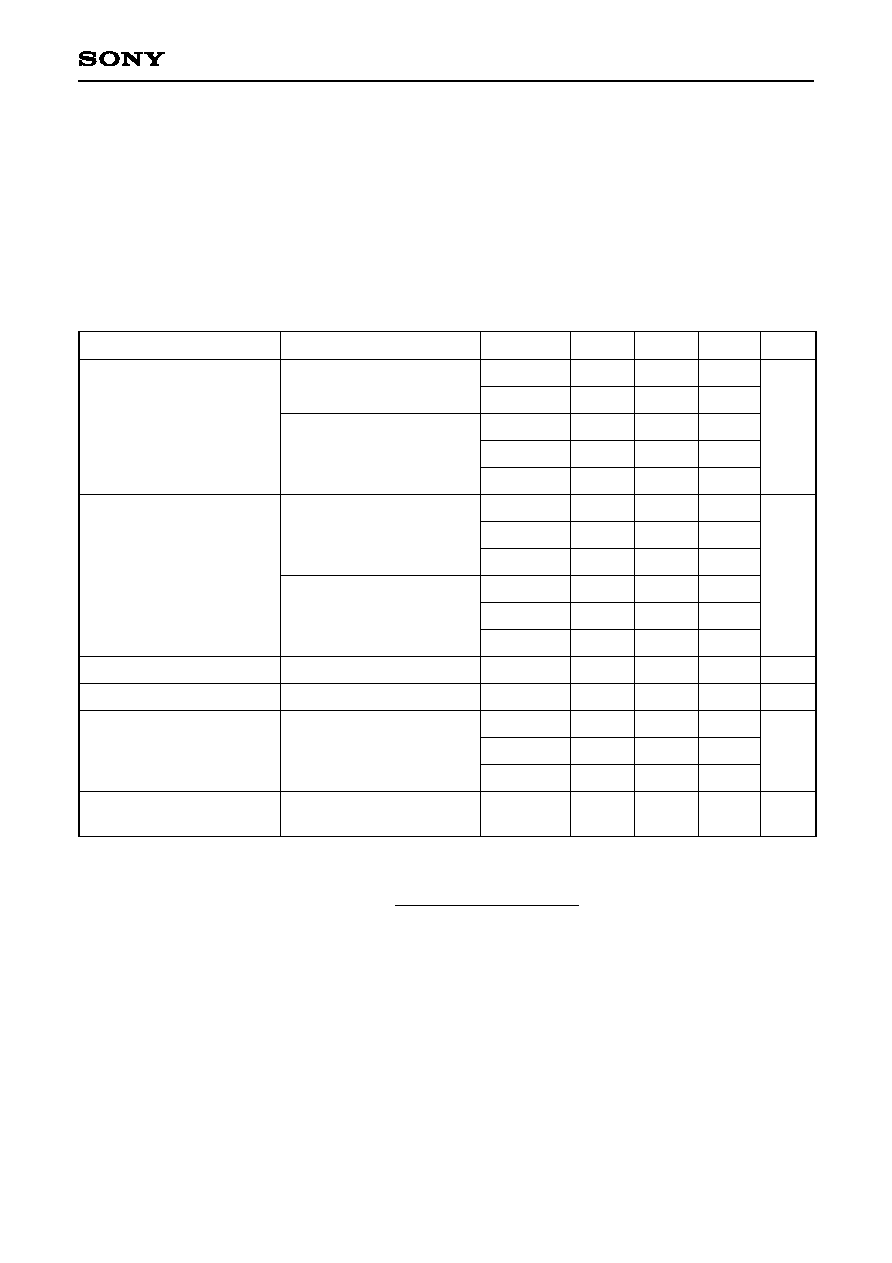

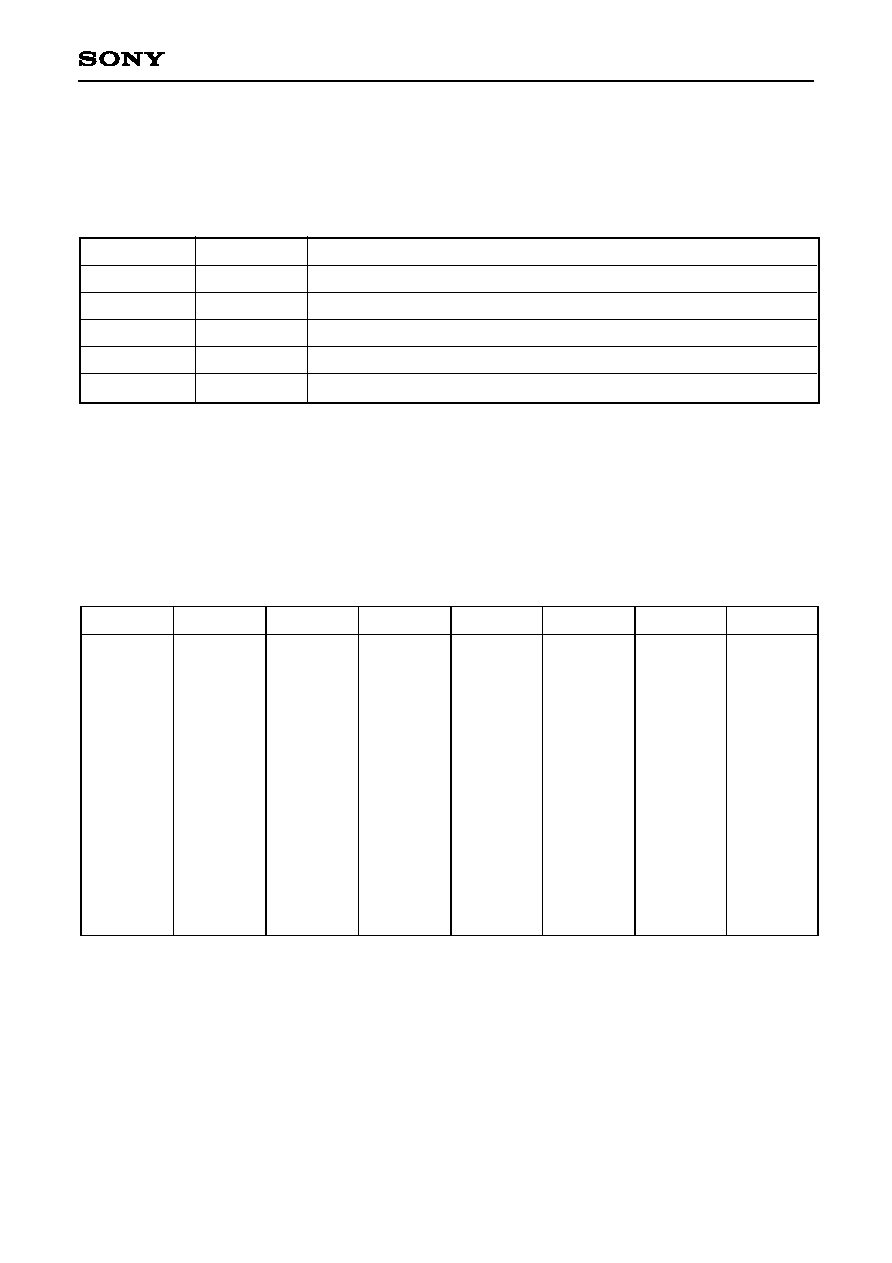

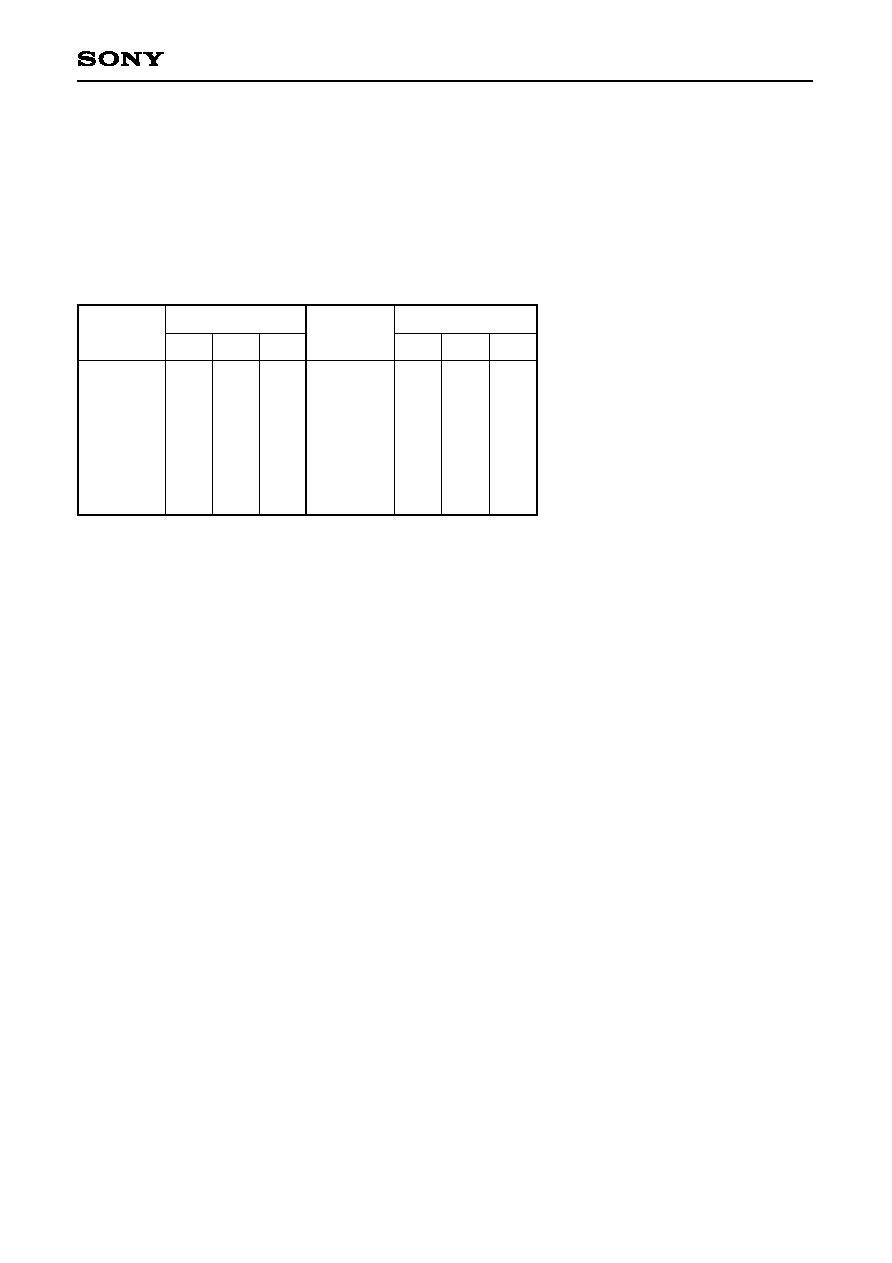

2. DAC Characteristics

In addition to the DAC, these characteristics include the built-in post filter and trim volume. Use the digital input

and analog output circuits in the Application Circuit for the measurement circuit.

2-1. When Pro Logic mode is on

Unless otherwise specified, the measurement conditions are as given below.

∑ Digital data = ≠20dBFS

∑ f

IN

= 3kHz

Channels

L, R

C, S

L, R

C

S

L, R

C

S

L, R

C

S

L, R-in

C-in

S-in

(all)

Min.

Typ.

77

68

60

52

65

0.05

0.08

0.06

0.15

0.3

0.08

≠20

200

62

87

79

±0.2

Max.

Unit

dB

%

dBFS

mVrms

dB

dB

Item

S/N ratio

THD + N

Dolby level

Output level

31

Matrix rejection

Level difference between

channels

Measurement conditions

CCIR/ARM filter

Data = ≠20dBFS

10Hz to 500kHz

Data = ≠20dBFS

10Hz to 20kHz

Data = ≠20dBFS

10Hz to 500kHz

Data = ≠20dBFS

Data = ≠20dBFS

f

IN

= 3kHz

31

The output level depends on supply voltage AVDn as shown in (Formula 2) below.

Output level [mVrms] = 285 [mVrms]

◊

(Formula 2)

Supply voltage AVDn [V]

5.0 [V]

≠ 11 ≠

CXD2719Q

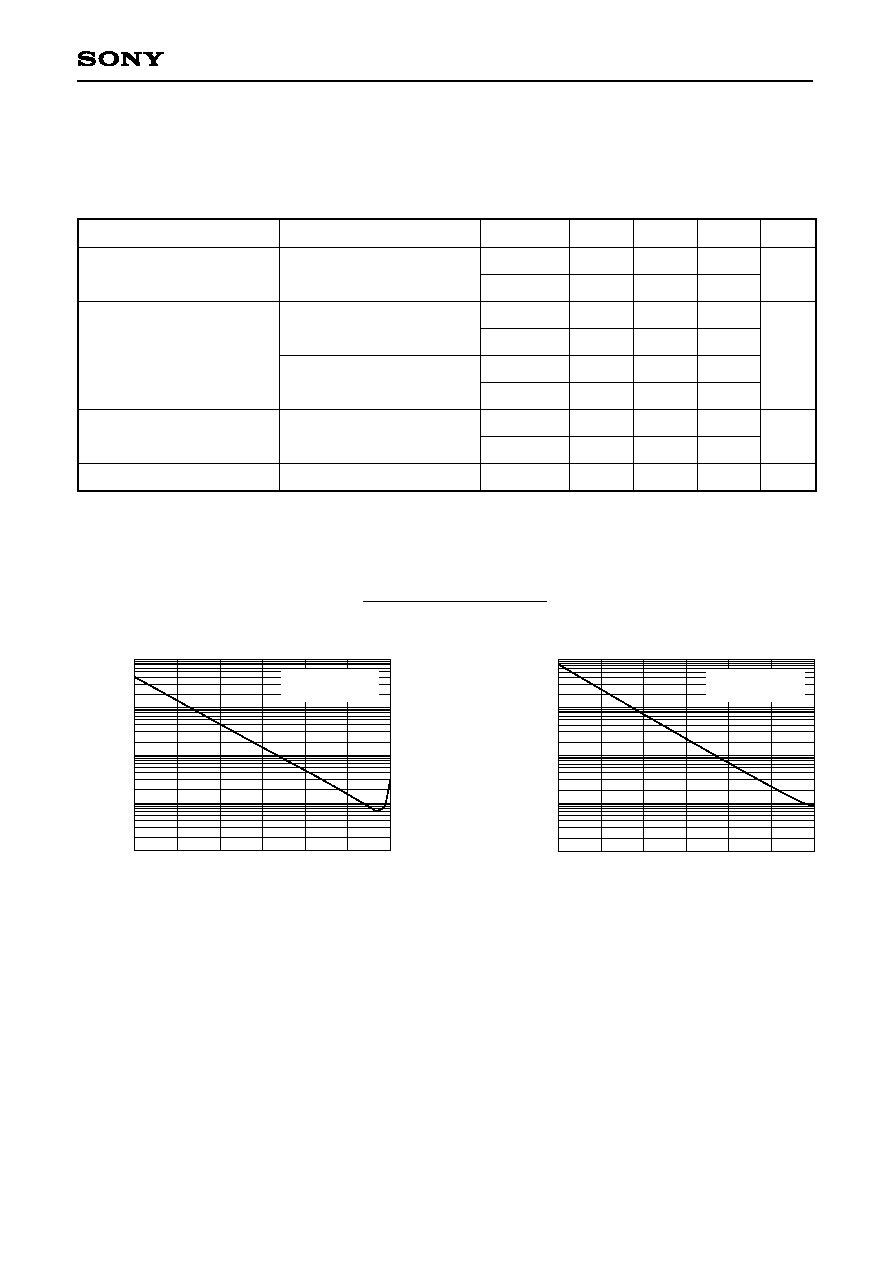

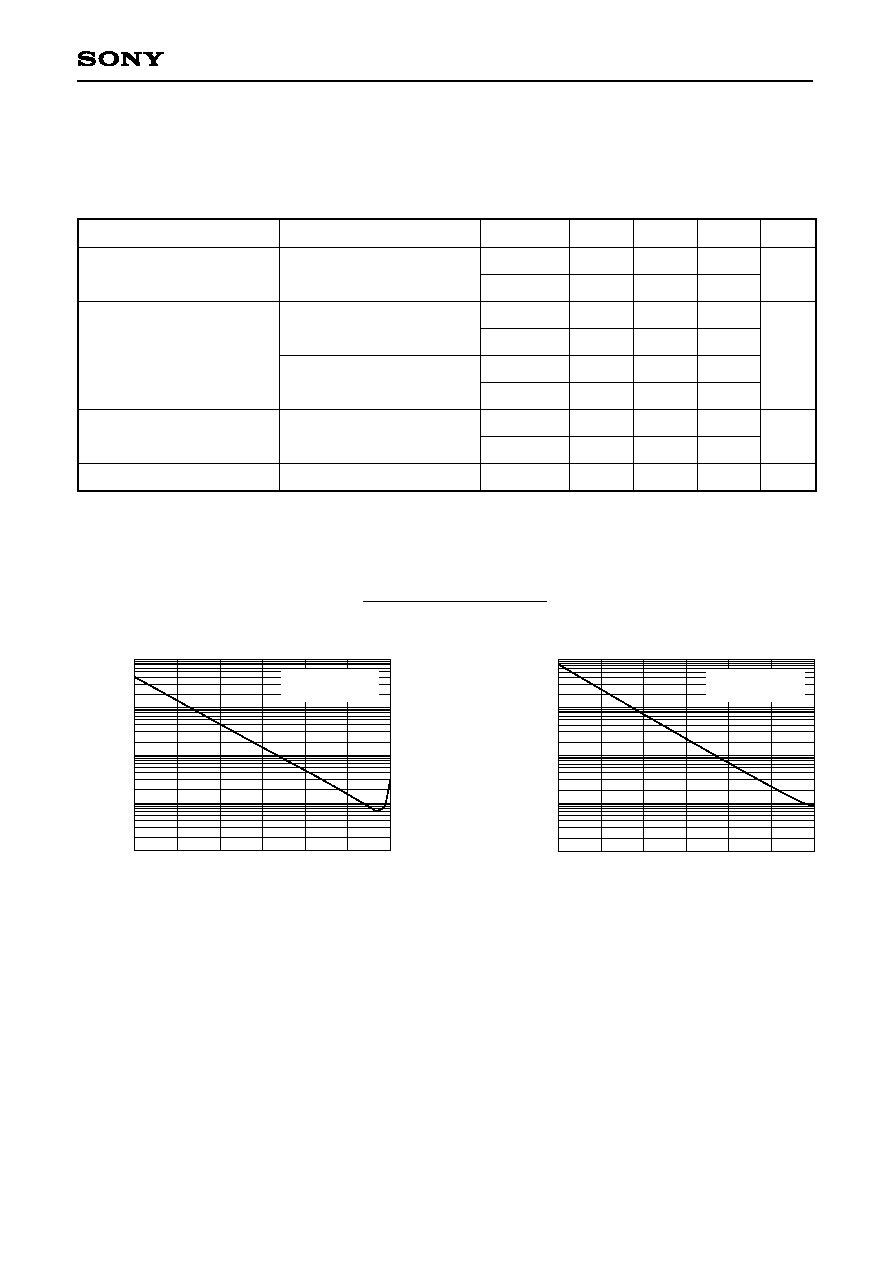

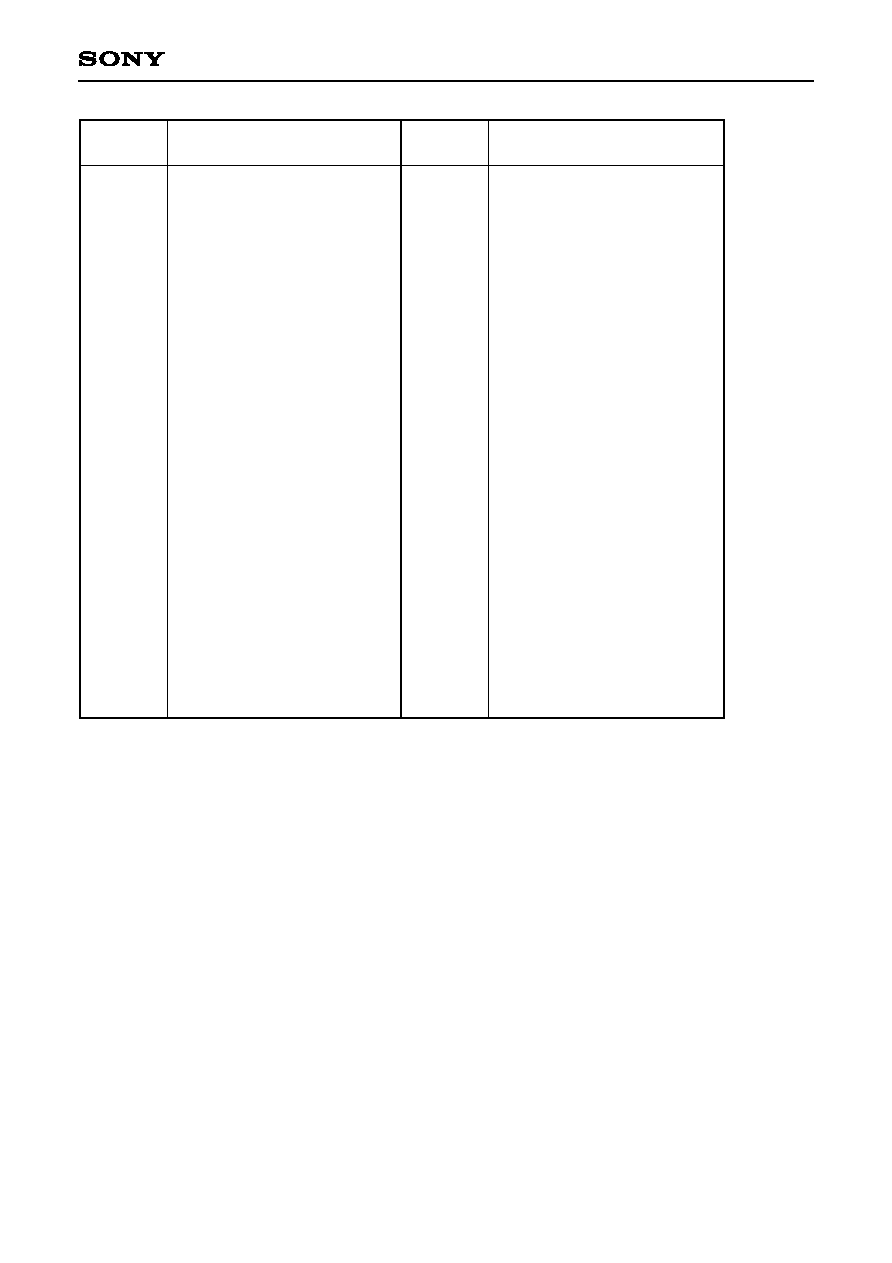

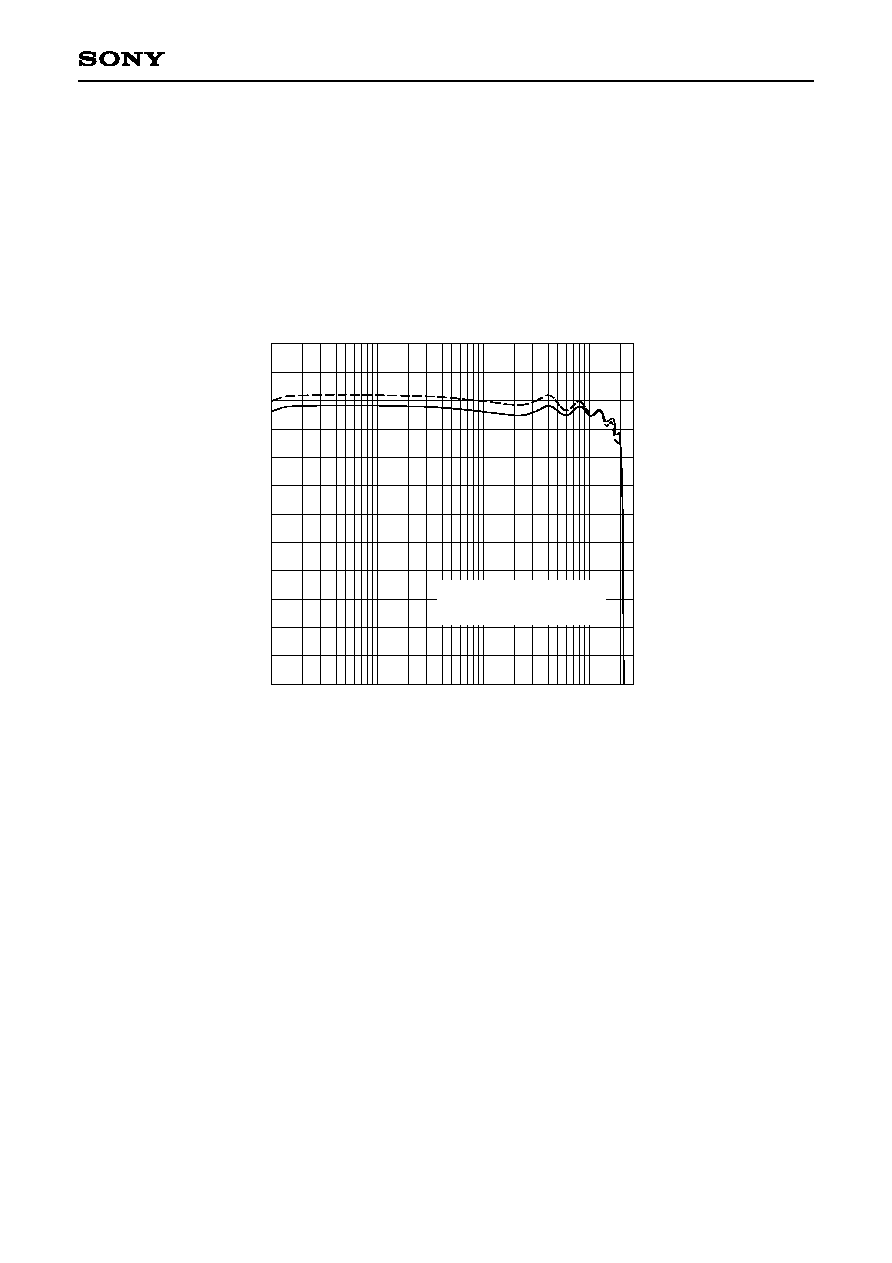

2-2. When Pro Logic mode is off

Unless otherwise specified, the measurement conditions are as given below.

∑ Digital data = Full scale (0dBFS)

∑ f

IN

= 1kHz

Channels

L, R

C, S

L, R

C, S

L, R

C, S

L, R

C, S

(all)

Min.

Typ.

100

91

0.03

0.007

0.007

0.01

87

83

2.0

Max.

Unit

dB

%

dB

Vrms

Item

S/N ratio

THD + N

41

Dynamic range

42

Output level

43

Measurement conditions

EIAJ

(with "A" weighting filter)

EIAJ (0dB)

EIAJ (≠3dB)

EIAJ (≠60dB)

41

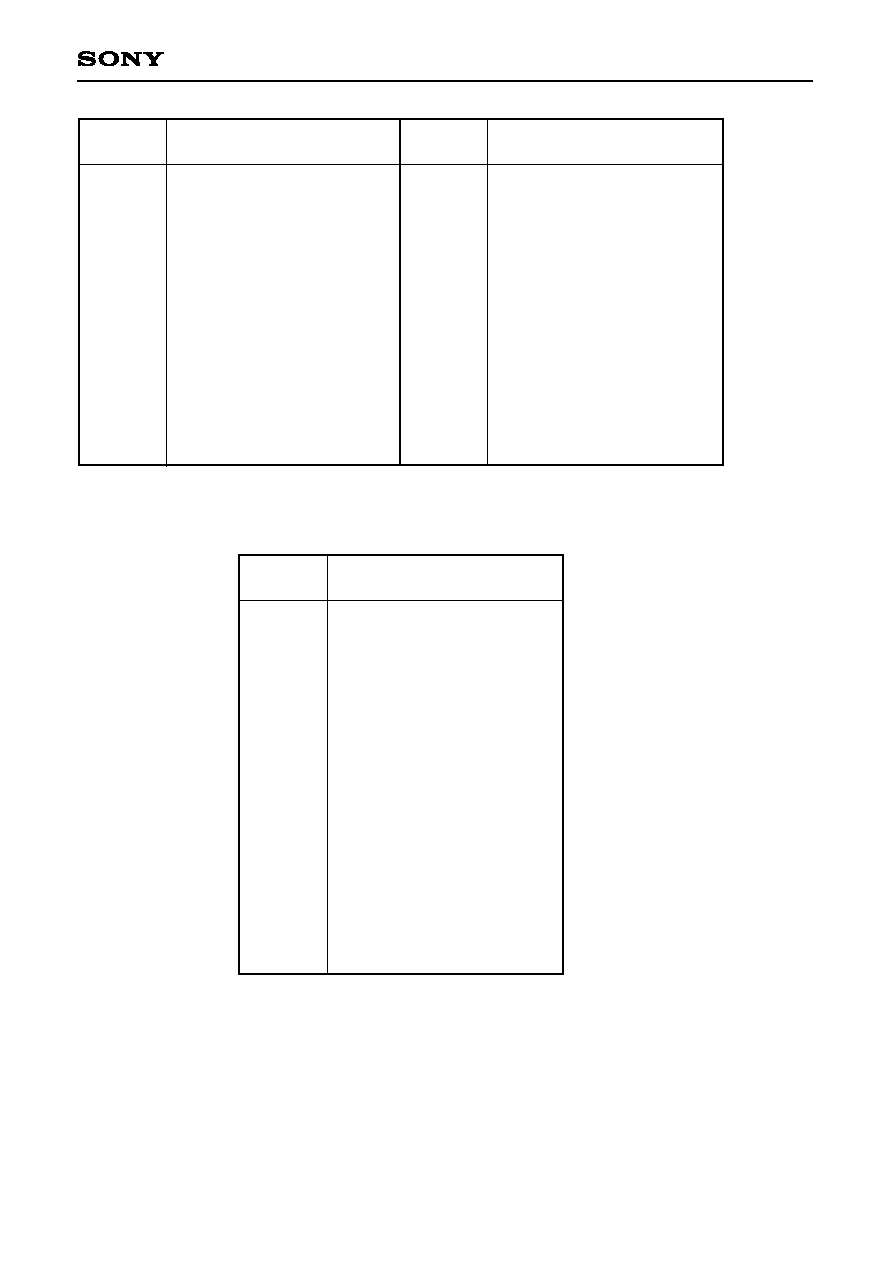

See Graphs 2a and 2b.

42

THD + N during ≠60dB input

43

The output level depends on supply voltage AVDn as shown in (Formula 3) below.

Output level [Vrms] = 1.9 [Vrms]

◊

(Formula 3)

Supply voltage AVDn [V]

5.0 [V]

≠60

≠50

≠40

≠30

≠20

≠10

0

0.001

0.01

0.1

1

10

Graph 2b. C, S Channel Characteristics

Digital input level [dB]

T

H

D

+

N

[

%

]

0dB = Full scale

fin = 1kHz

≠60

≠50

≠40

≠30

≠20

≠10

0

0.001

0.01

0.1

1

10

Graph 2a. L, R Channel Characteristics

T

H

D

+

N

[

%

]

Digital input level [dB]

0dB = Full scale

fin = 1kHz

≠ 12 ≠

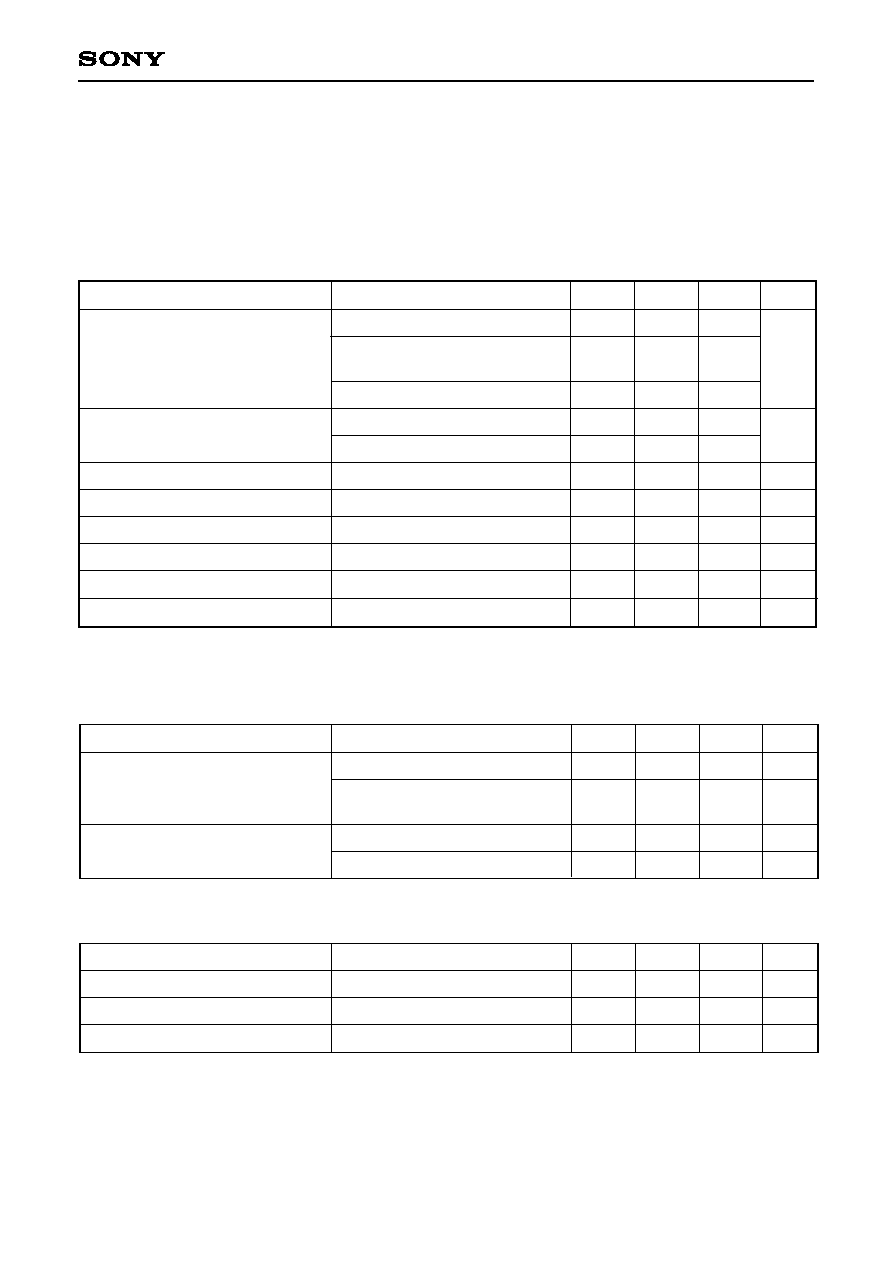

CXD2719Q

3. Bypass Mode Characteristics (L, R channels only)

These are the characteristics without passing through the DSP, and including the prefilter with built-in

operational amplifier and the built-in post filter. Use the analog I/O circuits in the Application Circuit for the

measurement circuit. Unless otherwise specified, the measurement conditions are as given below.

∑ f

IN

= 1kHz

∑ V

IN

(L, R) = 2.0Vrms (= 0dB)

Min.

Typ.

97

100

80

0.008

0.005

95

2.5

2.0

±0.2

105

7.5

Max.

Unit

dB

%

dB

Vrms

Vrms

dB

dB

dB

Item

S/N ratio

THD + N

Dynamic range

51

Maximum input level

Output level

Level difference between channels

Channel separation

Power supply rejection ratio

52

Measurement conditions

CCIR/ARM filter

10Hz to 20kHz, "A" weighting filter

10Hz to 500kHz

10Hz to 500kHz

10Hz to 20kHz

10Hz to 20kHz, V

IN

= ≠60dB

THD + N = 0.05%

1mVrms, 100Hz sine wave

Min.

10

10

Typ.

104

Max.

20

Unit

k

dB

k

kHz

Item

Prefilter

Post filter

Measurement conditions

Feedback resistance value

Maximum amplification rate

(100kHz or less)

Load resistance value

Cut-off frequency (= fc)

Min.

Typ.

1.5

≠29.5

1.0

Max.

Unit

dB

dB

dB

Item

Maximum gain

Minimum gain

Variable step

Symbol

TRIMmax

TRIMmin

TRIMstep

51

THD + N during ≠60dB input

52

Includes the amplification (5.27dB) of the external amplifier.

4. Filter Characteristics

5. Trim Volume Characteristics

≠ 13 ≠

CXD2719Q

Description of Functions

1. Master/Slave Modes

[Relevant pins] XMST, LRCK, BCK

When using the CXD2719Q alone without digital input, set the CXD2719Q to master mode.

When using digital input, the CXD2719Q may be set to either master mode or slave mode.

The clock applied to LRCK and BCK in slave mode must be synchronized to either the crystal oscillator clock

of the XTLI and XTLO pins or the external clock input from the XTLI pin.

Table 1-1. LRCK, BCK Mode Setting

XMST

H

L

Mode

Slave mode

Master mode

LRCK, BCK I/O

Input

Output

SQC05

0

0

1

1

SQC04

0

1

0

1

BFOT

384fs

256fs

512fs

768fs

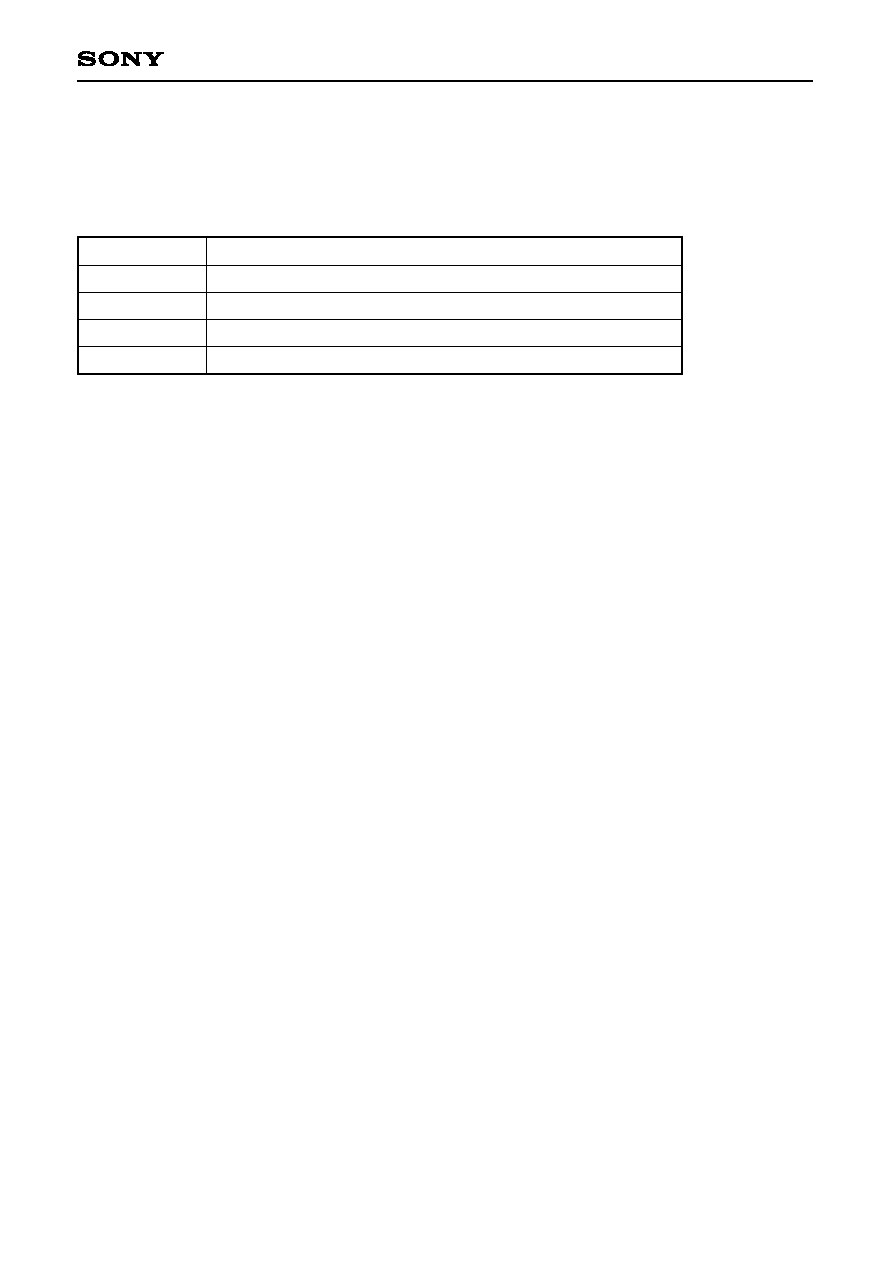

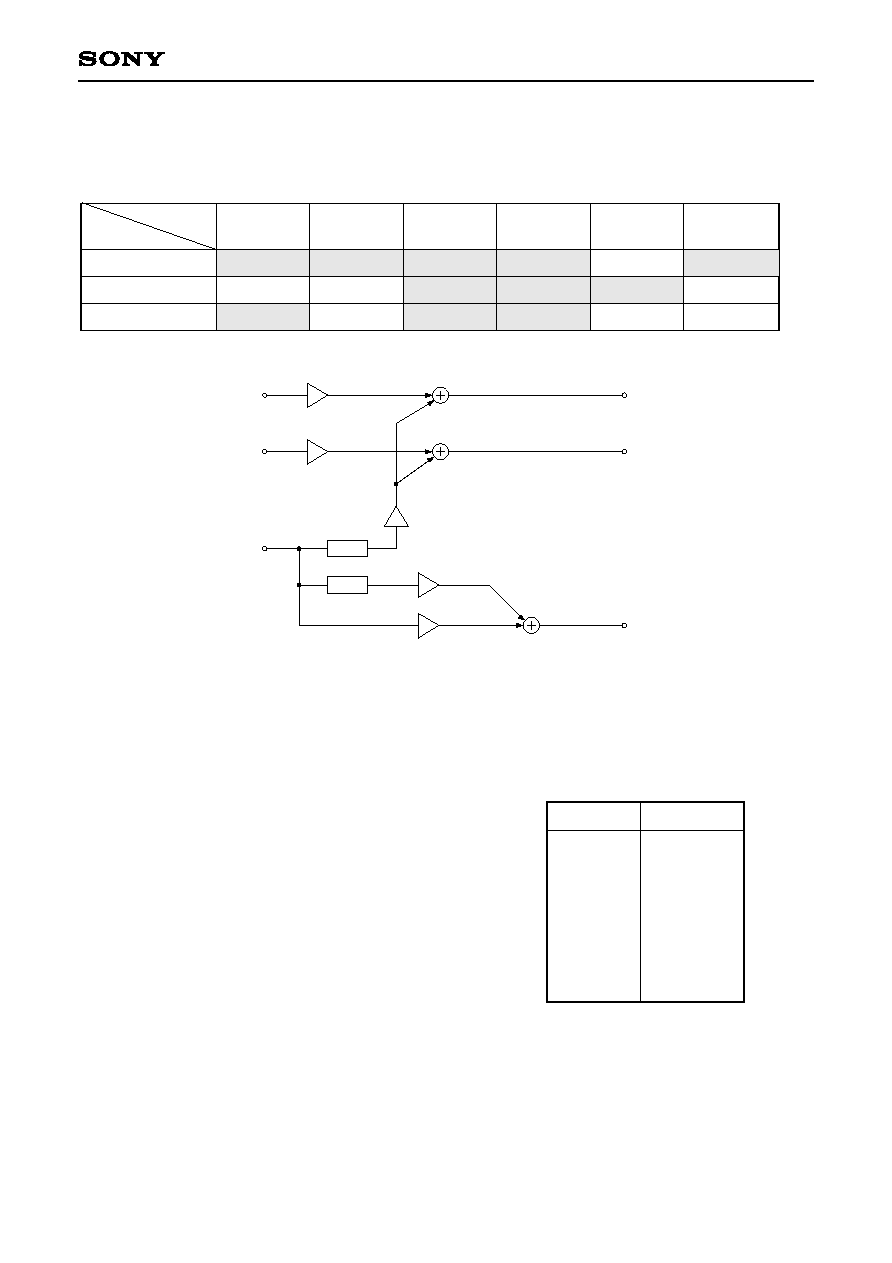

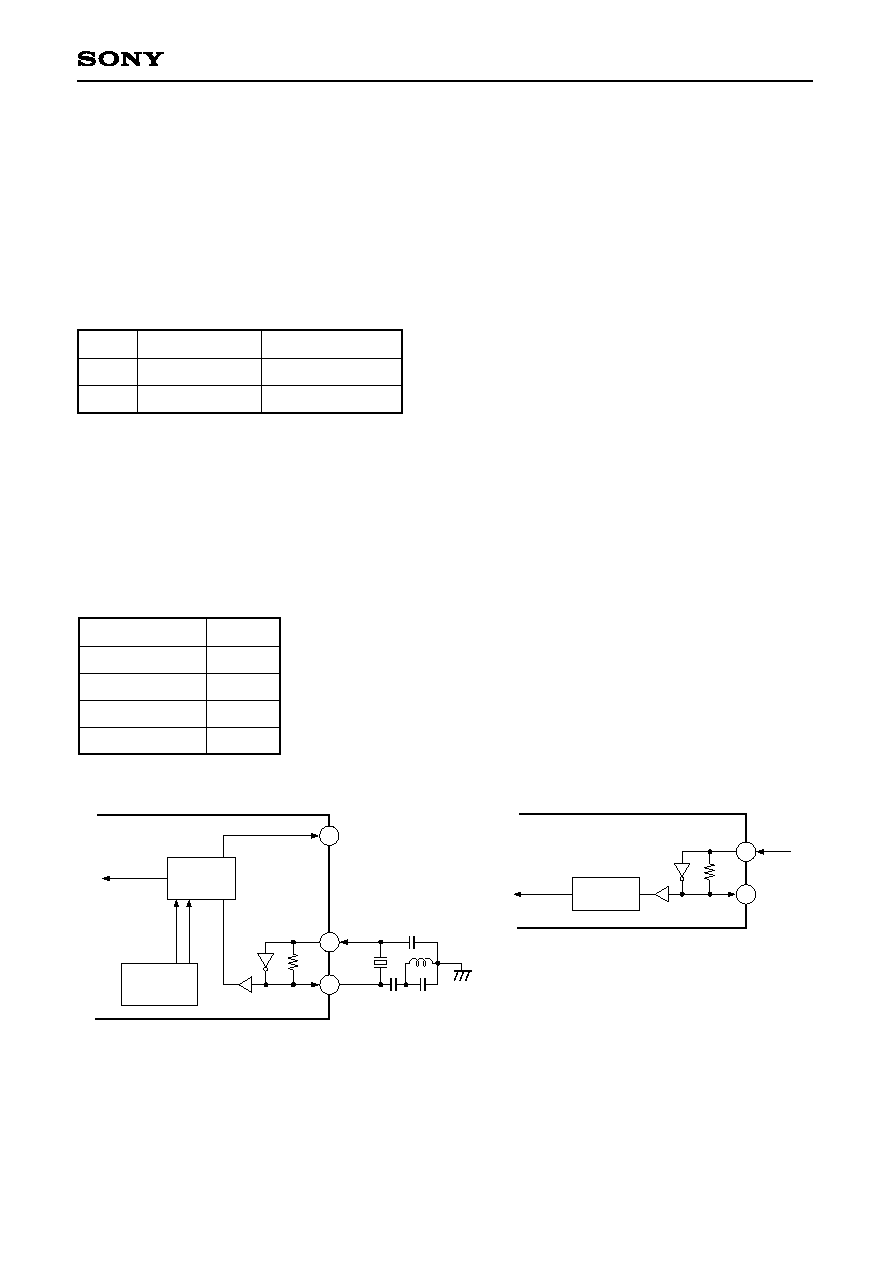

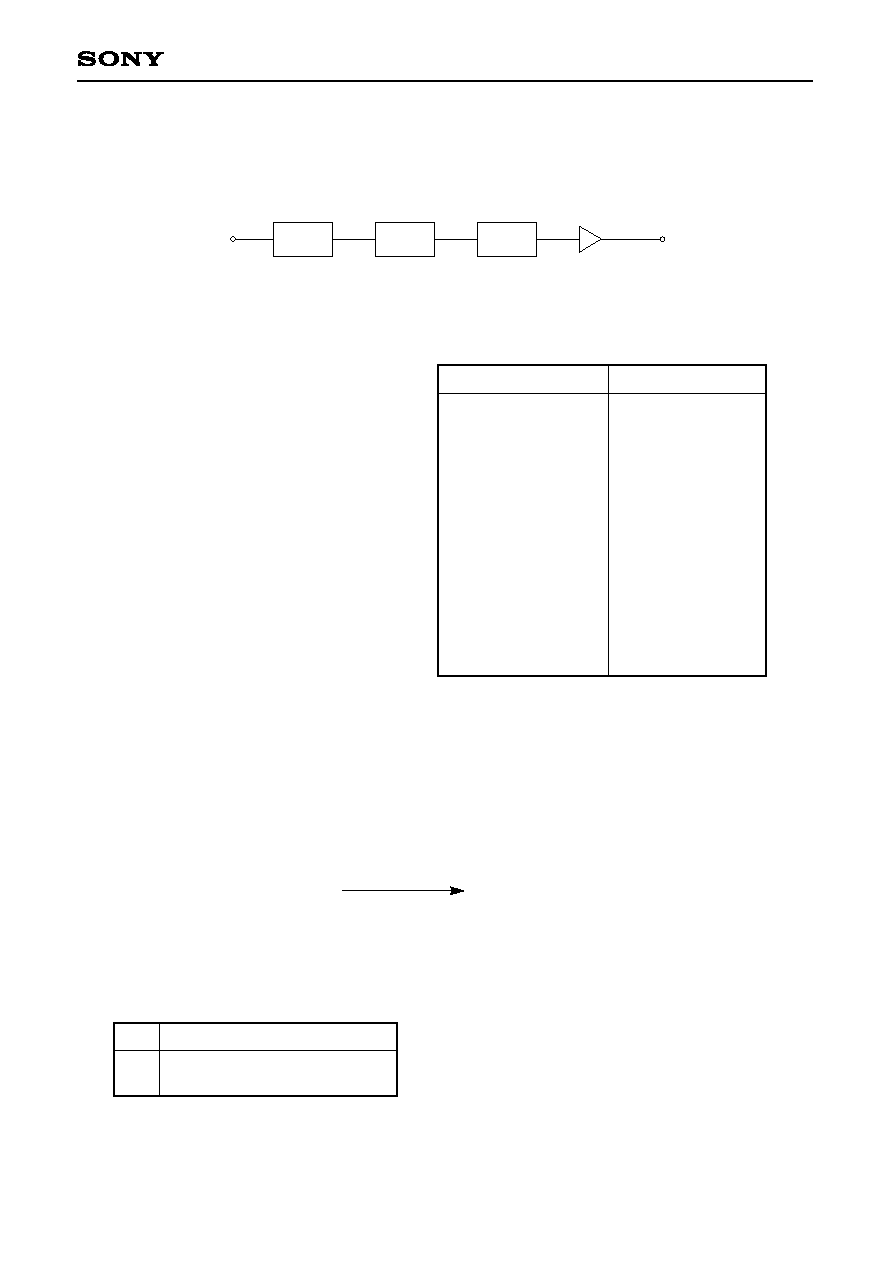

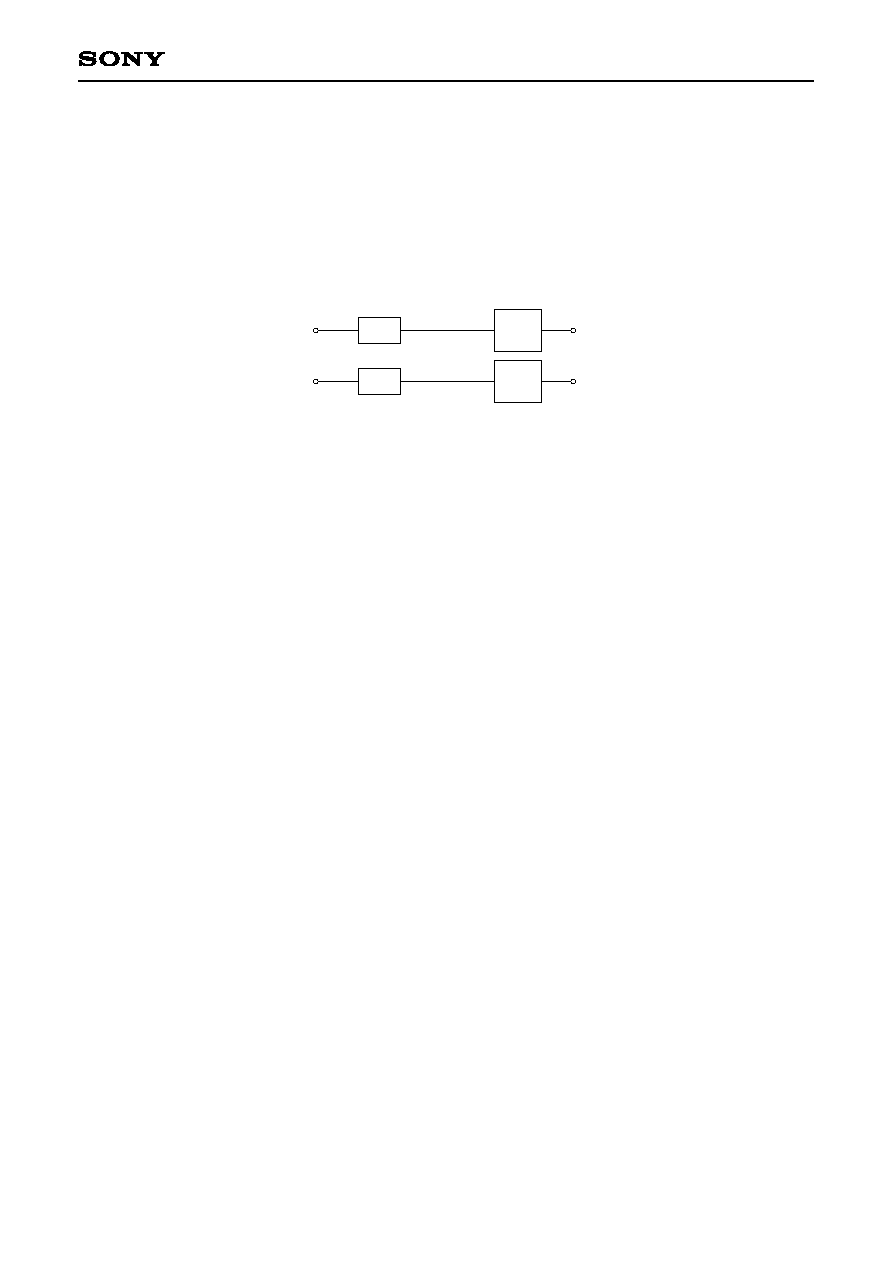

2. Master Clock System

[Relevant pins] XTLI, XTLO, BFOT

768fs (fs = 32 to 44.1kHz) is assumed for the master clock system, and the connection is as shown below.

BFOT outputs the clock obtained by frequency dividing the master clock. The frequency division ratio can be

changed by the setup register (SQC04, SQC05). (See "6. Setup Register".)

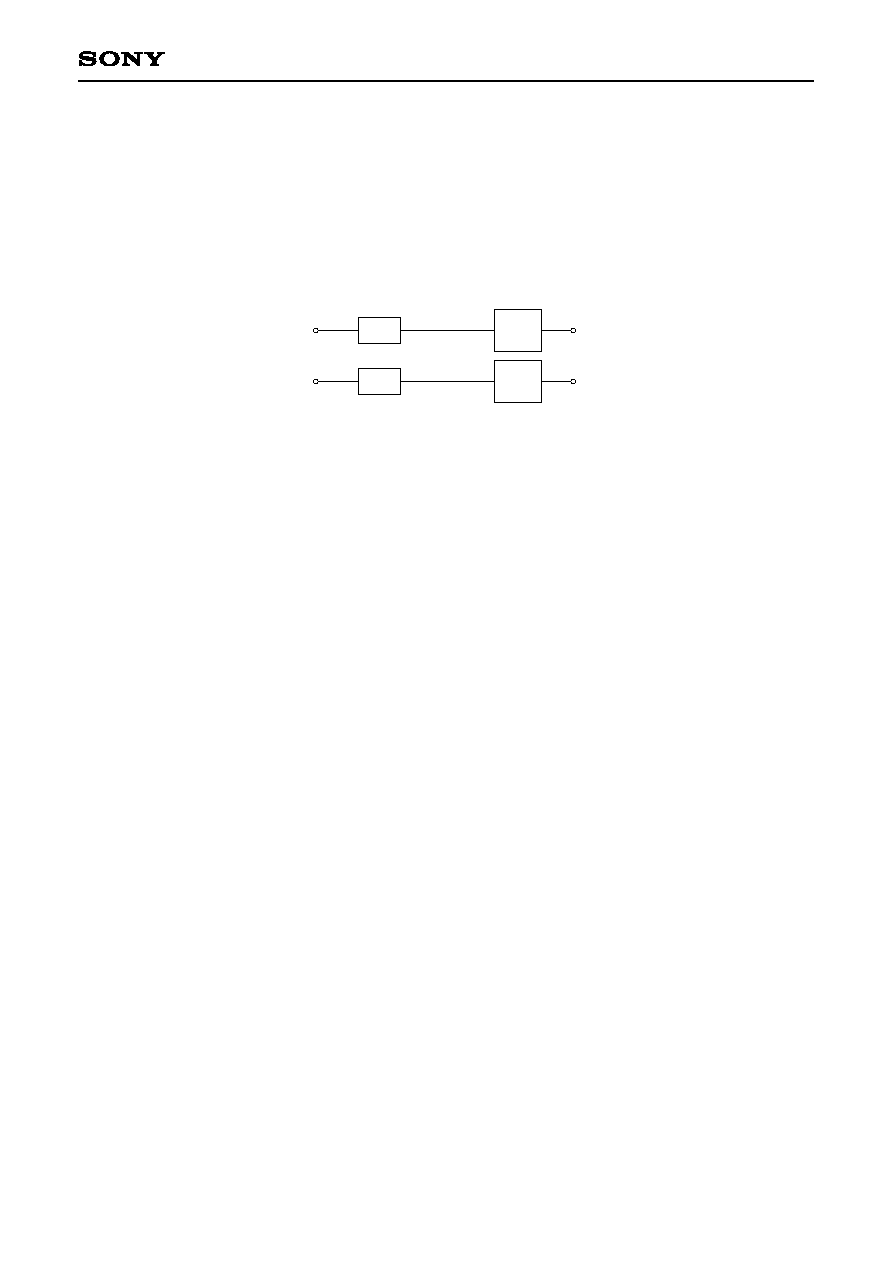

(1) Master

(2) Slave

O

I

O

Frequency

divider

Setup

Register

512fs

XTLI

XTLO

768fs

BFOT

256fs/384fs/512fs/768fs

O

512fs

XTLI

XTLO

768fs

I

OPEN

Frequency

divider

Fig. 2-1.

Note) Oscillation circuits may differ according to peripheral circuit and

substrate. Consult with crystal oscillator manufacturers about the

selecting oscillation circuits.

≠ 14 ≠

CXD2719Q

3. Reset Circuit

[Relevant pins] XRST, XTLI, XTLO

This LSI must be reset after the power is turned on.

Reset is done by setting the XRST pin Low for 1/fs or more after the supply voltage satisfies the recommended

operating condition, and the crystal oscillator clock of the XTLI and XTLO pins or the external clock input from

the XTLI pin is correctly applied. (See "AC Characteristics".)

4. Serial Audio Interface (SIF)

[Relevant pins] SI, BCK, LRCK, XS24, XMST

Serial data is used for the external communication of the digital audio data. The CXD2719Q has only one input

system, and 2 channels of data are input each sampling cycle. Either the 32-bit clock mode or the 24-bit clock

mode can be selected. In master mode, the mode is fixed to the 32-bit clock mode.

(1) Pin Configuration (The pins shown in the table below are assigned to the SIF.)

Serial input; taken with synchronized to BCK.

BCK I/O; either 32-bit clock mode (64fs) or 24-bit clock mode (48fs). BCK output supports

32-bit clock mode only.

LRCK I/O (1fs).

SIO slot number (24/32) selection input. Low: 24-bit slot; High: 32-bit slot.

Valid only in slave mode. Set High in master mode.

Do not switch between High and Low during DSP operation.

BCK, LRCK master mode/slave mode switching input.

Low: master mode; High: slave mode.

Symbol

SI

BCK

LRCK

XS24

XMST

I/O

Function

I

I/O

I/O

I

I

"0": normal,

"1": IIS

"0": Lch "H", "1": Lch "L"

"0": edge

,

"1" : edge

Setup register

SQC15

SQC14

SQC13

Function

Contents

LRCK format

LRCK polarity selection

BCK polarity selection relative to LRCK edge

Valid only in slave mode. Fix to "0" in master

mode.

Table 4-1. Pin Configuration

Table 4-2. LRCK/BCK Mode Setting

(2) Operation Modes

The LRCK/BCK mode can be selected by the setup register settings as follows. (See "6. Setup Register".)

LRCK/BCK Mode Setting

≠ 15 ≠

CXD2719Q

Table 4-3. Setup Register Settings

(3) SIF Format

The serial audio interface has only one input system, and except for the slot number, the following formats can

be set by setting the setup register. The serial audio interface can also support IIS format to enable connection

to Philips and other company's devices.

The timing charts for each data format are given on the following page.

SQC12

0

0

1

1

SQC11

0

1

0

1

Data arrangement/Frontward or rearward truncation/Data word length

MSB first/Frontward truncation/24 bits

MSB first/Rearward truncation/16 bits

MSB first/Rearward truncation/18 bits

MSB first/Rearward truncation/20 bits

All formats support either the 24- or 32-bit slot in slave mode.

≠ 16 ≠

CXD2719Q

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

7

1

6

1

9

1

8

1

9

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

7

1

6

1

8

L

R

C

K

B

C

K

S

I

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

∑

M

S

B

f

i

r

s

t

2

4

b

i

t

s

f

r

o

n

t

w

a

r

d

t

r

u

n

c

a

t

i

o

n

(

S

Q

C

1

2

,

1

1

=

0

,

0

)

∑

M

S

B

f

i

r

s

t

1

6

b

i

t

s

r

e

a

r

w

a

r

d

t

r

u

n

c

a

t

i

o

n

(

S

Q

C

1

2

,

1

1

=

0

,

1

)

∑

M

S

B

f

i

r

s

t

1

8

b

i

t

s

r

e

a

r

w

a

r

d

t

r

u

n

c

a

t

i

o

n

(

S

Q

C

1

2

,

1

1

=

1

,

0

)

∑

M

S

B

f

i

r

s

t

2

0

b

i

t

s

r

e

a

r

w

a

r

d

t

r

u

n

c

a

t

i

o

n

(

S

Q

C

1

2

,

1

1

=

1

,

1

)

L

c

h

R

c

h

L

S

B

M

S

B

I

a

v

a

l

i

d

L

S

B

I

a

v

a

l

i

d

M

S

B

I

a

v

a

l

i

d

L

S

B

M

S

B

I

a

v

a

l

i

d

L

S

B

L

S

B

M

S

B

I

a

v

a

l

i

d

L

S

B

L

S

B

M

S

B

I

a

v

a

l

i

d

L

S

B

M

S

B

M

S

B

I

a

v

a

l

i

d

I

a

v

a

l

i

d

M

S

B

M

S

B

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

L

R

C

K

B

C

K

S

I

L

S

B

M

S

B

L

S

B

M

S

B

L

S

B

M

S

B

I

a

v

a

l

i

d

L

S

B

L

S

B

M

S

B

I

a

v

a

l

i

d

L

S

B

L

S

B

M

S

B

I

a

v

a

l

i

d

L

S

B

M

S

B

M

S

B

I

a

v

a

l

i

d

I

a

v

a

l

i

d

I

a

v

a

l

i

d

L

c

h

R

c

h

M

S

B

∑

M

S

B

f

i

r

s

t

2

4

b

i

t

s

(

S

Q

C

1

2

,

1

1

=

0

,

0

)

∑

M

S

B

f

i

r

s

t

1

6

b

i

t

s

r

e

a

r

w

a

r

d

t

r

u

n

c

a

t

i

o

n

(

S

Q

C

1

2

,

1

1

=

0

,

1

)

∑

M

S

B

f

i

r

s

t

1

8

b

i

t

s

r

e

a

r

w

a

r

d

t

r

u

n

c

a

t

i

o

n

(

S

Q

C

1

2

,

1

1

=

1

,

0

)

∑

M

S

B

f

i

r

s

t

2

0

b

i

t

s

r

e

a

r

w

a

r

d

t

r

u

n

c

a

t

i

o

n

(

S

Q

C

1

2

,

1

1

=

1

,

1

)

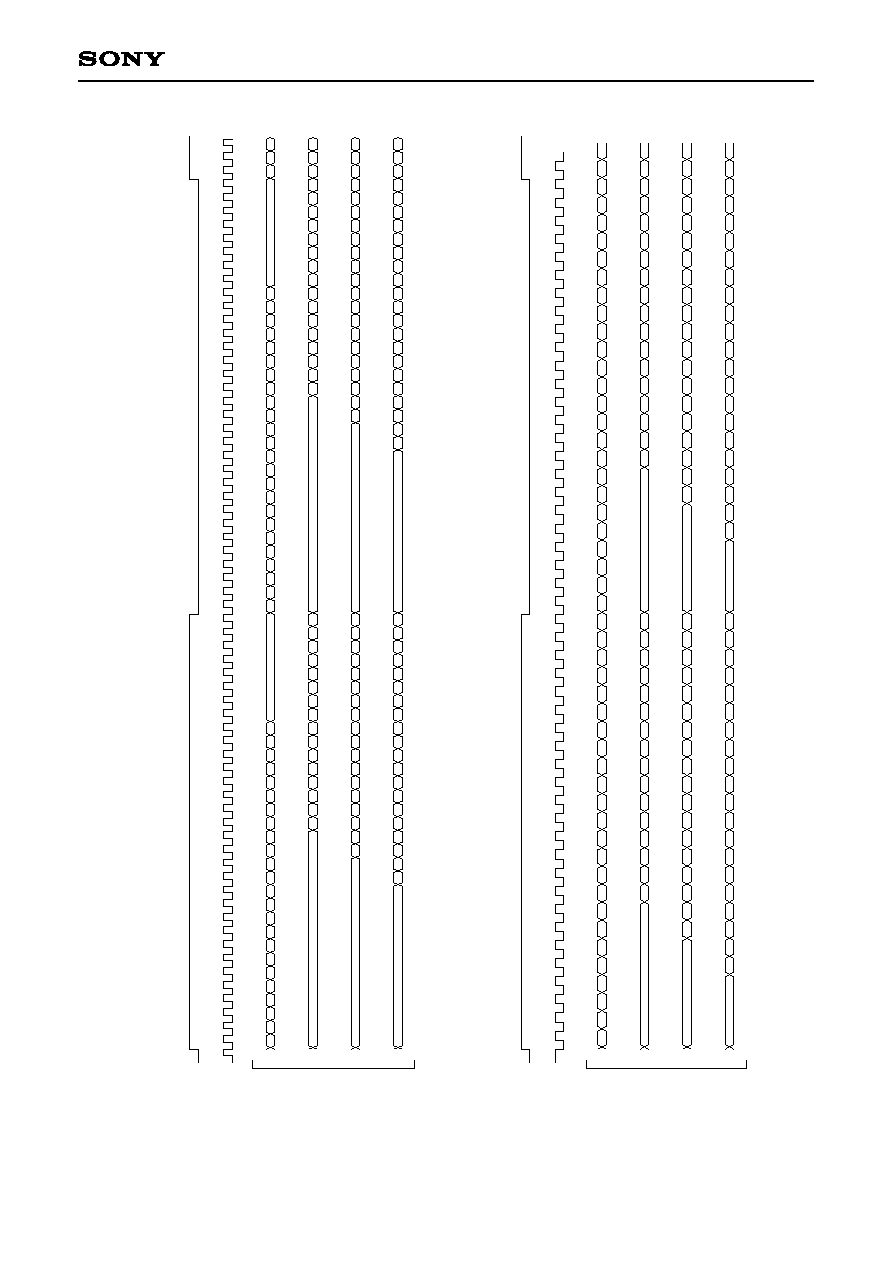

Digital Audio Data Input Timing

(with polarities: SQC15 = 0, SQC14 = 0, SQC13 = 0)

32-bit slot

24-bit slot

≠ 17 ≠

CXD2719Q

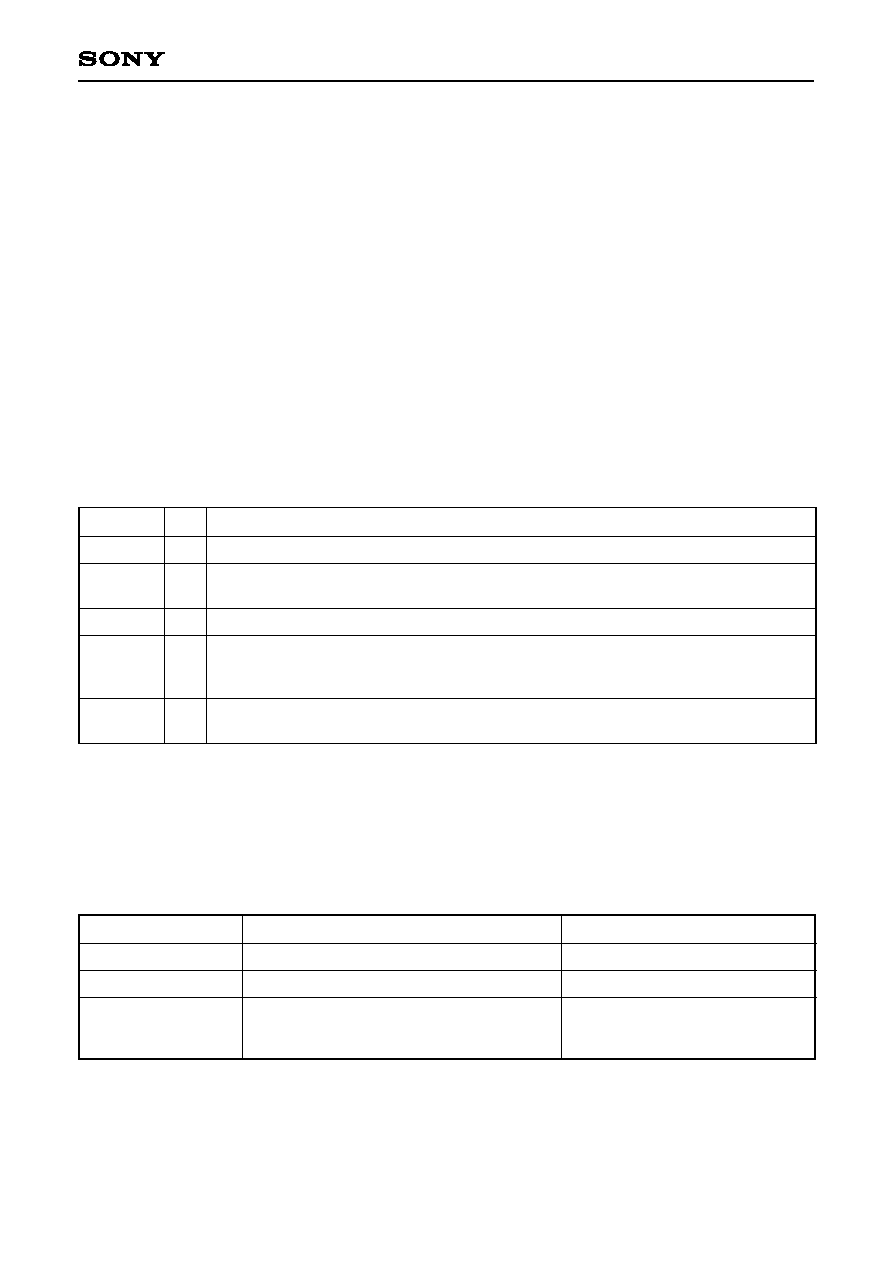

5. Microcomputer Interface

[Relevant pins] RVDT, SCK, XLAT, REDY

The CXD2719Q performs the serial audio interface format setting and the coefficient settings such as volume

and filter by serial data from the microcomputer.

(1) Pin Configuration

The four external pins indicated in the table below are assigned to the microcomputer interface.

Serial data input from microcomputer.

Shift clock for serial data. Input data from RVDT is taken according to the SCK rise.

Interprets the 8 bits of RVDT before this signal rises as transfer mode data, and the

bits before that as address data.

Transfer prohibited while at Low level. Transfer enabled at High. This pin is an open

drain, and must be pulled up externally.

Symbol

RVDT

SCK

XLAT

REDY

I/O

Function

I

I

I

O

Table 5-1. Microcomputer Interface External Pins

(2) Description of Communication Formats

The internal data transfer timing from the microcomputer interface to the coefficient RAM and setup register is

called the SV cycle, and is generated once per 1 LRCK.

The SV cycle is generated immediately preceding the signal processing program, so it has absolutely no effect

on signal processing, and there is no risk of the sound being cut.

Address section + Mode section + Data section

act as one package of data to transfer data from the microcomputer to the CXD2719Q.

[Write]

For coefficient RAM

A0

A7

M0

M7

D0

D15

Address section (8 bits) Mode section (8 bits)

RVDT

SCK

XLAT

REDY

Data section (16 bits)

Fig. 5-1. Example of Communication

≠ 18 ≠

CXD2719Q

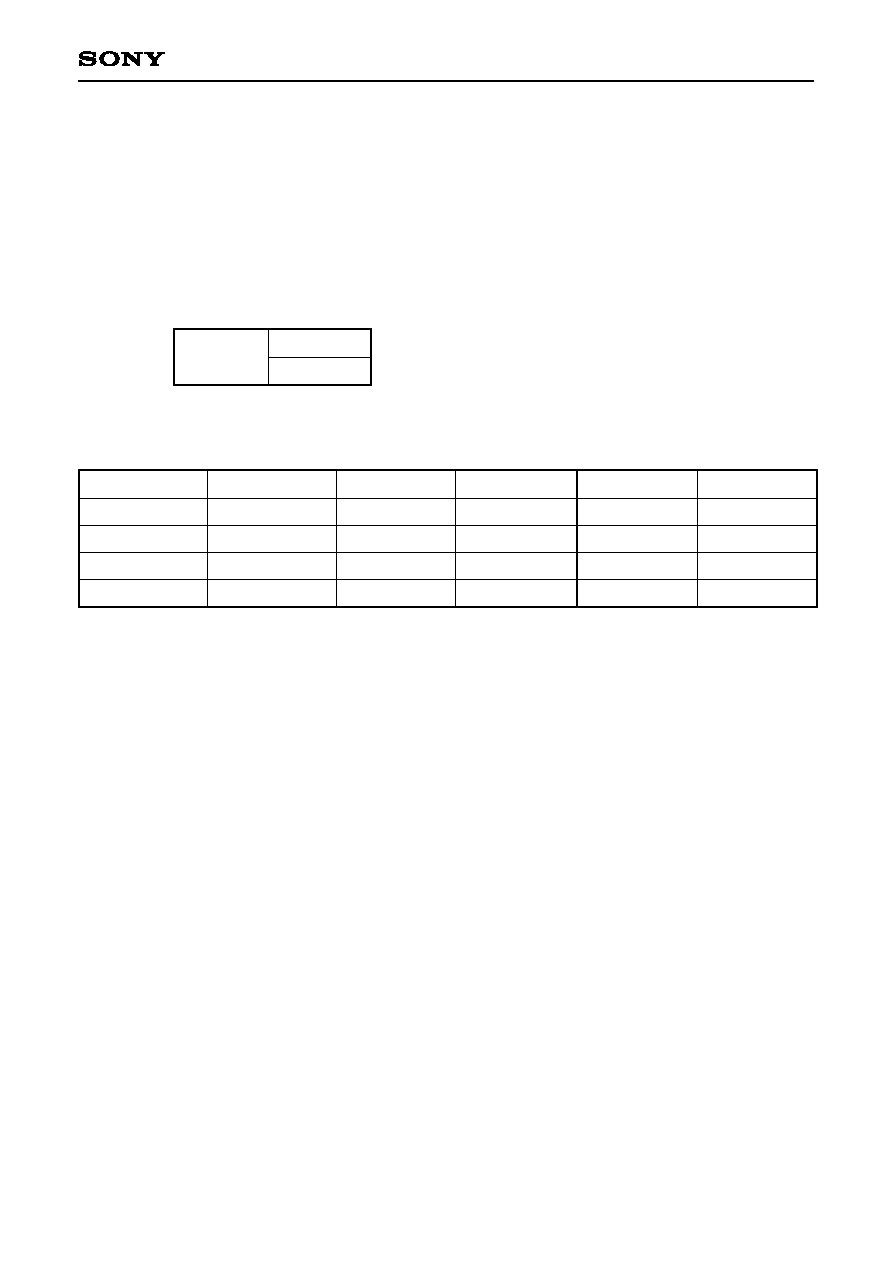

(3) Data Structure

The data structure is classified into three types, as shown in the table below. All data communication is done

with LSB first.

Coefficient RAM and setup register are both 16 bits

Symbol

A0 to A7

M0 to M7

D0 to D15/SQ00 to SQ15

Bit length

Remarks

8

8

16

Contents

Address section

Transfer mode section

Data section

Table 5-2. Data Structure

(3)-1. Transfer Mode Section

The transfer mode section is 8 bits and has the following functions.

Normally fixed to "0"

SU1 SU0

0 0 Field A

0 1 Field B

1 0 Field C

1 1 Field D

VS1 VS0

0 0 Setup register

1 0 Coefficient RAM

Normally fixed to "0"

Bit

M7

M6

M5

M4

M3

M2

M1

M0

Symbol

Function

SU1

SU0

VS1

VS0

Reserve

Setup Reg.

type

Data type

Reserve

Table 5-3. Transfer Mode Section

(3)-2. Address Section

The coefficient RAM has a 256-word structure, so the address section is 8 bits. The setup register has a 4-

word structure and the field (address) is specified by the mode section, so the address section data may be

optional.

(3)-3. Data Section

The coefficient RAM and setup register both have a 16-bit structure, so 16 SCK are required.

≠ 19 ≠

CXD2719Q

(4) Details of Communication Methods

The definitions of signal timing required for control from the microcomputer are given below.

(4)-1. Initializing the Microcomputer Interface

The microcomputer interface must be initialized after resetting the IC.

After resetting the IC (t1

1/fs), input 16 SCK rising edges. After that, REDY goes Low within 4t + 50ns (t2),

and initialization is completed when REDY goes High again. Set RVDT Low while inputting SCK.

Note that the REDY Low time (t3) is a maximum of 1/fs. See the following page for the SCK restrictions. The

same restrictions apply as during data transfer.

When REDY goes Low due to initialization:

∑ The SCK for the first transfer can rise.

∑ The XLAT for the first transfer can fall.

However, the XLAT for the first transfer must rise after REDY goes High.

Fig. 5-2. Initialize Specifications

RVDT

XRST

SCK

REDY

t1

16 rising edges

t2

t3

Microcomputer interface can be used

≠ 20 ≠

CXD2719Q

(4)-2. Signal Timing

First, address section data and mode section data are sent from the microcomputer, synchronized to SCK, to

the RVDT pin.

The address section data is 8 bits for both the coefficient RAM and setup register, and the setup register has a

length of one word, so optional data can be transferred. Address section data is sent with LSB first.

Mode section data is fixed at 8 bits regardless of the transfer contents.

The phase relationship between SCK and RV data (data applied to the RVDT pin) has the following

restrictions:

∑ RV data must be established before SCK rises (tDS

20ns).

∑ RV data must be held for 1t + 20ns or more after SCK rises (tDH).

SCK itself has the following restrictions:

∑ SCK Low level must be 1t + 20ns or more (tSWL).

∑ SCK High level must be 1t + 20ns or more (tSWH).

After the SCK rise which corresponds to the mode section final data, XLAT rises (tSLP

20ns).

The XLAT Low level width must be maintained at 1t + 20ns or more (tLWL). The fall timing is restricted in that

even if REDY falls due to SCK during the preceding transfer, 3t + 20ns or more (tSLD) is required from the

SCK rise which corresponds to the data section final data.

Further, if preceding transfers have been performed and REDY = Low, XLAT must rise after REDY = High.

A0

A7

M0

M7

SQ00

SQ15

RVDT

SCK

XLAT

REDY

A0

M7

tDH

tDS

tSWH

tSWL

tSLD or tLWH

tLWL

tRLP

tLDR

tLSD

tSLP

tBSP

tSLP

tLDR

tRLP

tSS

tSLD

tSBD

D0/SQ00

D15/SQ15

Fig. 5-3. Write Timing

t is the cycle of 2/3 the clock frequency applied to the XTLI pin. (512fs)

≠ 21 ≠

CXD2719Q

Data section write begins after XLAT rises, and here also transfer must be performed with LSB first, with tDS

and tDH restrictions. In addition, after XLAT rises at the starting point for sending the data section, wait for 3t +

20ns or more for the first SCK rise (tLSD).

When 16 bits of this write is repeated, REDY goes Low within 4t + 50ns, and the microcomputer is informed of

waiting status for the SV cycle, which is the dedicated data rewrite cycle, by the microcomputer interface

(tSBD).

When REDY goes High again, the corresponding data is written.

The next communication can be restarted by using the REDY signal as follows.

∑ When REDY = Low, the SCK for the next transfer can rise (tBSP

20ns).

∑ In the same way, when REDY = Low, the XLAT for the next transfer can fall (tLDR

20ns).

REDY will fall due to this communication, but it is prohibited for XLAT to rise for the next transfer before REDY

rises. Make sure that the next XLAT rises after REDY rises (tRLP

20ns).

In order to restart the next transfer without using the REDY signal, the following conditions must be observed:

∑ There should be 2t + 40ns or more left between the SCK rise for the final data section and the SCK rise for

the next transfer (tSS).

∑ In the same way, the XLAT for the next transfer can fall after waiting for 3t + 20ns or more after the final

data section SCK rise (tSLD).

The tSS and tSLD here are shorter times than tSBD

4t + 50ns, so these are rather loose restrictions.

However, even in this case the XLAT rise for the next transfer must come after REDY rises (tRLP

20ns).

Further, the restriction for the XLAT fall at the starting point of this transfer from tSLD can be:

tSLD

3t + 20ns

≠ 22 ≠

CXD2719Q

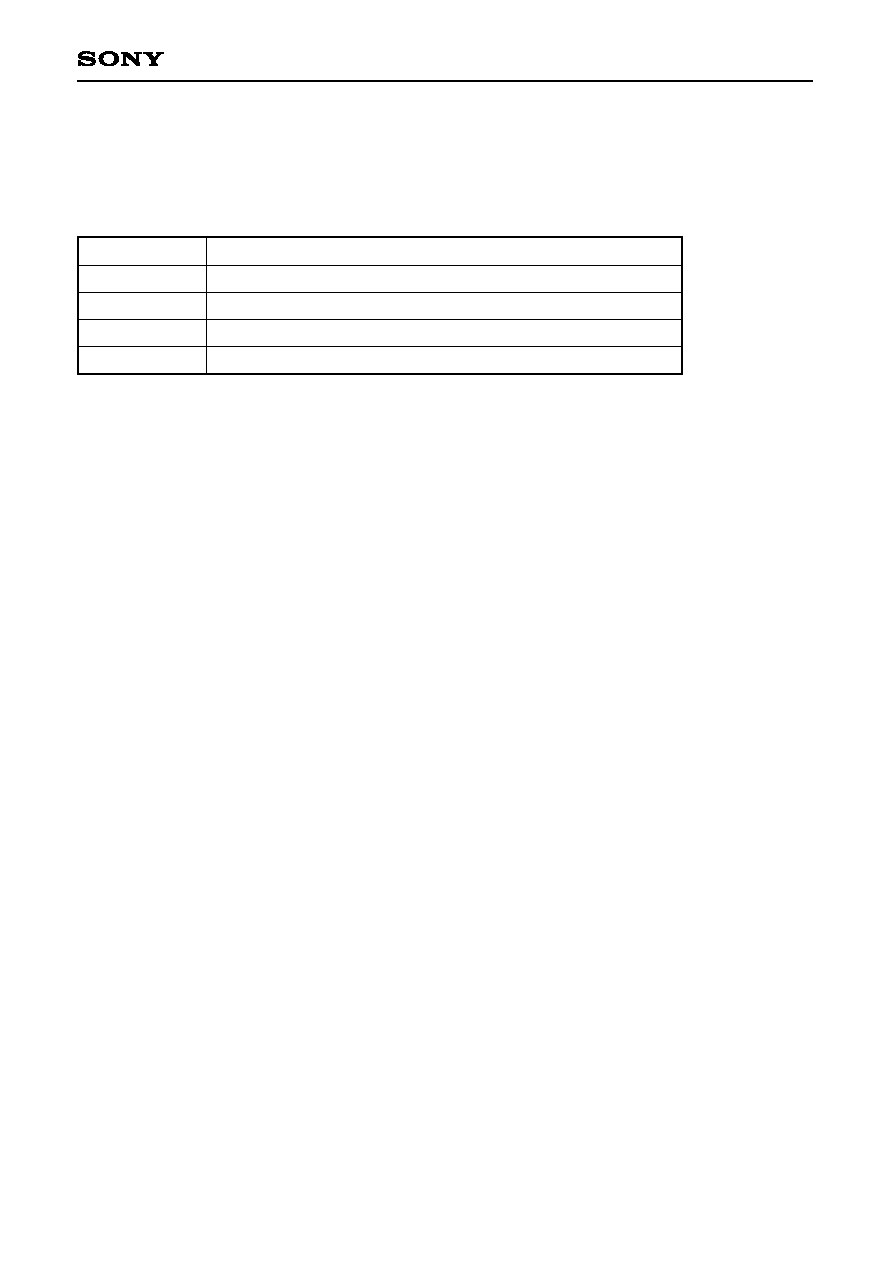

6. Setup Register

When the setup register is selected in microcomputer interface transfer mode, the following settings are

possible for hardware such as the serial audio interface and DAC, and for software such as the Dolby Pro

Logic Surround decoder.

The setup register has a total of four fields, and 16 bits of setup information can be stored per field. However,

when this LSI is reset, the setup register contents are also reset to the settings shown in the "When reset"

column in Tables 6-1 to 6-4 below.

(1) Field A

SQA15

SQA14

SQA13

SQA12

SQA11,

SQA10

SQA09,

SQA08

SQA07,

SQA06

SQA05,

SQA04

SQA03 to

SQA00

DSP bypass mode

0: OFF

1: ON

Noise sequencer

0: OFF

1: ON

Reserve bit

Be sure to set both bits Low when changing the

setup register Field A se

Compensation filter

0: OFF

1: ON

Decimation ratio setting SQA11 SQA10

(SFC mode only)

0

0

: 1/1 (No decimation)

Be sure to also set

0

1

: 1/2 decimation

SQC07 and SQC06.

1

0

: 1/3 decimation

Dolby 3 Stereo

SQA09 SQA08

0

0

: OFF

0

1

: ON

Reserve bit

Be sure to set both bits Low when changing the

setup register Field A settings.

SFC mode

SQA05 SQA04

0

0

: OFF

0

1

: ON

Reserve bit

Be sure to set both bits Low when changing the

setup register Field A settings.

OFF

OFF

all "L"

OFF

1/1

(No decimation)

OFF

all "L"

OFF

all "L"

Table 6-1. Setup Register Field A

Bit names are indicated by the field name and the bit number. The bit names for Field A are SQA00 to

SQA15, and the first three letters of the bit names for Fields B, C and D are SQB, SQC and SQD,

respectively.

Data

section bit

Control contents

When reset

≠ 23 ≠

CXD2719Q

SQB15 to

SQB11

SQB10 to

SQB06

SQB05 to

SQB00

Center channel trim volume

00000: 0dB

(5 bits, analog)

00001: ≠1dB

00010: ≠2dB

11101: ≠29dB

11110: ≠30dB

11111: ≠31dB

Center channel trim volume

00000: 0dB

(5 bits, analog)

00001: ≠1dB

00010: ≠2dB

11101: ≠29dB

11110: ≠30dB

11111: ≠31dB

Reserve bit

Be sure to set all of these bits Low when

changing the setup register Field B settings.

0dB

0dB

all "L"

Table 6-2. Setup Register Field B

(2) Field B

Data

section bit

Control contents

When reset

≠ 24 ≠

CXD2719Q

SQC15

SQC14

SQC13

SQC12,

SQC11

SQC10

SQC09,

SQC08

SQC07,

SQC06

SQC05,

SQC04

SQC03 to

SQC00

LRCK format

0: normal

1: IIS

LRCK polarity selection 0: Lch "H"

1: Lch "L"

BCK polarity selection

0: Falling edge

relative to LRCK edge

1: Rising edge

Serial audio

SQC12 SQC11

interface setting

0

0

: MSB first/Frontward truncation/24 bits

0

1

: MSB first/Rearward truncation/16 bits

1

0

: MSB first/Rearward truncation/18 bits

1

1

: MSB first/Rearward truncation/20 bits

DAC forced mute

0: ON

1: OFF

Reserve bit

Be sure to set both bits Low when changing

the setup register Field C settings.

Decimation ratio setting SQC07 SQC06

(SFC mode only)

0

0

: 1/1 (No decimation)

Be sure to also set

0

1

: 1/2 decimation

SQA11 and SQA10.

1

: 1/3 decimation

BFOT output clock

SQC05 SQC04

frequency division

0

0

: 384Fs

ratio setting

0

1

: 256Fs

1

0

: 512Fs

1

1

: 768Fs

Reserve bit

Be sure to set all of these bits Low when changing

the setup register Field C settings.

normal

Lch "H"

Falling edge

MSB

first/Frontward

truncation/24 bits

ON

all "L"

1/1

(No decimation)

384Fs

all "L"

(3) Field C

Table 6-3. Setup Register Field C

Data

section bit

Control contents

When reset

Note) BCK polarity selection (SQC13) is valid only in slave mode. Fix to "0" in master mode.

Data

section bit

SQD15 to

SQD03

SQD02 to

SQD00

Control contents

Reserve bit

Be sure to set all of these bits Low when changing the

setup register Field D settings.

Be sure to set all of these bits Low

all "L"

all "L"

(4) Field D

Table 6-4. Setup Register Field D

When reset

≠ 25 ≠

CXD2719Q

7. Coefficient RAM

When the coefficient RAM is selected in microcomputer interface transfer mode, the various application

functions can be turned on and off, and the coefficient parameters such as each section's volume and delay

time can be set.

Coefficient RAM addresses other than those given in these specifications are "don't care". However, the RAM

is not cleared entirely when this LSI is reset, so there are no initial values as for the setup register. Be sure to

set all of the necessary data; otherwise misoperation may result.

The coefficient RAM has the capacitance of 256 words x 16 bits and the data transferred differs for each mode.

(See "8. Applications" for the detailed contents.)

8. Applications

The CXD2719Q is equipped with various applications such as Dolby Pro Logic Surround mode (Pro Logic

mode), Dolby 3 Stereo mode, noise sequencer mode, SFC mode, and DSP bypass mode.

The methods of setting each mode and of changing the mode are described below.

Note) The filter and other parameter values for each application assume a sampling frequency (fs) of 44.1 [kHz].

Consult your Sony representative with regard to use at other fs.

8-1. Dolby Pro Logic Surround Mode (Pro Logic Mode)

Pro Logic mode is realized using the adaptive matrix, passive decoder including BNR, auto input balance,

center channel mode control, simple SFC and other functions.

(1) Setting Pro Logic Mode

Pro Logic mode must be set by the following procedures in order to achieve stable adaptive matrix operation.

Setting Pro Logic mode by procedures other than those given below may aggravate the decoder

characteristics.

∑ Immediately after power-on reset

i)

Transfer the following setup data.

SQA = 0030H (Field A)

SQD = 7ee7H (Field D)

Note) Field C is "All 0", so the DAC forced mute is applied.

ii) Transfer the Pro Logic mode coefficient data.

iii) Transfer the setup data set in Pro Logic mode.

∑ Changing to Pro Logic mode from a different mode (other than Virtual mode)

i)

Apply the soft mute

1

in the current mode.

ii) Set the coefficients at the following addresses to "0000H".

Addresses: 6eH to 7fH

iii) Transfer the following setup data.

SQA = 0030H (Field A)

SQD = 7ee7H (Field D)

Note) The DAC forced mute is not applied by Field C.

iv) Transfer the Pro Logic mode coefficients for the soft mute status.

v) Transfer the setup data set in Pro Logic mode.

vi) Cancel the Pro Logic mode soft mute.

1

Soft mute: See "Appendix 1. Soft Mute".

≠ 26 ≠

CXD2719Q

(2) Setting Data

(2)-1. Setup Data

Table 8-1-1 lists the registers most closely related to Pro Logic mode.

Setup data not listed in Table 8-1-1 may be set as desired, with due consideration given to the contents of

Fields A to D noted in "6. Setup Register".

1: Noise sequencer mode

01: Dolby 3 Stereo mode

01: SFC mode

Center channel (C-ch) trim volume

Surround channel (S-ch) trim volume

SQA14

SQA09, 08

SQA05, 04

SQB15 to 11

SQB10 to 06

"0"

"00"

"00"

Don't care

Don't care

Register name Setting value

Remarks

Table 8-1-1. Pro Logic Mode Setup Register Settings

≠ 27 ≠

CXD2719Q

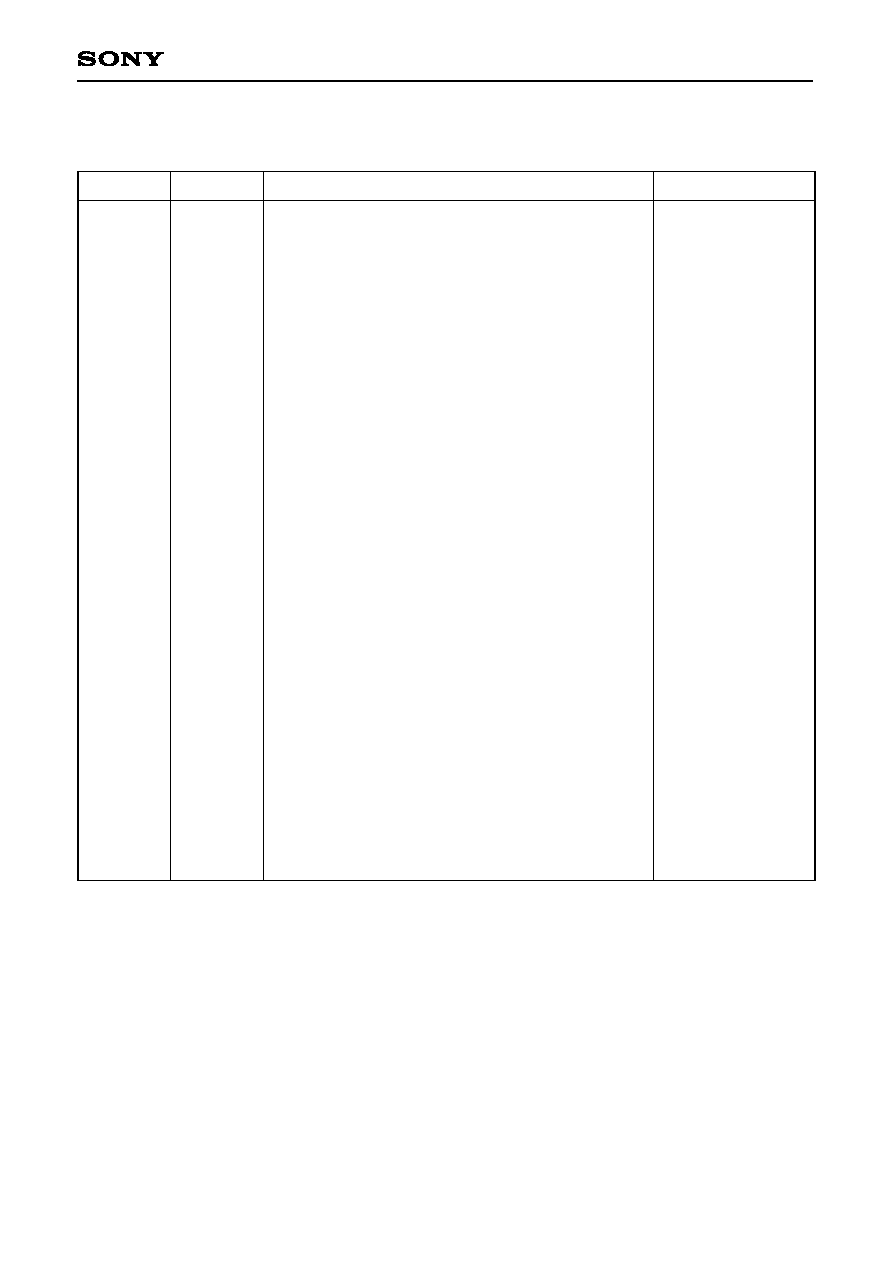

(2)-2. Coefficient Data

The coefficient data consists of "fixed values" shown in Table 8-1-2 and "setting values" shown in Table 8-1-3

which can be set by the user. All coefficient values must be sent to the coefficient RAM via the microcomputer

interface.

∑ Fixed values during Pro Logic mode initialization

The following fixed values must be set in the coefficient RAM to ensure proper internal operation.

Table 8-1-2. Pro Logic Mode Fixed Value Coefficients

27H

6dH

6eH

6fH

70H

71H

72H

73H

74H

75H

76H

77H

78H

79H

7aH

7bH

7cH

7dH

7eH

7fH

80H

81H

82H

83H

84H

85H

86H

87H

88H

89H

8aH

8bH

8cH

8dH

8eH

8fH

Address

0000H

051eH

ff86H

02a0H

f6c0H

2715H

4000H

5149H

e571H

0f4eH

f5b8H

075cH

fa97H

0402H

fd0bH

0225H

fe7cH

01d3H

f312H

4b85H

850fH

7d6bH

7d72H

22b6H

3a94H

0074H

7f18H

a000H

8000H

febfH

04f9H

eb83H

7b01H

cae0H

0400H

0074H

Fixed value

90H

91H

92H

93H

94H

95H

96H

97H

98H

99H

9aH

9bH

9cH

9dH

9eH

9fH

a0H

a1H

a2H

a3H

a4H

a5H

a6H

a7H

a8H

a9H

aaH

abH

acH

adH

aeH

b3H

b4H

b6H

b8H

b9H

Address

7f18H

0400H

001eH

7fc5H

0002H

7ffdH

8000H

dd1eH

da82H

109cH

2641H

3441H

dd1eH

109cH

da82H

2641H

3441H

0bbfH

e755H

4000H

f619H

e57eH

36dcH

5a82H

10c9H

2641H

7f18H

7e30H

4cbaH

c216H

0aa4H

27b4H

7e14H

7ff9H

0063H

0000H

Fixed value

baH

bbH

bcH

bdH

beH

bfH

c0H

c1H

c2H

c3H

c4H

c5H

c6H

c7H

c8H

c9H

caH

cbH

ccH

cdH

ceH

cfH

d0H

d1H

d2H

d3H

d5H

d7H

d8H

daH

dbH

deH

dfH

e3H

e4H

e5H

Address

43b9H

0400H

401eH

ec00H

8000H

a000H

0024H

ff92H

010aH

fce2H

097bH

e38dH

1555H

0400H

1400H

2000H

c000H

ffe4H

febcH

f520H

c144H

a57eH

0757H

0012H

7f00H

7fffH

fc00H

68a9H

5121H

7ff4H

7fe8H

8000H

c400H

0000H

0000H

0000H

Fixed value

e6H

e7H

e8H

e9H

eaH

ebH

ecH

edH

eeH

efH

f0H

f9H

feH

ffH

Address

0000H

0000H

0000H

0000H

0000H

0000H

0000H

0000H

0000H

0000H

7fffH

8000H

b800H

0001H

Fixed value

≠ 28 ≠

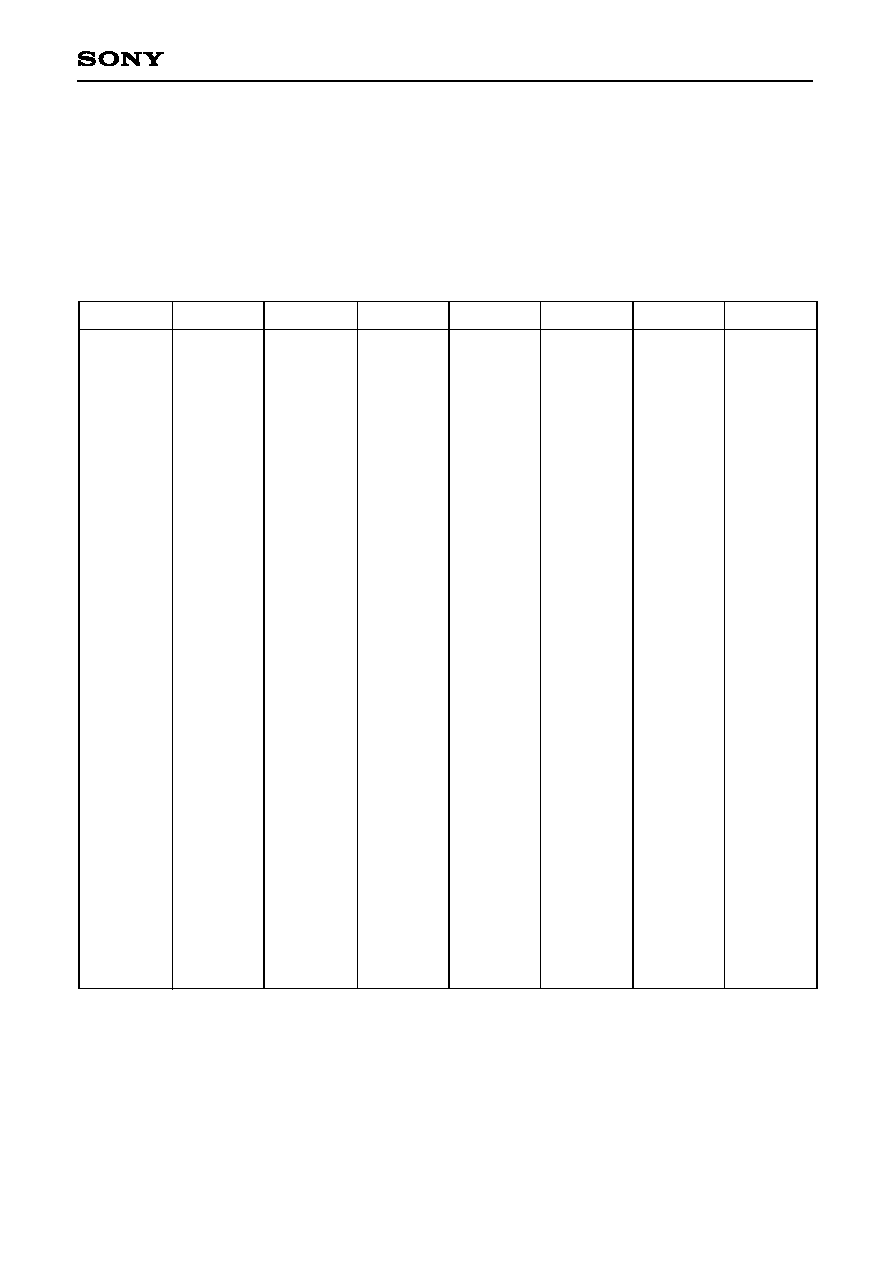

CXD2719Q

∑ Pro Logic mode user setting coefficients

The relationships between the coefficient RAM and each function during Pro Logic mode operation are as

follows.

00H

01H

02H

03H

04H

05H

06H

07H

08H

09H

0aH

0bH

0cH

0dH

0eH

0fH

10H

11H

12H

13H

14H

15H

16H

17H

18H

19H

1aH

1bH

1cH

1dH

1eH

1fH

20H

21H

22H

23H

24H

KLV

KRV

KCV

KSV

KLm1

KRm1

a0

a1

b

KLm2

KRm2

a0

a1

b

KLd

KRd

KCd

KSd

Kfb

a0

a1

b

a0

a1

b

KDin

TP1

TP2

TP3

TP4

TP5

TP6

KDout

KDV1

KDV2

KDV3

KLRm1

Simple SFC: L-ch dry

L-ch mix volume

Simple SFC: R-ch dry

R-ch mix volume

Simple SFC: C-ch

C-ch volume

Simple SFC: S + L/R (HPF1)

S-ch mix volume

Simple SFC: L-ch

LPF1 mix volume

Simple SFC: R-ch

LPF1 mix volume

Simple SFC: LPF1 coefficient

Simple SFC: LPF1 coefficient

Simple SFC: LPF1 coefficient

Simple SFC: L-ch

HPF1 mix volume

Simple SFC: R-ch

HPF1 mix volume

Simple SFC: HPF1 coefficient

Simple SFC: HPF1 coefficient

Simple SFC: HPF1 coefficient

Simple SFC: L-ch

Delay RAM mix volume

Simple SFC: R-ch

Delay RAM mix volume

Simple SFC: C-ch

Delay RAM mix volume

Simple SFC: S-ch

Delay RAM mix volume

Simple SFC: Delay RAM feedback volume

Simple SFC: HPF2 coefficient

Simple SFC: HPF2 coefficient

Simple SFC: HPF2 coefficient

Simple SFC: LPF2 coefficient

Simple SFC: LPF2 coefficient

Simple SFC: LPF2 coefficient

Simple SFC: Delay RAM write address

Simple SFC: Delay RAM read Tap1 address

Simple SFC: Delay RAM read Tap2 address

Simple SFC: Delay RAM read Tap3 address

Simple SFC: Delay RAM read Tap4 address

Simple SFC: Delay RAM read Tap5 address

Simple SFC: Delay RAM read Tap6 address

Simple SFC: Delay RAM feedback Tap address

Simple SFC: Delay RAM

S-ch mix volume

Simple SFC: Delay RAM

R-ch mix volume

Simple SFC: Delay RAM

L-ch mix volume

Simple SFC: LPF1

L-ch mix volume

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-16.

See Table 8-1-16.

See Table 8-1-16.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-16.

See Table 8-1-16.

See Table 8-1-16.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-16.

See Table 8-1-16.

See Table 8-1-16.

See Table 8-1-16.

See Table 8-1-16.

See Table 8-1-16.

See Table 8-1-15.

See Table 8-1-15.

See Table 8-1-15.

See Table 8-1-15.

See Table 8-1-15.

See Table 8-1-15.

See Table 8-1-15.

See Table 8-1-15.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

Table 8-1-3 (1). Pro Logic Mode Setting Value Coefficients

Address

Symbol

Function

Setting value

≠ 29 ≠

CXD2719Q

25H

26H

28H

29H

2aH

2bH

2cH

2dH

afH

b0H

b1H

b2H

b5H

b7H

d4H

d6H

d9H

dcH

ddH

f2H

f3H

f4H

f5H

f6H

f7H

f8H

faH

fbH

Address

KLRm2

KLRm3

KTP1

KTP2

KTP3

KTP4

KTP5

KTP6

b2

b1

a

≠a

aslw

2D

Kx

KiA

Ke

Kia

Kis

KL

KR

KH

KP

KCH

KCP

KS

Kdlb

Dly

Symbol

Simple SFC: LPF1

R-ch mix volume

Simple SFC: HPF1

S-ch mix volume

Simple SFC: Tap1 volume

Simple SFC: Tap2 volume

Simple SFC: Tap3 volume

Simple SFC: Tap4 volume

Simple SFC: Tap5 volume

Simple SFC: Tap6 volume

7K LPF parameter

7K LPF parameter

7K LPF parameter

7K LPF parameter

Passive decoder M-BNR

Passive decoder M-BNR

Auto input balance ON/OFF

Serial audio interface input volume

De-emphasis ON/OFF

Analog input mix volume

Digital input mix volume

Center mode control volume

Center mode control volume

Center mode control volume

Center mode control volume

Center mode control volume

Center mode control volume

Passive decoder volume

Passive decoder M-BNR ON/OFF

Passive decoder delay time adjustment

Function

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

See Table 8-1-13.

0000 = OFF, df66 = ON

0000 = OFF, 5723 = ON

0000 = OFF, 125e = ON

8000 = OFF, eda2 = ON

See Table 8-1-12.

See Table 8-1-12.

0000 = OFF, 00ff = ON

See Table 8-1-5.

0000 = OFF, ac19 = ON

See Table 8-1-4.

See Table 8-1-5.

See Tables 8-1-7, 8.

See Tables 8-1-7, 8.

See Tables 8-1-7, 8.

See Tables 8-1-7, 8.

See Tables 8-1-7, 8.

See Tables 8-1-7, 8.

See Table 8-1-8.

0000 = OFF, 2000 = ON

See Table 8-1-9.

Setting value

Table 8-1-3 (2). Pro Logic Mode Setting Value Coefficients

≠ 30 ≠

CXD2719Q

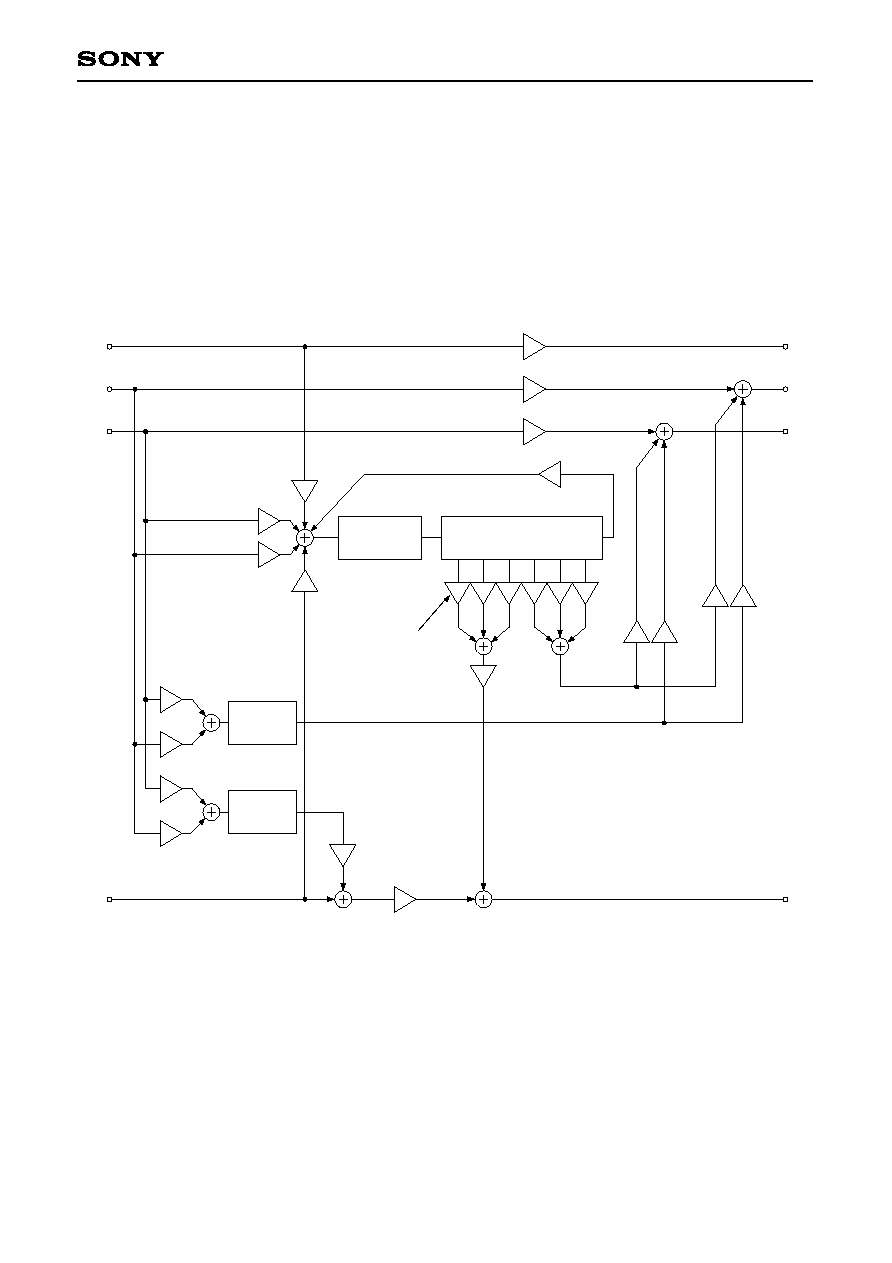

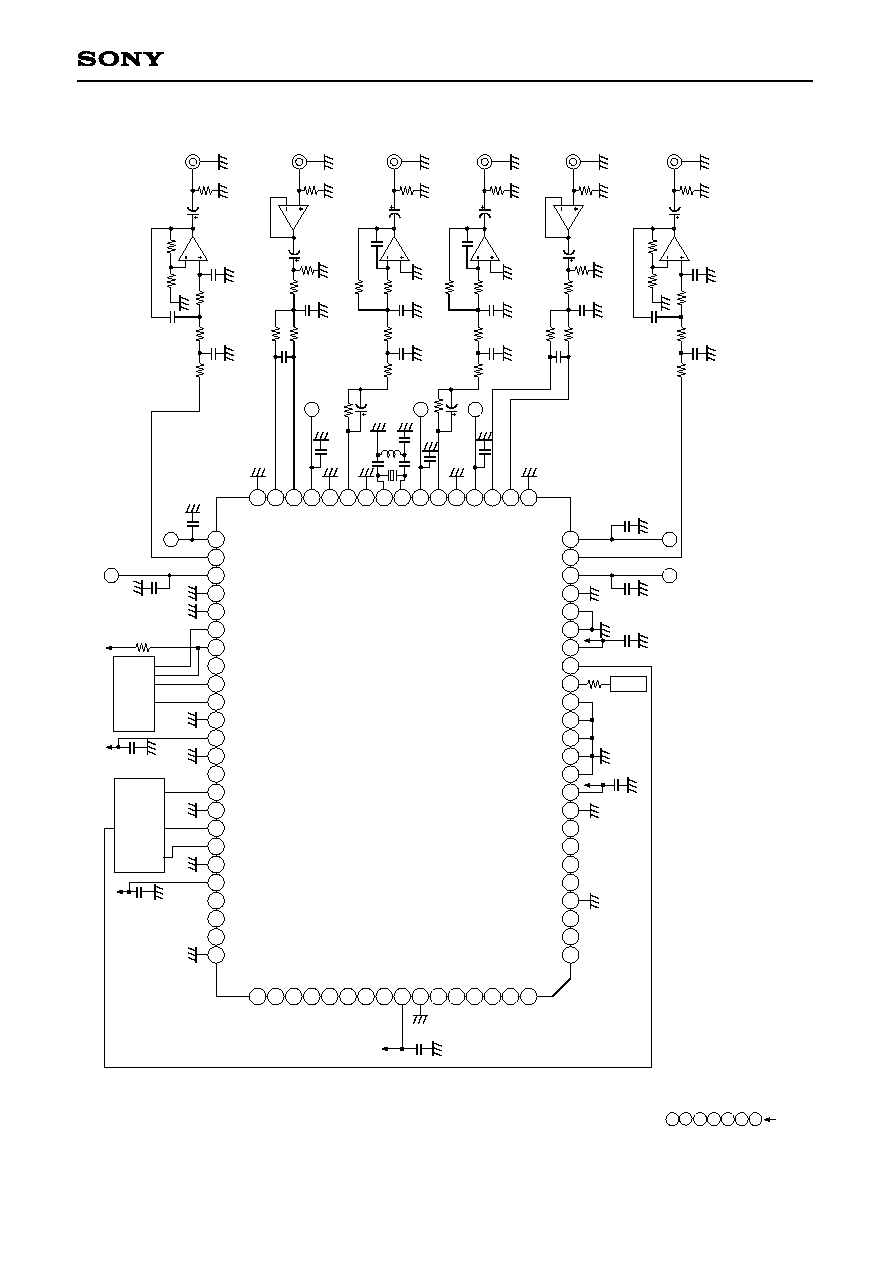

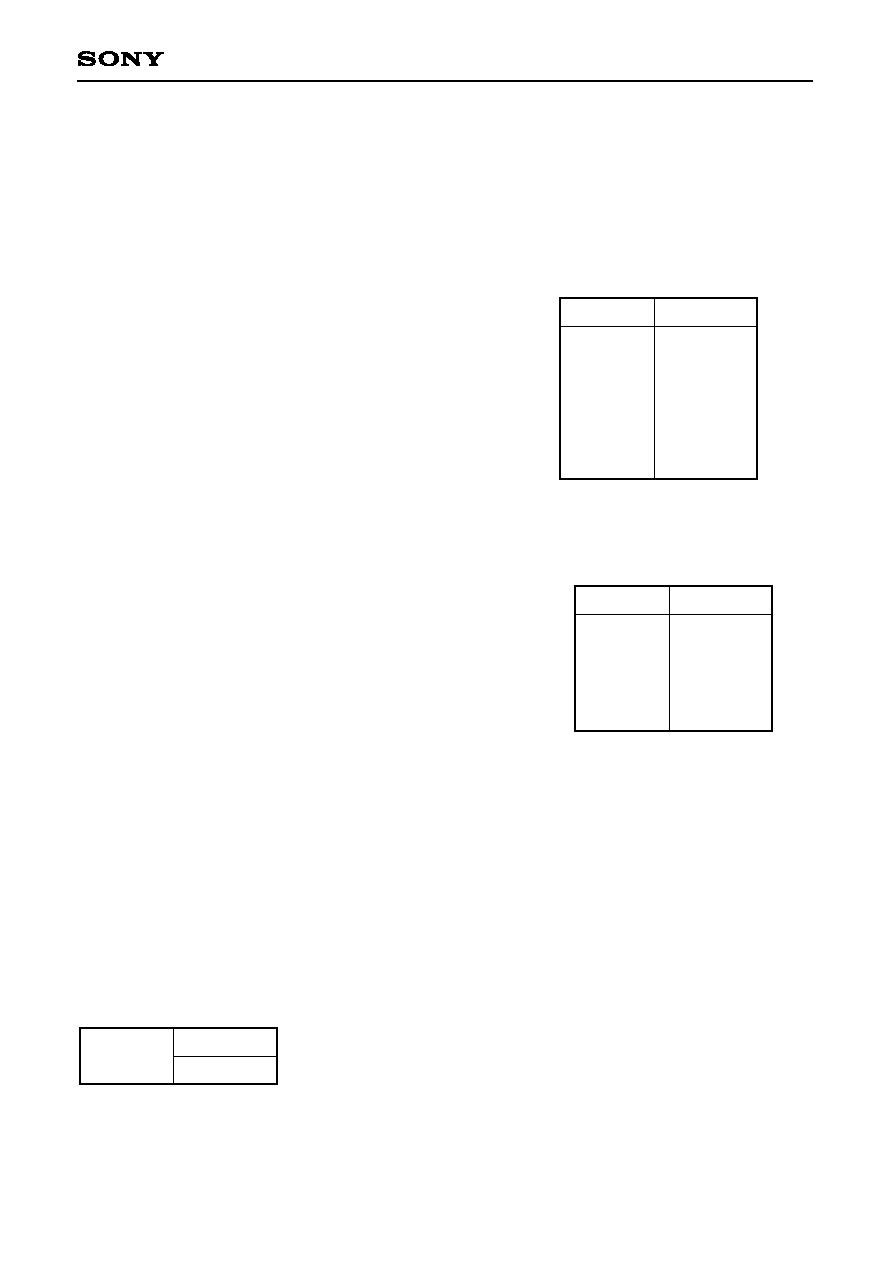

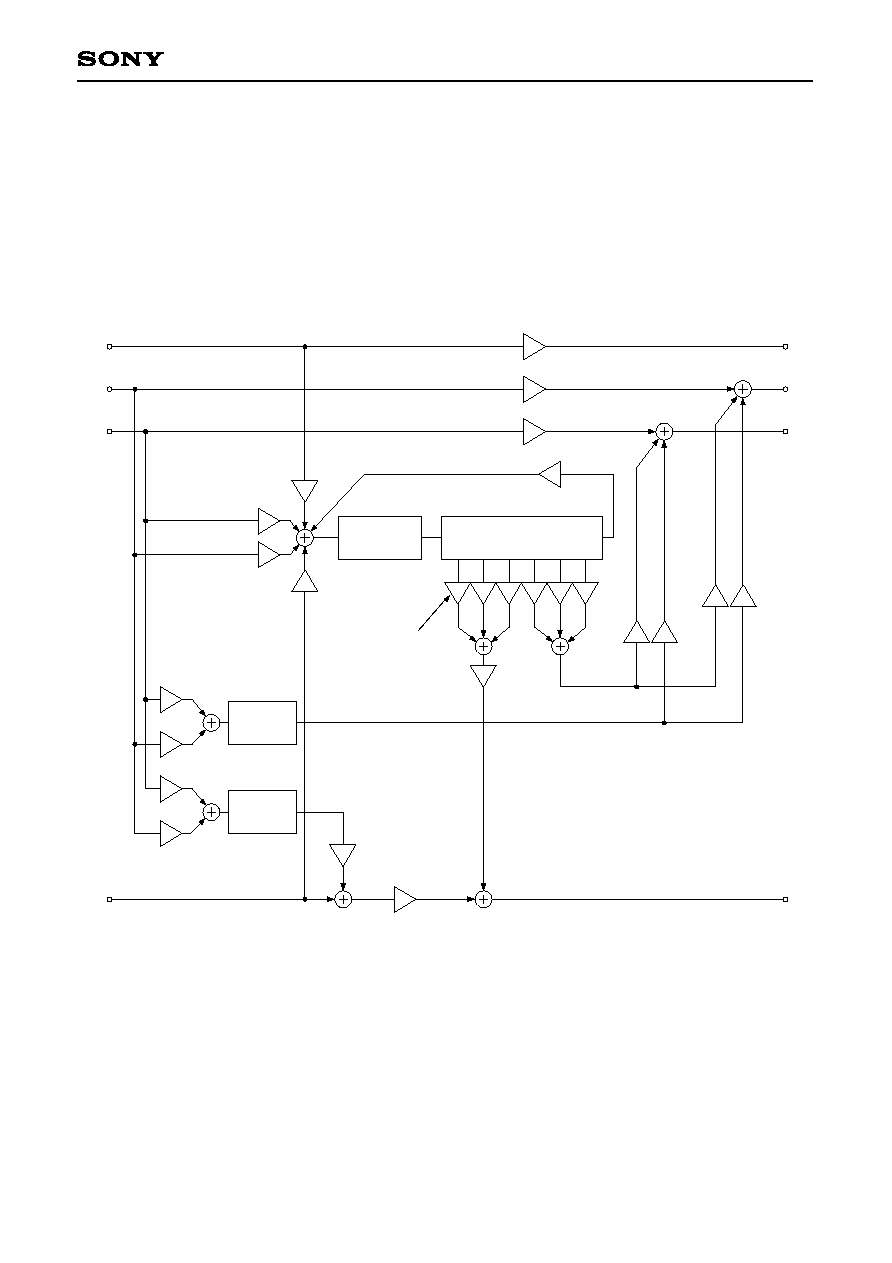

(2)-3. Signal Flow for Dolby Pro Logic Mode

L

P

F

A

D

C

D

e

c

i

m

a

t

i

o

n

D

C

C

u

t

L

P

F

A

D

C

D

e

c

i

m

a

t

i

o

n

D

C

C

u

t

D

e

E

m

p

h

a

s

i

s

L

I

N

R

I

N

S

I

A

1

S

I

A

2

D

e

E

m

p

h

a

s

i

s

≠

K

i

A

(

d

6

H

)

≠

K

i

A

(

d

6

H

)

≠

K

i

a

(

d

c

H

)

≠

K

i

s

(

d

d

H

)

≠

K

i

a

(

d

c

H

)

≠

K

i

s

(

d

d

H

)

L

t

L

R

C

S

R

t

P

r

o

L

o

g

i

c

D

e

c

o

d

e

r

L

L

R

C

S

S

S

i

m

p

l

e

S

F

C

R

C

D

A

C

D

A

C

O

v

e

r

S

a

m

p

l

i

n

g

O

v

e

r

S

a

m

p

l

i

n

g

D

A

C

D

A

C

O

v

e

r

S

a

m

p

l

i

n

g

O

v

e

r

S

a

m

p

l

i

n

g

L

P

F

L

P

F

M

U

X

&

L

P

F

M

U

X

&

L

P

F

T

r

i

m

V

o

l

L

O

U

T

R

O

U

T

X

C

O

U

T

X

S

O

U

T

T

r

i

m

V

o

l

Fig. 8-1-1

≠ 31 ≠

CXD2719Q

(3) Volume Coefficient Settings

[Relevant data] Coefficients: KiA (d6H), Kia (dcH), Kis (ddH)

The I/O levels and volumes are 2's complement format with a decimal point between D15 and D14, and

hexadecimal notation with D15 as MSB and D0 as LSB.

The coefficient and level relationships are as follows.

D15 to D0 are negative values, but the DSP calculation is (≠1)

◊

(D15 to D0).

(3)-1. Kia (dcH): 0dB = c000H

The I/O levels for 8000H to ffffH are obtained by the following formulas.

(Coefficient value) = [(≠1)

◊

D15 +

(Dn

◊

2

n ≠ 15

)]

◊

(≠2)

I/O level = 20 log [coefficient value] dB

(3)-2. KiA (d6H), Kis (ddH): 0dB = 8000H

The I/O levels for 8000H to ffffH are obtained by the following formulas.

(Coefficient value) = [(≠1)

◊

D15 +

(Dn

◊

2

n ≠ 15

)]

◊

(≠1)

I/O level = 20 log [coefficient value] dB

Unless otherwise specified, subsequent setting examples (Pro Logic mode) in these specifications assume

either:

Kia = d2b2H, KiA = 0000H, Kis = 0000H

or:

Kia = 0000H, KiA = 8000H, Kis = a563H

(4) Auto Input Balance Control

[Relevant data] Coefficient: Kx (d4H)

The auto input balance function is turned on and off by coefficient Kx (d4H).

8000H

a599H

c000H

d2b2H

e000H

eff6H

ffffH

0000H

D15 to D0

+6.02

+3.00

0.00

≠3.00

≠6.02

≠12.00

≠84.29

≠

Level [dB]

8000H

a563H

c000H

e000H

ffffH

0000H

D15 to D0

0.00

≠3.00

≠6.02

≠12.04

≠90.31

≠

Level [dB]

14

n = 0

14

n = 0

Table 8-1-4. Kia (dcH) Setting Value Examples

Table 8-1-5. KiA (d6H), Kis (ddH) Setting Value Examples

Coefficient

Kx (d4H)

OFF = 0000H

ON = 00ffH

Table 8-1-6. Auto Input Balance ON/OFF

≠ 32 ≠

CXD2719Q

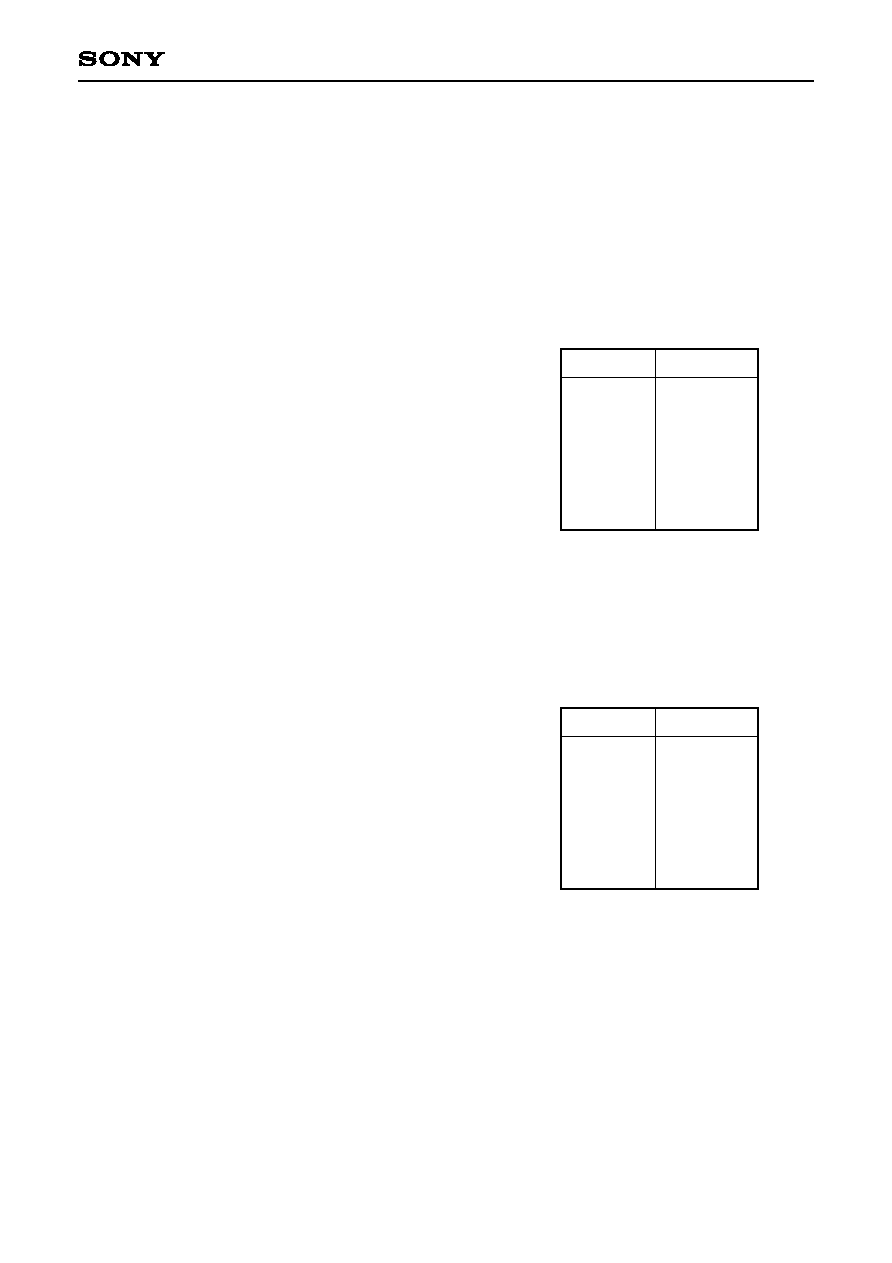

(5) Center Mode Control

[Relevant data] Coefficients: KP (f5H), KH (f4h), KL (f2H), KR (f3H), KCP (f7H), KCH (f6H)

The center channel output mode can be set to Normal, Wide or Phantom mode as shown in Table 8-1-7 below.

Coefficient

KP (f5H)

e000H

0000H

e000H

KH (f4H)

e000H

0000H

0000H

KL (f2H)

d2cdH

d2cdH

d2cdH

KR (f3H)

d2cdH

d2cdH

d2cdH

KCP (f7H)

0000H

e000H

0000H

KCH (f6H)

e000H

0000H

0000H

Mode

Normal

Wide

Phantom

Table 8-1-7. Center Mode Control Setting Value Examples

LP

RP

CP

≠KL (f2H)

≠KR (f3H)

LO

RO

CO

LPF

HPF

≠KCH (f6H)

≠KCP (f7H)

Note) If KH is set to 0000H in Phantom center channel mode, the LPF is set to

data through status and the data added to the L and R channels is CP

◊

KP.

≠KH (f4H), ≠KP (f5H)

Fig. 8-1-2. Signal Flow for Center Mode Control (L, R, C-ch)

Note) In Phantom center channel mode, the center channel information is divided equally between the left and

right speakers.

8000H

c000H

d2cdH

e000H

e959H

eff6H

f7f6H

ffffH

0000H

D15 to D0

+12.04

+6.02

+3.00

0

≠3.00

≠6.00

≠12.00

≠78.27

≠

Level [dB]

Table 8-1-8. KP, KH, KL, KR, KCP, KCH and KS

Setting Value Examples

The level of each channel can be adjusted by changing

the KP, KH, KL, KR, KCP and KCH setting values. In

these cases, be sure to change only the shaded portions

for each mode in Table 8-1-7.