| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CXD2930BR | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

GPS LSI with Built-in 32-bit RISC CPU

Description

The CXD2930BR is a dedicated LSI for the GPS

(Global Positioning System) satellite-based position

measurement system. This LSI contains a 32-bit

RISC CPU, RAM, UART, timer, etc.

This LSI, used together with an external ROM and

RF LSI (CXA1951AQ), enables the configuration of

a 3-chip system capable of measuring its position

anywhere on the globe.

Features

∑ 16-channel GPS receiver capable of simultaneously receiving 16 satellites

∑ Supports DARC system FM multiplexed differential GPS

∑ All-in-view measurement

∑ 2-satellite measurement

∑ Timer supporting GPS time

∑ High performance 32-bit RISC CPU

∑ 32K-byte RAM

∑ 3-channel UART

∑ Baud rate generator

∑ Supports 1.2K, 2.4K, 4.8K, 9.6K, 19.2K and 38.4K baud

∑ Supports 1/2/4-byte buffer mode

∑ 23-bit general-purpose I/O port capable of defining input/output independently for each bit

Structure

Silicon gate CMOS IC

Recommended Operating Conditions

∑ Supply voltage

V

DD

3.0 to 3.6

V

∑ Operating temperature

Topr ≠40 to +85

∞C

≠ 1 ≠

E98307A96-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXD2930BR

144 pin LQFP (Plastic)

≠ 2 ≠

CXD2930BR

Performance

∑ Reception frequency

1575.42MHz (L1 band, CA code)

∑ Reception sensitivity (using the CXA1951AQ in the RF block)

≠130dBm or less

∑ Time to first fix

(time until initial measurement after power-on)

Cold start (without ephemeris and almanac)

35 to 60s

Warm start (without ephemeris with almanac)

34 to 50s

Hot start (with ephemeris and almanac)

6 to 20s

Reacquisition time (interrupt recovery time)

Less than 5 minutes: < 3 to 6s

5 minutes or more: < 6 to 10s

∑ Positioning accuracy

Stand alone (GPS unit only)

1

: < 30m

3

: < 90m

DGPS (differential GPS)

1

: < 6m

3

: < 18m

∑ Measurement data update time

Every 1s

∑ Communication method

Sony standard serial communication

Supports NMEA

The noted values may be exceeded depending on the operating environment and other conditions.

The above performance values are as of February 1998. Sony reserves the right to change performance

without prior notice. Accordingly, the above performance values should be used only as reference data.

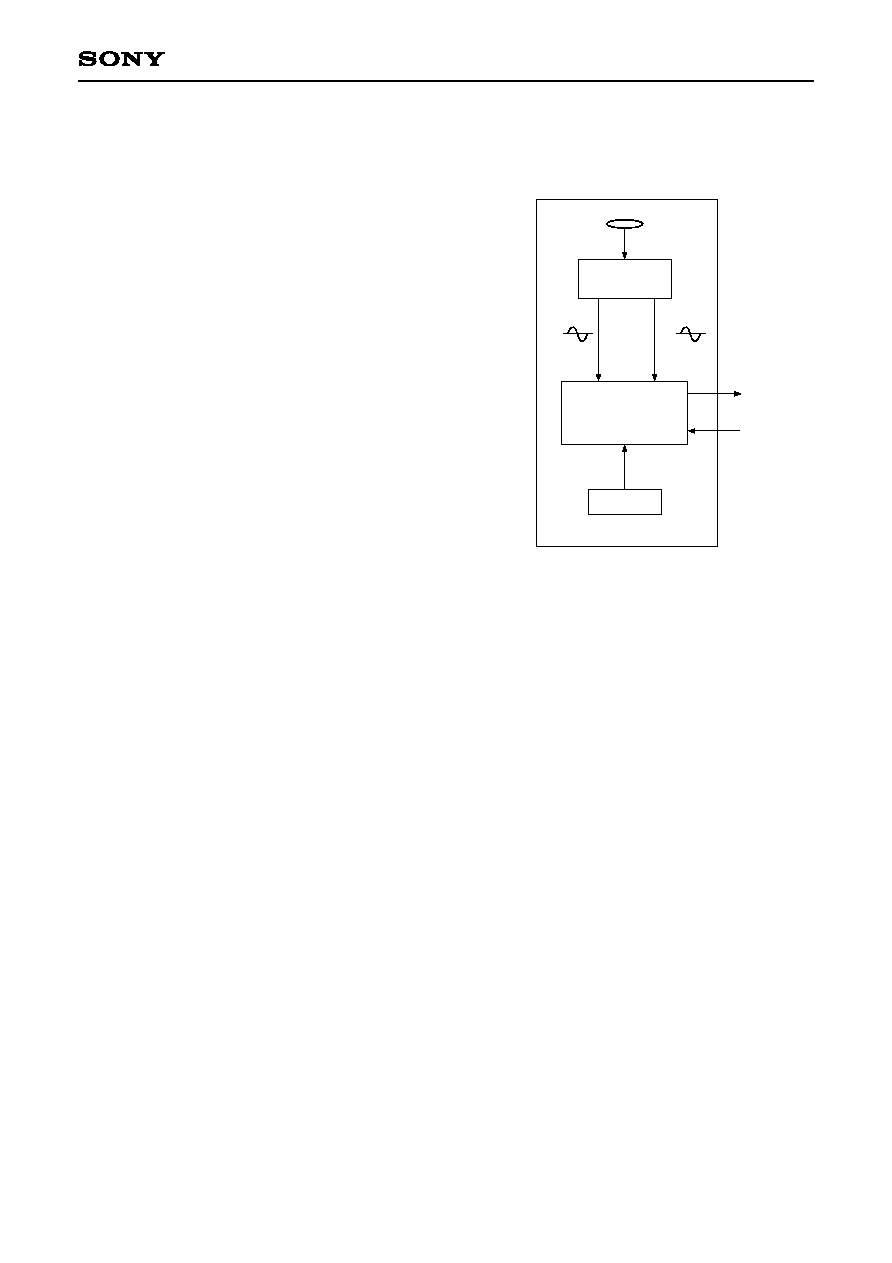

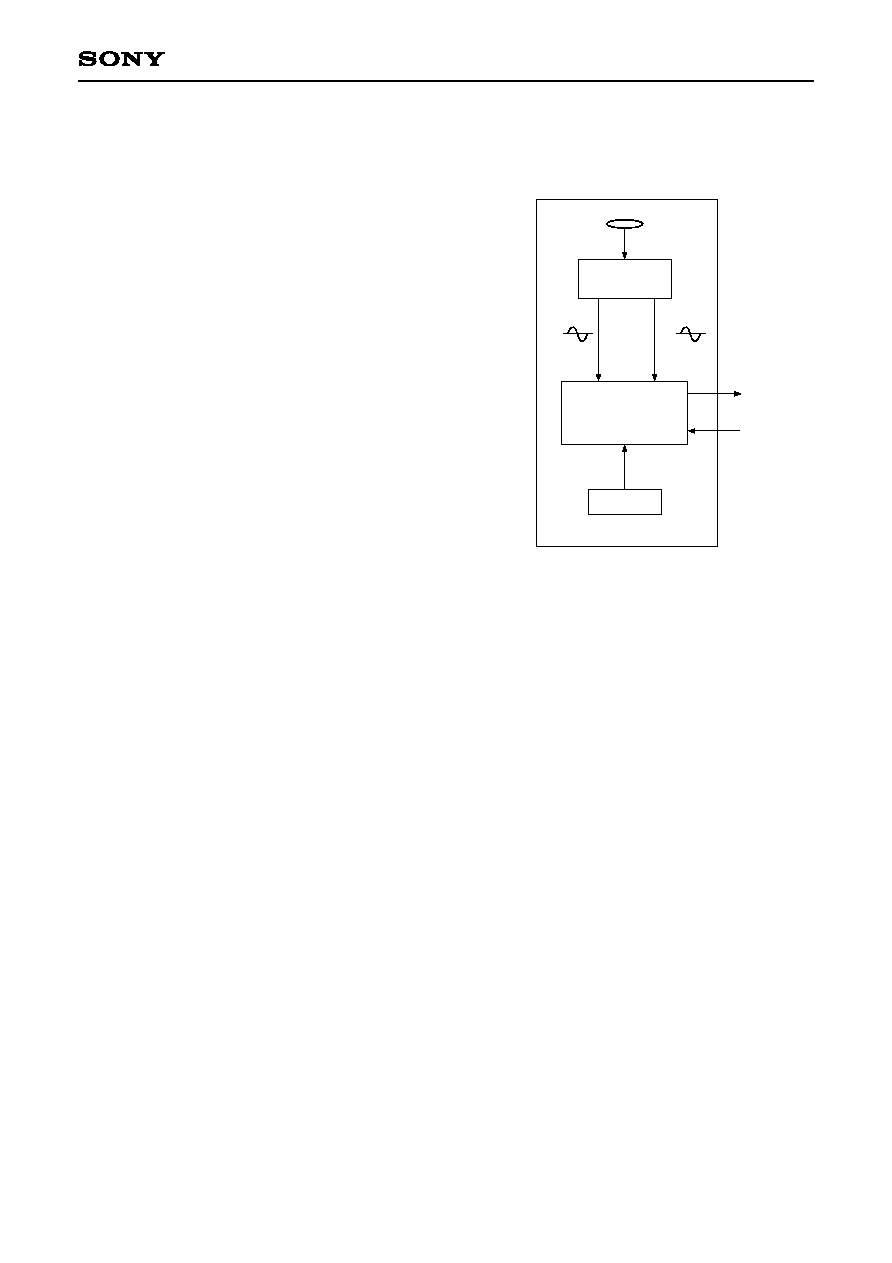

0V

CXA1951AQ

RF Converter

CXD2930BR

16ch GPS Processor

Flash ROM

2M bit

Antenna

GPS Receiver System Diagram Using the CXD2930BR

0V

TCXO

IF

TXD

RXD

≠ 3 ≠

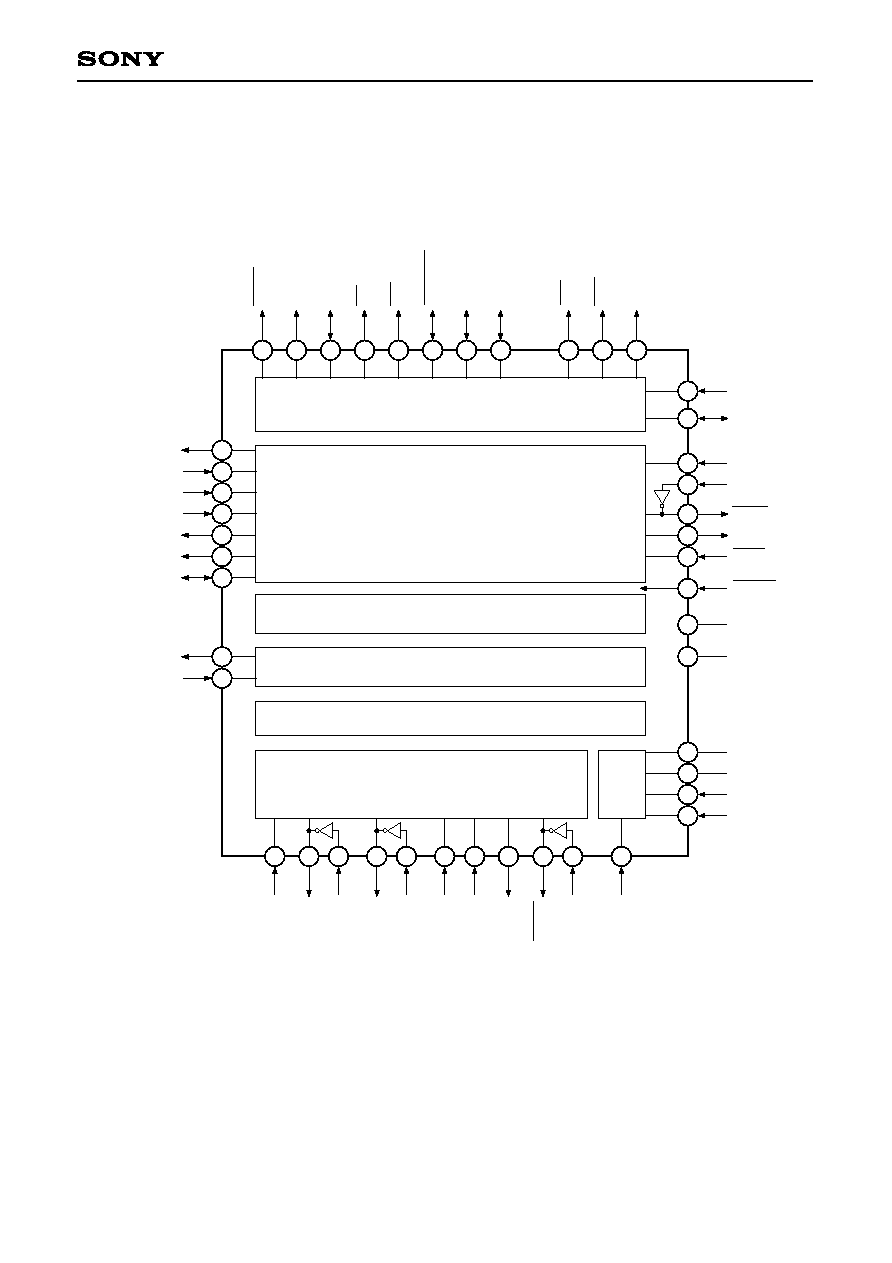

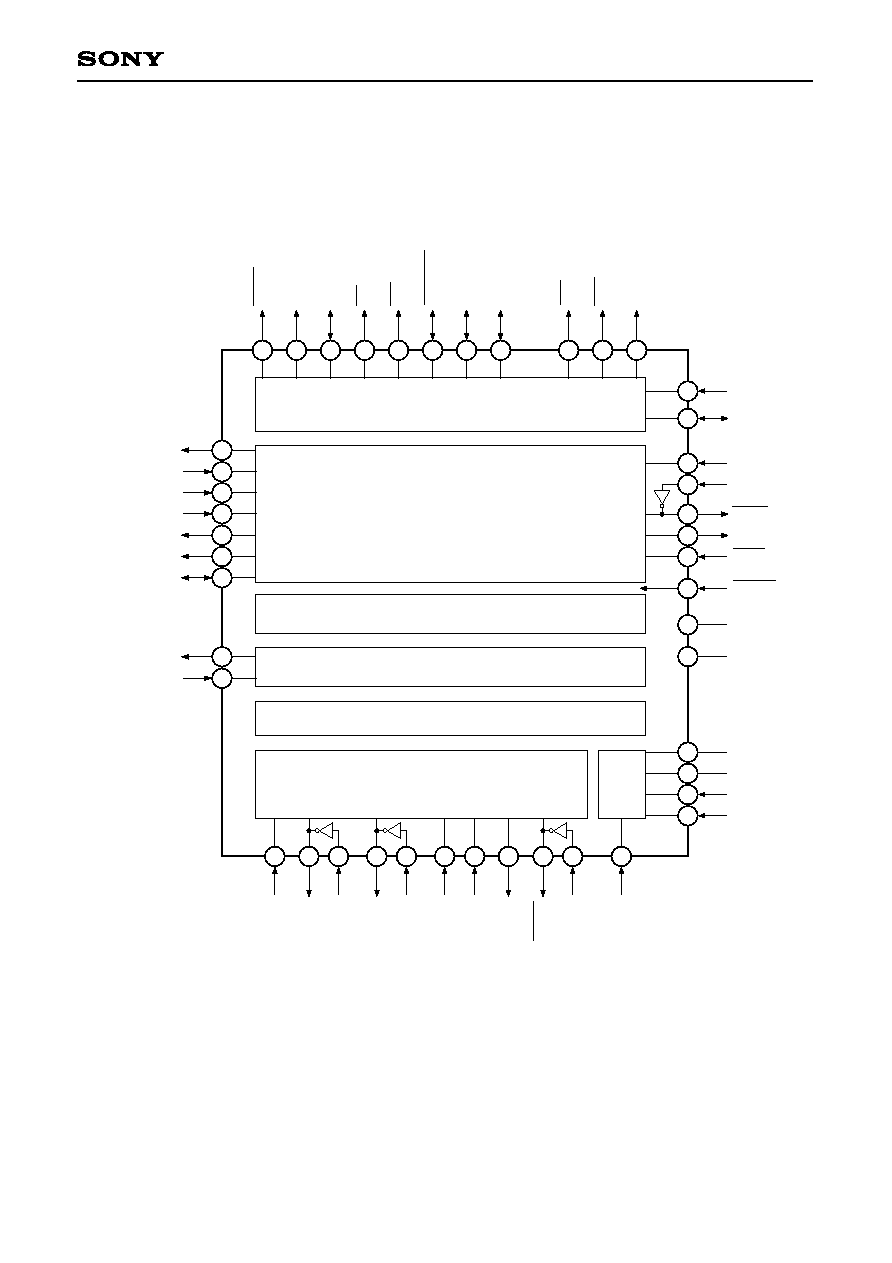

CXD2930BR

Block Diagram

I

C

S

0

,

1

I

A

D

R

(

0

:

1

8

)

I

B

(

0

:

1

5

)

I

R

D

I

W

R

D

C

S

0

t

o

5

/

P

O

R

T

(

1

6

:

2

1

)

D

A

D

R

(

0

:

1

5

)

D

B

(

0

:

7

)

D

R

D

D

W

R

X

C

S

0

TEST0 to 1

BIU

32 bit RISC

32K Byte SRAM

UART (Baud Rate Generator)

◊

3

TIMER

◊

3

16ch GPS DSP

8bit

ADC

PWRST

V

DD

◊

10

V

SS

◊

10

COSEL

MCKI

EXRS

AVD

AVS

VRT

VRB

PORT (0:15)

PMI

NMI

HOLD

SINT/PORT (22)

INBKOR

HOLDA

RUN

RXD0 to 2

TXD0 to 2

MCKO

CLKOUT

A

V

I

N

I

N

L

W

I

N

H

I

I

F

1

T

C

X

O

X

T

C

X

O

O

T

C

X

O

C

C

K

I

C

C

K

O

I

F

0

I

F

0

O

≠ 4 ≠

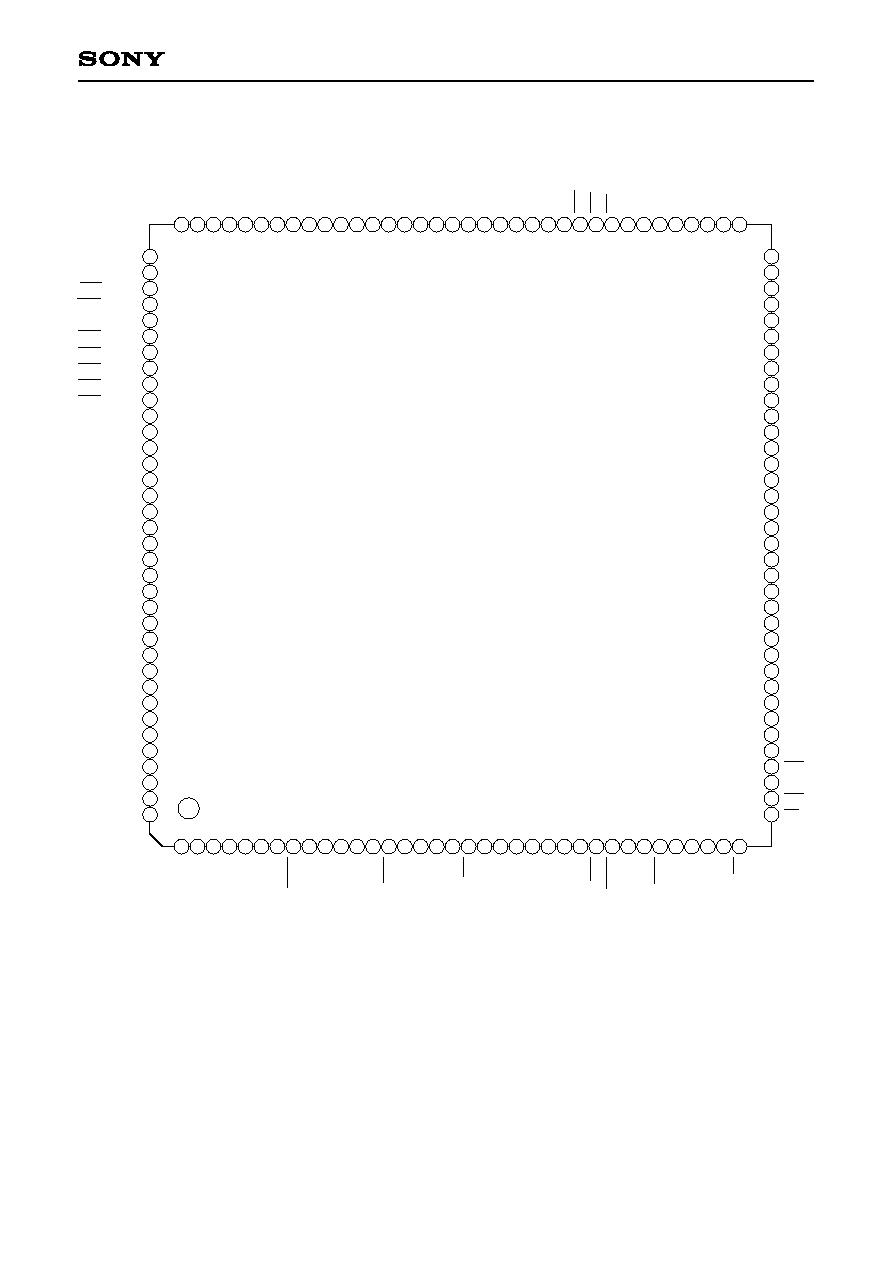

CXD2930BR

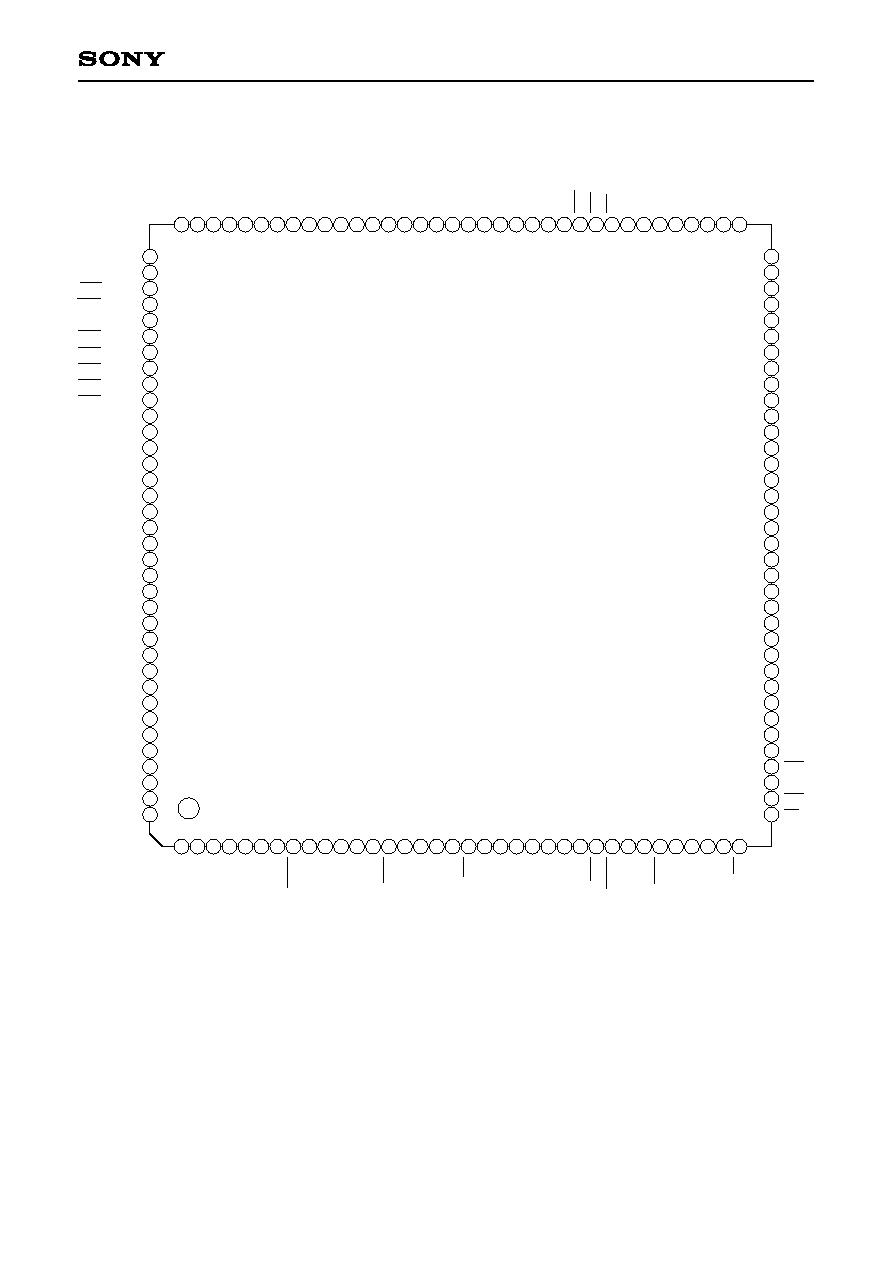

Pin Configuration

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

96

97

98

99

100

101

102

103

104

105

106

107

108

133

134

135

136

137

138

139

140

141

142

143

144

121

122

123

124

125

126

127

128

129

130

131

132

109

110

111

112

113

114

115

116

117

118

119

120

A

V

D

A

V

I

N

V

R

T

V

R

B

A

V

S

V

S

S

T

C

X

O

X

T

C

X

O

V

D

D

O

T

C

X

O

T

E

S

T

0

T

E

S

T

1

C

C

K

I

C

C

K

O

V

S

S

I

N

H

I

I

N

L

W

I

F

0

I

F

0

O

I

F

1

V

D

D

H

O

L

D

N

M

I

P

M

I

H

O

L

D

A

I

N

B

K

O

R

E

X

R

S

P

W

R

S

T

V

S

S

M

C

K

I

IADR18

IADR17

IADR16

IADR15

IADR14

IB3

IB2

IB1

V

DD

IB0

IB5

IB4

IB8

IB7

V

SS

IB6

IADR13

V

SS

IADR12

IADR11

IADR10

IADR9

IADR8

IADR7

IADR6

V

DD

IADR5

IADR4

IADR3

IADR2

IADR1

IADR0

ICS1

V

SS

ICS0

IRD

PORT14

V

SS

PORT13

PORT12

PORT11

91

92

93

94

95

DCS2/PORT19

DCS3/PORT18

DCS4/PORT17

DCS5/PORT16

PORT15

DCS1/PORT20

DB6

DB7

SINT/PORT22

DCS0/PORT21

V

DD

PORT10

PORT9

PORT8

PORT7

V

DD

PORT6

PORT5

PORT4

PORT3

PORT2

PORT1

PORT0

V

SS

TXD2

RXD2

TXD1

RXD1

TXD0

RXD0

V

DD

D

B

5

D

B

4

D

B

3

D

B

2

V

S

S

D

B

1

D

B

0

D

A

D

R

1

5

D

A

D

R

1

4

D

A

D

R

1

3

D

A

D

R

1

2

D

A

D

R

1

1

D

A

D

R

1

0

V

D

D

D

A

D

R

9

D

A

D

R

8

D

A

D

R

7

D

A

D

R

6

D

A

D

R

5

D

A

D

R

4

D

A

D

R

3

D

A

D

R

2

V

S

S

D

A

D

R

1

D

A

D

R

0

X

C

S

0

D

W

R

D

R

D

I

B

1

5

I

B

1

4

M

C

K

O

C

O

S

E

L

C

L

K

O

U

T

V

D

D

R

U

N

I

W

R

I

B

1

3

I

B

1

2

I

B

1

1

V

D

D

I

B

1

0

I

B

9

≠ 5 ≠

CXD2930BR

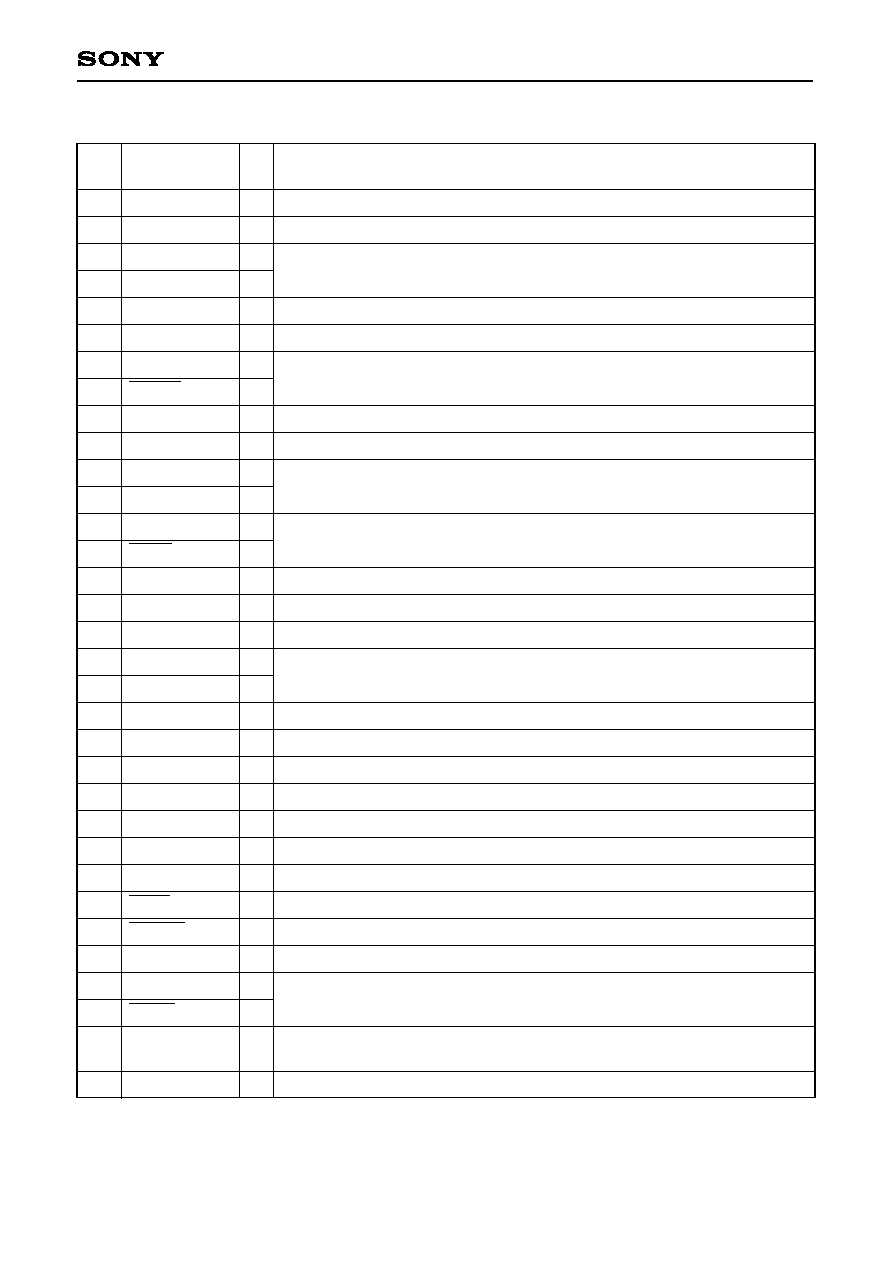

Pin Configuration

A/D converter power supply.

Analog input.

Reference input.

A/D converter GND.

GND

TCXO binary conversion circuit/crystal oscillator.

Power supply.

TCXO clock output.

Test. Fixed to low level.

Timer oscillation circuit. (32.768kHz ± 100ppm)

GND

Fixed to low level.

Fixed to low level.

IF signal binary conversion circuit.

IF signal input 1. Input the binary-converted input signal.

Power supply.

Hold input signal. Hold when high level.

Non maskable interrupt.

Power management interrupt.

Hold acknowledge signal.

Break signal for debugging.

Reset input signal.

Connect to main power supply. Leave open during backup.

GND

CPU clock oscillation circuit.

CPU clock select signal. Selects TCXO clock when low level; MCK clock when

high level.

CPU clock output.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

AVD

AVIN

VRT

VRB

AVS

V

SS

TCXO

XTCXO

V

DD

OTCXO

TEST0

TEST1

CCKI

CCKO

V

SS

INHI

INLW

IF0

IF0O

IF1

V

DD

HOLD

NMI

PMI

HOLDA

INBKOR

EXRS

PWRST

V

SS

MCK

MCKO

COSEL

CLKOUT

--

I

I

I

--

I

I

O

--

O

I

I

I

O

--

I

I

I

O

I

--

I

I

I

O

O

I

I

--

I

O

I

O

Pin

No.

Symbol

I/O

Description