1

E01739

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

CXR702F080

176 pin LFLGA (Plastic)

CMOS 32-bit Single Chip Microcomputer

Description

The CXR702F080 is a CMOS 32-bit microcomputer

integrating on a single chip an A/D converter, serial

interface, timer, bus interface unit, DMA controller,

memory stick interface, and as well as basic

configurations like a 32-bit RISC CPU, ROM, RAM,

and I/O port.

This also provides the idle/sleep/stop functions that

enable lower power consumption.

Features

· CPU

SR11 series 32-bit RISC CPU core

· Minimum instruction cycle

54.3ns (f

SRC

: 18.432MHz)

30.5µs (f

TEX

: 32.768kHz)

· Incorporated FLASH EEPROM

256K bytes

· Incorporated RAM

16K bytes

· Peripheral functions

-- Bus interface unit

-- DMA controller

4 channels

-- A/D converter

8-bit 4-analog input, successive approximation system

-- Serial interface

Clock synchronization, 2 channels

Clock synchronization, 1 channel (Incorporated 64-byte buffer RAM)

Asynchronization, 2 channels

-- Timers

8-bit timer, 8 channels

16-bit capture timer, 3 channels

8-bit time-base timer

Clock prescaler

16-bit watchdog timer

-- Memory stick interface

-- Beep output circuit

-- External interruption

11 channels (polarity selection and both edge detection possible)

· Standby mode

Idle/sleep/stop

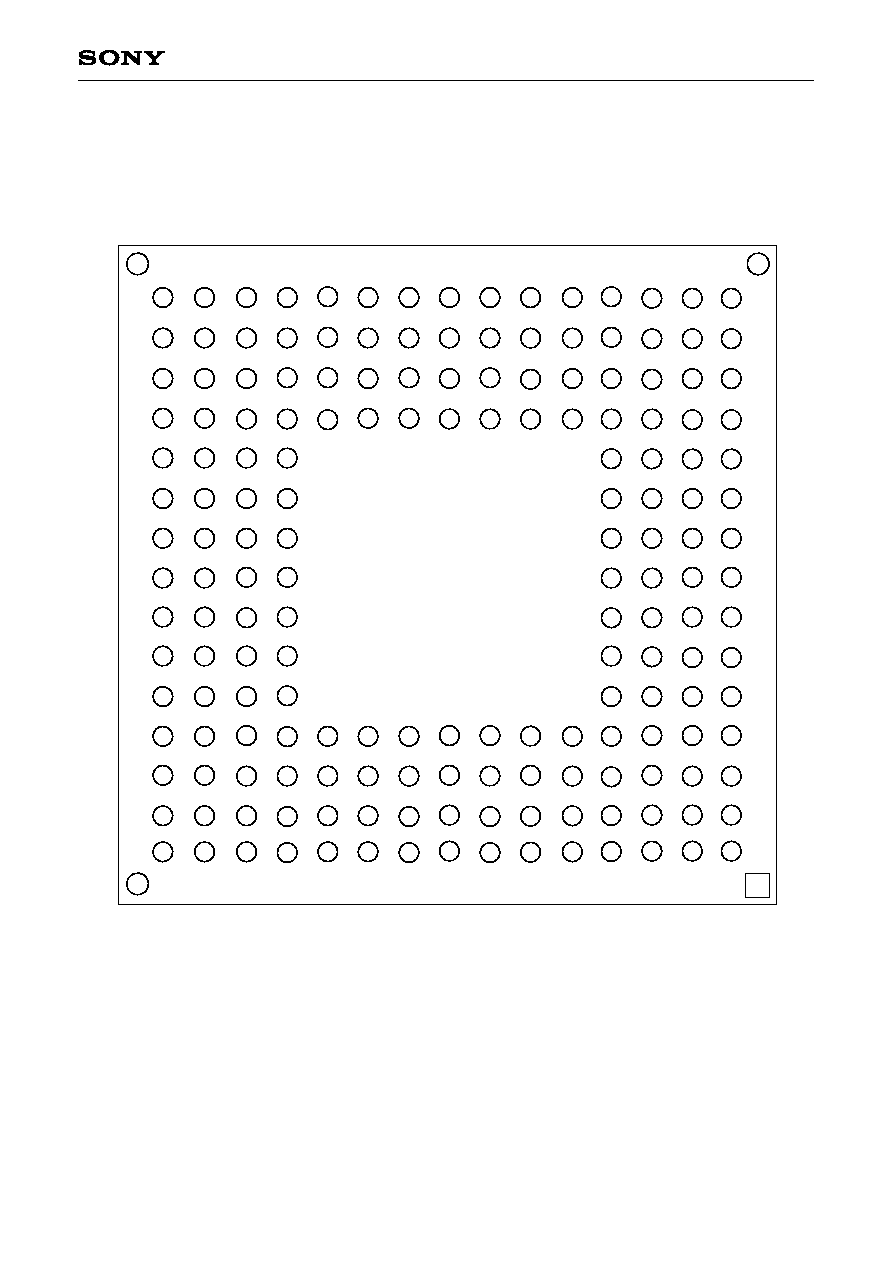

· Package

176-pin plastic LFLGA

Structure

Silicon gate CMOS IC

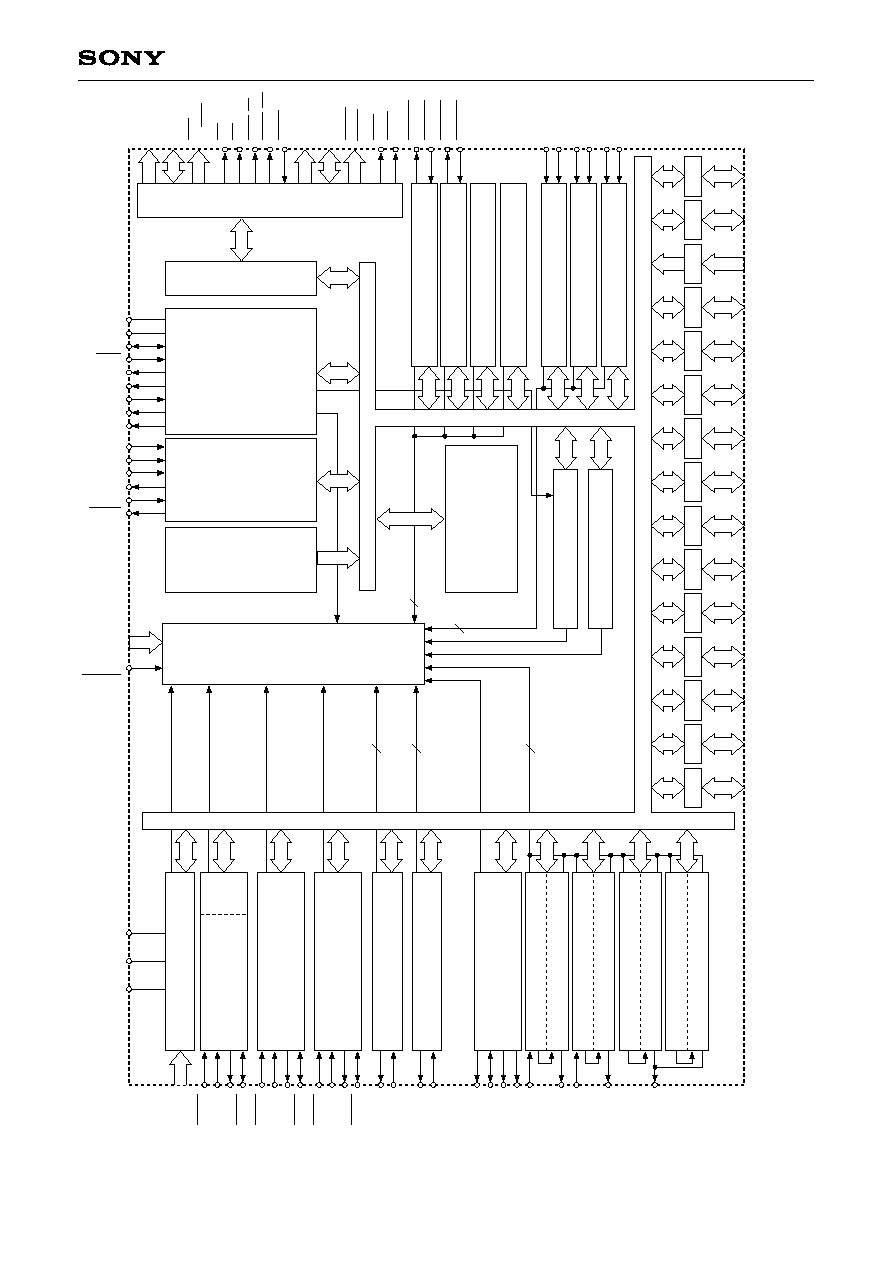

2

CXR702F080

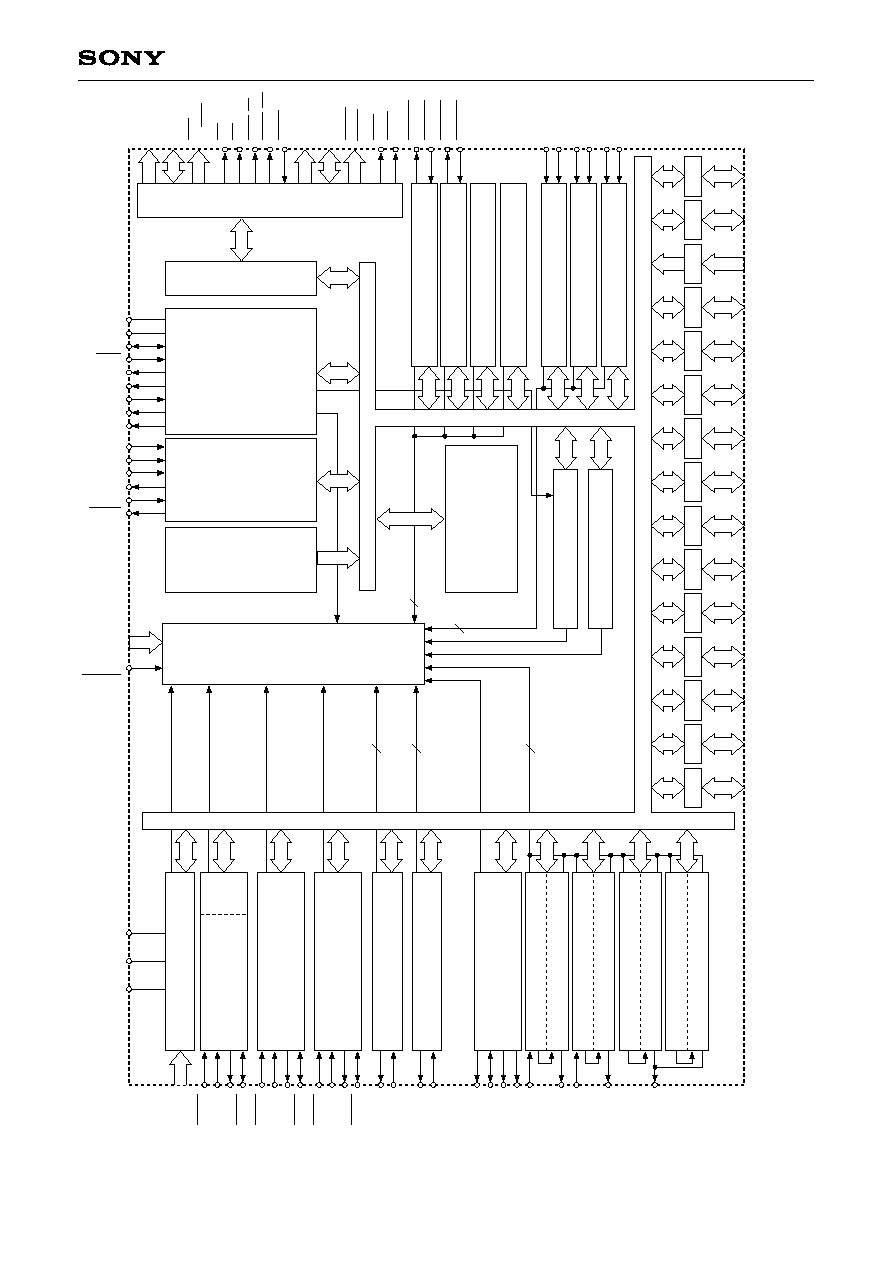

Bloc

k Dia

gram

3

POR

T M

8

2

19

16

8

24

SERIAL INTERF

A

C

E

UNIT (CH0)

RAM

INTERRUPT CONTR

OLLER

U

A

R

T

(CH0)

SCS0

AN0

to AN3

INT0

to INT9

SI0

SO0

SCK0

SCS1

SI1

SO1

EC0

T1

MSSCLK

MSIDR

MSDIO

MSBS

SCK1

A0

to A23

D0

to D15

CS0

to CS7

RD

WE

L

WR/LB

UWR/UB

W

AIT

10

8-BIT TIMER/COUNTER

(CH0)

8-BIT TIMER

(CH1)

SERIAL INTERF

A

C

E

UNIT (CH1)

MEMOR

Y STICK INTERF

A

C

E

8-BIT TIMER/COUNTER

(CH2)

8-BIT TIMER

(CH3)

8-BIT TIMER

(CH4)

8-BIT TIMER

(CH5)

8-BIT TIMER

(CH6)

8-BIT TIMER

(CH7)

TDI

TMS

TCK

TEX

TX

EXT AL

XT AL

V

DD

V

SS

AV

REF

AV

DD

AV

SS

TDO

RTCK

TXOUT

XOUT

EC2

T3

BEEP

SCS2

SI2

SO2

SCK2

SERIAL INTERF

A

C

E

UNIT (CH2)

U

A

R

T

(CH1)

TxD1

RxD1

TxD0

RxD0

A/D CONVER

TER

2

2

2

2

8

1

3

1

6

RAM

16K BYTES

EXTERNAL BU

S

DMA

C (CH0)

DMA

C (CH1)

DMA

C (CH2)

DMA

C (CH3)

16-BIT CAPTURE

TIMER (CH0)

16-BIT CAPTURE

TIMER (CH1)

16-BIT CAPTURE

TIMER (CH2)

T

OKEI PRESCALER

W

A

TCHDOG TIMER

TRST

MSINS

POR

T N

8

POR

T O

4

POR

T L

7

POR

T K

8

POR

T J

8

POR

T I

8

POR

T H

4

POR

T G

6

POR

T F

6

POR

T E

8

POR

T D

4

POR

T C

6

POR

T B

8

POR

T A

6

RST

D

A

CK0

DREQ0

MA0

to MA18

MD0

to MD7

MCS0,

MCS1

CT0ED0

CT0ED1

CT1ED0

CT1ED1

CT2ED0

CT2ED1

D

A

CK1

DREQ1

MRD

MWE

CLOCK GENERA TOR/

SYSTEM CONTROLLER

BUS INTERF

ACE UNIT

ARM7TDMI

CPU CORE

FLASH EEPROM

256K BYTES

1

2

4

1

The n

umber of causes of interr

upts generated from the module is as sho

wn.

But the number of causes input to the interr

upt contr

oller diff

ers from the shown becauses of OR.

2

A par

t of the interr

upt signals gener

ated from U

A

R

T

, MEMOR

Y STICK INTERF

A

CE is input to the interr

upt controller via DMA depend

ing on applications

.