| ÐлекÑÑоннÑй компоненÑ: ICX082AL | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

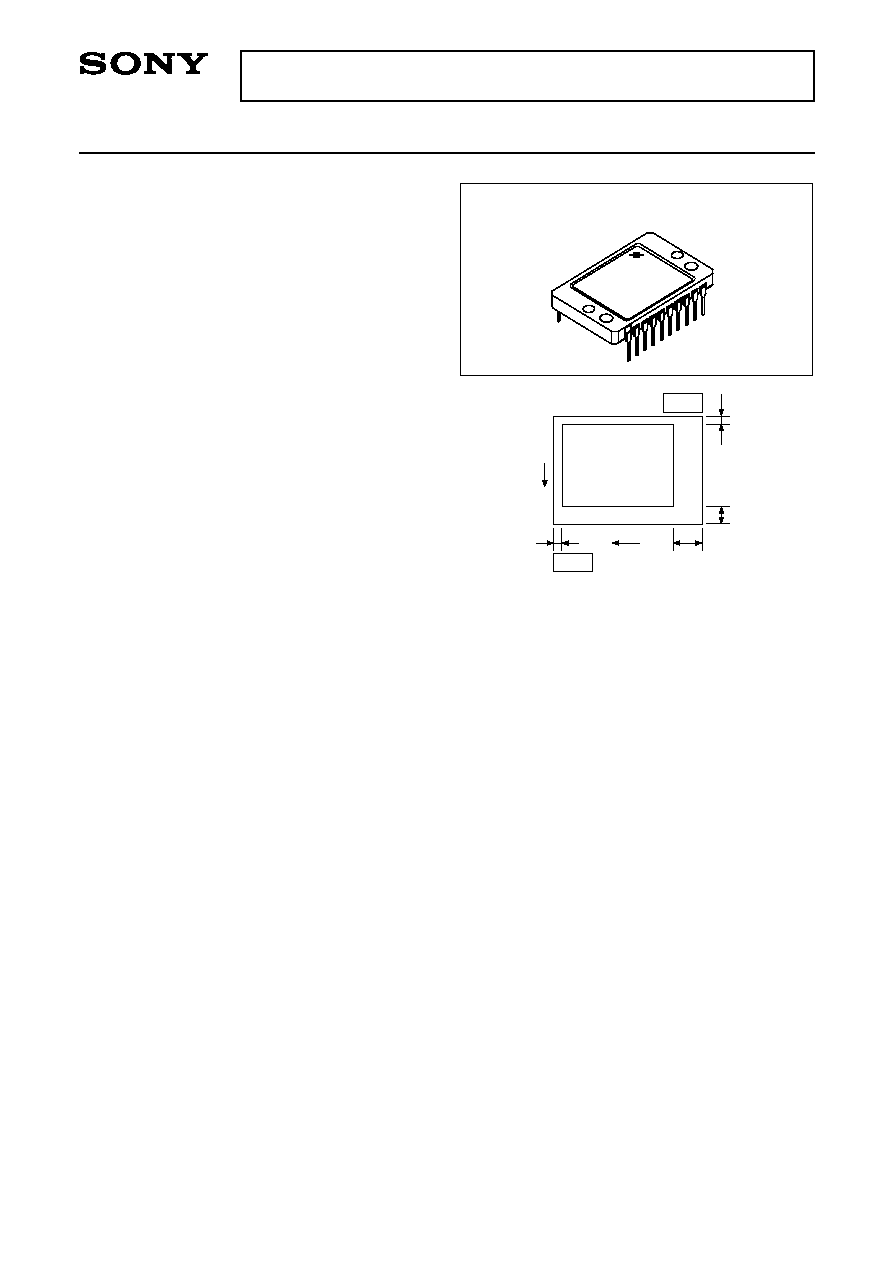

Description

The ICX082AL is an interline CCD solid-state

image sensor suitable for EIA black-and-white video

cameras with a diagonal 11mm (Type 2/3) system.

High sensitivity and low dark current are achieved

through the adoption of HAD (Hole-Accumulation

Diode) sensors.

This chip features a field period readout system

and an electronic shutter with variable charge-

storage time.

Features

· High sensitivity (+6dB compared with the ICX022BL)

· Low smear (20dB compared with the ICX022BL)

· High resolution, Low dark current

· Excellent antiblooming characteristics

· Continuous variable-speed shutter

Device Structure

· Interline CCD image sensor

· Image size:

Diagonal 11mm (Type 2/3)

· Number of effective pixels:

768 (H)

×

494 (V)

approx. 380K pixels

· Total number of pixels:

811 (H)

×

508 (V)

approx. 410K pixels

· Chip size:

10.25mm (H)

×

8.5mm (V)

· Unit cell size:

11.6µm (H)

×

13.5µm (V)

· Optical black:

Horizontal (H) direction: Front 3 pixels, rear 40 pixels

Vertical (V) direction:

Front 12 pixels, rear 2 pixels

· Number of dummy bits:

Horizontal 22

Vertical 1 (even fields only)

· Substrate material:

Silicon

1

ICX082AL

E95935C99

Diagonal 11mm (Type 2/3) CCD Image Sensor for EIA Black-and-White Video Cameras

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

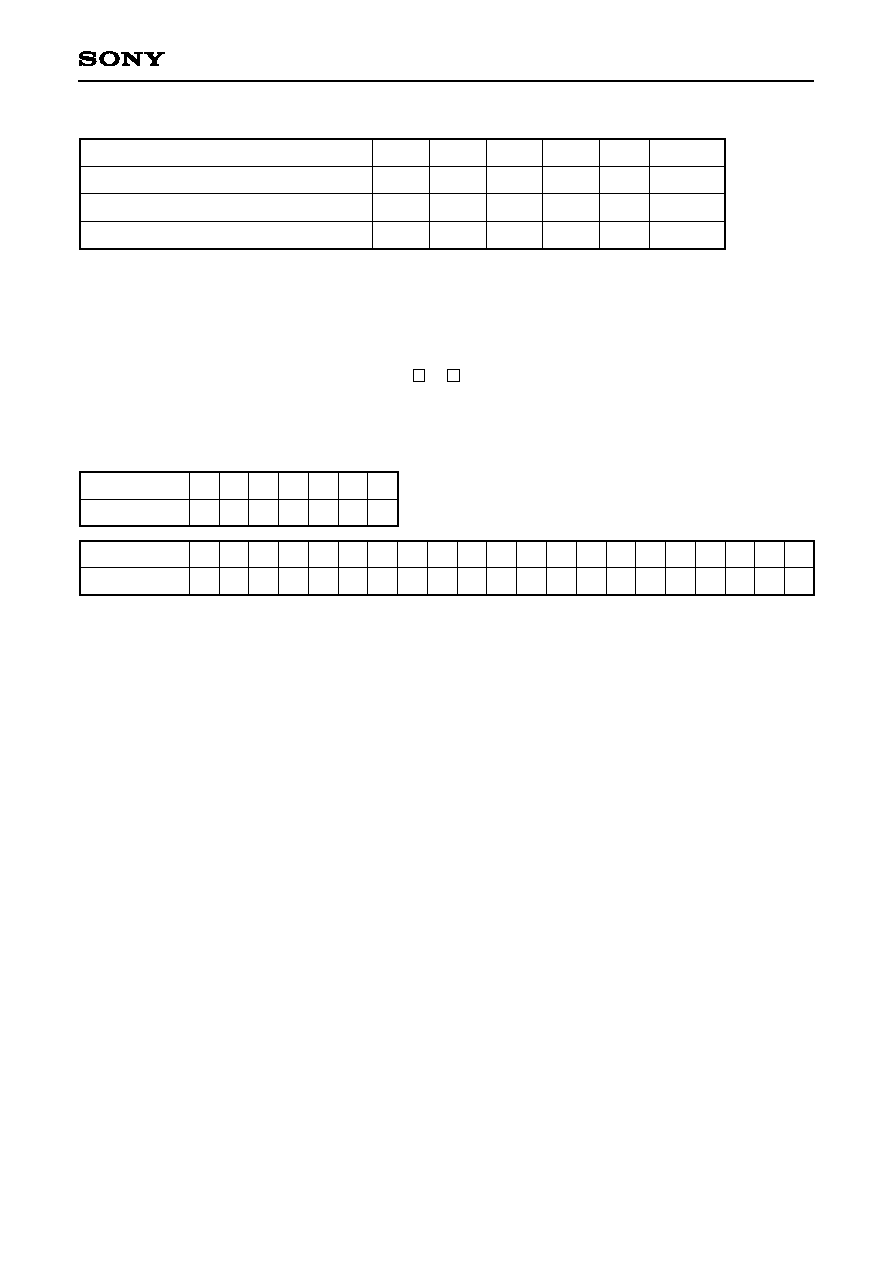

20 pin DIP (Ceramic)

Pin 1

V

3

40

2

12

Pin 11

H

Optical black position

(Top View)

2

ICX082AL

Pin No.

Symbol

Description

Description

Pin No.

Symbol

Pin Description

Vertical register transfer clock

Vertical register transfer clock

Vertical register transfer clock

Substrate (overflow drain)

GND

Vertical register transfer clock

Protective transistor bias

GND

Output amplifier drain power

1

2

3

4

5

6

7

8

9

10

V

4

V

3

V

2

SUB

GND

V

1

V

L

NC

GND

V

DD

11

12

13

14

15

16

17

18

19

20

V

OUT

V

GG

V

SS

GND

RD

RG

V

L

H

1

H

2

HIS

Signal output

Output amplifier gate bias

Output amplifier source

GND

Reset drain

Reset gate clock

Protective transistor bias

Horizontal register transfer clock

Horizontal register transfer clock

Horizontal register input source bias

Block Diagram and Pin Configuration

(Top View)

1

2

3

4

5

6

9

7

10

11

12

13

14

Note)

GND

V

DD

SUB

RG

H

1

15

16

17

18

19

20

HIS

V

OUT

V

4

V

3

V

2

V

1

V

L

GND

V

GG

V

SS

GND

RD

H

2

V

L

V

e

r

t

i

c

a

l

R

e

g

i

s

t

e

r

Horizontal Register

Note) : Photo sensor

O

u

t

p

u

t

U

n

i

t

3

ICX082AL

Item

0.3 to +55

0.3 to +20

55 to +10

15 to +20

to +10

to +15

to +17

17 to +17

10 to +15

55 to +10

65 to +0.3

0.3 to +30

0.3 to +24

0.3 to +20

30 to +80

10 to +60

V

V

V

V

V

V

V

V

V

V

V

V

V

V

°C

°C

1

Ratings

Unit

Remarks

Absolute Maximum Ratings

1

+27V (Max.) when clock width < 10µs, clock duty factor < 0.1%.

Substrate voltage SUB GND

HIS, V

DD

, RD, V

OUT

, V

SS

GND

HIS, V

DD

, RD, V

OUT

, V

SS

SUB

Vertical clock input pins GND

Vertical clock input pins SUB

Voltage difference between vertical clock input pins

Voltage difference between horizontal clock input pins

H

1

, H

2

V

4

H

1

, H

2,

RG, V

GG

GND

H

1

, H

2,

RG, V

GG

SUB

V

L

SUB

V

1

, V

3

, HIS, V

DD

, RD, V

OUT

V

L

RG V

L

V

2

, V

4

, V

GG

, V

SS

, H

1

, H

2

V

L

Storage temperature

Operating temperature

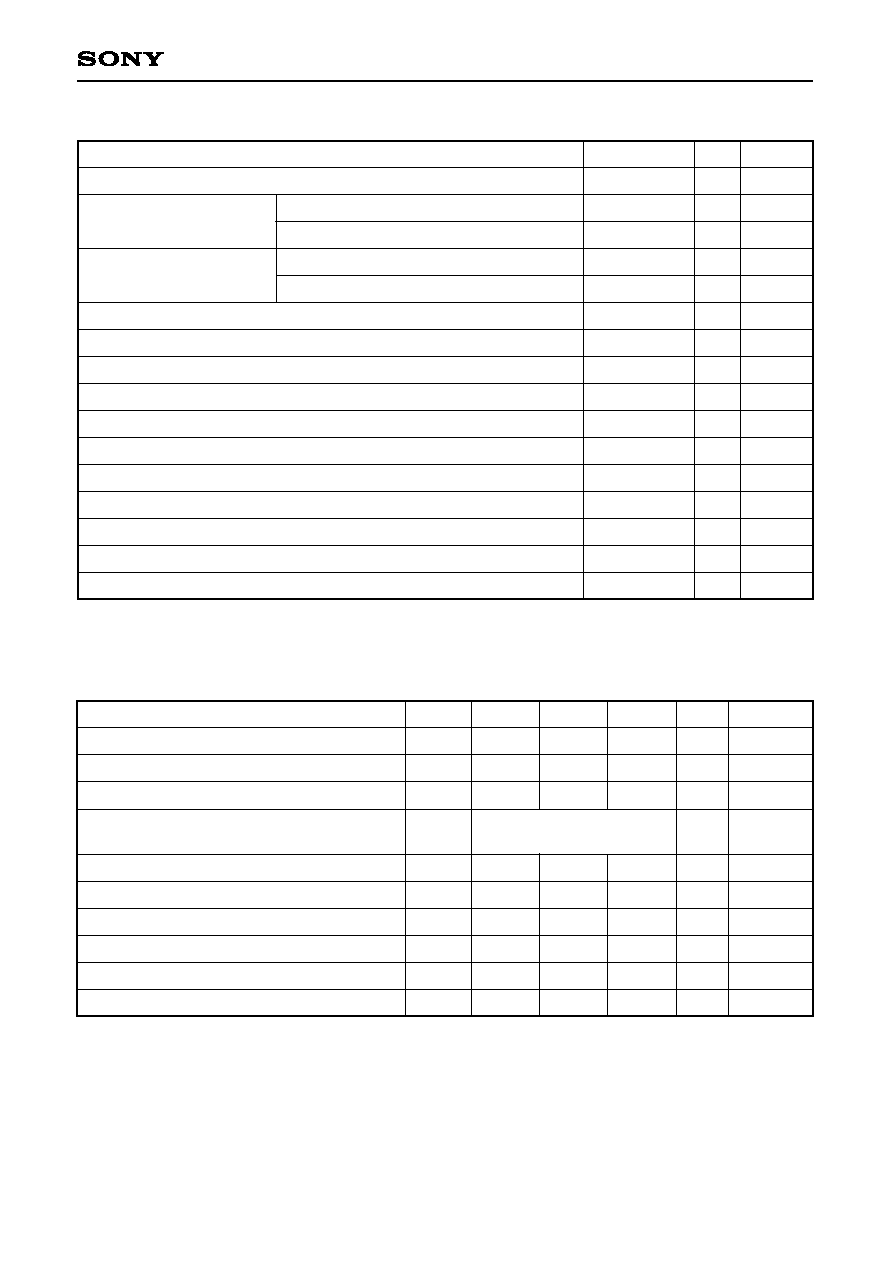

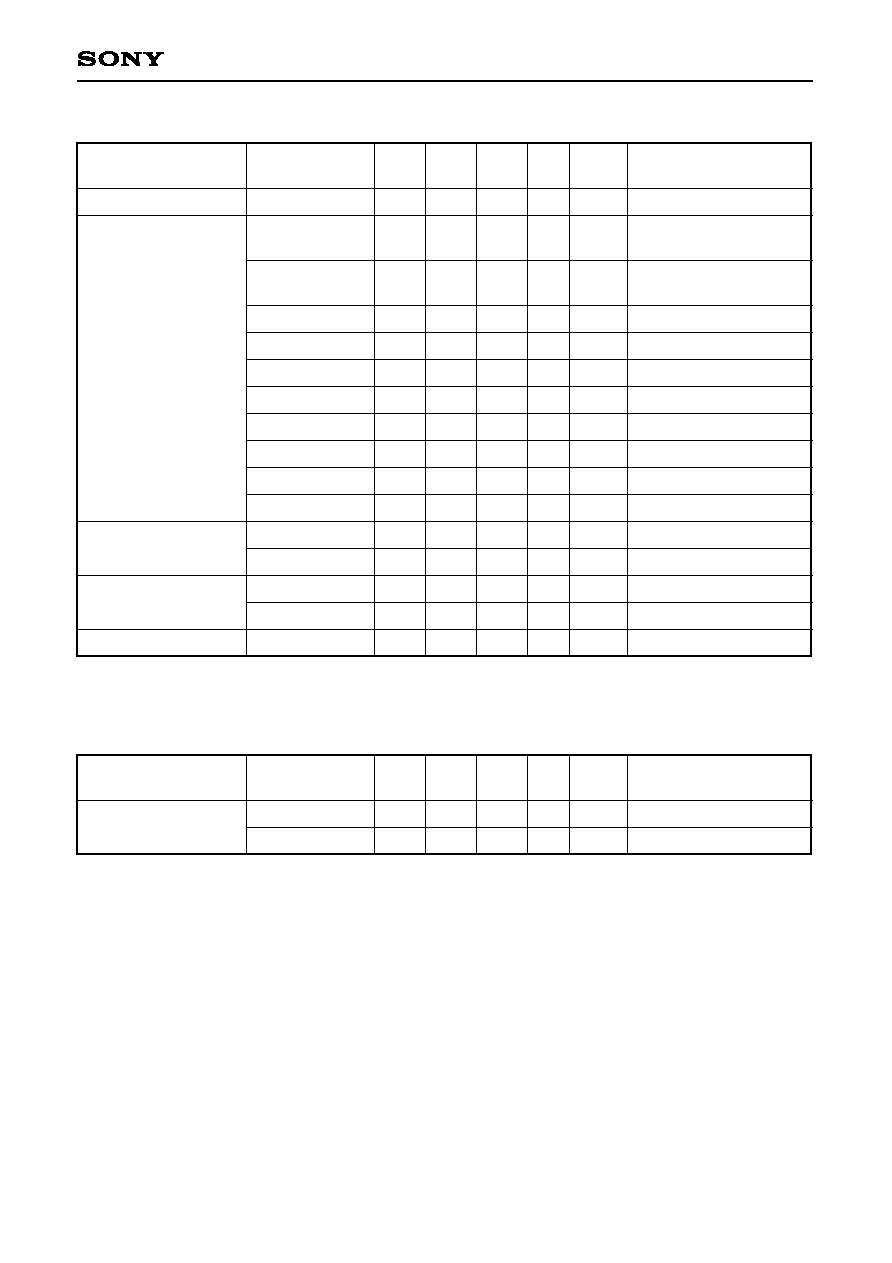

Item

V

DD

V

RD

V

GG

V

SS

V

SUB

V

SUB

V

RGL

V

RGL

V

L

V

HIS

Grounded with

750

resistor

V

V

V

V

%

V

%

V

V

V

RD

= V

DD

±5%

2

2

3

V

HIS

= V

DD

Symbol

Min.

Unit

Remarks

Bias Conditions

Output amplifier drain voltage

Reset drain voltage

Output amplifier gate voltage

Output amplifier source

Substrate voltage adjustment range

Substrate voltage adjustment precision

Reset gate clock voltage adjustment range

Reset gate clock voltage adjustment precision

Protective transistor bias

Horizontal register input source bias

14.7

14.7

3.8

Typ.

Max.

15.0

15.0

4.2

15.3

15.3

4.6

9

3

0

3

11

14.7

10.5

15.0

19

+3

3.0

+3

10

15.3

Supply voltage

Vertical clock input voltage

4

ICX082AL

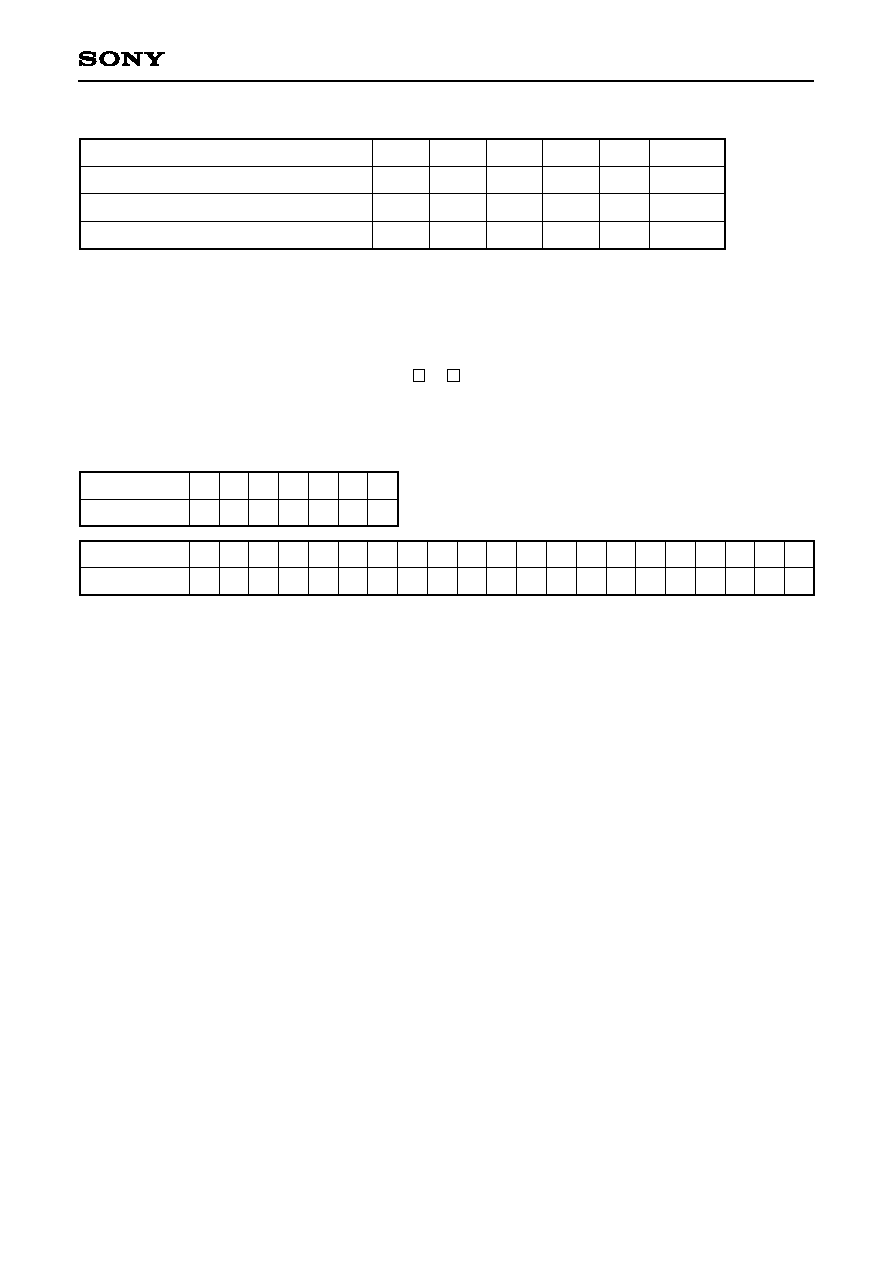

2

Indications of substrate voltage (V

SUB

) and reset gate clock voltage (V

RGL

) setting value

The setting value of the substrate voltage and reset gate clock voltage are indicated on the back of the

image sensor by a special code. Adjust the substrate voltage (V

SUB

) and reset gate clock voltage (V

RGL

) to

the indicated voltage. The adjustment precision is ±3%.

V

SUB

code -- one character indication

V

RGL

code -- one character indication

V

RGL

code

V

SUB

code

"Code" and optimal setting correspond to each other as follows.

DC Characteristics

<Example> "5K"

V

RGL

= 2.0V

V

SUB

= 12.0V

3

This must no exceed the V

VL

voltage of the vertical clock waveform.

4

1) Current to each pin when 20V is applied to V

DD

, RD, V

OUT

, V

SS

, HIS and SUB pins, while pins that are

not tested are grounded.

2) Current to each pin when 20V is applied sequentially to V

1

, V

2

, V

3

and V

4

pins, while pins that are

not tested are grounded. However, 20V is applied to SUB pin.

3) Current to each pin when 15V is applied sequentially to H

1

, H

2

, RG and V

GG

pins, while pins that are

not tested are grounded. However, 15V is applied to SUB pin.

4) Current to V

L

pin when 30V is applied to V

1

, V

3

, HIS, V

DD

, RD and V

OUT

pins or when, 24V is applied

to RG pin or when, 20V is applied to V

2

, V

4

, V

GG

, V

SS

, H

1

and H

2

pins, while V

L

pin is grounded.

However, GND and SUB pins are left open.

5

Current to SUB pin when 55V is applied to SUB pin, while pins that are not tested are grounded.

Item

Output amplifier drain current

Input current

Input current

I

DD

I

IN1

I

IN2

6

1

10

mA

µA

µA

4

5

Symbol

Min.

Typ.

Max.

Unit

Remarks

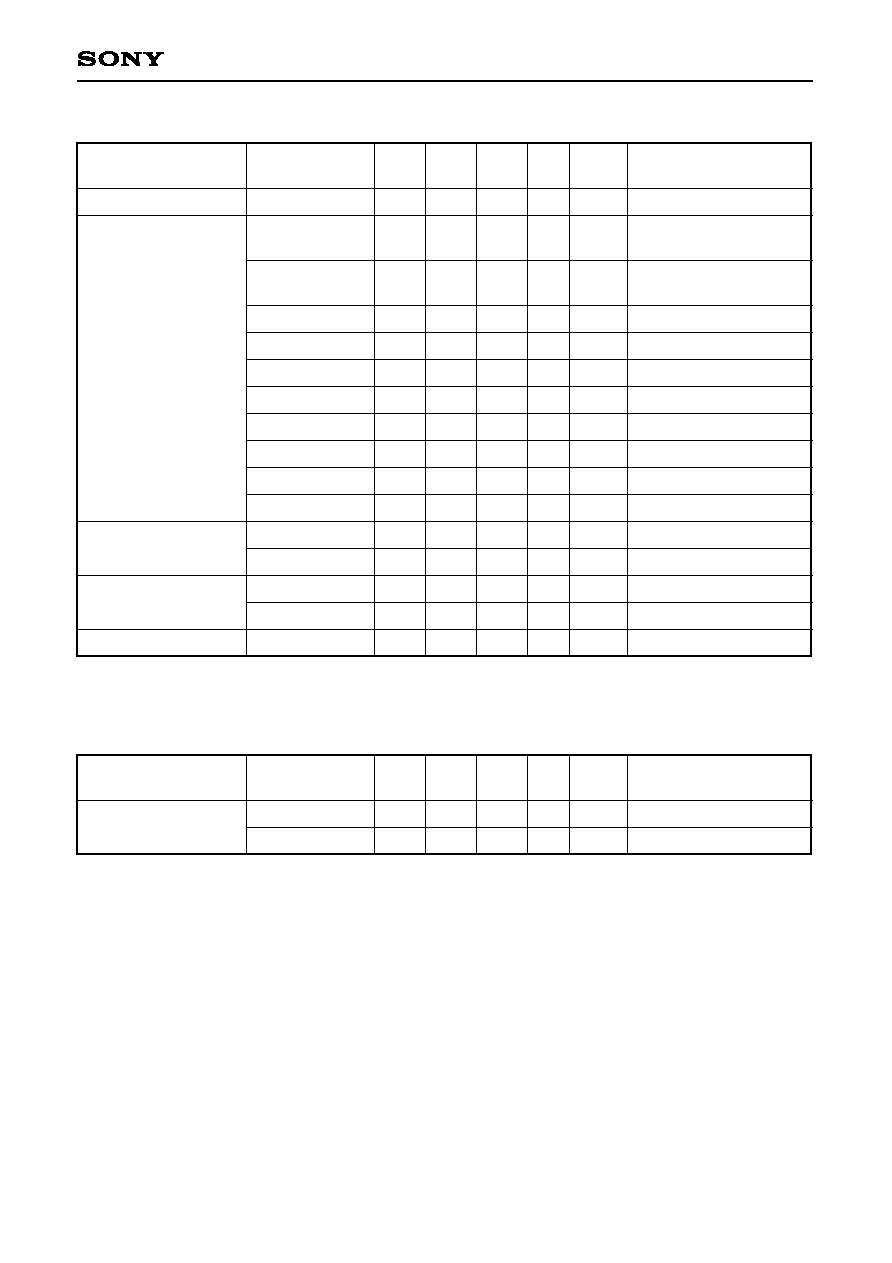

V

RGL

code

Optimal setting

0

0.5 1.0 1.5 2.0 2.5 3.0

1

2

3

4

5

6

7

V

SUB

code

Optimal setting 9.0 9.5 10.010.511.011.512.0

D

E

f

G

h

J

K

L

m

N

P

Q

R

S

T

U

V

W

X

Y

Z

12.513.013.514.014.515.015.516.016.517.017.518.018.519.0

5

ICX082AL

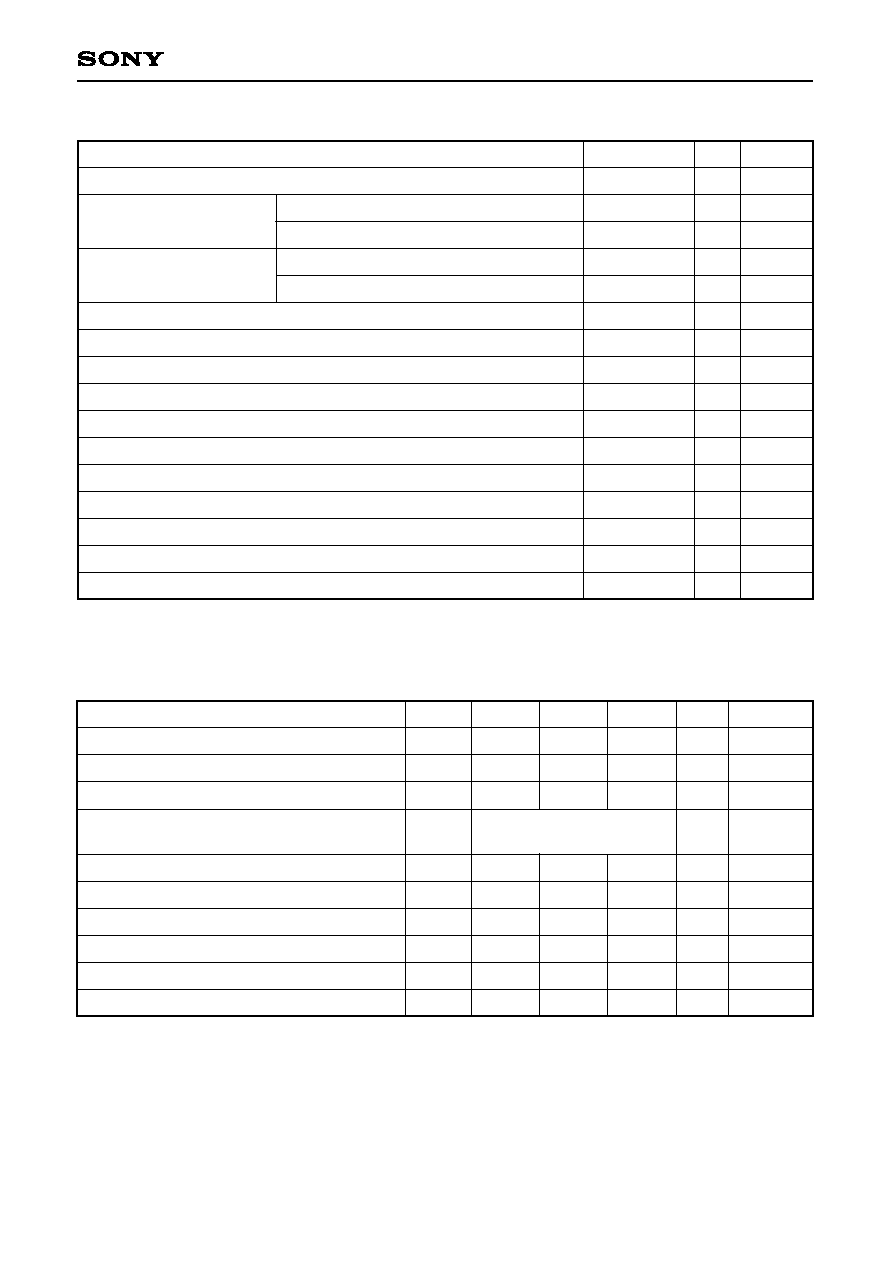

Item

V

VT

V

VH1

, V

VH2

,

V

VH3

, V

VH4

V

VL1

, V

VL2

,

V

VL3

, V

VL4

V

V

| V

VH1

V

VH2

|

V

VH3

V

VH

V

VH4

V

VH

V

VHH

V

VHL

V

VLH

V

VLL

V

H

V

HL

V

RG

V

RGL

V

SUB

14.5

0.6

8.9

0.5

0.5

6.0

3.5

6.0

0

27.0

15.0

9.6

15.5

0

0.2

0

0

0.8

1.0

0.8

0.8

8.0

3.0

13.0

3.0

32.0

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

1

2

2

2

2

2

2

2

2

2

2

3

3

3

3

4

V

VH

= (V

VH1

+ V

VH2

)/2

V

VL

= (V

VL3

+ V

VL4

)/2

V

V

= V

VH

n V

VL

n (n = 1 to 4)

High-level coupling

High-level coupling

Low-level coupling

Low-level coupling

1

Readout clock voltage

Vertical transfer clock

voltage

Horizontal transfer

clock voltage

Reset gate clock

voltage

Substrate clock voltage

Symbol

Min.

Typ.

Max.

Unit

Waveform

diagram

Remarks

Clock Voltage Conditions

1

The reset gate clock voltage need not be adjusted when the reset gate clock is driven when the

specifications are as given below. In this case, the reset gate clock voltage setting indicated on the back of

the image sensor has not significance.

Reset gate clock

voltage

Item

Symbol

Min.

Typ.

Max.

Unit

Waveform

diagram

Remarks

V

RGL

V

RG

0.2

8.5

0

9.0

0.2

9.5

V

V

3

3