Publication Number S29GLxxxA_00

Revision A Amendment 2 Issue Date January 28, 2005

ADVANCE

INFORMATION

S29GLxxxA MirrorBitTM Flash Family

S29GL064A, S29GL032A

64 Megabit, 32 Megabit 3.0, Volt-only Page Mode Flash

Memory Featuring 200 nm MirrorBit Process Technology

Data Sheet

Notice to Readers: The Advance Information status indicates that this

document contains information on one or more products under development

at Spansion LLC. The information is intended to help you evaluate this product.

Do not design in this product without contacting the factory. Spansion LLC

reserves the right to change or discontinue work on this proposed product

without notice.

This page intentionally left blank.

This document contains information on one or more products under development at Spansion LLC. The information is intended to help you evaluate this product. Do not

design in this product without contacting the factory. Spansion LLC reserves the right to change or discontinue work on this proposed product without notice.

Publication Number S29GLxxxA_00 Revision A Amendment 2 Issue Date January 28, 2005

ADVANCE

INFORMATION

S29GLxxxA MirrorBitTM Flash Family

S29GL064A, S29GL032A

64 Megabit, 32 Megabit 3.0, Volt-only Page Mode Flash

Memory Featuring 200 nm MirrorBit Process Technology

Data Sheet

Distinctive Characteristics

Architectural Advantages

Single power supply operation

-- 3 volt read, erase, and program operations

Manufactured on 200 nm MirrorBit process

technology

Secured Silicon Sector region

-- 128-word/256-byte sector for permanent, secure

identification through an 8-word/16-byte random

Electronic Serial Number, accessible through a

command sequence

-- May be programmed and locked at the factory or by

the customer

Flexible sector architecture

-- 64Mb (uniform sector models): 128 32 Kword (64 KB)

sectors

-- 64Mb (boot sector models): 127 32 Kword (64 KB)

sectors + 8 4Kword (8KB) boot sectors

-- 32Mb (uniform sector models): 64 32Kword (64KB)

sectors

-- 32Mb (boot sector models): 63 32Kword (64KB)

sectors + 8 4Kword (8KB) boot sectors

Compatibility with JEDEC standards

-- Provides pinout and software compatibility for single-

power supply flash, and superior inadvertent write

protection

100,000 erase cycles typical per sector

20-year data retention typical

Performance Characteristics

High performance

-- 90 ns access time

-- 4-word/8-byte page read buffer

-- 25 ns page read times

-- 16-word/32-byte write buffer which reduces overall

programming time for multiple-word updates

Low power consumption (typical values at 3.0 V, 5

MHz)

-- 18 mA typical active read current

-- 50 mA typical erase/program current

-- 1 µA typical standby mode current

Package options

-- 48-pin TSOP

-- 56-pin TSOP

-- 64-ball Fortified BGA

-- 48-ball fine-pitch BGA

Software & Hardware Features

Software features

-- Program Suspend & Resume: read other sectors

before programming operation is completed

-- Erase Suspend & Resume: read/program other

sectors before an erase operation is completed

-- Data# polling & toggle bits provide status

-- CFI (Common Flash Interface) compliant: allows host

system to identify and accommodate multiple flash

devices

-- Unlock Bypass Program command reduces overall

multiple-word programming time

Hardware features

-- Sector Group Protection: hardware-level method of

preventing write operations within a sector group

-- Temporary Sector Unprotect: V

ID

-level method of

charging code in locked sectors

-- WP#/ACC input accelerates programming time

(when high voltage is applied) for greater throughput

during system production. Protects first or last sector

regardless of sector protection settings on uniform

sector models

-- Hardware reset input (RESET#) resets device

-- Ready/Busy# output (RY/BY#) detects program or

erase cycle completion

2

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

Notice On Data Sheet Designations

Spansion LLC issues data sheets with Advance Information or Preliminary designations to advise

readers of product information or intended specifications throughout the product life cycle, in-

cluding development, qualification, initial production, and full production. In all cases, however,

readers are encouraged to verify that they have the latest information before finalizing their de-

sign. The following descriptions of Spansion data sheet designations are presented here to high-

light their presence and definitions.

Advance Information

The Advance Information designation indicates that Spansion LLC is developing one or more spe-

cific products, but has not committed any design to production. Information presented in a doc-

ument with this designation is likely to change, and in some cases, development on the product

may discontinue. Spansion LLC therefore places the following conditions upon Advance Informa-

tion content:

"This document contains information on one or more products under development at Spansion LLC. The

information is intended to help you evaluate this product. Do not design in this product without con-

tacting the factory. Spansion LLC reserves the right to change or discontinue work on this proposed

product without notice."

Preliminary

The Preliminary designation indicates that the product development has progressed such that a

commitment to production has taken place. This designation covers several aspects of the prod-

uct life cycle, including product qualification, initial production, and the subsequent phases in the

manufacturing process that occur before full production is achieved. Changes to the technical

specifications presented in a Preliminary document should be expected while keeping these as-

pects of production under consideration. Spansion places the following conditions upon Prelimi-

nary content:

"This document states the current technical specifications regarding the Spansion product(s) described

herein. The Preliminary status of this document indicates that product qualification has been completed,

and that initial production has begun. Due to the phases of the manufacturing process that require

maintaining efficiency and quality, this document may be revised by subsequent versions or modifica-

tions due to changes in technical specifications."

Combination

Some data sheets will contain a combination of products with different designations (Advance In-

formation, Preliminary, or Full Production). This type of document will distinguish these products

and their designations wherever necessary, typically on the first page, the ordering information

page, and pages with DC Characteristics table and AC Erase and Program table (in the table

notes). The disclaimer on the first page refers the reader to the notice on this page.

Full Production (No Designation on Document)

When a product has been in production for a period of time such that no changes or only nominal

changes are expected, the Preliminary designation is removed from the data sheet. Nominal

changes may include those affecting the number of ordering part numbers available, such as the

addition or deletion of a speed option, temperature range, package type, or V

IO

range. Changes

may also include those needed to clarify a description or to correct a typographical error or incor-

rect specification. Spansion LLC applies the following conditions to documents in this category:

"This document states the current technical specifications regarding the Spansion product(s) described

herein. Spansion LLC deems the products to have been in sufficient production volume such that sub-

sequent versions of this document are not expected to change. However, typographical or specification

corrections, or modifications to the valid combinations offered may occur."

Questions regarding these document designations may be directed to your local AMD or Fujitsu

sales office.

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

3

A d v a n c e I n f o r m a t i o n

General Description

The S29GLxxxA family of devices are 3.0 V single power Flash memory manufac-

tured using 200 nm MirrorBit technology. The S29GL064A is a 64 Mb, organized

as 4,194,304 words or 8,388,608 bytes. The S29GL032A is a 32 Mb, organized

as 2,097,152 words or 4,194,304 bytes. Depending on the model number, the

devices have an 8-bit wide data bus only, 16-bit wide data bus only, or a 16-bit

wide data bus that can also function as an 8-bit wide data bus by using the BYTE#

input. The devices can be programmed either in the host system or in standard

EPROM programmers.

Access times as fast as 90 ns are available. Note that each access time has a spe-

cific operating voltage range (V

CC

) as specified in the

Product Selector Guide

and

the

Ordering Information

sections. Package offerings include 48-pin TSOP, 56-pin

TSOP, 48-ball fine-pitch BGA and 64-ball Fortified BGA, depending on model num-

ber. Each device has separate chip enable (CE#), write enable (WE#) and output

enable (OE#) controls.

Each device requires only a single 3.0 volt power supply for both read and

write functions. In addition to a V

CC

input, a high-voltage accelerated program

(ACC) feature provides shorter programming times through increased current on

the WP#/ACC input. This feature is intended to facilitate factory throughput dur-

ing system production, but may also be used in the field if desired.

The device is entirely command set compatible with the JEDEC single-power-

supply Flash standard. Commands are written to the device using standard mi-

croprocessor write timing. Write cycles also internally latch addresses and data

needed for the programming and erase operations.

The sector erase architecture allows memory sectors to be erased and repro-

grammed without affecting the data contents of other sectors. The device is fully

erased when shipped from the factory.

Device programming and erasure are initiated through command sequences.

Once a program or erase operation has begun, the host system need only poll the

DQ7 (Data# Polling) or DQ6 (toggle) status bits or monitor the Ready/Busy#

(RY/BY#) output to determine whether the operation is complete. To facilitate

programming, an Unlock Bypass mode reduces command sequence overhead

by requiring only two write cycles to program data instead of four.

Hardware data protection measures include a low V

CC

detector that automat-

ically inhibits write operations during power transitions. The hardware sector

protection feature disables both program and erase operations in any combina-

tion of sectors of memory. This can be achieved in-system or via programming

equipment.

The Erase Suspend/Erase Resume feature allows the host system to pause an

erase operation in a given sector to read or program any other sector and then

complete the erase operation. The Program Suspend/Program Resume fea-

ture enables the host system to pause a program operation in a given sector to

read any other sector and then complete the program operation.

The hardware RESET# pin terminates any operation in progress and resets the

device, after which it is then ready for a new operation. The RESET# pin may be

tied to the system reset circuitry. A system reset would thus also reset the device,

enabling the host system to read boot-up firmware from the Flash memory

device.

4

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

The device reduces power consumption in the standby mode when it detects

specific voltage levels on CE# and RESET#, or when addresses have been stable

for a specified period of time.

The Write Protect (WP#) feature protects the first or last sector by asserting

a logic low on the WP#/ACC pin or WP# pin, depending on model number. The

protected sector will still be protected even during accelerated programming.

The Secured Silicon Sector provides a 128-word/256-byte area for code or

data that can be permanently protected. Once this sector is protected, no further

changes within the sector can occur.

Spansion MirrorBit flash technology combines years of Flash memory manufac-

turing experience to produce the highest levels of quality, reliability and cost

effectiveness. The device electrically erases all bits within a sector simultaneously

via hot-hole assisted erase. The data is programmed using hot electron injection.

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

5

A d v a n c e I n f o r m a t i o n

Table of Contents

General Description . . . . . . . . . . . . . . . . . . . . . . . . .3

Product Selector Guide . . . . . . . . . . . . . . . . . . . . . .7

S29GL064A, S29GL032A ....................................................................................7

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Logic Symbol-S29GL064A (Model R6, R7) .................................................. 14

Ordering Information-S29GL032A . . . . . . . . . . . . 15

S29GL032A Standard Products .......................................................................15

Table 1. S29GL032A Ordering Options ................................. 16

Ordering Information-S29GL064A . . . . . . . . . . . . 17

S29GL064A Standard Products .......................................................................17

Table 2. S29GL064A Valid Combinations .............................. 18

Device Bus Operations . . . . . . . . . . . . . . . . . . . . . . 19

Table 3. Device Bus Operations ........................................... 19

Word/Byte Configuration ................................................................................20

Requirements for Reading Array Data ........................................................ 20

Page Mode Read ............................................................................................. 20

Writing Commands/Command Sequences ................................................ 20

Write Buffer ..................................................................................................... 21

Accelerated Program Operation ............................................................... 21

Autoselect Functions ..................................................................................... 21

Standby Mode ....................................................................................................... 21

Automatic Sleep Mode ..................................................................................... 22

RESET#: Hardware Reset Pin ........................................................................ 22

Output Disable Mode ....................................................................................... 22

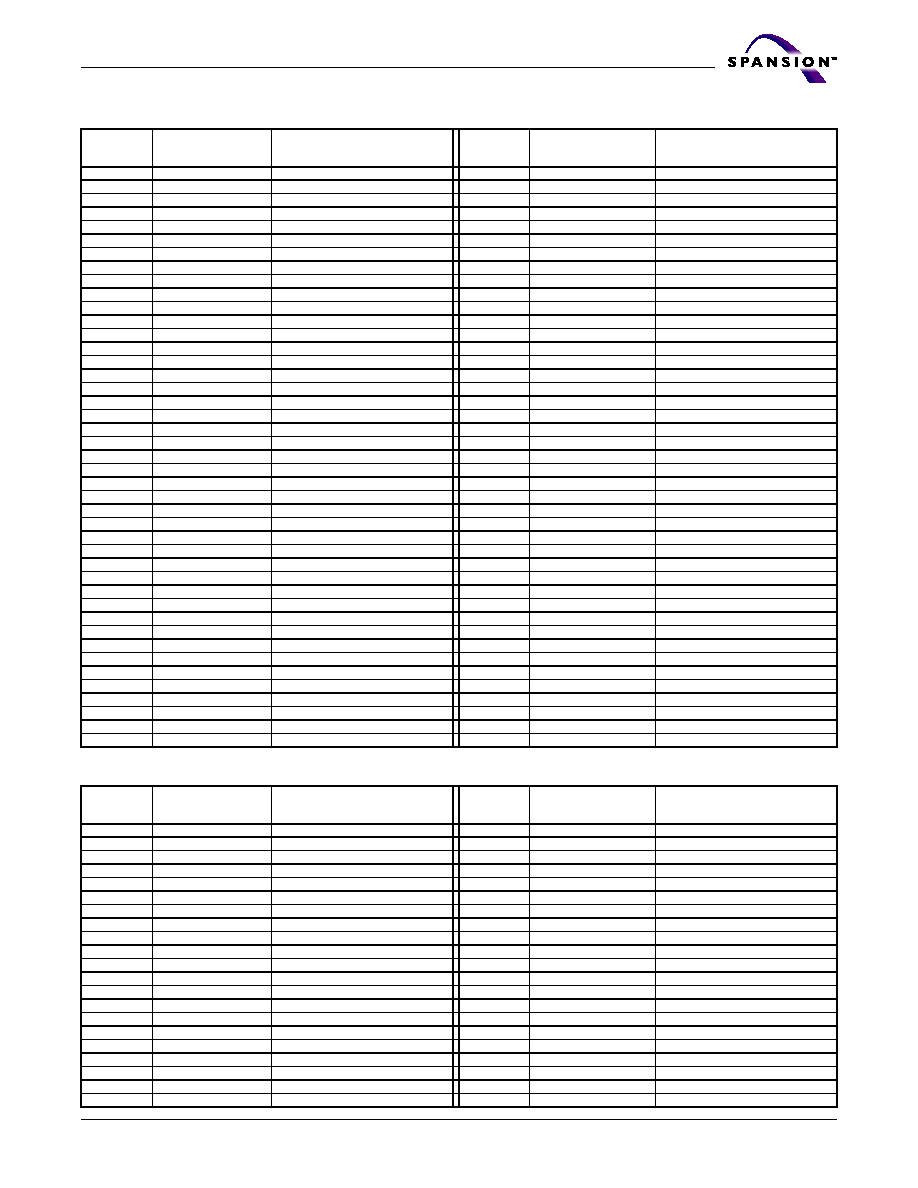

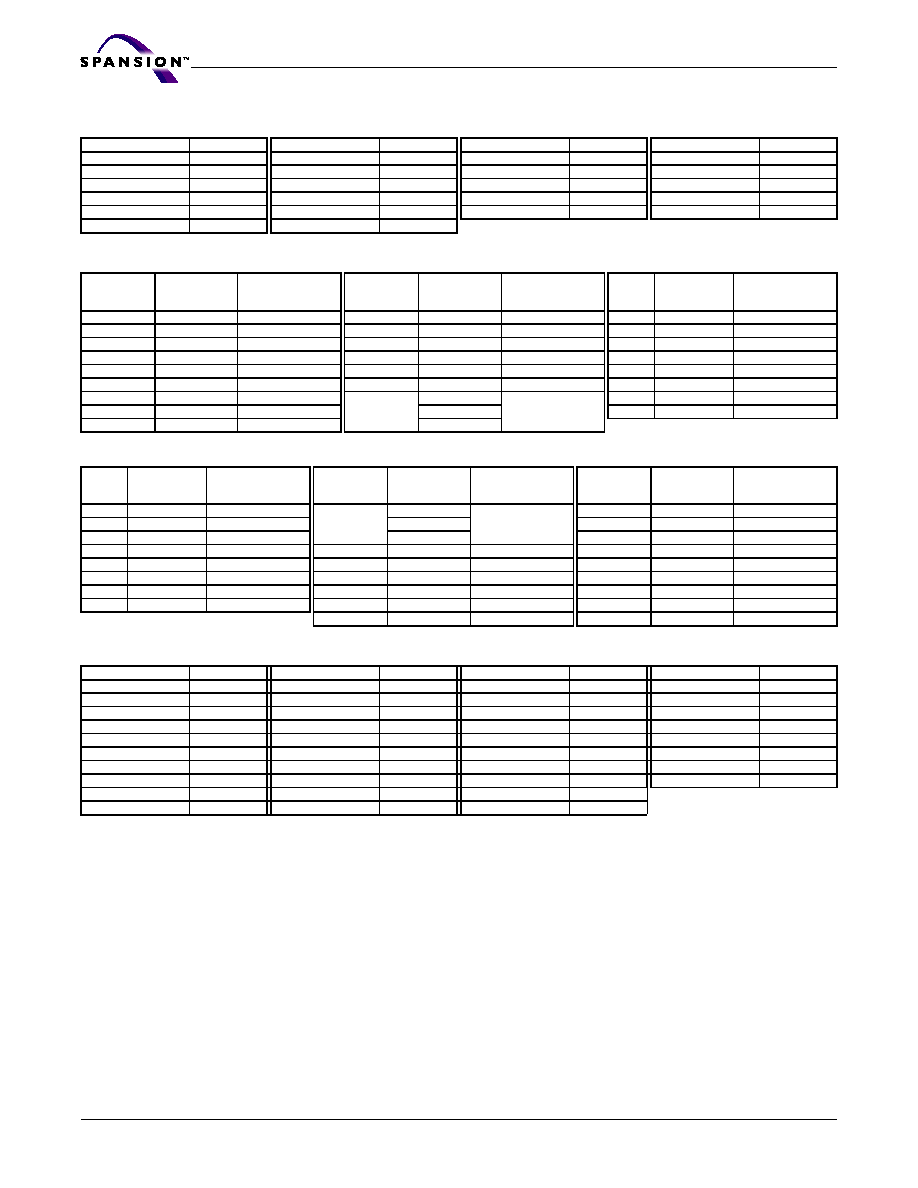

Table 4. S29GL032M (Models R1, R2) Sector Addresses ......... 23

Table 5. S29GL032M (Models R3) Top Boot Sector Addresses . 24

Table 6. S29GL032M (Models R4) Bottom Boot

Sector Addresses .............................................................. 24

Table 7. S29GL064A (Models R1, R2, R8, R9) Sector Addresses 25

Table 8. S29GL064A (Model R3) Top Boot Sector Addresses ... 26

Table 9. S29GL064A (Model R4) Bottom Boot Sector Addresses 27

Table 10. S29GL064A (Model R5) Sector Addresses ............... 28

Table 11. S29GL064A (Models R6, R7) Sector Addresses ........ 29

Autoselect Mode ................................................................................................ 30

Table 12. Autoselect Codes, (High Voltage Method) .............. 31

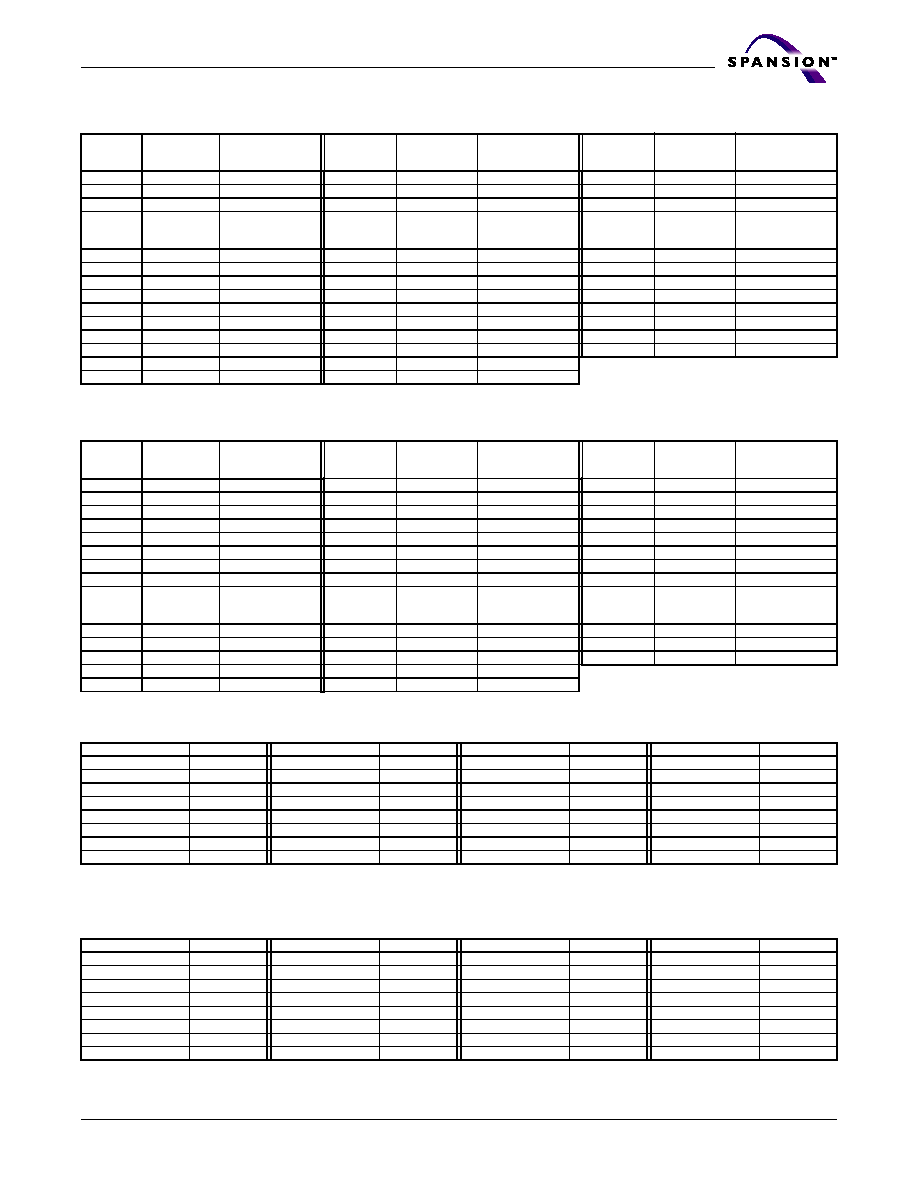

Sector Group Protection and Unprotection ...............................................31

Table 13. S29GL032A (Models R1, R2) Sector Group Protection/Un-

protection Addresses ......................................................... 32

Table 14. S29GL032A (Models R3) Sector Group Protection/Unpro-

tection Address Table ......................................................... 32

Table 15. S29GL032A (Models R4) Sector Group Protection/Unpro-

tection Address Table ......................................................... 32

Table 16. S29GL064A (Models R1, R2, R8, R9) Sector Group Protec-

tion/Unprotection Addresses ............................................... 32

Table 17. S29GL064A (Model R3) Top Boot Sector Protection/Unpro-

tection Addresses .............................................................. 33

Table 18. S29GL064A (Model R4) Bottom Boot Sector Protection/

Unprotection Addresses ...................................................... 33

Table 19. S29GL064A (Model R5) Sector Group Protection/Unpro-

tection Addresses .............................................................. 33

Table 20. S29GL064A (Models R6, R7) Sector Group Protection/Un-

protection Addresses ......................................................... 33

Temporary Sector Group Unprotect ...........................................................34

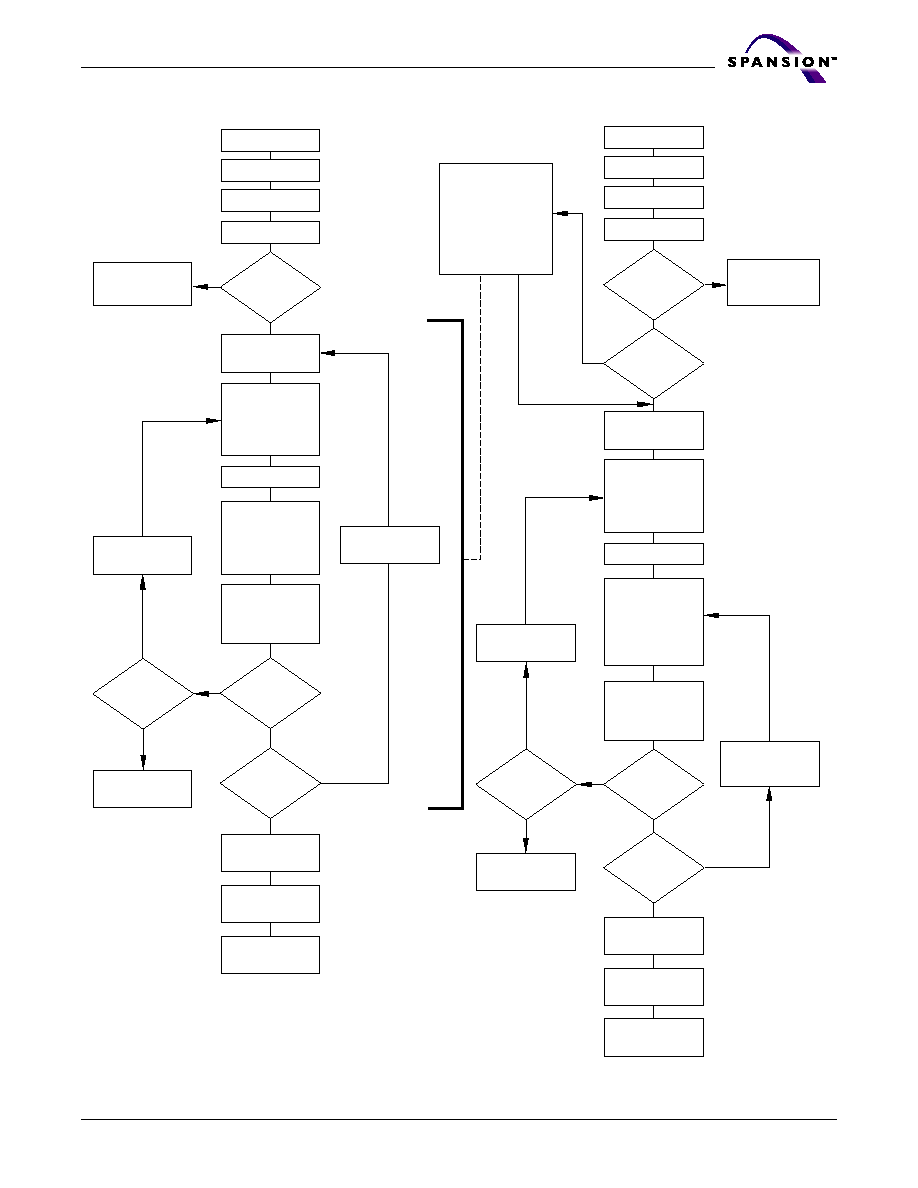

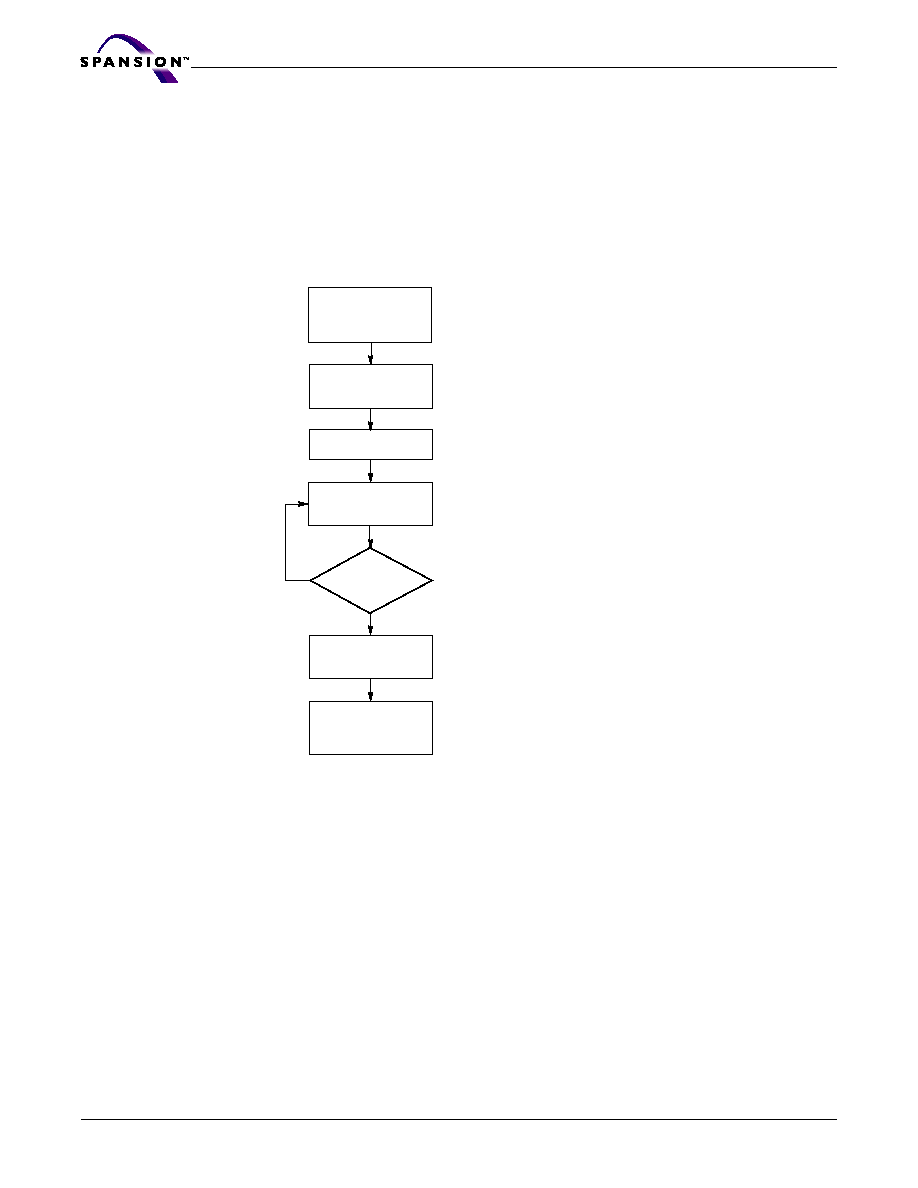

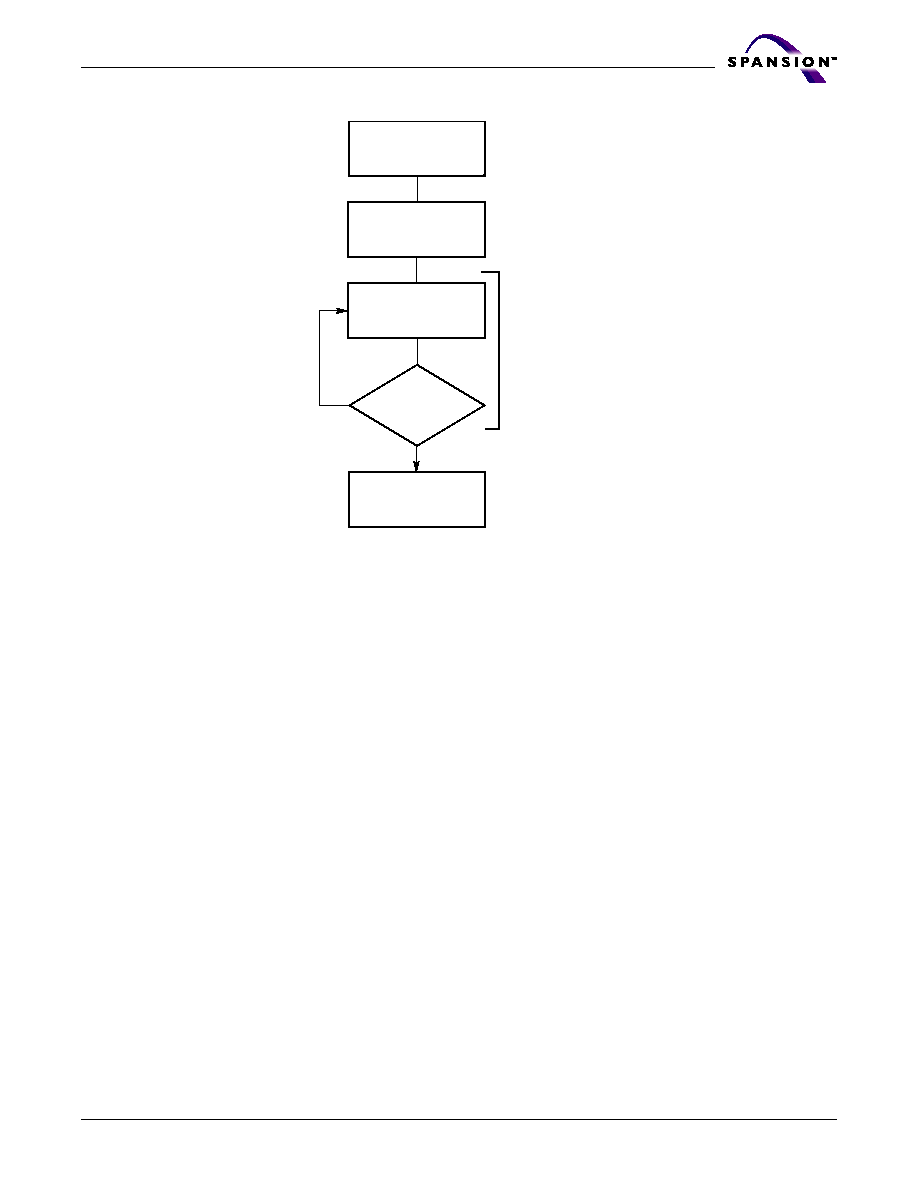

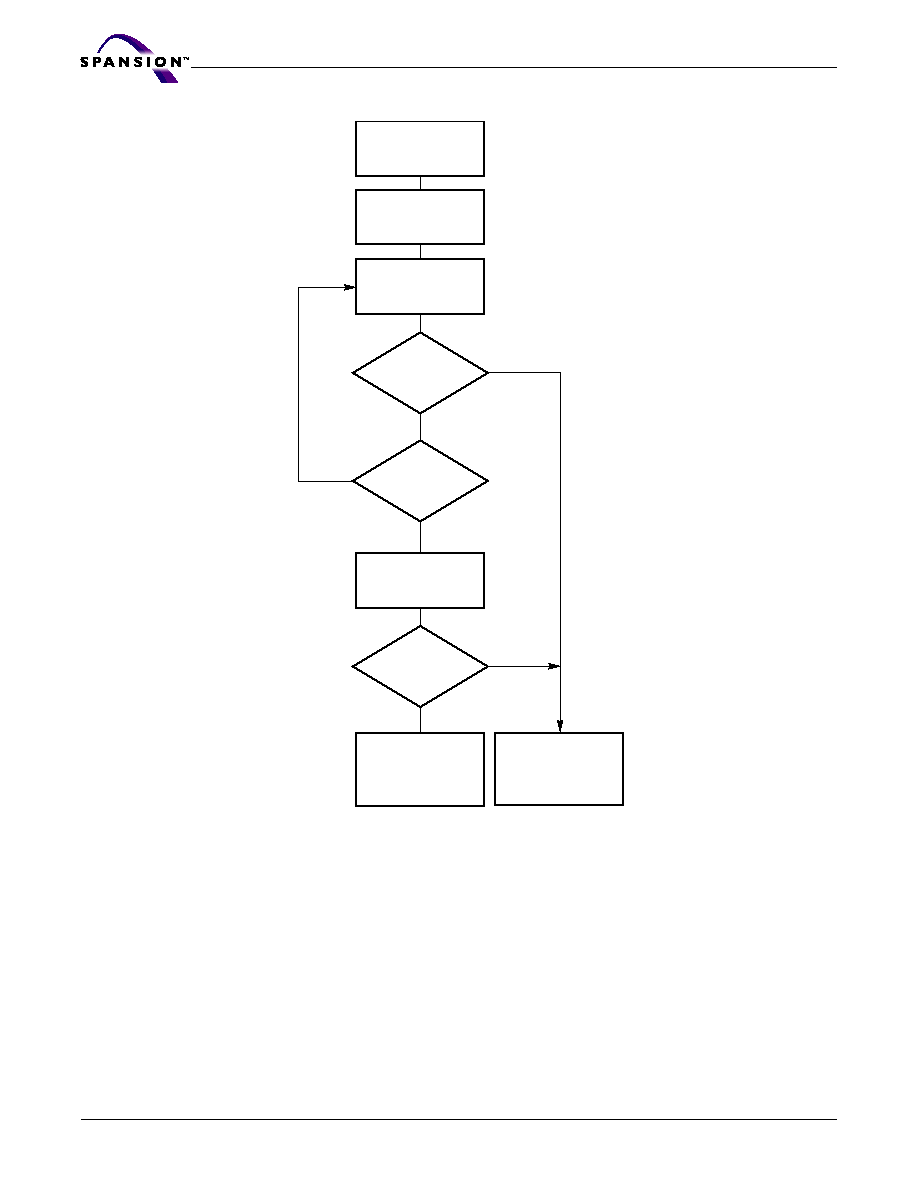

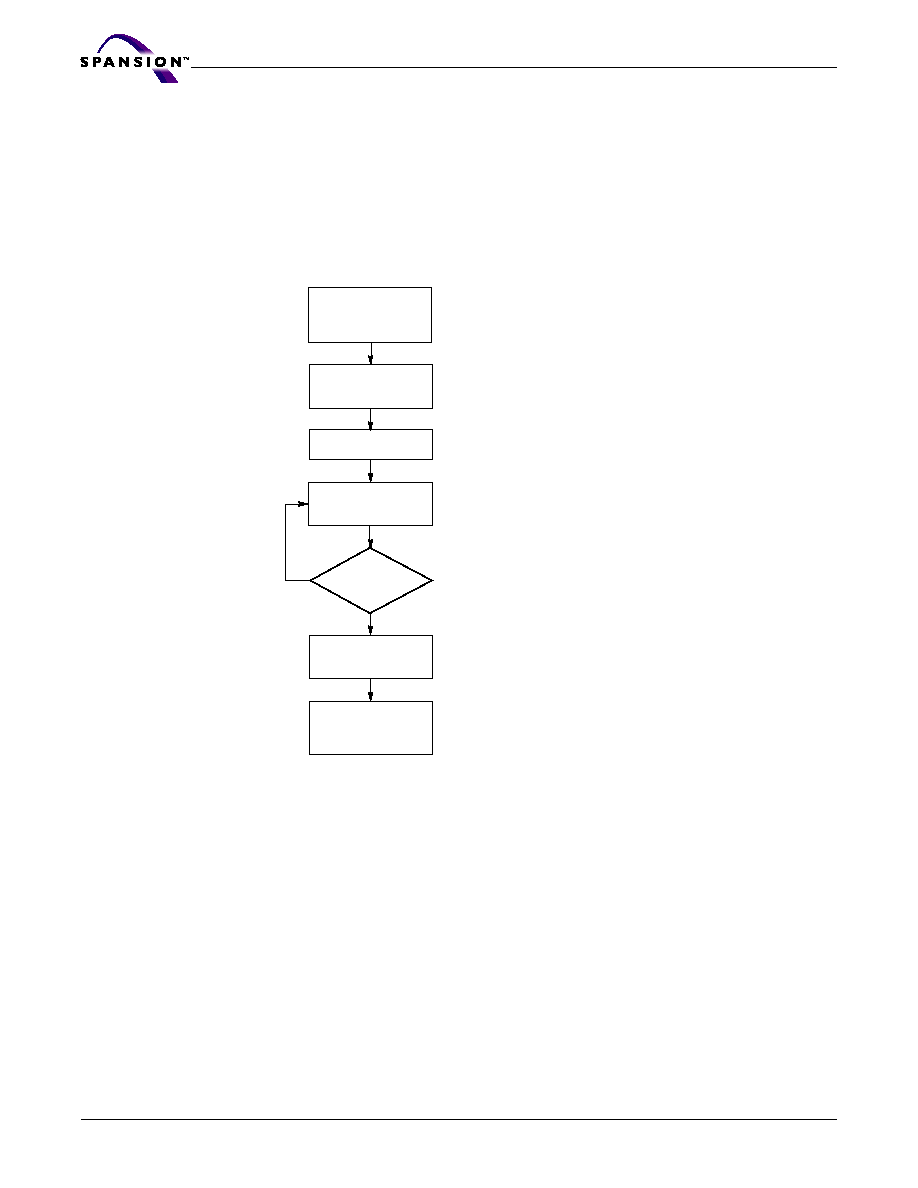

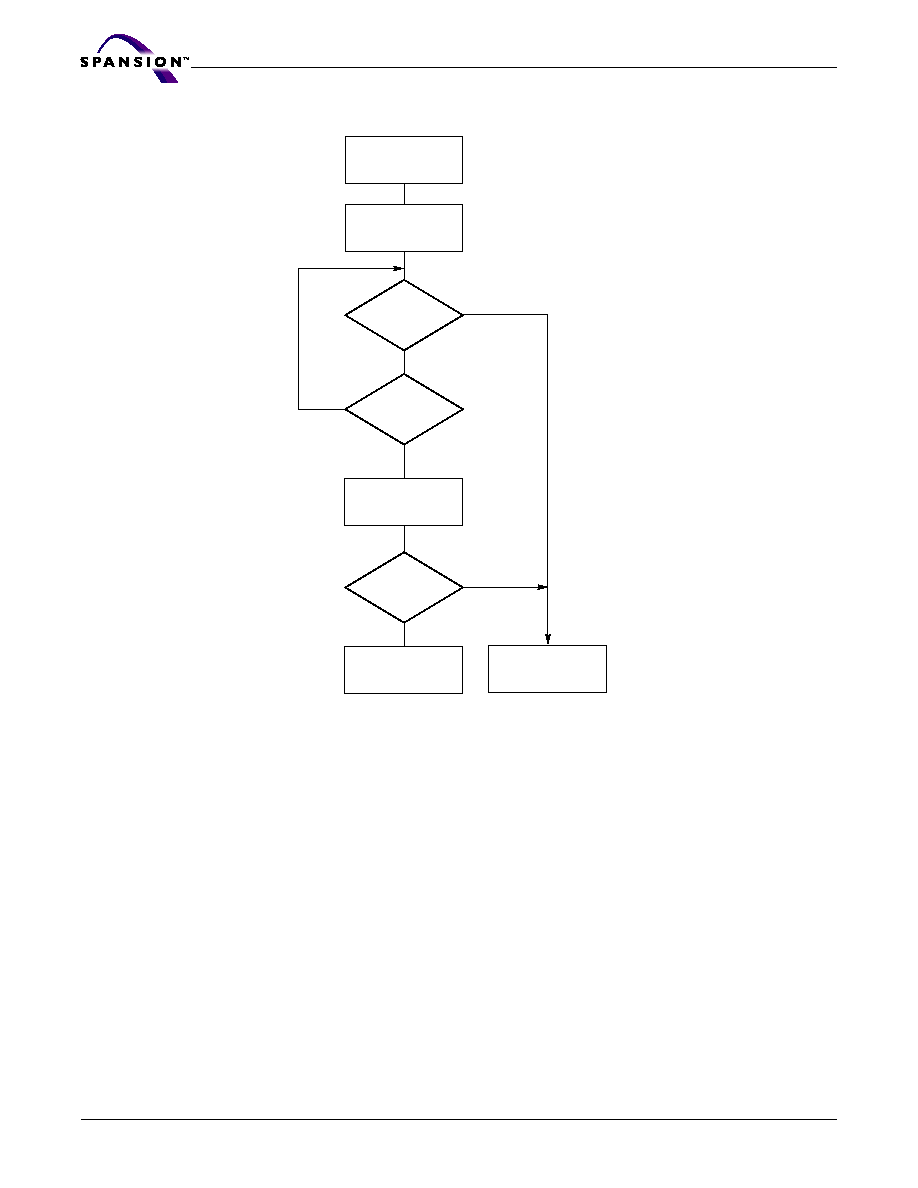

Figure 1. Temporary Sector Group Unprotect Operation .......... 34

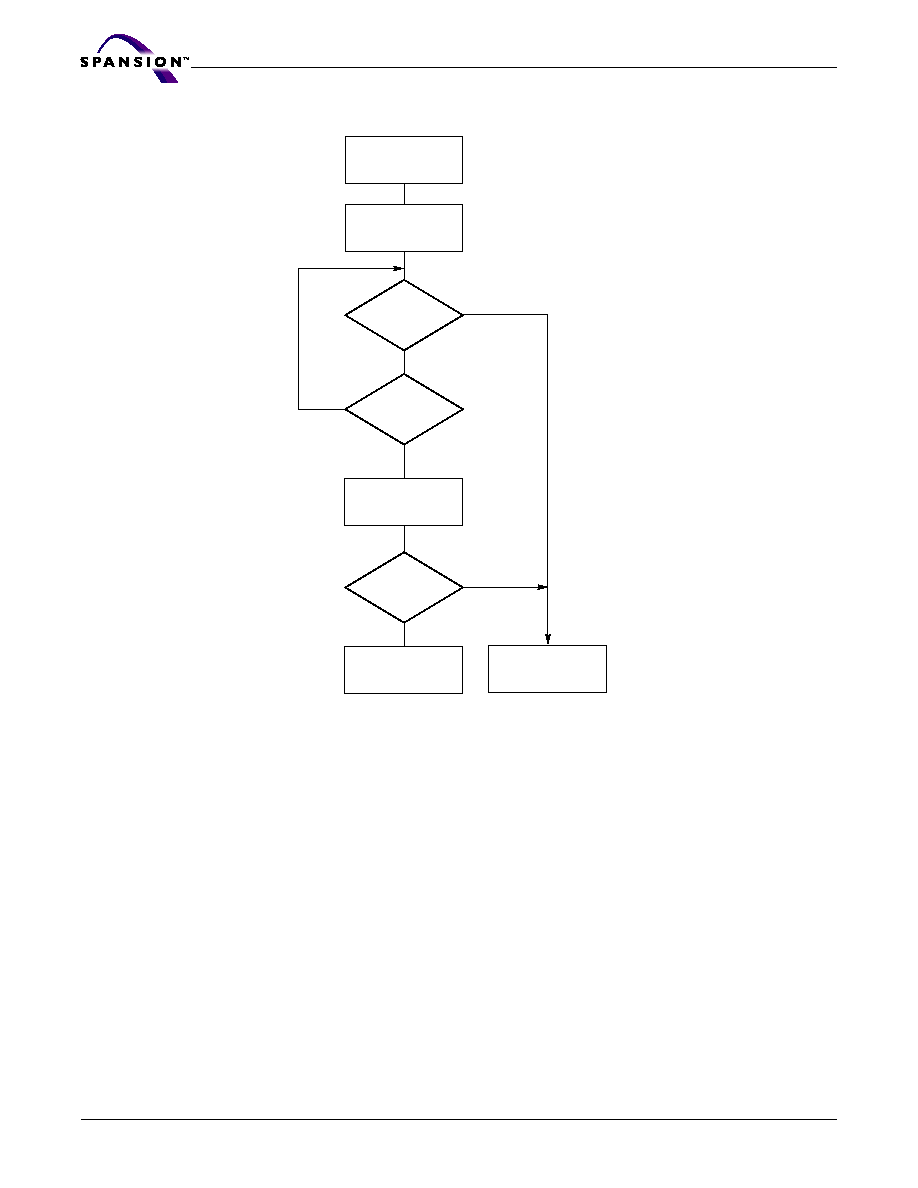

Figure 2. In-System Sector Group Protect/Unprotect Algorithms 35

Secured Silicon Sector Flash Memory Region ............................................36

Write Protect (WP#) ........................................................................................37

Hardware Data Protection ..............................................................................37

Low VCC Write Inhibit ................................................................................37

Write Pulse "Glitch" Protection ............................................................... 38

Logical Inhibit ................................................................................................... 38

Power-Up Write Inhibit ............................................................................... 38

Common Flash Memory Interface (CFI) . . . . . . . 39

Table 21. CFI Query Identification String ...............................39

Table 22. System Interface String........................................ 40

Command Definitions . . . . . . . . . . . . . . . . . . . . . . 43

Reading Array Data ........................................................................................... 43

Reset Command ................................................................................................. 43

Autoselect Command Sequence ...................................................................44

Enter Secured Silicon Sector/Exit Secured Silicon

Sector Command Sequence ............................................................................44

Word Program Command Sequence ......................................................44

Unlock Bypass Command Sequence ........................................................ 45

Write Buffer Programming ......................................................................... 45

Accelerated Program .................................................................................... 47

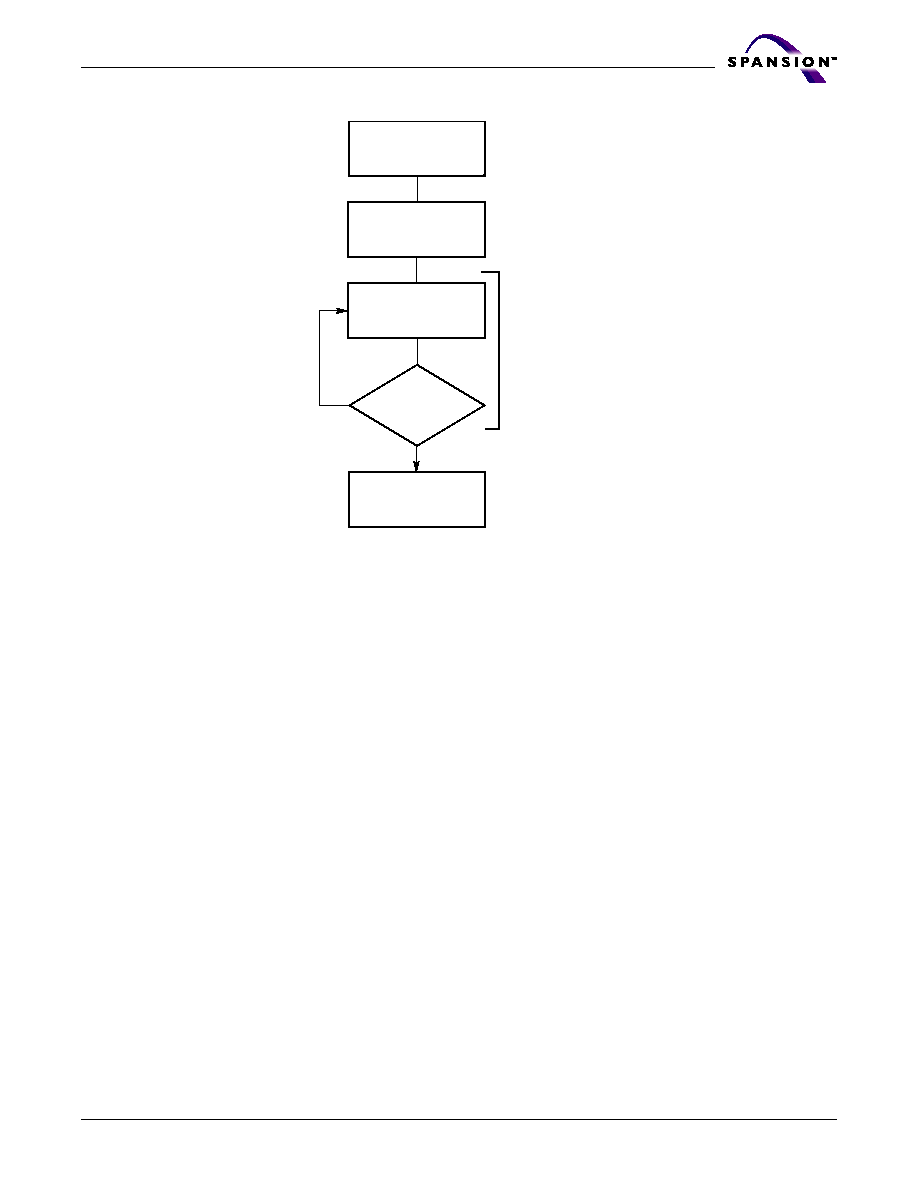

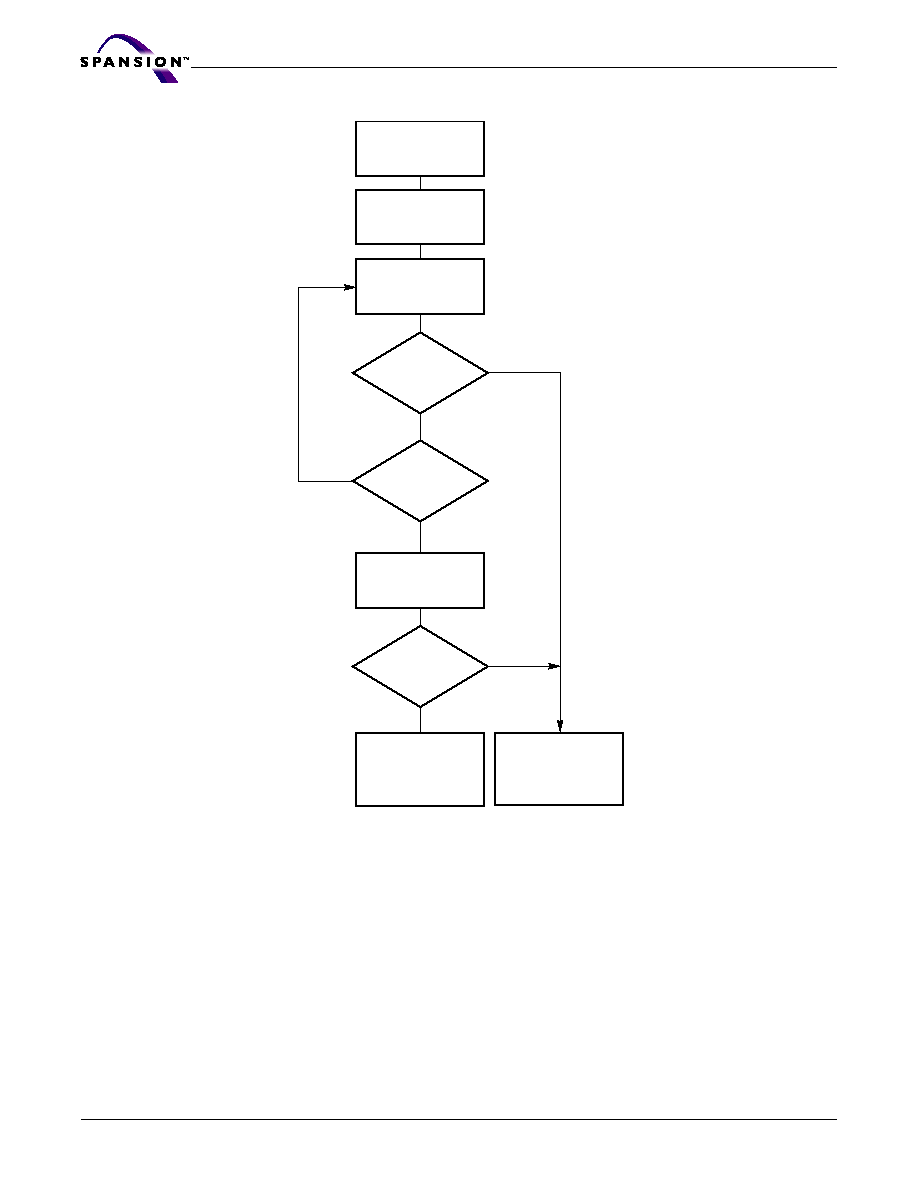

Figure 3. Write Buffer Programming Operation....................... 48

Figure 4. Program Operation ............................................... 49

Program Suspend/Program Resume Command Sequence ....................49

Figure 5. Program Suspend/Program Resume........................ 50

Chip Erase Command Sequence ...................................................................50

Sector Erase Command Sequence . . . . . . . . . . . 52

Figure 6. Erase Operation ................................................... 53

Erase Suspend/Erase Resume Commands ...................................................53

Command Definitions ........................................................................................55

Table 25. Command Definitions (x16 Mode, BYTE# = V

IH

) ......55

Table 26. Command Definitions (x8 Mode, BYTE# = V

IL

) .........56

Write Operation Status ....................................................................................57

DQ7: Data# Polling ........................................................................................... 57

Figure 7. Data# Polling Algorithm ........................................ 58

RY/BY#: Ready/Busy# ....................................................................................... 58

DQ6: Toggle Bit I ................................................................................................59

Figure 8. Toggle Bit Algorithm ............................................. 60

DQ2: Toggle Bit II ................................................................................................61

Reading Toggle Bits DQ6/DQ2 ...................................................................... 61

DQ5: Exceeded Timing Limits ......................................................................... 61

DQ3: Sector Erase Timer ................................................................................ 62

DQ1: Write-to-Buffer Abort ........................................................................... 62

Table 27. Write Operation Status .........................................63

Absolute Maximum Ratings ..............................................................................64

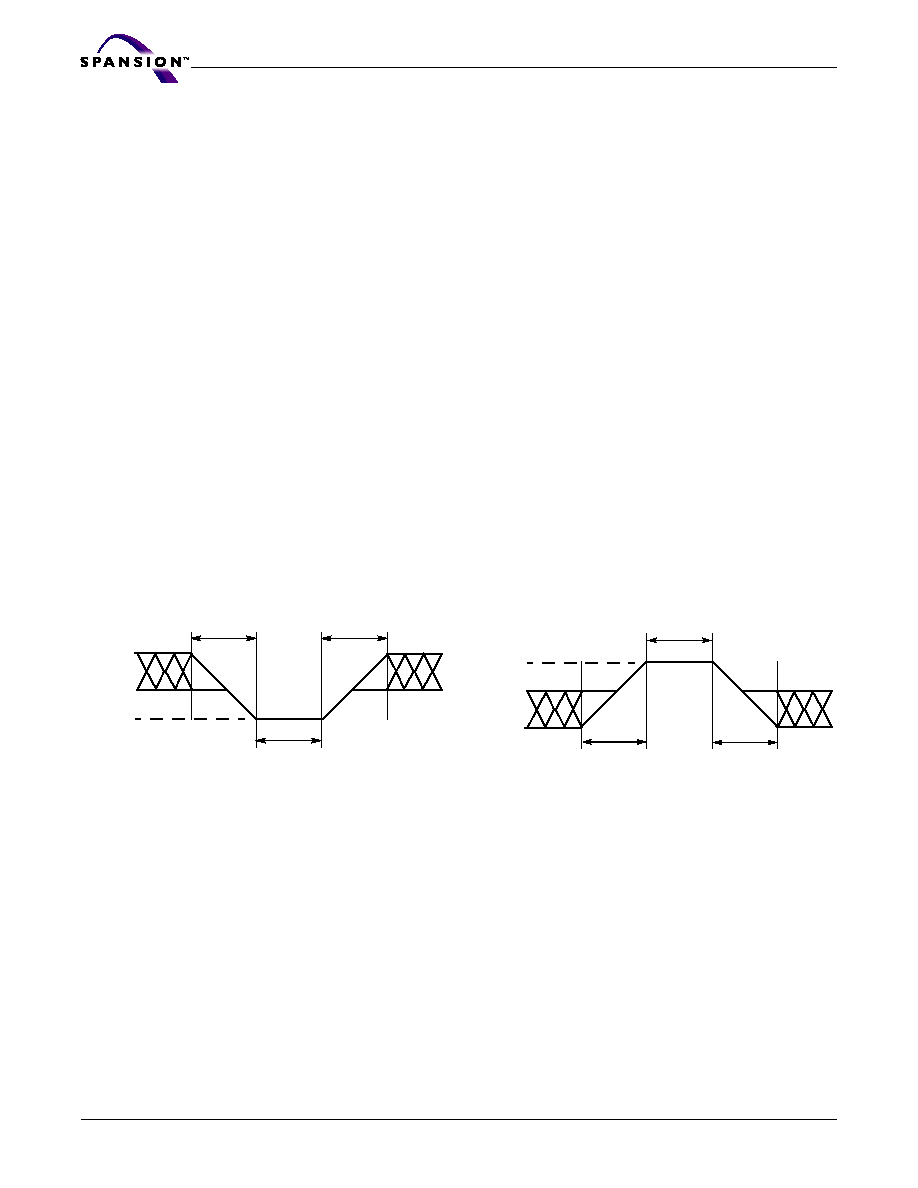

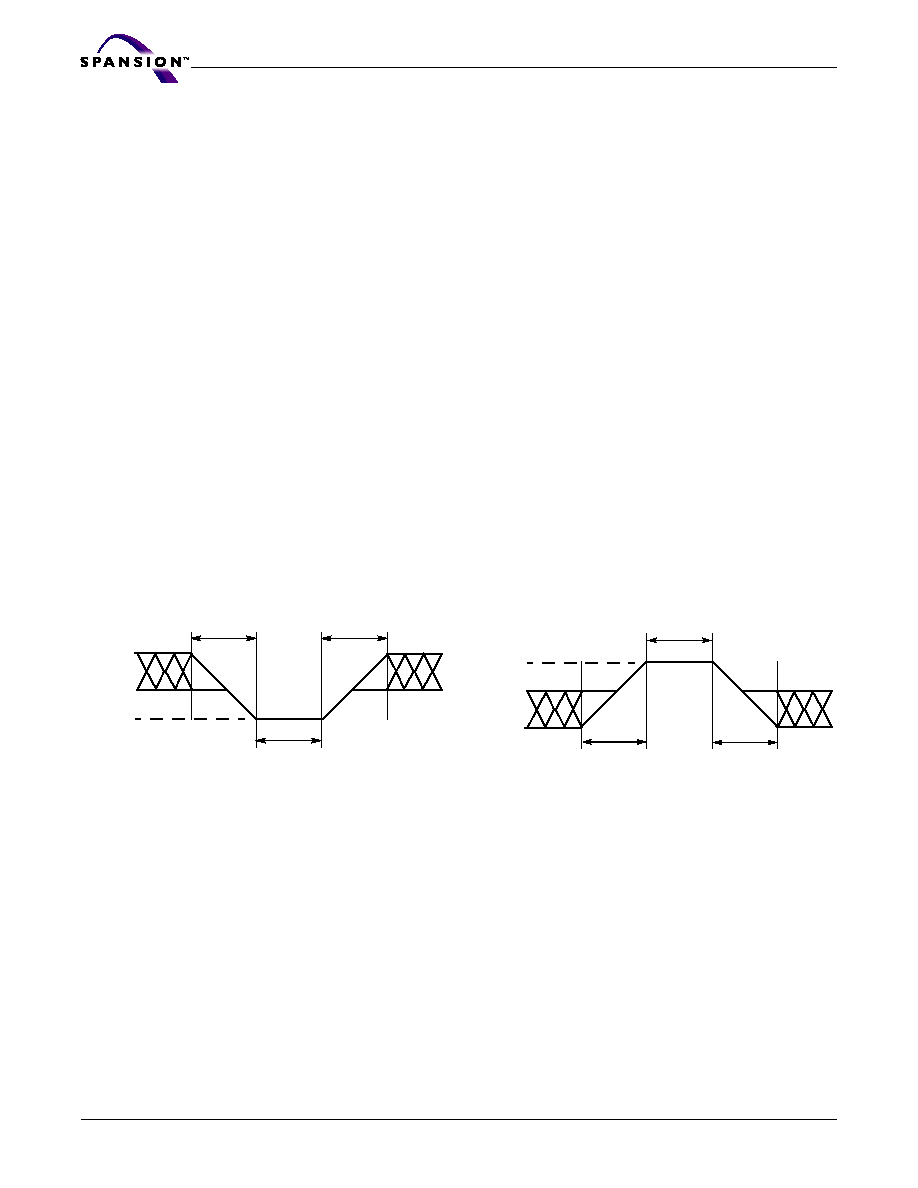

Figure 9. Maximum Negative Overshoot Waveform................. 64

Figure 10. Maximum Positive

Overshoot Waveform.......................................................... 64

Operating Ranges . . . . . . . . . . . . . . . . . . . . . . . . . 64

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 65

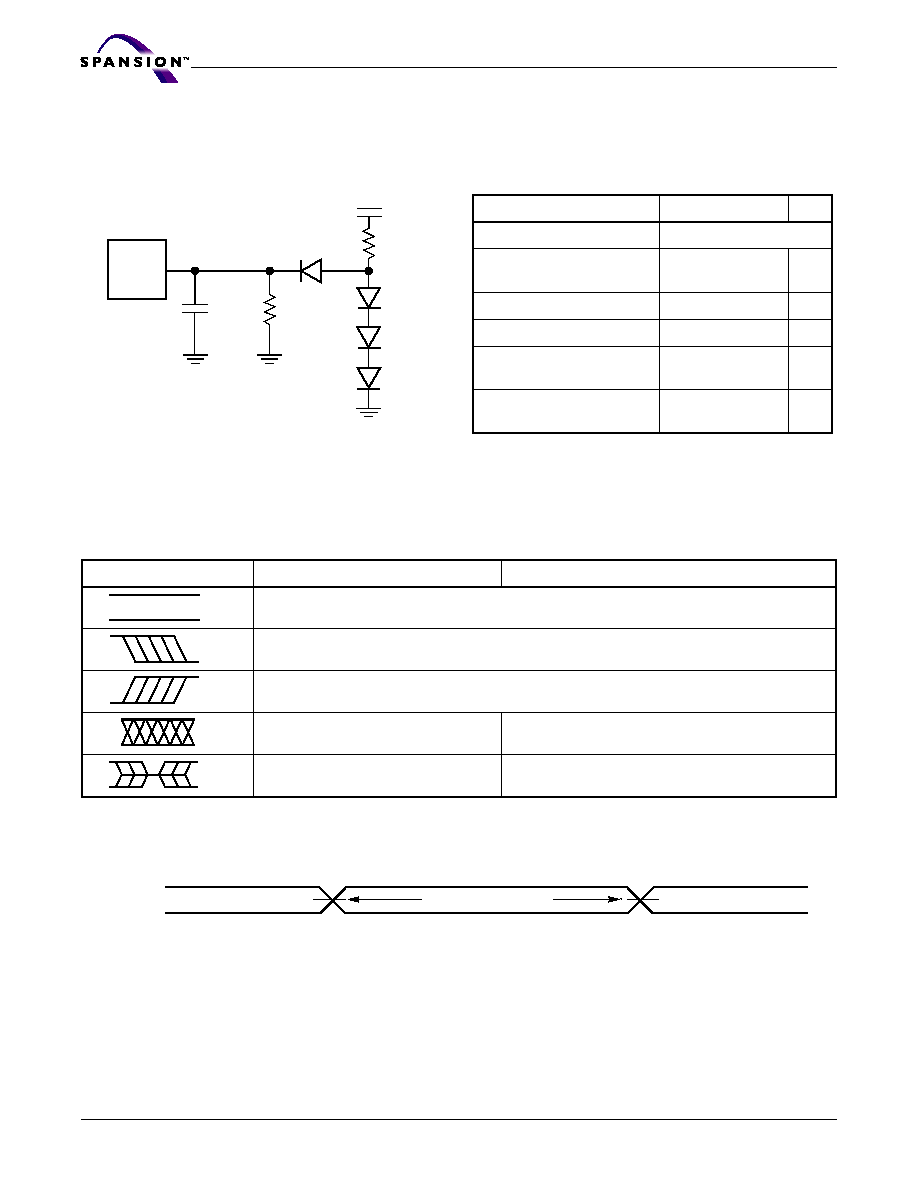

Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

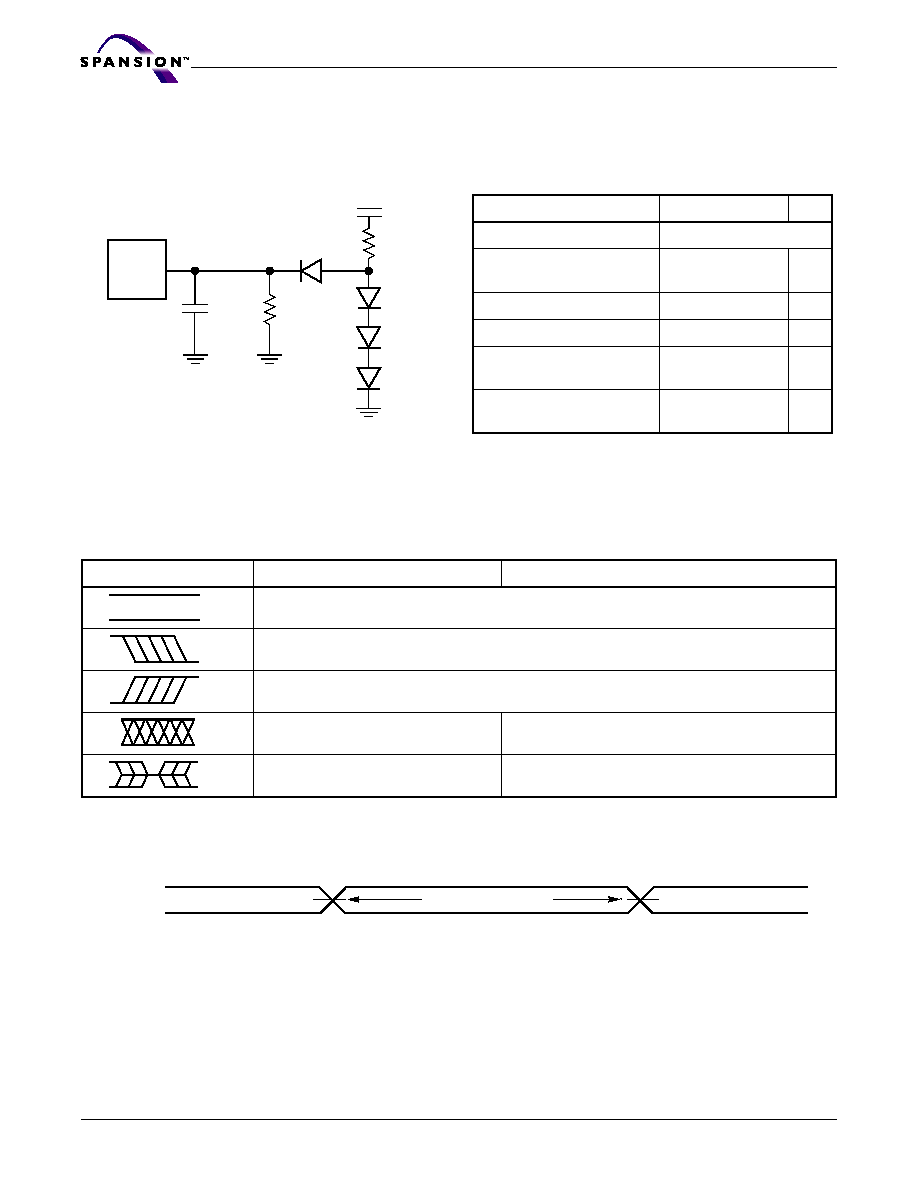

Figure 11. Test Setup ......................................................... 66

Table 28. Test Specifications ...............................................66

Key to Switching Waveforms . . . . . . . . . . . . . . . . 66

Figure 12. Input Waveforms and Measurement Levels ............ 66

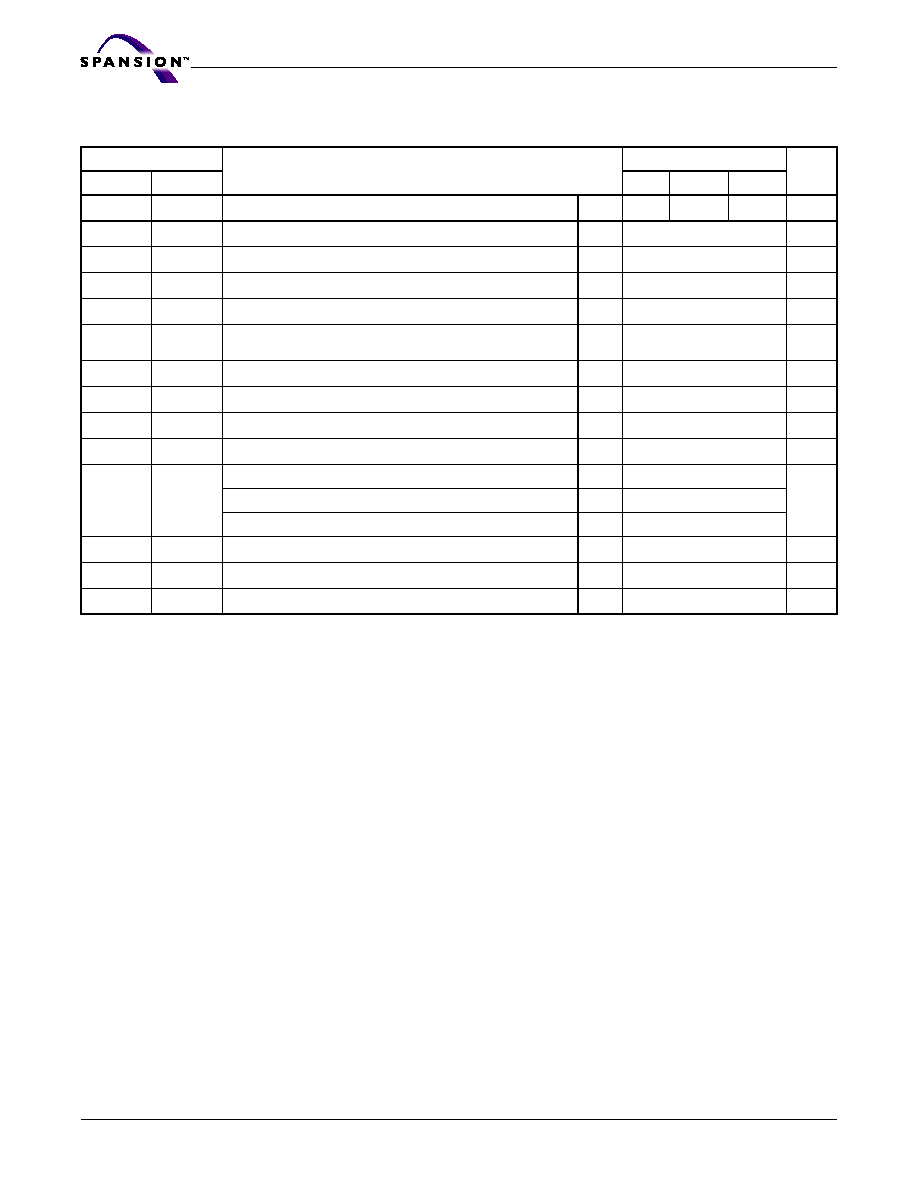

Read-Only Operations-S29GL064A only ................................................... 67

Read-Only Operations-S29GL032A only .................................................... 67

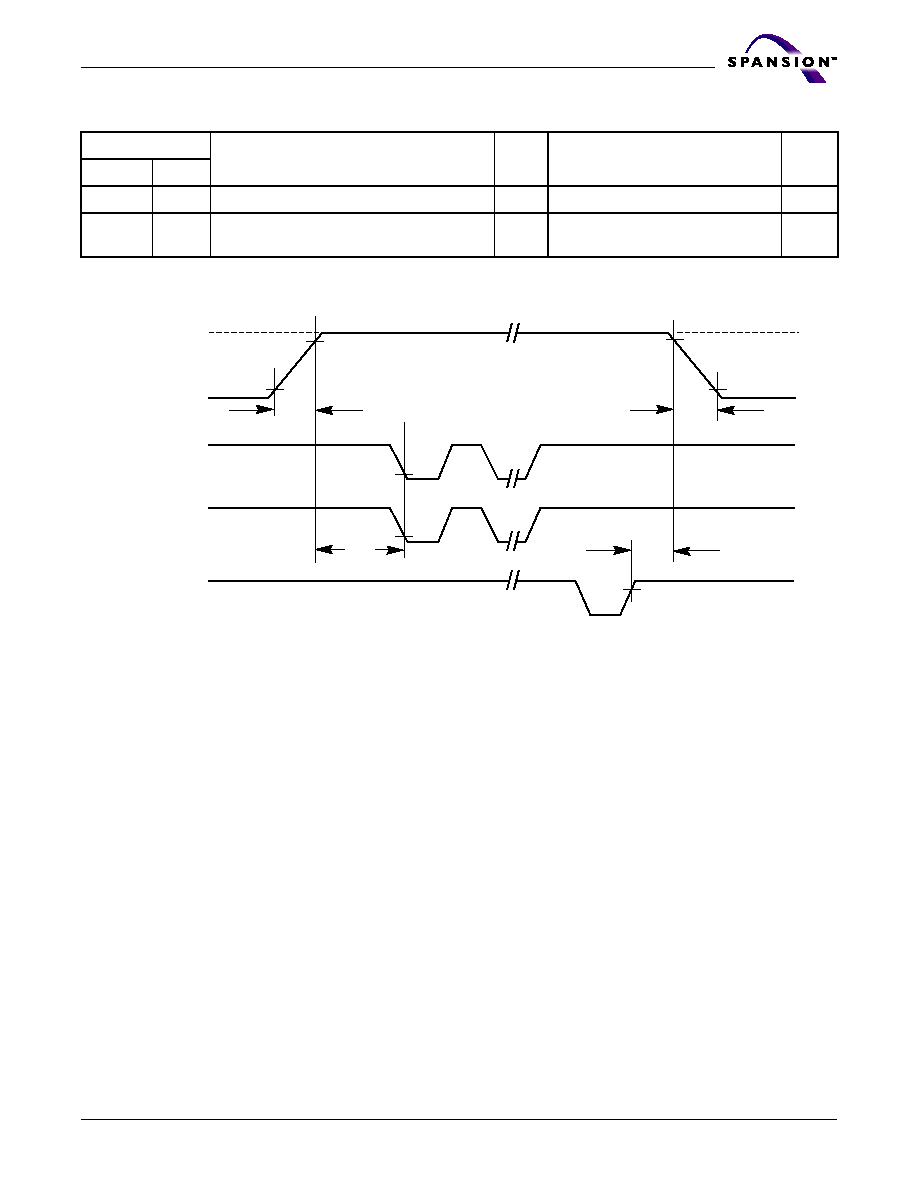

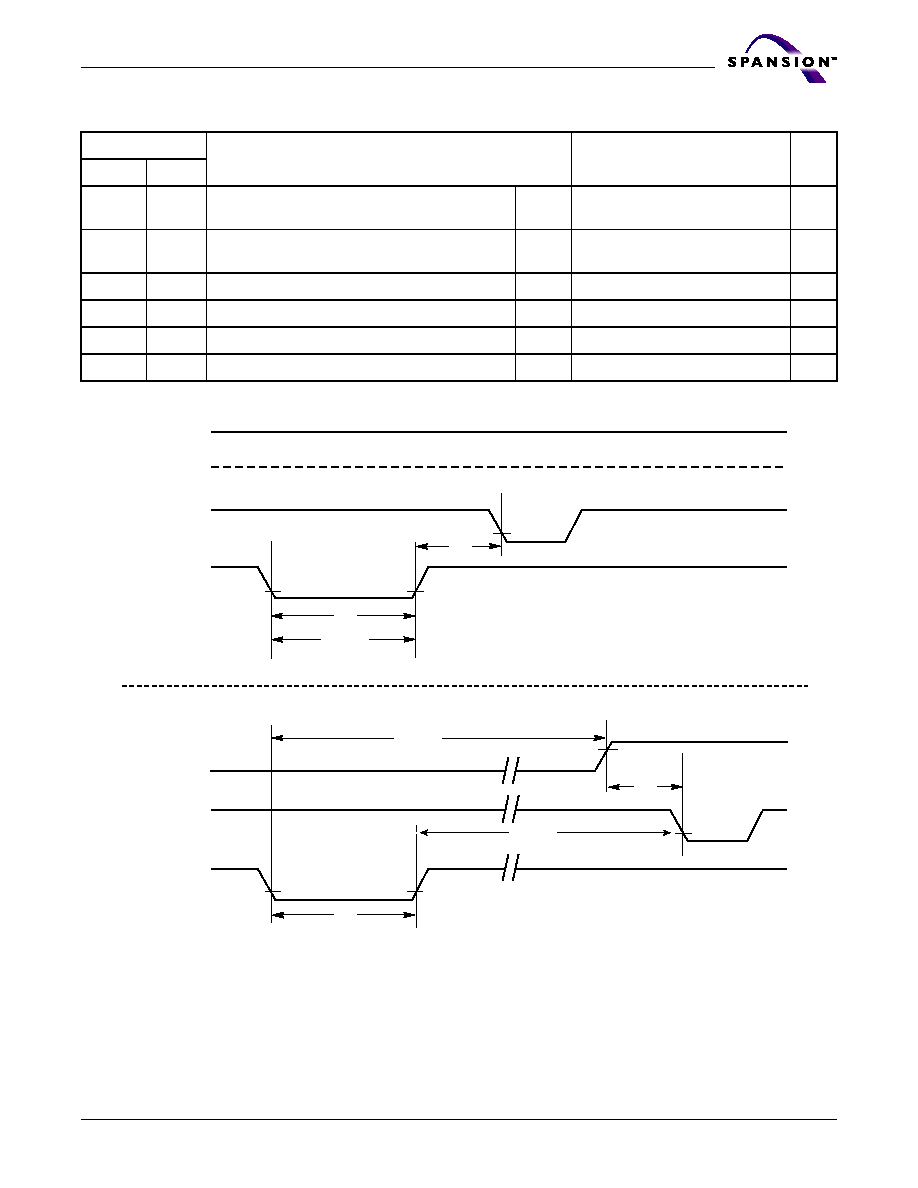

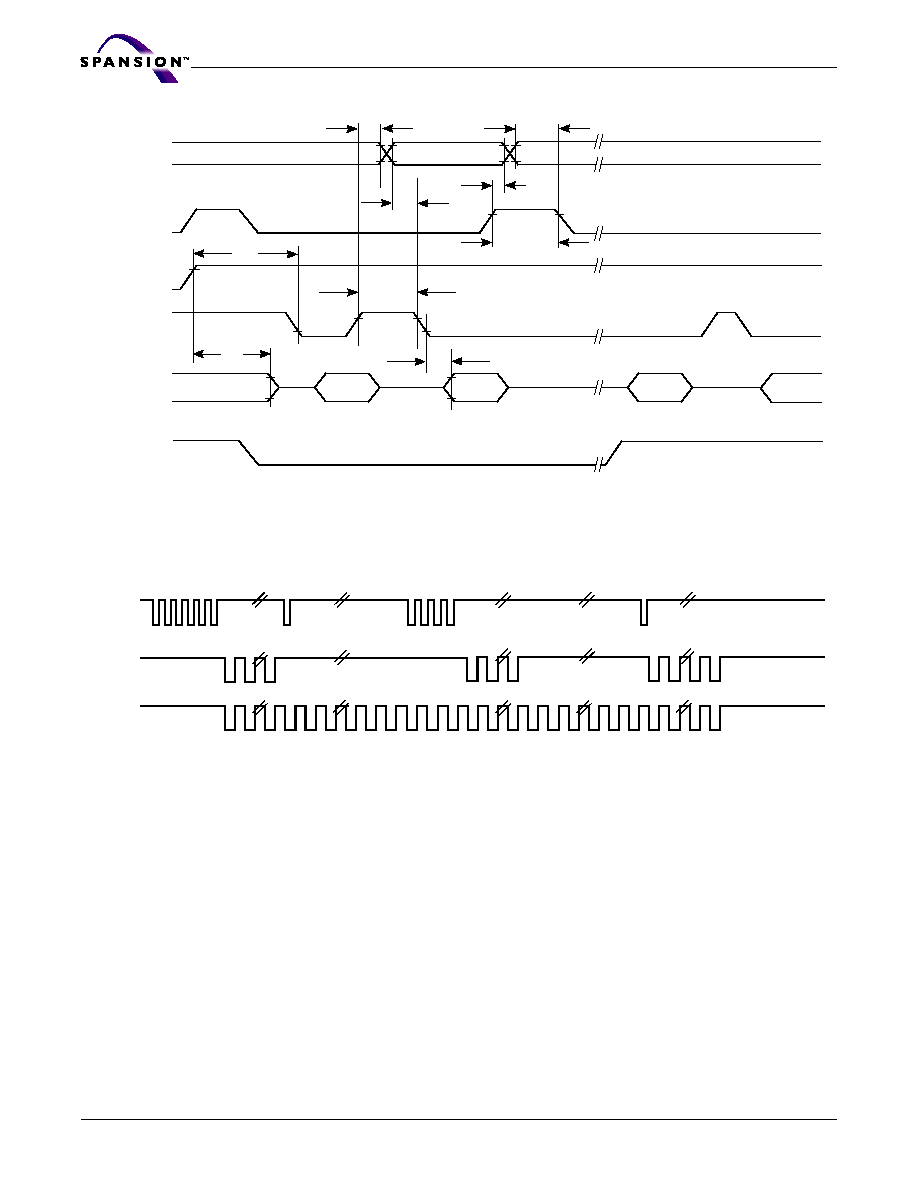

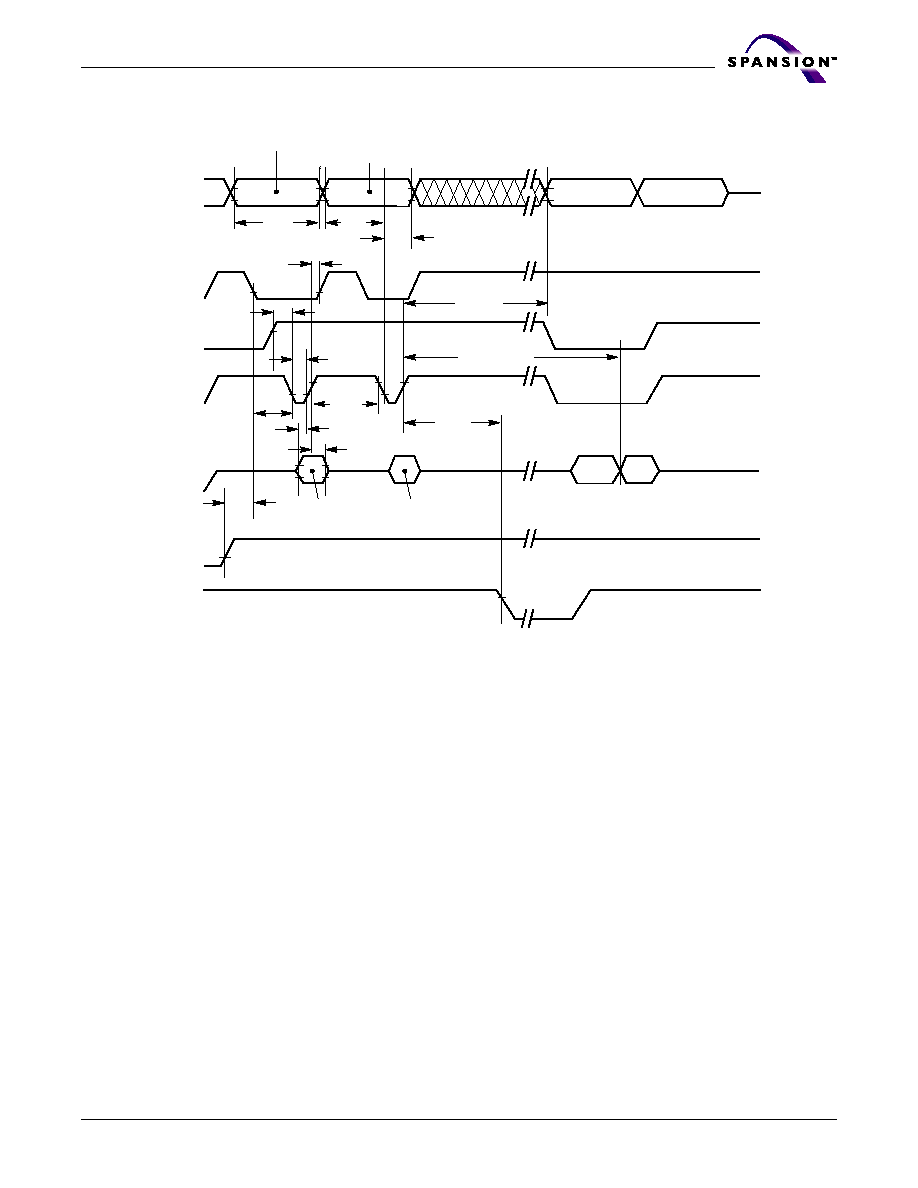

Figure 13. Read Operation Timings....................................... 68

Figure 14. Page Read Timings.............................................. 68

Hardware Reset (RESET#) ..............................................................................69

Figure 15. Reset Timings .................................................... 69

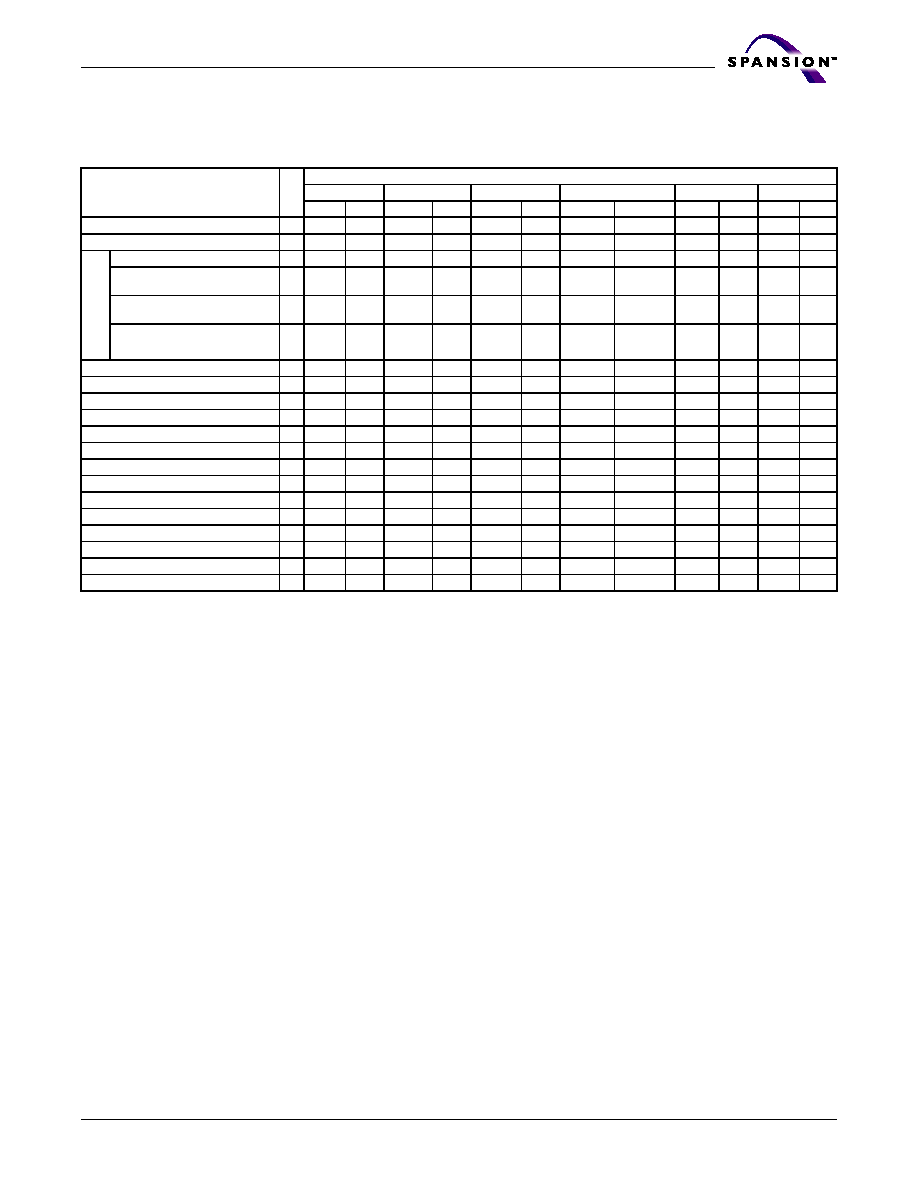

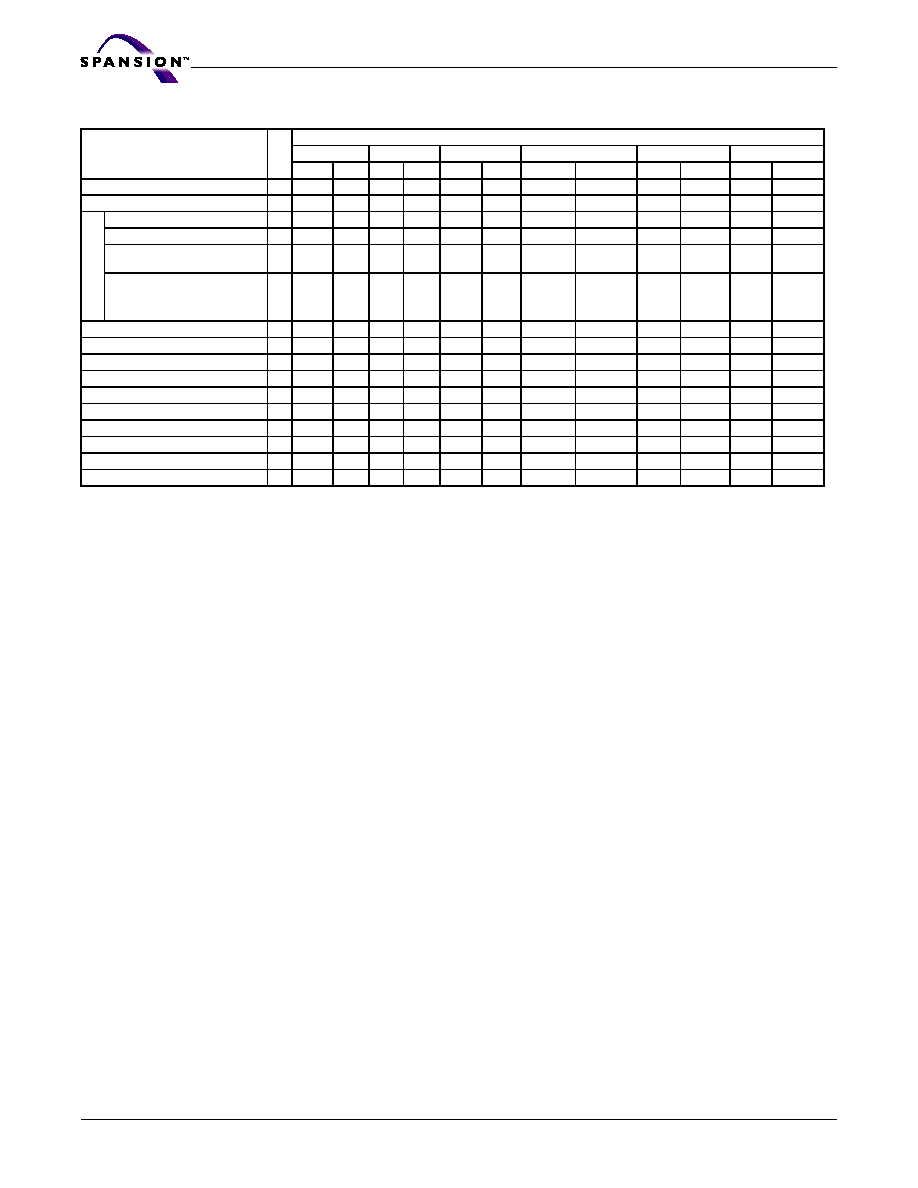

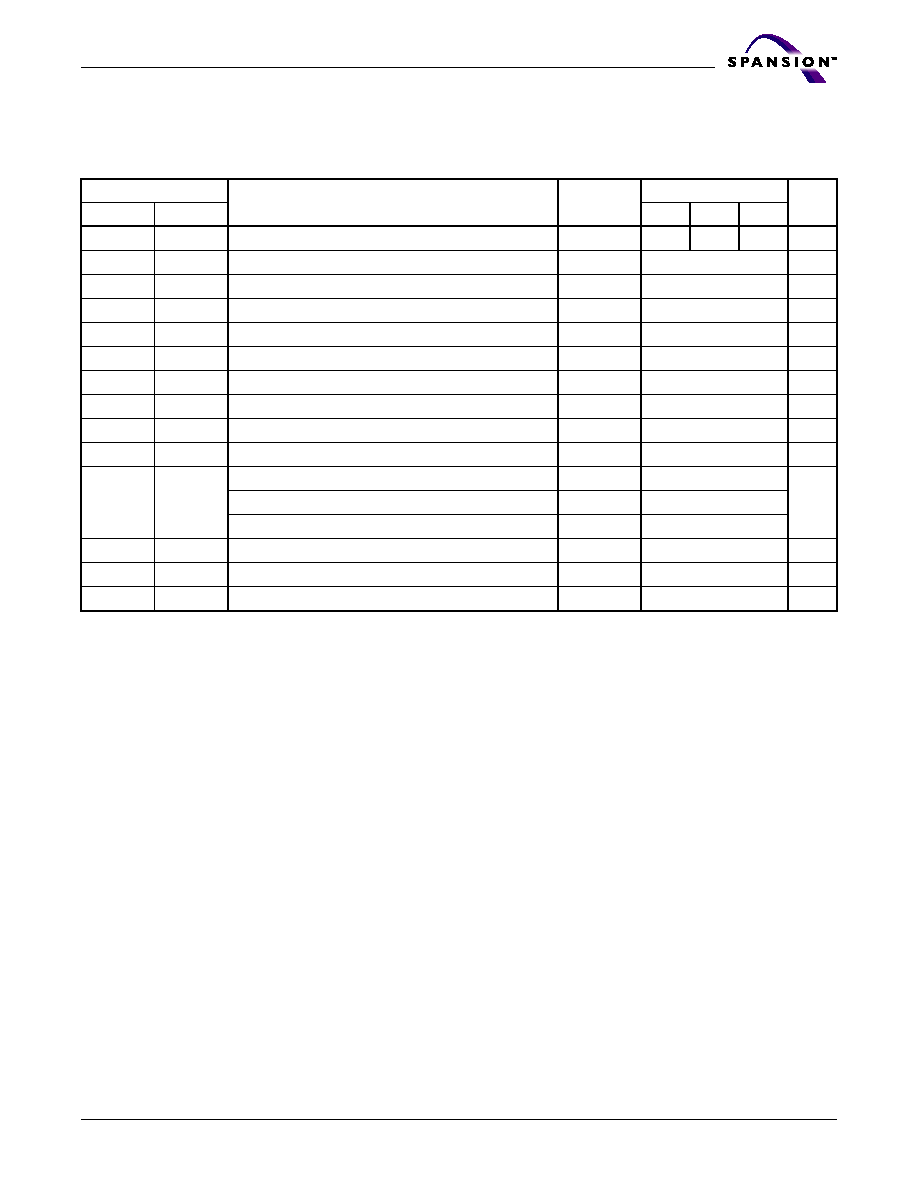

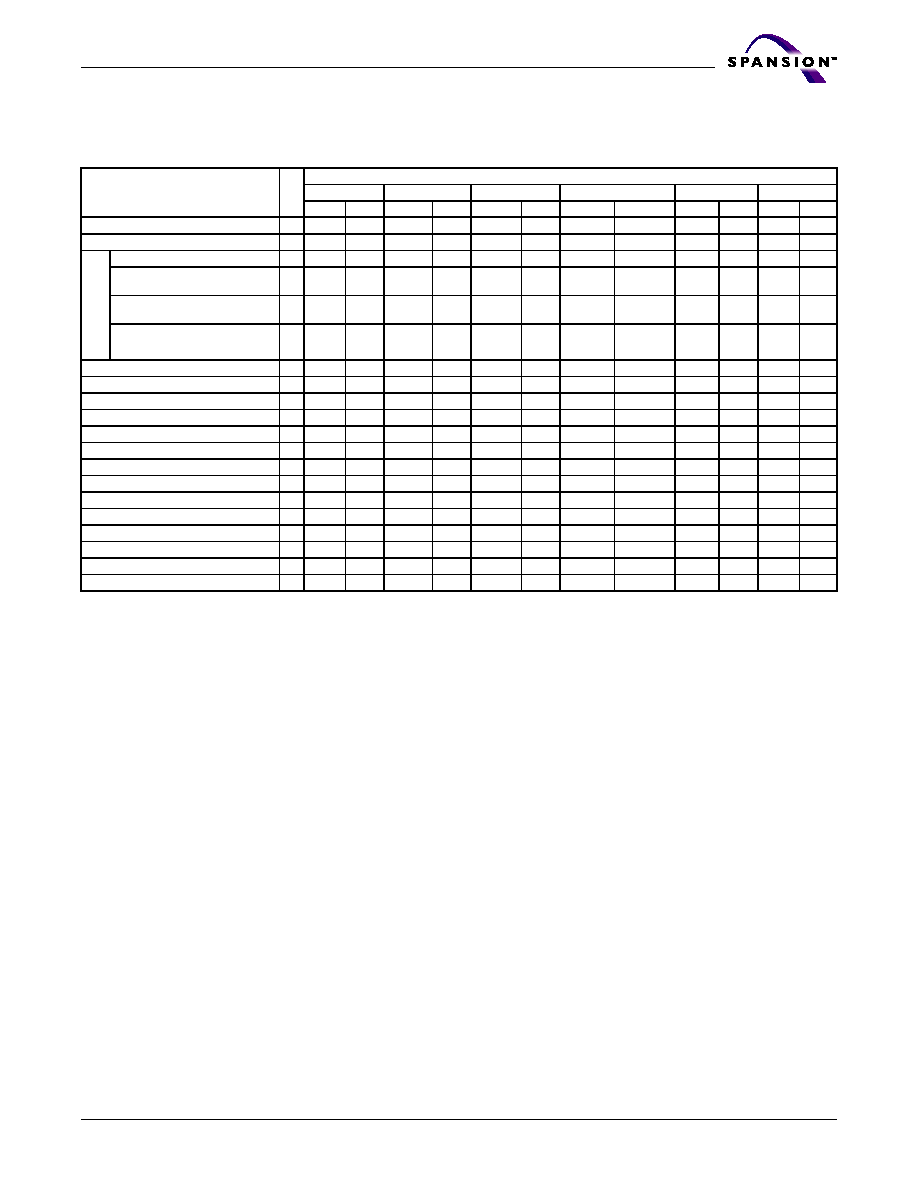

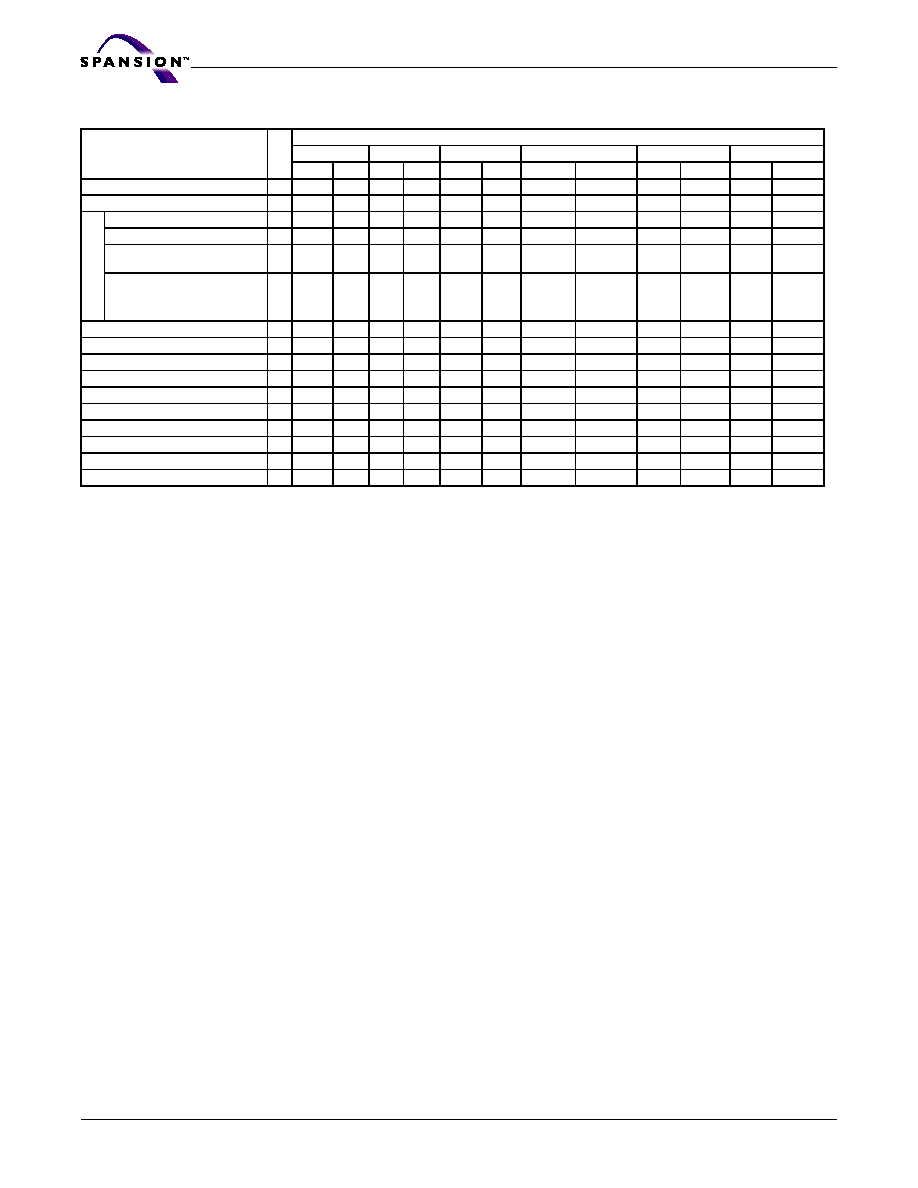

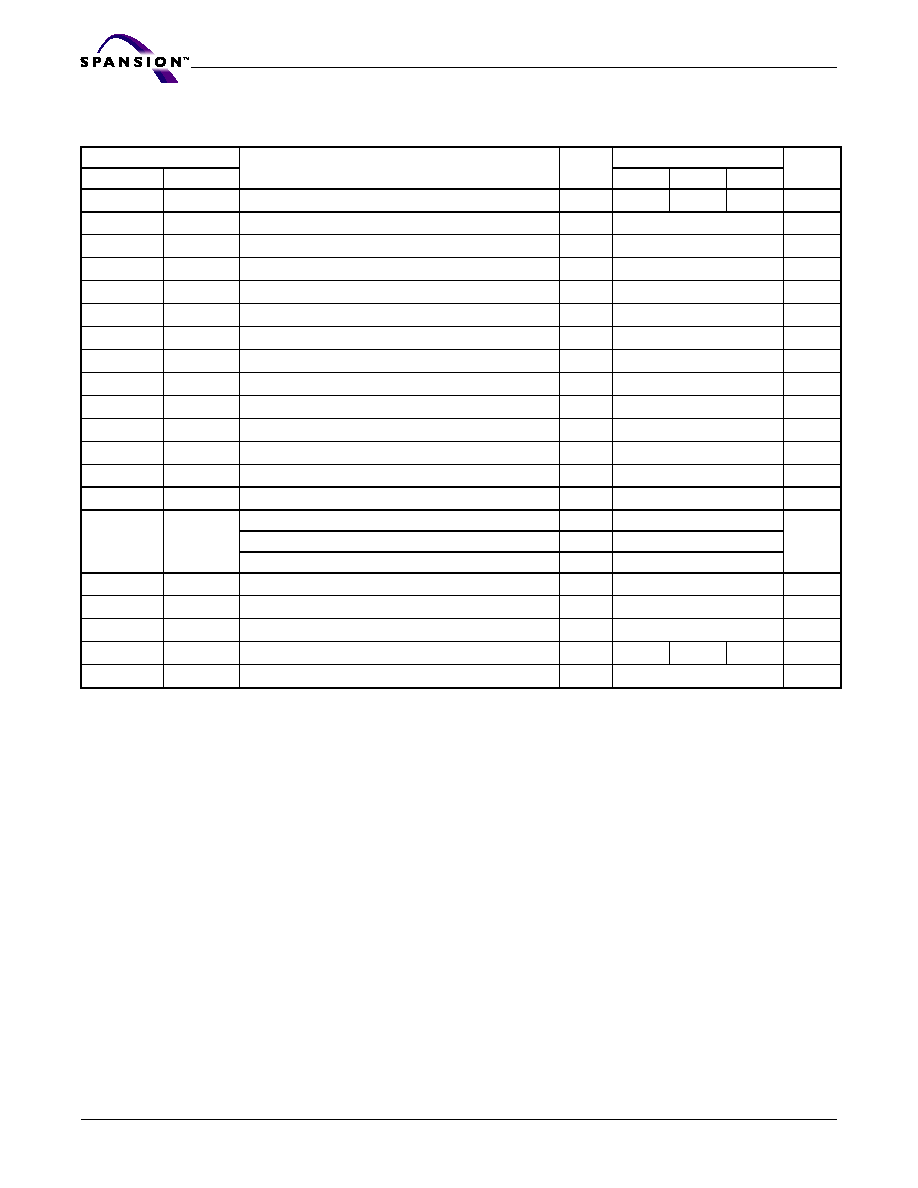

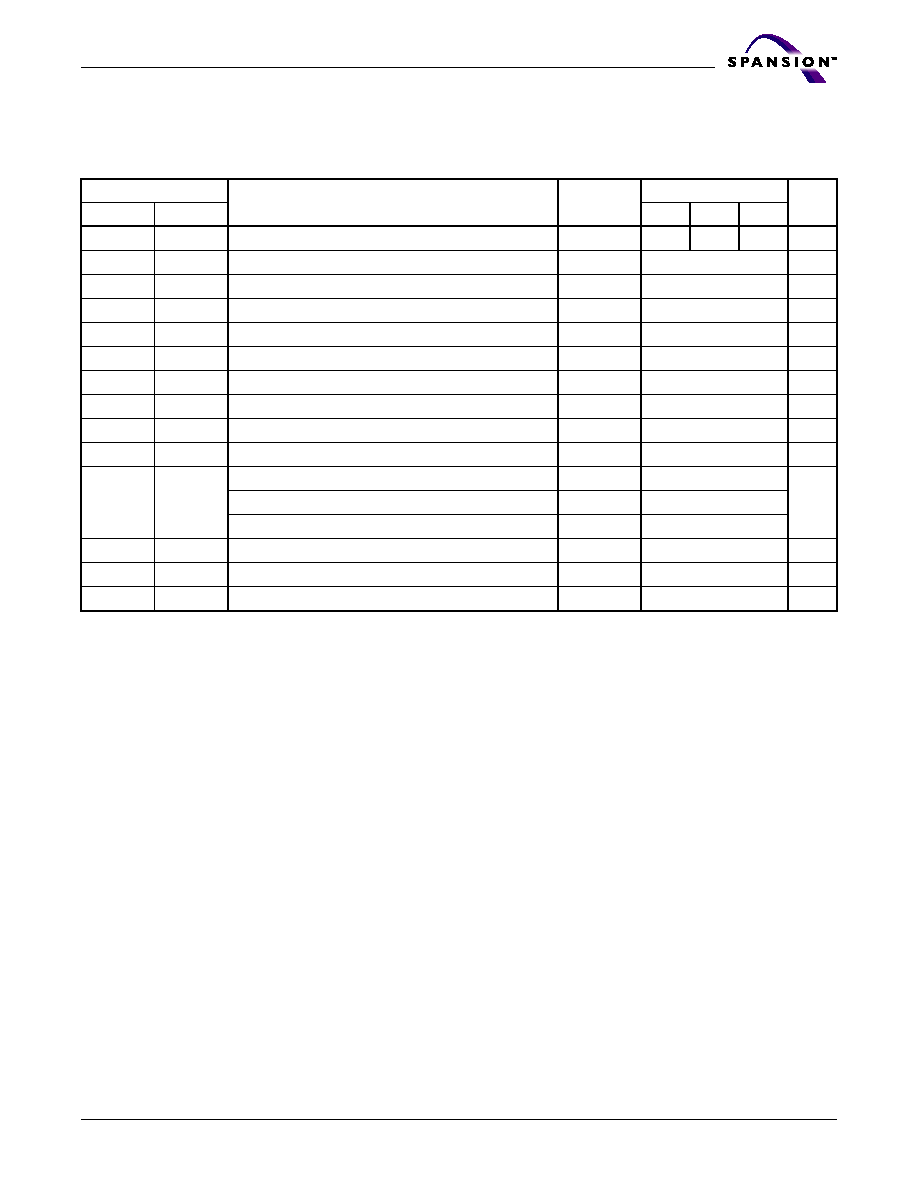

Erase and Program Operations-S29GL064A Only ..................................70

Erase and Program Operations-S29GL032A Only ....................................71

Figure 16. Program Operation Timings.................................. 72

Figure 17. Accelerated Program Timing Diagram .................... 72

6

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

Figure 18. Chip/Sector Erase Operation Timings..................... 73

Figure 19. Data# Polling Timings

(During Embedded Algorithms) ............................................ 73

Figure 20. Toggle Bit Timings (During Embedded Algorithms) .. 74

Figure 21. DQ2 vs. DQ6 ...................................................... 74

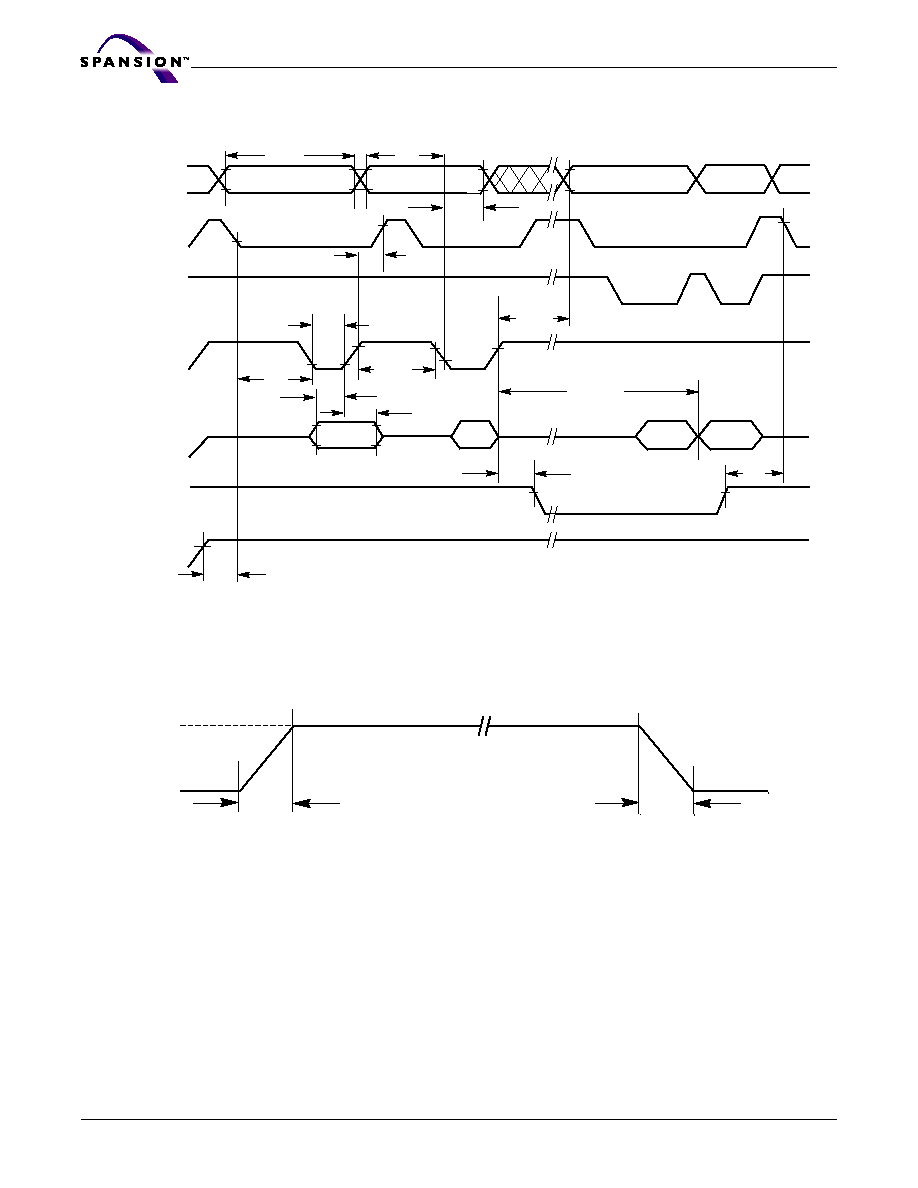

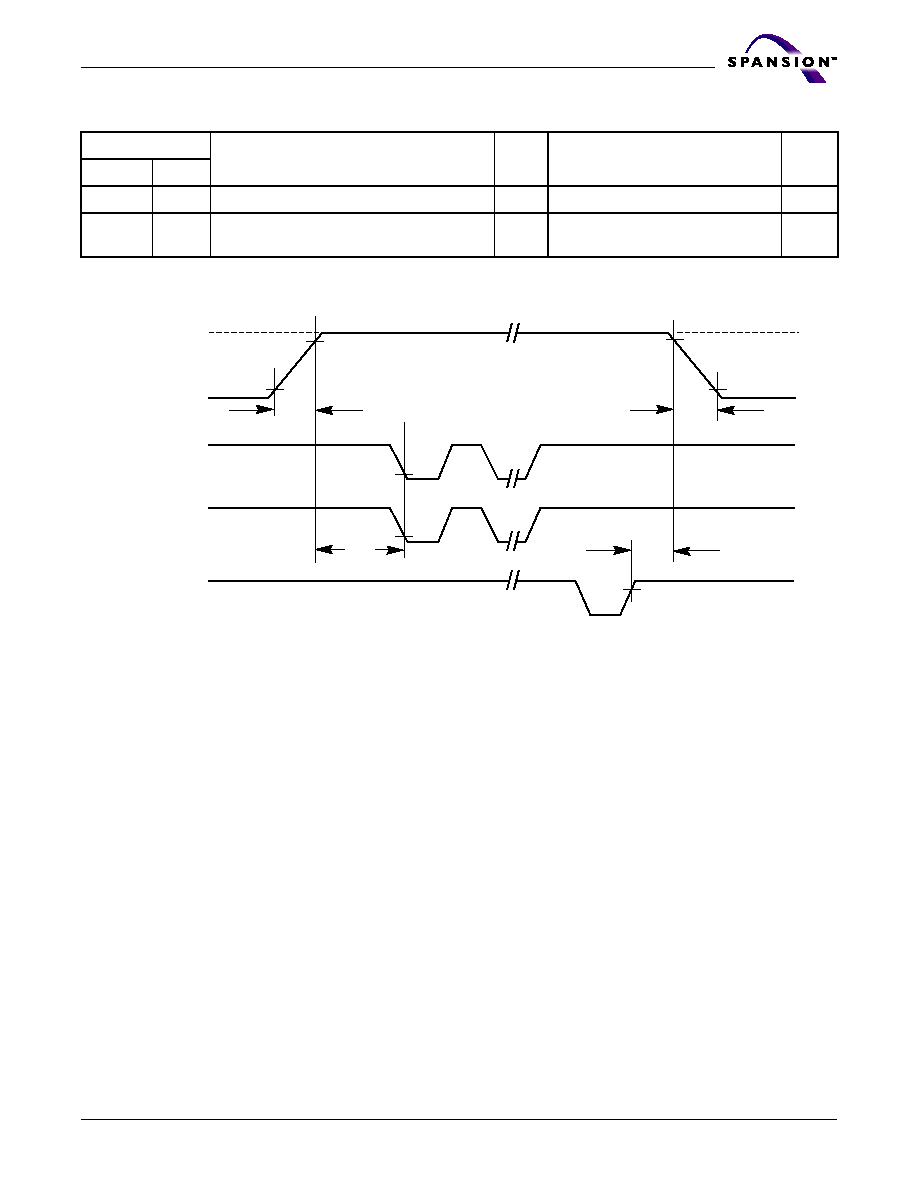

Temporary Sector Unprotect .........................................................................75

Figure 22. Temporary Sector Group Unprotect Timing Diagram 75

Figure 23. Sector Group Protect and Unprotect Timing Diagram 76

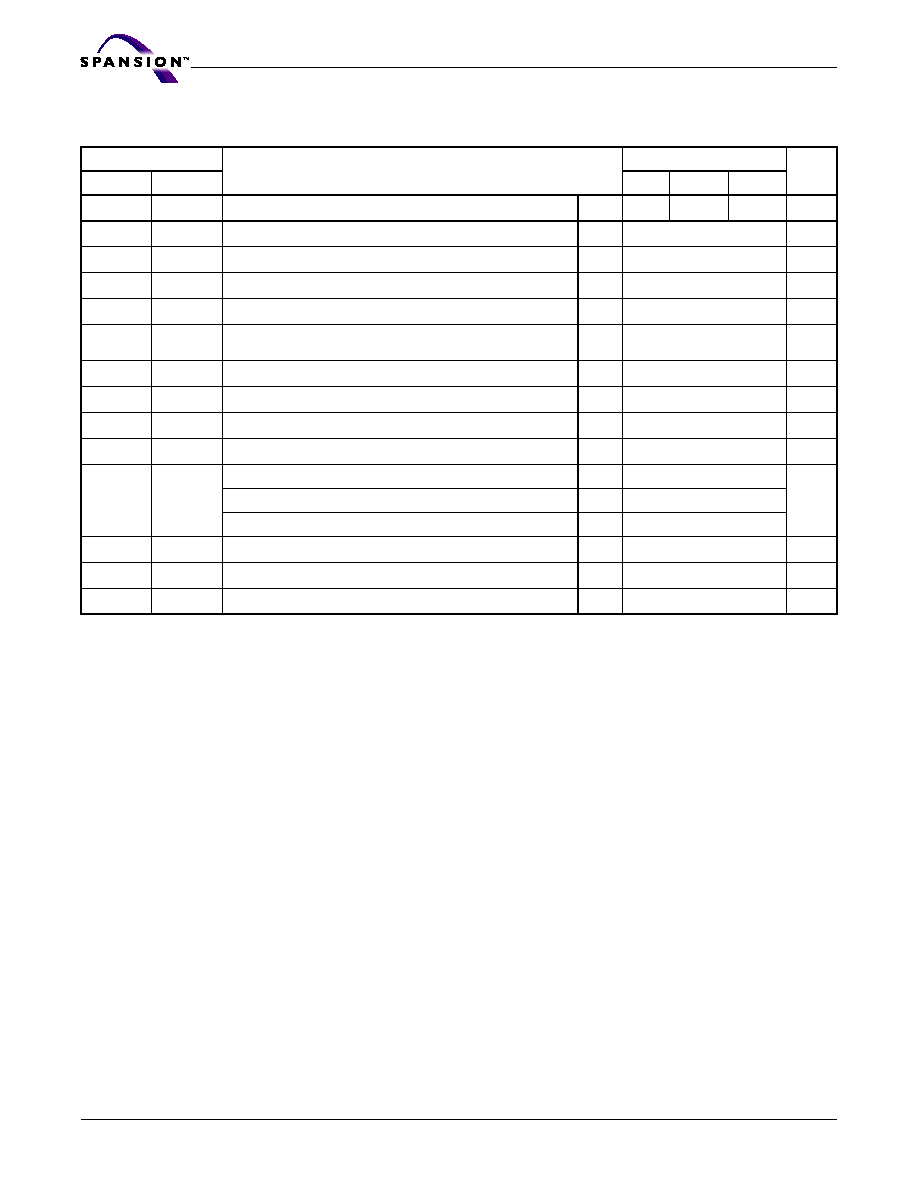

Alternate CE# Controlled Erase and

Program Operations-S29GL064A ..................................................................77

Alternate CE# Controlled Erase and

Program Operations-S29GL032A ..................................................................78

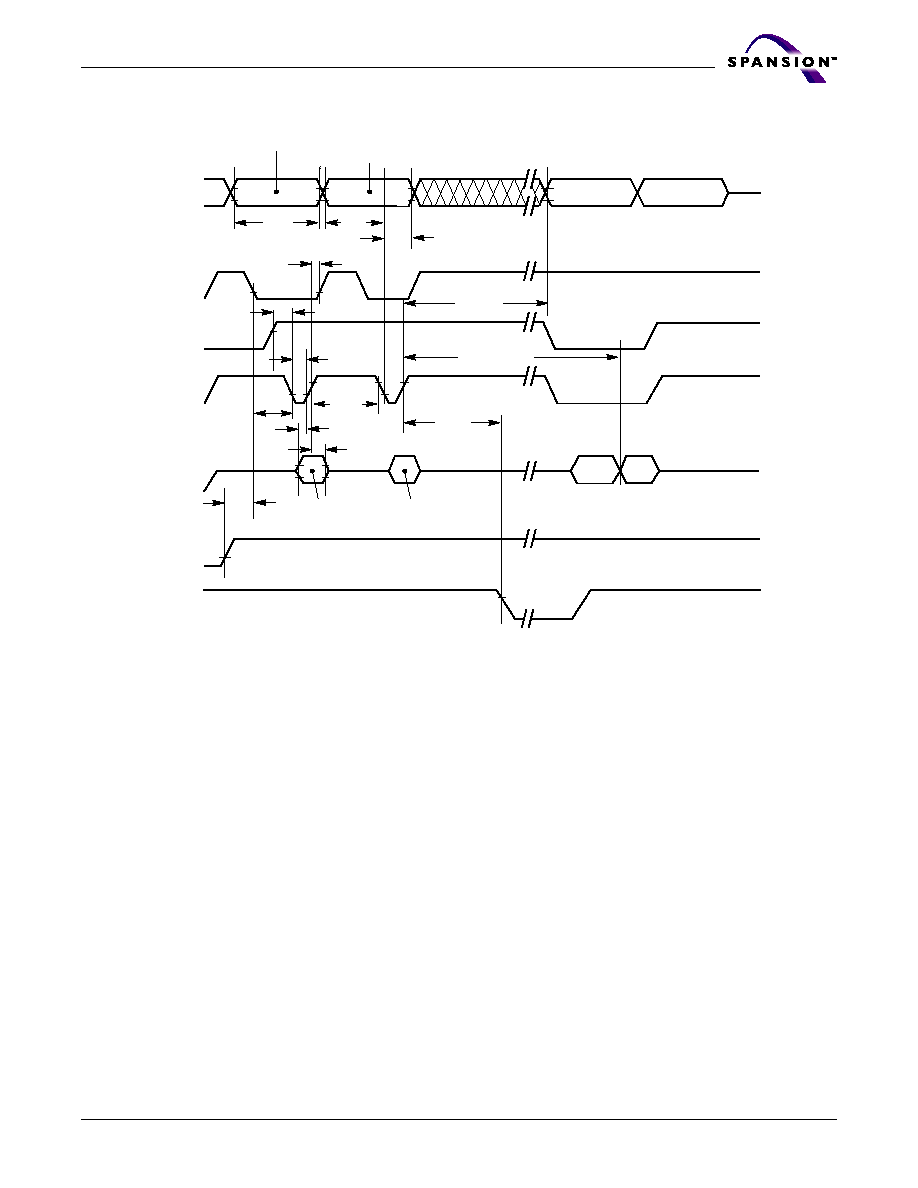

Figure 24. Alternate CE# Controlled Write

(Erase/Program) Operation Timings ..................................... 79

Erase And Programming Performance . . . . . . . . 80

TSOP Pin and BGA Package Capacitance . . . . . 81

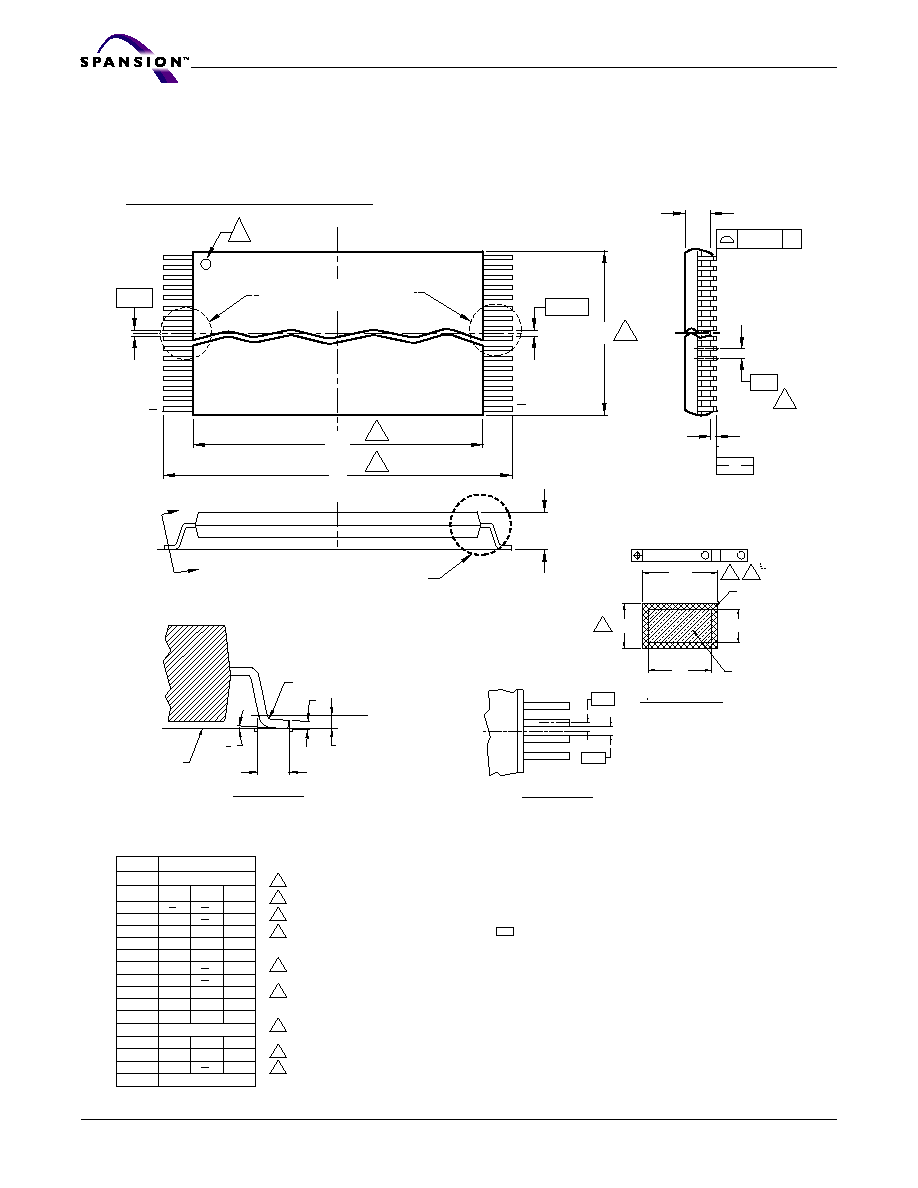

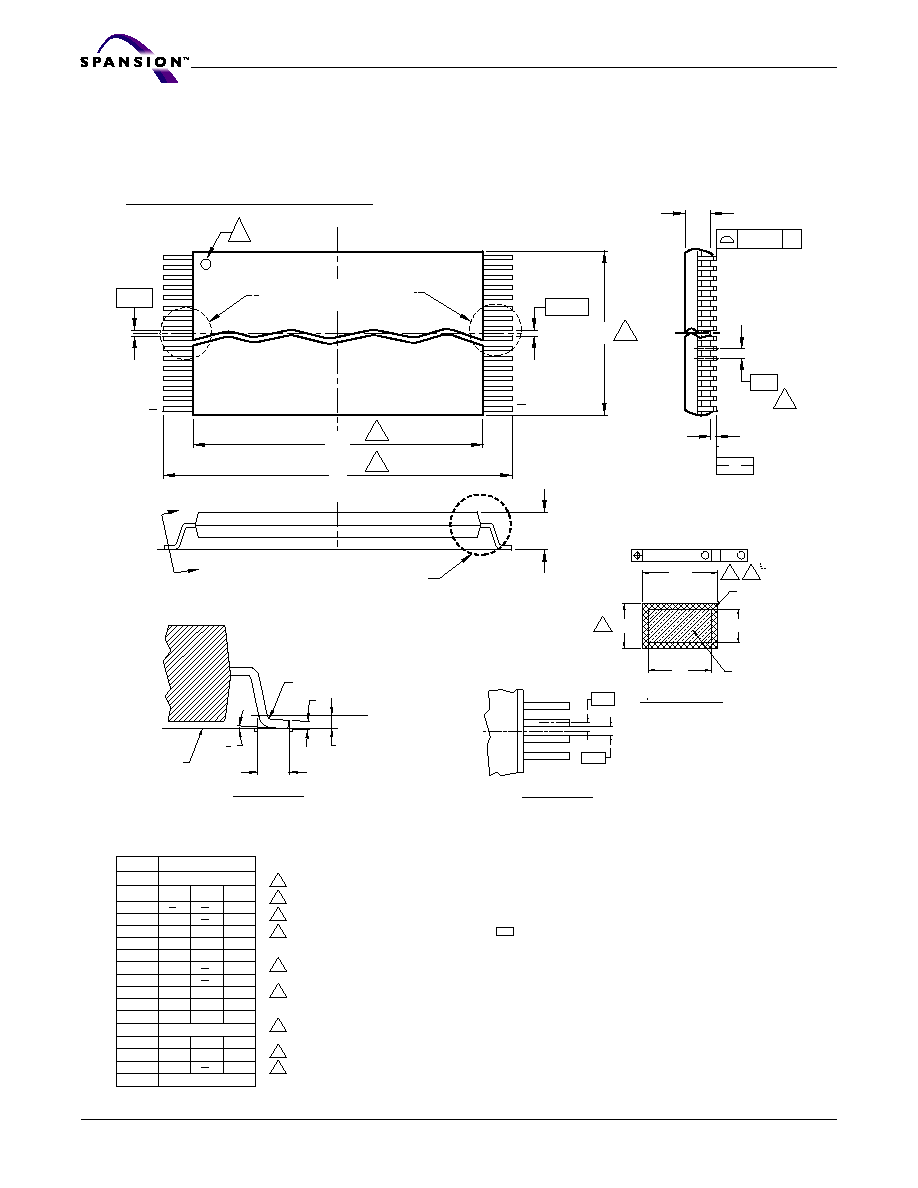

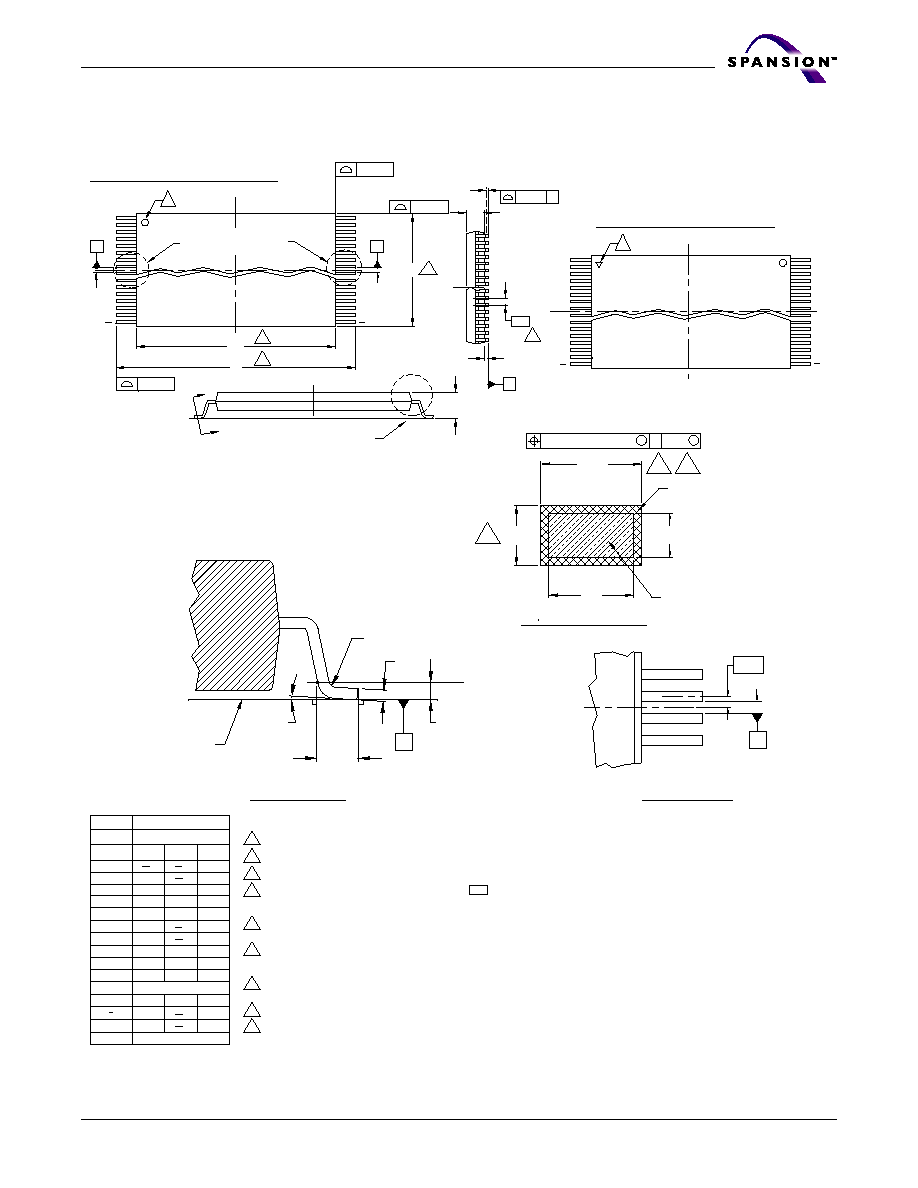

TS048--48-Pin Standard Thin Small Outline Package (TSOP) ............82

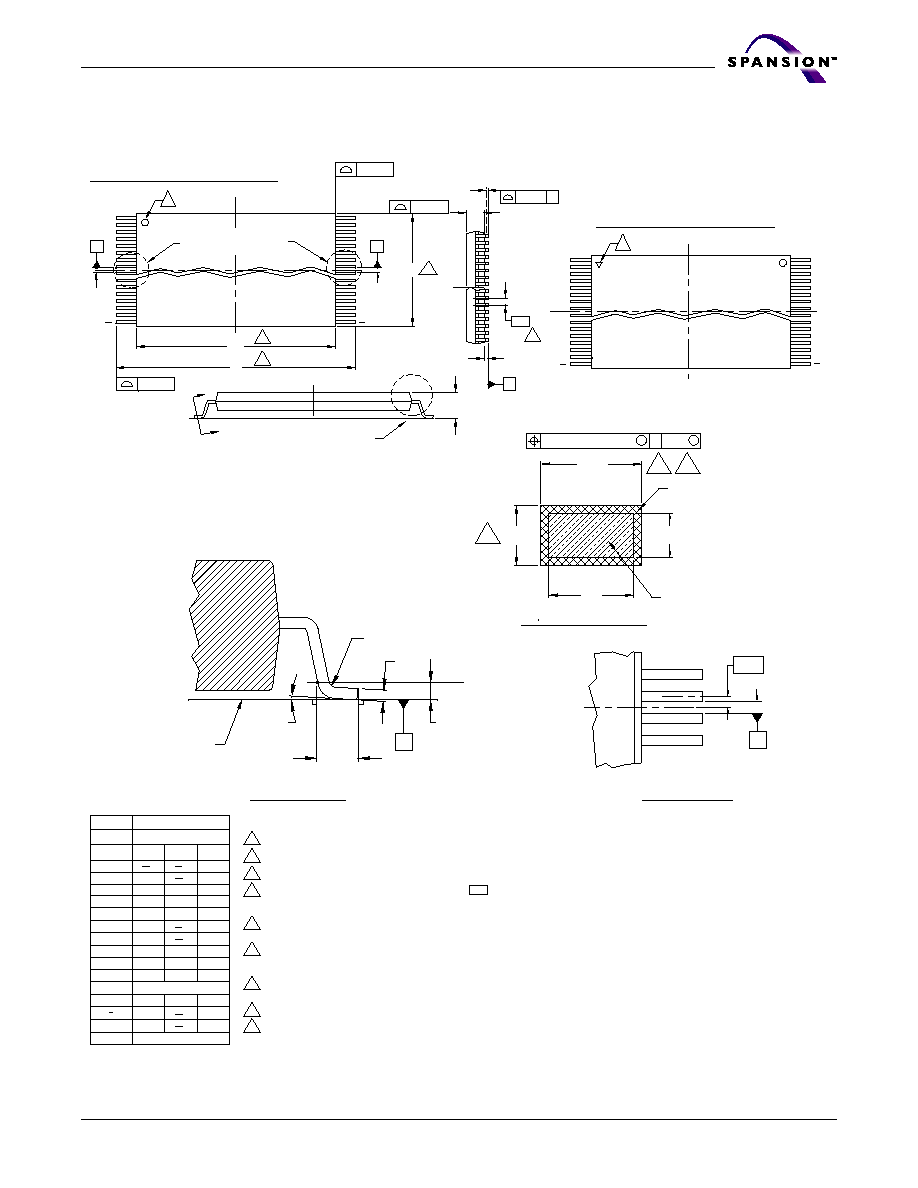

TS056--56-Pin Standard Thin Small Outline Package (TSOP) ............. 83

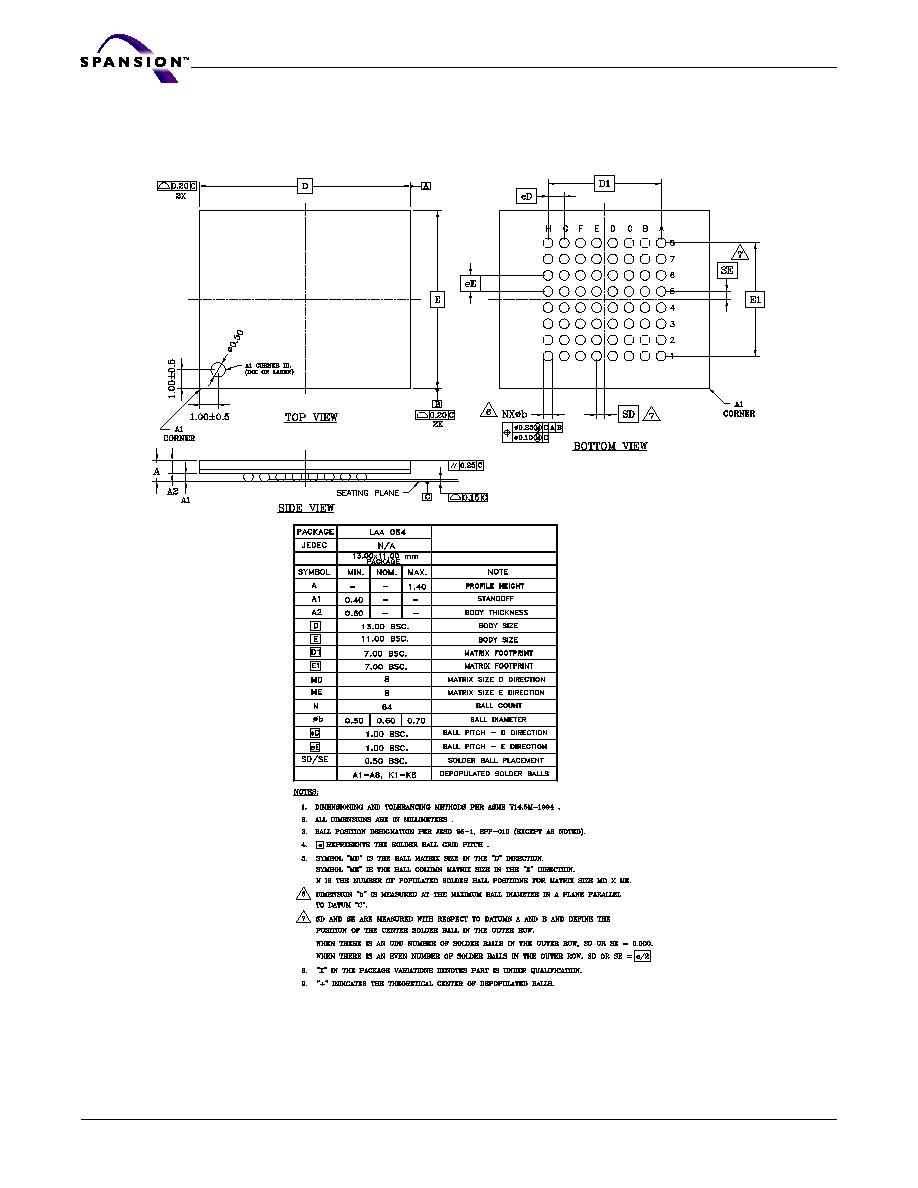

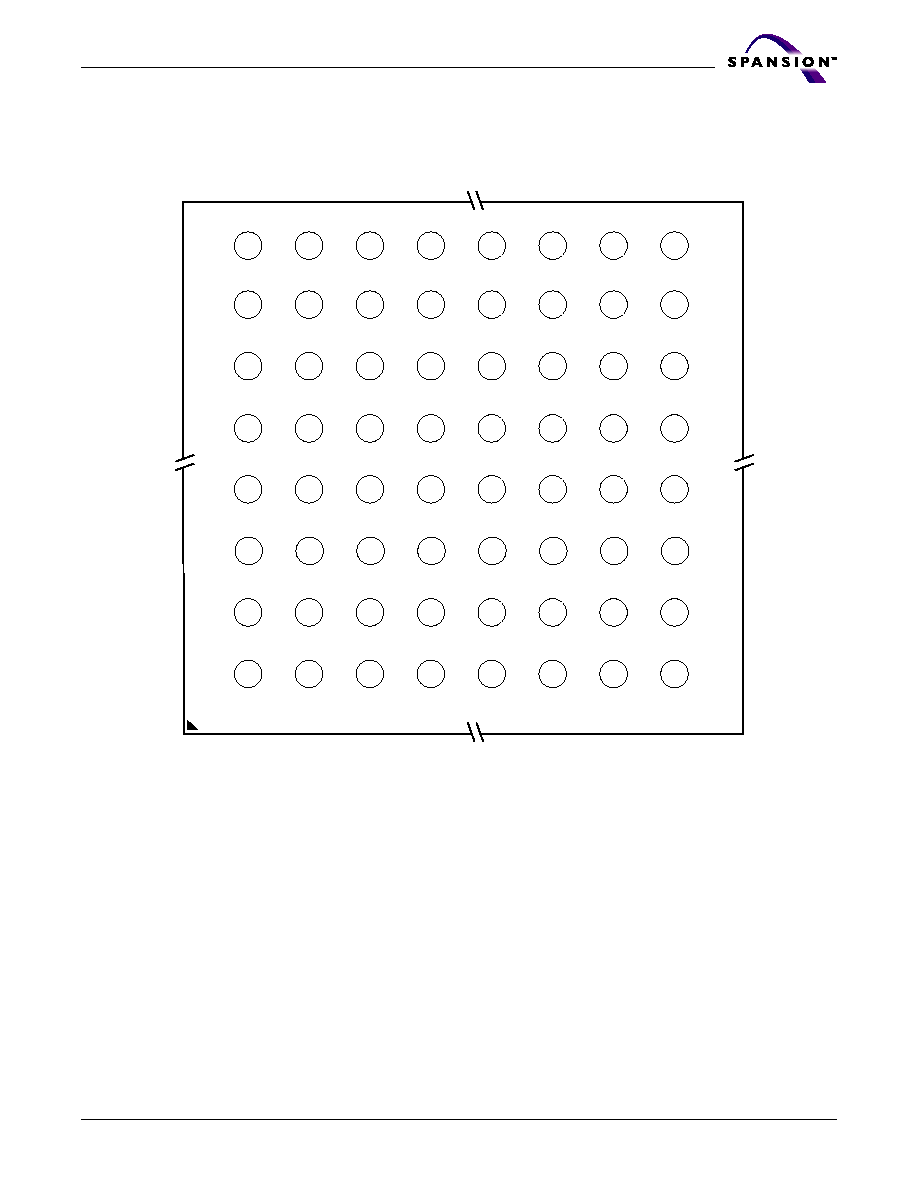

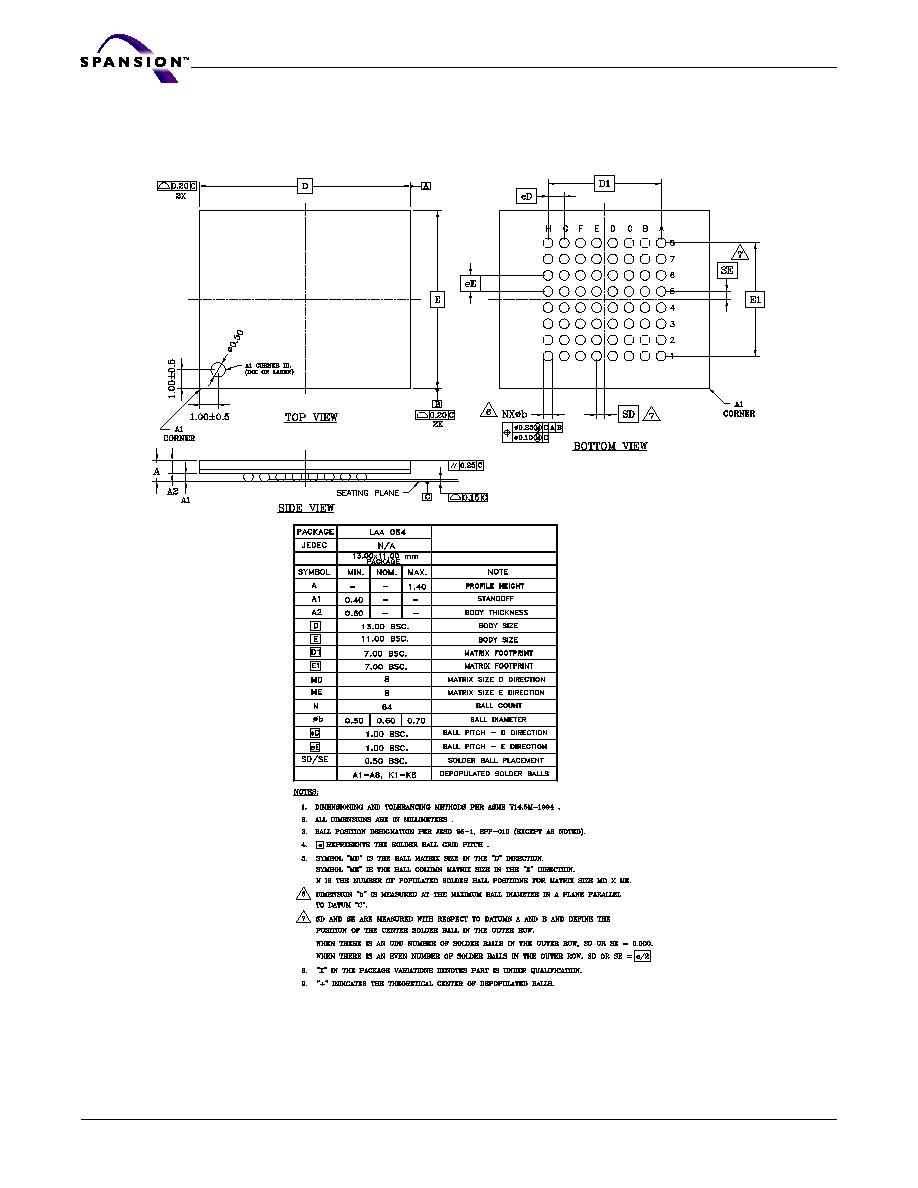

LAA064--64-Ball Fortified Ball Grid Array (BGA) ..................................84

Revision Summary . . . . . . . . . . . . . . . . . . . . . . . . . 86

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

7

A d v a n c e I n f o r m a t i o n

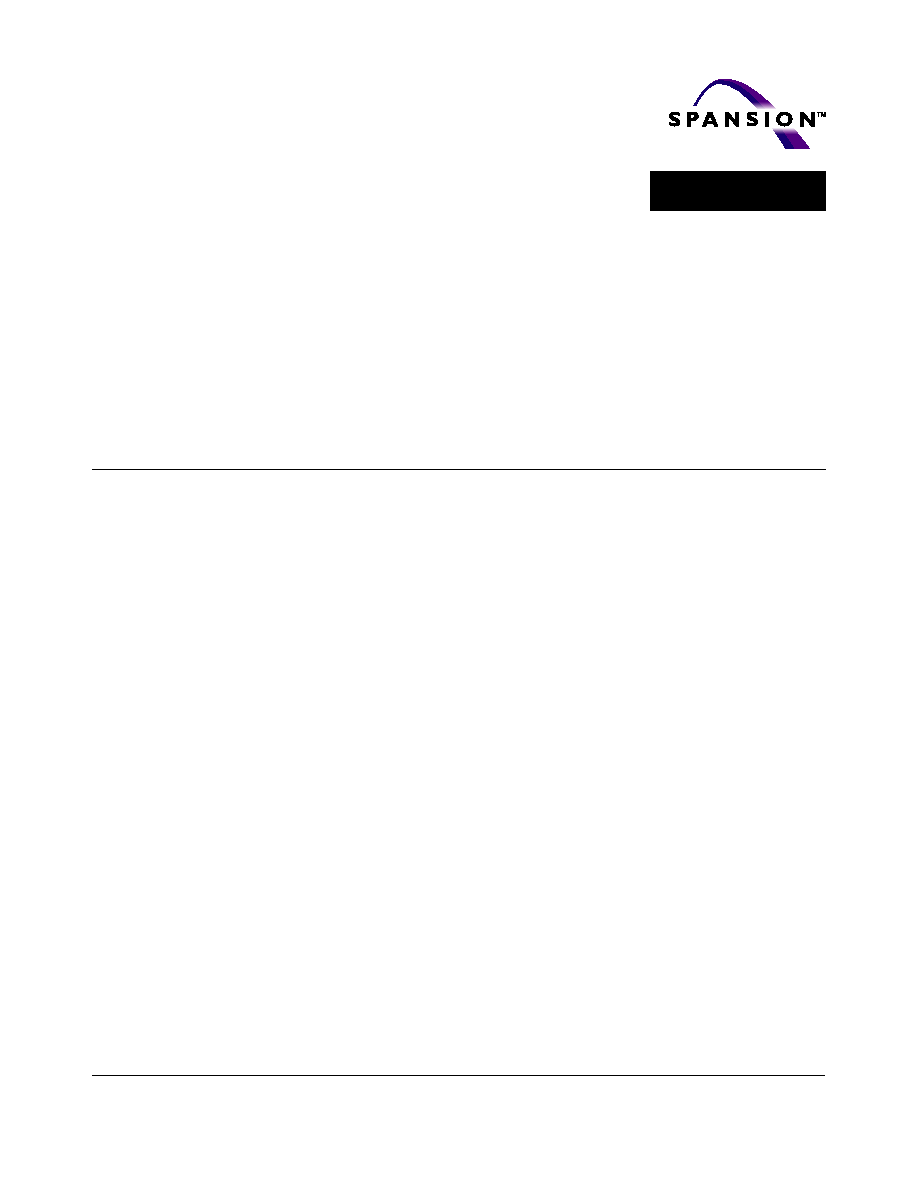

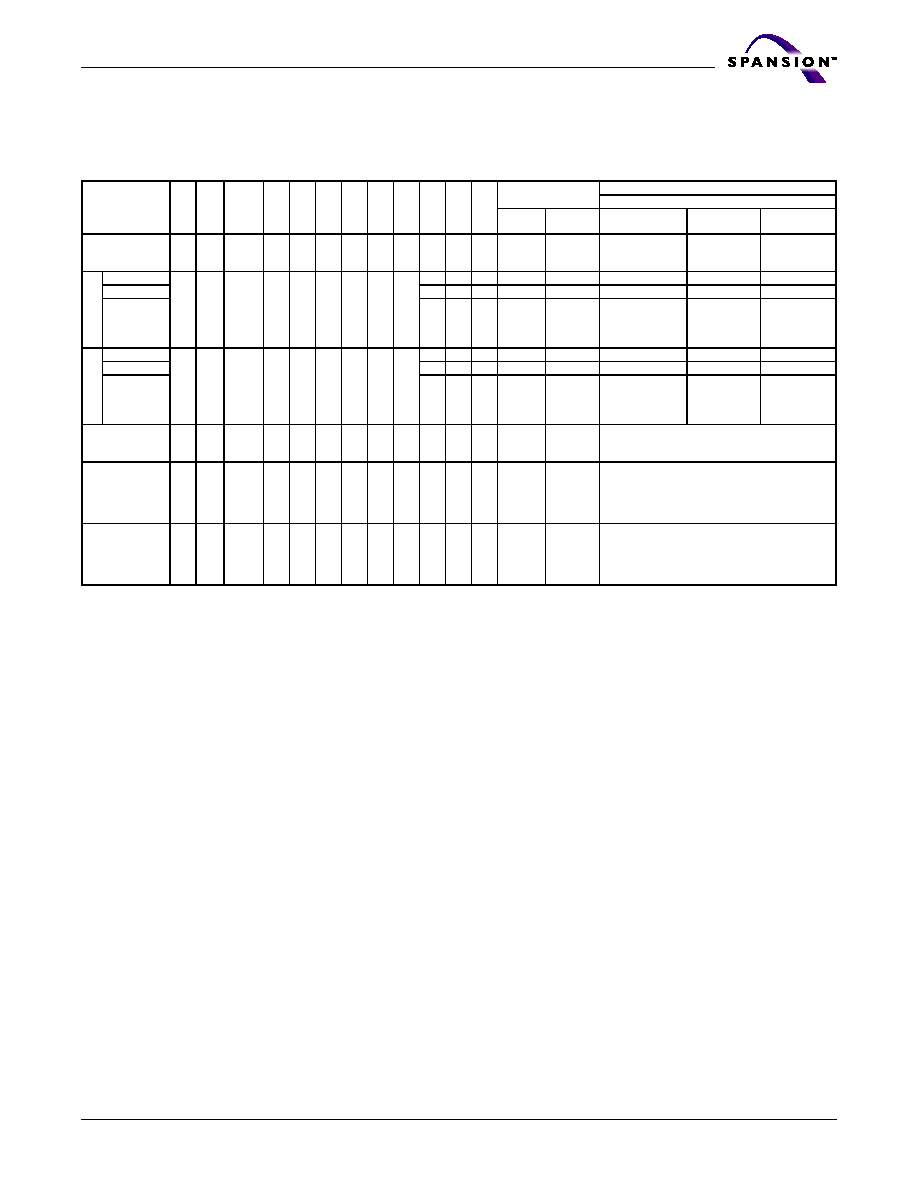

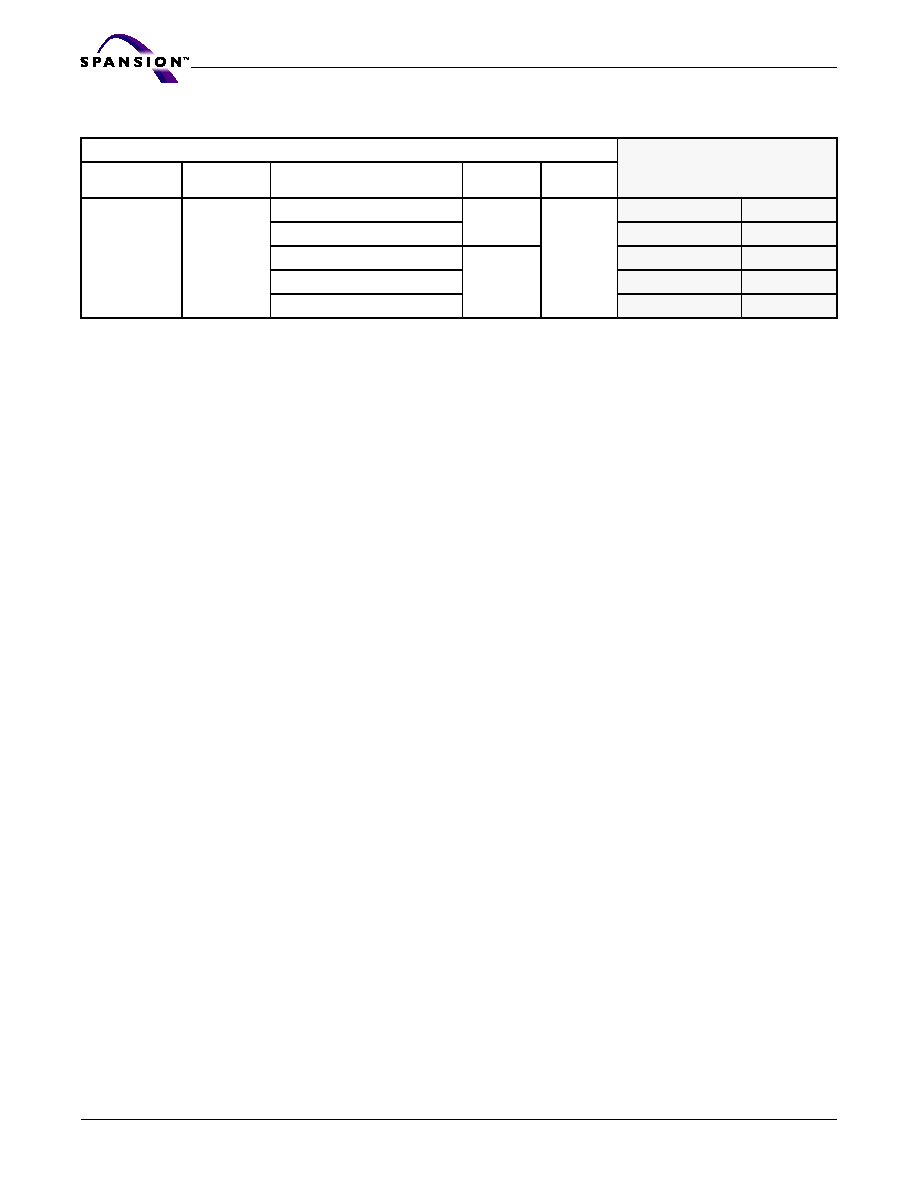

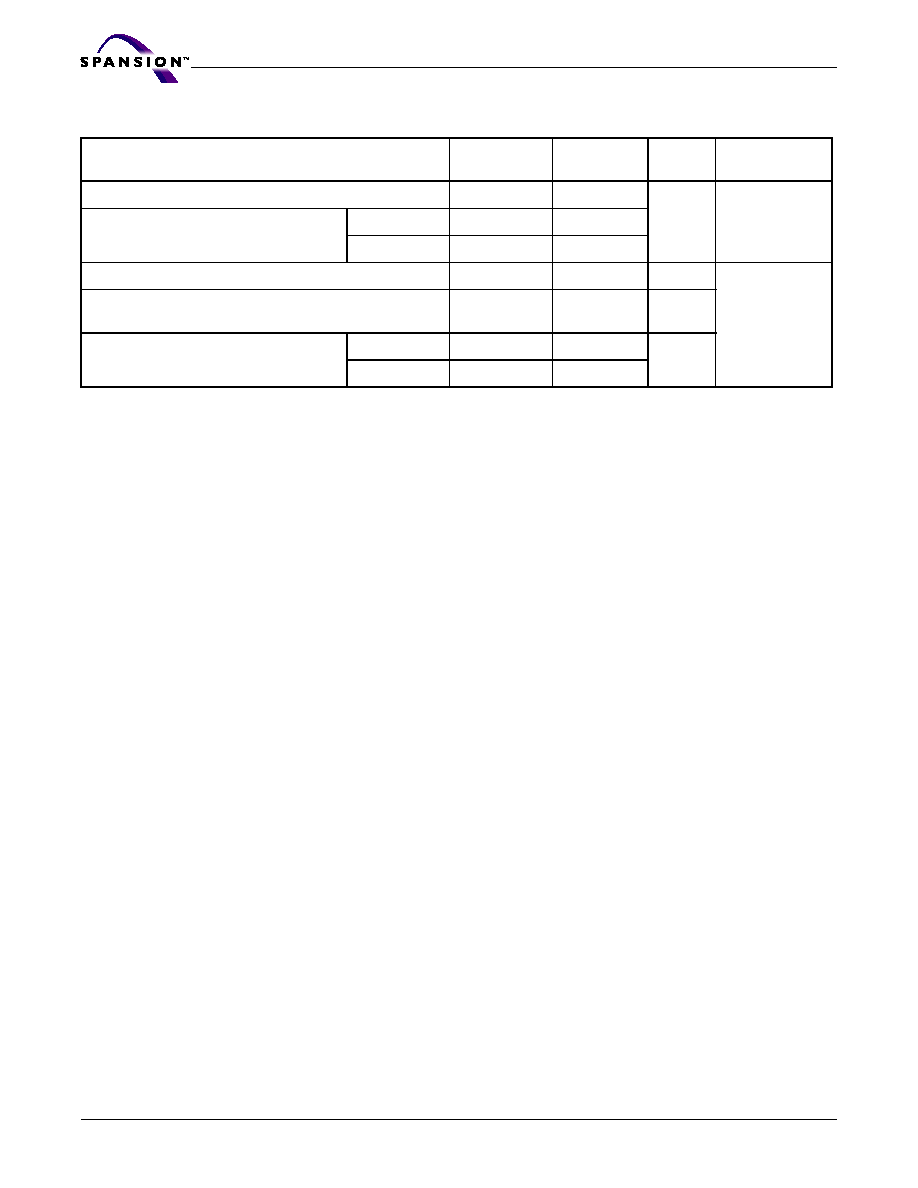

Product Selector Guide

S29GL064A, S29GL032A

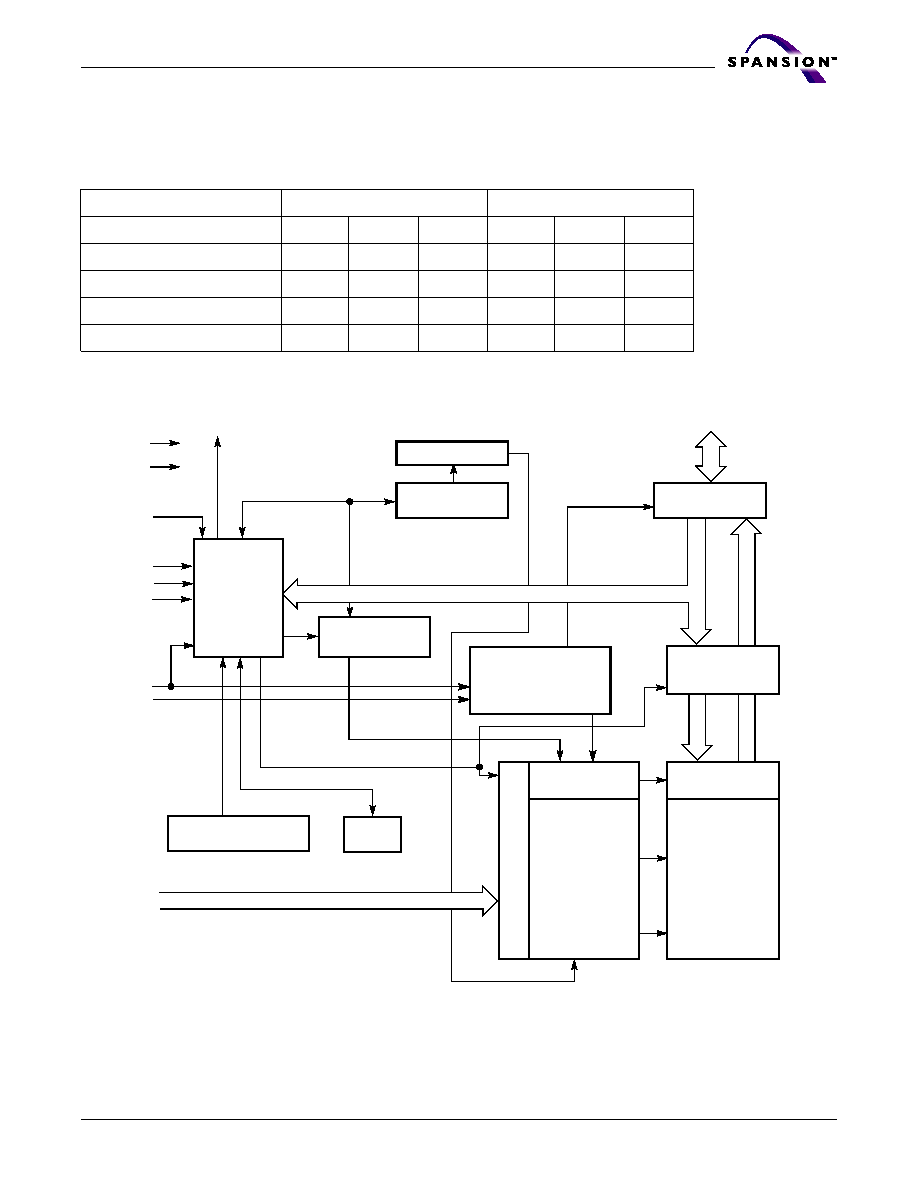

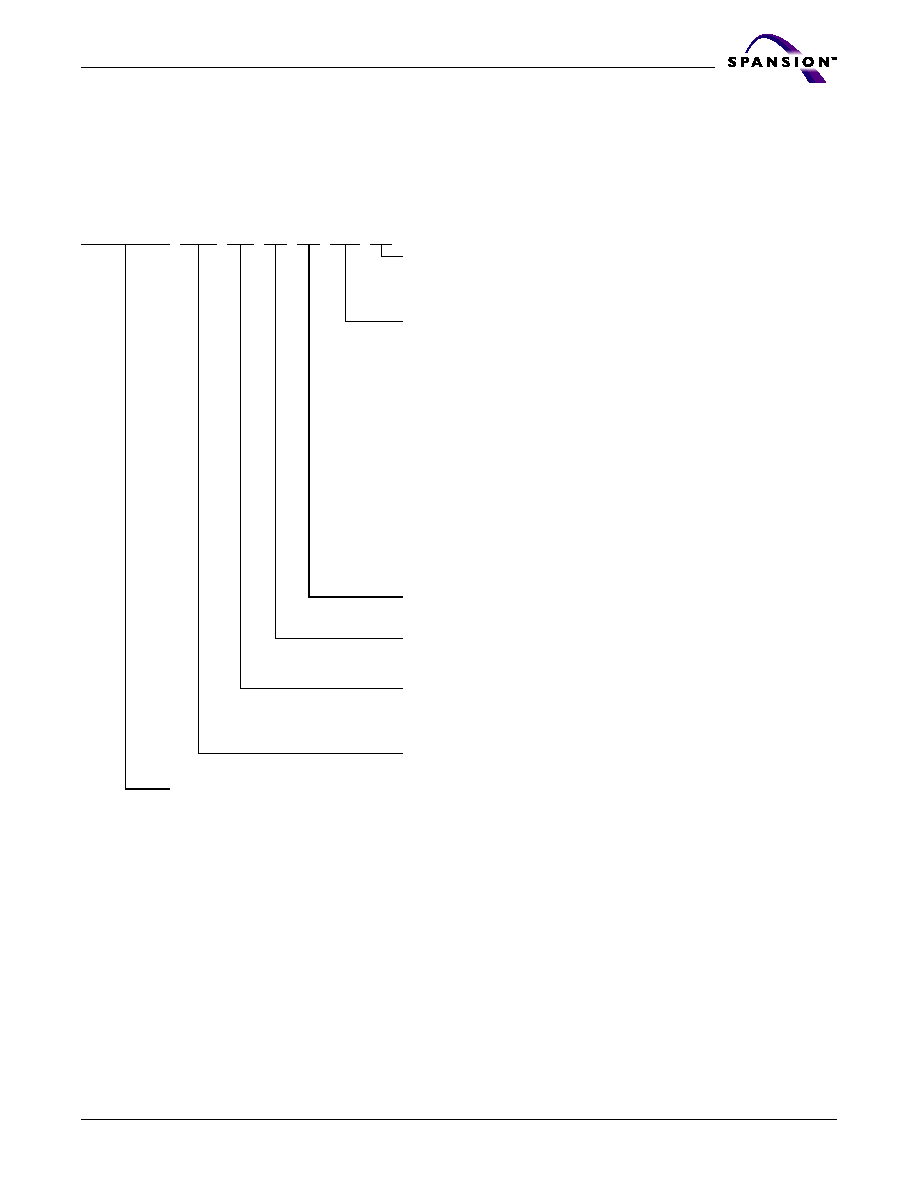

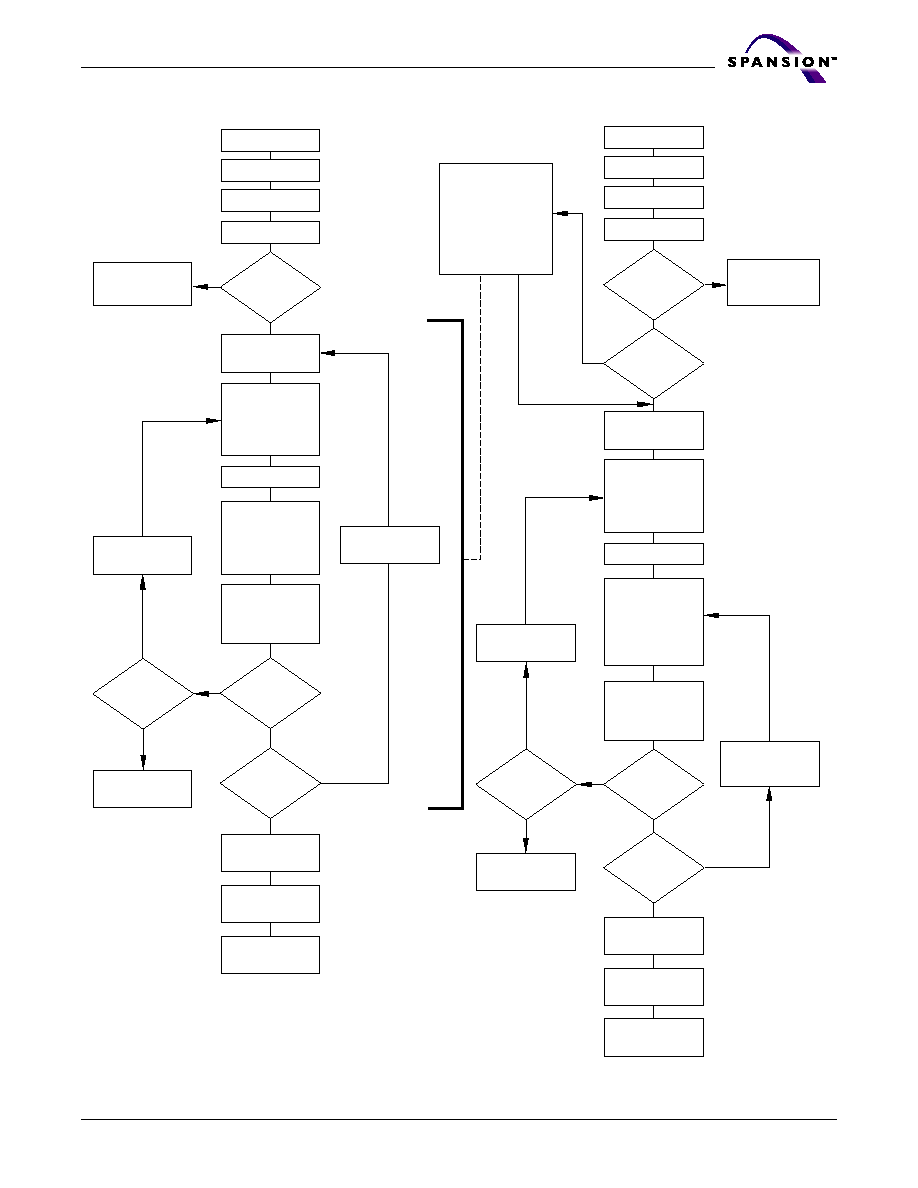

Block Diagram

Note:

**A

MAX

GL064A = A21.

**A

MAX

GL032A = A20.

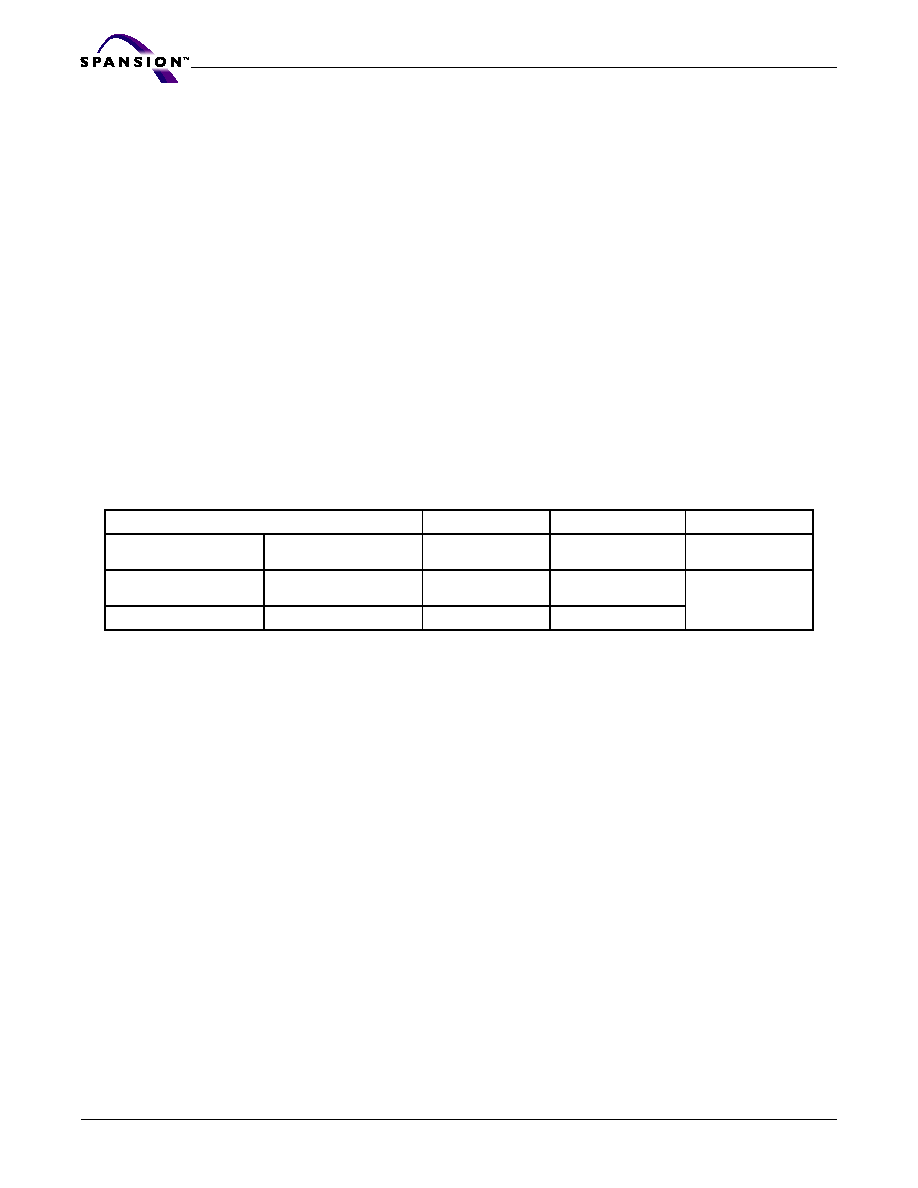

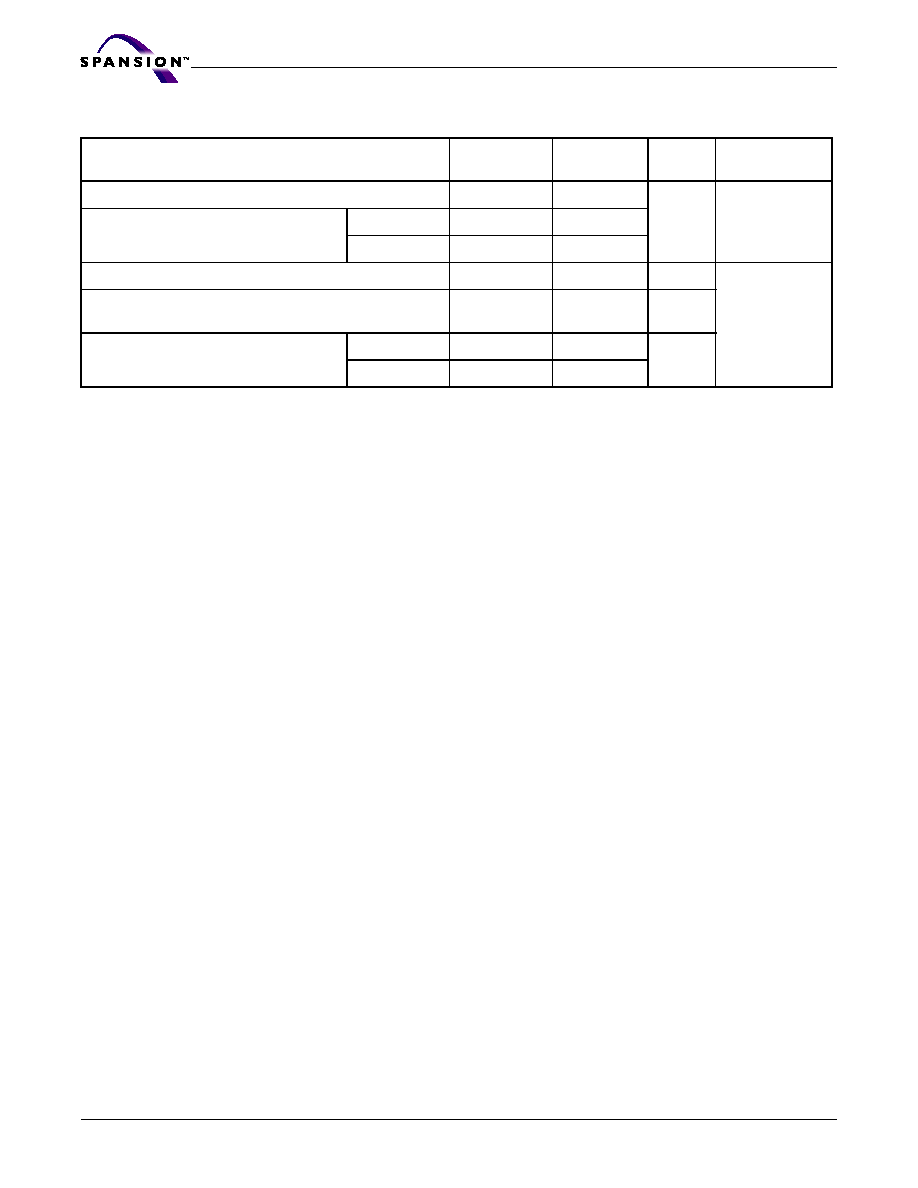

Part Number

S29GL064A

S29GL032A

Speed Option

90

10

11

90

10

11

Max. Access Time (ns)

90

100

110

90

100

110

Max. CE# Access Time (ns)

90

100

110

90

100

110

Max. Page Access Time (ns)

25

30

30

25

30

30

Max. OE# Access Time (ns)

25

30

30

25

30

30

Input/Output

Buffers

X-Decoder

Y-Decoder

Chip Enable

Output Enable

Logic

Erase Voltage

Generator

PGM Voltage

Generator

Timer

V

CC

Detector

State

Control

Command

Register

V

CC

V

SS

WE#

WP#/ACC

BYTE#

CE#

OE#

STB

STB

DQ15

≠

DQ0 (A-1)

Sector Switches

RY/BY#

RESET#

Data

Latch

Y-Gating

Cell Matrix

Addre

s

s Latch

A

Max

**≠A0

8

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

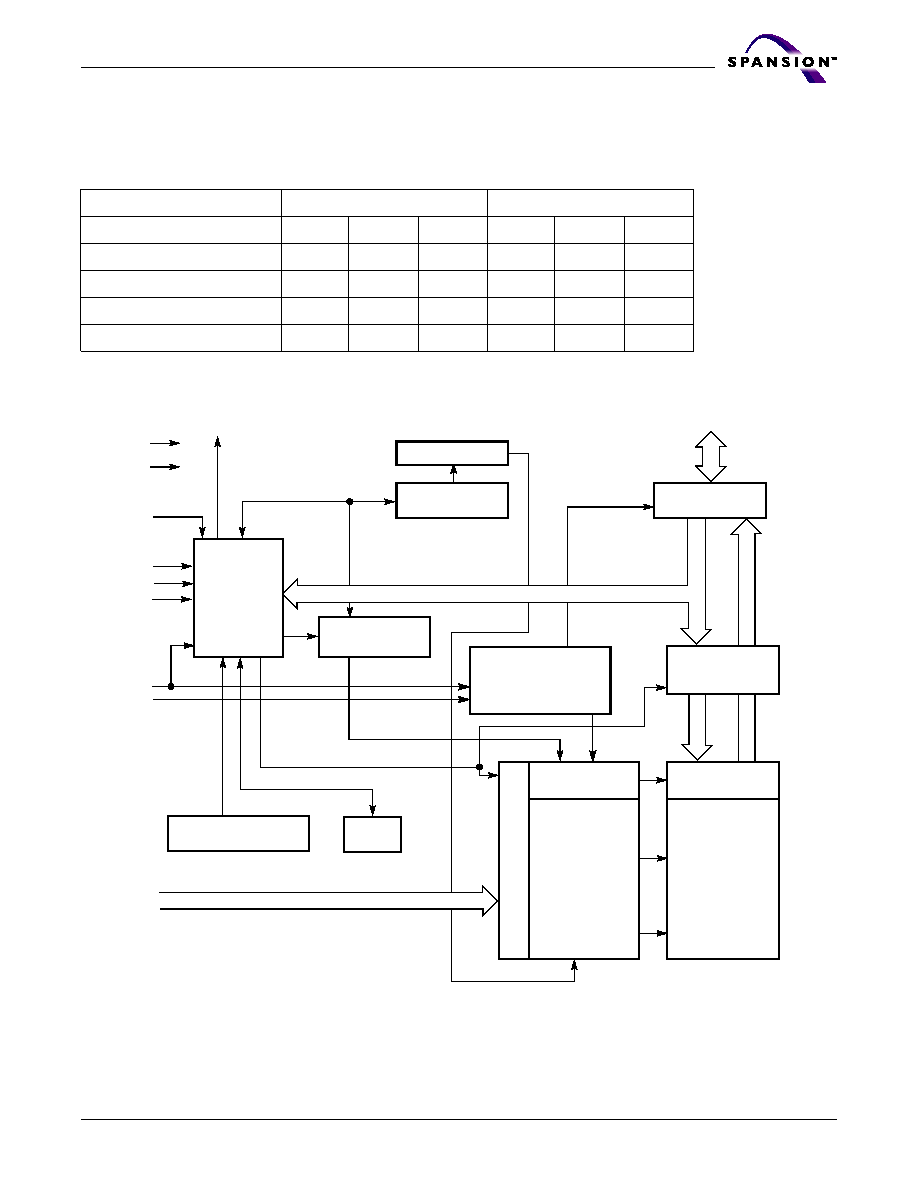

Connection Diagrams

Notes:

1. Pin 9 is A21, Pin 13 is ACC, Pin 14 is WP#, Pin 15 is A19, and Pin 47 is V

IO

on S29GL064A (models R6, R7).

2. Pin 13 is NC on S29GL032A.

Notes:

1. Pin 15 is NC on S29GL032A.

1

16

2

3

4

5

6

7

8

17

18

19

20

21

22

23

24

9

10

11

12

13

14

15

48

33

47

46

45

44

43

42

41

40

39

38

37

36

35

34

25

32

31

30

29

28

27

26

A15

A18

A14

A13

A12

A11

A10

A9

A8

A19

1

A20

WE#

RESET#

A21

1,2

WP#/ACC

1

RY/BY#

1

A1

A17

A7

A6

A5

A4

A3

A2

A16

DQ2

BYTE#

1

V

SS

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ9

DQ1

DQ8

DQ0

OE#

V

SS

CE#

A0

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

48-Pin Standard TSOP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

NC

NC

A15

A14

A13

A12

A11

A10

A9

A8

A19

A20

WE#

RESET#

A21

1

WP#/ACC

RY/BY#

A18

A17

A7

A6

A5

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

NC

NC

A16

BYTE#

V

SS

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

23

24

25

26

27

28

A4

A3

A2

A1

NC

NC

34

33

32

31

30

29

OE#

V

SS

CE#

A0

NC

V

IO

56-Pin Standard TSOP

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

9

A d v a n c e I n f o r m a t i o n

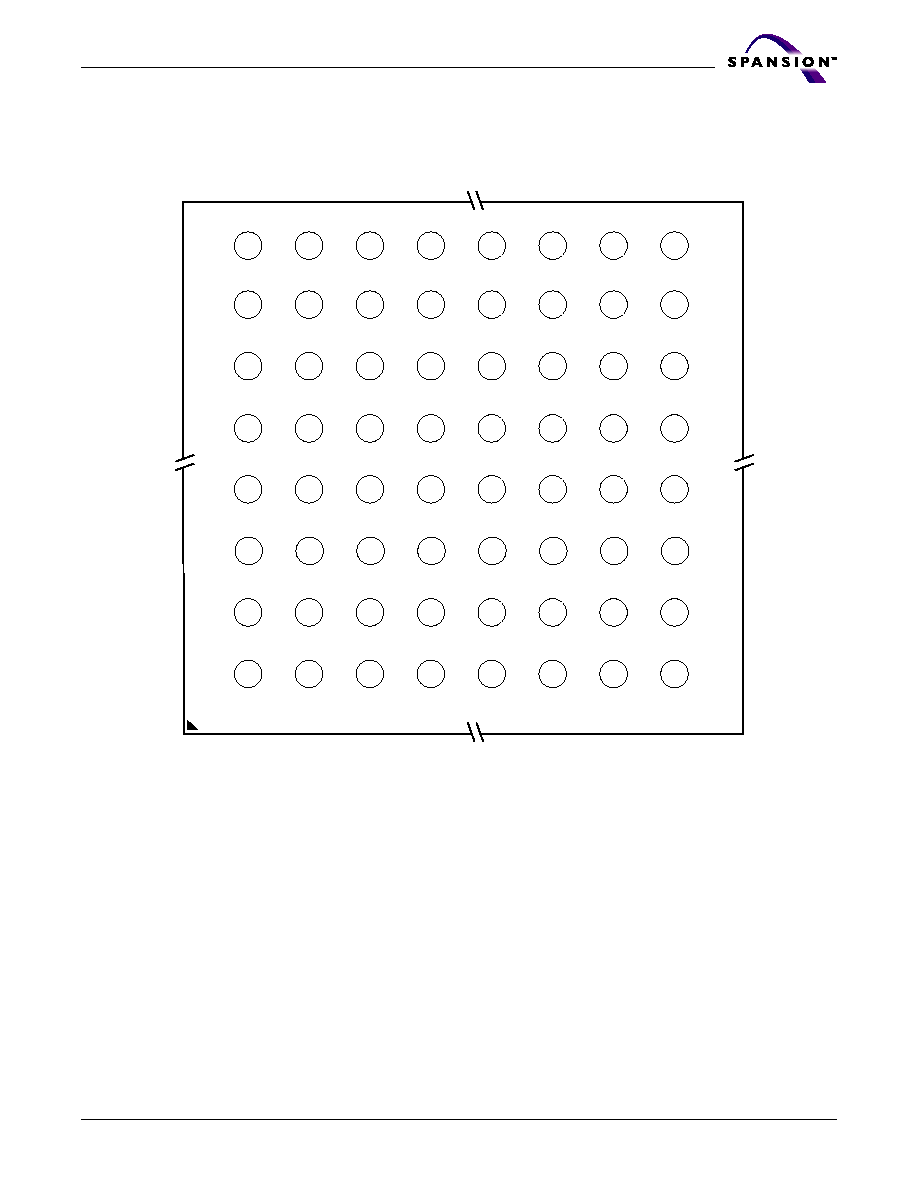

Notes:

1. Ball D8 and Ball F1 are NC on S29GL064A (models R3, R4).

2. Ball F7 is NC on S29GL064A (model R5).

3. Ball C5 is NC on S29GL032A.

Special Package Handling Instructions

Special handling is required for Flash Memory products in moulded packages

(TSOP and BGA). The package and/or data integrity may be compromised if the

package body is exposed to temperatures above 150∞C for prolonged periods of

time.

A2

C2

D2

E2

F2

G2

H2

A3

C3

D3

E3

F3

G3

H3

A4

C4

D4

E4

F4

G4

H4

A5

C5

D5

E5

F5

G5

H5

A6

C6

D6

E6

F6

G6

H6

A7

C7

D7

E7

F7

G7

H7

DQ15/A-1

V

SS

BYTE#

2

A16

A15

A14

A12

A13

DQ13

DQ6

DQ14

DQ7

A11

A10

A8

A9

V

CC

DQ4

DQ12

DQ5

A19

A213

RESET#

WE#

DQ11

DQ3

DQ10

DQ2

A20

A18

WP#/ACC

RY/BY#

DQ9

DQ1

DQ8

DQ0

A5

A6

A17

A7

OE#

V

SS

CE#

A0

A1

A2

A4

A3

A1

C1

D1

E1

F1

G1

H1

NC

NC

V

IO

4

NC

NC

NC

NC

NC

A8

C8

B2

B3

B4

B5

B6

B7

B1

B8

D8

E8

F8

G8

H8

NC

NC

NC

V

SS

V

IO

1

NC

NC

NC

64-ball Fortified BGA

Top View, Balls Facing Down

10

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

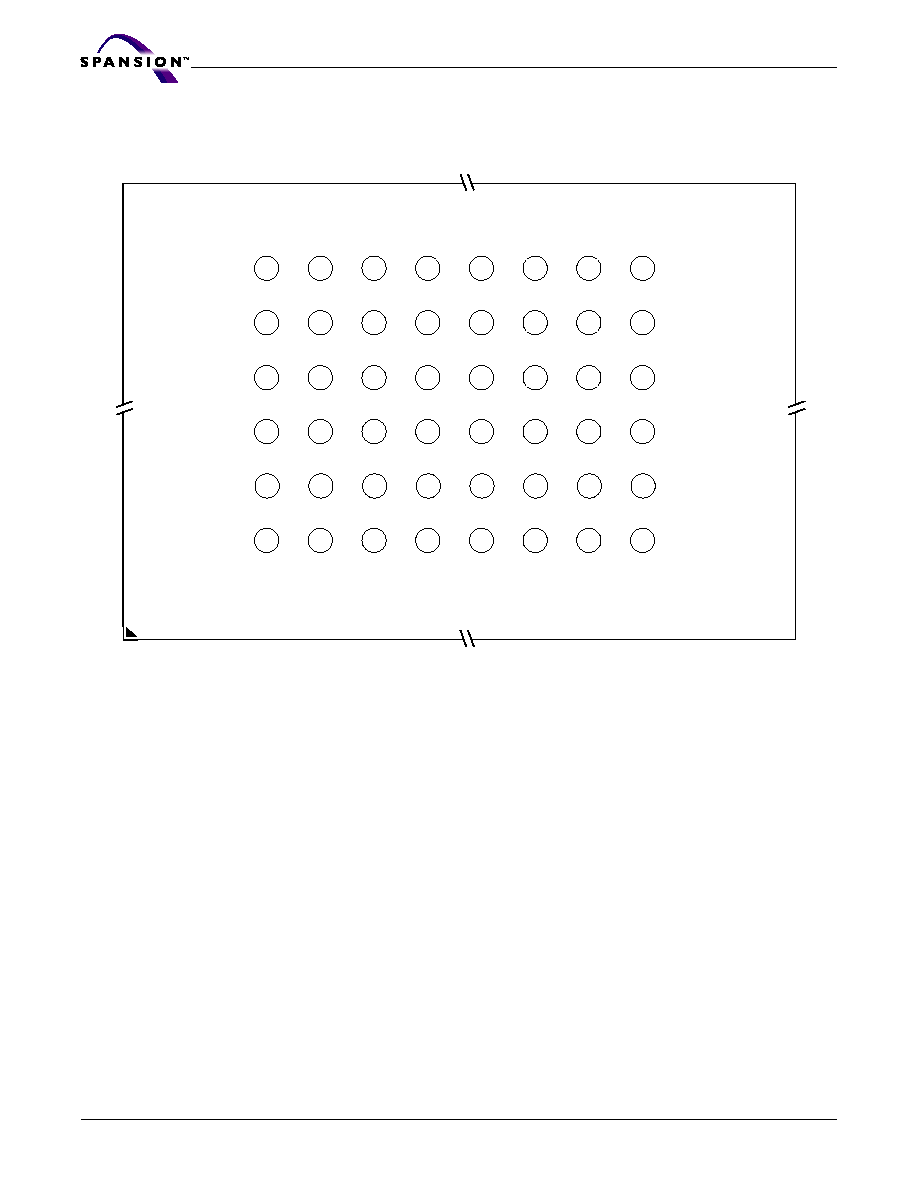

Notes:

1. Ball F6 is V

IO

on S29GL064A (models R5).

2. Ball C4 is NC on S29GL032A.

Special Package Handling Instructions

Special handling is required for Flash Memory products in molded packages

(TSOP and BGA). The package and/or data integrity may be compromised if the

package body is exposed to temperatures above 150∞C for prolonged periods of

time.

A1

B1

C1

D1

E1

F1

G1

H1

A2

B2

C2

D2

E2

F2

G2

H2

A3

B3

C3

D3

E3

F3

G3

H3

A4

B4

C4

D4

E4

F4

G4

H4

A5

B5

C5

D5

E5

F5

G5

H5

A6

B6

C6

D6

E6

F6

G6

H6

DQ15/A-1

V

SS

BYTE#

1

A16

A15

A14

A12

A13

DQ13

DQ6

DQ14

DQ7

A11

A10

A8

A9

V

CC

DQ4

DQ12

DQ5

A19

A212

RESET#

WE#

DQ11

DQ3

DQ10

DQ2

A20

A18

WP#/ACC

RY/BY#

DQ9

DQ1

DQ8

DQ0

A5

A6

A17

A7

OE#

V

SS

CE#

A0

A1

A2

A4

A3

48-ball Fine-pitch BGA

Top View, Balls Facing Down

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

11

A d v a n c e I n f o r m a t i o n

Pin Descriptions

A21≠A0

=

22 Address inputs

A20≠A0

=

21 Address inputs

DQ7≠DQ0

=

8 Data inputs/outputs

DQ14≠DQ0

=

15 Data inputs/outputs

DQ15/A-1

=

DQ15 (Data input/output, word mode), A-1 (LSB

Address input, byte mode)

CE#

=

Chip Enable input

OE#

=

Output Enable input

WE#

=

Write Enable input

WP#/ACC

=

Hardware Write Protect input/Programming

Acceleration input

ACC

=

Acceleration input

WP#

=

Hardware Write Protect input

RESET#

=

Hardware Reset Pin input

RY/BY#

=

Ready/Busy output

BYTE#

=

Selects 8-bit or 16-bit mode

V

CC

=

3.0 volt-only single power supply

(see Product Selector Guide for speed options and

voltage supply tolerances)

V

SS

=

Device Ground

NC

=

Pin Not Connected Internally

V

IO

=

Output Buffer Power

12

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

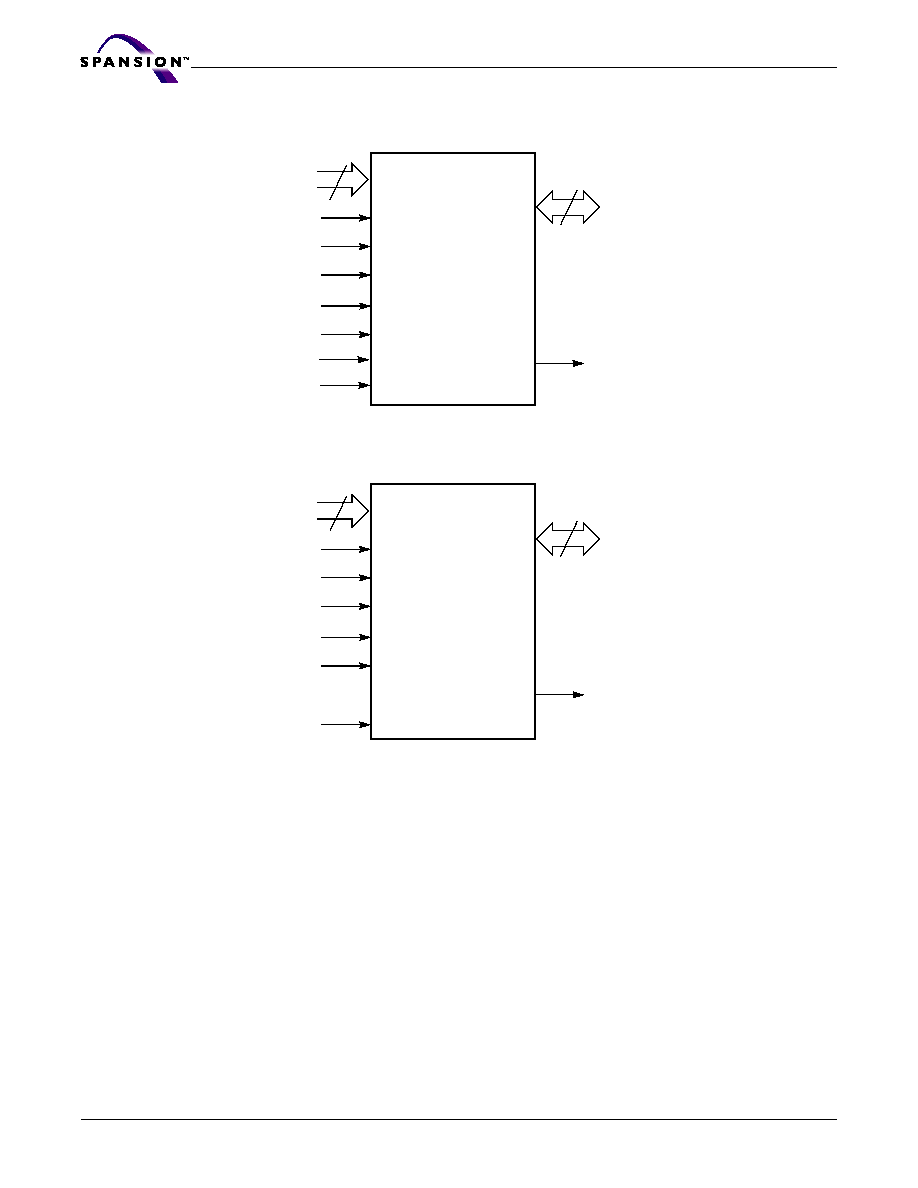

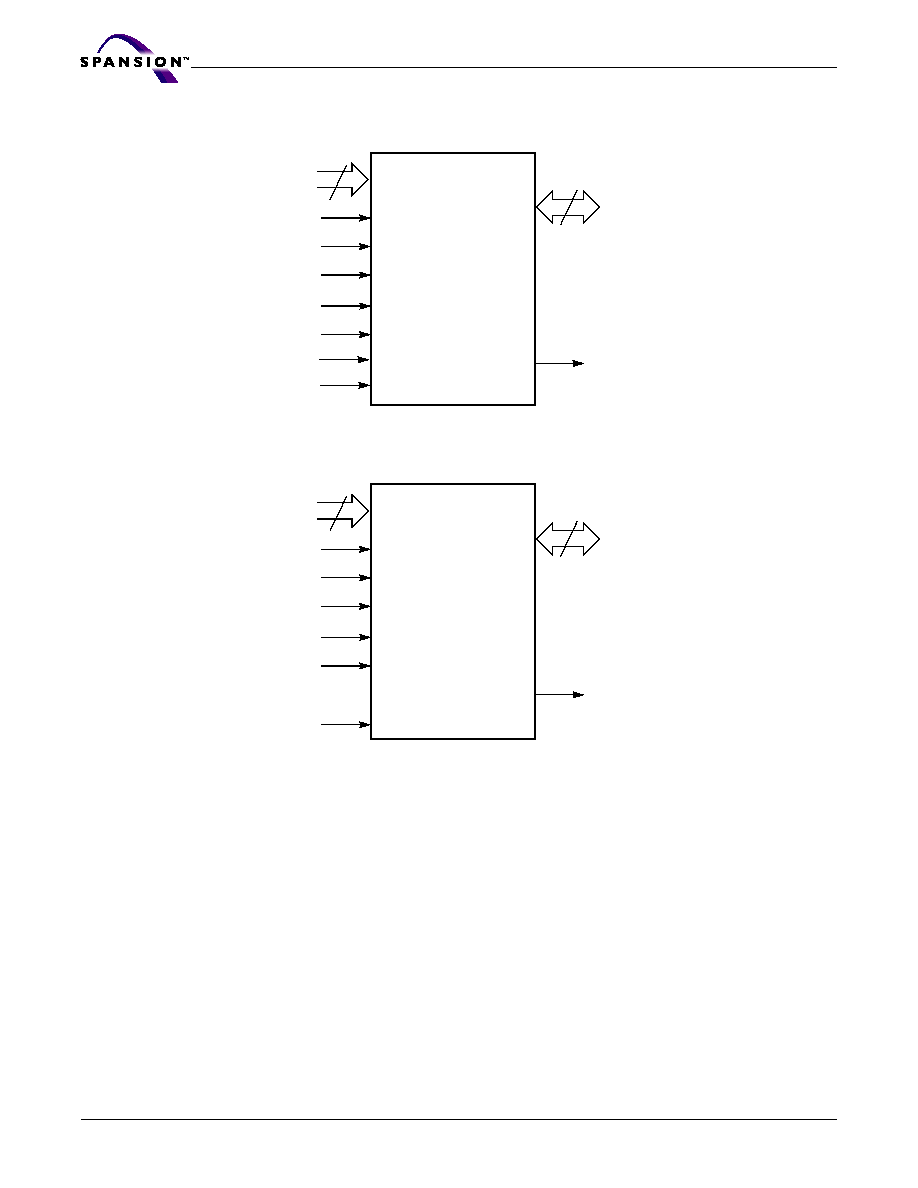

Logic Symbol-S29GL032A (Models R1, R2)

Logic Symbol-S29GL032A (Models R3, R4)

21

16 or 8

DQ15≠DQ0

(A-1)

A20≠A0

CE#

OE#

WE#

RESET#

RY/BY#

WP#/ACC

BYTE#

V

IO

21

16 or 8

DQ15≠DQ0

(A-1)

A20≠A0

CE#

OE#

WE#

RESET#

RY/BY#

WP#/ACC

BYTE#

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

13

A d v a n c e I n f o r m a t i o n

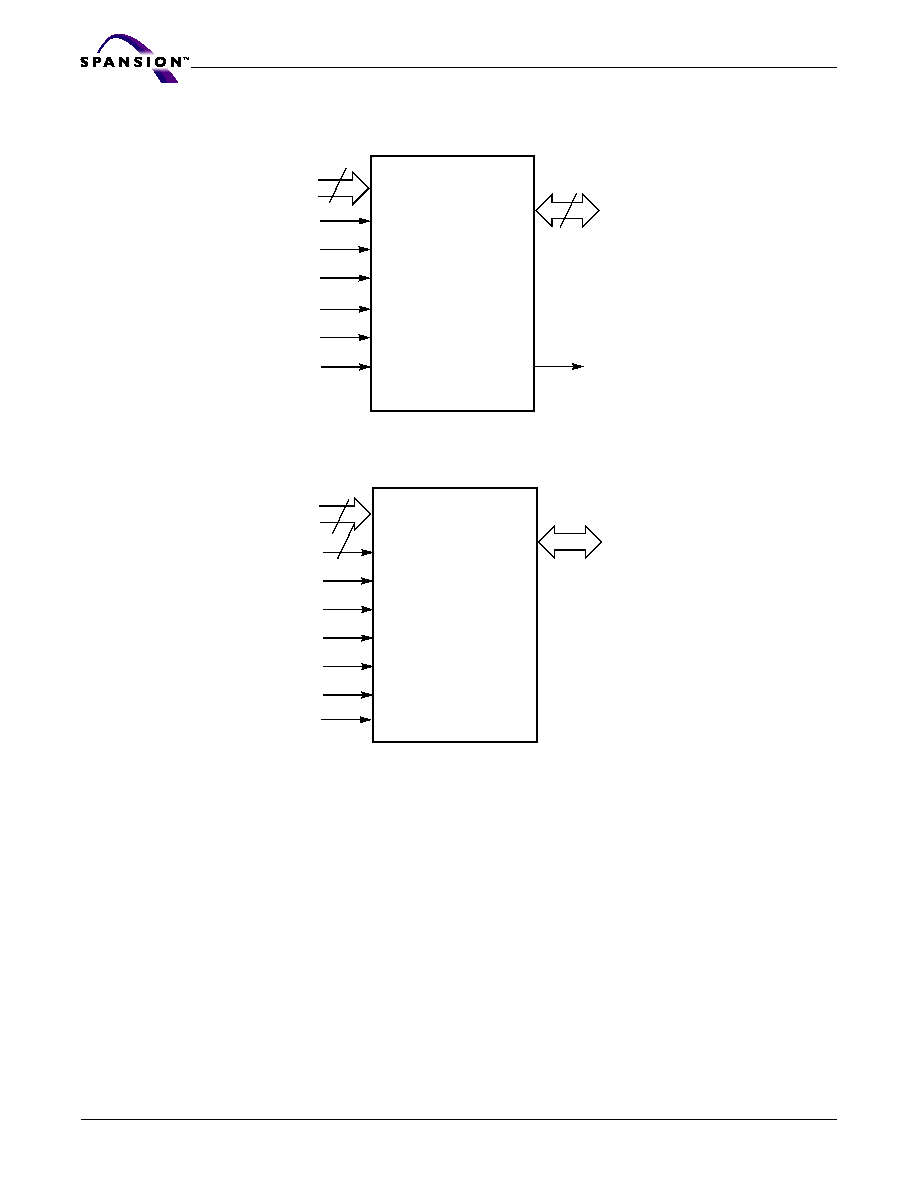

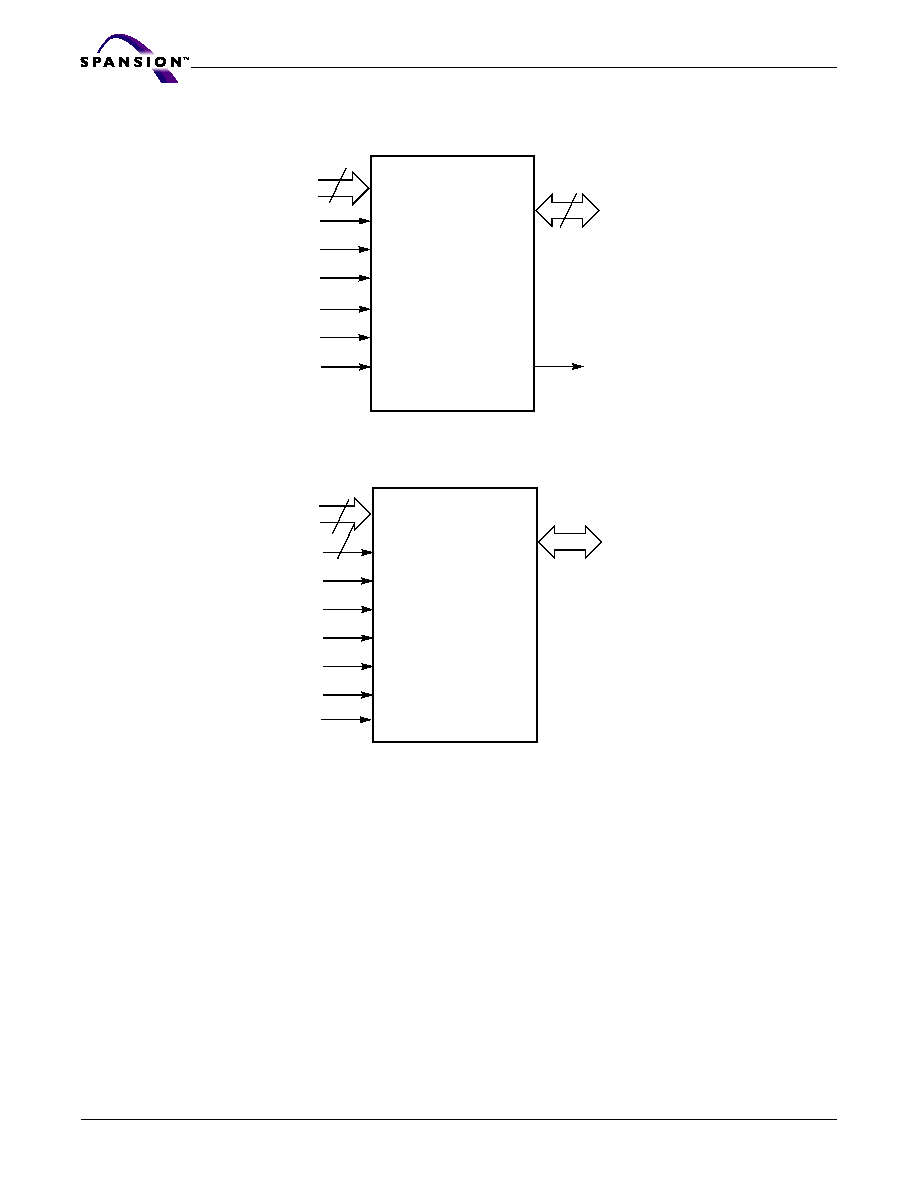

Logic Symbol-S29GL064A (Models R1, R2, R8, R9)

Logic Symbol-S29GL064A (Models R3, R4)

22

16 or 8

DQ15≠DQ0

(A-1)

A21≠A0

CE#

OE#

WE#

RESET#

RY/BY#

WP#/ACC

BYTE#

V

IO

22

16 or 8

DQ15≠DQ0

(A-1)

A21≠A0

CE#

OE#

WE#

RESET#

RY/BY#

WP#/ACC

BYTE#

14

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

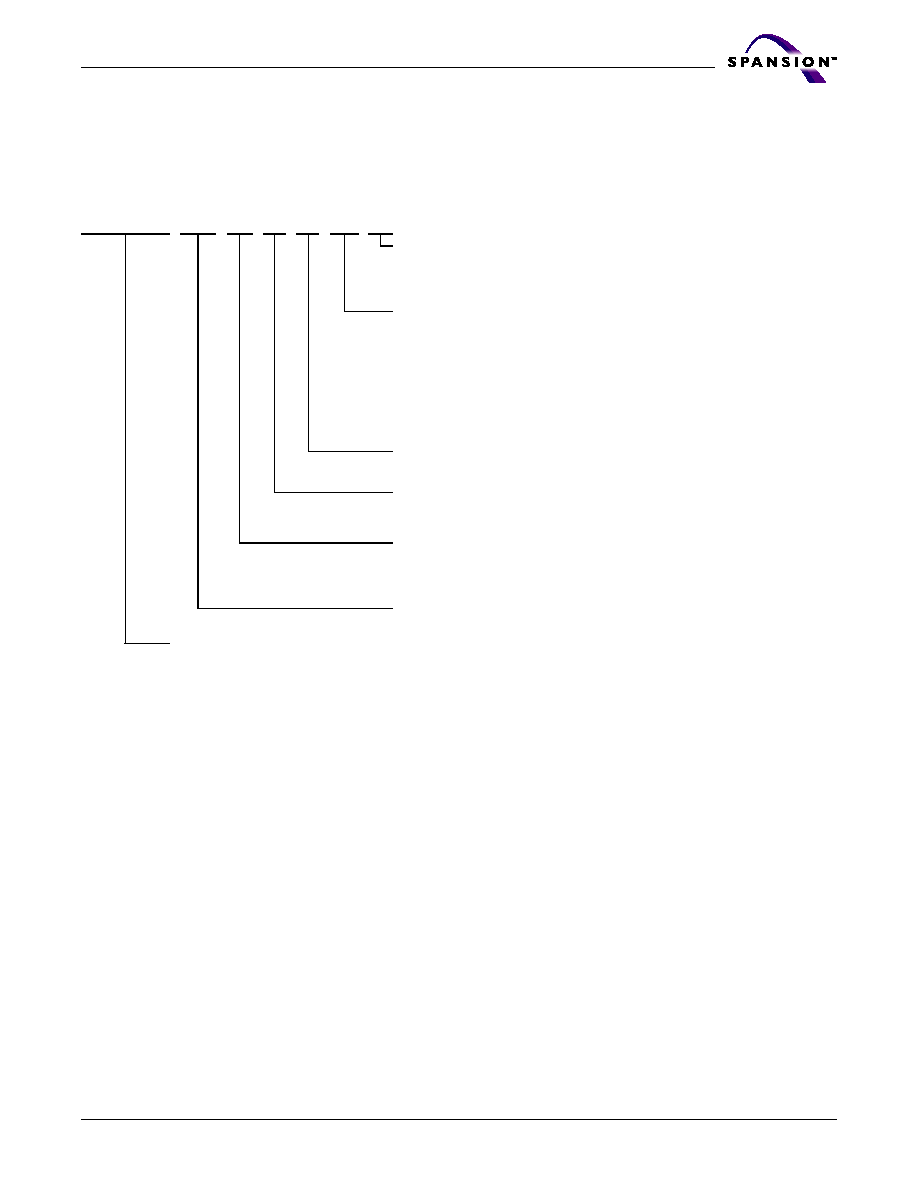

Logic Symbol-S29GL064A (Model R5)

Logic Symbol-S29GL064A (Model R6, R7)

22

16

DQ15≠DQ0

A21≠A0

CE#

OE#

WE#

RESET#

RY/BY#

ACC

V

IO

22

16

DQ15≠DQ0

A21≠A0

CE#

OE#

WE#

RESET#

ACC

WP#

V

IO

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

15

A d v a n c e I n f o r m a t i o n

Ordering Information-S29GL032A

S29GL032A Standard Products

Standard products are available in several packages and operating ranges. The

order number (Valid Combination) is formed by a combination of the following:

S29GL032A

90

T

A

I

R1

0

PACKING TYPE

0

= Tray

2

= 7" Tape and Reel

3

= 13" Tape and Reel

MODEL NUMBER

R1

= x8/x16, V

CC

=3.0-3.6V, Uniform sector device, highest address sector

protected when WP#/ACC=V

IL

R2

= x8/x16, V

CC

=3.0-3.6V, Uniform sector device, lowest address sector

protected when WP#/ACC=V

IL

R3

= x8/x16, V

CC

=3.0-3.6V, Top boot sector device, top two address sectors

protected when WP#/ACC=V

IL

R4

= x8/x16, V

CC

=3.0-3.6V, Bottom boot sector device, bottom two

address sectors protected when WP#/ACC=V

IL

TEMPERATURE RANGE

I =

Industrial

(≠40

∞

C to +85

∞

C)

PACKAGE MATERIAL SET

A

= Standard

F

= Pb-Free

PACKAGE TYPE

T

= Thin Small Outline Package (TSOP) Standard Pinout

B

= Fine-pitch Ball-Grid Array Package

F

= Fortified Ball-Grid Array Package

SPEED OPTION

See Product Selector Guide and Valid Combinations

DEVICE NUMBER/DESCRIPTION

S29GL032A

32 Megabit Page-Mode Flash Memory Manufactured using 200 nm MirrorBitTM

Process Technology, 3.0 Volt-only Read, Program, and Erase

16

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

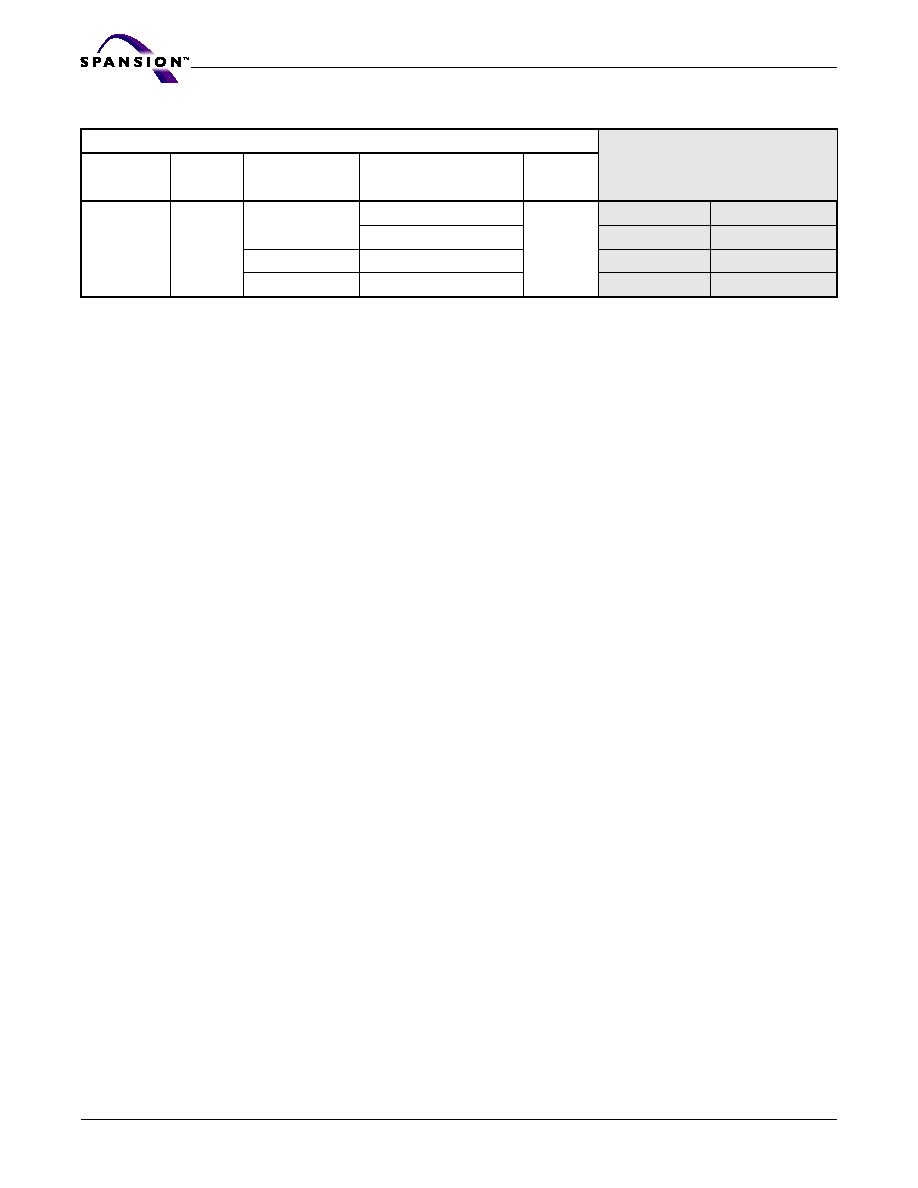

Notes:

1. Type 0 is standard. Specify others as required: TSOPs can be packed in Types 0 and 3; BGAs can

be packed in Types 0, 2, or 3.

2. TSOP package marking omits packing type designator from the ordering part number.

3. BGA package marking omits leading "S29" and packing type designator from the ordering part

number.

Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult

your local sales office to confirm availability of specific valid combinations and to check on newly

released combinations.

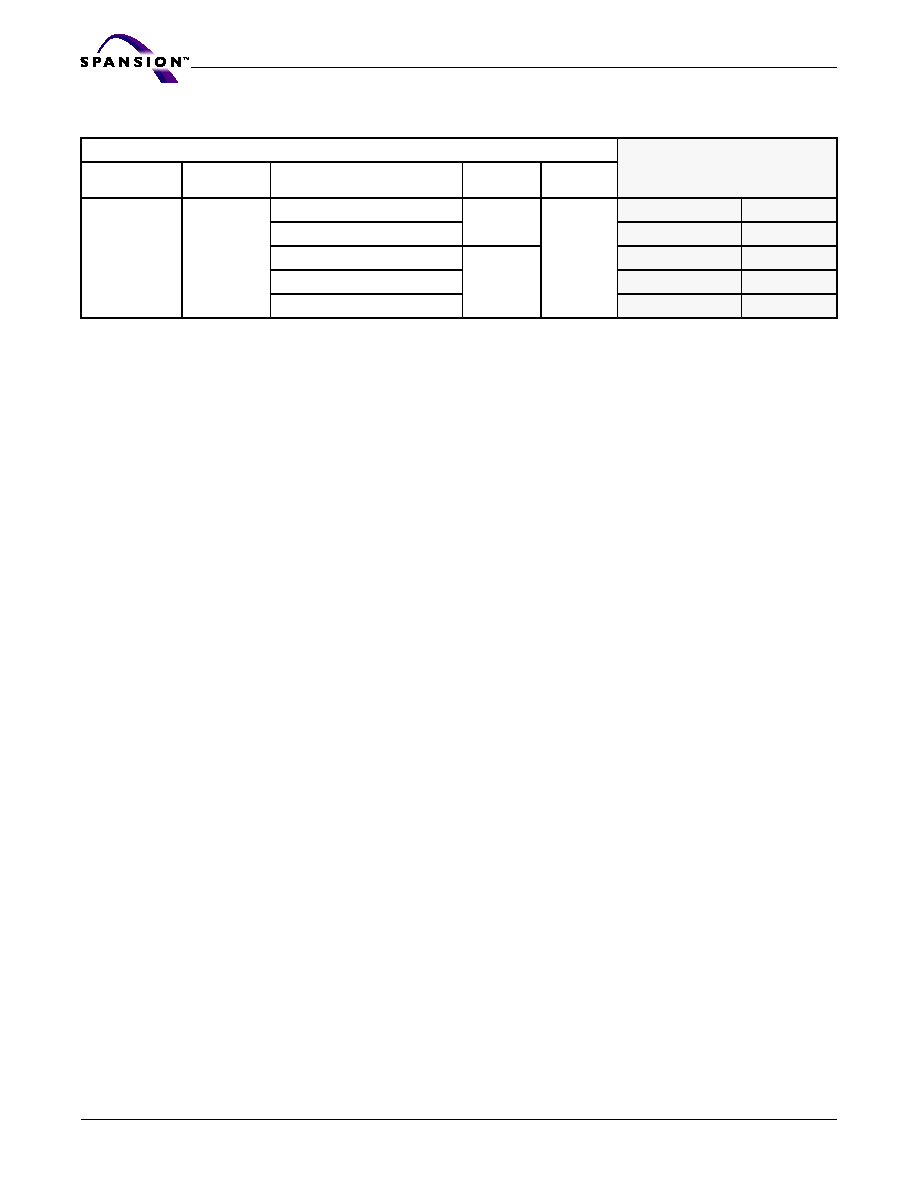

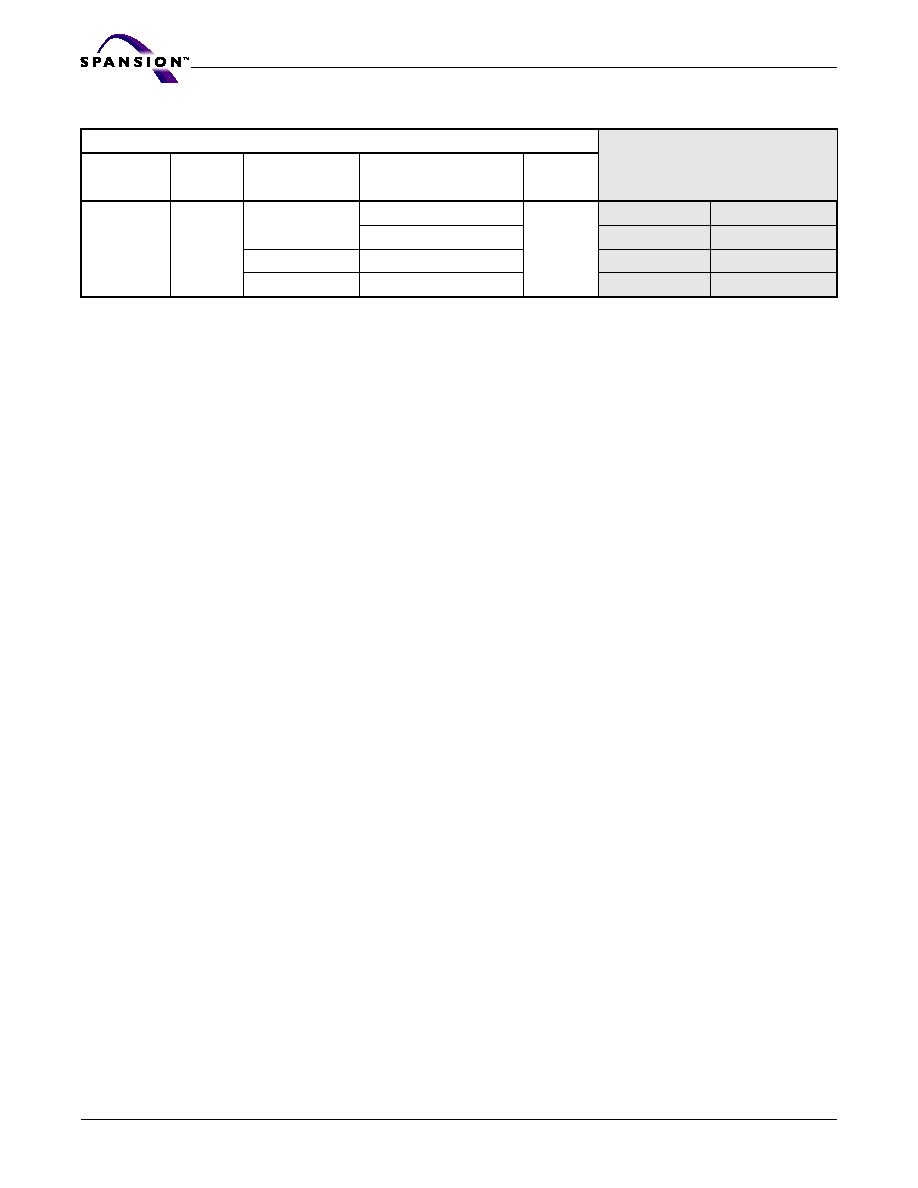

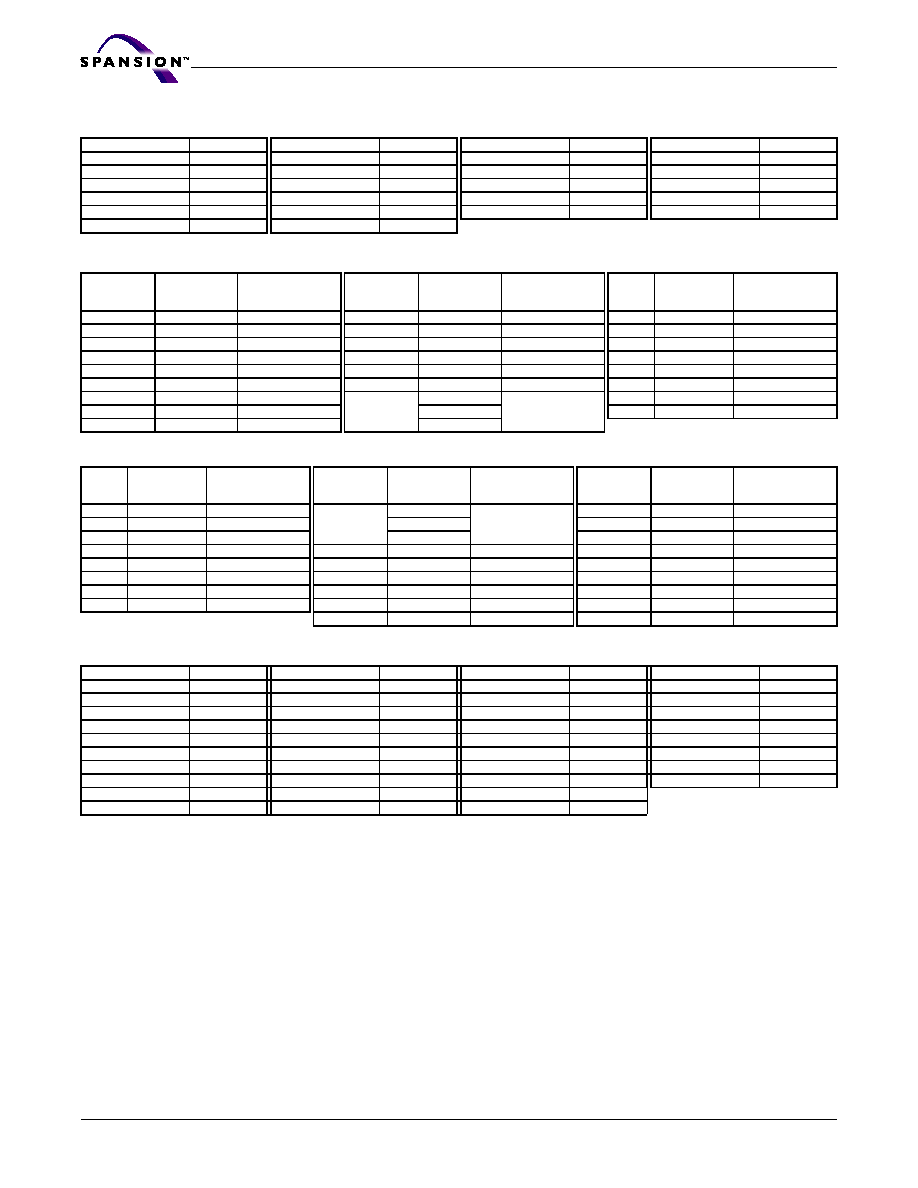

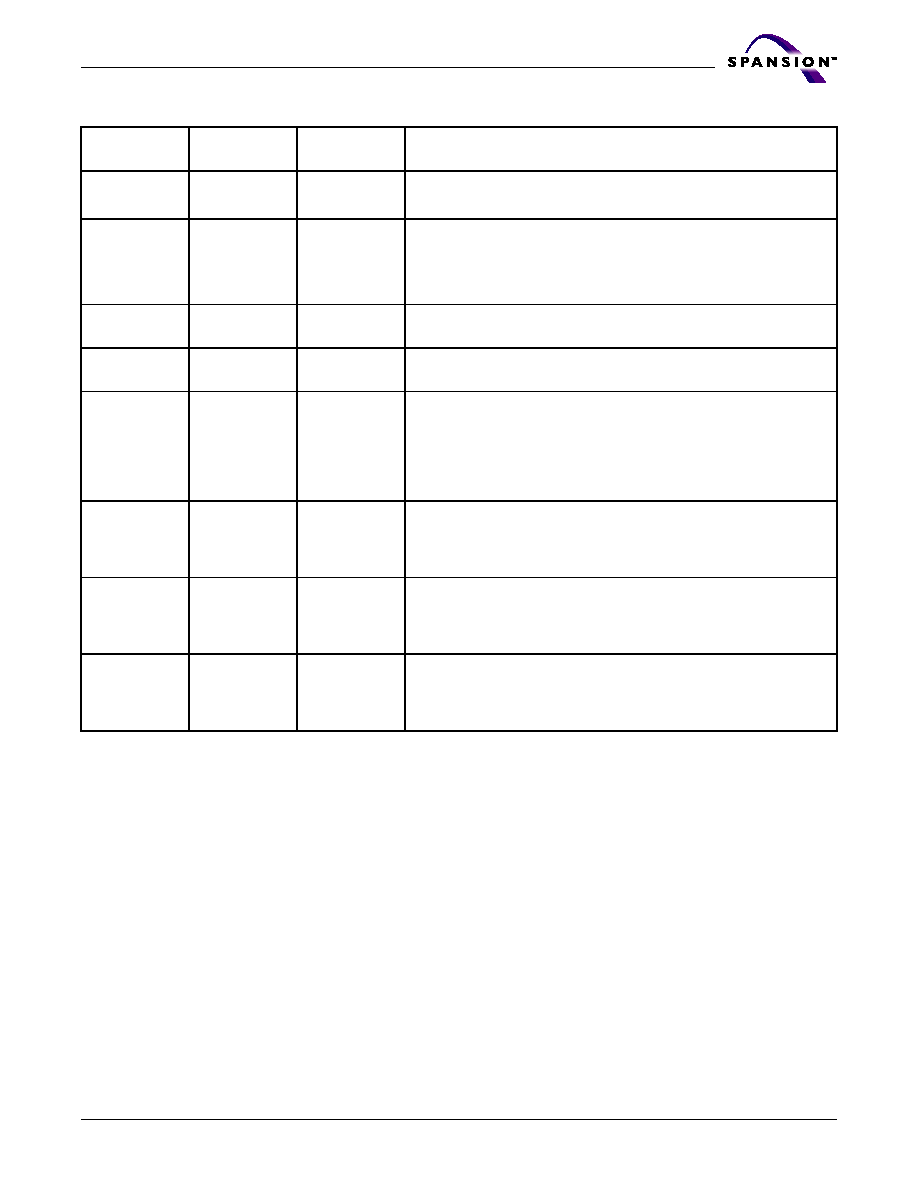

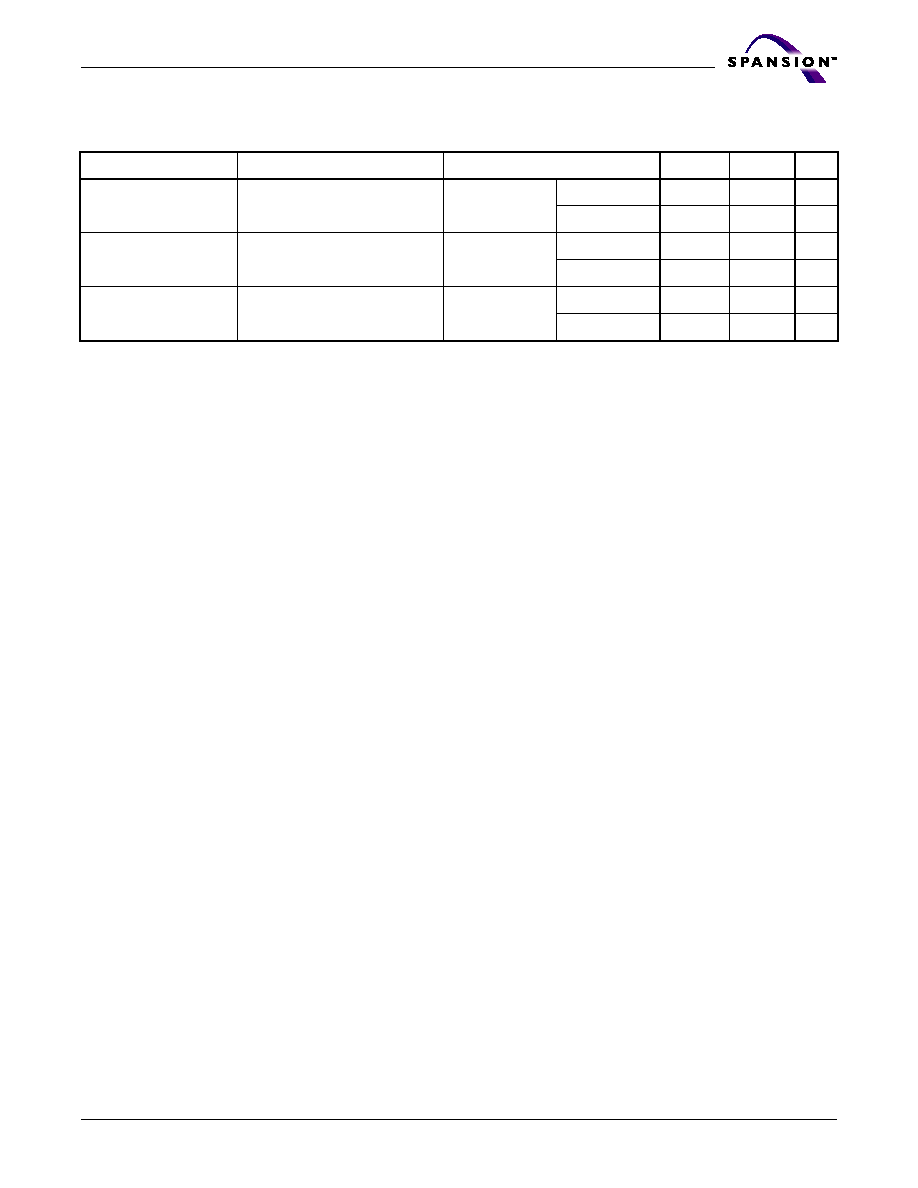

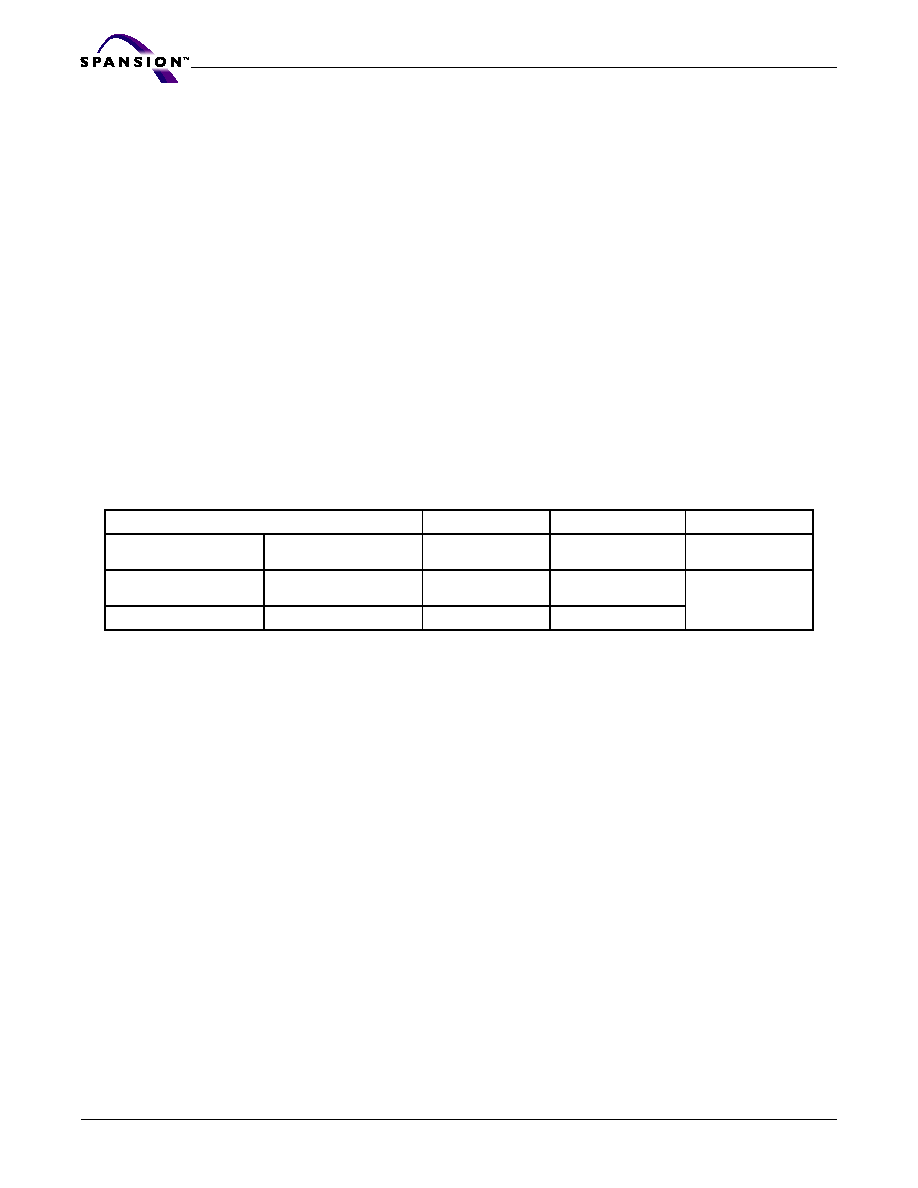

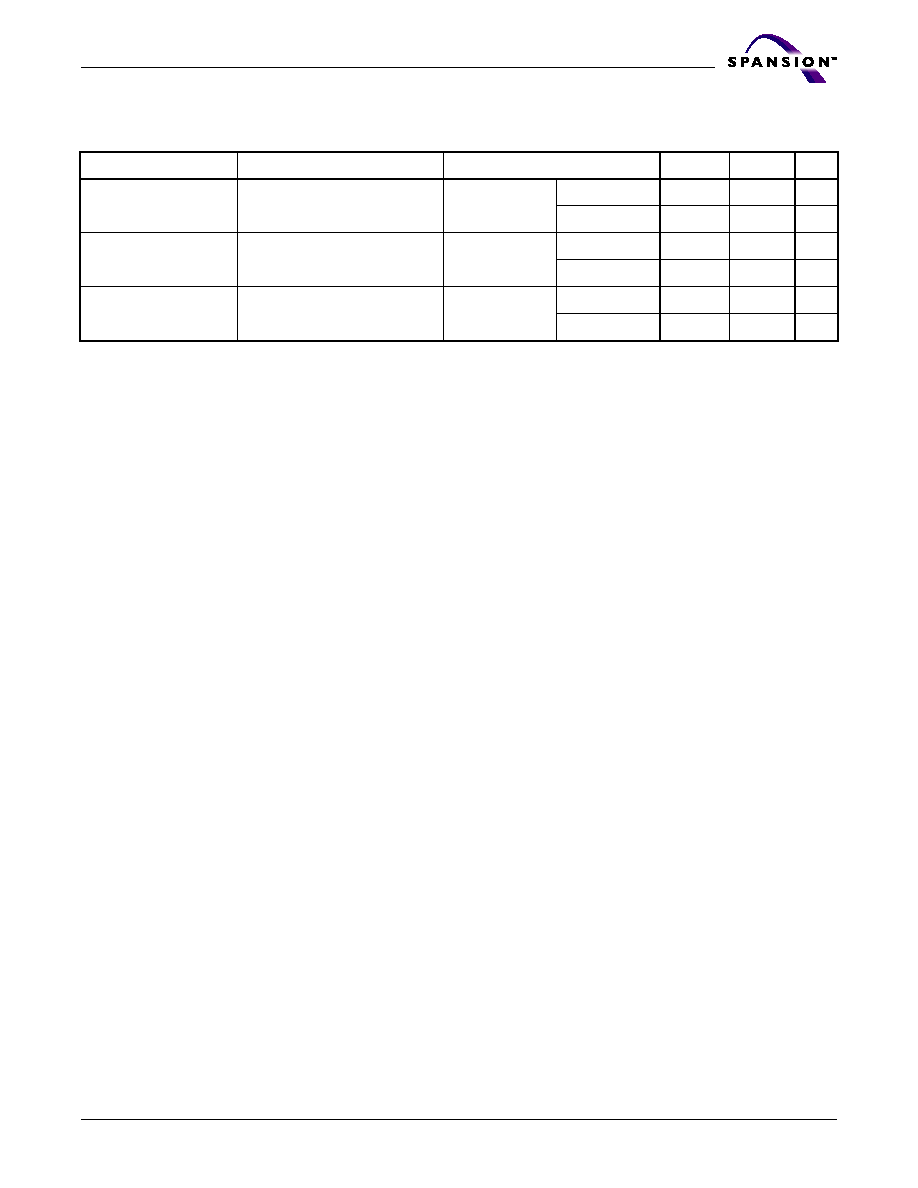

Table 1. S29GL032A Ordering Options

S29GL032A Valid Combinations

Package Description

(Notes)

Device

Number

Speed

Option

Package, Material,

& Temperature Range

Model

Number

Packing

Type

S29GL032A

90, 10, 11

TAI,TFI

R1,R2

0,2,3

(Note 1)

TS056 (2)

TSOP

FAI,FFI

LAA064 (3)

Fortified BGA

TAI,TFI

R3,R4

TS048 (2)

TSOP

BAI,BFI

FBC048 (3)

Fine-Pitch BGA

FAI,FFI

LAA064 (3)

Fortified BGA

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

17

A d v a n c e I n f o r m a t i o n

Ordering Information-S29GL064A

S29GL064A Standard Products

Standard products are available in several packages and operating ranges. The

order number (Valid Combination) is formed by a combination of the following:

S29GL064A

90

T

A

I

R1

2

PACKING TYPE

0 =

Tray

2

= 7" Tape and Reel

3

= 13" Tape and Reel

MODEL NUMBER

R1

= x8/x16, V

CC

=3.0-3.6V, Uniform sector device, highest address

sector protected when WP#/ACC=V

IL

R2

= x8/x16, V

CC

=3.0-3.6V, Uniform sector device, lowest address sector

protected when WP#/ACC=V

IL

R3

= x8/x16, V

CC

=3.0-3.6V, Top boot sector device, top two address

sectors protected when WP#/ACC=V

IL

R4

= x8/x16, V

CC

=3.0-3.6V, Bottom boot sector device, bottom two

address sectors protected when WP#/ACC=V

IL

R5

= x16, V

CC

=3.0-3.6V, Uniform sector device

R6

= x16, V

CC

=3.0-3.6V, Uniform sector device, highest address sector

protected when WP#=V

IL

R7

= x16, V

CC

=3.0-3.6V, Uniform sector device, lowest address sector

protected when WP#=V

IL

R8

= x8/x16, V

CC

=3.0-3.6V, Uniform sector device, highest address

sector protected when WP#=V

IL,

TSO48 only

R9

= x8/x16, V

CC

=3.0-3.6V, Uniform sector device, lowest address sector

protected when WP#=V

IL,

TSO48 only

TEMPERATURE RANGE

I =

Industrial

(≠40

∞

C to +85

∞

C)

PACKAGE MATERIAL SET

A

= Standard

F

= Pb-Free

PACKAGE TYPE

T

= Thin Small Outline Package (TSOP) Standard Pinout

B

= Fine-pitch Ball-Grid Array Package

F

= Fortified Ball-Grid Array Package

SPEED OPTION

See Product Selector Guide and Valid Combinations

DEVICE NUMBER/DESCRIPTION

S29GL064A

64 Megabit Page-Mode Flash Memory Manufactured using 200 nm MirrorBit

TM

Process Technology, 3.0 Volt-only Read, Program, and Erase

18

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

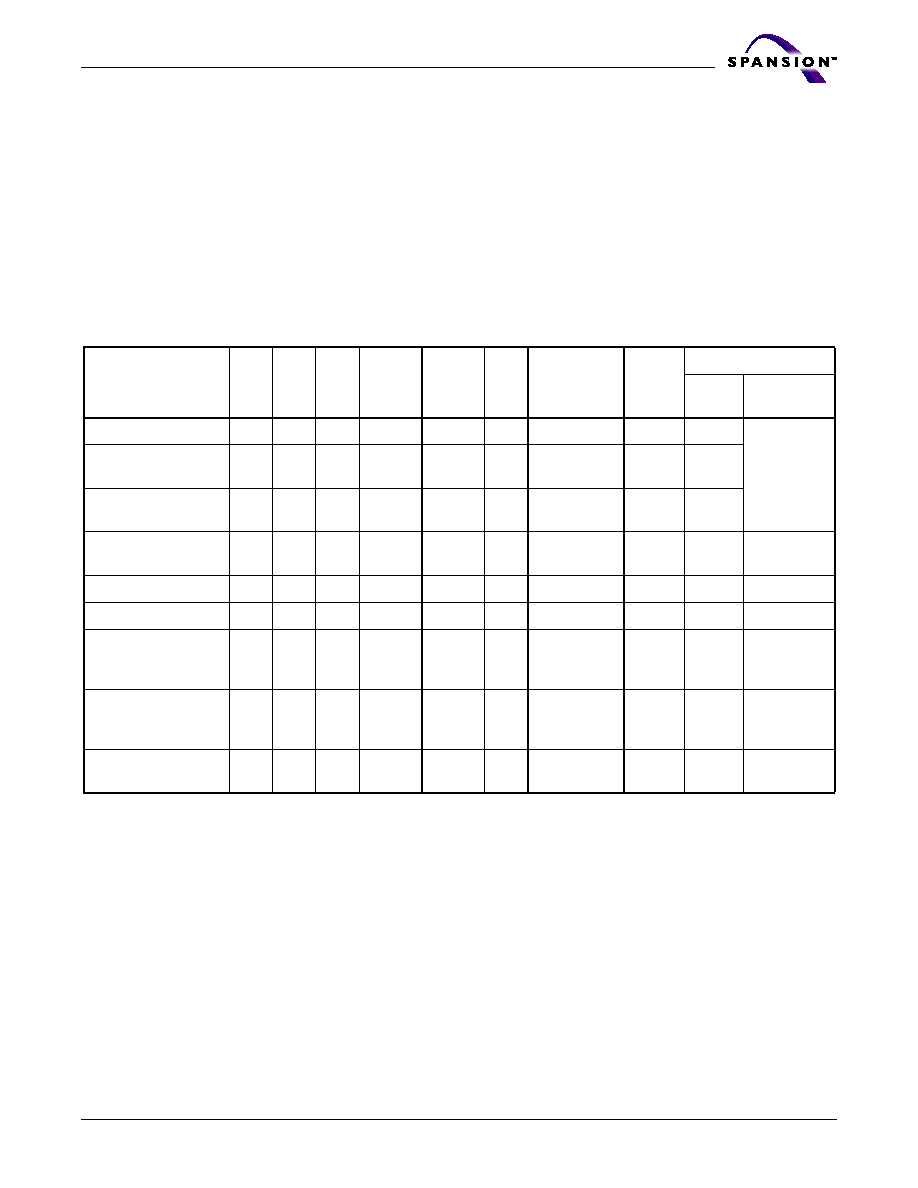

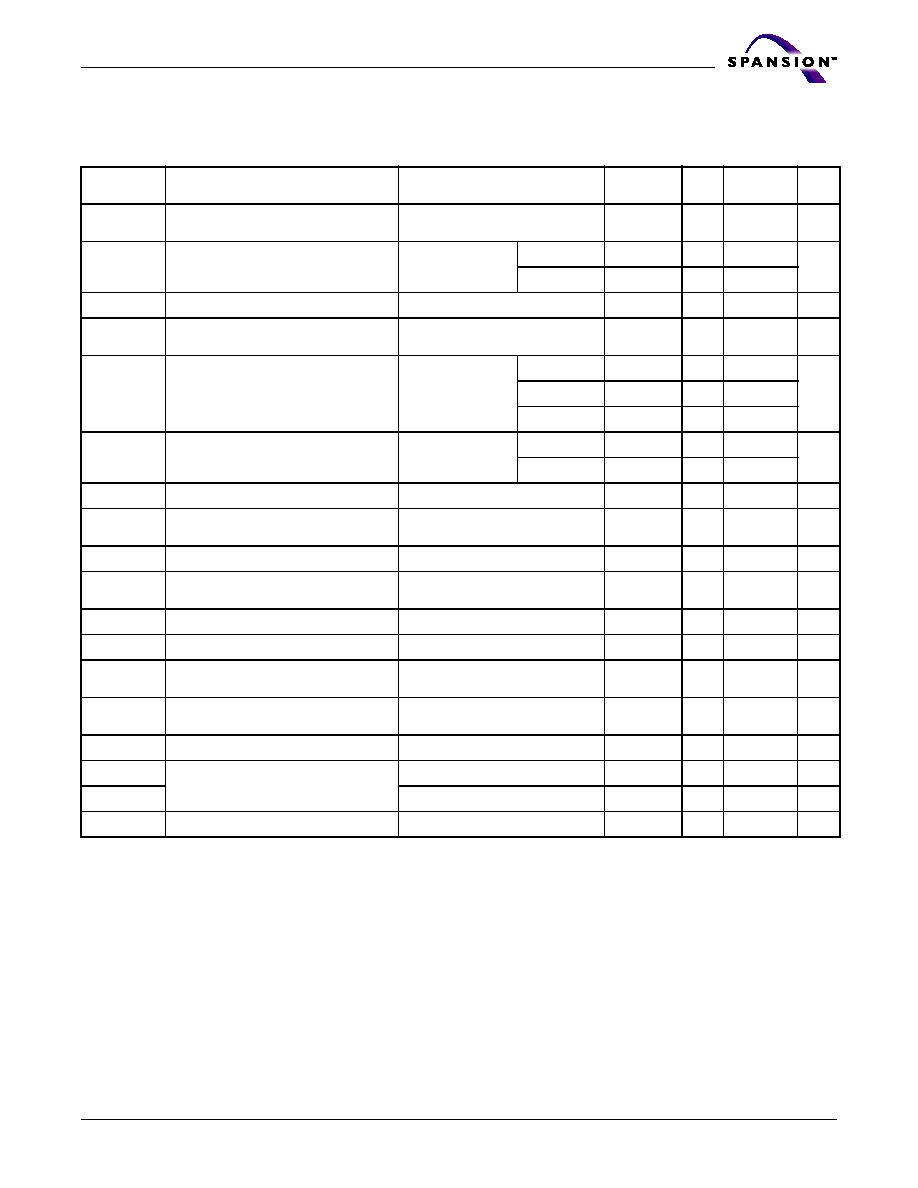

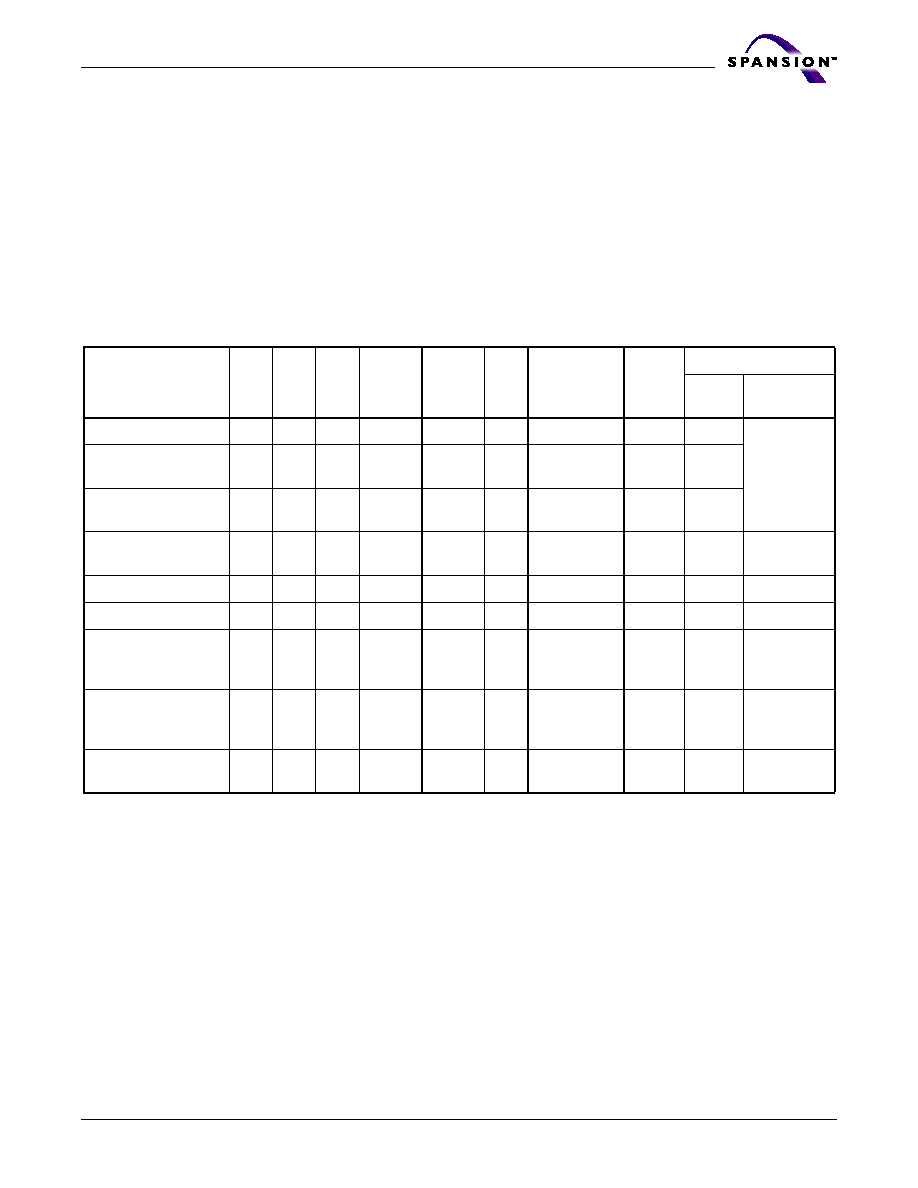

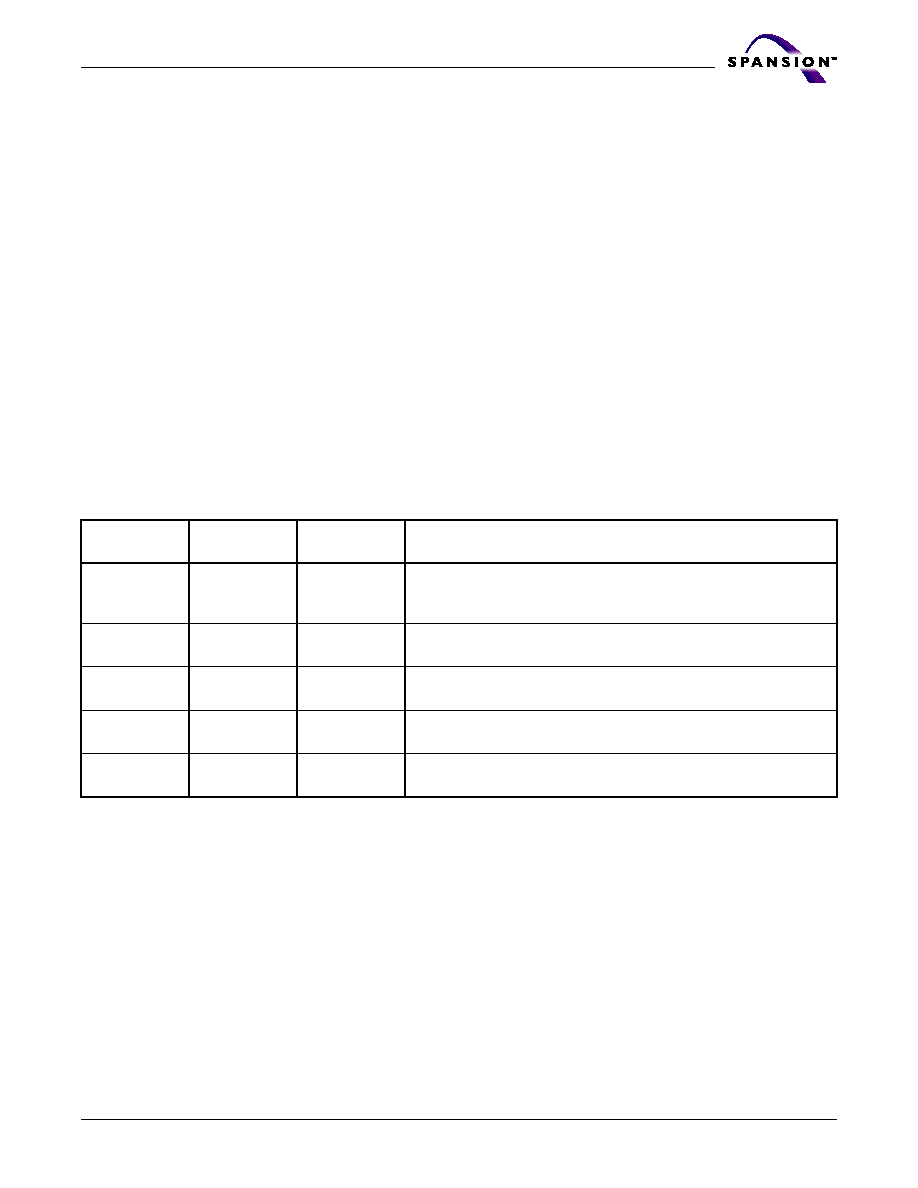

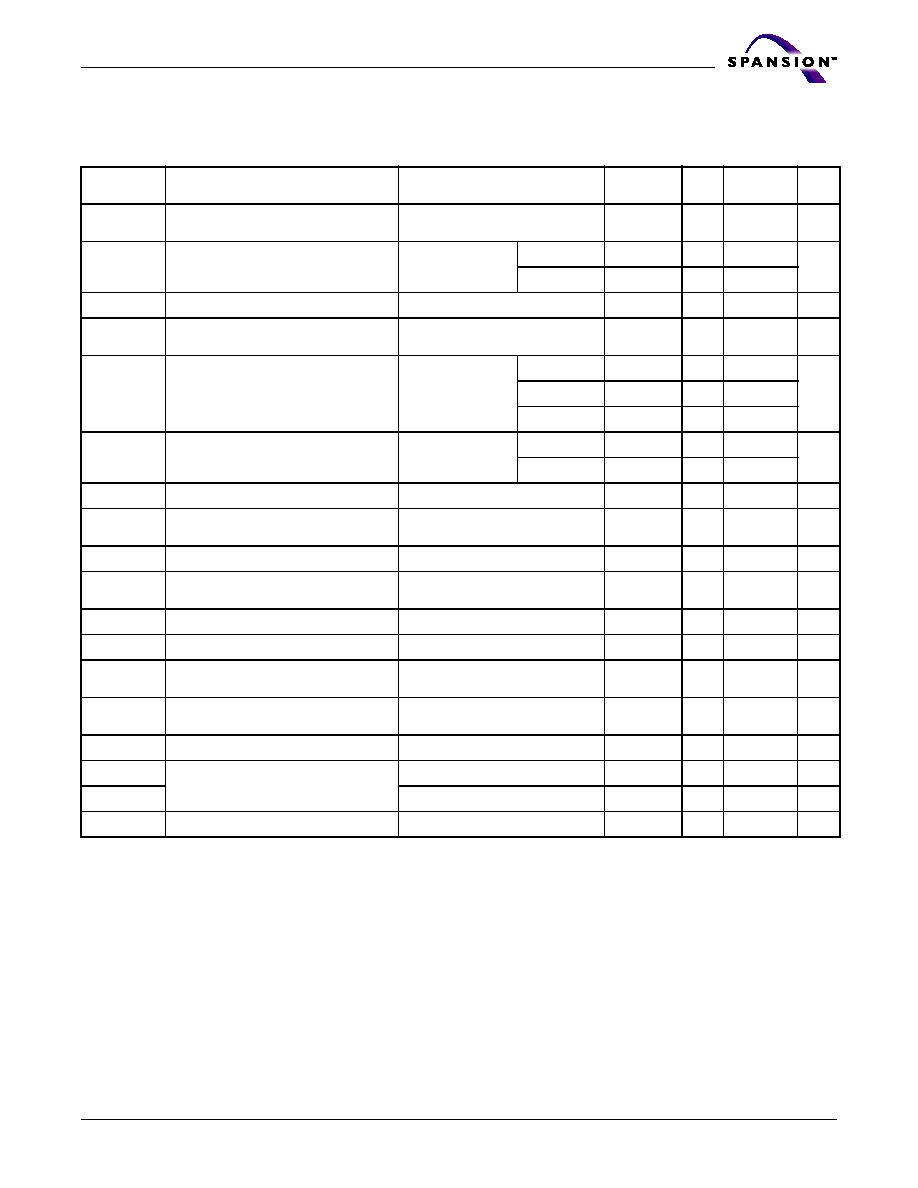

Table 2. S29GL064A Valid Combinations

Notes:

1. Type 0 is standard. Specify others as required: TSOPs can be packed in Types 0 and 3; BGAs can be packed in Types

0, 2, or 3.

2. TSOP package marking omits packing type designator from ordering part number.

3. BGA package marking omits leading "S29" and packing type designator from ordering part number.

Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device.

Consult your local sales office to confirm availability of specific valid combinations and to

check on newly released combinations.

S29GL064A Valid Combinations

Package Description

Device

Number

Speed

Option

Package, Material

& Temperature

Range

Model Number

Packing

Type

S29GL064A

90, 10, 11

TAI, TFI

R3, R4, R6, R7, R8, R9

0, 2, 3

(Note 1)

TS048 (note 2)

TSOP

R1, R2

TS056 (note 2)

TSOP

BAI, BFI

R3, R4, R5

VBN048 (note 3)

Fine-pitch BGA

FAI, FFI

R1, R2, R3, R4, R5

LAA064 (note 3)

Fortified BGA

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

19

A d v a n c e I n f o r m a t i o n

Device Bus Operations

This section describes the requirements and use of the device bus operations,

which are initiated through the internal command register. The command register

itself does not occupy any addressable memory location. The register is a latch

used to store the commands, along with the address and data information

needed to execute the command. The contents of the register serve as inputs to

the internal state machine. The state machine outputs dictate the function of the

device.

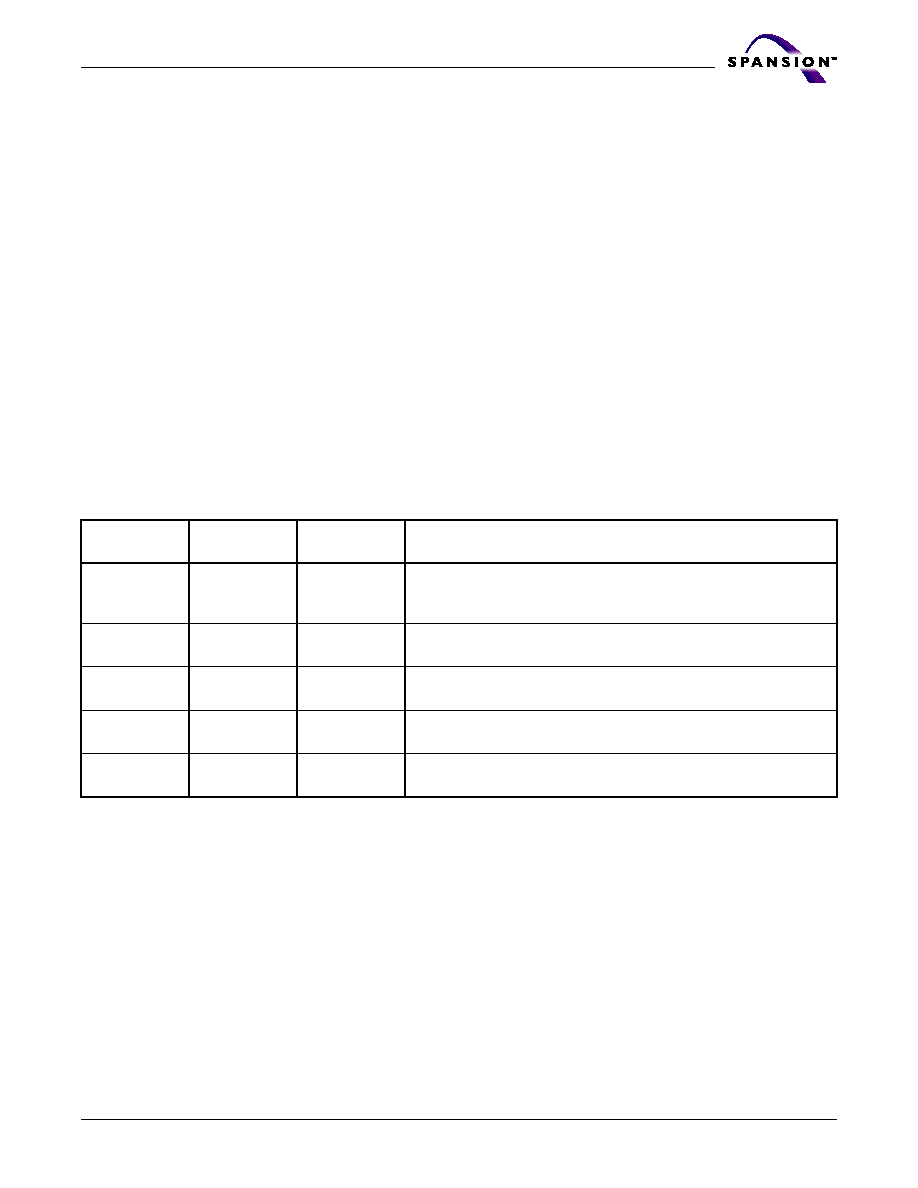

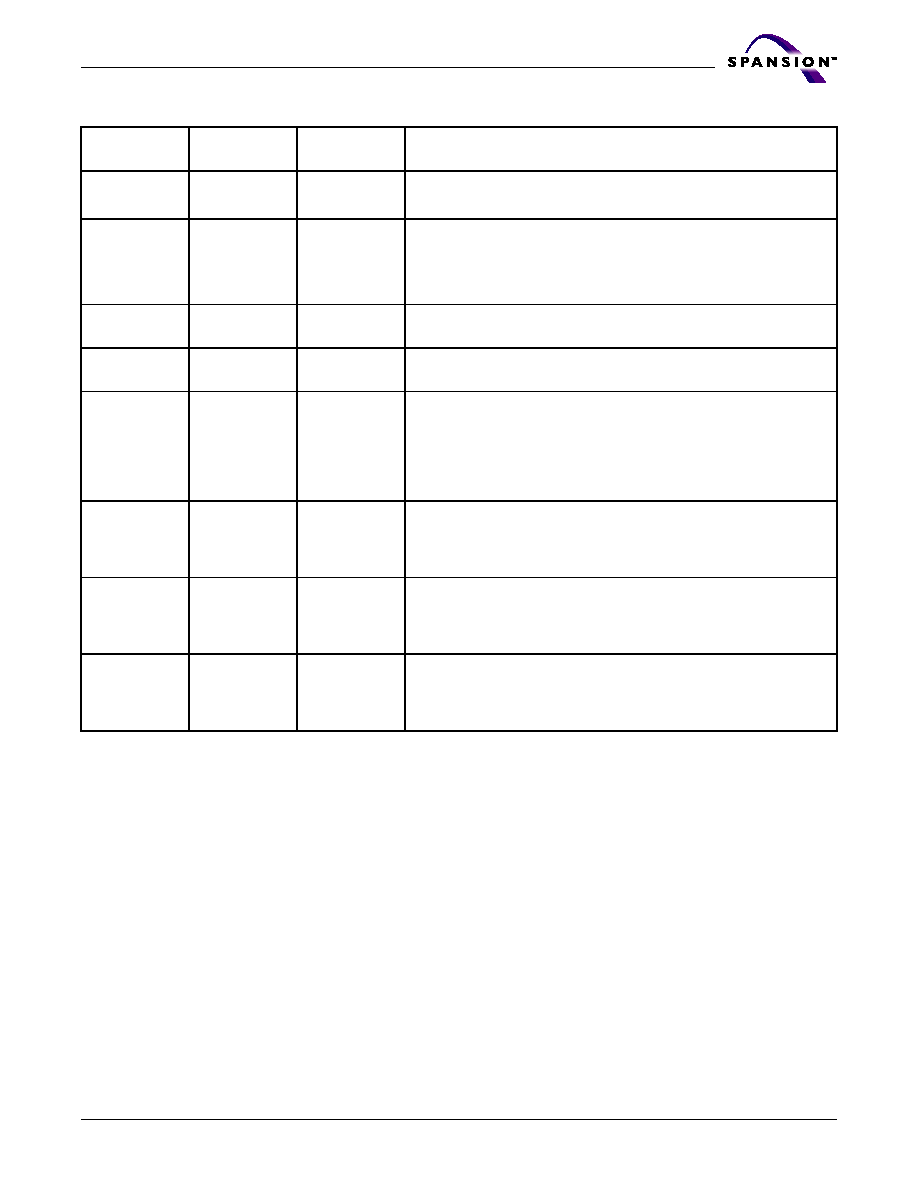

Table 3

lists the device bus operations, the inputs and control levels they

require, and the resulting output. The following subsections describe each of

these operations in further detail.

Table 3. Device Bus Operations

Legend: L = Logic Low = V

IL

, H = Logic High = V

IH

, V

ID

= 11.5≠12.5 V, V

HH

= 11.5≠12.5 V, X = Don't Care, SA = Sector

Address, A

IN

= Address In, D

IN

= Data In, D

OUT

= Data Out

Notes:

1. Addresses are Amax:A0 in word mode; Amax:A-1 in byte mode. Sector addresses are Amax:A15 in both modes.

2. The sector protect and sector unprotect functions may also be implemented via programming equipment. See the

"Sector Group Protection and Unprotection" section.

3. If WP# = V

IL

, the first or last sector remains protected (for uniform sector devices), and the two outer boot sectors

are protected (for boot sector devices). If WP# = V

IH

, the first or last sector, or the two outer boot sectors will be

protected or unprotected as determined by the method described in "Sector Group Protection and Unprotection".

All sectors are unprotected when shipped from the factory (The Secured Silicon Sector may be factory protected

depending on version ordered.)

4. D

IN

or D

OUT

as required by command sequence, data polling, or sector protect algorithm (see

Figure 7

).

Operation

CE# OE# WE# RESET#

WP#

ACC

Addresses

(Note 1)

DQ0≠

DQ7

DQ8≠DQ15

BYTE#

= V

IH

BYTE#

= V

IL

Read

L

L

H

H

X

X

A

IN

D

OUT

D

OUT

DQ8≠DQ14

= High-Z,

DQ15 = A-1

Write (Program/Erase)

L

H

L

H

(Note 3)

X

A

IN

(Note 4)

(Note

4)

Accelerated Program

L

H

L

H

(Note 3) V

HH

A

IN

(Note 4)

(Note

4)

Standby

V

CC

±

0.3 V

X

X

V

CC

±

0.3 V

X

H

X

High-Z

High-Z

High-Z

Output Disable

L

H

H

H

X

X

X

High-Z

High-Z

High-Z

Reset

X

X

X

L

X

X

X

High-Z

High-Z

High-Z

Sector Group Protect

(Note 2)

L

H

L

V

ID

H

X

SA, A6 =L,

A3=L, A2=L,

A1=H, A0=L

(Note 4)

X

X

Sector Group

Unprotect

(Note 2)

L

H

L

V

ID

H

X

SA, A6=H,

A3=L, A2=L,

A1=H, A0=L

(Note 4)

X

X

Temporary Sector

Group Unprotect

X

X

X

V

ID

H

X

A

IN

(Note 4)

(Note

4)

High-Z

20

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

Word/Byte Configuration

The BYTE# pin controls whether the device data I/O pins operate in the byte or

word configuration. If the BYTE# pin is set at logic `1', the device is in word con-

figuration, DQ0≠DQ15 are active and controlled by CE# and OE#.

If the BYTE# pin is set at logic `0', the device is in byte configuration, and only

data I/O pins DQ0≠DQ7 are active and controlled by CE# and OE#. The data I/

O pins DQ8≠DQ14 are tri-stated, and the DQ15 pin is used as an input for the

LSB (A-1) address function.

Requirements for Reading Array Data

To read array data from the outputs, the system must drive the CE# and OE#

pins to V

IL

. CE# is the power control and selects the device. OE# is the output

control and gates array data to the output pins. WE# should remain at V

IH

.

The internal state machine is set for reading array data upon device power-up,

or after a hardware reset. This ensures that no spurious alteration of the memory

content occurs during the power transition. No command is necessary in this

mode to obtain array data. Standard microprocessor read cycles that assert valid

addresses on the device address inputs produce valid data on the device data

outputs. The device remains enabled for read access until the command register

contents are altered.

See "Reading Array Data" for more information. Refer to the AC Read-Only Op-

erations table for timing specifications and the timing diagram. Refer to the DC

Characteristics table for the active current specification on reading array data.

Page Mode Read

The device is capable of fast page mode read and is compatible with the page

mode Mask ROM read operation. This mode provides faster read access speed for

random locations within a page. The page size of the device is 4 words/8 bytes.

The appropriate page is selected by the higher address bits A(max)≠A2. Address

bits A1≠A0 in word mode (A1≠A-1 in byte mode) determine the specific word

within a page. This is an asynchronous operation; the microprocessor supplies

the specific word location.

The random or initial page access is equal to t

ACC

or t

CE

and subsequent page

read accesses (as long as the locations specified by the microprocessor falls

within that page) is equivalent to t

PACC

. When CE# is deasserted and reasserted

for a subsequent access, the access time is t

ACC

or t

CE

. Fast page mode accesses

are obtained by keeping the "read-page addresses" constant and changing the

"intra-read page" addresses.

Writing Commands/Command Sequences

To write a command or command sequence (which includes programming data

to the device and erasing sectors of memory), the system must drive WE# and

CE# to V

IL

, and OE# to V

IH

.

The device features an Unlock Bypass mode to facilitate faster programming.

Once the device enters the Unlock Bypass mode, only two write cycles are re-

quired to program a word, instead of four. The "Word Program Command

Sequence" section has details on programming data to the device using both

standard and Unlock Bypass command sequences.

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

21

A d v a n c e I n f o r m a t i o n

An erase operation can erase one sector, multiple sectors, or the entire device.

Table 4

-

Table 20

indicates the address space that each sector occupies.

Refer to the DC Characteristics table for the active current specification for the

write mode. The AC Characteristics section contains timing specification tables

and timing diagrams for write operations.

Write Buffer

Write Buffer Programming allows the system write to a maximum of 16 words/32

bytes in one programming operation. This results in faster effective programming

time than the standard programming algorithms. See "Write Buffer" for more

information.

Accelerated Program Operation

The device offers accelerated program operations through the ACC function. This

is one of two functions provided by the WP#/ACC or ACC pin, depending on model

number. This function is primarily intended to allow faster manufacturing

throughput at the factory.

If the system asserts V

HH

on this pin, the device automatically enters the afore-

mentioned Unlock Bypass mode, temporarily unprotects any protected sector

groups, and uses the higher voltage on the pin to reduce the time required for

program operations. The system would use a two-cycle program command se-

quence as required by the Unlock Bypass mode. Removing V

HH

from the WP#/

ACC or ACC pin, depending on model number, returns the device to normal op-

eration. Note that the WP#/ACC or ACC pin must not be at V

HH

for operations

other than accelerated programming, or device damage may result. WP# has an

internal pullup; when unconnected, WP# is at V

IH

.

Autoselect Functions

If the system writes the autoselect command sequence, the device enters the au-

toselect mode. The system can then read autoselect codes from the internal

register (which is separate from the memory array) on DQ7≠DQ0. Standard read

cycle timings apply in this mode. Refer to the

"Autoselect Mode" section on page

30

and

"Autoselect Command Sequence" section on page 44

sections for more

information.

Standby Mode

When the system is not reading or writing to the device, it can place the device

in the standby mode. In this mode, current consumption is greatly reduced, and

the outputs are placed in the high impedance state, independent of the OE#

input.

The device enters the CMOS standby mode when the CE# and RESET# pins are

both held at V

IO

± 0.3 V. (Note that this is a more restricted voltage range than

V

IH

.) If CE# and RESET# are held at V

IH

, but not within V

IO

± 0.3 V, the device

will be in the standby mode, but the standby current will be greater. The device

requires standard access time (t

CE

) for read access when the device is in either

of these standby modes, before it is ready to read data.

If the device is deselected during erasure or programming, the device draws ac-

tive current until the operation is completed.

Refer to the

"DC Characteristics" section on page 65

for the standby current

specification.

22

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

Automatic Sleep Mode

The automatic sleep mode minimizes Flash device energy consumption. The de-

vice automatically enables this mode when addresses remain stable for t

ACC

+

30 ns. The automatic sleep mode is independent of the CE#, WE#, and OE# con-

trol signals. Standard address access timings provide new data when addresses

are changed. While in sleep mode, output data is latched and always available to

the system. Refer to the

"DC Characteristics" section on page 65

for the

automatic sleep mode current specification.

RESET#: Hardware Reset Pin

The RESET# pin provides a hardware method of resetting the device to reading

array data. When the RESET# pin is driven low for at least a period of t

RP

, the

device immediately terminates any operation in progress, tristates all output

pins, and ignores all read/write commands for the duration of the RESET# pulse.

The device also resets the internal state machine to reading array data. The op-

eration that was interrupted should be reinitiated once the device is ready to

accept another command sequence, to ensure data integrity.

Current is reduced for the duration of the RESET# pulse. When RESET# is held

at V

SS

±0.3 V, the device draws CMOS standby current (I

CC5

). If RESET# is held

at V

IL

but not within V

SS

±0.3 V, the standby current will be greater.

The RESET# pin may be tied to the system reset circuitry. A system reset would

thus also reset the Flash memory, enabling the system to read the boot-up firm-

ware from the Flash memory.

Refer to the AC Characteristics tables for RESET# parameters and to

Figure 15

for the timing diagram.

Output Disable Mode

When the OE# input is at V

IH

, output from the device is disabled. The output pins

are placed in the high impedance state.

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

23

A d v a n c e I n f o r m a t i o n

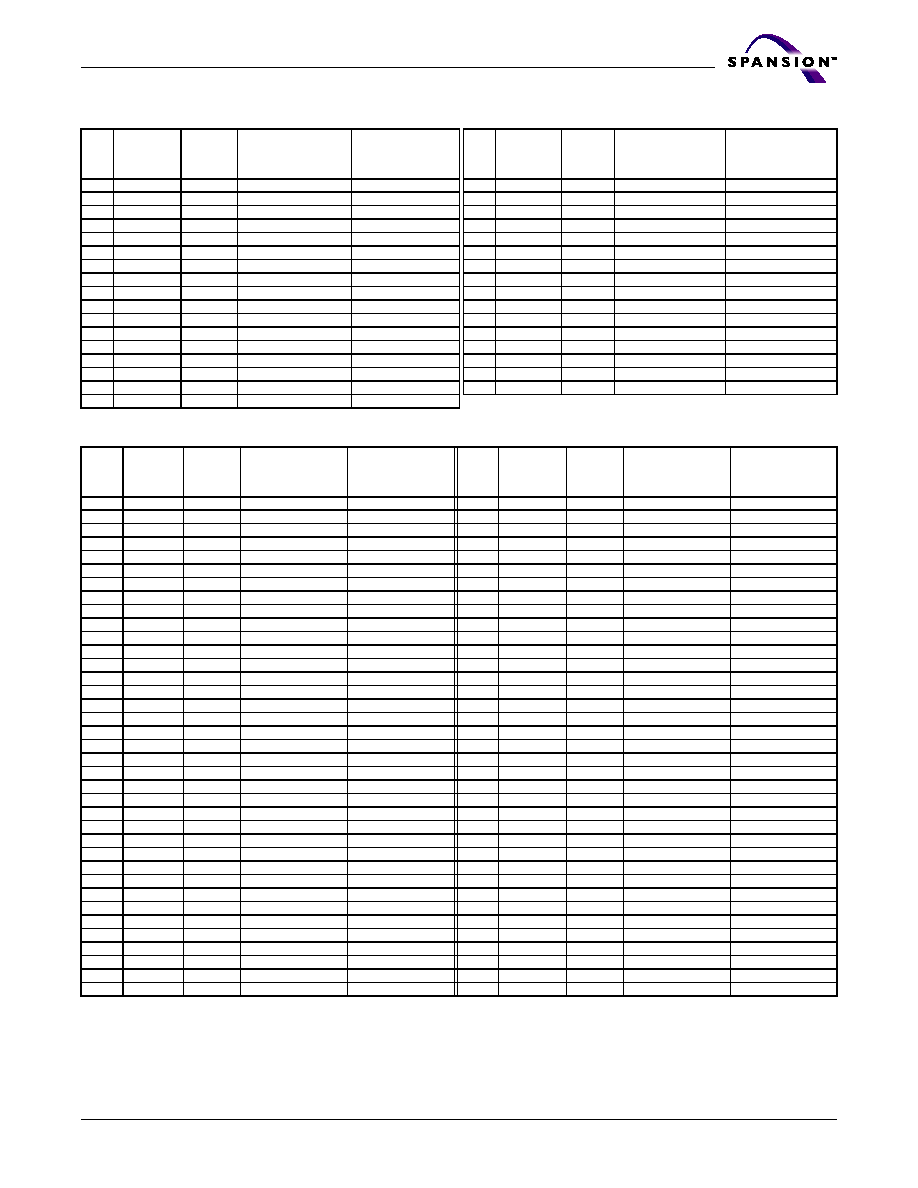

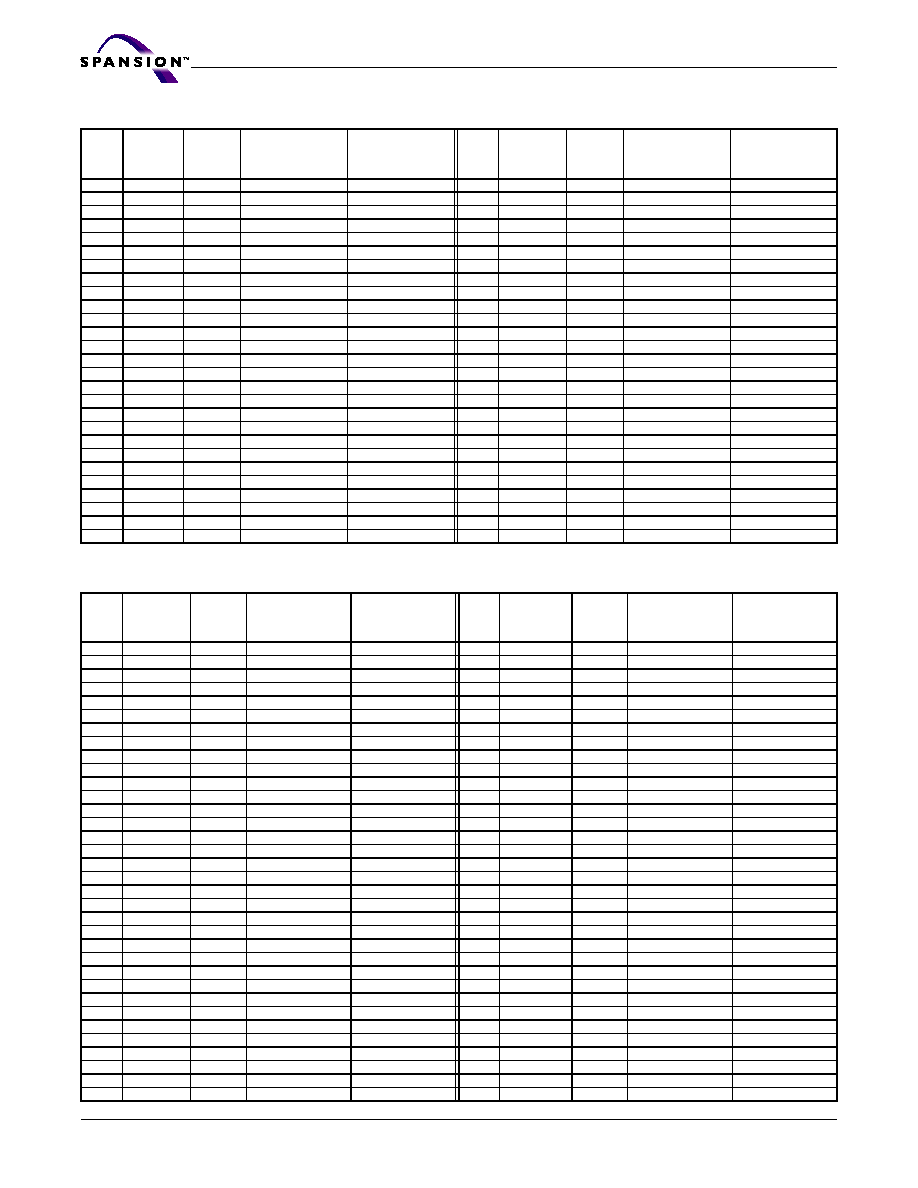

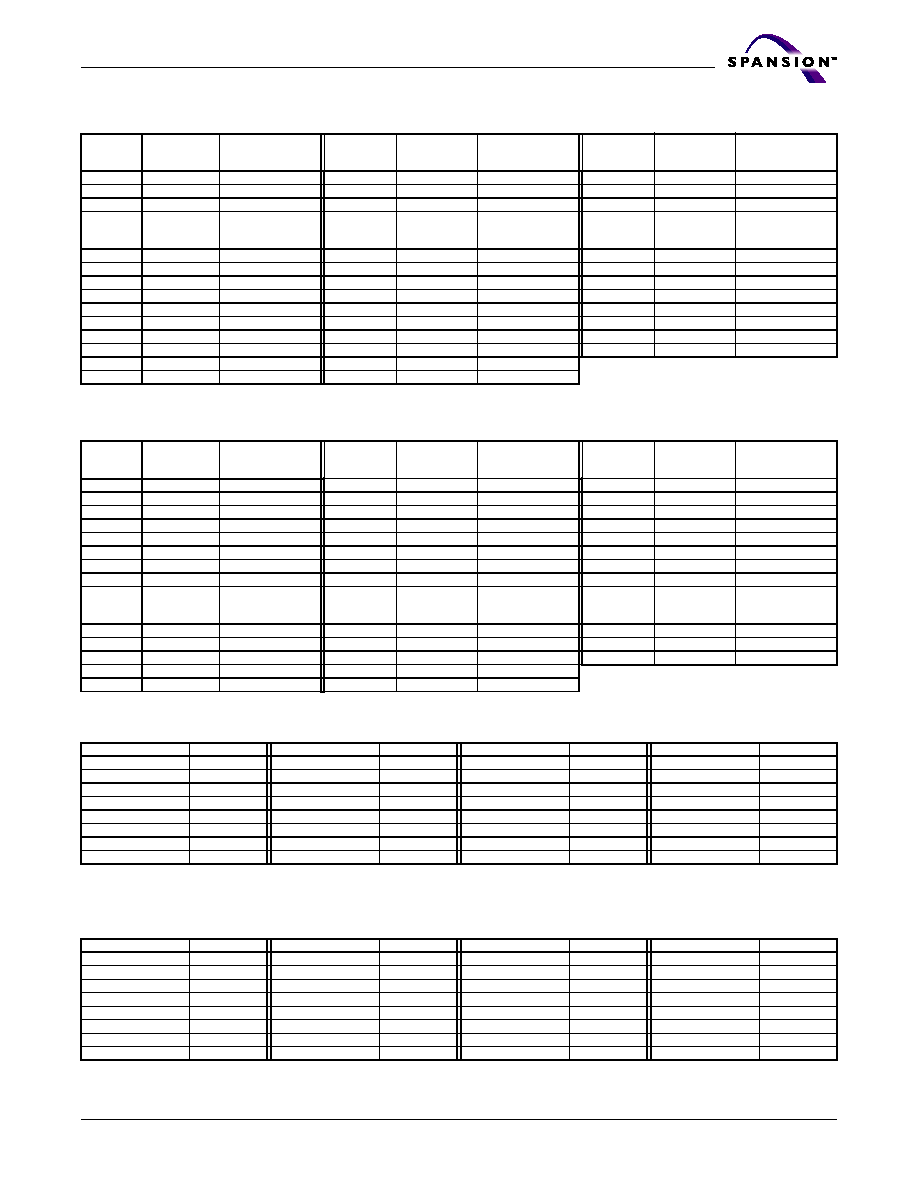

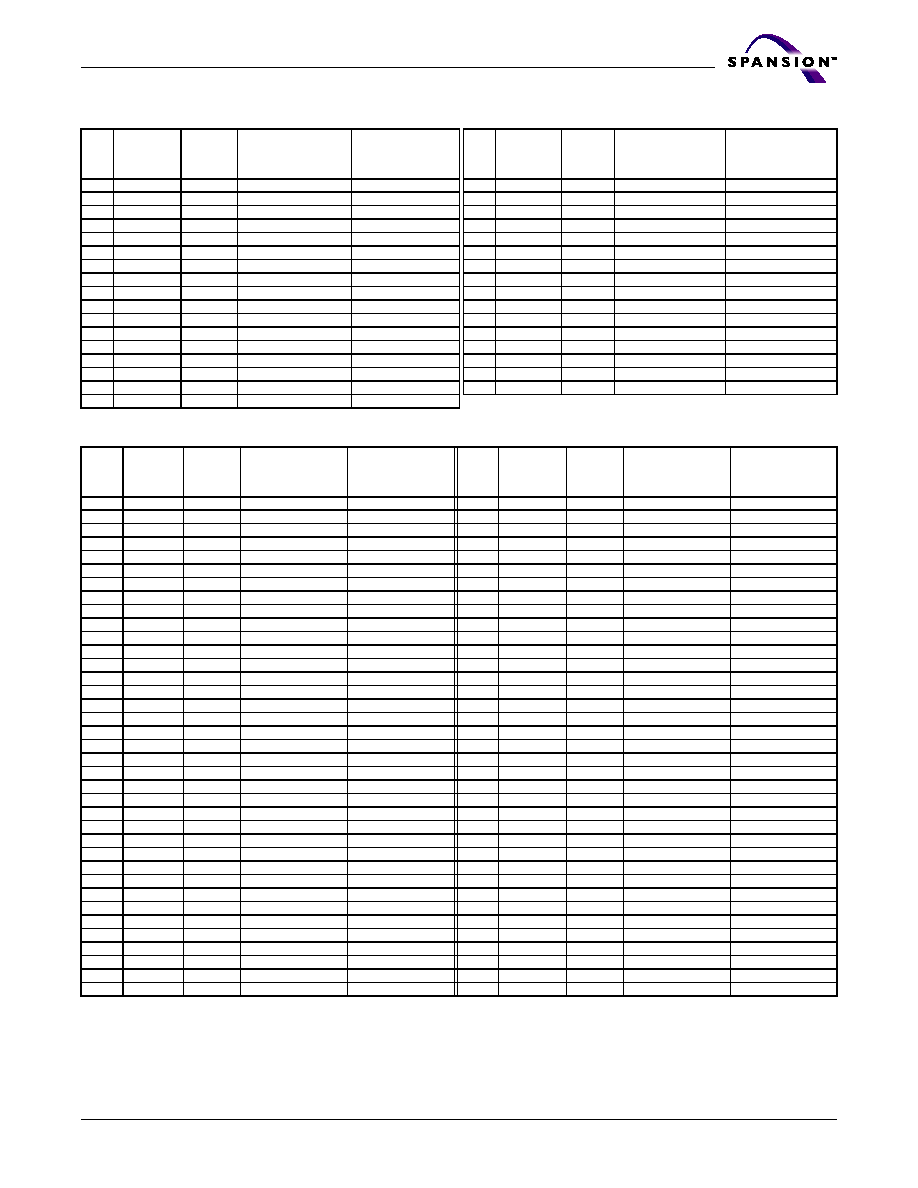

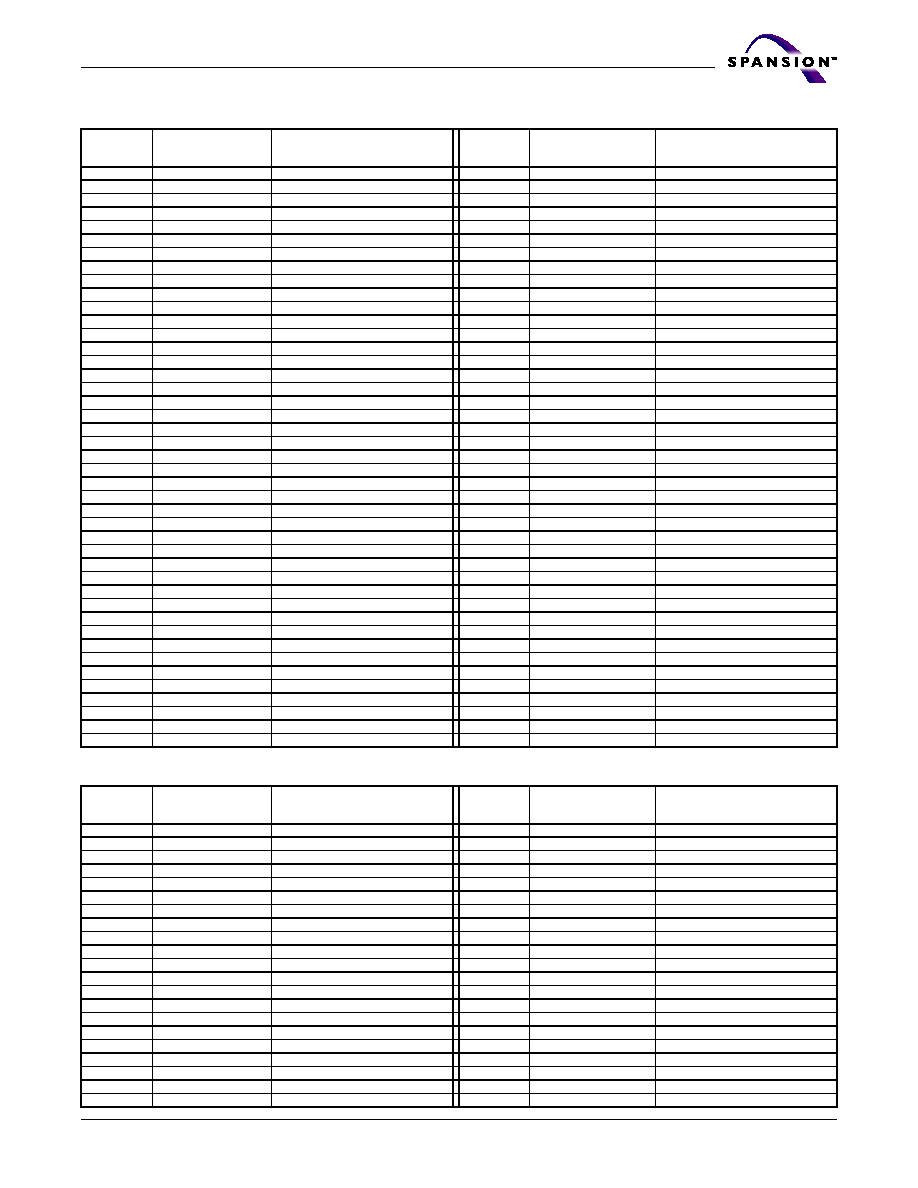

Table 4. S29GL032M (Models R1, R2) Sector Addresses

Se

ct

or

A20-A15

Sector

Size

(KB/

Kwords)

8-bit

Address

Range

16-bit

Address

Range

Se

ct

or

A20-A15

Sector

Size

(KB/

Kwords)

8-bit

Address

Range

16-bit

Address

Range

SA0 0 0 0 0 0 0

64/32

000000≠00FFFF

000000≠007FFF

SA32 1 0 0 0 0 0

64/32

200000≠20FFFF

100000≠107FFF

SA1 0 0 0 0 0 1

64/32

010000≠01FFFF

008000≠00FFFF

SA33 1 0 0 0 0 1

64/32

210000≠21FFFF

108000≠10FFFF

SA2 0 0 0 0 1 0

64/32

020000≠02FFFF

010000≠017FFF

SA34 1 0 0 0 1 0

64/32

220000≠22FFFF

110000≠117FFF

SA3 0 0 0 0 1 1

64/32

030000≠03FFFF

018000≠01FFFF

SA35 1 0 0 0 1 1

64/32

230000≠23FFFF

118000≠11FFFF

SA4 0 0 0 1 0 0

64/32

040000≠04FFFF

020000≠027FFF

SA36 1 0 0 1 0 0

64/32

240000≠24FFFF

120000≠127FFF

SA5 0 0 0 1 0 1

64/32

050000≠05FFFF

028000≠02FFFF

SA37 1 0 0 1 0 1

64/32

250000≠25FFFF

128000≠12FFFF

SA6 0 0 0 1 1 0

64/32

060000≠06FFFF

030000≠037FFF

SA38 1 0 0 1 1 0

64/32

260000≠26FFFF

130000≠137FFF

SA7 0 0 0 1 1 1

64/32

070000≠07FFFF

038000≠03FFFF

SA39 1 0 0 1 1 1

64/32

270000≠27FFFF

138000≠13FFFF

SA8 0 0 1 0 0 0

64/32

080000≠08FFFF

040000≠047FFF

SA40 1 0 1 0 0 0

64/32

280000≠28FFFF

140000≠147FFF

SA9 0 0 1 0 0 1

64/32

090000≠09FFFF

048000≠04FFFF

SA41 1 0 1 0 0 1

64/32

290000≠29FFFF

148000≠14FFFF

SA10 0 0 1 0 1 0

64/32

0A0000≠0AFFFF

050000≠057FFF

SA42 1 0 1 0 1 0

64/32

2A0000≠2AFFFF

150000≠157FFF

SA11 0 0 1 0 1 1

64/32

0B0000≠0BFFFF

058000≠05FFFF

SA43 1 0 1 0 1 1

64/32

2B0000≠2BFFFF

158000≠15FFFF

SA12 0 0 1 1 0 0

64/32

0C0000≠0CFFFF

060000≠067FFF

SA44 1 0 1 1 0 0

64/32

2C0000≠2CFFFF

160000≠167FFF

SA13 0 0 1 1 0 1

64/32

0D0000≠0DFFFF

068000≠06FFFF

SA45 1 0 1 1 0 1

64/32

2D0000≠2DFFFF

168000≠16FFFF

SA14 0 0 1 1 1 0

64/32

0E0000≠0EFFFF

070000≠077FFF

SA46 1 0 1 1 1 0

64/32

2E0000≠2EFFFF

170000≠177FFF

SA15 0 0 1 1 1 1

64/32

0F0000≠0FFFFF

078000≠07FFFF

SA47 1 0 1 1 1 1

64/32

2F0000≠2FFFFF

178000≠17FFFF

SA16 0 1 0 0 0 0

64/32

100000≠10FFFF

080000≠087FFF

SA48 1 1 0 0 0 0

64/32

300000≠30FFFF

180000≠187FFF

SA17 0 1 0 0 0 1

64/32

110000≠11FFFF

088000≠08FFFF

SA49 1 1 0 0 0 1

64/32

310000≠31FFFF

188000≠18FFFF

SA18 0 1 0 0 1 0

64/32

120000≠12FFFF

090000≠097FFF

SA50 1 1 0 0 1 0

64/32

320000≠32FFFF

190000≠197FFF

SA19 0 1 0 0 1 1

64/32

130000≠13FFFF

098000≠09FFFF

SA51 1 1 0 0 1 1

64/32

330000≠33FFFF

198000≠19FFFF

SA20 0 1 0 1 0 0

64/32

140000≠14FFFF

0A0000≠0A7FFF

SA52 1 1 0 1 0 0

64/32

340000≠34FFFF

1A0000≠1A7FFF

SA21 0 1 0 1 0 1

64/32

150000≠15FFFF

0A8000≠0AFFFF

SA53 1 1 0 1 0 1

64/32

350000≠35FFFF

1A8000≠1AFFFF

SA22 0 1 0 1 1 0

64/32

160000≠16FFFF

0B0000≠0B7FFF

SA54 1 1 0 1 1 0

64/32

360000≠36FFFF

1B0000≠1B7FFF

SA23 0 1 0 1 1 1

64/32

170000≠17FFFF

0B8000≠0BFFFF

SA55 1 1 0 1 1 1

64/32

370000≠37FFFF

1B8000≠1BFFFF

SA24 0 1 1 0 0 0

64/32

180000≠18FFFF

0C0000≠0C7FFF

SA56 1 1 1 0 0 0

64/32

380000≠38FFFF

1C0000≠1C7FFF

SA25 0 1 1 0 0 1

64/32

190000≠19FFFF

0C8000≠0CFFFF

SA57 1 1 1 0 0 1

64/32

390000≠39FFFF

1C8000≠1CFFFF

SA26 0 1 1 0 1 0

64/32

1A0000≠1AFFFF

0D0000≠0D7FFF

SA58 1 1 1 0 1 0

64/32

3A0000≠3AFFFF

1D0000≠1D7FFF

SA27 0 1 1 0 1 1

64/32

1B0000≠1BFFFF

0D8000≠0DFFFF

SA59 1 1 1 0 1 1

64/32

3B0000≠3BFFFF

1D8000≠1DFFFF

SA28 0 1 1 1 0 0

64/32

1C0000≠1CFFFF

0E0000≠0E7FFF

SA60 1 1 1 1 0 0

64/32

3C0000≠3CFFFF

1E0000≠1E7FFF

SA29 0 1 1 1 0 1

64/32

1D0000≠1DFFFF

0E8000≠0EFFFF

SA61 1 1 1 1 0 1

64/32

3D0000≠3DFFFF

1E8000≠1EFFFF

SA30 0 1 1 1 1 0

64/32

1E0000≠1EFFFF

0F0000≠0F7FFF

SA62 1 1 1 1 1 0

64/32

3E0000≠3EFFFF

1F0000≠1F7FFF

SA31 0 1 1 1 1 1

64/32

1F0000≠1FFFFF

0F8000≠0FFFFF

SA63 1 1 1 1 1 1

64/32

3F0000≠3FFFFF

1F8000≠1FFFFF

24

S29GLxxxA MirrorBitTM Flash Family

S29GLxxxA_00_A2 January 28, 2005

A d v a n c e I n f o r m a t i o n

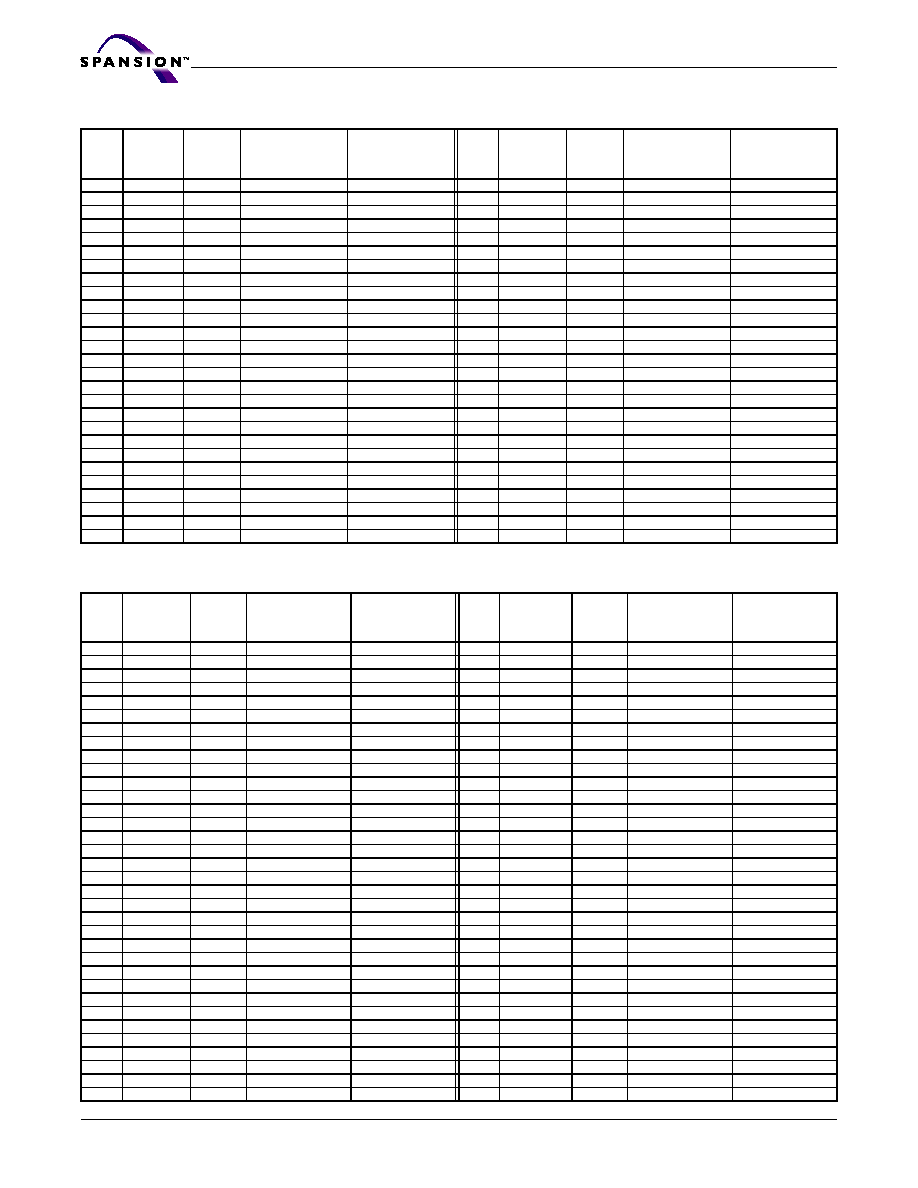

Table 5. S29GL032M (Models R3) Top Boot Sector Addresses

Se

ct

or

A20≠A12

Sector

Size

(KB/

Kwords)

8-bit

Address

Range

16-bit

Address

Range

Se

ct

or

A20≠A12

Sector

Size

(KB/

Kwords)

8-bit

Address

Range

16-bit

Address

Range

SA0 000000xxx

64/32

000000h≠00FFFFh

00000h≠07FFFh

SA36 100100xxx

64/32

240000h≠24FFFFh 120000h≠127FFFh

SA1 000001xxx

64/32

010000h≠01FFFFh

08000h≠0FFFFh

SA37 100101xxx

64/32

250000h≠25FFFFh

128000h≠12FFFFh

SA2 000010xxx

64/32

020000h≠02FFFFh

10000h≠17FFFh

SA38 100110xxx

64/32

260000h≠26FFFFh 130000h≠137FFFh

SA3 000011xxx

64/32

030000h≠03FFFFh

18000h≠1FFFFh

SA39 100111xxx

64/32

270000h≠27FFFFh

138000h≠13FFFFh

SA4 000100xxx

64/32

040000h≠04FFFFh

20000h≠27FFFh

SA40 101000xxx

64/32

280000h≠28FFFFh 140000h≠147FFFh

SA5 000101xxx

64/32

050000h≠05FFFFh

28000h≠2FFFFh

SA41 101001xxx

64/32

290000h≠29FFFFh

148000h≠14FFFFh

SA6 000110xxx

64/32

060000h≠06FFFFh

30000h≠37FFFh

SA42 101010xxx

64/32

2A0000h≠2AFFFFh 150000h≠157FFFh

SA7 000111xxx

64/32

070000h≠07FFFFh

38000h≠3FFFFh

SA43 101011xxx

64/32

2B0000h≠2BFFFFh 158000h≠15FFFFh

SA8 001000xxx

64/32

080000h≠08FFFFh

40000h≠47FFFh

SA44 101100xxx

64/32

2C0000h≠2CFFFFh 160000h≠167FFFh

SA9 001001xxx

64/32

090000h≠09FFFFh

48000h≠4FFFFh

SA45 101101xxx

64/32

2D0000h≠2DFFFFh 168000h≠16FFFFh

SA10 001010xxx

64/32

0A0000h≠0AFFFFh

50000h≠57FFFh

SA46 101110xxx

64/32

2E0000h≠2EFFFFh 170000h≠177FFFh

SA11 001011xxx

64/32

0B0000h≠0BFFFFh

58000h≠5FFFFh

SA47 101111xxx

64/32

2F0000h≠2FFFFFh

178000h≠17FFFFh

SA12 001100xxx

64/32

0C0000h≠0CFFFFh

60000h≠67FFFh

SA48 110000xxx

64/32

300000h≠30FFFFh 180000h≠187FFFh

SA13 001101xxx

64/32

0D0000h≠0DFFFFh

68000h≠6FFFFh

SA49 110001xxx

64/32

310000h≠31FFFFh

188000h≠18FFFFh

SA14 001101xxx

64/32

0E0000h≠0EFFFFh

70000h≠77FFFh

SA50 110010xxx

64/32

320000h≠32FFFFh 190000h≠197FFFh

SA15 001111xxx

64/32

0F0000h≠0FFFFFh

78000h≠7FFFFh

SA51 110011xxx

64/32

330000h≠33FFFFh

198000h≠19FFFFh

SA16 010000xxx

64/32

100000h≠00FFFFh

80000h≠87FFFh

SA52 100100xxx

64/32

340000h≠34FFFFh 1A0000h≠1A7FFFh

SA17 010001xxx

64/32

110000h≠11FFFFh

88000h≠8FFFFh

SA53 110101xxx

64/32

350000h≠35FFFFh 1A8000h≠1AFFFFh

SA18 010010xxx

64/32

120000h≠12FFFFh

90000h≠97FFFh

SA54 110110xxx

64/32

360000h≠36FFFFh 1B0000h≠1B7FFFh

SA19 010011xxx

64/32

130000h≠13FFFFh

98000h≠9FFFFh

SA55 110111xxx

64/32

370000h≠37FFFFh 1B8000h≠1BFFFFh

SA20 010100xxx

64/32

140000h≠14FFFFh

A0000h≠A7FFFh

SA56 111000xxx

64/32

380000h≠38FFFFh 1C0000h≠1C7FFFh

SA21 010101xxx

64/32

150000h≠15FFFFh

A8000h≠AFFFFh

SA57 111001xxx

64/32

390000h≠39FFFFh 1C8000h≠1CFFFFh

SA22 010110xxx

64/32

160000h≠16FFFFh

B0000h≠B7FFFh

SA58 111010xxx

64/32

3A0000h≠3AFFFFh 1D0000h≠1D7FFFh

SA23 010111xxx

64/32

170000h≠17FFFFh

B8000h≠BFFFFh

SA59 111011xxx

64/32

3B0000h≠3BFFFFh 1D8000h≠1DFFFFh

SA24 011000xxx

64/32

180000h≠18FFFFh

C0000h≠C7FFFh

SA60 111100xxx

64/32

3C0000h≠3CFFFFh 1E0000h≠1E7FFFh

SA25 011001xxx

64/32

190000h≠19FFFFh

C8000h≠CFFFFh

SA61 111101xxx

64/32

3D0000h≠3DFFFFh 1E8000h≠1EFFFFh

SA26 011010xxx

64/32

1A0000h≠1AFFFFh

D0000h≠D7FFFh

SA62 111110xxx

64/32

3E0000h≠3EFFFFh

1F0000h≠1F7FFFh

SA27 011011xxx

64/32

1B0000h≠1BFFFFh

D8000h≠DFFFFh

SA63 111111000

8/4

3F0000h≠3F1FFFh

1F8000h≠1F8FFFh

SA28 011000xxx

64/32

1C0000h≠1CFFFFh

E0000h≠E7FFFh

SA64 111111001

8/4

3F2000h≠3F3FFFh

1F9000h≠1F9FFFh

SA29 011101xxx

64/32

1D0000h≠1DFFFFh

E8000h≠EFFFFh

SA65 111111010

8/4

3F4000h≠3F5FFFh

1FA000h≠1FAFFFh

SA30 011110xxx

64/32

1E0000h≠1EFFFFh

F0000h≠F7FFFh

SA66 111111011

8/4

3F6000h≠3F7FFFh

1FB000h≠1FBFFFh

SA31 011111xxx

64/32

1F0000h≠1FFFFFh

F8000h≠FFFFFh

SA67 111111100

8/4

3F8000h≠3F9FFFh

1FC000h≠1FCFFFh

SA32 100000xxx

64/32

200000h≠20FFFFh

F9000h≠107FFFh

SA68 111111101

8/4

3FA000h≠3FBFFFh 1FD000h≠1FDFFFh

SA33 100001xxx

64/32

210000h≠21FFFFh 108000h≠10FFFFh SA69 111111110

8/4

3FC000h≠3FDFFFh 1FE000h≠1FEFFFh

SA34 100010xxx

64/32

220000h≠22FFFFh 110000h≠117FFFh SA70 111111111

8/4

3FE000h≠3FFFFFh

1FF000h≠1FFFFFh

SA35 101011xxx

64/32

230000h≠23FFFFh 118000h≠11FFFFh

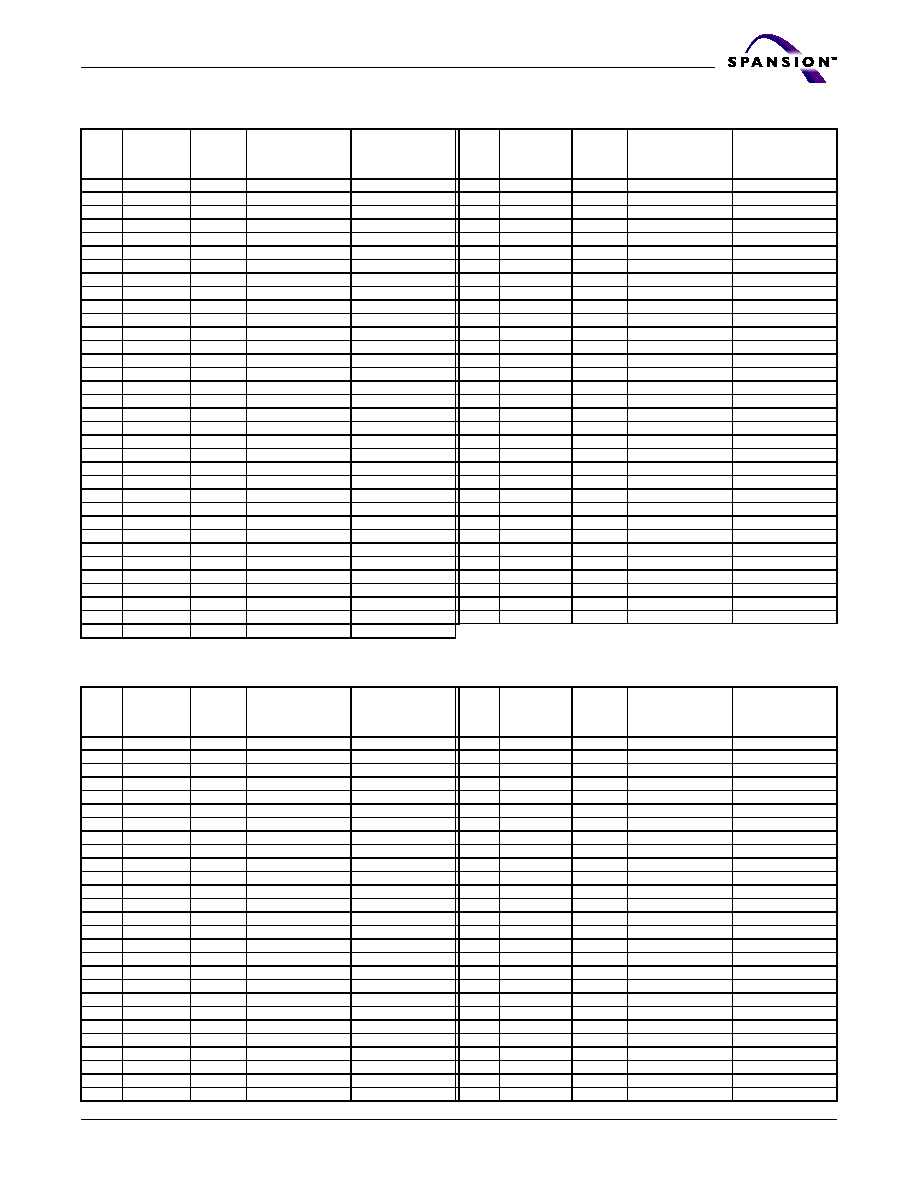

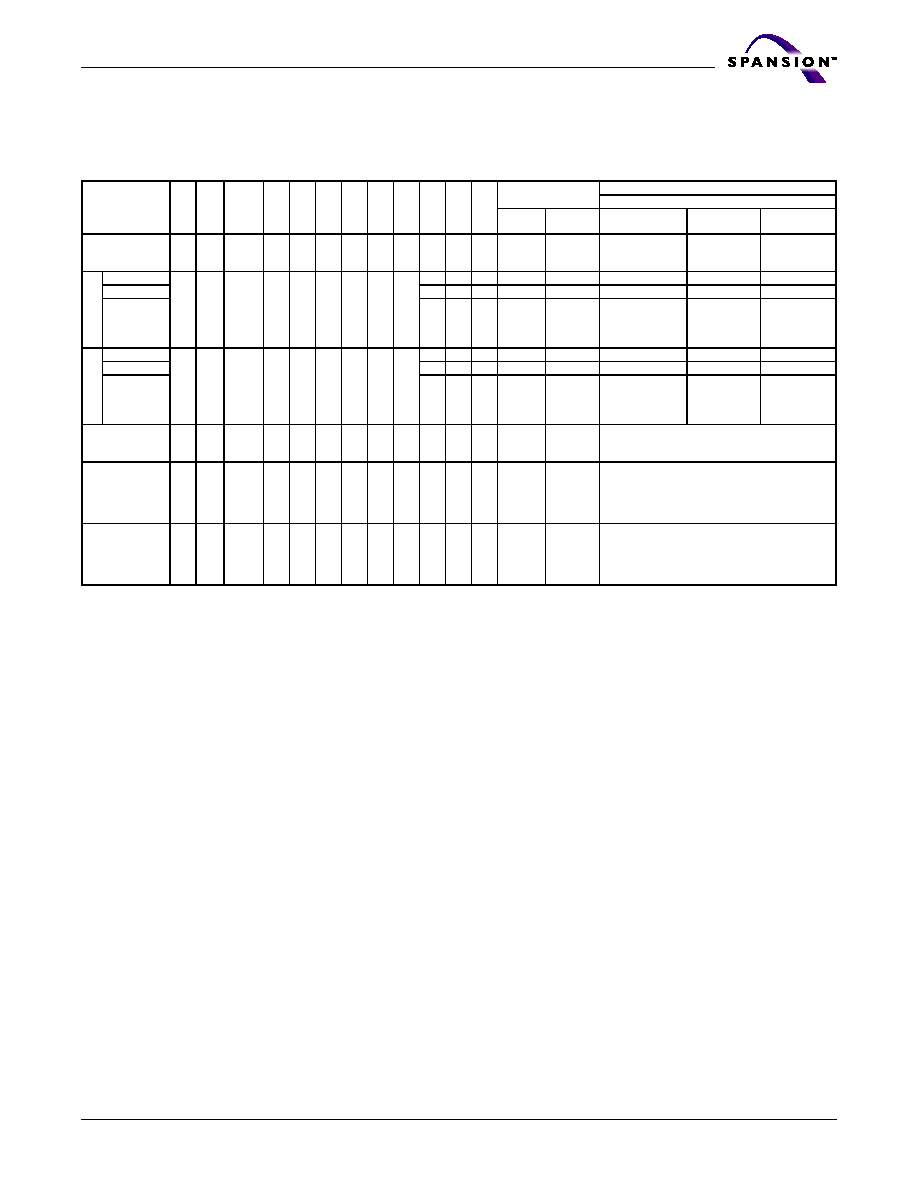

Table 6. S29GL032M (Models R4) Bottom Boot Sector Addresses (Sheet 1 of 2)

Se

ctor

A20≠A12

Sector

Size

(KB/

Kwords)

8-bit

Address

Range

16-bit

Address

Range

Se

ctor

A20≠A12

Sector

Size

(KB/

Kwords)

8-bit

Address

Range

16-bit

Address

Range

SA0 000000000

8/4

000000h≠001FFFh

00000h≠00FFFh

SA19 001100xxx

64/32

0C0000h≠0CFFFFh

60000h≠67FFFh

SA1 000000001

8/4

002000h≠003FFFh

01000h≠01FFFh

SA20 001101xxx

64/32

0D0000h≠0DFFFFh

68000h≠6FFFFh

SA2 000000010

8/4

004000h≠005FFFh

02000h≠02FFFh

SA21 001101xxx

64/32

0E0000h≠0EFFFFh

70000h≠77FFFh

SA3 000000011

8/4

006000h≠007FFFh

03000h≠03FFFh

SA22 001111xxx

64/32

0F0000h≠0FFFFFh

78000h≠7FFFFh

SA4 000000100

8/4

008000h≠009FFFh

04000h≠04FFFh

SA23 010000xxx

64/32

100000h≠00FFFFh

80000h≠87FFFh

SA5 000000101

8/4

00A000h≠00BFFFh

05000h≠05FFFh

SA24 010001xxx

64/32

110000h≠11FFFFh

88000h≠8FFFFh

SA6 000000110

8/4

00C000h≠00DFFFh

06000h≠06FFFh

SA25 010010xxx

64/32

120000h≠12FFFFh

90000h≠97FFFh

SA7 000000111

8/4

00E000h≠00FFFFFh

07000h≠07FFFh

SA26 010011xxx

64/32

130000h≠13FFFFh

98000h≠9FFFFh

SA8 000001xxx

64/32

010000h≠01FFFFh

08000h≠0FFFFh

SA27 010100xxx

64/32

140000h≠14FFFFh

A0000h≠A7FFFh

SA9 000010xxx

64/32

020000h≠02FFFFh

10000h≠17FFFh

SA28 010101xxx

64/32

150000h≠15FFFFh

A8000h≠AFFFFh

SA10 000011xxx

64/32

030000h≠03FFFFh

18000h≠1FFFFh

SA29 010110xxx

64/32

160000h≠16FFFFh

B0000h≠B7FFFh

SA11 000100xxx

64/32

040000h≠04FFFFh

20000h≠27FFFh

SA30 010111xxx

64/32

170000h≠17FFFFh

B8000h≠BFFFFh

SA12 000101xxx

64/32

050000h≠05FFFFh

28000h≠2FFFFh

SA31 011000xxx

64/32

180000h≠18FFFFh

C0000h≠C7FFFh

SA13 000110xxx

64/32

060000h≠06FFFFh

30000h≠37FFFh

SA32 011001xxx

64/32

190000h≠19FFFFh

C8000h≠CFFFFh

SA14 000111xxx

64/32

070000h≠07FFFFh

38000h≠3FFFFh

SA33 011010xxx

64/32

1A0000h≠1AFFFFh

D0000h≠D7FFFh

SA15 001000xxx

64/32

080000h≠08FFFFh

40000h≠47FFFh

SA34 011011xxx

64/32

1B0000h≠1BFFFFh

D8000h≠DFFFFh

SA16 001001xxx

64/32

090000h≠09FFFFh

48000h≠4FFFFh

SA35 011000xxx

64/32

1C0000h≠1CFFFFh

E0000h≠E7FFFh

SA17 001010xxx

64/32

0A0000h≠0AFFFFh

50000h≠57FFFh

SA36 011101xxx

64/32

1D0000h≠1DFFFFh

E8000h≠EFFFFh

SA18 001011xxx

64/32

0B0000h≠0BFFFFh

58000h≠5FFFFh

SA37 011110xxx

64/32

1E0000h≠1EFFFFh

F0000h≠F7FFFh

January 28, 2005 S29GLxxxA_00_A2

S29GLxxxA MirrorBitTM Flash Family

25

A d v a n c e I n f o r m a t i o n

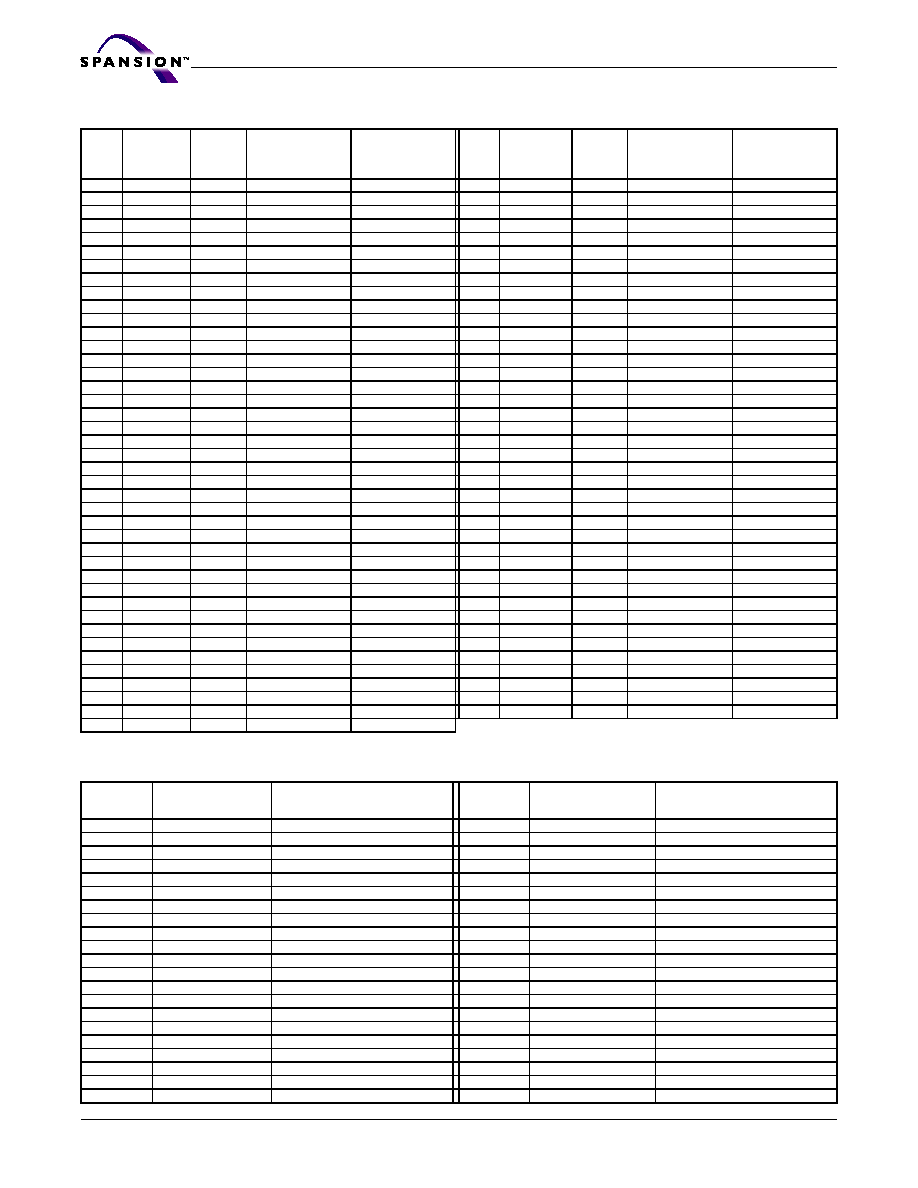

SA38 011111xxx

64/32

1F0000h≠1FFFFFh

F8000h≠FFFFFh

SA55 110000xxx

64/32

300000h≠30FFFFh

180000h≠187FFFh

SA39 100000xxx

64/32

200000h≠20FFFFh

F9000h≠107FFFh

SA56 110001xxx

64/32

310000h≠31FFFFh

188000h≠18FFFFh

SA40 100001xxx

64/32

210000h≠21FFFFh

108000h≠10FFFFh SA57 110010xxx

64/32

320000h≠32FFFFh

190000h≠197FFFh

SA41 100010xxx

64/32

220000h≠22FFFFh

110000h≠117FFFh SA58 110011xxx

64/32

330000h≠33FFFFh

198000h≠19FFFFh

SA42 101011xxx

64/32

230000h≠23FFFFh

118000h≠11FFFFh SA59 100100xxx

64/32

340000h≠34FFFFh

1A0000h≠1A7FFFh

SA43 100100xxx

64/32

240000h≠24FFFFh

120000h≠127FFFh SA60 110101xxx

64/32

350000h≠35FFFFh

1A8000h≠1AFFFFh

SA44 100101xxx

64/32

250000h≠25FFFFh

128000h≠12FFFFh SA61 110110xxx

64/32

360000h≠36FFFFh

1B0000h≠1B7FFFh

SA45 100110xxx

64/32

260000h≠26FFFFh

130000h≠137FFFh SA62 110111xxx

64/32

370000h≠37FFFFh

1B8000h≠1BFFFFh

SA46 100111xxx

64/32

270000h≠27FFFFh

138000h≠13FFFFh SA63 111000xxx

64/32

380000h≠38FFFFh

1C0000h≠1C7FFFh

SA47 101000xxx

64/32

280000h≠28FFFFh

140000h≠147FFFh SA64 111001xxx

64/32

390000h≠39FFFFh

1C8000h≠1CFFFFh

SA48 101001xxx

64/32

290000h≠29FFFFh

148000h≠14FFFFh SA65 111010xxx

64/32

3A0000h≠3AFFFFh 1D0000h≠1D7FFFh

SA49 101010xxx

64/32

2A0000h≠2AFFFFh

150000h≠157FFFh SA66 111011xxx

64/32

3B0000h≠3BFFFFh 1D8000h≠1DFFFFh

SA50 101011xxx

64/32

2B0000h≠2BFFFFh

158000h≠15FFFFh SA67 111100xxx

64/32

3C0000h≠3CFFFFh

1E0000h≠1E7FFFh

SA51 101100xxx

64/32

2C0000h≠2CFFFFh

160000h≠167FFFh SA68 111101xxx

64/32

3D0000h≠3DFFFFh 1E8000h≠1EFFFFh

SA52 101101xxx

64/32

2D0000h≠2DFFFFh 168000h≠16FFFFh SA69 111110xxx

64/32

3E0000h≠3EFFFFh

1F0000h≠1F7FFFh

SA53 101110xxx

64/32

2E0000h≠2EFFFFh

170000h≠177FFFh SA70 111111xxx

64/32

3F0000h≠3FFFFFh

1F8000h≠1FFFFFh

SA54 101111xxx

64/32

2F0000h≠2FFFFFh

178000h≠17FFFFh

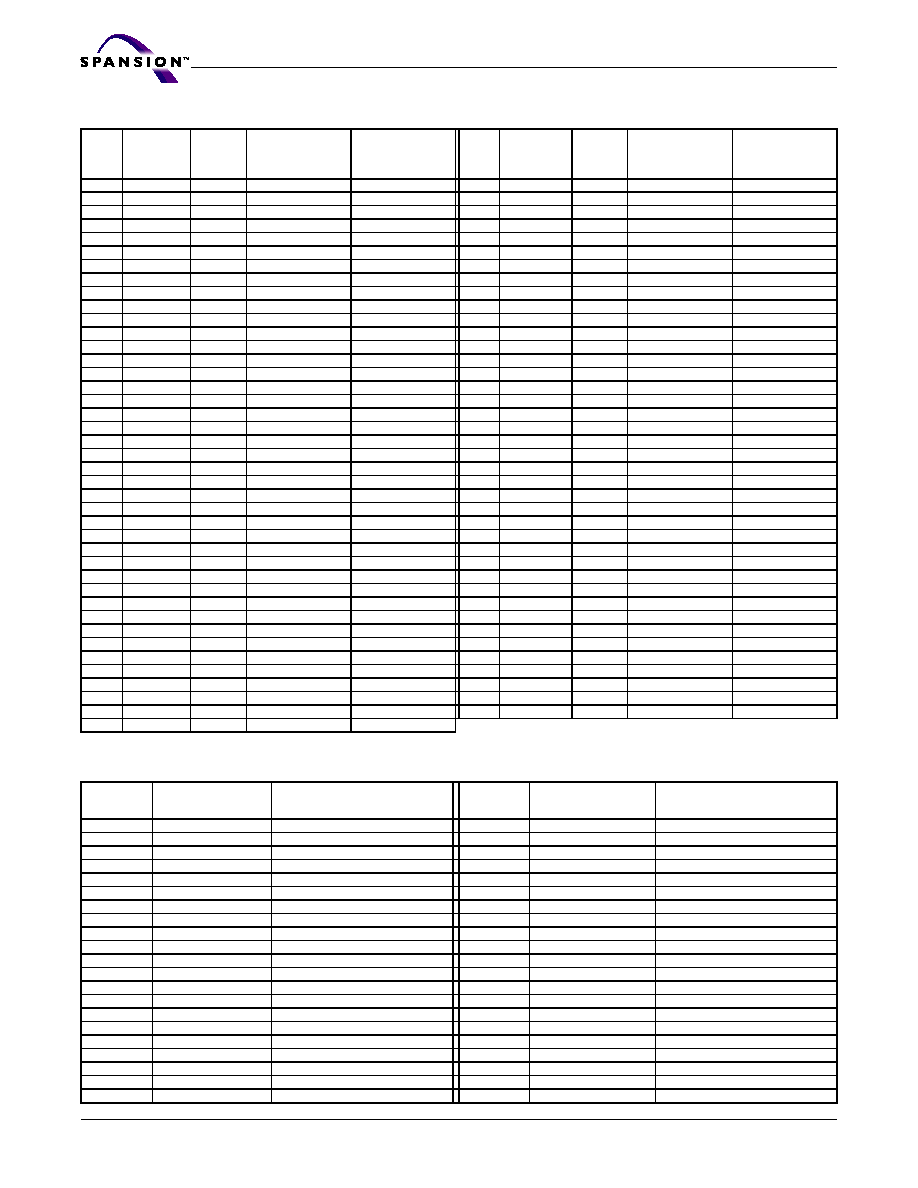

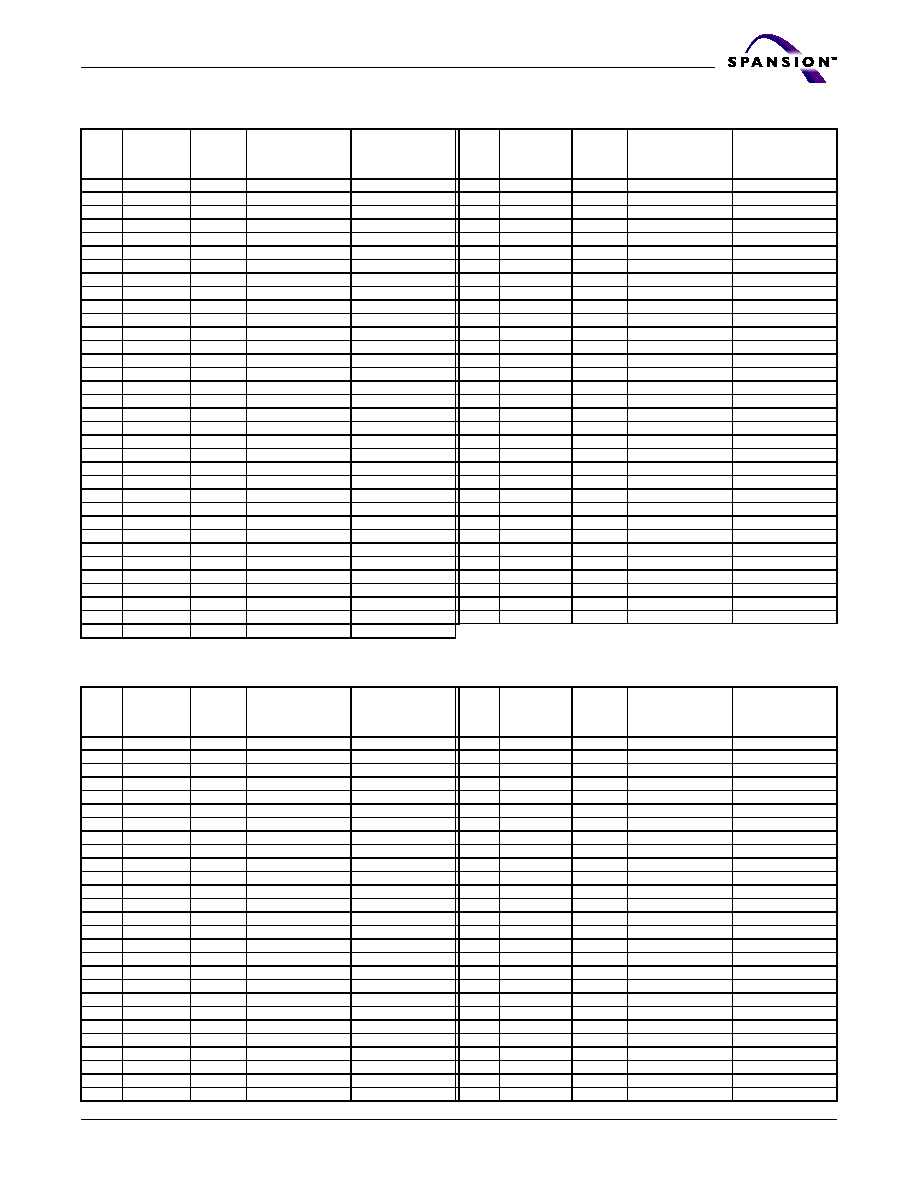

Table 7. S29GL064A (Models R1, R2, R8, R9) Sector Addresses (Sheet 1 of 2)

Se

ct

or

A21≠A15

Sector

Size

(KB/

Kwords)

8-bit

Address

Range

16-bit

Address

Range

Se

ct

or

A21≠A15

Sector

Size

(KB/

Kwords)

8-bit

Address

Range

16-bit

Address

Range

SA0

0000000

64/32

000000≠00FFFF

000000≠007FFF

SA37

0100101

64/32

250000≠25FFFF

128000≠12FFFF

SA1

0000001

64/32

010000≠01FFFF

008000≠00FFFF

SA38

0100110

64/32

260000≠26FFFF

130000≠137FFF

SA2

0000010

64/32

020000≠02FFFF

010000≠017FFF

SA39

0100111

64/32

270000≠27FFFF

138000≠13FFFF

SA3

0000011

64/32

030000≠03FFFF

018000≠01FFFF

SA40

0101000

64/32

280000≠28FFFF

140000≠147FFF

SA4

0000100

64/32

040000≠04FFFF

020000≠027FFF

SA41

0101001

64/32

290000≠29FFFF

148000≠14FFFF

SA5

0000101

64/32

050000≠05FFFF

028000≠02FFFF

SA42

0101010

64/32

2A0000≠2AFFFF

150000≠157FFF

SA6

0000110

64/32

060000≠06FFFF

030000≠037FFF

SA43

0101011

64/32

2B0000≠2BFFFF

158000≠15FFFF

SA7

0000111

64/32

070000≠07FFFF

038000≠03FFFF

SA44

0101100

64/32

2C0000≠2CFFFF

160000≠167FFF

SA8

0001000

64/32

080000≠08FFFF

040000≠047FFF

SA45

0101101

64/32

2D0000≠2DFFFF

168000≠16FFFF

SA9

0001001

64/32

090000≠09FFFF

048000≠04FFFF

SA46

0101110

64/32

2E0000≠2EFFFF

170000≠177FFF

SA10

0001010

64/32

0A0000≠0AFFFF

050000≠057FFF

SA47

0101111

64/32

2F0000≠2FFFFF

178000≠17FFFF

SA11

0001011

64/32

0B0000≠0BFFFF

058000≠05FFFF

SA48

0110000

64/32

300000≠30FFFF

180000≠187FFF

SA12

0001100

64/32

0C0000≠0CFFFF

060000≠067FFF

SA49

0110001

64/32

310000≠31FFFF

188000≠18FFFF

SA13

0001101

64/32

0D0000≠0DFFFF

068000≠06FFFF

SA50

0110010

64/32

320000≠32FFFF

190000≠197FFF

SA14

0001110

64/32

0E0000≠0EFFFF

070000≠077FFF

SA51

0110011

64/32

330000≠33FFFF

198000≠19FFFF

SA15

0001111

64/32

0F0000≠0FFFFF

078000≠07FFFF

SA52

0110100

64/32

340000≠34FFFF

1A0000≠1A7FFF

SA16

0010000

64/32

100000≠10FFFF

080000≠087FFF

SA53

0110101

64/32

350000≠35FFFF

1A8000≠1AFFFF

SA17

0010001

64/32

110000≠11FFFF

088000≠08FFFF

SA54

0110110

64/32

360000≠36FFFF

1B0000≠1B7FFF

SA18

0010010

64/32

120000≠12FFFF

090000≠097FFF

SA55

0110111

64/32

370000≠37FFFF

1B8000≠1BFFFF

SA19

0010011

64/32

130000≠13FFFF

098000≠09FFFF

SA56

0111000

64/32

380000≠38FFFF

1C0000≠1C7FFF

SA20

0010100

64/32

140000≠14FFFF

0A0000≠0A7FFF

SA57

0111001

64/32

390000≠39FFFF

1C8000≠1CFFFF

SA21

0010101

64/32

150000≠15FFFF

0A8000≠0AFFFF

SA58

0111010

64/32

3A0000≠3AFFFF

1D0000≠1D7FFF

SA22

0010110

64/32

160000≠16FFFF

0B0000≠0B7FFF

SA59

0111011

64/32

3B0000≠3BFFFF

1D8000≠1DFFFF

SA23

0010111

64/32

170000≠17FFFF

0B8000≠0BFFFF

SA60

0111100

64/32

3C0000≠3CFFFF

1E0000≠1E7FFF

SA24

0011000

64/32

180000≠18FFFF

0C0000≠0C7FFF

SA61

0111101

64/32

3D0000≠3DFFFF

1E8000≠1EFFFF

SA25

0011001

64/32

190000≠19FFFF

0C8000≠0CFFFF

SA62

0111110

64/32

3E0000≠3EFFFF

1F0000≠1F7FFF

SA26

0011010

64/32

1A0000≠1AFFFF

0D0000≠0D7FFF

SA63

0111111

64/32

3F0000≠3FFFFF

1F8000≠1FFFFF

SA27

0011011

64/32

1B0000≠1BFFFF

0D8000≠0DFFFF

SA64

1000000

64/32

400000≠40FFFF

200000≠207FFF

SA28

0011100

64/32

1C0000≠1CFFFF

0E0000≠0E7FFF

SA65

1000001

64/32

410000≠41FFFF

208000≠20FFFF

SA29

0011101

64/32

1D0000≠1DFFFF

0E8000≠0EFFFF

SA66

1000010

64/32

420000≠42FFFF

210000≠217FFF

SA30

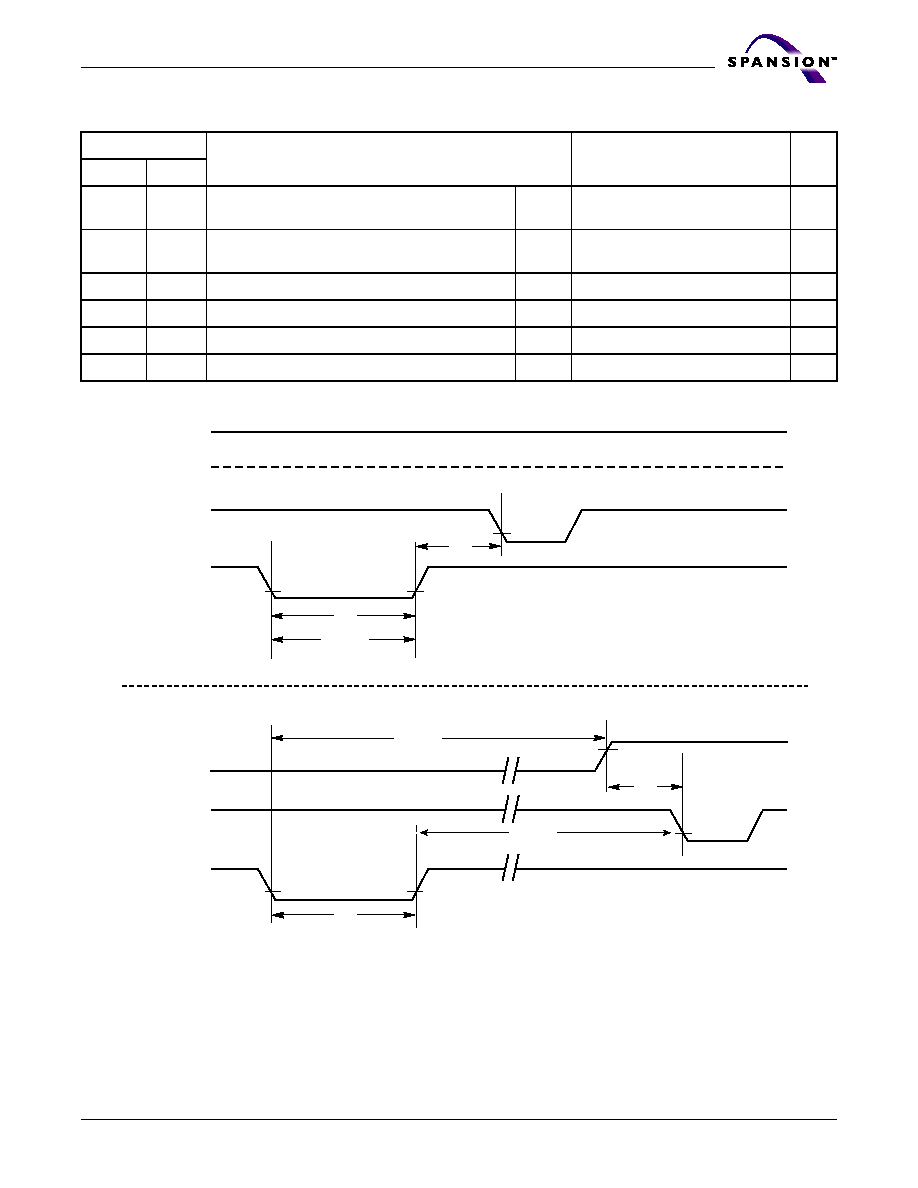

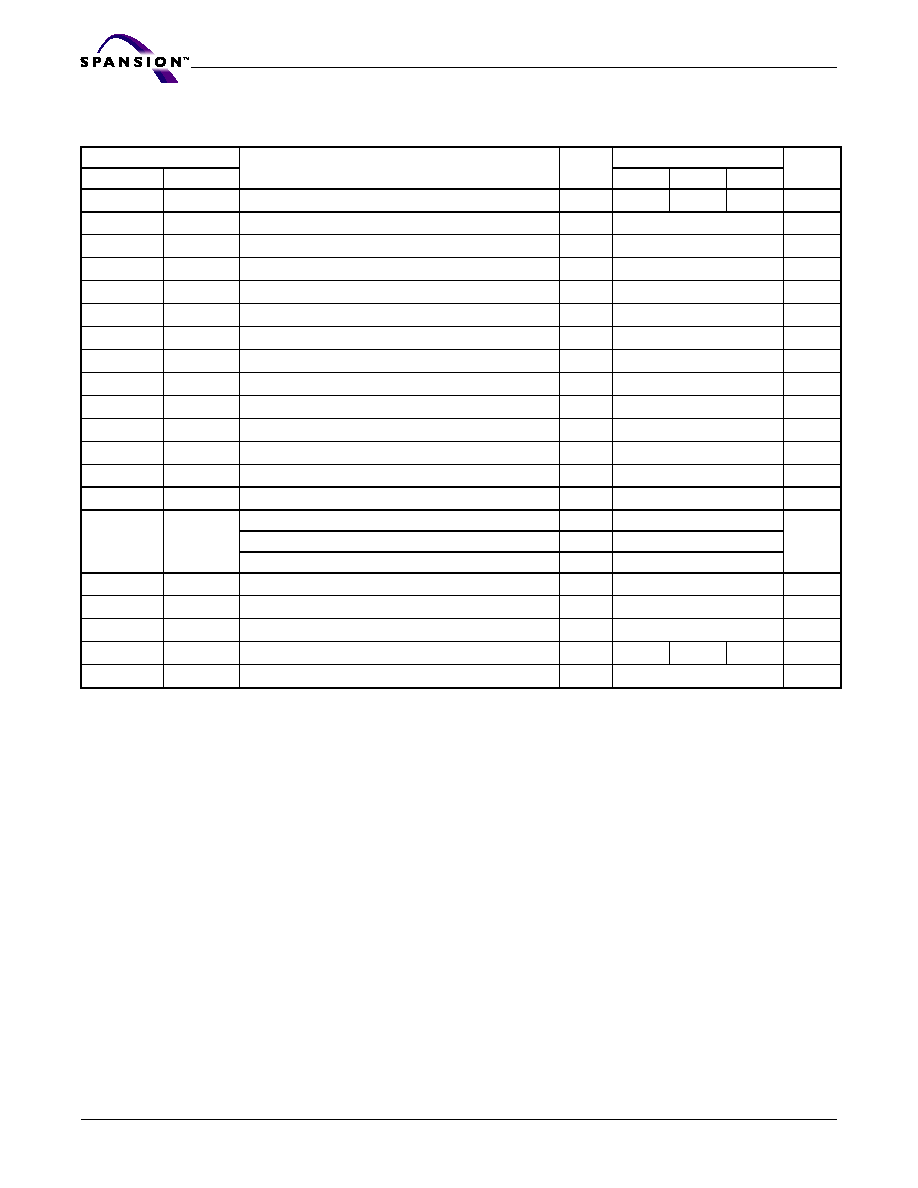

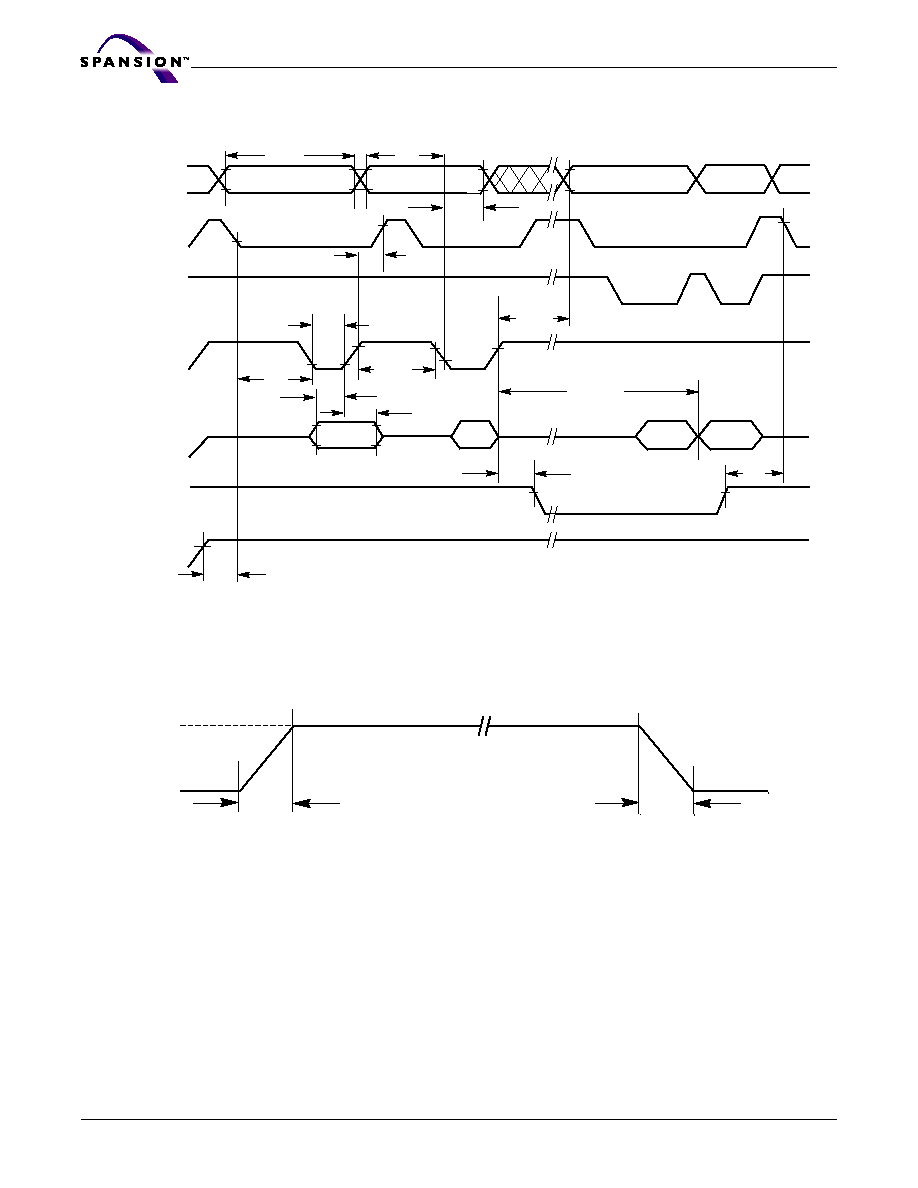

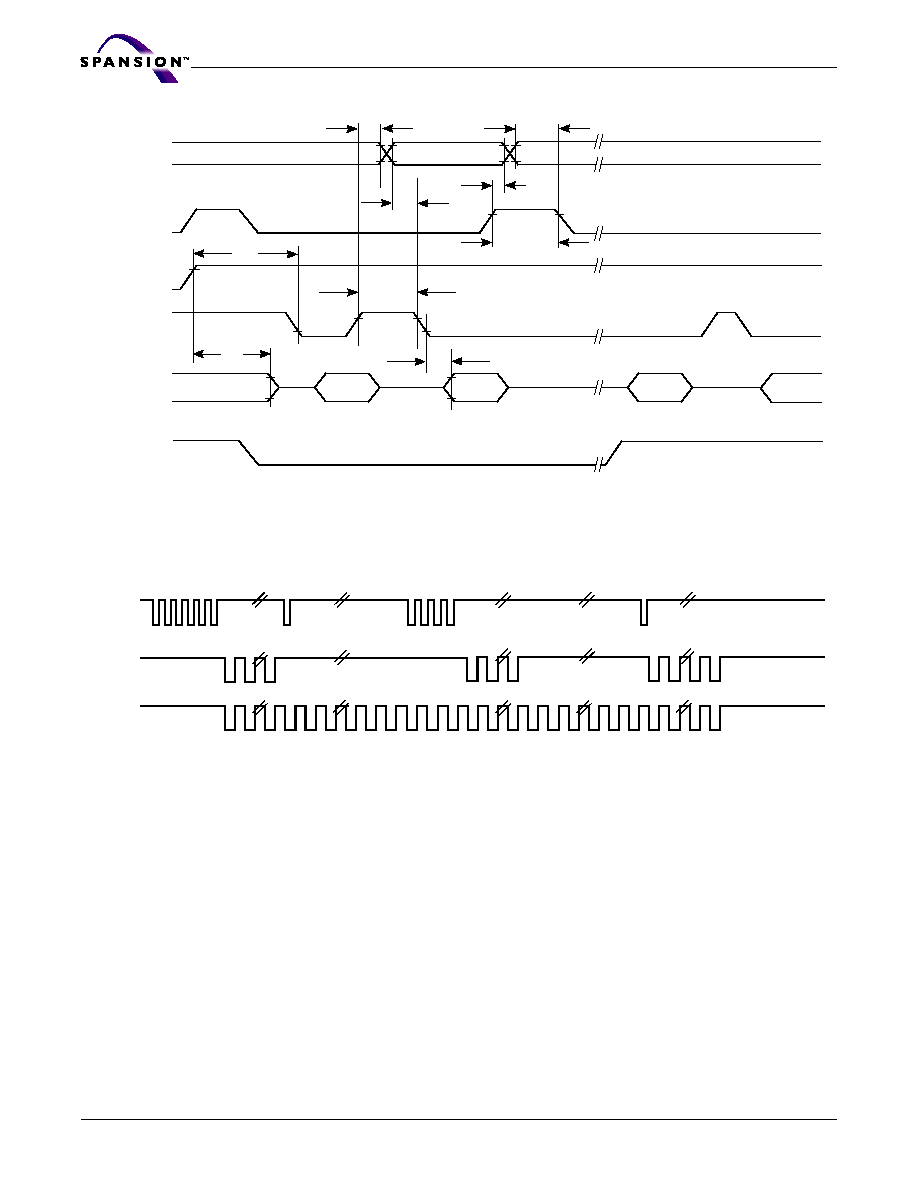

0011110