| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: SSSB152 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

- 1 -

Swindon Silicon Systems Limited

Jan 96

SSSB152

Byte Multiplexer

SDH Product Range

∑ High performance Silicon Bipolar process

∑ Eight CMOS compatible byte-wide STM1 input ports

∑ Byte-wide ECL100k compatible output port

∑ Interfaces between SSSM112 and SSSB148

∑ Built in scrambling and parity circuits

∑ Built in clock and frame pulse generators

∑ Twin power supply (-5 V & +5V)

∑ Low dissipation (1.55W)

∑ 132 pin gull-wing ceramic package

∑ Meets ITU-T recommendations

Byte Multiplexer

FEATURES

The SSSB152 accepts eight byte-wide input channels (STM1 frames in byte parallel form) at 19.44MByte/s and

multiplexes these onto one byte-wide output channel at 155.52MByte/s. The device includes circuits for parity

generation and scrambling for STM16 or STM64 frames in accordance with the ITU-T recommendations. The

SSSB152 also provides clock and frame synchronisation signals for SSSM112 STM1 Adapter devices.

Two SSSB152 devices and one SSSB148 16:1 multiplexer device form a circuit which merges 16 channels carrying

STM1 frames in byte parallel form into one STM16 serial data stream at 2.48832GBit/s.

Eight SSSB152 devices and a 10GHz 64:1 multiplexer form a circuit which merges 64 channels carrying STM1

frames in byte parallel form into one STM64 serial data stream at 9.95328GBit/s.

FUNCTIONAL OVERVIEW

SSSB152

DATE CODE

The SSSB152 is a 155.52MHz byte-wide 8:1 multiplexer, with additional features to allow it to be used in an STM1

to STM16 or an STM1 to STM64 multiplexer applications.

Pin 1

Top View

SSSB152

Byte Multiplexer

- 2 -

Swindon Silicon Systems Limited

Jan 96

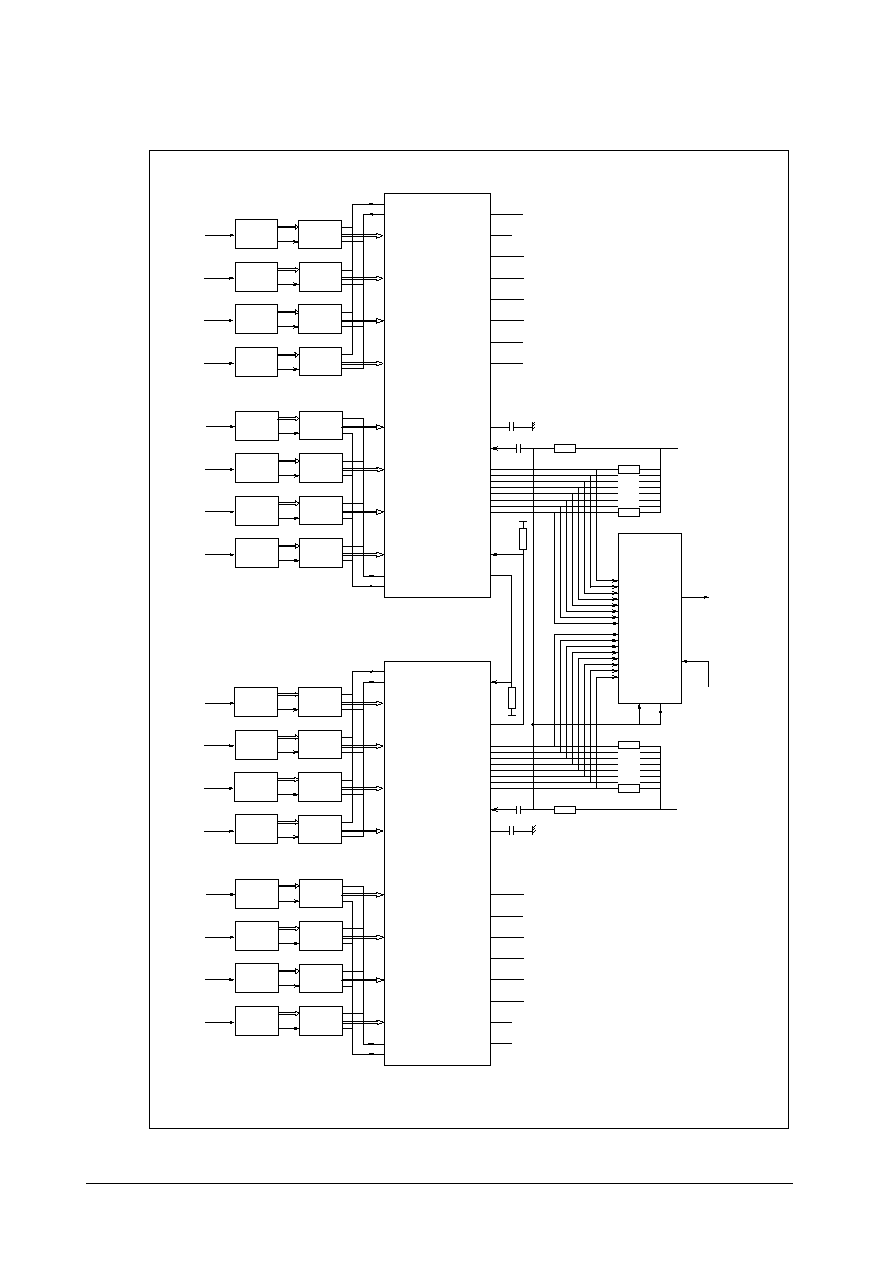

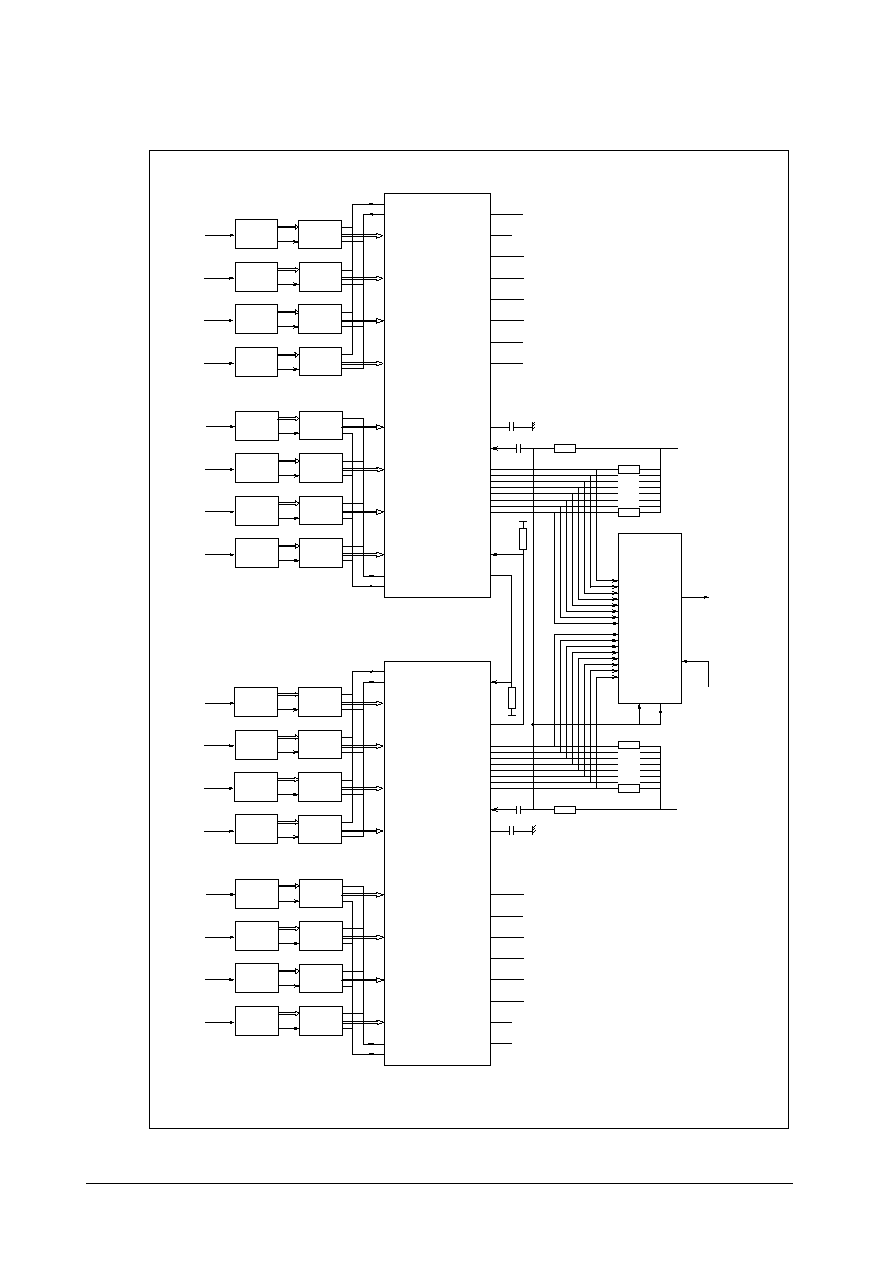

STM1 - STM16 Multiplexer Block Diagram

SSSM

112

SSSB

151

SSSM

112

SSSB

151

SSSM

112

SSSB

151

SSSM

112

SSSB

151

SSSM

112

SSSB

151

SSSM

112

SSSB

151

SSSM

112

SSSB

151

SSSM

112

SSSB

151

1

3

5

7

9

11

13

15

SYNCBO2

MCK2

STMIA

STMIB

STMIC

STMID

STMIE

STMIF

STMIG

STMIH

SYNCBO1

MCK1

SSSB152

MASTER

SSSM

112

SSSB

151

SSSM

112

SSSB

151

SSSM

112

SSSB

151

SSSM

112

SSSB

151

SSSM

112

SSSB

151

112

SSSB

151

SSSM

112

SSSB

151

SSSM

112

SSSB

151

2

4

6

8

10

12

14

16

SYNCBO2

MCK2

STMIA

STMIB

STMIC

STMID

STMIE

STMIF

STMIG

STMIH

SYNCBO1

MCK1

SSSB152

SLAVE

STM1

INPUTS

8x

50

SYNCAI

POUT

B1ENB

MSA

STM16_64

MSB

MSC

SCRB

SYNC IN

n/c

low

low

x

x

50

10n

10n

V

TT

V

TT

CKINB

CKIN

MSTM7

MSTM0

PIN

SYNCAO

SYNCAI

POUT

MSA

MSB

MSC

SCRB

CKINB

CKIN

MSTM7

MSTM0

PIN

SYNCAO

x

x

high

low

low

n/c

10n

10n

STM16_64

B1ENB

SSSB148

D15

D8

D7

D0

Q

QB

CK

CKB

TCK

ICK

100

V

TT

100

V

TT

50

8x

50

STM16

OUTPUT

2.48832 GHz

CLOCK IN

SSSB152

Byte Multiplexer

- 3 -

Swindon Silicon Systems Limited

Jan 96

STM1 - STM16 Multiplexer FUNCTIONAL DESCRIPTION

This description of a complete STM1 to STM16 multiplexer is included to help understand the operation of the

SSSB152 device.

The block diagram shows a complete STM1 to STM16 multiplexer. This multiplexer combines sixteen STM1 serial

data streams at 155.52MBit/s onto one STM16 serial data stream at 2.48832GBit/s. A set of devices to perform the

retiming and reframing of the pleisiochronous STM1 data streams, and to perform the multiplexing functions onto

the STM16 serial data stream is available from Swindon Silicon Systems.

An SSSB151 and an SSSM112 device are used for each STM1 input channel to retime and reframe the

pleisiochronous STM1 155.52MBit/s serial data streams into synchronous, frame aligned, byte-wide 19.44MByte/s

parallel data streams. Two SSSB152 devices and one SSSB148 device are used to multiplex the sixteen STM1

parallel data streams into one STM16 serial data stream at 2.48832GBit/s.

The inputs to the sixteen SSSB151 clock and data receiver devices are the sixteen pleisiochronous STM1 serial data

streams. Each SSSB151 device accepts the STM1 serial data stream in either 155.52MBit/s NRZ data format or

311.04MBaud CMI data format. Each SSSB151 recovers the inbound STM1 clock signal, retimes the data to that

clock signal, then outputs the data in byte-wide parallel form with an associated 19.44MHz clock. The outputs from

the SSSB151 devices are pleisiochronous STM1 data streams in byte parallel form at 19.44MByte/s for the SSSM112

STM1 Adapter devices.

The sixteen SSSM112 devices process the STM1 data in byte parallel form at a clock rate of 19.44MHz. Each

SSSM112 performs the clock synchronisation and frame alignment needed to allow the sixteen pleisiochronous

STM1 channels to be multiplexed onto one STM16 channel. STM1 data is clocked into each SSSM112 by a

19.44MHz clock signal which is derived by the associated SSSB151 device from the inbound STM1 serial data

stream. STM1 frames are clocked out of each SSSM112 device by 19.44MHz clock and 8kHz frame synchronisation

signals which are derived by the SSSB152 and SSSB148 devices from the 2.48832GHz STM16 clock. The outputs

of the SSSM112 devices are STM1 frames in byte parallel form at 19.44MByte/s which are in clock synchronism

and frame alignment with each other.

The two SSSB152 devices are byte-wide 8:1 multiplexers which take in STM1 frames in byte parallel form at

19.44MByte/s, and have byte-wide outputs at 155.52MByte/s. The SSSB152 devices multiplex the STM1 channels,

generate parity and perform the scrambling needed for the STM16 frames. One SSSB152 device acts as the Master

device, this device performs the multiplexing of the odd numbered STM1 channels (1, 3, 5, 7, 9, 11, 13, 15). The

other SSSB152 acts as a Slave device, this device multiplexes the even numbered STM1 channels (2, 4, 6, 8, 10, 12,

14, 16). These devices also divide the 155.52MHz clock from the SSSB148 device to form the 19.44MHz clock and

8kHz (125

µ

s) frame synchronisation signals for the SSSM112 devices. Connections between the two SSSB152

devices maintain synchronisation of the clock and frame dividers in each SSSB152 device, and allow the correct

parity to be generated and inserted into the output frame. Outputs from the SSSB152 devices are 8 STM1 channels

multiplexed together in byte-wide parallel form at 155.52MByte/s.

The SSSB148 device is a 2.5GHz 16:1 Multiplexer which combines the two byte-wide 155.52MByte/s parallel data

streams from the SSSB152 devices onto one 2.48832GBit/s STM16 serial data stream. The SSSB148 also divides

the 2.48832GHz clock down to 155.52MHz for the SSSB152 devices.

Note: Although this description is of an STM1 to STM16 multiplexer, the SSSB152 device also has features which

allow 8 devices (one Master and 7 Slaves) to be used together with a 10GHz 64:1 Multiplexer to form an STM1 to

STM64 multiplexer.

SSSB152

Byte Multiplexer

- 4 -

Swindon Silicon Systems Limited

Jan 96

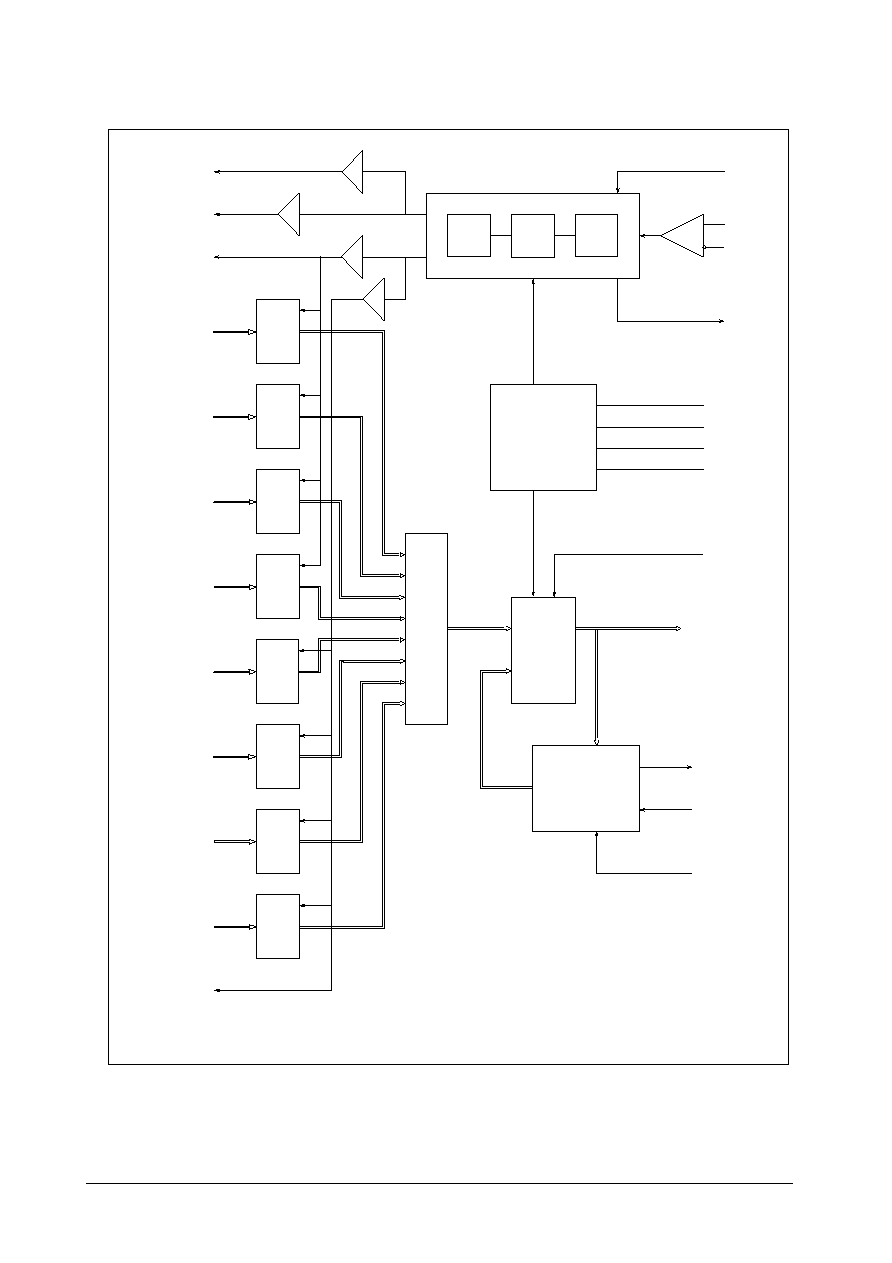

˜

270

˜

9

˜

8

CLOCK DIVIDER

SYNCAO

CKINB

CKIN

SYNCAI

SYNCBO1

SYNCBO2

MCK2

STMIA

{7:0}

LA

TCHES

STMIB

{7:0}

LA

TCHES

STMIC

{7:0}

LA

TCHES

STMID

{7:0}

LA

TCHES

LA

TCHES

LA

TCHES

LA

TCHES

LA

TCHES

STMIE

{7:0}

STMIF

{7:0}

STMIG

{7:0}

STMIH

{7:0}

MCK1

MUL

TIPLEXER

STM16_64

MSA

MSB

MSC

CONTROL

LOGIC

SCRAMBLER

PARITY

B1ENB

PIN

POUT

SCRB

MSTM

7:0

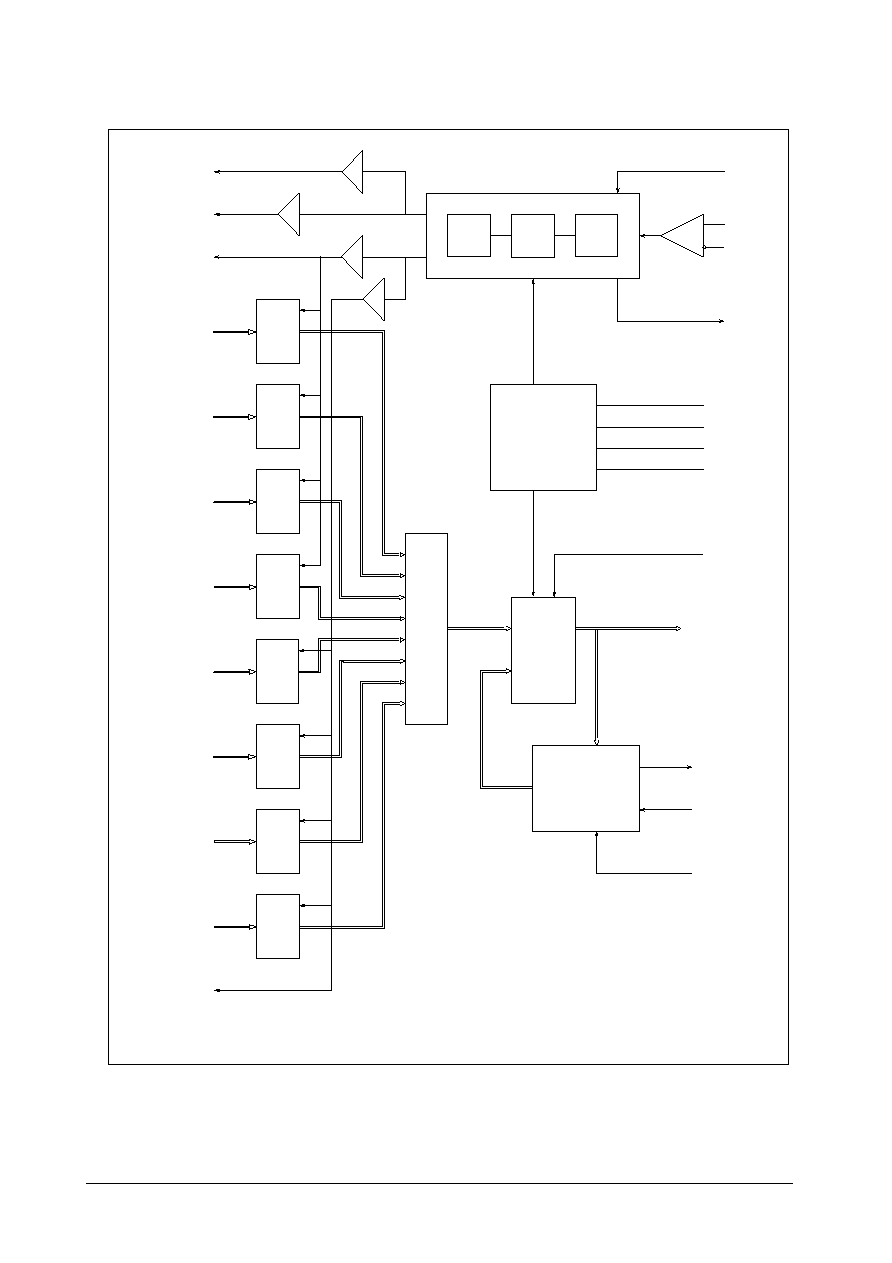

SSSB152 Block Diagram

SSSB152

Byte Multiplexer

- 5 -

Swindon Silicon Systems Limited

Jan 96

SSSB152 FUNCTIONAL DESCRIPTION

The SSSB152 device is designed as part of a chip set for a complete STM1 to STM16 (16:1) or STM1 to STM64

(64:1) multiplexer.

The main function of the SSSB152 device is to multiplex eight STM1 frames in byte-wide parallel form at a clock

rate of 19.44MHz onto one byte-wide parallel data stream at a clock rate of 155.52MHz. The device provides parity

generation and scrambling for STM16 or STM64 frames in accordance with the ITU-T recommendations. The

device also divides the 155.52MHz input clock to form the 19.44MHz clock and 8kHz (125

µ

s) frame

synchronisation output signals which may be used for frame alignment of the STM1 channels external to the

SSSB152.

A complete STM16 or STM64 multiplexer requires multiple SSSB152 devices, a Master device and either one or

seven Slave devices respectively. The SSSB152 has configuration control inputs which vary the operation of the

device depending on whether the device is in an STM16 or STM64 multiplexer application, and whether it is in a

Master or a Slave position. Connections between the SSSB152 devices maintain synchronisation of the clock and

frame dividers in each SSSB152 device, and allow the correct parity to be generated and inserted into the output

frame.

Data Path

The data inputs to the SSSB152 consist of eight ports, each port having eight input pins. The ports are identified as

STMIA{7:0} to STMIH{7:0}. For SDH applications, each port carries STM1 frames in clock synchronism and

frame alignment with each other. Data on all 64 inputs is latched into the SSSB152 by the falling edge of the MCK

signal. MCK is a 19.44MHz clock output of the SSSB152. The Swindon Silicon Systems SSSM112 STM1 Adapter

devices interface directly with the 19.44MHz data inputs, clock outputs and frame pulse outputs of the SSSB152.

The data outputs of the SSSB152 device are identified as MSTM{7:0}. Data is clocked out by the rising edge of

the 155.52MHz CKIN clock. Output data cycles round the input ports STMIA{7:0} to STMIH{7:0} in alphabetical

order at 155.52MHz. If inputs SCRB and B1ENB are both high, the data is unmodified. The action of inputs SCRB

and B1ENB is described below. The Swindon Silicon Systems SSSB148 2.5GHz Multiplexer device interfaces

directly with the 155.52MHz data outputs and clock input of the SSSB152.

Scrambling

The SSSB152 includes scrambler circuits. Scrambling is enabled when the SCRB control input is low. Scrambling

operates on all bits of the STM16 or STM64 frames except during the Regenerator Section OverHead (RSOH).

Scrambling operates in a way which is functionally equivalent to a frame synchronous bit serial scrambler of

sequence length 127 operating on the STM16 or STM64 frames at the line rate. The SSSB152 uses an equivalent

parallel scrambler. Scrambling conforms to ITU Rec. G709.

For each SSSB152 device in an STM16 or STM64 multiplexer, the polynomial and start code used for scrambling

depends on the state of the four configuration control inputs STM16_64, MSA, MSB, and MSC. The STM16_64

input sets the correct polynomial for either an STM16 or an STM64 multiplexer. The MSA, MSB, and MSC inputs

set the correct start code for the device position, i.e. whether the device is in a Master or Slave position, or which

of the seven Slave positions in the case of the STM64 multiplexer application.