| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 74VHC374 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

74VHC374

OCTAL D-TYPE FLIP FLOP

WITH 3 STATE OUTPUT NON INVERTING

June 1999

s

HIGH SPEED:

s

f

MAX

= 270 MHz (TYP.) at V

CC

= 5V

s

LOW POWER DISSIPATION:

I

CC

= 4

µ

A (MAX.) at T

A

= 25

o

C

s

HIGH NOISE IMMUNITY:

V

NIH

= V

NIL

= 28% V

CC

(MIN.)

s

POWER DOWN PROTECTION ON INPUTS

s

SYMMETRICAL OUTPUT IMPEDANCE:

|I

OH

| = I

OL

= 8 mA (MIN)

s

BALANCED PROPAGATION DELAYS:

t

PLH

t

PHL

s

OPERATING VOLTAGE RANGE:

V

CC

(OPR) = 2V to 5.5V

s

PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 374

s

IMPROVED LATCH-UP IMMUNITY

s

LOW NOISE V

OLP

= 0.9V (Max.)

DESCRIPTION

The 74VHC374 is an advanced high-speed

CMOS OCTAL D-TYPE FLIP FLOP with 3

STATE OUTPUT NON INVERTING fabricated

with sub-micron silicon gate and double-layer

metal wiring C

2

MOS technology.

This 8 bit D-Type flip-flop is controlled by a clock

input (CK) and an output enable input (OE).

On the positive transition of the clock, the Q

outputs will be set to the logic state that were

setup at the D inputs.

While the (OE) input is low, the 8 outputs will be

in a normal logic state (high or low logic level)

and while high level the outputs will be in a high

impedance state.

The output control does not affect the internal

operation of flip flops; that is, the old data can be

retained or the new data can be entered even

while the outputs are off.

Power down protection is provided on all inputs

and 0 to 7V can be accepted on inputs with no

regard to the supply voltage. This device can be

used to interface 5V to 3V.

All inputs

and

outputs are

equipped with

protection circuits against static discharge, giving

them 2KV ESD immunity and transient excess

voltage.

PIN CONNECTION AND IEC LOGIC SYMBOLS

ORDER CODES :

74VHC374M

74VHC374T

M

(Micro Package)

T

(TSSOP Package)

Æ

1/10

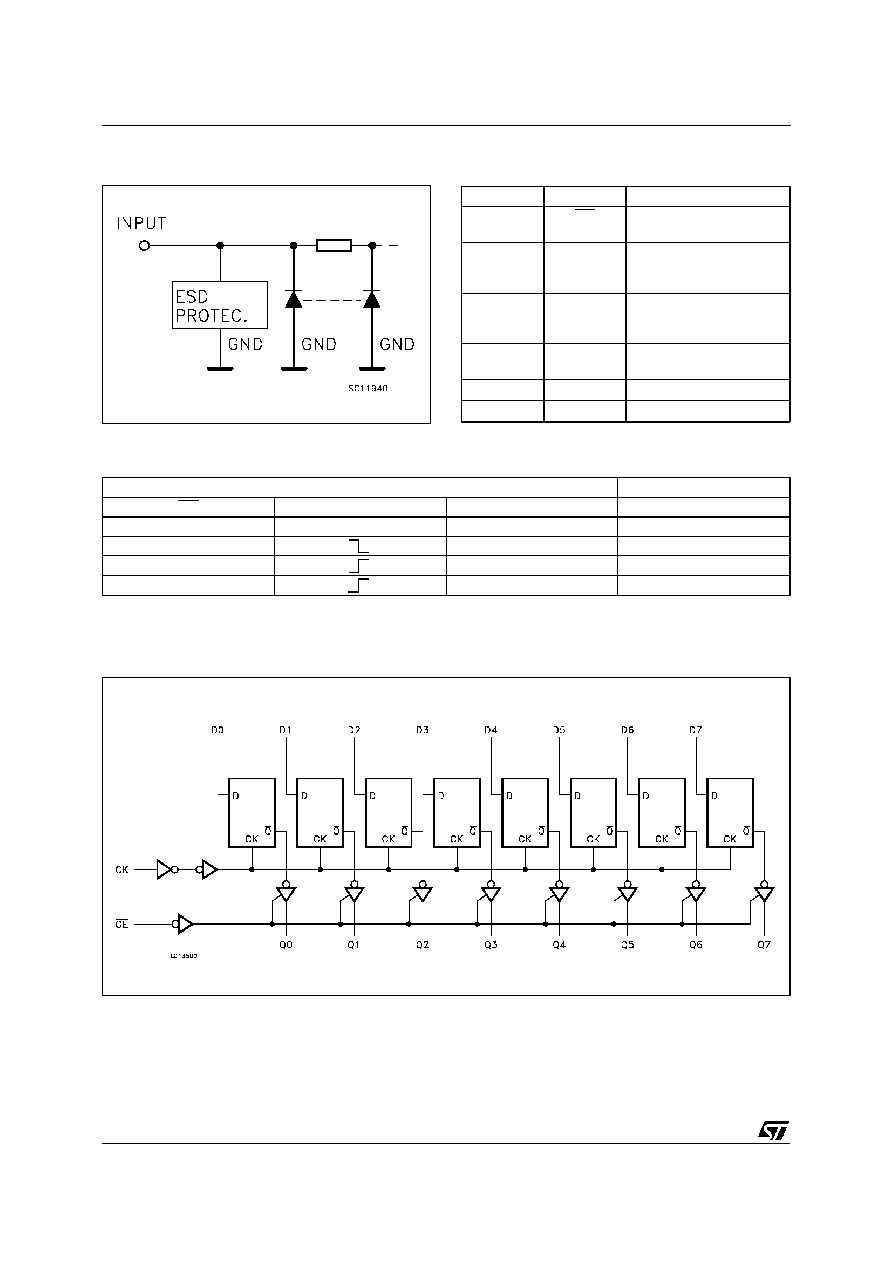

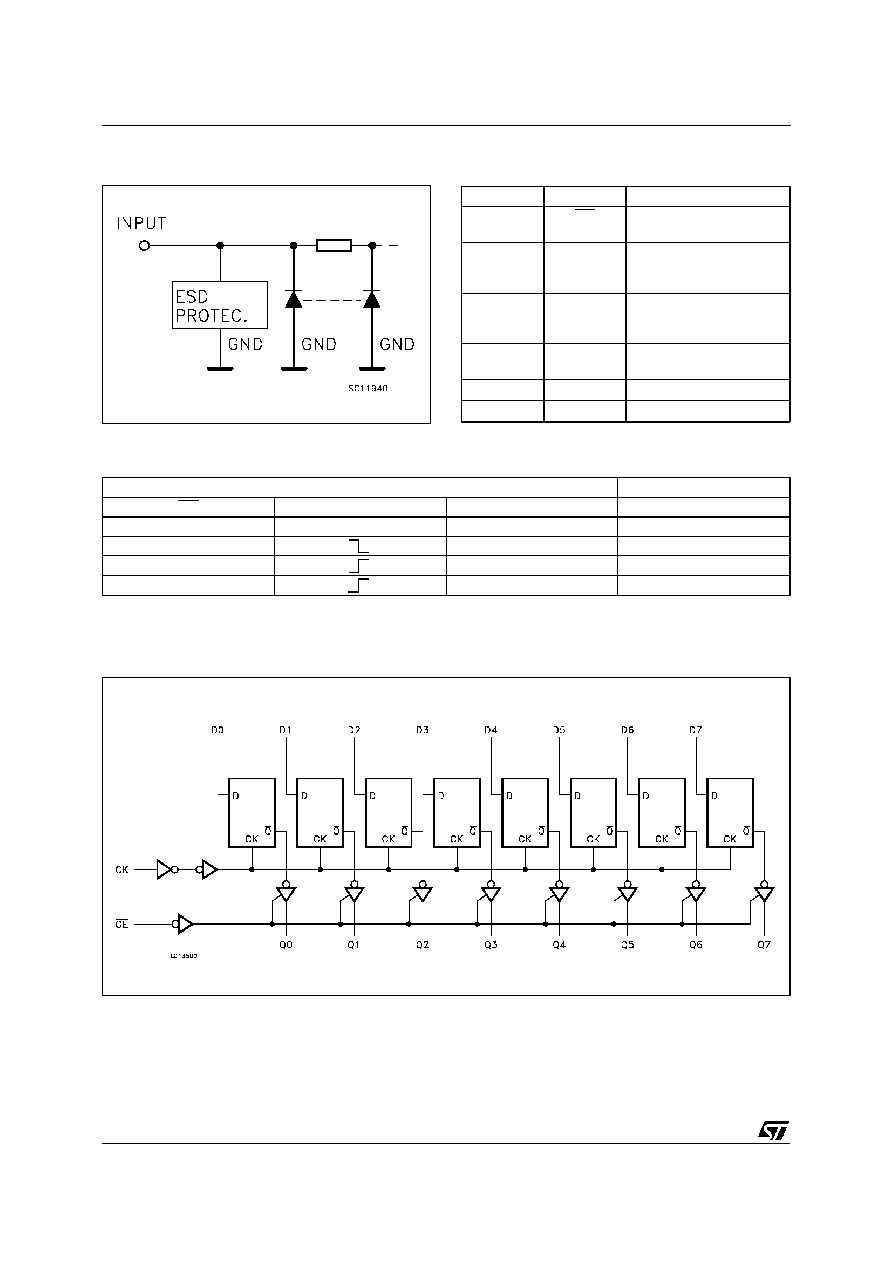

INPUT EQUIVALENT CIRCUIT

PIN DESCRIPTION

PI N No

SYMBOL

NAME AND FUNCT ION

1

OE

3 State Output Enable

Input (Active LOW)

2, 5, 6, 9,

12, 15, 16,

19

Q0 to Q7

3 State Outputs

3, 4, 7, 8,

13, 14, 17,

18

D0 to D7

Data Inputs

11

CLOCK

Clock Input (LOW to

HIGH, edge triggered)

10

GND

Ground (0V)

20

V

CC

Positive Supply Voltage

TRUTH TABLE

INPUTS

OUT PUTS

OE

CK

D

Q

H

X

X

Z

L

X

NO CHANGE

L

L

L

L

H

H

X:Don't care

Z: High impedance

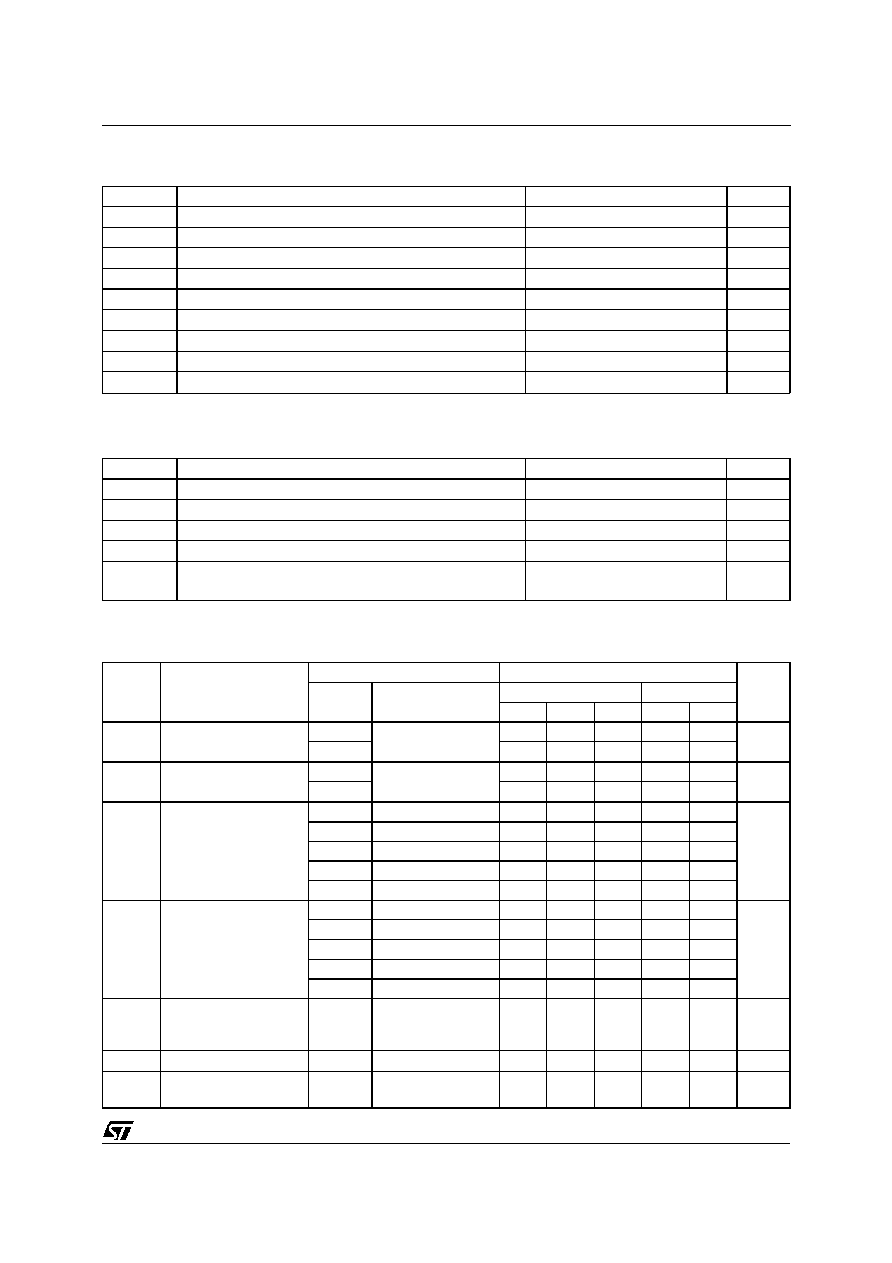

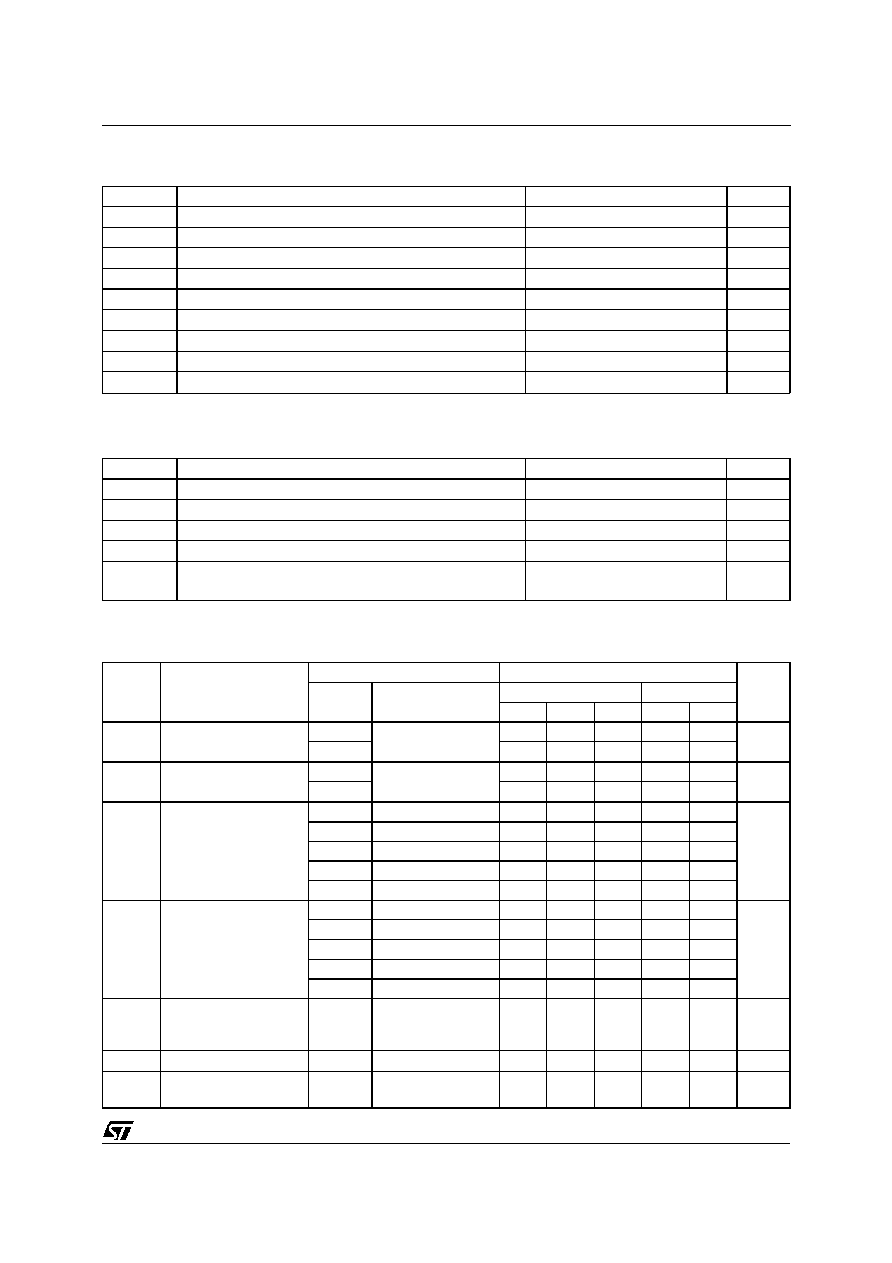

LOGIC DIAGRAM

74VHC374

2/10

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Val ue

Unit

V

CC

Supply Voltage

-0.5 to +7.0

V

V

I

DC Input Voltage

-0.5 to +7.0

V

V

O

DC Output Voltage

-0.5 to V

CC

+ 0.5

V

I

IK

DC Input Diode Current

- 20

mA

I

OK

DC Output Diode Current

±

20

mA

I

O

DC Output Current

±

25

mA

I

CC

or I

GND

DC V

CC

or Ground Current

±

75

mA

T

stg

Storage Temperature

-65 to +150

o

C

T

L

Lead Temperature (10 sec)

300

o

C

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

RECOMMENDED OPERATING CONDITIONS

Symbol

Parameter

Valu e

Uni t

V

CC

Supply Voltage

2.0 to 5.5

V

V

I

Input Voltage

0 to 5.5

V

V

O

Output Voltage

0 to V

CC

V

T

op

Operating Temperature

-40 to +85

o

C

dt/dv

Input Rise and Fall Time (see note 1) (V

CC

= 3.3

±

0.3V)

(V

CC

= 5.0

±

0.5V)

0 to 100

0 to 20

ns/V

ns/V

1) V

IN

from 30% to70%of V

CC

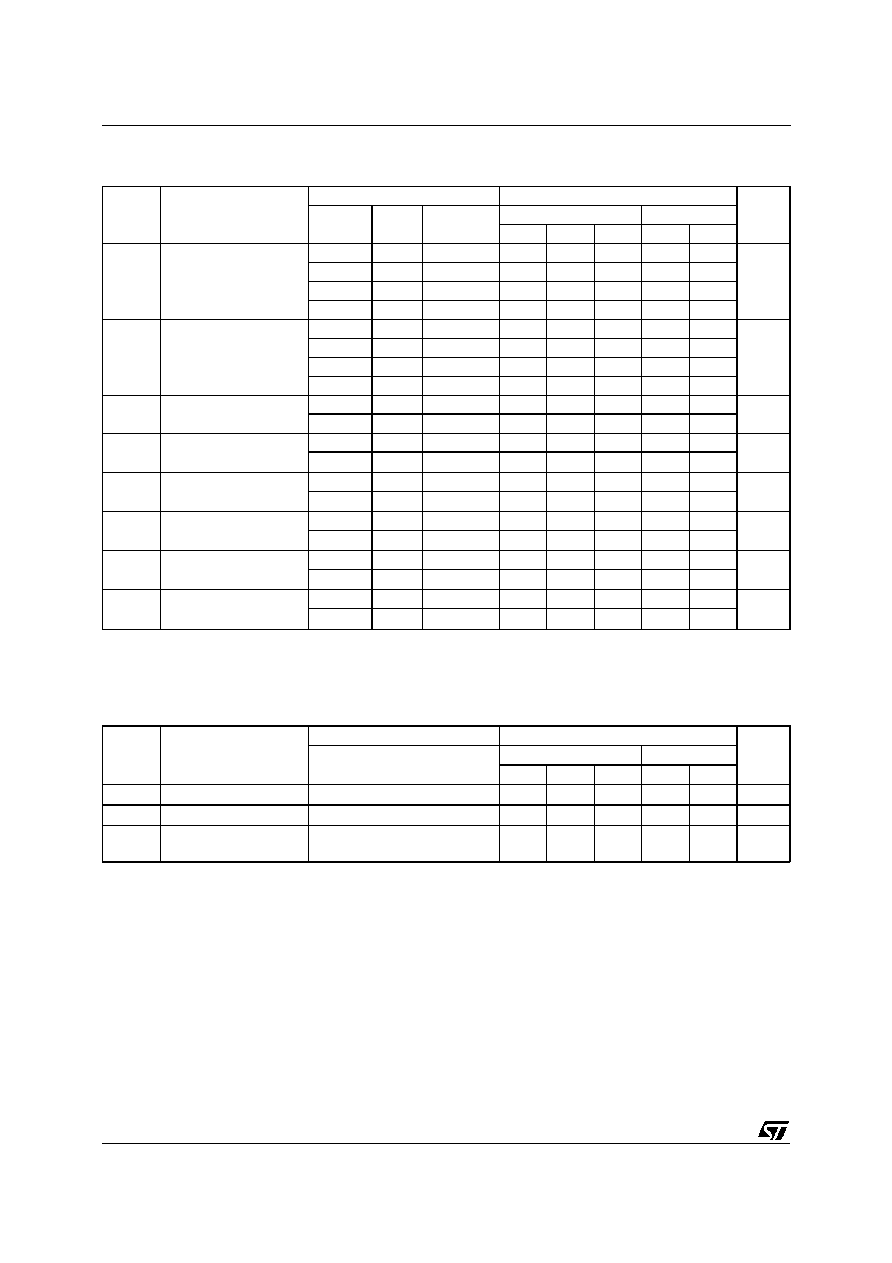

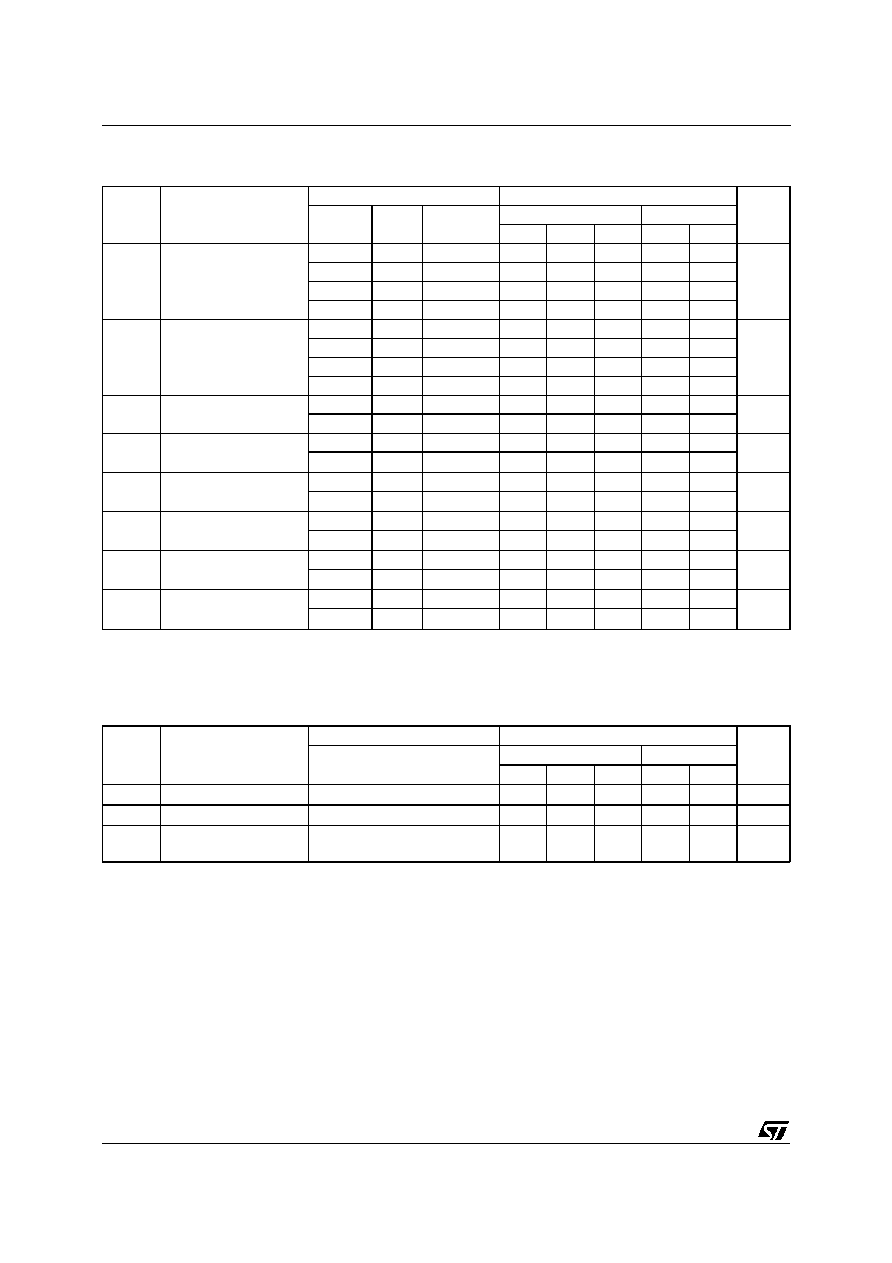

DC SPECIFICATIONS

Symb ol

Parameter

T est Cond ition s

Val ue

Un it

V

CC

(V)

T

A

= 25

o

C

-40 to 85

o

C

Min.

Typ .

Max.

Min .

Max.

V

IH

High Level Input

Voltage

2.0

1.5

1.5

V

3.0 to 5.5

0.7V

CC

0.7V

CC

V

IL

Low Level Input

Voltage

2.0

0.5

0.5

V

3.0 to 5.5

0.3V

CC

0.3V

CC

V

OH

High Level Output

Voltage

2.0

I

O

=-50

µ

A

1.9

2.0

1.9

V

3.0

I

O

=-50

µ

A

2.9

3.0

2.9

4.5

I

O

=-50

µ

A

4.4

4.5

4.4

3.0

I

O

=-4 mA

2.58

2.48

4.5

I

O

=-8 mA

3.94

3.8

V

OL

Low Level Output

Voltage

2.0

I

O

=50

µ

A

0.0

0.1

0.1

V

3.0

I

O

=50

µ

A

0.0

0.1

0.1

4.5

I

O

=50

µ

A

0.0

0.1

0.1

3.0

I

O

=4 mA

0.36

0.44

4.5

I

O

=8 mA

0.36

0.44

I

OZ

High Impedance

Output Leakage

Current

5.5

V

I

= V

IH

or V

IL

V

O

= V

CC

or GND

±

0.25

±

2.5

µ

A

I

I

Input Leakage Current

0 to 5.5

V

I

= 5.5V or GND

±

0.1

±

1.0

µ

A

I

CC

Quiescent Supply

Current

5.5

V

I

= V

CC

or GND

4

40

µ

A

74VHC374

3/10

CAPACITIVE CHARACTERISTICS

Symb ol

Parameter

T est Cond ition s

Val ue

Un it

T

A

= 25

o

C

-40 to 85

o

C

Min.

Typ .

Max.

Min .

Max.

C

IN

Input Capacitance

4

10

10

pF

C

OUT

Output Capacitance

6

pF

C

PD

Power Dissipation

Capacitance (note 1)

32

pF

1) C

PD

isdefined as the value of the IC'sinternal equivalent capacitance which is calculated fromthe operating current consumption without load. (Referto

Test Circuit).Average operating current can be obtained by the following equation. I

CC

(opr) = C

PD

∑

V

CC

∑

f

IN

+ I

CC

/8 (per Flip-Flop)

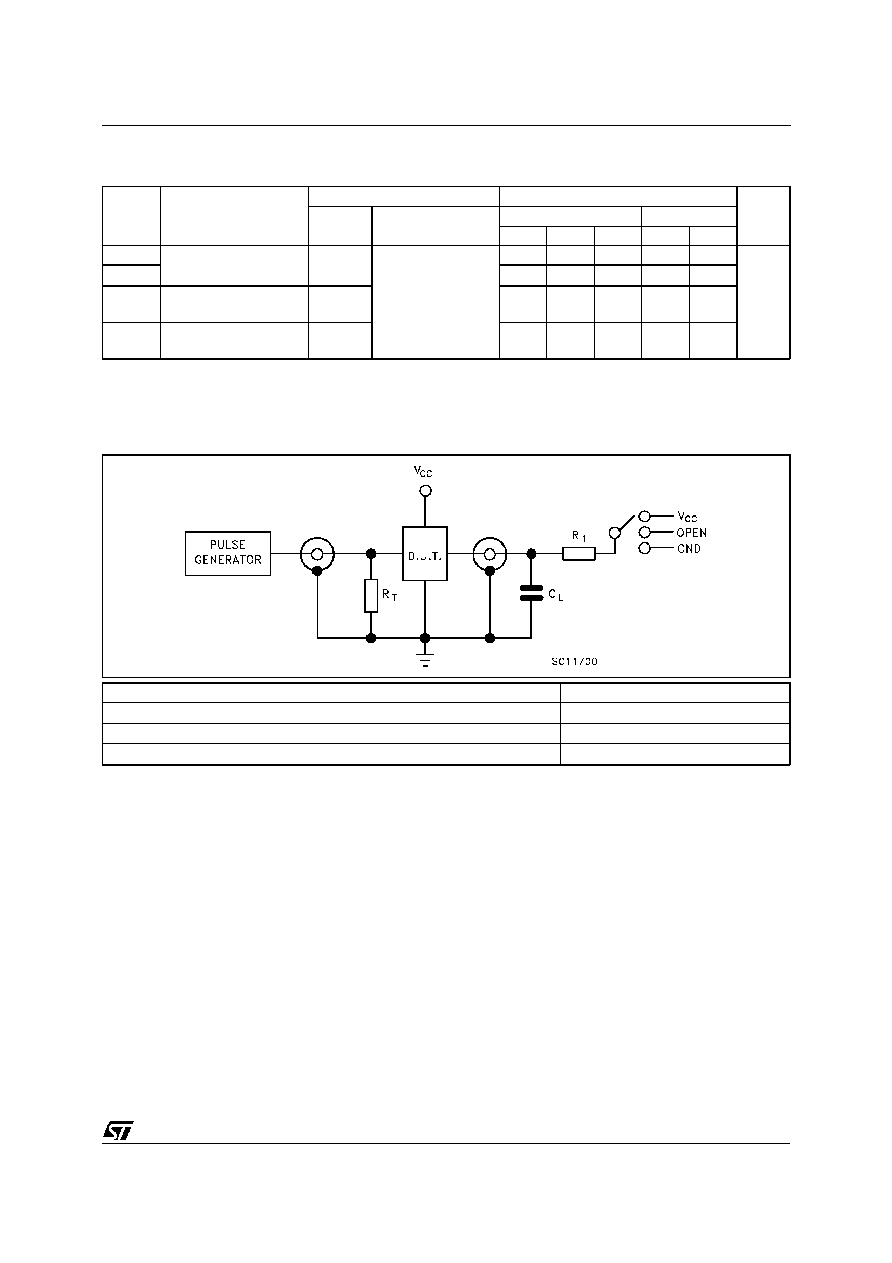

AC ELECTRICAL CHARACTERISTICS (Input t

r

= t

f

=3 ns)

Symb ol

Parameter

Test Co nditi on

Val ue

Un it

V

CC

(V)

C

L

(pF )

T

A

= 25

o

C

-40 to 85

o

C

Min.

Typ .

Max.

Min .

Max.

t

PLH

t

PHL

Propagation Delay

Time

CK to Q

3.3

(*)

15

8.1

12.7

1.0

15.0

ns

3.3

(*)

50

10.6

16.2

1.0

18.5

5.0

(**)

15

5.4

8.1

1.0

9.5

5.0

(**)

50

6.9

10.1

1.0

11.5

t

PZL

t

PZH

Output EnableTime

3.3

(*)

15

R

L

= 1K

7.1

11.0

1.0

13.0

ns

3.3

(*)

50

R

L

= 1K

9.6

14.5

1.0

16.5

5.0

(**)

15

R

L

= 1K

5.1

7.6

1.0

9.0

5.0

(**)

50

R

L

= 1K

6.6

9.6

1.0

11.0

t

PLZ

t

PHZ

Output Disable Time

3.3

(*)

50

R

L

= 1K

10.2

14.0

1.0

16.0

ns

5.0

(**)

50

R

L

= 1K

6.1

8.8

1.0

10.0

t

w

Clock Pulse Width

HIGH or LOW

3.3

(*)

5.0

5.5

ns

5.0

(**)

5.0

5.0

t

s

Setup Time D to CK

HIGH or LOW

3.3

(*)

4.5

4.5

ns

5.0

(**)

3.0

3.0

t

h

Hold Time D to CK

HIGH or LOW

3.3

(*)

2.0

2.0

ns

5.0

(**)

2.0

2.0

f

MAX

Maximum Clock

Frequency

3.3

(*)

60

250

60

MHz

5.0

(**)

100

270

100

t

OSLH

t

OSHL

Output to Output Skew

Time (note 1)

3.3

(*)

50

1.5

1.5

ns

5.0

(**)

50

1.0

1.0

(*) Voltage range is 3.3V

±

0.3V

(**) Voltage range is 5V

±

0.5V

Note 1: Parameter guaranteed by design. t

soLH

= |t

pLHm

- t

pLHn

|, t

soHL

= |t

pHLm

- t

pHLn

|

74VHC374

4/10

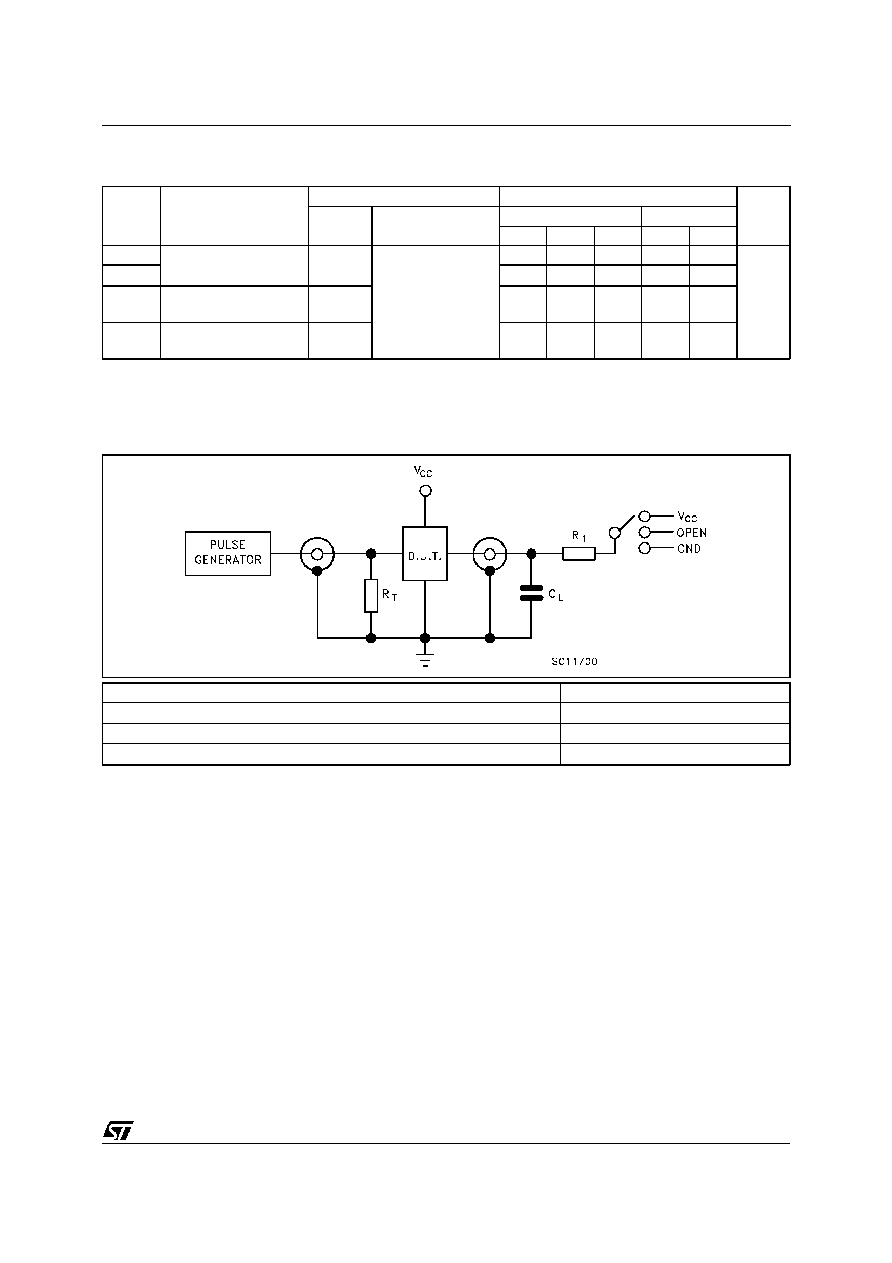

DYNAMIC SWITCHING CHARACTERISTICS

Symb ol

Parameter

T est Cond ition s

Val ue

Un it

V

CC

(V)

T

A

= 25

o

C

-40 to 85

o

C

Min.

Typ .

Max.

Min .

Max.

V

OLP

Dynamic Low Voltage

Quiet Output (note 1, 2)

5.0

C

L

= 50 pF

0.6

0.9

V

V

OLV

-0.9

-0.6

V

IHD

Dynamic High Voltage

Input (note 1, 3)

5.0

3.5

V

IL D

Dynamic Low Voltage

Input (note 1, 3)

5.0

1.5

1) Worst case package.

2) Max number of outputs defined as (n). Data inputs are driven 0V to 5.0V, (n -1) outputs switching and one output at GND.

3) Max number of data inputs (n) switching. (n-1) switching 0V to5.0V. Inputs under test switching: 5.0V to threshold (V

ILD

), 0V to threshold (V

IHD

), f=1MHz.

TEST CIRCUIT

T EST

SW IT CH

t

PLH

, t

PHL

Open

t

PZL

, t

PLZ

V

CC

t

PZH

, t

PHZ

GND

C

L

= 15/50 pF or equivalent (includes jig and probe capacitance)

R

L

= R

1

= 1K

orequivalent

R

T

= Z

OUT

of pulse generator (typically 50

)

74VHC374

5/10