| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ACS4025 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1/8

ACS402-5SB4

Æ

October 2001 - Ed: 6B

QUAD AC LINE SWITCH ARRAY

DIP-20

s

4 high voltage AC switch array

s

Blocking voltage: V

DRM

/ V

RRM

= 500V

s

Clamping voltage: V

CL

= 600V

s

Nominal current: I

T(RMS)

= 0.2 A per switch

s

Nominal current: I

T(RMS

) = 0.4 A for the total

array

s

Switch integrated driver

s

Triggering current is sourced by the gate

s

Gate triggering current : I

GT

< 10 mA

FEATURES

The ACS402 belongs to the AC line switches array

family built around the ASDTM concept. This high

performance device includes 4 bi-directional a.c.

switches able to control an 0.2 A resistive or induc-

tive load device.

Each ACSTM switch integrates a high voltage

clamping structure to absorb the inductive turn off

energy and a gate level shifter driver to separate

the digital controller from each main switch. It is

triggered with a negative gate current flowing out

of the gate pin.

For further technical information, please refer to

AN1172 the Application note.

DESCRIPTION

s

Needs no external overvoltage protection.

s

Enables the equipment to meet IEC61000-4-5

standard.

s

Miniaturizes 4 switches in 1 package.

s

Reduces the switch component count by up to

80%.

s

Interfaces directly with the microcontroller.

s

Eliminates any stressing gate kick back on the

microcontroller.

BENEFITS

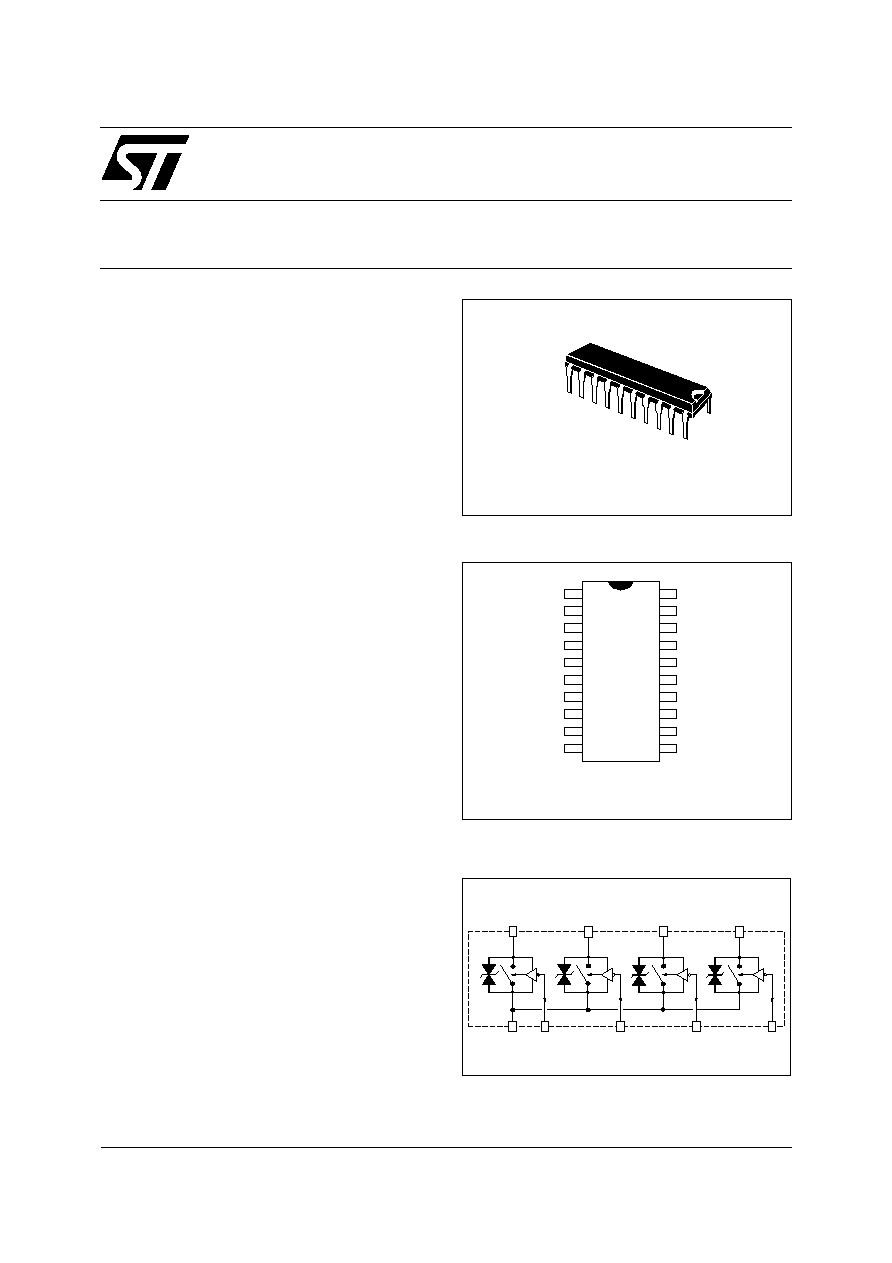

PIN OUT CONNECTION

OUT1

OUT2

OUT3

OUT4

1

G1

G2

G3

G4

COM

COM

note : pins 1, 3, 5, 7, 9, 12, 14, 16, 18, 20 not connected.

s

AC on-off static switching in appliance &

industrial control systems

s

Drive of low power high inductive or resistive

loads like:

- relay, valve, solenoid, dispenser

- pump, fan, micro-motor

- low power lamp bulb, door lock

MAIN APPLICATIONS

ASDTM

AC Switch Family

ASD and ACS are a trademarks of STMicroelectronics .

ON

G1

G2

G3

G4

Com

OUT1

OUT2

OUT3

OUT4

ON

S1

D1

S2

D2

S3

D3

S4

D4

ACS402

ON

ON

FUNCTIONAL DIAGRAM

ACS402-5SB4

2/8

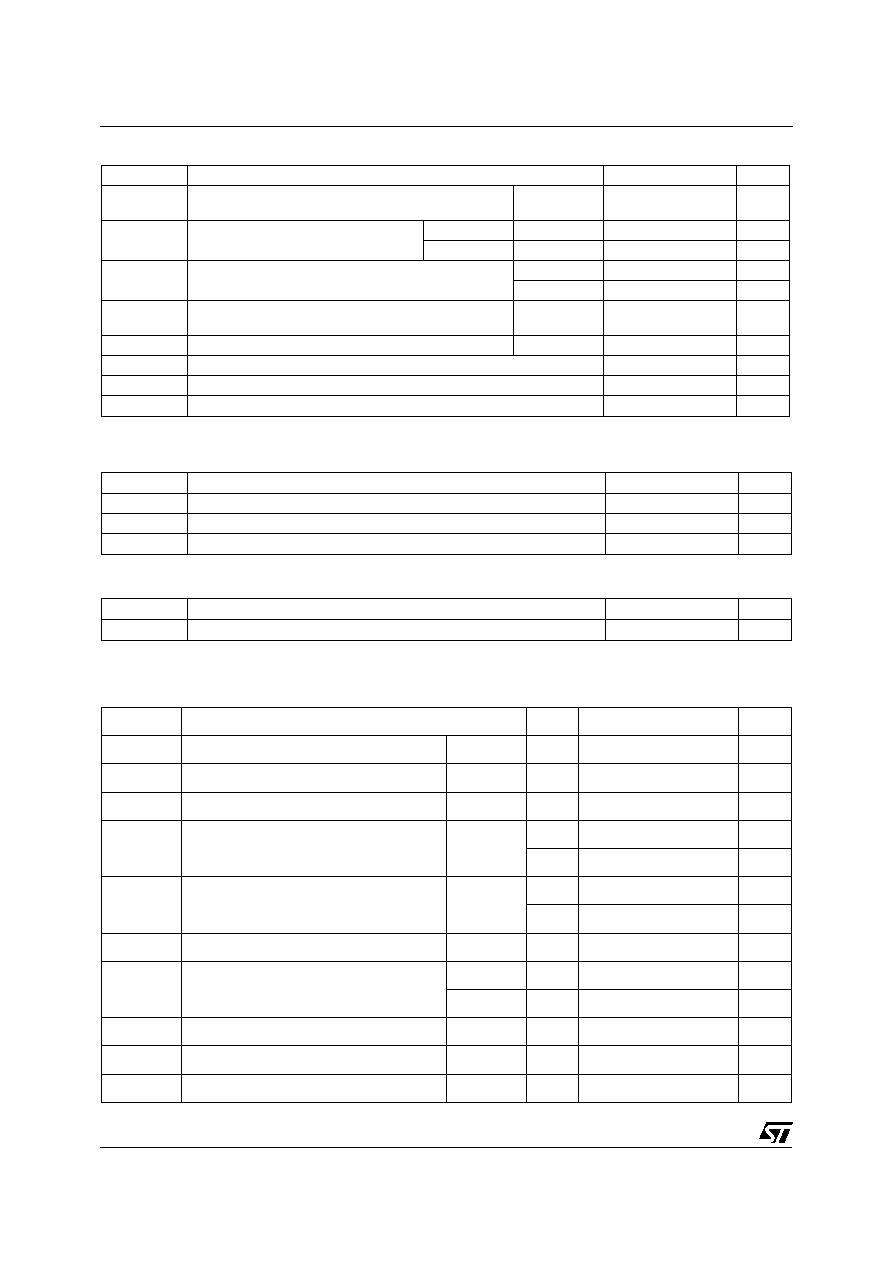

Symbol

Parameter

Value

Unit

V

DRM /

V

RRM

Repetitive peak off-state voltage

Tj = 125 ∞C

500

V

I

T(RMS)

RMS on-state current full cycle sine

wave 50 to 60 Hz

per switch

Tamb = 110 ∞C

0.2

A

total array

Tamb = 90 ∞C

0.4

A

I

TSM

Non repetitive surge peak on-state current

Tj initial = 25∞C, full cycle sine wave

F =50 Hz

5

A

F =60 Hz

5.5

A

dI/dt

Critical rate of repetitive rise of on-state current

I

G

= 20mA (tr = 100ns)

F =120 Hz

20

A/

µ

s

V

PP

Non repetitive line peak pulse voltage

note 1

2

kV

Tstg

Storage temperature range

- 40 to + 150

∞C

Tj

Operating junction temperature range

- 30 to + 125

∞C

Tl

Maximum lead temperature for soldering during 10s

260

∞C

Note 1: according to test described by IEC61000-4-5 standard & Figure 3.

ABSOLUTE RATINGS (limiting values)

Symbol

Parameter

Value

Unit

P

G (AV)

Average gate power dissipation

0.1

W

I

GM

Peak gate current (tp = 20

µ

s)

1

A

V

GM

Peak positive gate voltage (respect to the pin COM)

5

V

SWITCH GATE CHARACTERISTICS (maximum values)

Symbol

Parameter

Value

Unit

Rth (j-a)

Junction to ambient

90

∞

C/W

THERMAL RESISTANCE

Symbol

Test conditions

Values

Unit

I

GT

V

D

= 12V

R

L

= 140

Tj=25∞C

MAX.

10

mA

V

GT

V

D

= 12V

R

L

= 140

Tj=25∞C

MAX.

1

V

V

GD

V

OUT

= V

DRM

R

L

= 3.3k

Tj=125∞C

MIN.

0.15

V

I

H

I

OUT

= 100mA gate open

Tj=25∞C

TYP.

25

mA

MAX.

60

mA

I

L

I

G

= 20mA

Tj=25∞C

TYP.

30

mA

MAX.

65

mA

V

TM

I

OUT

= 0.3A

tp = 500

µ

s

Tj=25∞C

MAX.

1.1

V

I

DRM

I

RRM

V

OUT

= V

DRM

V

OUT

= V

RRM

Tj=25∞C

MAX.

2

µ

A

Tj=125∞C

MAX.

200

µ

A

dV/dt

V

OUT

= 400V gate open

Tj=110∞C

MIN.

500

V/

µ

s

(dI/dt)c

(dV/dt)c = 10V/

µ

s

Tj=110∞C

MIN.

0.1

A/ms

V

CL

I

CL

= 1mA

tp = 1ms

Tj=25∞C

TYP.

600

V

ELECTRICAL CHARACTERISTICS PER SWITCH

For either positive or negative polarity of pin OUT1, OUT2, OUT3, OUT4 voltage respect to pin COM voltage.

ACS402-5SB4

3/8

LOAD

POWER

(VA)

POWER

FACTOR

RMS LOAD

CURRENT

(A)

(dI

OUT

/dt)c

(A/ms)

(dV

OUT

/dt)c

(V/

µ

s)

Door lock Bulb

Lamp

< 40

1

< 0.2

< 0.1

< 0.15

Relay Valve

Dispenser

Micro-motor

Solenoid

< 20

> 0.7

< 0.1

< 0.05

< 2

Pump Fan

< 40

> 0.2

< 0.2

< 0.1

< 10

(*): Measured with an ACS402 switch

Table 1: Load grouping versus their turn off commutation requirement (230V AC applications).

MAINS

L

N

VALVE / DISPENSER

DOOR LOCK

RELAY

PUMP/FAN

M

G1

G2

G3

G4

COM

OUT1

OUT2

OUT3

OUT4

ACS402

PA0

ST72 MCU

PA1

PA3

PA2

Vcc

Vss

ON

ON

S1

D1

S2

D2

S3

D3

S4

D4

ON

ON

TYPICAL APPLICATION DIAGRAM

The ACS402 device is well adapted to washing machines, dishwashers, tumble driers, refrigerators, water

heaters and cookware. It has been designed especially to switch ON and OFF low power loads such as so-

lenoids, valves, relays, micro-motors, pumps, fans, door locks and low power lamp bulbs.

Pin COM:

Common drive reference to connect to the power line neutral

Pin G:

Switch Gate input to connect to the digital controller through the resistor

Pin OUT:

Switch Output to connect to the load

Each ACSTM switch is triggered with a negative gate current flowing out of the gate pin G. It can be driven

directly by the digital controller through a resistor as shown on the typical application diagram. No protec-

tion device are required between the gates and common terminals.

In appliance systems, this ACSTM switch intends to drive low power load in full cycle ON / OFF mode. The

turn off commutation characteristics of these loads can be classified in 3 groups as shown in Table 1.

Thanks to its thermal and turn-off commutation performance, each switch of the ACS402 is able to drive

an inductive or resistive load up to 0.2 A with no additional turn-off snubber.

AC LINE SWITCH BASIC APPLICATION

ACS402-5SB4

4/8

Each ACS402 switch is able to safely withstand the AC line transient voltages either by clamping the low

energy spikes or by breaking over under high energy shocks.

The test circuit in Figure 3 is representative of the final ACSTM application and is also used to stress the

ACSTM switch according to the IEC61000-4-5 standard conditions. Thanks to the load, the ACSTM switch

withstands the voltage spikes up to 2 kV above the peak line voltage. It will break over safely even on resis-

tive load where the turn-on current rise is high as shown in Figure 4. Such non repetitive test can be done

10 times on each AC line voltage polarity.

AC LINE TRANSIENT VOLTAGE RUGGEDNESS

Fig 3: Overvoltage ruggedness test circuit for resistive

and inductive loads according to IEC61000-4-5

standard.

R = 150

, L = 5

µ

H, V

PP

= 2kV.

Iout (2 A/div)

Vout (200 V/div)

dI/dt = 100 A/µs

Fig 4: Current and voltage of the ACSTM during

IEC61000-4-5 standard test with a 150

- 10

µ

H

load & V

PP

= 2kV.

Fig 1: Turn-off operation of the ACS402 switch

with an electro valve: waveform of the gate current

I

G

, pin OUT current I

OUT

& voltage V

OUT

.

T

ime (400µs/div)

I

OUT

(10 mA/div)

V

OUT

(200V/div)

I

H

V

CL

= 650V

At the end of the last conduction half-cycle, the load current reaches the holding current level I

H

, and the

ACSTM switch turns off. Because of the inductance L of the load, the current flows through the avalanche

diode D and decreases linearly to zero. During this time, the voltage across the switch is limited to the

clamping voltage V

CL

.

The energy stored in the inductance of the load depends on the holding current I

H

and the inductance (up to

10 H); it can reach about 20 mJ and is dissipated in the clamping section that is especially designed for that

purpose.

HIGH INDUCTIVE SWITCH-OFF OPERATION

Fig 2: ACS402 switch static characteristic.

I

H

V

CL

I

OUT

V

OUT

R

L

R

G

= 220

V

AC

+ V

PP

AC LINE &

SURGE VOLTAGE

GENERATOR

G

COM

OUT

ACSxx

ON

S

D

ACS402-5SB4

5/8

0.00

0.05

0.10

0.15

0.20

0.25

0.30

0.35

0.40

0.00

0.05

0.10

0.15

0.20

0.25

0.30

0.35

0.40

0.45

0.50

IT(RMS)(A)

P(W)

Fig. 5: Maximum power dissipation versus RMS

on-state current (per switch).

0

25

50

75

100

125

0.00

0.05

0.10

0.15

0.20

0.25

0.30

0.35

0.40

0.45

0.50

Tamb(∞C)

IT(RMS)(A)

4 switches ON

1 switch ON

Fig. 6:

RMS on-state current versus ambient

temperature.

1E-4

1E-3

1E-2

1E-1

1E+0

1E+1

1E+2 5E+2

1E-3

1E-2

1E-1

1E+0

tp (s)

Zth(j-a)/Rth(j-a)

1 switch

4 switches

Fig. 7: Relative variation of thermal impedance

junction to ambient versus pulse duration (device

mounted on printed circuit board FR4, e(Cu) =

35

µ

m)

-40

-20

0

20

40

60

80

100

120

140

0.0

0.5

1.0

1.5

2.0

2.5

3.0

Tj(∞C)

IGT [Tj] / IGT [Tj=25∞C]

Fig. 8: Relative variation of gate trigger current

versus junction temperature.

-40

-20

0

20

40

60

80

100

120

140

0.0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

1.8

2.0

Tj(∞C)

IH,IL [Tj] / IH,IL [Tj=25∞C]

Fig. 9: Relative variation of holding and latching

current versus junction temperature.

1

10

100

1000

0

1

2

3

4

5

6

Number of cycles

ITSM(A)

Non repetitive

Tj initial=25∞C

Tamb=25∞C

Repetitive

One cycle

t=20ms

Fig. 10: Surge peak on-state current versus

number of cycles.