| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: BU808DFP | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

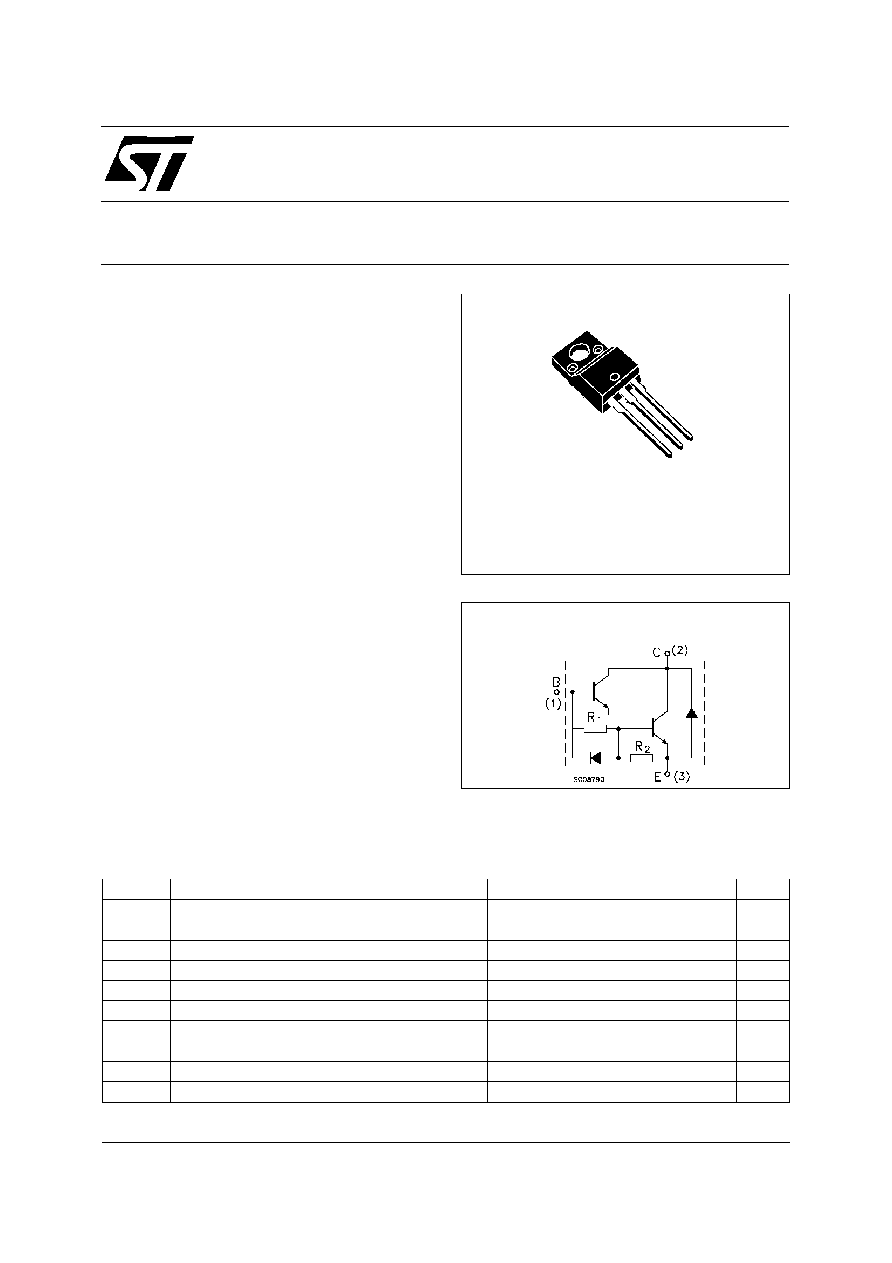

BU808DFP

HIGH VOLTAGE FAST-SWITCHING

NPN POWER DARLINGTON

s

STMicroelectronics PREFERRED

SALESTYPE

s

NPN MONOLITHIC DARLINGTON WITH

INTEGRATED FREE-WHEELING DIODE

s

HIGH VOLTAGE CAPABILITY ( > 1400 V )

s

HIGH DC CURRENT GAIN ( TYP. 150 )

s

FULLY MOLDED ISOLATED PACKAGE 2KV

DC ISOLATION (U.L. COMPLIANT)

s

LOW BASE-DRIVE REQUIREMENTS

s

DEDICATED APPLICATION NOTE AN1184

APPLICATIONS

s

COST EFFECTIVE SOLUTION FOR

HORIZONTAL DEFLECTION IN LOW END

TV UP TO 21 INCHES.

DESCRIPTION

The BU808DFP is a NPN transistor in monolithic

Darlington configuration. It is manufactured using

Multiepitaxial Mesa technology for cost-effective

high performance.

Æ

INTERNAL SCHEMATIC DIAGRAM

June 2000

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Val ue

Uni t

V

CBO

Collector-Base Voltage (I

E

= 0)

1400

V

V

CEO

Collector-Emit ter Volt age (I

B

= 0)

700

V

V

EBO

Emitt er-Base Voltage (I

C

= 0)

5

V

I

C

Collector Current

8

A

I

CM

Collector Peak Current (t

p

< 5 ms)

10

A

I

B

Base Current

3

A

I

BM

Base Peak Current (t

p

< 5 ms)

6

A

P

t ot

Tot al Dissipation at T

c

= 25

o

C

42

W

T

stg

St orage Temperature

-65 to 150

o

C

T

j

Max. Operat ing Junction Temperat ure

150

o

C

1

2

3

TO-220FP

1/7

THERMAL DATA

R

t hj-ca se

Thermal Resistance Junction-case

Max

2.98

o

C/W

ELECTRICAL CHARACTERISTICS (T

case

= 25

o

C unless otherwise specified)

Symb ol

Parameter

Test Cond ition s

Mi n.

Typ .

Max.

Un it

I

CES

Collector Cut -of f

Current (V

BE

= 0)

V

CE

= 1400 V

400

µ

A

I

EBO

Emitt er Cut -of f Current

(I

C

= 0)

V

EB

= 5 V

100

mA

V

CE(sat )

Collector-Emit ter

Saturation Voltage

I

C

= 5 A

I

B

= 0. 5 A

1.6

V

V

BE(s at)

Base-Emitt er

Saturation Voltage

I

C

= 5 A

I

B

= 0. 5 A

2.1

V

h

F E

DC Current Gain

I

C

= 5 A

V

CE

= 5 V

I

C

= 5 A

V

CE

= 5 V

T

j

= 100

o

C

60

20

230

t

s

t

f

INDUCTIVE LO AD

St orage Time

Fall Time

V

CC

= 150 V

I

C

= 5 A

I

B1

= 0.5 A

V

BEoff

= -5 V

3

0.8

µ

s

µ

s

t

s

t

f

INDUCTIVE LO AD

St orage Time

Fall Time

V

CC

= 150 V

I

C

= 5 A

I

B1

= 0.5 A

V

BEoff

= -5 V

T

j

= 100

o

C

2

0.8

µ

s

µ

s

V

F

Diode F orward Voltage

I

F

= 5 A

3

V

Pulsed: Pulse duration = 300

µ

s, duty cycle 1.5 %

Safe Operating Area

Thermal Impedance

BU808DFP

2/7

Derating Curve

Collector Emitter Saturation Voltage

Power Losses at 16 KHz

DC Current Gain

Base Emitter Saturation Voltage

Switching Time Inductive Load at 16KHz

BU808DFP

3/7

Switching Time Inductive Load at 16KHZ

Reverse Biased SOA

BASE DRIVE INFORMATION

In order to saturate the power switch and reduce

conduction losses, adequate direct base current

I

B1

has to be provided for the lowest gain h

FE

at

100

o

C (line scan phase). On the other hand,

negative base current I

B2

must be provided to

turn off the power transistor (retrace phase).

Most

of

the

dissipation,

in

the

deflection

application, occurs at switch-off. Therefore it is

essential to determine the value of I

B2

which

minimizes

power

losses,

fall

time

t

f

and,

consequently, T

j

. A new set of curves have been

defined to give total power losses, t

s

and t

f

as a

function of

I

B2

at both

16 KHz scanning

frequencies for choosing the optimum negative

drive. The test circuit is illustrated in figure 1.

Inductance L

1

serves to control the slope of the

negative base current I

B2

to recombine the

excess carrier in the collector when base current

is still present, this would avoid any tailing

phenomenon in the collector current.

The values of L and C are calculated from the

following equations:

1

2

L

(

I

C

)

2

=

1

2

C

(

V

CEfly

)

2

=

2

f

=

1

L

C

Where I

C

= operating collector current, V

CEfly

=

flyback voltage, f= frequency of oscillation during

retrace.

BU808DFP

4/7

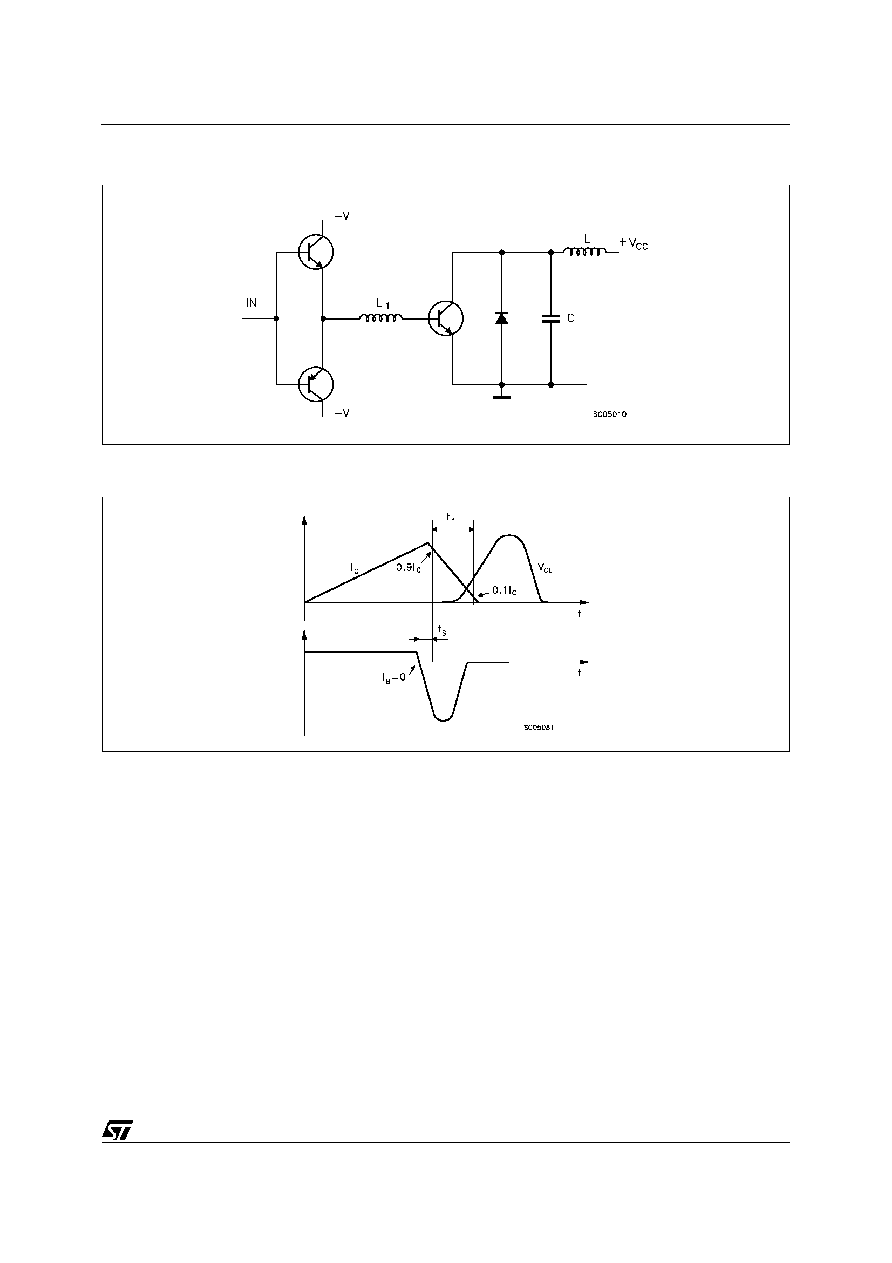

Figure 1: Inductive Load Switching Test Circuits.

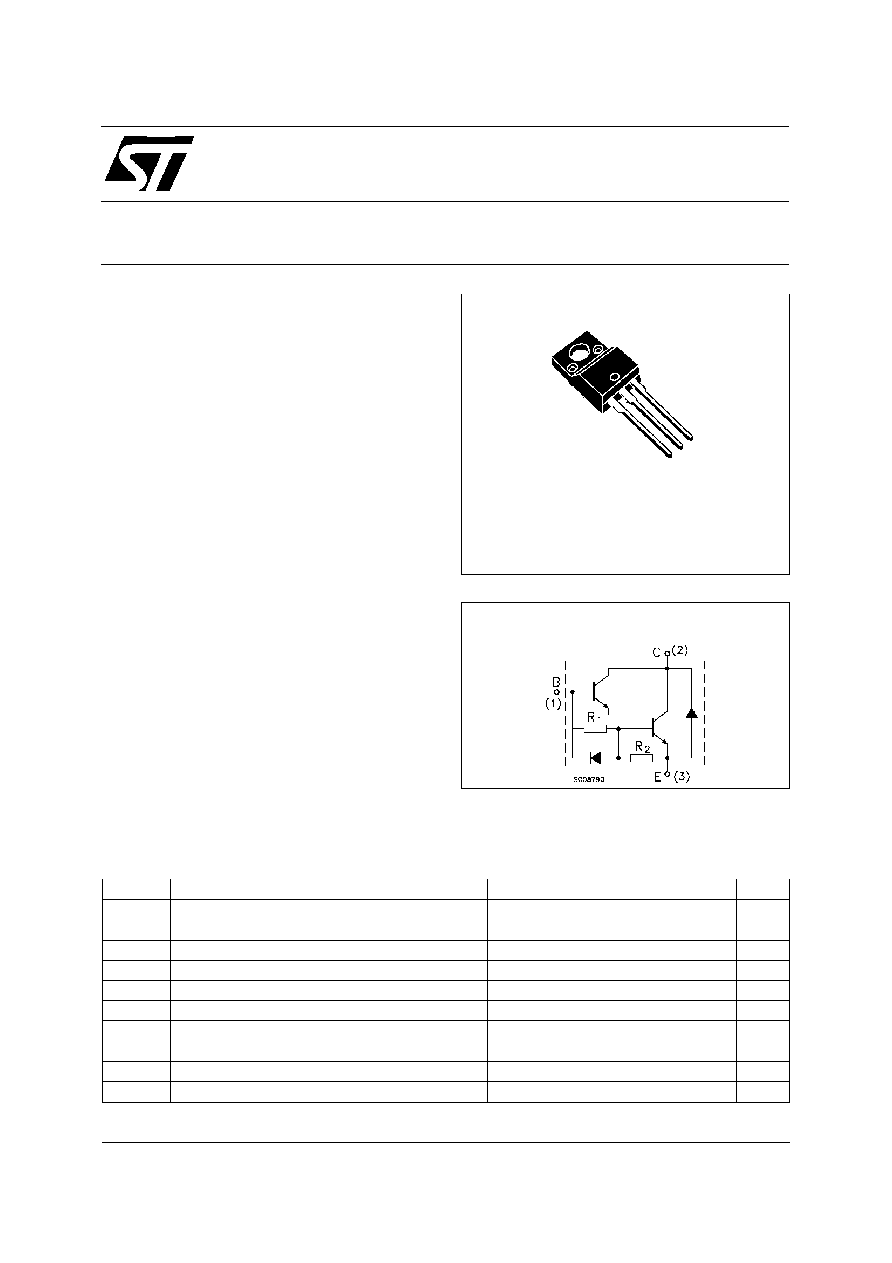

Figure 2: Switching Waveforms in a Deflection Circuit

BU808DFP

5/7