| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: L6258 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

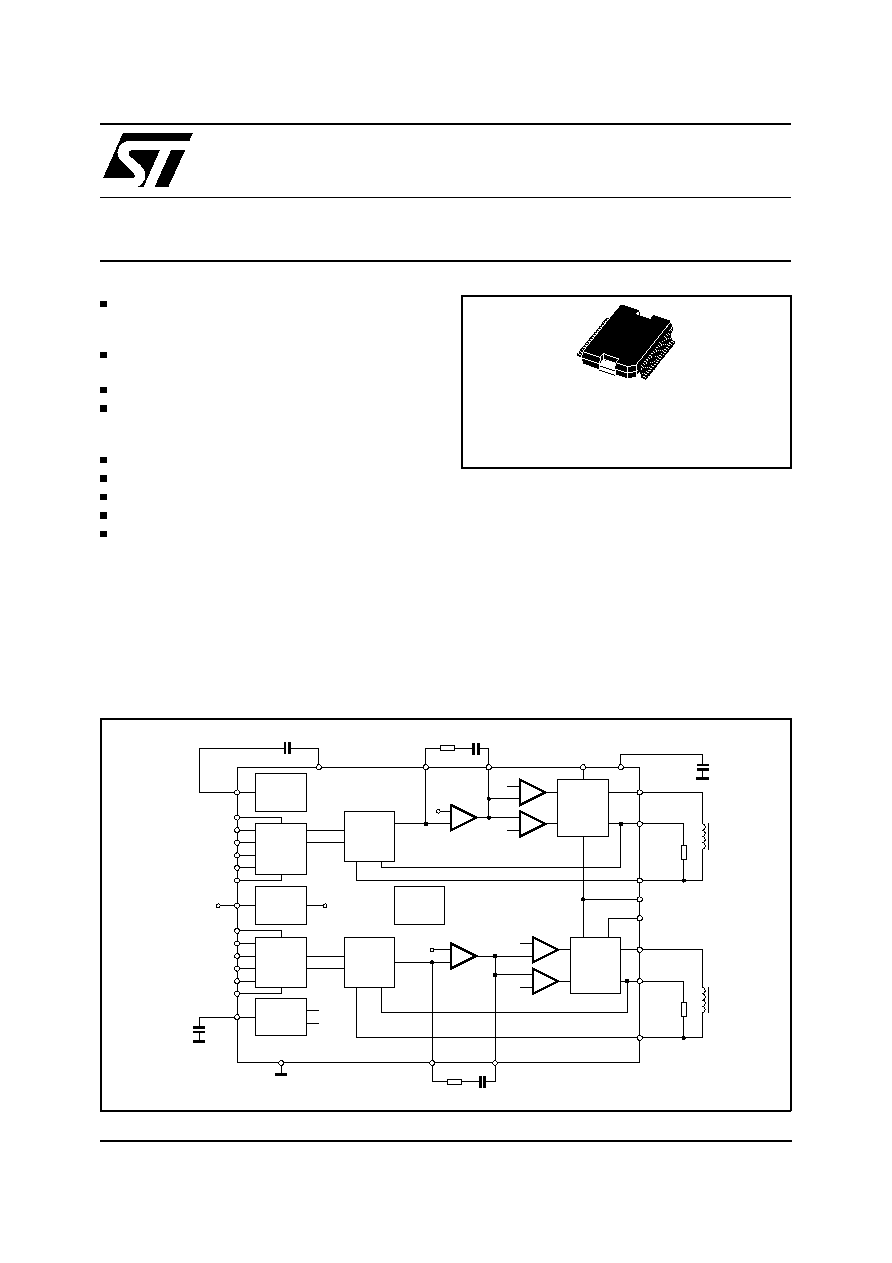

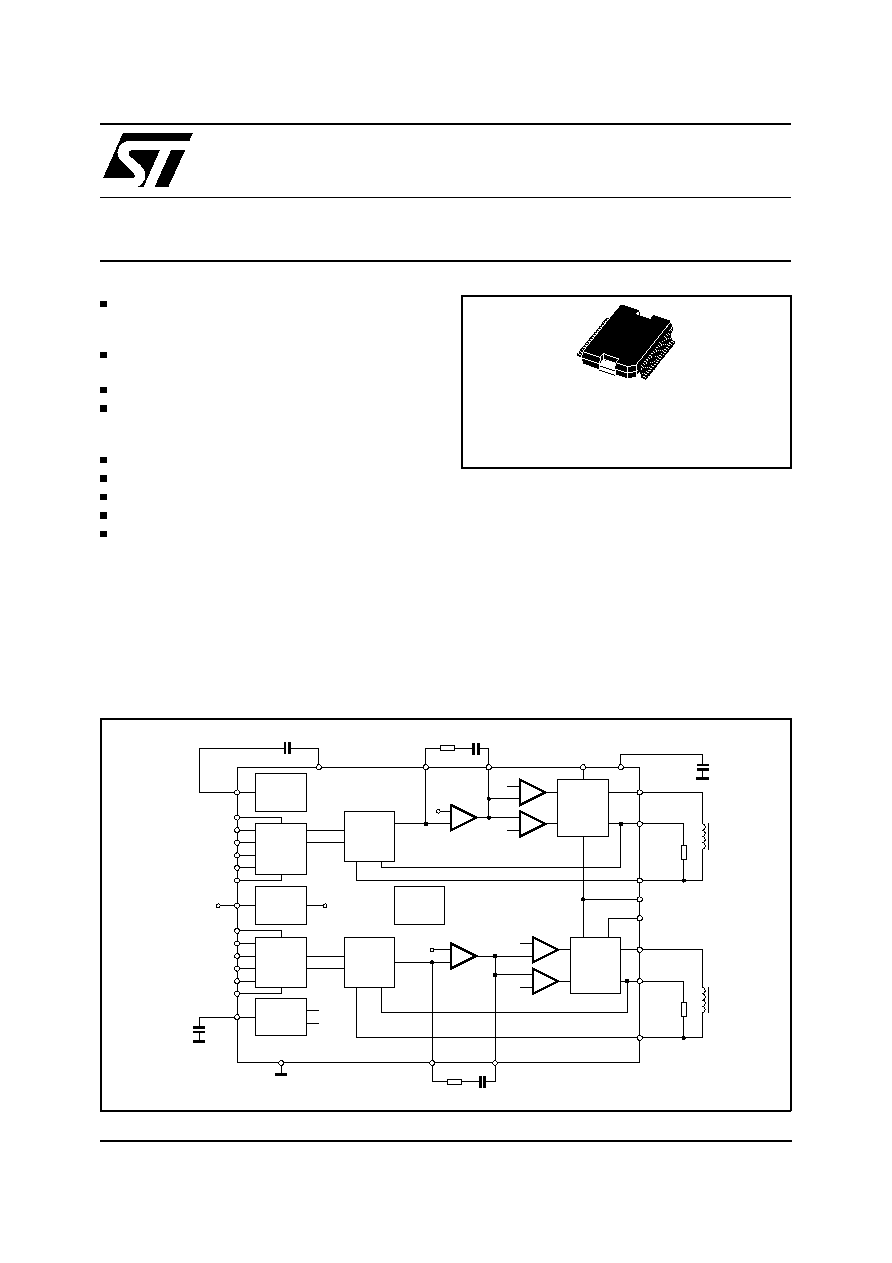

L6258

PWM CONTROLLED - HIGH CURRENT

DMOS UNIVERSAL MOTOR DRIVER

PRELIMINARY DATA

ABLE TO DRIVE BOTH WINDINGS OF A BI-

POLAR STEPPER MOTOR OR TWO DC MO-

TORS

OUTPUT CURRENT UP TO 1.5A EACH

WINDING

WIDE VOLTAGE RANGE: 12V TO 45V

FOUR QUADRANT CURRENT CONTROL,

IDEAL FOR MICROSTEPPING AND DC MO-

TOR CONTROL

PRECISION PWM CONTROL

NO NEED FOR RECIRCULATION DIODES

TTL/CMOS COMPATIBLE INPUTS

CROSS CONDUCTION PROTECTION

THERMAL SHUTDOWN

DESCRIPTION

L6258 is a dual full bridge for motor control appli-

cations realized in BCD technology, with the ca-

pability of driving both windings of a bipolar step-

per motor or bidirectionally control two DC

motors.

L6258 and a few external components form a

complete control and drive circuit. It has high effi-

ciency phase shift chopping that allows a very low

current ripple at the lowest current control levels,

and makes this device ideal for steppers as well

as for DC motors.

The power stage is a dual DMOS full bridge capa-

ble of sustaining up to 45V, and includes the di-

odes for current recirculation.

The output current capability is 1.5A per winding

in continuous mode, with peak start-up current up

to 2A.

A thermal protection circuitry disables the outputs

if the chip temperature exceeds the safe limits.

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

April 2000

Æ

DAC

CHARGE

PUMP

V

R

(V

DD

/2)

VCP1

PH_1

I0_1

I1_1

I2_1

VREF1

TRIANGLE

GENERATOR

TRI_CAP

ERROR

AMP

+

-

V

R

+

-

+

-

C

C

POWER

BRIDGE

1

TRI_0

TRI_180

TRI_180

TRI_0

DAC

PH_2

I0_2

I1_2

I2_2

VREF1

ERROR

AMP

+

-

V

R

+

-

+

-

C

C

POWER

BRIDGE

2

TRI_0

TRI_180

THERMAL

PROT.

OUT1A

OUT1B

R

s

SENSE1A

VBOOT

DISABLE

VS

OUT2A

OUT2B

SENSE2A

R

s

VS

EA_IN1

EA_OUT1

GND

EA_IN2

EA_OUT2

VCP2

V

DD

(5V)

D96IN430D

VR GEN

INPUT

&

SENSE

AMP

C

P

C

FREF

C

BOOT

INPUT

&

SENSE

AMP

I3_1

I3_2

SENSE1B

SENSE2B

R

C2

R

C1

C

C1

C

C2

BLOCK DIAGRAM

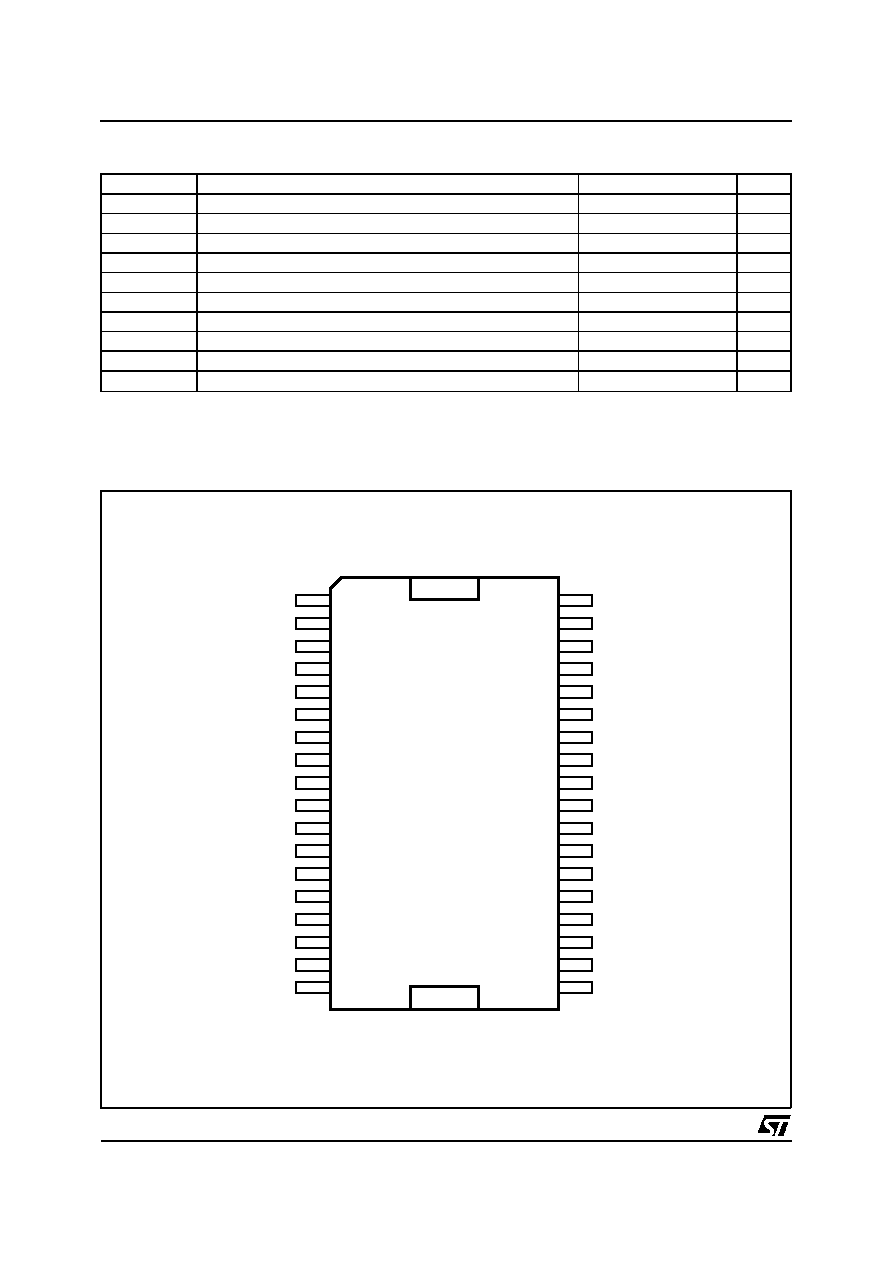

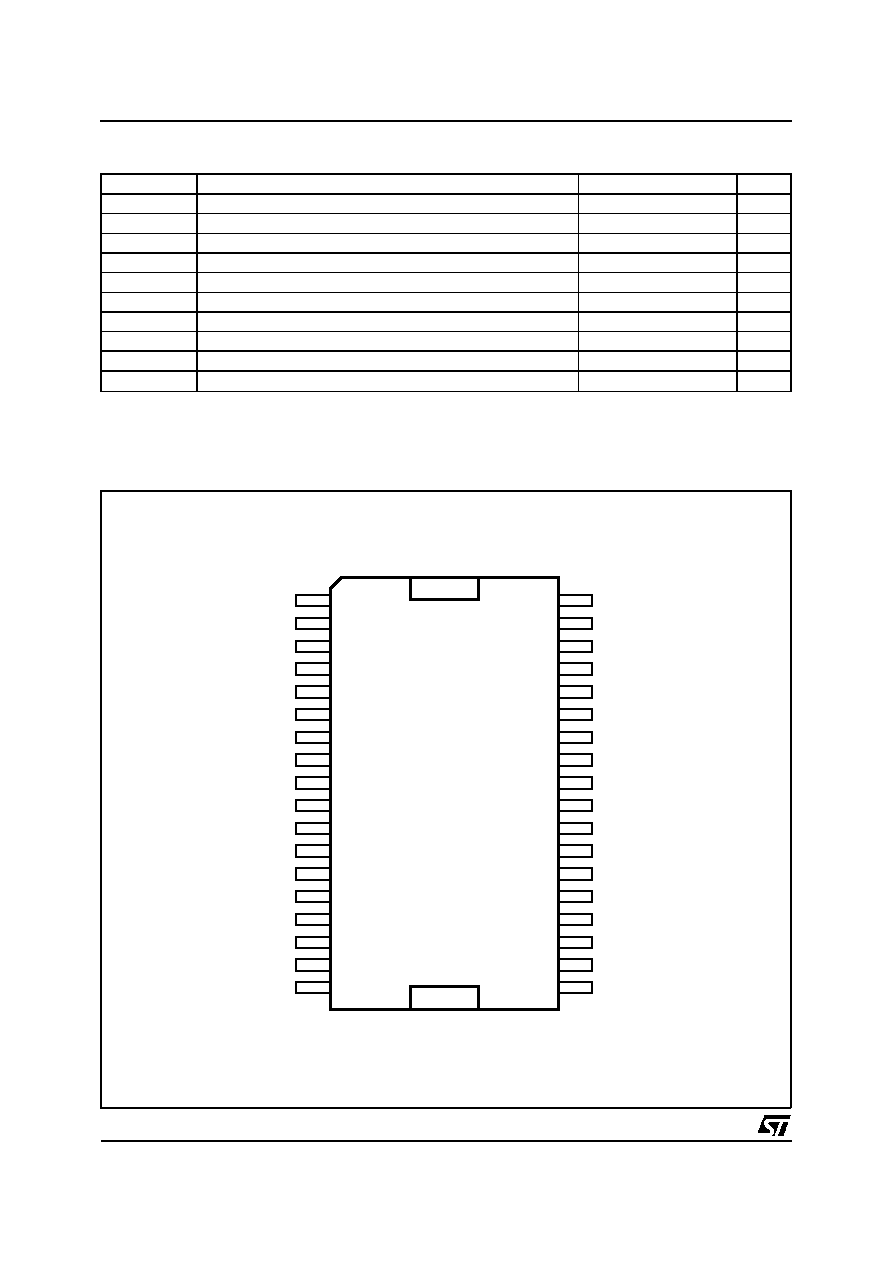

ORDERING NUMBER: L6258

PowerSO36

1/18

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Unit

Vs

Supply Voltage

50

V

V

CC

Logic Supply Voltage

7

V

V

ref1

/V

ref2

Reference Voltage

2.5

V

I

O

Output Current (peak)

2

A

I

O

Output Current (continuous)

1.5

A

V

in

Logic Input Voltage Range

-0.3 to 7

V

V

boot

Bootstrap Supply

60

V

V

boot -

V

s

Maximum Vgate applicable

15

V

T

j

Junction Temperature

150

∞C

T

stg

Storage Temperature Range

-55 to 150

∞C

PWR_GND

PH_2

EA_IN2

EA_OUT2

DISABLE

EA_OUT1

OUT1A

EA_IN1

PH_1

SENSE1

OUT1B

I3_1

VS

I2_1

I3_2

OUT2B

SENSE2

PWR_GND

18

16

17

15

6

5

4

3

2

21

22

31

32

33

35

34

36

20

1

19

PWR_GND

PWR_GND

D96IN432E

GND

TRI_CAP

V

CC

I0_1

VREF1

I1_1

9

8

7

28

29

30

VCP1

SIG_GND

10

27

OUT2A

VCP2

VBOOT

VREF2

I2_2

I0_2

14

12

11

23

25

26

VS

I1_2

13

24

PIN CONNECTION (Top view)

L6258

2/18

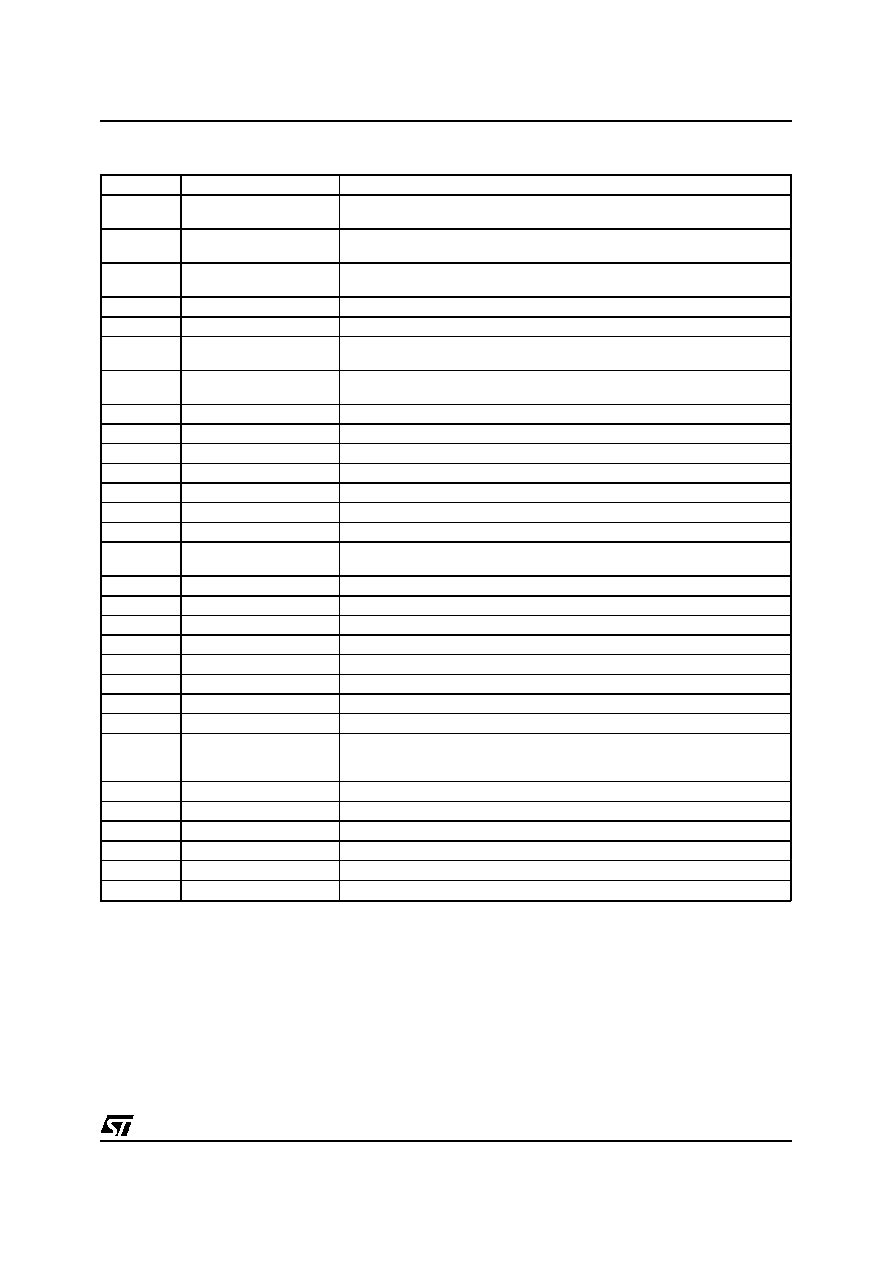

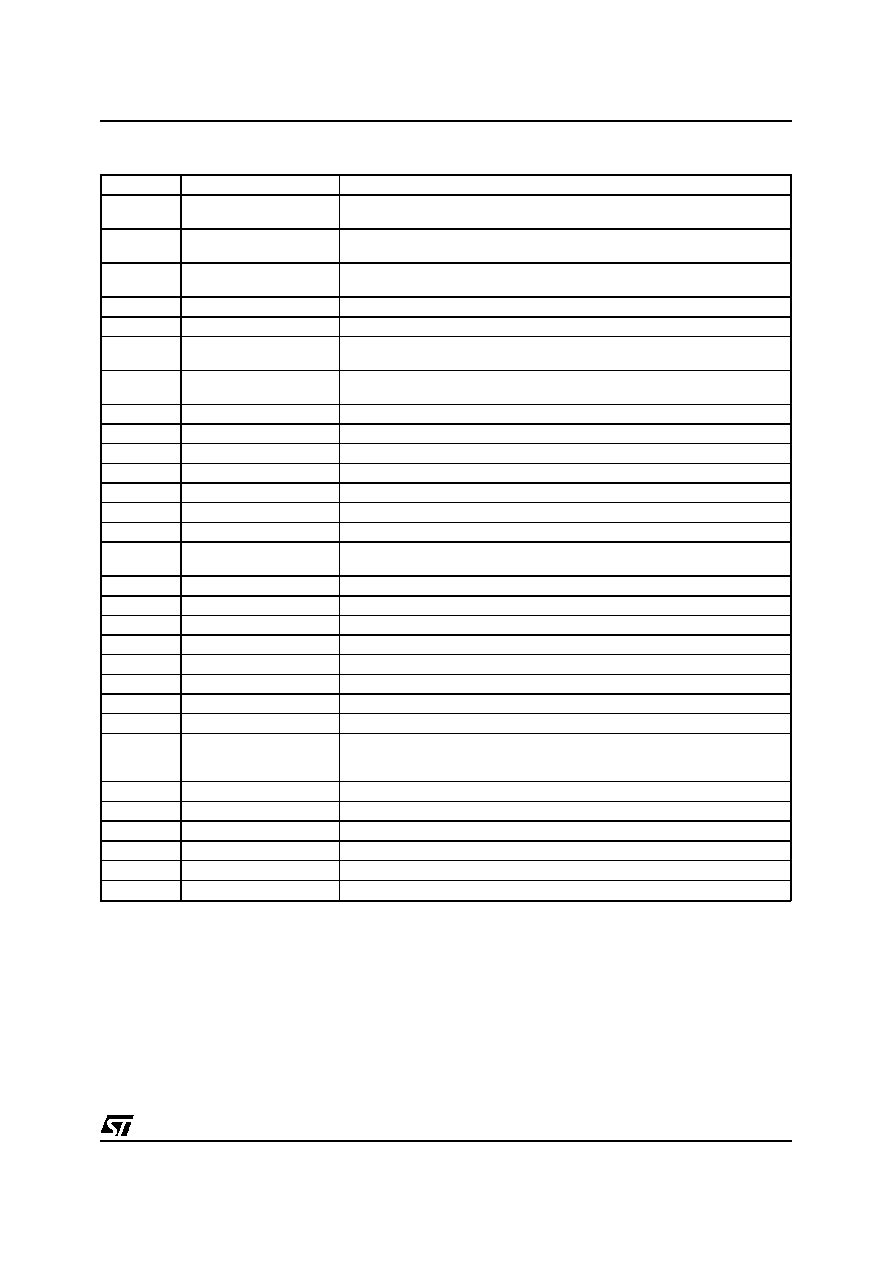

PIN FUNCTIONS

Pin #

Name

Description

1, 36

PWR_GND

Ground connection (1). They also conduct heat from die to printed circuit

copper.

2, 17

PH_1, PH_2

These TTL compatible logic inputs set the direction of current flow through

the load. A high level causes current to flow from OUTPUT A to OUTPUT B.

3

I

1_1

Logic input of the internal DAC (1). The output voltage of the DAC is a

percentage of the Vref voltage applied according to the thruth table of page 7

4

I

0_1

See pin 3

5

OUT1A

Bridge output connection (1)

6

DISABLE

Disables the bridges for additional safety during switching. When not

connected the bridges are enabled

7

TRI_cap

Triangular wave generation circuit capacitor. The value of this capacitor

defines the output switching frequency

8

V

CC

(5V)

Supply Voltage Input for logic circuitry

9

GND

Power Ground connection of the internal charge pump circuit

10

V

CP1

Charge pump oscillator output

11

V

CP2

Input for external charge pump capacitor

12

V

BOOT

Overvoltage input for driving of the upper DMOS

13, 31

V

S

Supply voltage input for output stage. They are shorted internally

14

OUT2A

Bridge output connection (2)

15

I

0_2

Logic input of the internal DAC (2). The output voltage of the DAC is a

percentage of the VRef voltage applied according to the truth table of page 7

16

I

1_2

See pin 15

18, 19

PWR_GND

Ground connection. They also conduct heat from die to printed circuit copper

20, 35

SENSE2, SENSE1

Negative input of the transconductance input amplifier (2, 1)

21

OUT2B

Bridge output connection and positive input of the tranconductance (2)

22

I

1_3

See pin 15

23

I

2_2

See pin 15

24

EA_OUT_2

Error amplifier output (2)

25

EA_IN_2

Negative input of error amplifier (2)

26, 28

V

REF2

, V

REF1

Reference voltages for the internal DACs, determining the output current

value. Output current also depends on the logic inputs of the DAC and on

the sensing resistor value

27

SIG_GND

Signal ground connection

29

EA_IN_1

Negative input of error amplifier (1)

30

EA_OUT_1

Error amplifier output (1)

32

I

2_1

See pin 3

33

I

3_1

See pin 3

34

OUT1B

Bridge output connection and positive input of the tranconductance (1)

Note: The number in parenthesis shows the relevant Power Bridge of the circuit. Pins 18, 19, 1 and 36 are connected together.

L6258

3/18

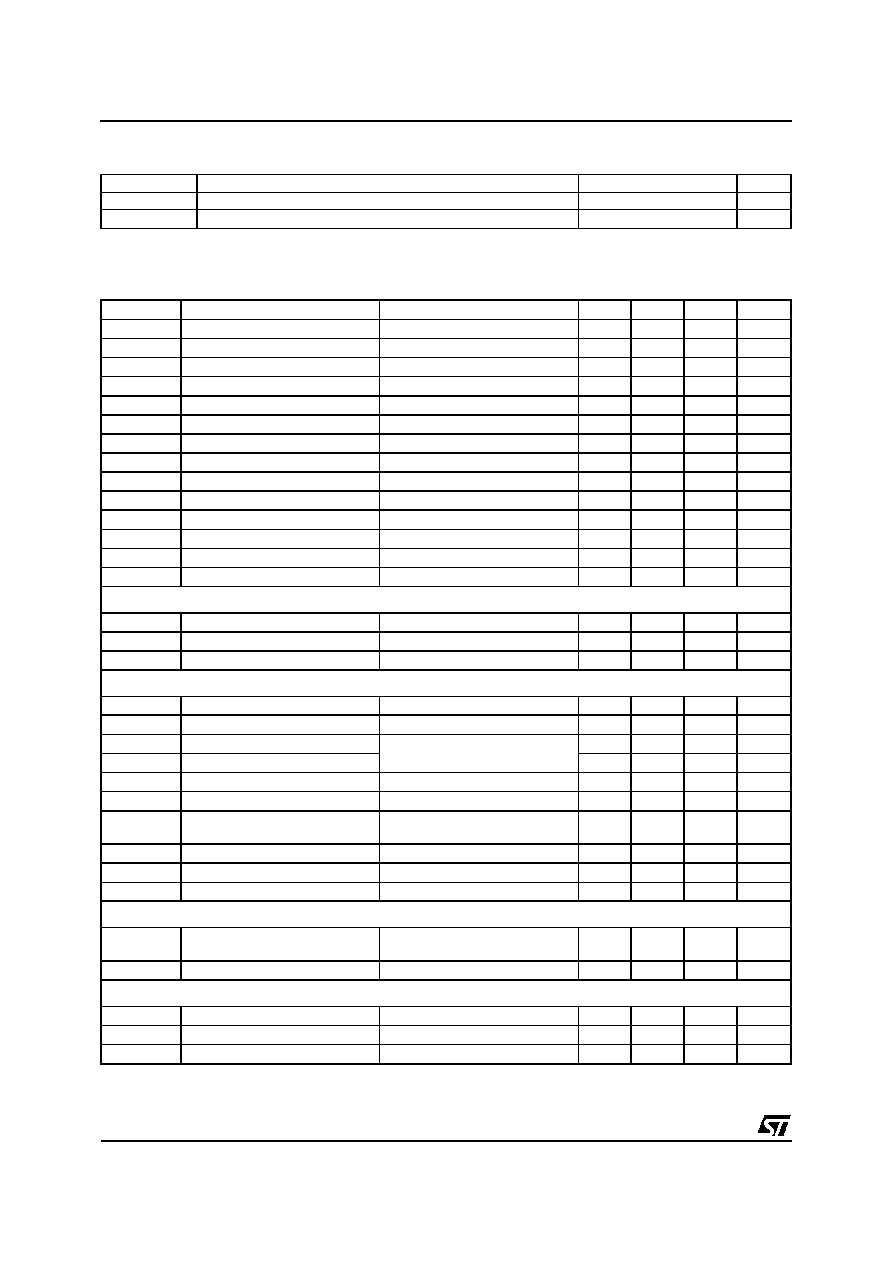

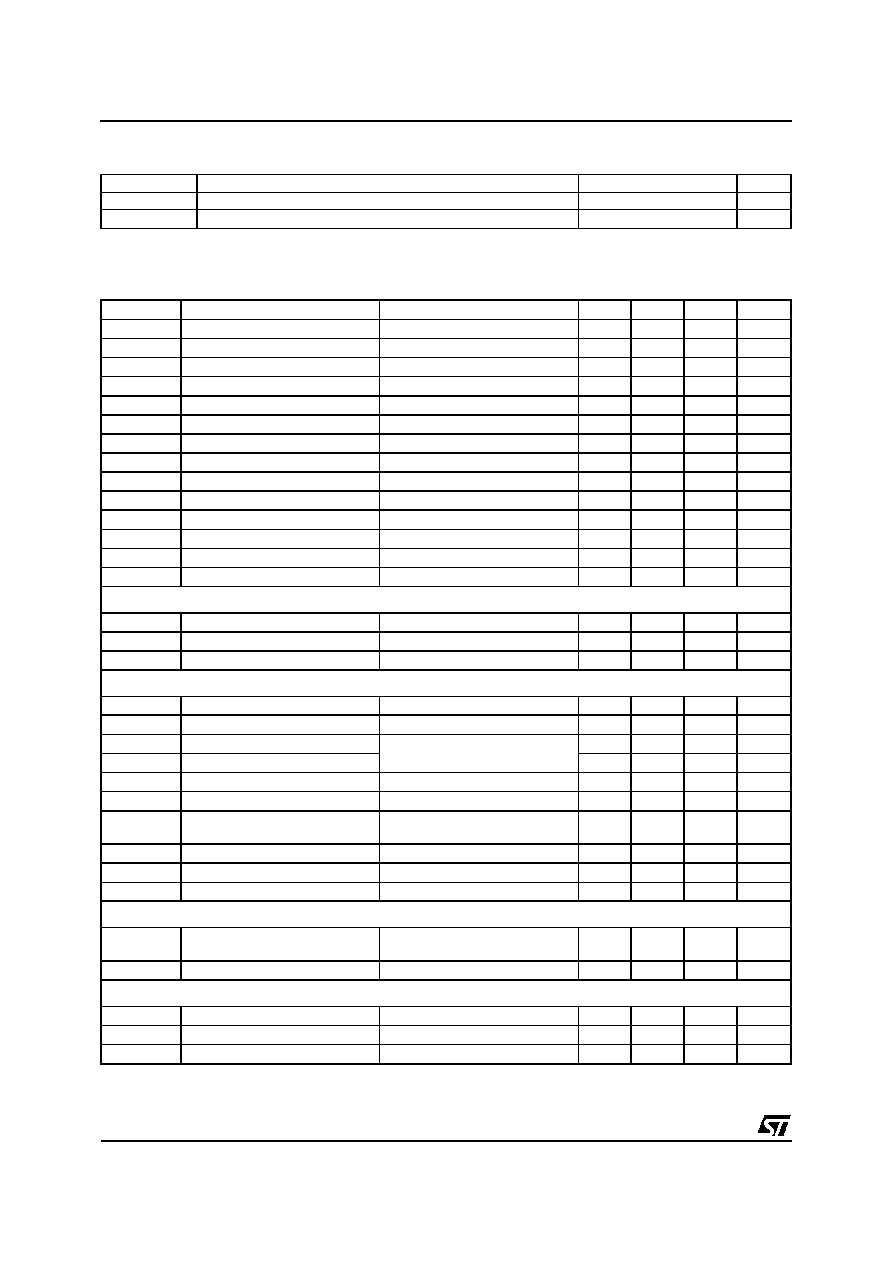

ELECTRICAL CHARACTERISTICS

(V

S

= 42V; V

CC

= 5V; V

boot

= 52V; T

j

= 25∞; unless otherwise specified.)

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

V

S

Supply Voltage

12

40

V

V

CC

Logic Supply Voltage

4.75

5.25

V

V

BOOT

Storage Voltage

V

S

= 12 to 45V

V

S

+6

V

S

+12

V

V

Sense

Max Drop Across Sense Resistor

1.25

V

V

S(off)

Power on Reset

Off Threshold

6

7.2

V

V

SH

/V

CC14

Power on Histeresys

0.3

V

V

CC(off)

Power on Reset

Off Threshold

3.3

4.1

V

I

S(on)

V

S

Quiescent Current

Both bridges ON, No Load

15

mA

I

S(off)

V

S

Quiescent Current

Both bridges OFF

7

mA

I

CC (OFF)

V

CC

Operative Current

DISABLE = LOW

7

mA

T

SD

Shut Down Temperature

145

∞C

T

SD-H

Shut Down Hysteresis

25

∞C

T

J

Thermal Shutdown

150

∞C

f

osc

Triangular Oscillator Frequency (*)

C

FREF

= TBD

12.5

15

17.5

KHz

TRANSISTORS

I

DSS

Leakage Current

OFF State

500

µ

A

R

ds(on)

On Resistance

ON State

0.6

0.75

V

f

Flywheel diode Voltage

If =1.0A

1

1.4

V

CONTROL LOGIC

V

in(H)

lnput Voltage

All Inputs

2

V

CC

V

V

in(L)

Input Voltage

All Inputs

0

0.8

V

I

in

Input Current (Note 1)

0 < V

in

< 5V

-150

+10

µ

A

I

dis

Disable Pin Input Current

-10

+150

µ

A

V

ref1/ref2

Reference Voltage

operating

0

2.5

V

I

ref

V

ref

Terminal Input Current

V

ref

= 1.25

-2

5

µ

A

FI =

V

ref

/V

sense

PWM Loop Transfer Ratio

2

V

FS

DAC Full Scale Precision

Vref = 2.5V I

0

/I

1

/I

2

/I

3

= L

123

134

mV

V

offset

Current Loop Offset

Vref = 2.5V I

0

/I

1

/I

2

/I

3

= H

-30

+30

mV

DAC Factor Ratio

Normalized @ Full scale Value

-2

+2

%

SENSE AMPLIFIER

V

cm

lnput Common Mode Voltage

Range

-0.7

V

S

+0.7

V

I

inp

Input Bias

sense1/sense2

-200

0

µ

A

ERROR AMPLIFIER

G

V

Open Loop Voltage Gain

70

dB

SR

Output Slew Rate

Open Loop

0.2

V/

µ

s

GBW

Gain Bandwidth Product

400

kHz

Note 1: This is true for all the logic inputs except the disable input.

(*) Chopping frequency is twice fosc value.

THERMAL DATA

Symbol

Parameter

Value

Unit

R

th j-amb

Thermal Resistance Junction Ambient

20

∞C/W

R

th j-case

Thermal Resistance Junction-case (*)

2.2

∞C/W

(*) Depending on board and soldering.

L6258

4/18

FUNCTIONAL DESCRIPTION

The circuit is intended to drive both windings of a

bipolar stepper motor or two DC motors.

The current control is generated through a switch

mode regulation.

With this system the direction and the amplitude

of the load current are depending on the relation

of phase and duty cycle between the two outputs

of the current control loop.

The L6258 power stage is composed by power

DMOS in bridge configuration as it is shown in fig-

ure 1, where the bridge outputs OUT_A and

OUT_B are driven to Vs with an high level at the

inputs IN_A and IN_B while are driven to ground

with a low level at the same inputs .

The zero current condition is obtained by driving

the two half bridge using signals IN_A and IN_B

with the same phase and 50% of duty cycle.

In this case the outputs of the two half bridges are

continuously switched between power supply (Vs)

and ground, but keeping the differential voltage

across the load equal to zero.

In figure 1A is shown the timing diagram of the

two outputs and the load current for this working

condition.

Following we consider positive the current flowing

into the load with a direction from OUT_A to

OUT_B, while we consider negative the current

flowing into load with a direction from OUT_B to

OUT_A.

Now just increasing the duty cycle of the IN_A

signal and decreasing the duty cycle of IN_B sig-

nal we drive positive current into the load.

In this way the two outputs are not in phase, and

the current can flow into the load trough the di-

agonal bridge formed by T1 and T4 when the out-

put OUT_A is driven to Vs and the output OUT_B

is driven to ground, while there will be a current

recirculation into the higher side of the bridge,

through T1 and T2, when both the outputs are at

Vs and a current recirculation into the lower side

of the bridge, through T3 and T4, when both the

outputs are connected to ground.

Since the voltage applied to the load for recircula-

tion is low, the resulting current discharge time

constant is higher than the current charging time

constant during the period in which the current

flows into the load through the diagonal bridge

formed by T1 and T4. In this way the load current

will be positive with an average amplitude de-

pending on the difference in duty cycle of the two

driving signals.

In figure 1B is shown the timing diagram in the

case of positive load current

On the contrary, if we want to drive negative cur-

rent into the load is necessary to decrease the

duty cycle of the IN_A signal and increase the

duty cycle of the IN_B signal. In this way we ob-

tain a phase shift between the two outputs such

to have current flowing into the diagonal bridge

formed by T2 and T3 when the output OUT_A is

driven to ground and output OUT_B is driven to

Vs, while we will have the same current recircula-

tion conditions of the previous case when both

the outputs are driven to Vs or to ground.

So, in this case the load current will be negative

with an average amplitude always depending by

the difference in duty cycle of the two driving sig-

nals.

In figure 1C is shown the timing diagram in the

case of negative load current .

Figure 2 shows the device block diagram of the

complete current control loop.

Reference Voltage

The voltage applied to V

REF

pin is the reference

for the internal DAC and, together with the sense

resistor value, defines the maximum current into

the motor winding according to the following rela-

tion:

I

MAX

=

0.5

V

REF

R

S

=

1

FI

V

REF

R

S

where Rs = sense resistor value

L6258

5/18