| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: L9935 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

2 X 1.1A FULL BRIDGE OUTPUTS

INTEGRATED CHOPPING CURRENT REGU-

LATION

MINIMIZED POWER DISSIPATION DURING

FLYBACK

OUTPUT

STAGES

WITH

CONTROLLED

OUTPUT VOLTAGE SLOPES TO REDUCE

ELECTROMAGNETIC RADIATION

SHORT-CIRCUIT

PROTECTION

OF

ALL

OUTPUTS

ERROR-FLAG FOR OVERLOAD, OPEN LOAD

AND OVERTEMPERATURE PREALARM

DELAYED CHANNEL SWITCH-ON TO RE-

DUCE PEAK CURRENTS

MAX. OPERATING SUPPLY VOLTAGE 24V

STANDBY CONSUMPTION TYPICALLY 40

µ

A

SERIAL INTERFACE (SPI)

DESCRIPTION

The L9935 is a two-phase stepper motor driver

circuit suited to drive bipolar stepper motors. The

device can be controlled by a serial interface

(SPI). All protections required to design a well

protected system (short-circuit, overtemperature,

cross conduction etc.) are integrated.

November 1999

Æ

COMMON

LOGIC

OSCILLATOR

DIAGNOSTIC

BIASING

DRIVER

LOGIC

DRIVER

LOGIC

~

~

D99AT415

GND

20

1

GND

19

SR

A

18

17

OUT

A2

16

V

S

N.C.

15

OSC

14

C

DRV

13

OUT

B2

12

SR

B

11

GND

OUT

A1

2

SCK

3

EN

8

CSN

7

VCC

6

SDO

5

SDI

4

OUT

B1

9

GND

10

BLOCK DIAGRAM

PowerSO20

ORDERING NUMBER: L9935

L9935

TWO-PHASE STEPPER MOTOR DRIVER

1/19

PIN FUNCTIONS

Pin N

o

Name

Description

1,10,11,20

GND

Ground. (All ground pins are internally connected to the frame of the device).

2

OUT

A1

Output 1 of full bridge 1

3

SCK

Clock for serial interface (SPI)

4

SDI

Serial data input

5

SDO

Serial data output

6

VCC

5V logic suplly voltage

7

CSN

Chip select (Low active)

8

EN

Enable (Low active)

9

OUT

B1

Output 1 of full bridge 2

12

SR

B

Cyrrent sense resistor of the chopper regulator for OUT

B

13

OUT

B2

Output 2 of full bridge 2

14

C

DRV

Charge pump buffer capacitor

15

OSC

Oscillator capacitor or external clock

16

VS

Supply voltage

17

NC

Not connected

18

OUT

A2

Output of full bridge 1

19

SR

A

Current sense resistor of the chopper regulator for OUT

A

GND

OUT

B1

EN

CSN

VCC

SDI

SDO

SCK

OUT

A1

SR

A

OUT

A2

N.C.

OSC

V

S

C

DRV

OUT

B2

SR

B

GND

10

8

9

7

6

5

4

3

2

13

14

15

16

17

19

18

20

12

1

11

GND

GND

D99AT416

PIN CONNECTION

L9935

2/19

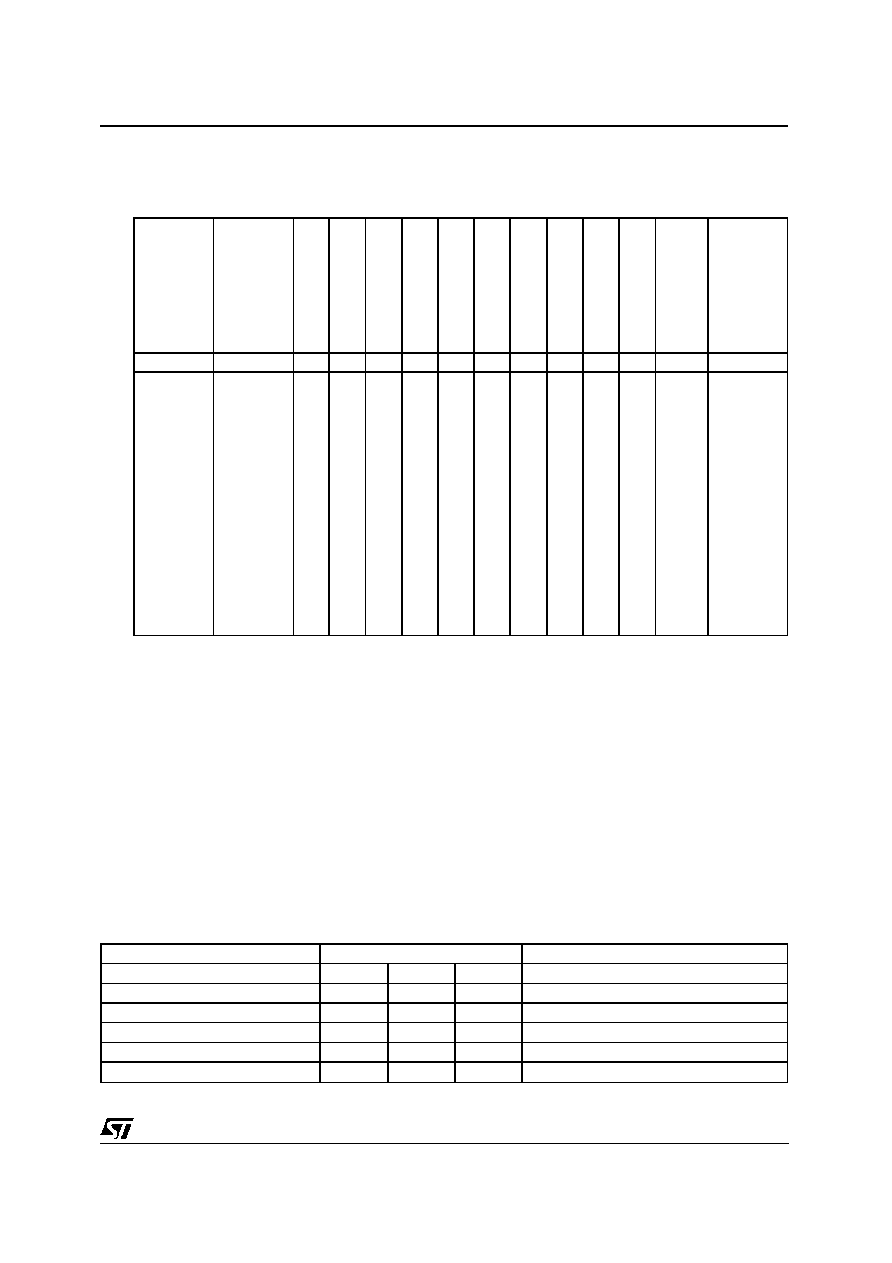

ELECTRICAL CHARACTERISTICS (8V

V

S

24V; -40

∞

C

T

j

150

∞

C; 4.5V

V

CC

5.5V, unless oth-

erwise specified.)

1)

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

SUPPLY

IS

85

Total Supply Current

I

S

+ I

VCC

(Both Bridges Off)

V

S

= 14V

EN = HIGH

T

J

85

∞

C

40

100

µ

A

I

SOP

Operating Supply Current

I

OUT Ai/Bi

= 0

f

OSC

= 30kHz

V

S

= 14V

4.5

mA

I

CC

5V Supply Current

EN = LOW

1.4

10

mA

FULL BRIDGES

R

OUT, Sink

R

DSON

of Sink Transistors

Current bit

combinations LL, LH,

V

S

12V

0.4

0.7

R

OUT, Source

RDSON of Source Transistors

0.4

0.7

R

OUT8, Sink

RDSON of Sink Transistors +

R

DSON

of Source Transistors

Current bit

Combinations LL, LH,

V

S

= 8V

1.6

3

V

FWD

Forward Voltage of the DMOS

Body Diodes

EN = HIGH

I

FWD

= 1A; V

S

12V

1

1.4

V

V

REV

Reverse DMOS Voltage

EN = LOW

I

REV

= 1A

0.5

0.9

V

t

r

, t

f

Rise and Fall Time of Outputs

OUT

Ai/Bi

0.1...0.9 V

OUT

V

S

= 14V

Chopping 550mA

0.3

0.6

1.5

µ

s

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Unit

V

S

DC Supply Voltage

-0.3 to 35

V

V

SPulsed

Pulsed supply voltage T < 400ms

-0.3 to 40

V

V

OUT (Ai/Bi)

Output Voltages

internally clamped to V

S

or GND depending on the

current direction

I

OUT (Ai/Bi)

DC Output Currents

Peak Output Currents (T/tp

10)

±

1.2

±

2.5

A

A

V

SRA/SRB

Sense Resistor Voltages

-0.3 to 6.2

V

V

CC

Logic Supply Voltages

-0.3 to 6.2

V

V

CDRV

Charge Pump Buffer Voltage versus V

S

-0.3 to 10

V

V

SCK

, V

SDI

,

V

CSN

, V

EN

Logic Input Voltages

-2 to 8

V

V

OSC

, V

SDO

Oscillator Voltage Range, Logic Output

-0.3 to V

CC

+0.3

V

Note: ESD for all pins, except pins SDO, SRA and SRB, are according to MIL883C, tested at 2kV, corre sponding to a maximum energy

dissipation of 0.2mJ. SDO, SRA and SRB pins are tested with 800V.

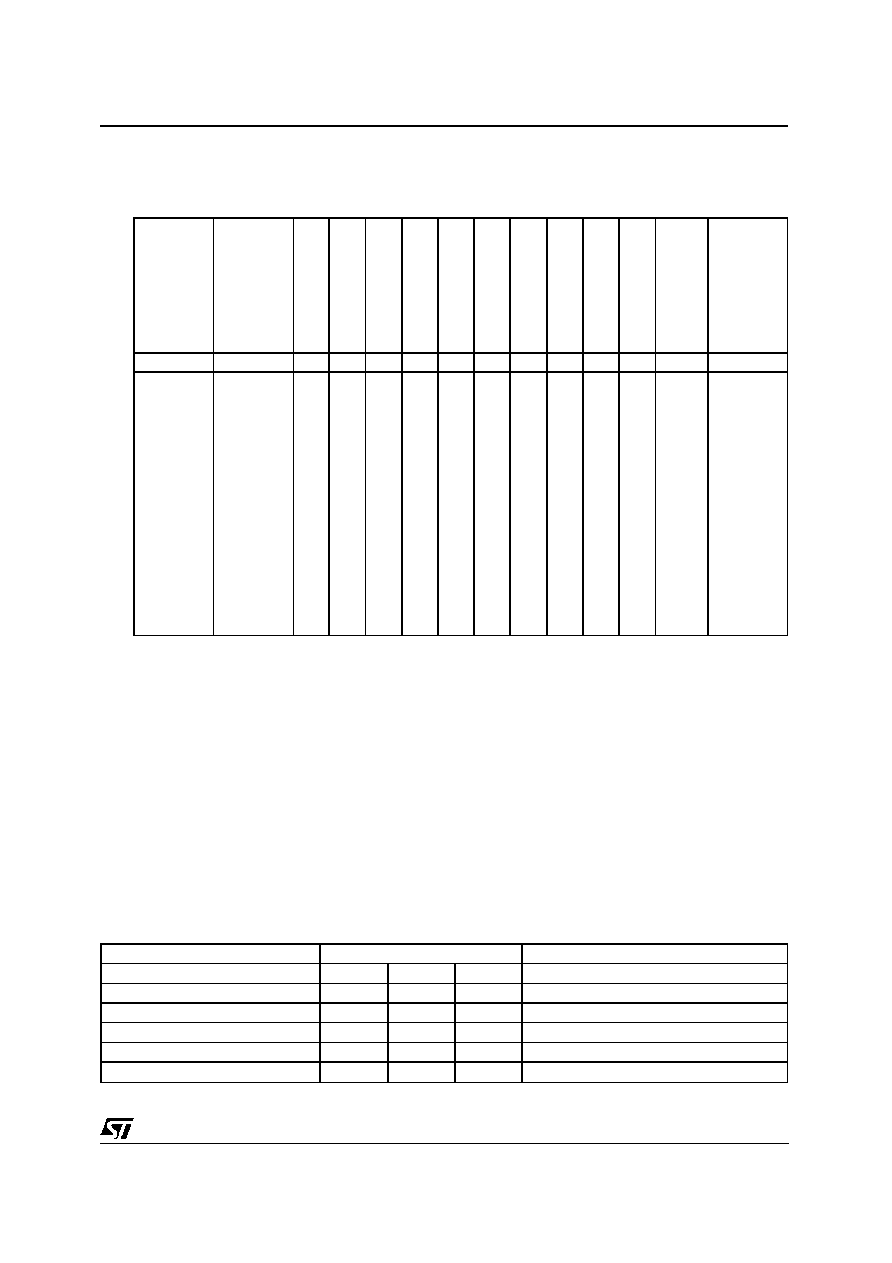

THERMAL DATA

Symbol

Parameter

Value

Unit

R

th j-case

Typical Thermal Resistance Junction to Case

5

∞

C/W

R

th j-amb

Typical Thermal Resistance Junction to Ambient

(6cm

2

Ground Plane 35

µ

m Thhickness)

35

∞

C/W

R

th j-amb, FR4

Typical Thermal Resistance Junction to Ambient

(soldered on a FR 4 board with through holes for heat transfer

and external heat sink applied)

8

∞

C/W

T

S

Storage Temperature

-40 to 150

∞

C

T

SD

Typical Thermal Shut-Down Temperature

180

∞

C

L9935

3/19

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

SWITCH OFF THRESHOLD OF THE CHOPPER (R

1

R

2

= 0.33

)

V

SRHL

Voltage Drops Across R

1

R

2

2)

(Voltage at Pin SR

A

or SR

B

vs.

GND)

Bit 5, 2 = H

Bit 4, 1 = L

12

20

35

mV

V

SRLH

Bit 5, 2 = L

Bit 4, 1 = H

160

180

210

mV

V

SRLL

Bit 5, 4, 2, 1 = L

270

300

340

mV

ENABLE INPUT EN

V

EN High

High Input Voltage

V

CC

-1.2V

V

V

EN low

Low Input Voltage

1.2

V

V

EN Hyst

Enable Hysteresis

0.1

V

I

EN High

High Input Current

V

High

= V

CC

-10

0

10

µ

A

I

EN Low

Low Input Current

VLOW = 0V

-3

-10

-30

µ

A

LOGIC INPUTS SDI. SCK, CSN

V

HIGH

High Input Voltage

EN = LOW

2.6

8

V

V

LOW

Low Input Voltage

-0.3

1

V

V

Hyst

Hysteresis

0.8

1.2

1.6

V

I

HIGH

High Input Current

V

High

= V

CC

-10

0

10

µ

A

I

Low

Low Input Current

V

Low

= 0V

-3

-10

-30

µ

A

LOGIC OUTPUTS (SDO)

V

SDO,High

High Output Voltage

I

SDO

= -1mA

V

CC

-1

V

CC

-0.17

V

CC

V

V

SDO,Low

Low Output Voltage

ISDO = 1mA

0.17

1

V

OSCILLATOR

V

OSC, H

High Peak Voltage

EN = LOW

2.2

2.46

2.6

V

V

OSC, L

Low Peak Voltage

EN = LOW

1

1.23

1.4

V

I

OSC

Charging/Discharging Current

45

62

80

µ

A

f

OSC

Oscillator Frequency

C

OSC

= 1nF

20

25

31

kHz

t

Start

Oscillator Startup Time

EN = High

Low

2/f

osc

5/f

osc

8/f

osc

THERMAL PROTECTION

T

J-OFF

Thermal Shut-Down

Temperature

160

180

200

∞

C

T

J-ALM

Thermal Prealarm

130

160

∞

C

T

MGN

Margin Prealarm/Shut-Down

10

20

30

K

1) Parameters are tested at 125

∞

C. Values at 140

∞

C are guaranteed by design and correlation.

2) Currents of combinations LH and LL are sensed at the external resistors. The Current of bit combination HL is sensed internally and

cannot be adjusted by changing the sense resistors.

ELECTRICAL CHARACTERISTICS (continued)

L9935

4/19

COMMON

LOGIC

OSCILLATOR

DIAGNOSTIC

BIASING

DRIVER

LOGIC

DRIVER

LOGIC

~

~

D99AT417

GND

20

1

GND

19

SR

A

18

R1 0.33

C1

100nF

C

OSC

1nF

C

Driver

100nF

POWER

SUPPLY

+5V

STEPPER

MOTOR

C2

10

µ

F

OUT

A2

17

N.C.

16

V

S

15

OSC

14

C

DRV

13

OUT

B2

12

SR

B

11

GND

OUT

A1

2

SCK

SDI

INTERFACE

µ

C

3

EN

8

CSN

7

VCC

6

SDO

5

SDI

4

OUT

B1

9

GND

10

R2 0.33

100nF

Figure 1. General Application Circuit Proposal.

Application hints:

C1 and C2 should be placed as close to the de-

vice as possible. Low ESR of C2 is advanta-

geous. Peak currents through C1 and C2 may

reach 2A. Care should be taken that the reso-

nance of C1, C2 together with supply wire induc-

tances is not the chopping frequency or a multiple

of it.

FUNCTIONAL DESCRIPTION

Basic structure

The L9935 is a dual full bridge driver for inductive

loads with a chopper current regulation.

Outputs

A1 and A2

belong to full bridge A

Outputs

B1 and B2

belong to full bridge B

The polarity of the bridges can be controlled by

bit0 and bit3 (for full bridge A, bit3, for full bridge

B, bit0). Bit5, bit4 (for full bridge A) and bit2, bit1

(for full bridge B) control the currents. Bit3 high

leads to output A1 high. Bit0 high leads to output

B1 high.

Current setting Table 1 using a 0.33W sense re-

sistor.

Table 1.

bit5, bit2

bit4, bit1

I

QX

(Typ.)

I

RX/max

Remark

H

H

L

L

H

L

H

L

0

60mA

550mA

900mA

0%

61%

100%

inernally sensed

L9935

5/19

I

A

1.8

1.1

1

0.8

0.6

0.4

0.2

0.075

0

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.0

1.1

1.2

1.3

1.4

1.5

1.6

I

HL

I

LH

I

LL

typical current limitation of high side transistor

limit recommended for usual application

R

suggested range of operation

D99AT418

Figure 2. Typical average load current dependence on R

Sense

.

DRIVE

LOGIC

CURRENT

LOGIC

bit3, (bit0)

bit5, (bit2)

bit4, (bit1)

CURRENT ADJUST

INHIBIT

ON HH

LOAD

+

-

D

11

M

11

D

12

M

12

D

11

A

1

A

2

V

S

R

1

R

1

EXTERNAL

SENSE RESISTOR

D

12

COMP1

D

22

D

21

D

22

M

22

D

21

M

21

D99AT419

Full Bridge Function

Figure 3. Displays a full bridge including the current sense circuit.

L9935

6/19

No current:

Bit 5, bit 4 (corresponding bit 2 and bit1 for bridge

B) both are HIGH, the current logic will inhibit all

drivers D

11

, D

12

, D

21

, D

22

turning off M

11

, M

12

,

M

21

, M

22

independently from the signal of the cur-

rent sense comparator comp 1.

Turning on:

Changing bit 5 or bit 4 or both to LOW will turn on

either M

11

and M

22

or M

21

and M

12

(depending on

the phase signal bit 3). Current will start to flow

through the load. The current will be sensed by

the drop across R

1

.

The threshold of the comparator comp 1 depends

on the current settings of bit 5 and bit 4.

The current will rise until it exceeds the turn off

threshold of comp 1.

Chopping:

Exceeding the threshold of comp 1 the drive logic

will turn off the sink transistor (M

12

or M

22

). The

sink transistor periodically is turned on again by

the oscillator. Immediately after turning on M

12

or

M

22

the comparator comp 1 will be inhibited for a

certain time to blank switch over spikes caused

by capacitive load components up to 5 nF.

Turning off for example M

12

will yield a flyback

current through D

11

. (So now the free wheeling

current flows through M21, the load and D11).

This leads to a slow current decay during flyback.

Maximum duty cycles of more than 85% (at f

OSC

= 25kHz) are possible. In this case current flows

of both bridges will overlap (not shown in Fig. 5).

Reversing phase:

Suppose the current flowed via M

21

, the load and

M

12

before reversing phase. Reversing phase

M

21

and M

12

will be turned off. So now the cur-

rent will flow through D

22

, the load and D

11

. This

leads to a fast current decay.

Chopper control by oscillator

Both chopping circuits work with offset phase.

One chopper will switch on the bridge at the

maximum voltage of the oscillator while the other

chopper will switch on the bridge at minimum

voltage of the oscillator.

MS1 and MS2 blank switching spikes that could

lead to errors of the current control circuit.

SRA

SRB

OSC

C

OSC

MS1

MS2

Comp1

inhibit

inhibit

D99AT420

+

+

-

-

Comp2

Dr1

OSCILLATOR

Dr2

RES2

RES1

R

R

S

S

MOS DRIVERS

RESET

DOMINANT

RESET

DOMINANT

RSFF1

RSFF2

f

OSC

=

i

OSC

2.46V ∑ C

OSC

Figure 4. Principal chopper control circuit.

L9935

7/19

turn off delay

due to slope

velocity control

I

V

OSC

V

SRB

total current consumption

current

threshold 1

current

threshold 2

V

SRA

I

VS

D99AT421

Figure 5. Pulse diagram to explain offset chopping.

Using offset chopping the changes of the supply current remain half as large as using non offset chop-

ping.

Turning off the oscillator for example by shorting pin OSC to ground will hinder turning on of the bridges

anymore after the comparators have generated a turn off signal.

External clocking is possible overdriving the charge and discharge currents of the oscillator for example

with a push pull logic gate. So several devices can be synchronized.

Protection and Diagnosis Functions

The L9935 provides several protection functions and error detection functions. Current limitation usually

is customer defined by the external current sense resistors. The current sensed there is used to regulate

the current through the stepper motor windings by pulse width modulation. This PWM regulation protects

the sink transistors. The source transistors are protected by an internal overcurrent shut down turning off

the source transistors in case of overload.

Overload detection of the source transistor will turn off the bridge and set the corresponding error flag.

To turn on the bridge again a new byte must be written into the interface. (Rising slope of CSN resets

the overload error flag).

Both bridges use the same flags. To locate which bridge is affected by an error the bridges can be

tested individually (One bridge just is turned off to check for the error in the other bridge).

Short from an Output to the Supply Voltage VS

The current will be limited by the pulse width modulator. The sink transistor will turn off again after some

microseconds. The transistor will periodically be turned on again by the oscillator 8 times. After having

detected short 8 times the low side transistor will remain off until the next data transfer took place. After

detection of a short to VS we suggest to turn off the corresponding bridge to reduce power dissipation

for at least 1ms.

L9935

8/19

Diagnosis of a Short to VS

During the short current through the sink transistor will rise more rapidly than under normal load condi-

tions. Reaching a peak current of 1.5 times the maximum PWM current between typically 2

µ

s and 5

µ

s

after turn on will be detected as a short to V

S

.

Detecting a short the low side transistor will try to turn on again the next 7 trigger pulse of the oscillator.

Simultaneously the error flag will updated on each pulse.

t

t

ON

I

Q

short threshold

t

on

:

turn on of the sink transistor

t

on

+ t

1

= t

short

:

activation of short threshold

t

on

+ t

delay

= t

PWM

: activation of PWM threshold

PWM threshold

PWM detection

signal (internal)

Short detection

signal (internal)

Error 1

t

short

t

PWM

t

ON

t

ON

t

ON

t

short

t

short

t

PWM

t

short

t

PWM

t

PWM

t

t

t

D99AT422

Figure 6. Normal PWM current versus short circuit current and detection of short to VS..

Between t

on

and t

short

the over current detection is totally blanked.

Between t

short

and t

PWM

the current threshold is set to 1.5 times the maximum PWM current (1.5 times

the current of current setting LL).

Overcurrent now will set the error flag.

After t

PWM

the current threshold is the nominal PWM current set by the external resistor. Exceeding this

current will just turn off the sink transistor. This is considered as normal operation. The error flag is de-

tached from the comparator after tPWM so no error flag is set during normal pulse width modulation.

Short from an Output to Ground

The current through the short will be detected by the protection of the source transistor. The source tran-

sistor will turn off exceeding a current of typically 1.8A. Minimum overload detection current is 1.2A. To

obtain proper current regulation (by the sink transistors and not by source transistor shut down) the

maximum current of the PWM regulator should be set to a maximum value of 1.1A.

L9935

9/19

Diagnosis of a Short to Ground

Detecting an overload will set an overcurrent error (Error2 = LOW) (bit6). To reset the error flag a new

byte must be written into the interface. (Reset of the error flag takes place at the rising slope of CSN).

Shorted Load

With a shorted load both, the sink- and the source protection or the PWM alone will respond. In either

case there will be no flyback pulse.

Diagnosis of a Shorted Load

Shorting the load two events may take place:

- overload (of the high side transistor) while low side transistor overcurrent is detected will set the

following combinations:

bit6 = LOW

bit7 = HIGH

- overload is marginal. So the low side driver may turn off before overload is detected. This leads to the

combination bit6 = HIGH and bit7 = LOW.

Open Load

An open load will not lead to any flyback pulses. Error detection will take advantage of the flyback pulse.

Missing the flyback pulse after reversing the polarity of a motor winding bit7 will become LOW.

Open load will not be tested in the low current mode (current bits HL) to avoid the risk of instable diagno-

sis at low flayback currents. Open load immediately after reset or power down may on random be de-

tected in the low current mode too. This diagnosis however will not persist longer than 8 changes of po-

larity. We strongly suggest to test open load at a high current mode (combination LH or LL).

Overtemperature Prealarm

Typically 20K before thermal shut down takes place an overtemperature prealarm (bit7 and bit6 low)

takes place. Typically overtemperature prealarm temperature is between 150

∞

C and 160

∞

C.

Application hints using a high resistive stepper motor

The L9935 was originally targeted on stepper chopping stepper motor application with typical resis-

tances of 8..12W. Using motors with higher resistance will work too but diagnosis behaviour will slightly

change. This paragraph shows the details that should be taken in account using diagnosis for high resis-

tive motors.

Startup behaviour:

The device has simple digital filter to avoid triggering diagnosis at a single event that could be random

noise. This digital filter needs 4 chopping pulses to settle. Using a high resistive motor this chopping

does not take place. Instead the digital filter samples each time a polarty change takes place. So the first

three response telegrams after reset may show an 'open load' error.

Inpu t data

High resistive motor (error bits)

Low resistive motor (error bits)

Standby

1st telegram (550mA or 900mA)

HH

HH

Reverse phase (550mA or 900mA)

XH

HH

Reverse phase (550mA or 900mA)

XH

HH

Any data

XH

HH

Any data

HH

HH

H means check for HIGH at the error bits.

X means don't care because filter is not yet settled.

L9935

10/19

Using 75mA chopping immediatelly after stand by:

The high resistive motor can be forced to chopping operation in the low current range. This leads to the

samebehaviour as using a low resistive motor.

Short to V

S

detection using high resistive motors:

The short to VS flag is overwritten each time the chopper comparator responds. Having detected a short

this flagonly can be reset by reaching chopping operation or resetting the circuit (ENN=1). For a high re-

sistive motor thisleads to the following consequence: Once a short to VS is detected the error flag will

persist even if the short is removed again until either a reset (ENN=1) or chopping (for example in 75mA

mode) has taken place. We suggest to return to operation once a short to VS was detected by using the

low current mode to reset the flag.

Limitation of the Diagnosis

The diagnosis depends on either detecting an overcurrent of more than typically 1.8A through the

source transistor or on not detecting a flyback pulse, or on detecting severe overcurrents of the sink

transistor immediately after turn on.

Small currents bypassing the load will not be detected.

In the low current range (hold current) the flyback pulse (especially commutating against the supply

voltage after changing phase) may (depending on the inductivity of the stepper motor windings) be

too short to be detected correctly. For this reason diagnosis using the flyback pulse is blanked at

phase reversal at hold current.

In the low current range (hold current) the current capability of the bridge is reduced on purpose.

Short to VS may not be detected. In stead the bridge may just chop like normal operation.

Flyback pulse detection is not blanked during PWM regulation at hold current

(here commutation

voltage is less than 1V thus providing a longer pulse duration.) This however should be taken in ac-

count using stepper motors with low inductivity (less than 0.5mH). Using motors with such a low in-

ductivity the flyback voltage in hold mode may decay too fast.

Motors with extremely low ohmic resistance tend to pump up the current because current decay dur-

ing flyback approaches zero while at bridge turn on the current will increase. This may lead to over-

current detection. We suggest to use stepper motors with an ohmic resistance of approximately 3

or

more.

Partial shorts of windings or shorts of stepper motors with coils in series may still yield a flyback pulses

that are accepted by the diagnosis as a proper signal.

Table 2. Error table.

Error 1

bit7

Error 2

bit6

Description

H

H

Normal operation

L

H

Short to VS (sink overload immediately after turn on)

shorted load (no flyback)

open load (no flyback)

H

L

short to gnd (source overload, missing flyback is masked)

L

L

overtemperature prealarm

At stepping rates faster than 1ms/data transfer error flags indicating a short should be used to initiate a

pause of at least 1ms to allow the power bridges to cool down again.

L9935

11/19

MSB7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

SCK

EN

CSN

CSN

SCK

SDI

SDO

t

1

t

1

t

1

t

zch

t

1

t

cl

t

su

t

sh

td

SDI

t

Pd

CURRENT B

POLARITY B

POLARITY A

D99AT437

t

en_sck

MSB7

bit6

bit7

bit7

bit5

bit4

bit3

bit2

bit1

bit0

bit0

bit0

SDO

AX

CURRENT A

ERROR BITS

t

ch

Figure 7. SPI Data/Clock Timing.

Serial Data Interface (SPI)

The serial data interface itself consists of the pins SCL (serial clock), SDI (serial data input) and SDO

(serial data output).

To especially support bus controlled applications the additional signals EN (chip enable not) and CSN

(chip select not) are available.

Startup of the Serial Data Interface

Falling slope of EN activates the device. After t

en.sck

the device is ready to work.

Falling slope of CSN indicates start of frame. Data transfer (reading SDI into the register) takes place at

the rising slopes of SCK.

Data transfer of the register to SDO takes place at the falling slope of SCK.

Rising slope of CSN indicates end of frame. At the end of frame data will only be accepted if modulo 8

bit (modulo 8 falling slopes to SCK) have been transferred. If this is not the case the input will be ignored

and the bridges will maintain the same status as before.

SDO is a tristate output.

SDO is active while CSN = LOW, while CSN = HIGH SDO is high resistive.

L9935

12/19

SDO

SCK

CSN

CSN

µ

P

SDO

SDI

SCK

CSN

SCK

CSN

SCK

SDO

SDI

SDO

SDI

no.1

no.2

no.3

D99AT438

Figure 8. Cascading Several Stepper motor drivers.

byte for no. 3

byte for no. 2

byte for no. 1

SCK

EN

CSN

D99AT439

Q

XX

SDO

of

µ

P

Figure 9. Control sequence for 3 Stepper motor drivers.

Test condition for all propagation times (unless otherwise specified)

HIGH

3V; LOW

0.8V; t

r

, t

f

= 10ns, Enable: ENN Low < 0.8V, ENN High > V

cc

-0.8V

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

f

SCLK

SCK-Frequency

DC

2MHz

t

1

SCK stable before and after

CSN = 0

100

ns

t

ch

Width of SCK high pulse

200

ns

t

cl

Width of SCK low pulse

200

ns

t

su

SDI setup time

80

ns

t

sh

SDI hold time

80

ns

t

d

SDO delay time (CL = 50pF)

100

ns

t

zc

SDO high Z CSN high

100

ns

t

en_sck

Setup time ENABLE to SCK

HIGH > V

CC

-1.2V

30

µ

s

t

pd

Propagation delay SPI to

output Q

XX

2 (*)

µ

s

(*) Measured at a transition from High impedance (Bridge off) to bridge on. (Reversing polarity takes about 1

µ

s longer because the bridge first

turns off before turning on in reverse direction).

Table of bits

bit5,bit4 : current range of bridge A (Outputs A1 and A2)

bit3

: polarity of bridge A

bit2,bit1 : current range of bridge B (Outputs B1 and B2)

bit0

: polarity of bridge B

bit7,bit6 : Error1 and Error 2

Cascading several Devices

Cascading several devices can be done using the SDO output to pass data to the next device. The

whole frame now consists of n byte. n is the number of devices used.

L9935

13/19

here usually only one Stepper motor driver is selected at a time while all others are deselected.

Application Information

For driving a stepper motor we suggest to use the following codes. The columned 'SDO correct' shows

the data returned at SDO in correct function. The columnes presented under 'Error cases' display the di-

agnosis bits if errors are detected.

Examples of control sequences

Full step mode control sequences and diagnosis response.

SDI

SDO

correct

Error cases and SDObit7, bit6

A

O

P

E

N

B

O

P

E

N

A1

S

H

O

R

T

VS

A2

S

H

O

R

T

VS

B1

S

H

O

R

T

VS

B2

S

H

O

R

T

VS

A1

*)

S

H

O

R

T

GND

A2

*)

S

H

O

R

T

GND

B1

*)

S

H

O

R

T

GND

B2

*)

S

H

O

R

T

GND

therm.

alarm

therm.

shut

down

(reset

operating

codes)

bit

76543210

76543210

76

76

76

76

76

76

76

76

76

76

76

76543210

XX111111

SDO PRESENT LAST DATA OR 11111111 IN CASE PREV. STATE WAS STAND BY

XX011011

XX010011

XX010010

XX011010

XX011011

XX010011

XX010010

XX011010

11111111

11011011

11010011

11010010

11011010

11011011

11010011

11010010

11

11

01

11

01

11

01

11

11

11

11

01

11

01

11

01

11

11

01

01

01

11

01

01

11

01

01

11

01

01

01

11

11

11

11

01

01

01

11

01

11

01

01

01

11

01

01

01

11

10

01

11

10

10

01

11

11

11

10

10

01

11

10

10

11

10

10

01

11

10

10

01

11

11

11

10

10

01

11

10

00

00

00

00

00

00

00

00

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

SDI

SDO

SCK

CSN1

CSN2

µ

P

SDI

SDO

SCK

CSN

SDI

SDO

SCK

CSN

no.1

no.2

D99AT440

Figure 10. Paralleling several Devices.

*) Motor resistance approximatelly 10

and V

S

= 12V. So a short to ground only is detected on one branche of the bridge. Lower resistivity of

the motor may lead to detection of short to ground on both branches of the bridge leading to code 10 on all steps.

L9935

14/19

These sequences are intended to give the user a good starting point for his software development. Be-

sides these two there are further possibilities how to implement control sequences for this device (other

currents, quarters step etc.).

SDI

SDO

A

O

P

E

N

B

O

P

E

N

A1

S

H

O

R

T

VS

A2

S

H

O

R

T

VS

B1

S

H

O

R

T

VS

B2

S

H

O

R

T

VS

A1

*)

S

H

O

R

T

GND

A2

*)

S

H

O

R

T

GND

B1

*)

S

H

O

R

T

GND

B2

*)

S

H

O

R

T

GND

therm.

alarm

therm.

shut

down

(reset

operating

codes)

bit

76543210

76543210

76

76

76

76

76

76

76

76

76

76

76

76543210

XX111111

XX011111

XX011111

XX011111

XX011011

XX111011

XX010011

XX010111

XX010010

XX110010

XX011010

XX011110

XX011011

XX111011

XX010011

XX010111

XX010010

XX110010

previous code

11111111

11011111

11011111

11011111

11011111

11011011

11111011

11010011

11010111

11110010

11011010

11011110

11011011

11111011

11010011

11010111

11010010

11

11

11

11

11

01

11

11

11

01

11

11

11

01

11

11

11

11

11

11

11

11

11

11

01

11

11

11

01

11

11

11

01

11

11

11

11

11

11

01

01

01

01

01

11

11

01

01

01

01

01

11

01

01

01

01

01

11

11

11

01

01

01

01

01

11

11

11

11

11

11

11

11

11

11

01

01

01

01

01

11

11

11

01

01

11

11

11

11

01

01

01

01

11

11

11

01

01

01

01

01

11

11

10

10

10

10

01

11

11

11

11

10

01

10

01

11

11

11

11

11

11

11

11

11

10

10

10

01

11

11

11

11

10

10

10

11

11

11

11

10

10

10

01

11

11

11

11

10

10

10

01

11

11

11

11

11

11

11

11

11

10

10

10

01

11

11

11

11

10

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

00111111

Double errors: Double errors will create composite codes by an AND operation between columns of the

same dominance. Open and short to VS are the least dominant error codes. (first 6 error code columns).

Short to ground is the second dominant error code. detection of short to gnd will overwrite error codes of

the least dominant kind (open, short to VS). Temperature prealarm and thermal shut down are the most

dominant error codes. Thermal prealarm returns error code 00 but the device still is working and returns

the appropriate operation code (bits 0..5).

Thermal shut down returns error code 00 and turns off the device. The opcode returned corresponds the

action eventually performed (bit 0..5 become 1).

For example open bridge A and simultaneously open bridge B will lead to error code 01 by performing

an AND operation between the two corresponding columns.

Electromagnetic Emission classification(EME)

Electromagnetic Emission classes presented below are typical data found on bench test. For detailed test de-

scription please refer to 'Electromagnetic Emission (EME) Measurement of Integrated Circuits, DC to 1GHz' of

VDE/ZVEI work group 767.13 and VDE/ZVEI work group 767.14 or IEC project number 47A 1967Ed. This data

is targetedto boarddesigners to allow an estimation of emission filtering effortrequired in application.

Pin

EME class

Remark

GND

E

10

0

1

test

V

CC

E

e

Blocked with 100nF closemto the device

EN. SDI, CSN, CSK, SDO in tristate

K

h

SDO

G

f

SDO in low-Z state, no data transfer

Power output A

1

, A

2

, B

1

, B

2

E

5

f

Sourcing output

Power output A

1

, A

2

, B

1

, B

2

6

f

Sinking output in chopping mode f

osc

= 20kHz

Electromagnetic Emission is not tested in production.

*) Motor resistance approximatelly 10

and V

S

= 12V. So a short to ground only is detected on one branche of the bridge. Lower resistivity of

the motor may lead to detection of short to ground on both branches of the bridge leading to code 10 on all steps.

L9935

15/19

STAND

BY

OFF

OFF

ON

11

ON

01

DEVICE ON

CHECKS FOR

ERRORS 11

CHECKING

FOR ERRORS

01

CHECKING

FOR ERRORS

10

LOGIC

SELECTS

BRANCHE

DEPENDING

ON PREVIOUS

STATE

ON

CHECKING

FLYBACK 6

turn on

new telegram

no error

new telegram

new

telegram

new

telegram

new telegram current = 0

new

telegram

missing

flyback

different polar ity

shor t

to gnd

shor t to VS

no shor t

no shor t

same polarity as before

shor t to VS

short

to gnd

shor

t

to

gnd

shor t

to VS

shor

t

to

VS

shor

t to

gnd

short

to VS

shor

t to

gnd

new telegram

same polarity

flyback OK

or reverse polarity

than before

D99AT441

Figure 11. State diagram.

Remark: Return to stand by is possible from every state

Note: Reversing polarity in low current mode no flyback check will be performed.

Electromagnetic Emission classification(EME)

Electromagnetic Emission classes presentel below are typical data found on bench test. For detailed test

description please refer to 'Electromagnetic Emission (EME) Measurement of Integrated Circuits, DC to

1GHz' of VDE/ZVEI work group 767.13 and VDE/ZVEI work group 767.14 or IEC project number 47A

1967Ed. This data is targeted to board designers to allow an estimation of emission filtering effort re-

quired in application.

Pin

EME class

Remark

GND

E

10

o

1

test

V

CC

E

e

Blocked with 100nF close to the device

EN, SDI, CSN, SCK, SDO in tristate

K

h

SDO

G

f

SDO in low-state, no data transfer

Power output A

1

, A

2

, B

1

, B

2

E

5

f

Sourcing output

Power output A

1

, A

2

, B

1

, B

2

6

f

Sinking output in chopping mode fOSC = 20kHz

Electromagnetic Emission is not tested in production.

L9935

16/19

100 H

47nF

47nF100 F

4* 2,2nF

to motors

Vs

Out 1

Out 2

Out 3

Out 4

GND 1/10/

11/20

Vbatt

Figure 12. EMC Compatibility for L9935

L9935

17/19

L9935

18/19

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are

subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

©

1999 STMicroelectronics ≠ Printed in Italy ≠ All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -

Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

L9935

19/19