1/24

February 2003

M24C64

M24C32

64Kbit and 32Kbit Serial I≤C Bus EEPROM

FEATURES SUMMARY

s

Two Wire I

2

C Serial Interface

Supports 400 kHz Protocol

s

Single Supply Voltage:

≠ 4.5V to 5.5V for M24Cxx

≠ 2.5V to 5.5V for M24Cxx-W

≠ 1.8V to 5.5V for M24Cxx-R

s

Write Control Input

s

BYTE and PAGE WRITE (up to 32 Bytes)

s

RANDOM and SEQUENTIAL READ Modes

s

Self-Timed Programming Cycle

s

Automatic Address Incrementing

s

Enhanced ESD/Latch-Up Behavior

s

More than 1 Million Erase/Write Cycles

s

More than 40 Year Data Retention

Figure 1. Packages

PDIP8 (BN)

8

1

SO8 (MN)

150 mil width

8

1

TSSOP8 (DW)

169 mil width

TSSOP8 (DS)

3x3mm≤ body size (MSOP)

M24C64, M24C32

2/24

SUMMARY DESCRIPTION

These I

2

C-compatible electrically erasable

programmable memory (EEPROM) devices are

organized as 8192 x 8 bits (M24C64) and 4096 x 8

bits (M24C32).

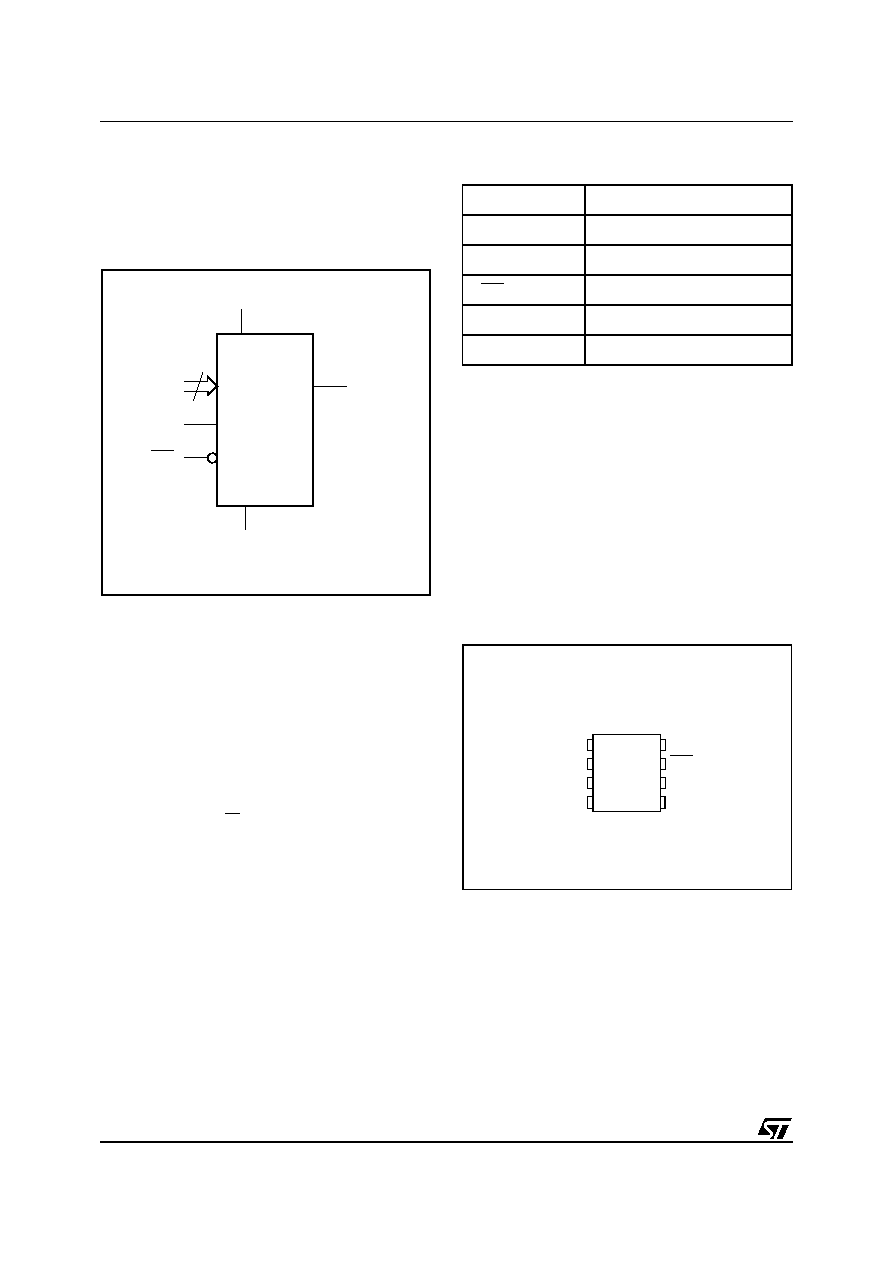

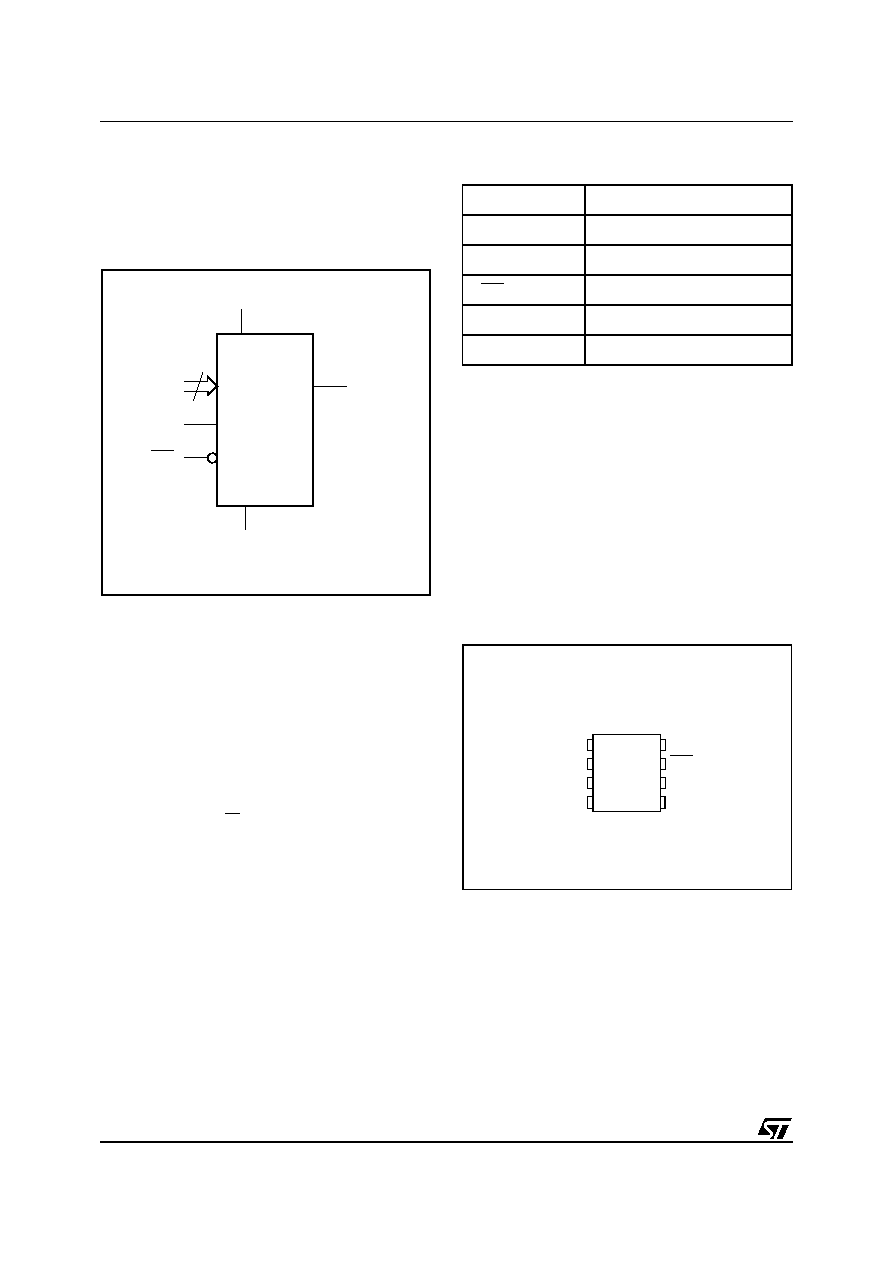

Figure 2. Logic Diagram

These devices are compatible with the I

2

C memo-

ry protocol. This is a two wire serial interface that

uses a bi-directional data bus and serial clock. The

devices carry a built-in 4-bit Device Type Identifier

code (1010) in accordance with the I

2

C bus defini-

tion.

The device behaves as a slave in the I

2

C protocol,

with all memory operations synchronized by the

serial clock. Read and Write operations are initiat-

ed by a Start condition, generated by the bus mas-

ter. The Start condition is followed by a Device

Select Code and RW bit (as described in Table 2),

terminated by an acknowledge bit.

When writing data to the memory, the device in-

serts an acknowledge bit during the 9

th

bit time,

following the bus master's 8-bit transmission.

When data is read by the bus master, the bus

master acknowledges the receipt of the data byte

in the same way. Data transfers are terminated by

a Stop condition after an Ack for Write, and after a

NoAck for Read.

Table 1. Signal Names

Power On Reset: V

CC

Lock-Out Write Protect

In order to prevent data corruption and inadvertent

Write operations during Power-up, a Power On

Reset (POR) circuit is included. The internal reset

is held active until V

CC

has reached the POR

threshold value, and all operations are disabled ≠

the device will not respond to any command. In the

same way, when V

CC

drops from the operating

voltage, below the POR threshold value, all oper-

ations are disabled and the device will not respond

to any command. A stable and valid V

CC

must be

applied before applying any logic signal.

Figure 3. DIP, SO and TSSOP Connections

Note: 1. See page 18 (onwards) for package dimensions, and how

to identify pin-1.

AI01844B

3

E0-E2

SDA

VCC

M24C64

M24C32

WC

SCL

VSS

E0, E1, E2

Chip Enable

SDA

Serial Data

SCL

Serial Clock

WC

Write Control

V

CC

Supply Voltage

V

SS

Ground

SDA

VSS

SCL

WC

E1

E0

VCC

E2

AI01845C

M24C64

M24C32

1

2

3

4

8

7

6

5

3/24

M24C64, M24C32

SIGNAL DESCRIPTION

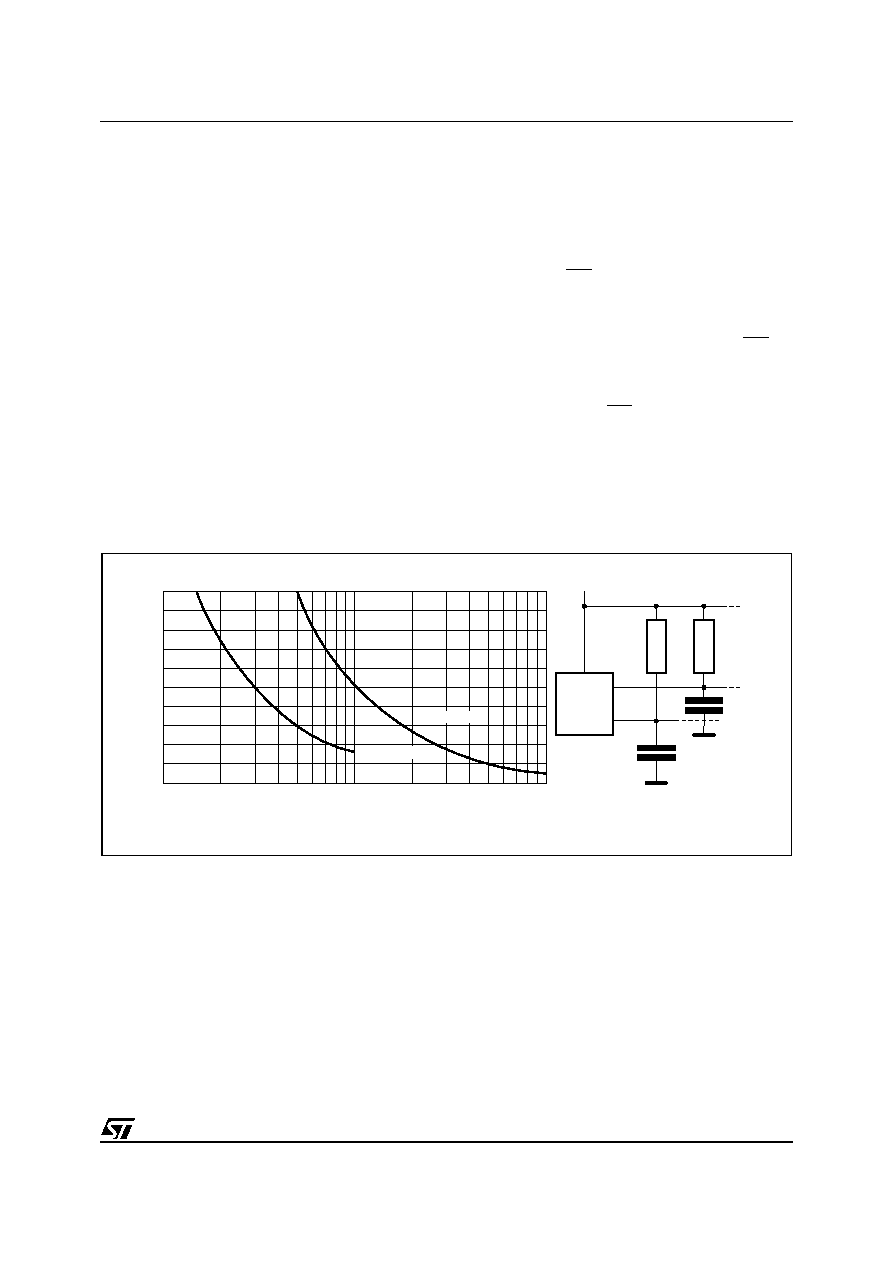

Serial Clock (SCL)

This input signal is used to strobe all data in and

out of the device. In applications where this signal

is used by slave devices to synchronize the bus to

a slower clock, the bus master must have an open

drain output, and a pull-up resistor must be con-

nected from Serial Clock (SCL) to V

CC

. (Figure 4

indicates how the value of the pull-up resistor can

be calculated). In most applications, though, this

method of synchronization is not employed, and

so the pull-up resistor is not necessary, provided

that the bus master has a push-pull (rather than

open drain) output.

Serial Data (SDA)

This bi-directional signal is used to transfer data in

or out of the device. It is an open drain output that

may be wire-OR'ed with other open drain or open

collector signals on the bus. A pull up resistor must

be connected from Serial Data (SDA) to V

CC

. (Fig-

ure 4 indicates how the value of the pull-up resistor

can be calculated).

Chip Enable (E0, E1, E2)

These input signals are used to set the value that

is to be looked for on the three least significant bits

(b3, b2, b1) of the 7-bit Device Select Code. These

inputs must be tied to V

CC

or V

SS

, to establish the

Device Select Code.

Write Control (WC)

This input signal is useful for protecting the entire

contents of the memory from inadvertent write op-

erations. Write operations are disabled to the en-

tire memory array when Write Control (WC) is

driven High. When unconnected, the signal is in-

ternally read as V

IL

, and Write operations are al-

lowed.

When Write Control (WC) is driven High, Device

Select and Address bytes are acknowledged,

Data bytes are not acknowledged.

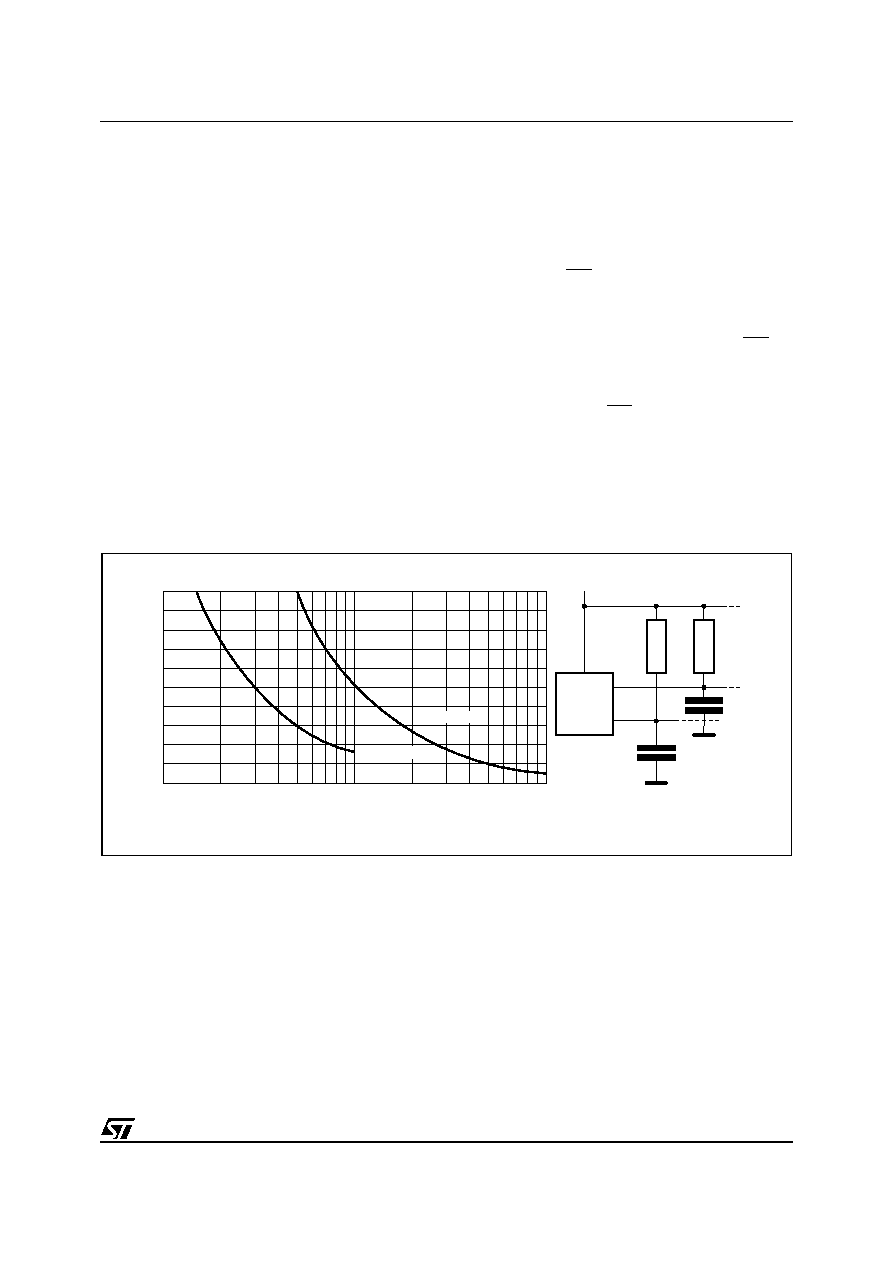

Figure 4. Maximum R

L

Value versus Bus Capacitance (C

BUS

) for an I

2

C Bus

AI01665

VCC

CBUS

SDA

RL

MASTER

RL

SCL

CBUS

100

0

4

8

12

16

20

CBUS (pF)

Maximum RP value (k

)

10

1000

fc = 400kHz

fc = 100kHz

M24C64, M24C32

4/24

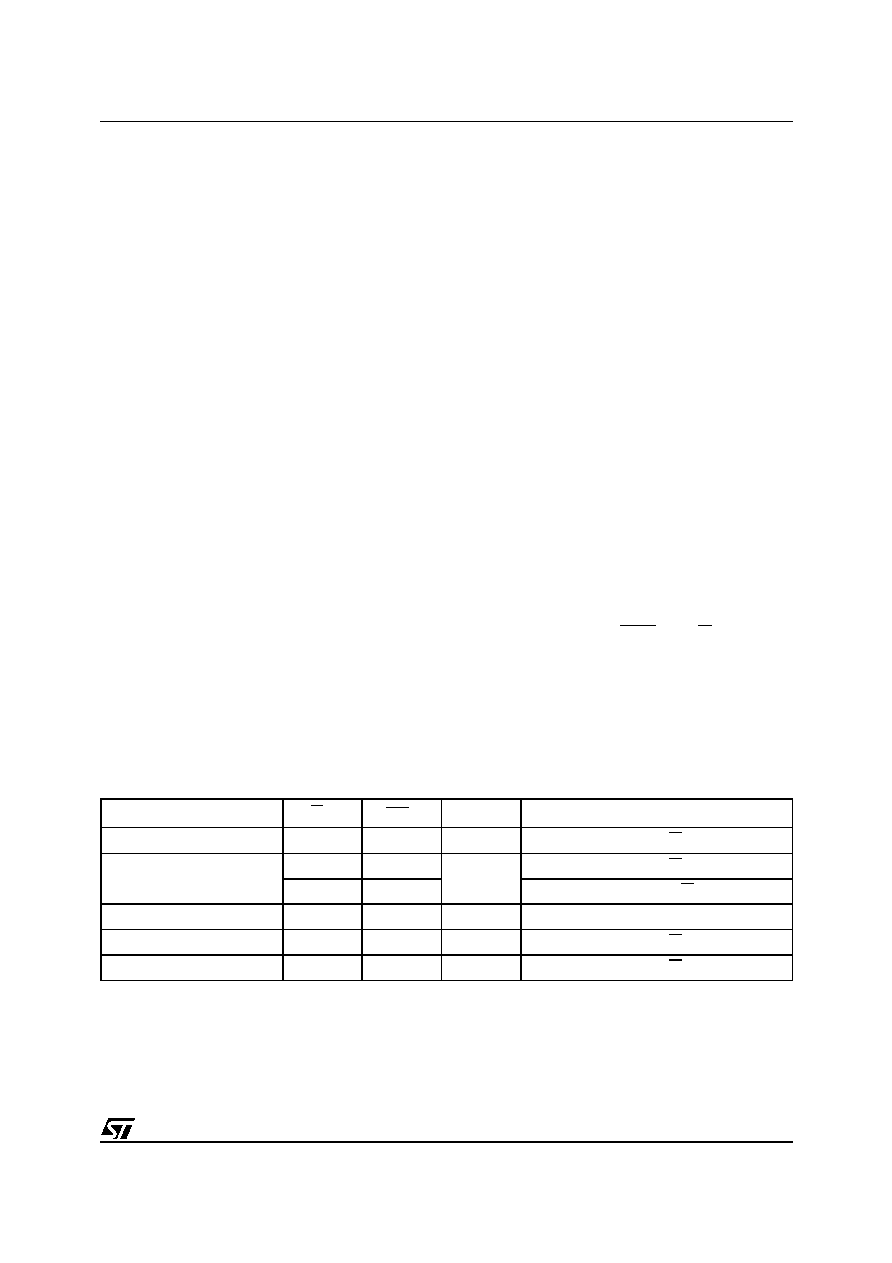

Figure 5. I

2

C Bus Protocol

Table 2. Device Select Code

Note: 1. The most significant bit, b7, is sent first.

2. E0, E1 and E2 are compared against the respective external pins on the memory device.

Table 3. Most Significant Byte

Table 4. Least Significant Byte

Device Type Identifier

1

Chip Enable Address

2

RW

b7

b6

b5

b4

b3

b2

b1

b0

Device Select Code

1

0

1

0

E2

E1

E0

RW

SCL

SDA

SCL

SDA

SDA

START

Condition

SDA

Input

SDA

Change

AI00792B

STOP

Condition

1

2

3

7

8

9

MSB

ACK

START

Condition

SCL

1

2

3

7

8

9

MSB

ACK

STOP

Condition

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

5/24

M24C64, M24C32

DEVICE OPERATION

The device supports the I

2

C protocol. This is sum-

marized in Figure 5. Any device that sends data on

to the bus is defined to be a transmitter, and any

device that reads the data to be a receiver. The

device that controls the data transfer is known as

the bus master, and the other as the slave device.

A data transfer can only be initiated by the bus

master, which will also provide the serial clock for

synchronization. The M24Cxx device is always a

slave in all communication.

Start Condition

Start is identified by a falling edge of Serial Data

(SDA) while Serial Clock (SCL) is stable in the

High state. A Start condition must precede any

data transfer command. The device continuously

monitors (except during a Write cycle) Serial Data

(SDA) and Serial Clock (SCL) for a Start condition,

and will not respond unless one is given.

Stop Condition

Stop is identified by a rising edge of Serial Data

(SDA) while Serial Clock (SCL) is stable and driv-

en High. A Stop condition terminates communica-

tion between the device and the bus master. A

Read command that is followed by NoAck can be

followed by a Stop condition to force the device

into the Stand-by mode. A Stop condition at the

end of a Write command triggers the internal EE-

PROM Write cycle.

Acknowledge Bit (ACK)

The acknowledge bit is used to indicate a success-

ful byte transfer. The bus transmitter, whether it be

bus master or slave device, releases Serial Data

(SDA) after sending eight bits of data. During the

9

th

clock pulse period, the receiver pulls Serial

Data (SDA) Low to acknowledge the receipt of the

eight data bits.

Data Input

During data input, the device samples Serial Data

(SDA) on the rising edge of Serial Clock (SCL).

For correct device operation, Serial Data (SDA)

must be stable during the rising edge of Serial

Clock (SCL), and the Serial Data (SDA) signal

must change

only

when Serial Clock (SCL) is driv-

en Low.

Memory Addressing

To start communication between the bus master

and the slave device, the bus master must initiate

a Start condition. Following this, the bus master

sends the Device Select Code, shown in Table 2

(on Serial Data (SDA), most significant bit first).

The Device Select Code consists of a 4-bit Device

Type Identifier, and a 3-bit Chip Enable "Address"

(E2, E1, E0). To address the memory array, the 4-

bit Device Type Identifier is 1010b.

Up to eight memory devices can be connected on

a single I

2

C bus. Each one is given a unique 3-bit

code on the Chip Enable (E0, E1, E2) inputs.

When the Device Select Code is received on Seri-

al Data (SDA), the device only responds if the Chip

Enable Address is the same as the value on the

Chip Enable (E0, E1, E2) inputs.

The 8

th

bit is the Read/Write bit (RW). This bit is

set to 1 for Read and 0 for Write operations.

If a match occurs on the Device Select code, the

corresponding device gives an acknowledgment

on Serial Data (SDA) during the 9

th

bit time. If the

device does not match the Device Select code, it

deselects itself from the bus, and goes into Stand-

by mode.

Table 5. Operating Modes

Note: 1. X =

V

IH

or V

IL

.

Mode

RW bit

WC

1

Bytes

Initial Sequence

Current Address Read

1

X

1

START, Device Select, RW = 1

Random Address Read

0

X

1

START, Device Select, RW = 0, Address

1

X

reSTART, Device Select, RW = 1

Sequential Read

1

X

1

Similar to Current or Random Address Read

Byte Write

0

V

IL

1

START, Device Select, RW = 0

Page Write

0

V

IL

32

START, Device Select, RW = 0