Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

1/55

August 2005

M28W320FST, M28W320FSB,

M28W640FSB, M28W640FST

32Mbit (2Mb x16) and 64Mbit (4Mb x16)

3V Supply, Boot Block, Secure Flash Memories

FEATURES SUMMARY

SUPPLY VOLTAGE

V

DD

= 2.7V to 3.6V Core Power Supply

V

DDQ

= 1.65V to 3.6V for Input/Output

V

PP

= 12V for fast Program (optional)

ACCESS TIME: 70ns

PROGRAMMING TIME:

10µs typical

Double Word Programming Option

Quadruple Word Programming Option

COMMON FLASH INTERFACE

MEMORY BLOCKS

Parameter Blocks (Top or Bottom

location)

Main Blocks

HARDWARE PROTECTION

V

PP

Pin for write protect of all blocks

SECURITY FEATURES

128 bit User-programmable OTP segment

64 bit Unique Device Identifier

KRYPTO Features:

Modify Protection,

Read Protection,

Device Authentication

AUTOMATIC STAND-BY MODE

PROGRAM and ERASE SUSPEND

100,000 PROGRAM/ERASE CYCLES per

BLOCK

ELECTRONIC SIGNATURE

Manufacturer Code: 20h

Device Codes:

M28W320FST: 880Ah,

M28W320FSB: 880Bh

M28W640FST: 8858h,

M28W640FSB: 8859h

ECOPACK

®

PACKAGE AVAILABLE

Figure 1. Package

BGA

TBGA64 (ZA)

10 x 13mm

M28W320FST, M28W320FSB, M28W640FST, M28W640FSB

2/55

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 1. Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

SUMMARY DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 1. M28W320FS and M28W640FS Memory Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 2. M28W320FS Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 3. M28W640FS Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 2. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 4. TBGA Connections (Top view through package) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 5. M28W320FST and M28W320FSB Block Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 6. M28W640FST and M28W640FSB Block Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 7. Protection Register Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Address Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Data Input/Output (DQ0-DQ15). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Chip Enable (E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Output Enable (G). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Write Enable (W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Reset (RP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

V

DD

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

V

DDQ

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

V

PP

Program Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

V

SS

Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

BUS OPERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Output Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Automatic Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 3. Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

HARDWARE PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

V

PP

V

PPLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

SECURITY FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

COMMAND INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Read Memory Array Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Read Status Register Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Read Electronic Signature Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3/55

M28W320FST, M28W320FSB, M28W640FST, M28W640FSB

Table 4. Command Codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Read CFI Query Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Block Erase Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Double Word Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Quadruple Word Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Clear Status Register Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Program/Erase Suspend Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Program/Erase Resume Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Protection Register Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 5. Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 6. Read Electronic Signature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 7. Read Protection Register and Protection Register Lock . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 8. Program, Erase Times and Program/Erase Endurance Cycles

. . . . . . . . . . . . . . . . . . . 18

STATUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Program/Erase Controller Status (Bit 7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Erase Suspend Status (Bit 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Erase Status (Bit 5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Program Status (Bit 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

V

PP

Status (Bit 3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Program Suspend Status (Bit 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Block Protection Status (Bit 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Reserved (Bit 0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 9. Status Register Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 10. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

DC and AC PARAMETERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 11. Operating and AC Measurement Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 8. AC Measurement I/O Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 9. AC Measurement Load Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 12. Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 13. DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 10.Read AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 14. Read AC Characteristics

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 11.Write AC Waveforms, Write Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 15. Write AC Characteristics, Write Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 12.Write AC Waveforms, Chip Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 16. Write AC Characteristics, Chip Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 13.Power-Up and Reset AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 17. Power-Up and Reset AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 14.TBGA64 - 10x13 active ball array, 1mm pitch, Bottom View Package Outline . . . . . . . . 30

M28W320FST, M28W320FSB, M28W640FST, M28W640FSB

4/55

Table 18. TBGA64 - 10x13 active ball array, 1mm pitch, Package Mechanical Data . . . . . . . . . . . 30

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 19. Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 20. Daisy Chain Ordering Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

APPENDIX A.BLOCK ADDRESS TABLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 21. Top Boot Block Addresses, M28W320FST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 22. Bottom Boot Block Addresses, M28W320FSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 23. Top Boot Block Addresses, M28W640FST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 24. Bottom Boot Block Addresses, M28W640FSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

APPENDIX B.COMMON FLASH INTERFACE (CFI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 25. Query Structure Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 26. CFI Query Identification String. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 27. CFI Query System Interface Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 28. Device Geometry Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 29. Primary Algorithm-Specific Extended Query Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 30. Security Code Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

APPENDIX C.FLOWCHARTS AND PSEUDO CODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 15.Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 16.Double Word Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 17.Quadruple Word Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 18.Program Suspend & Resume Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . 48

Figure 19.Erase Flowchart and Pseudo Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 20.Erase Suspend & Resume Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 21.Protection Register Program Flowchart and Pseudo Code. . . . . . . . . . . . . . . . . . . . . . . 51

APPENDIX D.COMMAND INTERFACE AND PROGRAM/ERASE CONTROLLER STATE. . . . . . . . 52

Table 31. Write State Machine Current/Next, sheet 1 of 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 32. Write State Machine Current/Next, sheet 2 of 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 33. Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

5/55

M28W320FST, M28W320FSB, M28W640FST, M28W640FSB

SUMMARY DESCRIPTION

The M28W320FS and M28W640FS are 32 Mbit

(2Mbit x 16) and 64 Mbit (4Mbit x 16) Secure Flash

memories. The devices can be erased electrically

at block level and programmed in-system on a

Word-by-Word basis using a 2.7V to 3.6V V

DD

supply for the circuitry and a 1.65V to 3.6V V

DDQ

supply for the Input/Output pins. An optional 12V

V

PP

power supply is provided to speed up custom-

er programming.

The M28W320FS and M28W640FS feature

32Mbit and 64 Mbits respectively and have an

asymmetrical block architecture with 4 KWord Pa-

rameter Blocks and 32 KWord Main Blocks. The

M28W320FST and M28W640FST have the Pa-

rameter Blocks at the top of the memory address

space while the M28W320FSB and

M28W640FSB locate the Parameter Blocks start-

ing from the bottom. Refer to

Table 1.

,

Figure 5.

and

Figure 6.

for a detailed description of the de-

vices memory architecture and map.

All devices are equipped with hardware and soft-

ware block protection features to avoid unwanted

program/erase (modify) or read of the Flash mem-

ory content:

Hardware Protection:

When V

PP

V

PPLK

all blocks are protected

against program or erase.

Software Protection thanks to KRYPTO

Security Features:

Modify Protection: volatile and non-

volatile.

Read Protection.

The KRYPTO Security features are described in a

dedicated Application Note. Please contact STMi-

croelectronics for further details.

Two registers are available for protection purpose:

The Protection Register

The KRYPTO Protection Register.

The Protection Register is a 192 bit Protection

Register to increase the protection of a system de-

sign. The Protection Register is divided into a 64

bit segment and a 128 bit segment. The 64 bit seg-

ment contains a unique device number written by

ST, while the second one is one-time-programma-

ble by the user. The user programmable segment

can be permanently protected.

Figure 7.

, shows

the Protection Register Memory Map.

The KRYPTO Protection Register is used to man-

age the Modify and Read protection modes. It also

features a Device Authentication mechanism. The

KRYPTO Protection Register is described in a

dedicated Application Note. Please contact STMi-

croelectronics for further details.

Each block can be erased separately. Erase can

be suspended in order to perform either read or

program in any other block and then resumed.

Program can be suspended to read data in any

other block and then resumed. Each block can be

programmed and erased over 100,000 cycles.

Program and Erase commands are written to the

Command Interface of the memory. An on-chip

Program/Erase Controller takes care of the tim-

ings necessary for program and erase operations.

The end of a program or erase operation can be

detected and any error conditions identified. The

command set required to control the memory is

consistent with JEDEC standards.

All the devices are offered in a TBGA64 (10 x

13mm) package.

In order to meet environmental requirements, ST

offers the M28W320FS and M28W640FS in ECO-

PACK

®

packages. ECOPACK packages are

Lead-free. The category of second Level Intercon-

nect is marked on the package and on the inner

box label, in compliance with JEDEC Standard

JESD97. The maximum ratings related to solder-

ing conditions are also marked on the inner box la-

bel.

ECOPACK is an ST trademark. ECOPACK speci-

fications are available at: www.st.com.

All devices are supplied with all the bits erased

(set to '1').

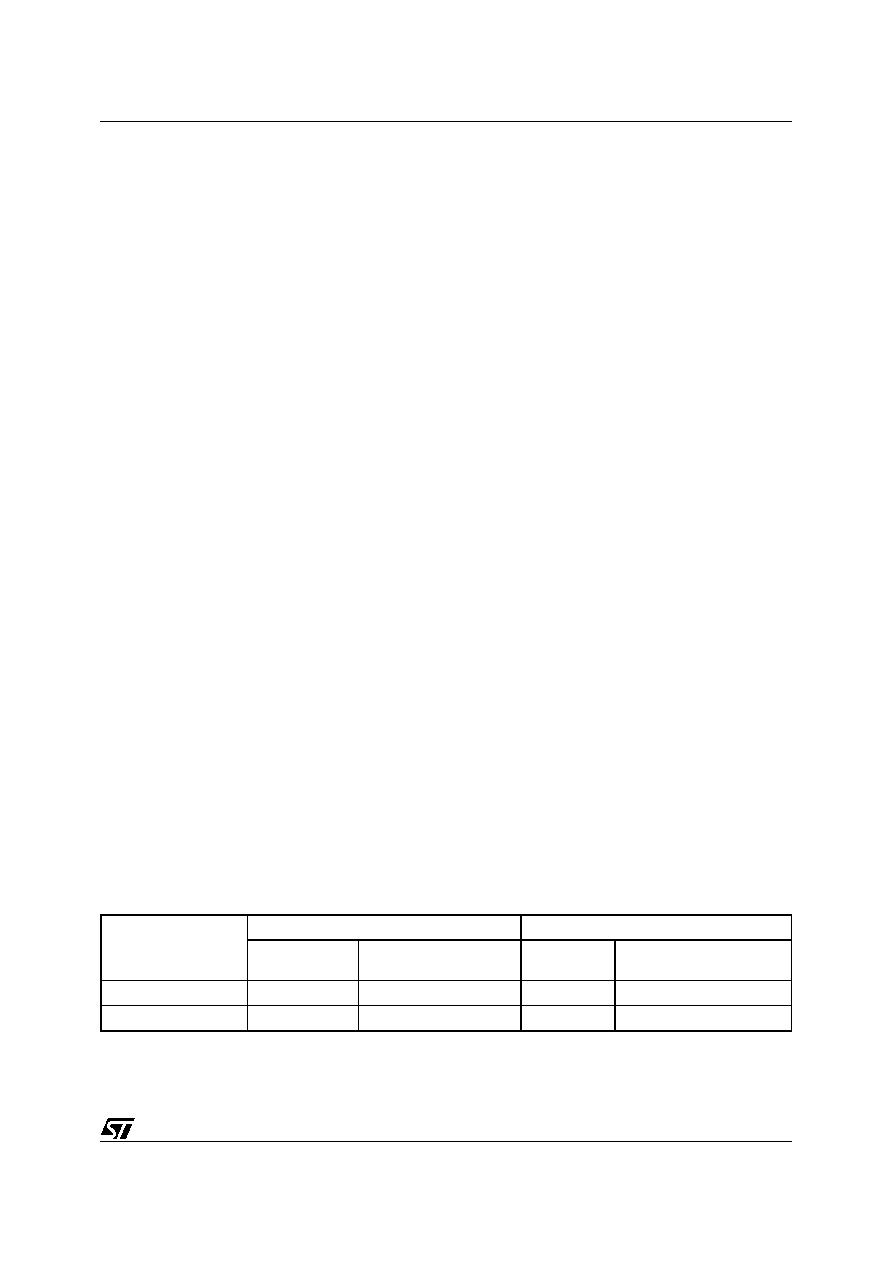

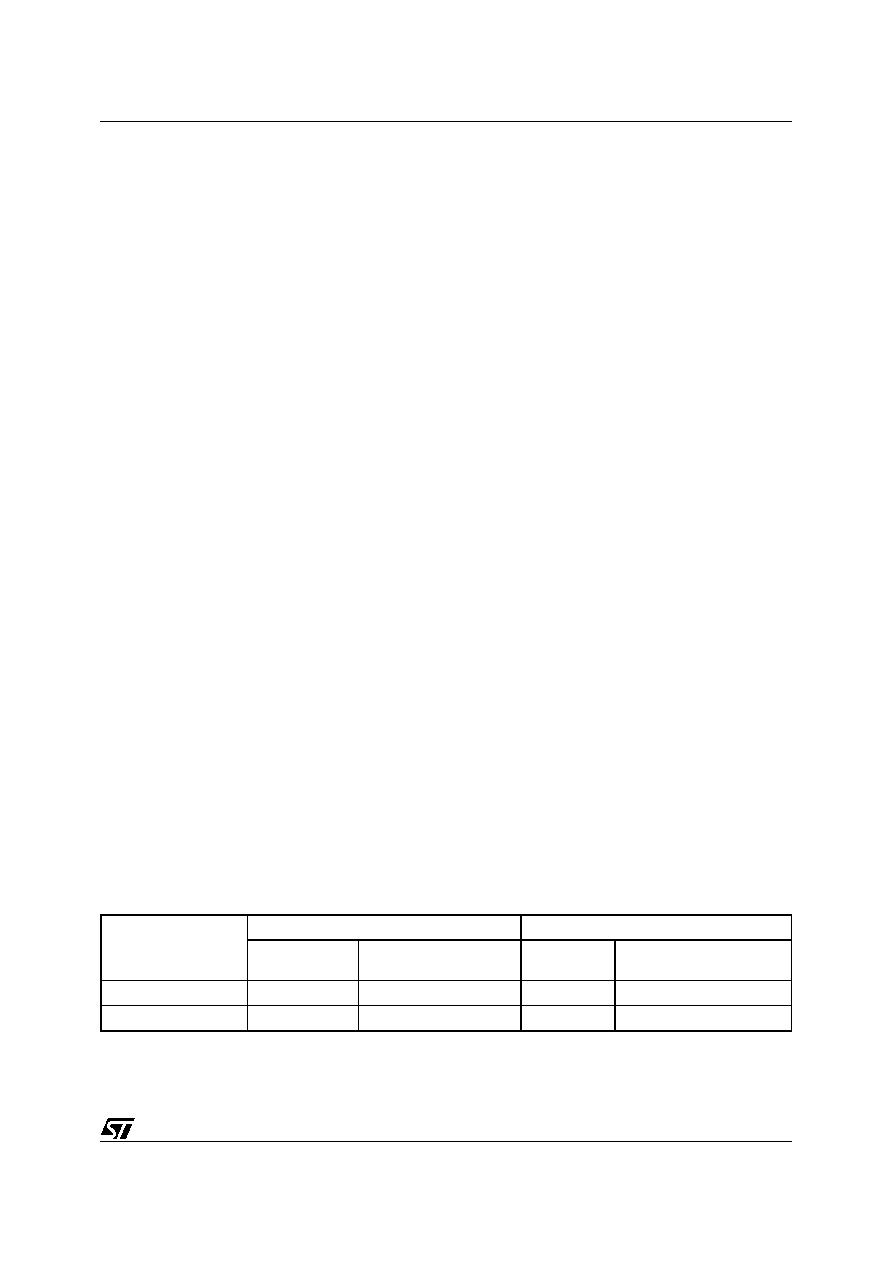

Table 1. M28W320FS and M28W640FS Memory Architecture

Note: 1. Erasable Block size.

Device

Parameter Blocks

Main Blocks

No. of Blocks

Block Size

(1)

No. of

Blocks

Block Size

M28W320FS

8

4 KWords

63

32 KWords

M28W640FS

8

4 KWords

127

32 KWords

Document Outline