| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ST6242BQ1 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

August 1999

1/68

Rev. 2.6

ST62T42B/E42B

8-BIT OTP/EPROM MCU WITH LCD DRIVER,

EEPROM AND A/D CONVERTER

s

3.0 to 6.0V Supply Operating Range

s

8 MHz Maximum Clock Frequency

s

-40 to +85

∞

C Operating Temperature Range

s

Run, Wait and Stop Modes

s

5 Interrupt Vectors

s

Look-up Table capability in Program Memory

s

Data Storage in Program Memory:

User selectable size

s

Data RAM: 192 bytes

s

Data EEPROM: 128 bytes

s

User Programmable Options

s

18 I/O pins, fully programmable as:

≠ Input with pull-up resistor

≠ Input without pull-up resistor

≠ Input with interrupt generation

≠ Open-drain or push-pull output

≠ Analog Input

≠ LCD segments (8 combiport lines)

s

4 I/O lines can sink up to 20mA to drive LEDs or

TRIACs directly

s

Two

8-bit

Timer/Counter

with

7-bit

programmable prescaler

s

Digital Watchdog

s

8-bit A/D Converter with 6 analog inputs

s

8-bit Synchronous Peripheral Interface (SPI)

s

LCD driver

with 40

segment outputs,

4

backplane outputs and selectable multiplexing

ratio.

s

On-chip Clock oscillator can be driven by Quartz

Crystal or Ceramic resonator

s

One external Non-Maskable Interrupt

s

ST6242-EMU2 Emulation and Development

System (connects to an MS-DOS PC via a

parallel port).

DEVICE SUMMARY

(See end of Datasheet for Ordering Information)

PQFP64

CQFP64W

DEVICE

OTP

(Bytes)

EPROM

(Bytes)

I/O Pins

ST62T42B

7948

-

10 to 18

ST62E42B

7948

10 to 18

1

2/68

Table of Contents

68

Document

Page

2

ST62T42B/E42B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1 GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.2 PIN DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.3 MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.3.2 Program Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.3.3 Data Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.3.4 Stack Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.3.5 Data Window Register (DWR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.3.6 Data RAM/EEPROM Bank Register (DRBR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.3.7 EEPROM Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.4 PROGRAMMING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.4.1 Option Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.4.2 Program Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.4.3 EEPROM Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.4.4 EPROM Erasing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2 CENTRAL PROCESSING UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.2 CPU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3 CLOCKS, RESET, INTERRUPTS AND POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . 18

3.1 CLOCK SYSTEM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.1.1 Main Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.2 RESETS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.2.1 RESET Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.2.2 Power-on Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.2.3 Watchdog Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.2.4 Application Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.2.5 MCU Initialization Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.3 DIGITAL WATCHDOG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.3.1 Digital Watchdog Register (DWDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.3.2 Application Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.4 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.4.1 Interrupt request . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.4.2 Interrupt Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.4.3 Interrupt Option Register (IOR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.4.4 Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.5 POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.5.1 WAIT Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.5.2 STOP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.5.3 Exit from WAIT and STOP Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3/68

Table of Contents

Document

Page

3

4 ON-CHIP PERIPHERALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

4.1 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

4.1.1 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.1.2 Safe I/O State Switching Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

5 I/O PORTS (Cont'd) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

5.0.1 LCD alternate functions (combiports) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

5.0.2 SPI alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

5.0.3 I/O Port Option Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.0.4 I/O Port Data Direction Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.0.5 I/O Port Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.1 TIMER 1 & 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.1.1 TIMER 1 & 2 Operating Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.1.2 Timer Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.1.3 Application Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.1.4 TIMER 1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

5.1.5 TIMER 2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

5.2

A/D CONVERTER (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.2.1 Application Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.3 SERIAL PERIPHERAL INTERFACE (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.4 LCD CONTROLLER-DRIVER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.4.1 Multiplexing ratio and frame frequency setting . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

5.4.2 Segment and common plates driving . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

5.4.3 LCD RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

5.4.4 Stand by or STOP operation mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

5.4.5 LCD Mode Control Register (LCDCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6 SOFTWARE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

6.1 ST6 ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

6.2 ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

6.3 INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

7 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

7.1 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

7.2 RECOMMENDED OPERATING CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

7.3 DC ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

7.4 AC ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

7.5 A/D CONVERTER CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

7.6 TIMER CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

7.7 SPI CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

7.8 LCD ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

7.9 PSS ELECTRICAL CHARACTERISTICS (WHEN AVAILABLE) . . . . . . . . . . . . . . . . . . . . 61

8 GENERAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

8.1 PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

8.2 PACKAGE THERMAL CHARACTERISTIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

8.3 ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

4/68

Table of Contents

68

Document

Page

4

ST6242B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

1 GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

1.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

1.2 ROM READOUT PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

1.3 ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

1.3.1 Transfer of Customer Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

1.3.2 Listing Generation and Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

5/68

ST62T42B/E42B

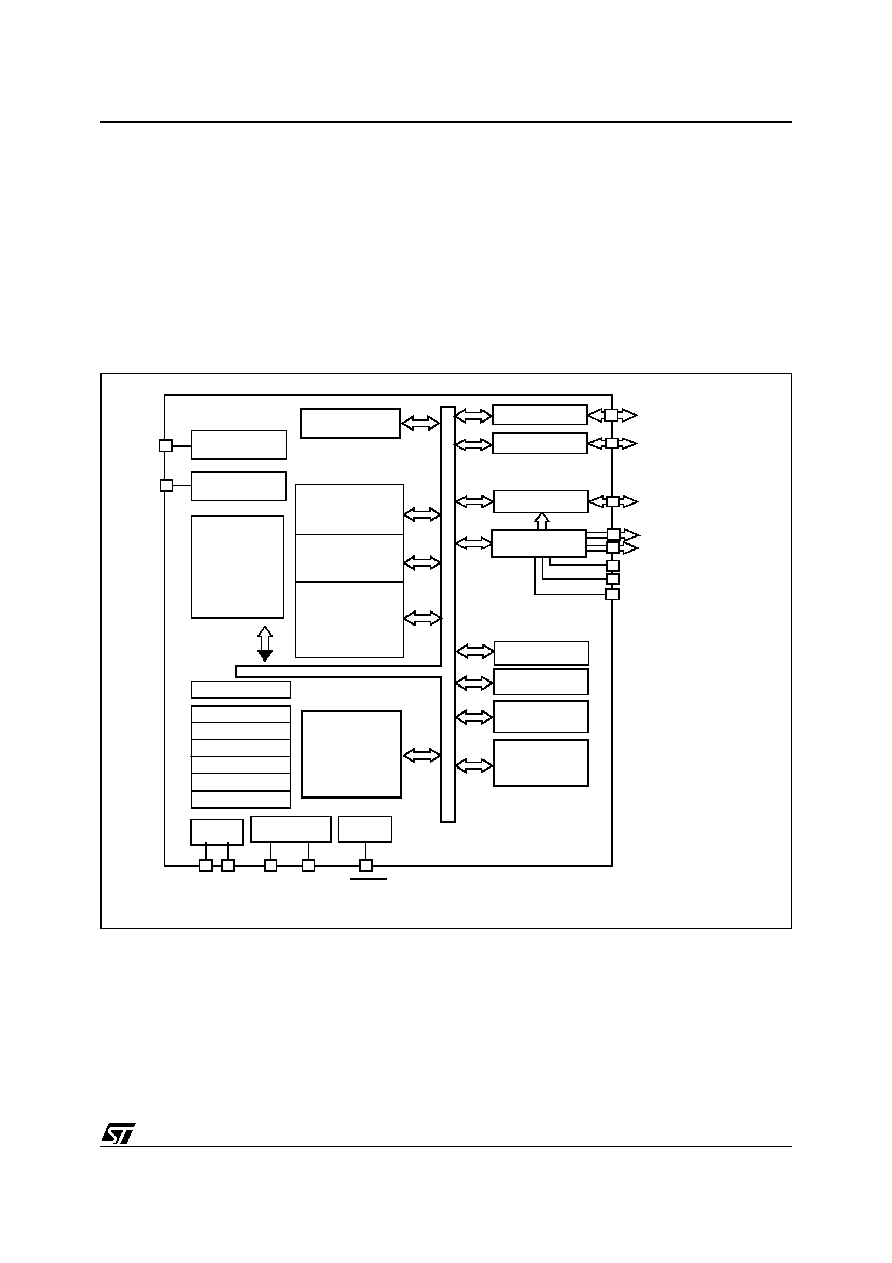

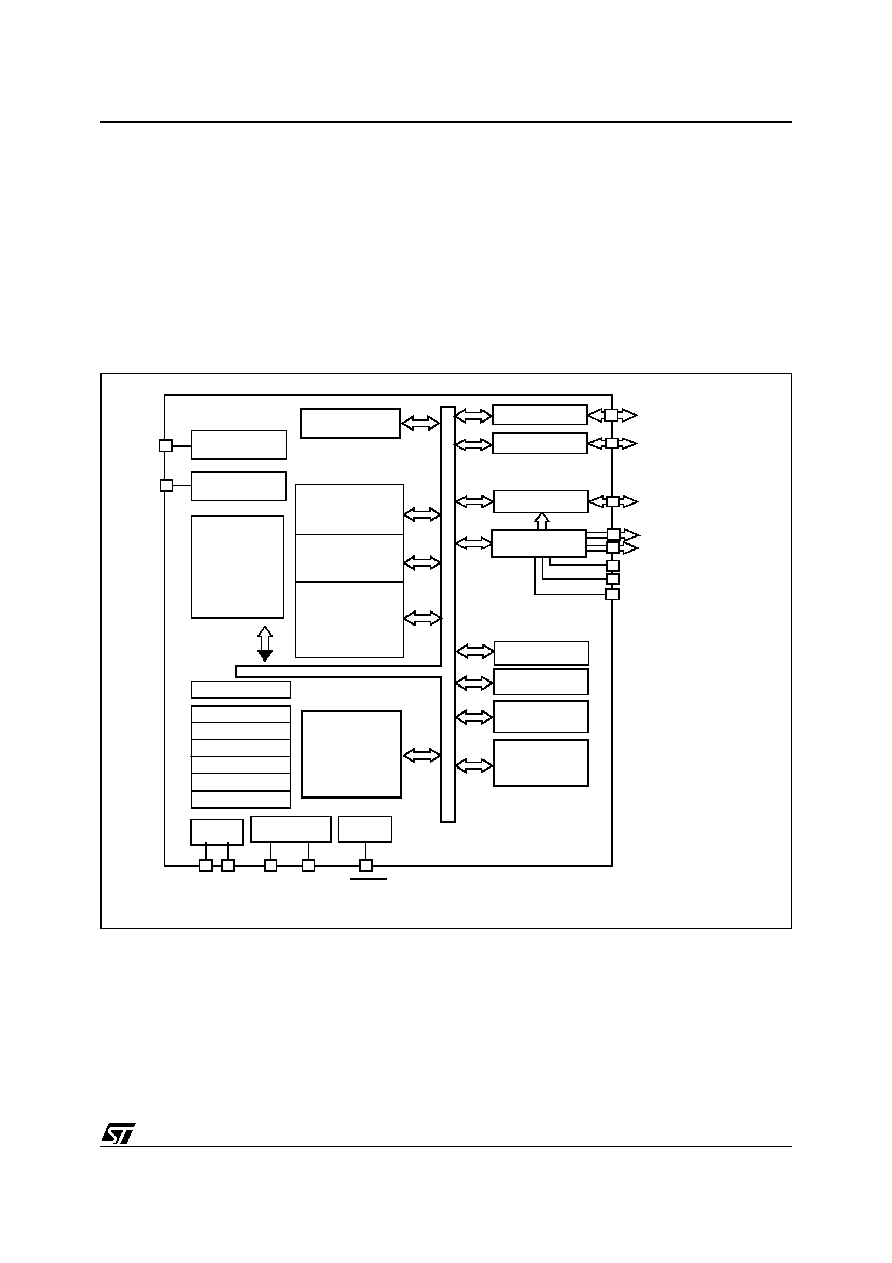

1 GENERAL DESCRIPTION

1.1 INTRODUCTION

The ST62T42B and ST62E42B devices are low

cost members of the ST62xx 8-bit HCMOS family

of microcontrollers, which are targeted at low to

medium complexity applications. All ST62xx de-

vices are based on a building block approach: a

common core is surrounded by a number of on-

chip peripherals.

The ST62E42B is the erasable EPROM version of

the ST62T42B device, which may be used to em-

ulate the ST62T42B device, as well as the respec-

tive ST6242B ROM devices.

Figure 1. Block Diagram

TEST

NMI

INTERRUPT

PROGRAM

PC

STACK LEVEL 1

STACK LEVEL 2

STACK LEVEL 3

STACK LEVEL 4

STACK LEVEL 5

STACK LEVEL 6

POWER

SUPP LY

OSCILLATOR

RESET

DATA ROM

USER

SELECTABLE

DATA RAM

PORT A

PORT B

TIMER 1

DIGITAL

8 BIT CORE

TEST/V

PP

8-BIT

A/D CONVERTER

PA4..PA7/Ain

V

DD

V

SS

OSCin OSCout

RESET

WATCHD OG

Memory

PORT C

SPI (SERIAL

PERI PHERAL

INTE RFACE)

192 Bytes

7948 bytes

DATA EEPROM

128 Bytes

PB2..PB3/Ai n

PC0..PC7/S33..S40

S9..S32, S41..S48

COM1..COM4

(V

PP

on EPROM/OTP versions only)

PB4/20mA Sink

PB5/Scl/20mA Sink

PB6/Sin/20mA Sink

PB7/Sout/20mA Sink

VLCD

VLCD1/3

VLCD2/3

TIMER 2

LCD DRIVER

VA0479M

5