Rev. 2.7

June 2003

1/158

ST72589BW,

ST72389BW

8-BIT MCU WITH NESTED INTERRUPTS, DOT MATRIX LCD,

ADC, TIMERS, PWM-BRM, SPI, SCI, I�C, CAN INTERFACES

DATASHEET

s

16K ROM or 24 Kbytes EPROM/OTP/

FASTROM

s

Master Reset and Power-on Reset

s

Low consumption resonator main oscillator

s

4 Power saving modes

s

Nested interrupt controller

s

NMI dedicated non maskable interrupt pin

s

31 multifunctional bidirectional I/O lines with:

� external interrupt capability (5 vectors)

� 21 alternate function lines

s

LCD driver with 60 segment outputs and 8

backplane outputs able to drive up to 60x8 (480)

or 60x4 (240) LCD displays

s

Real time base, Beep and Clock-out capabilities

s

Software watchdog reset

s

Two 16-bit timers with:

� 2 input captures

� 2 output compares

� external clock input on one timer

� PWM and Pulse generator modes

s

10-bit PWM (DAC) with 4 dedicated output pins

s

SPI synchronous serial interface

s

SCI asynchronous serial interface

s

I2C multi master / slave interface

s

CAN interface

s

8-bit ADC with 5 dedicated input pins

s

8-bit Data Manipulation

s

63 Basic Instructions

s

17 main Addressing Modes

s

8 x 8 Unsigned Multiply Instruction

s

True Bit Manipulation

s

Full hardware/software development package

Device Summary

PQFP128

14 x 20

Features

ST72589BW5

ST72389BW4

Program memory - bytes

24K OTP/FASTROM

16K ROM

RAM (stack) - bytes

1024 (256)

512 (256)

Std. Peripherals

LCD 60x8, Watchdog,

16-bit Timers, PWM-BRM,

SPI, SCI, I2C, CAN, ADC

LCD 60x8, Watchdog,

16-bit Timers,

SPI, SCI, ADC

Operating Supply

4.5V to 5.5V

CPU Frequency

4 to 8 MHz (with 8 to 16 MHz oscillator)

Temperature Range

-40�C to +85�C

Packages

PQFP128

Development device

ST72E589BW5

1

Table of Contents

158

2/158

2

1 GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

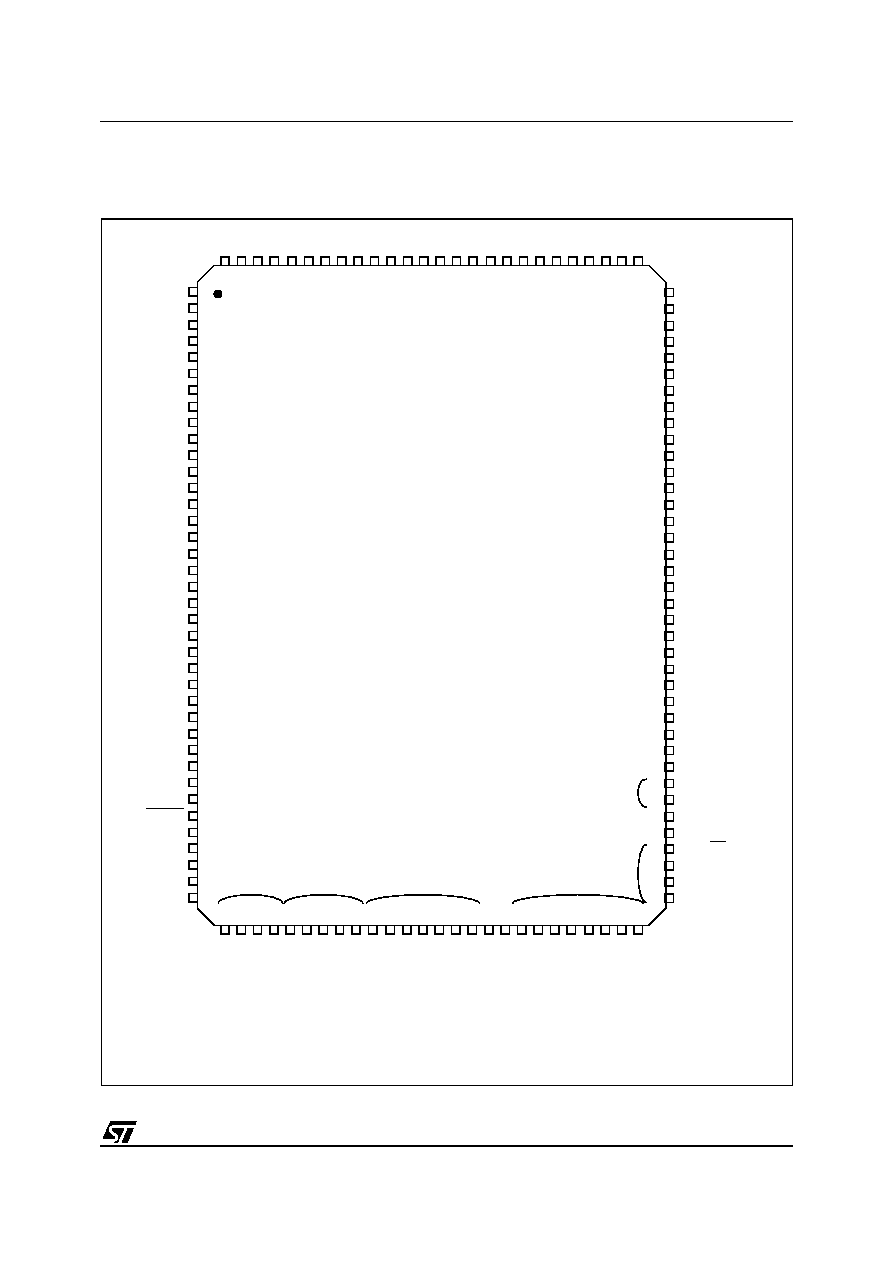

1.2 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.3 REGISTER & MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.4 MEMORIES AND PROGRAMMING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2 CENTRAL PROCESSING UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.2 MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.3 CPU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3 SUPPLY, RESET AND CLOCK MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1 RESET MANAGER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 7

3.2 LOW CONSUMPTION OSCILLATOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.3 MAIN CLOCK CONTROLLER (MCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4 INTERRUPTS & POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.1 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.2 POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

5 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.2 FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.3 I/O PORT IMPLEMENTATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6 MISCELLANEOUS REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.1 I/O PORT INTERRUPT SENSITIVITY DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.2 I/O PORT ALTERNATE FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.3 MISCELLANEOUS REGISTERS DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

7 ON-CHIP PERIPHERALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7.1 LCD DRIVER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7.2 WATCHDOG TIMER (WDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.3 16-BIT TIMER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

7.4 PWM/BRM GENERATOR (DAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

7.5 SERIAL PERIPHERAL INTERFACE (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

7.6 SERIAL COMMUNICATIONS INTERFACE (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

7.7 I2C BUS INTERFACE (I2C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.8 CONTROLLER AREA NETWORK (CAN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.9 8-BIT A/D CONVERTER (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

8 INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

8.1 CPU ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

8.2 INSTRUCTION GROUPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

9 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

9.1 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

9.2 RECOMMENDED OPERATING CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

9.3 TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

9.4 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table of Contents

3/158

3

9.5 I/O PORTS CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

9.6 SUPPLY, RESET AND CLOCK CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . 143

9.7 MEMORY AND PERIPHERAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

10 PACKAGE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

10.1 PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

11 DEVICE CONFIGURATION AND ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . 154

11.1 ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE . . . . . . . . . . . . 154

11.2 ST7 APPLICATION NOTES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

12 SUMMARY OF CHANGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

ST72589BW, ST72389BW

4/158

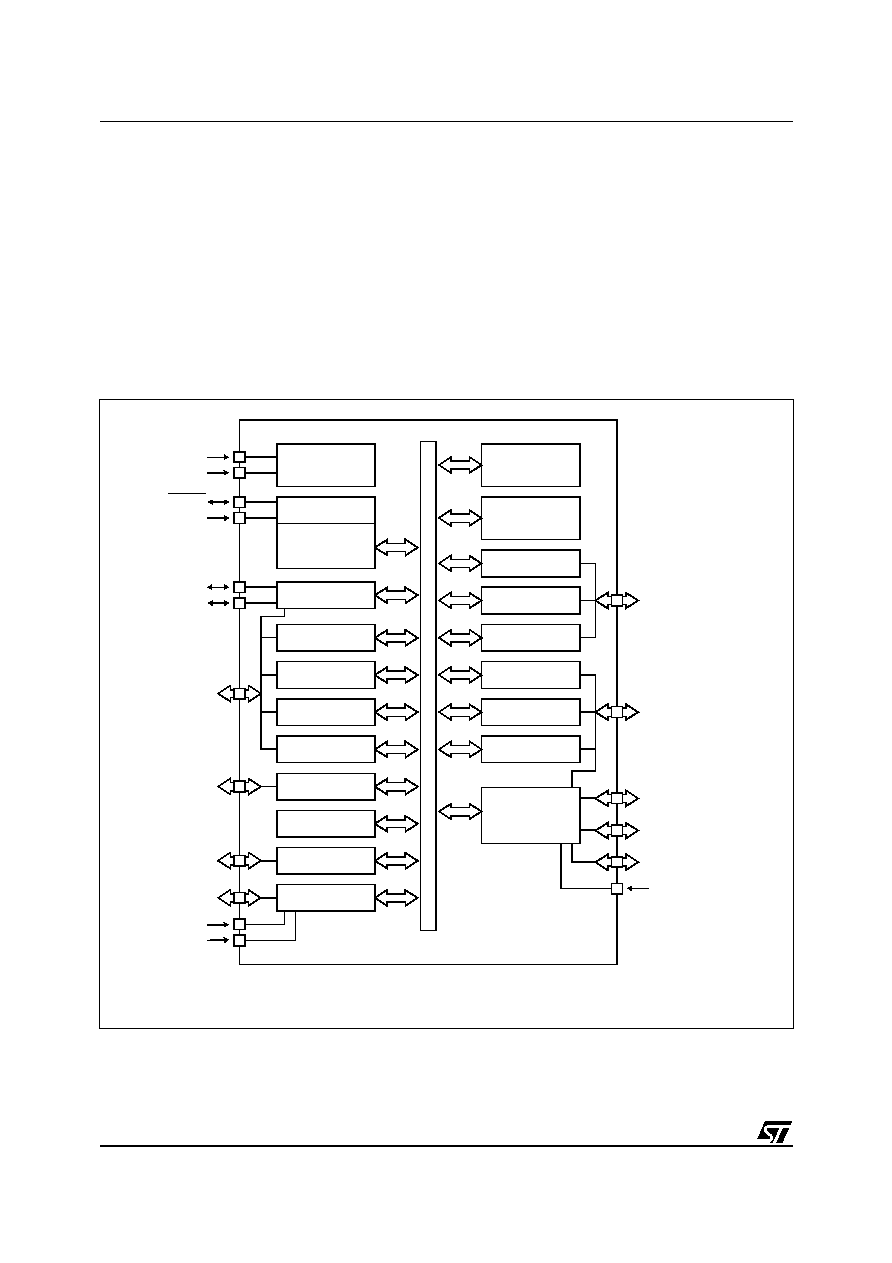

1 GENERAL DESCRIPTION

1.1 INTRODUCTION

The ST72589W and ST72389W Microcontroller

Units are members of the ST7 family of Microcon-

trollers dedicated to high-end applications with

LCD driver capability.

These devices are based on an industry-standard

8-bit core and feature an enhanced instruction set.

Under software control, these microcontrollers

may be placed in either WAIT, SLOW, ACTIVE-

HALT or HALT modes, thus reducing power con-

sumption.

The enhanced instruction set and addressing

modes afford real programming potential. In addi-

tion to standard 8-bit data management, these mi-

crocontrollers feature true bit manipulation, 8x8

unsigned multiplication and indirect addressing

modes.

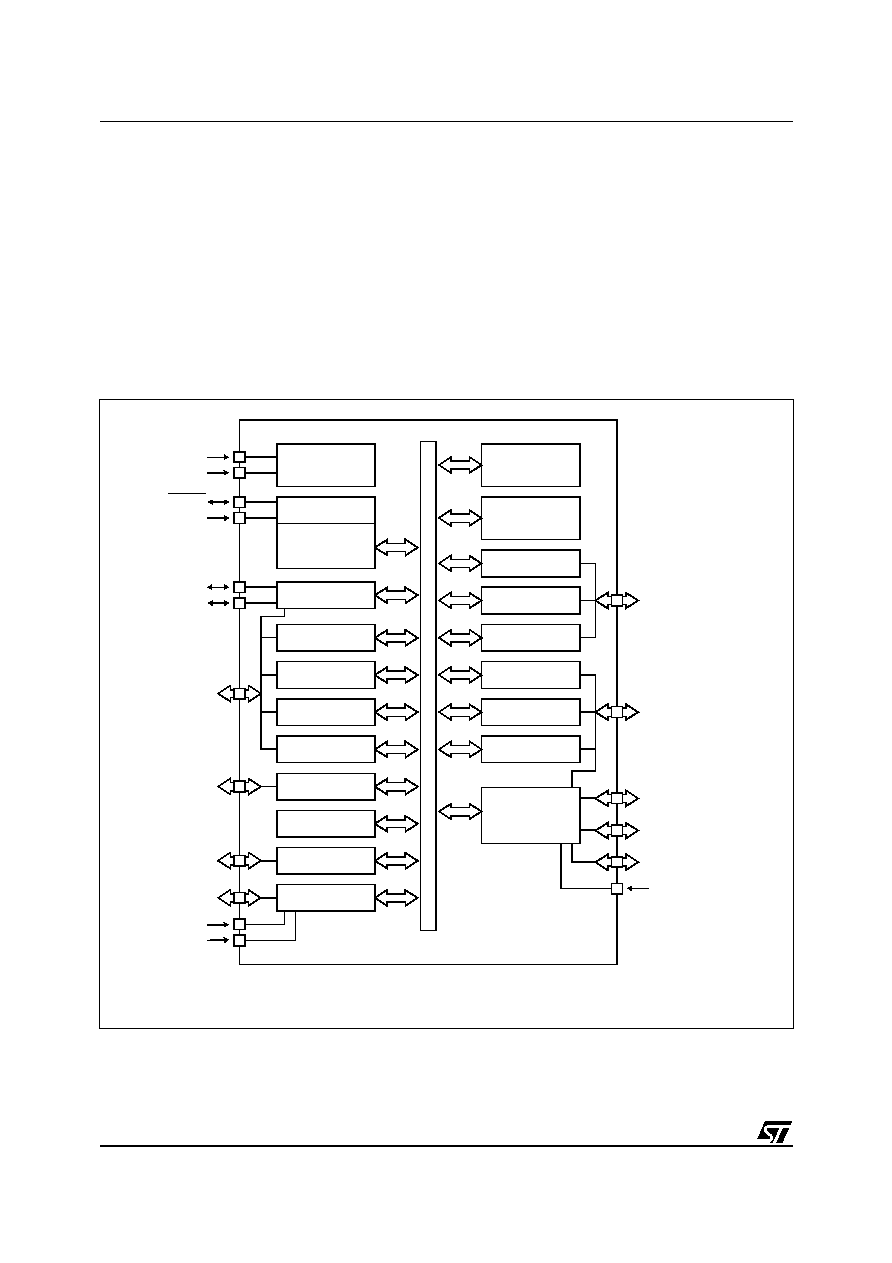

Figure 1. Device Block Diagram

8-BIT CORE

ALU

A

DDRE

S

S

A

ND DA

T

A

B

U

S

OSC2

OSC1

RESET

MAIN OSC

CONTROL

EPROM

24K

V

DD

NMI

PORT C

PC0 -> PC7

(8-bit)

SCI

BEEP

TIMER A

RAM

512 or 1K

POWER

SUPPLY

V

SS

WATCHDOG

PWM-BRM*

8-bit ADC

PWM0 -> PWM3

(4-bit)

AIN0 -> AIN4

(5-channel)

V

DDA

V

SSA

PORT B

PB0 -> PB6

(7-bit)

TIMER B

CAN*

PORT D

PD0 -> PD7

(8-bit)

SPI

I2C*

LCD DRIVER

+

LCD RAM (60x8)

S1 -> S60

(60-segment)

COM1 -> COM8

(60-common)

GLCD

VLCD, VLCD3/4,

VLCD1/2, VLCD1/4

PORT A

PA0 -> PA7

(8-bit)

*available on ST72589 version only

4