June 2003

1/80

Rev. 2.1

ST7261

LOW SPEED USB 8-BIT MCU WITH 3 ENDPOINTS,

ROM MEMORY, LVD, WDG, TIMER

s

Memories

� 4K Program memory (ROM) with read-write

protection.

In-Circuit programming for Flash versions

� 256 bytes RAM memory (128-byte stack)

s

Clock, Reset and Supply Management

� Enhanced Reset System (Power On Reset)

� Low Voltage Detector (LVD)

� Clock-out capability

� 6 or 12 MHz Oscillator (8, 4, 2, 1 MHz internal

freq.)

� 3 Power saving modes: Halt, Wait and Slow

s

USB (Universal Serial Bus) Interface

� DMA for low speed applications compliant

with USB 1.5 Mbs specification (v 1.1) and

USB HID specification (v 1.0):

� Integrated 3.3V voltage regulator and trans-

ceivers

� Suspend and Resume operations

� 3 Endpoints

s

11 I/O Ports

� 11 multifunctional bidirectional I/O lines

� Up to 7 External interrupts (2 vectors)

� 8 high sink outputs (8mA@0.4 V/20mA@1.3)

s

2 Timers

� Configurable watchdog timer (8 to 500ms

timeout)

� 8-bit Time Base Unit (TBU) for generating pe-

riodic interrupts

s

Instruction Set

� 8-bit data manipulation

� 63 basic instructions

� 17 main addressing modes

� 8 x 8 unsigned multiply instruction

� True bit manipulation

s

Nested interrupts

s

Development Tools

� Full hardware/software development package

Device Summary

SO20

PDIP20

Features

ST72611F1

Program memory - bytes

4K ROM

RAM (stack) - bytes

256 (128)

Peripherals

USB, Watchdog, Low Voltage Detector, Time Base Unit

I/Os

11

Operating Supply

4.0V to 5.5V

CPU Frequency

Up to 8 MHz (with 6 or 12 MHz oscillator)

Operating Temperature

0�C to +70�C

Packages

PDIP20/SO20

1

Table of Contents

80

2/80

1

1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

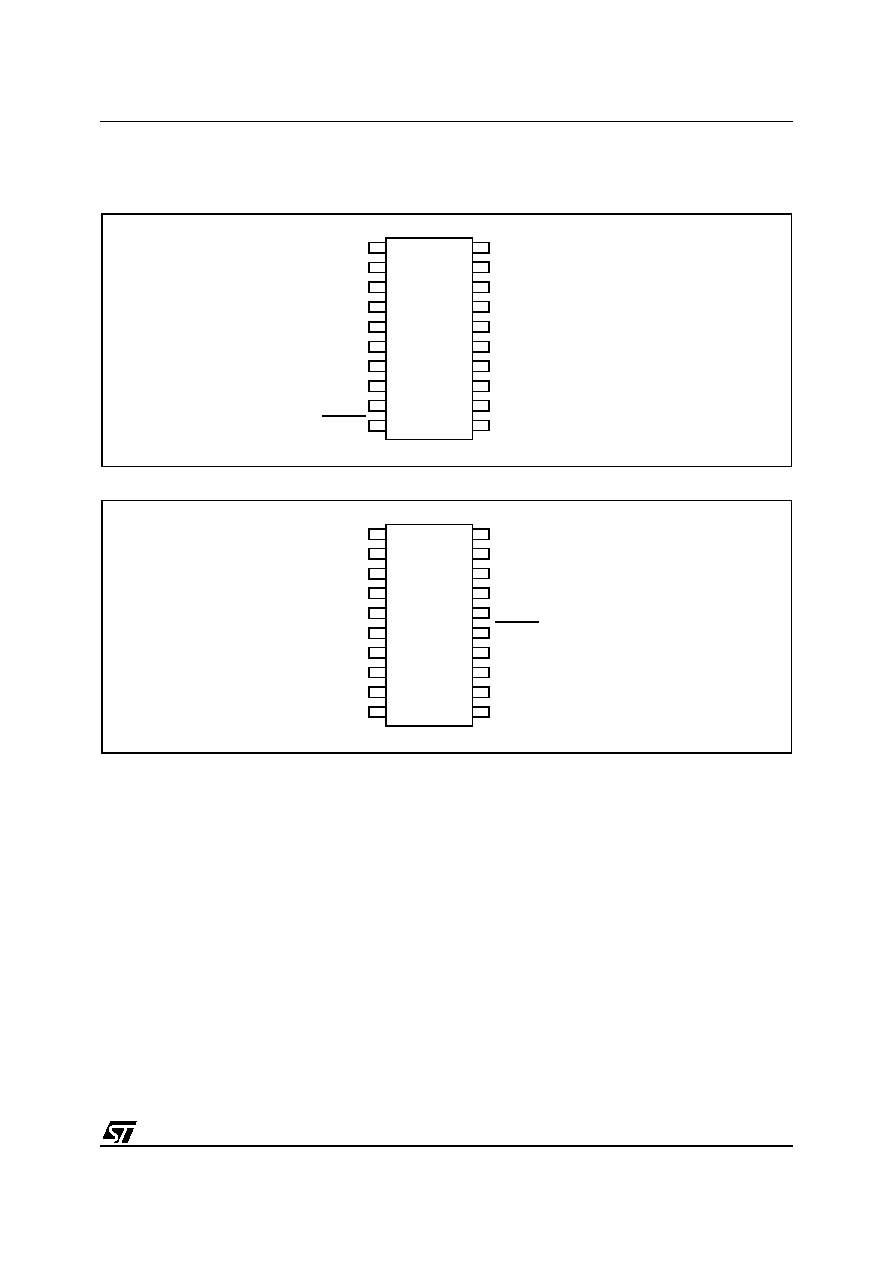

2 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.1 PCB LAYOUT RECOMMENDATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3 REGISTER & MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4 CENTRAL PROCESSING UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.2 MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.3 CPU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

5 CLOCKS AND RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5.1 CLOCK SYSTEM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5.2 RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

6 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

6.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

6.2 MASKING AND PROCESSING FLOW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

6.3 INTERRUPTS AND LOW POWER MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

6.4 CONCURRENT & NESTED MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

6.5 INTERRUPT REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

6.6 INTERRUPT REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7 POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7.2 WAIT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7.3 HALT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

8 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

8.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

8.2 FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

8.3 MISCELLANEOUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

9 ON-CHIP PERIPHERALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

9.1 WATCHDOG TIMER (WDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

9.2 TIMEBASE UNIT (TBU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

9.3 USB INTERFACE (USB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

10 INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

10.1 CPU ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

10.2 INSTRUCTION GROUPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

11 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

11.1 PARAMETER CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

11.2 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

11.3 OPERATING CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

11.4 SUPPLY CURRENT CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.5 CLOCK AND TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

11.6 MEMORY CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

11.7 EMC CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table of Contents

80

3/80

11.8 I/O PORT PIN CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

11.9 CONTROL PIN CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

11.10COMMUNICATION INTERFACE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . 67

12 PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

13 DEVICE CONFIGURATION AND ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . 69

13.1 OPTION BYTE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

13.2 DEVICE ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

13.3 DEVELOPMENT TOOLS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

14 IMPORTANT NOTE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

14.1 UNEXPECTED RESET FETCH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

14.2 ST7 APPLICATION NOTES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

15 SUMMARY OF CHANGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

16 SILICON IDENTIFICATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

17 REFERENCE SPECIFICATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

18 SILICON LIMITATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

18.1 LVD RESET ON VDD BROWNOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

19 ERRATA SHEET ReVISION History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

20 Device Marking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

To obtain the most recent version of this datasheet,

please check at www.st.com>products>technical literature>datasheet

Please note that an errata sheet can be found at the end of this document on

page 77

and pay special attention to the Section "IMPORTANT NOTE" on page 73.

ST7261

4/80

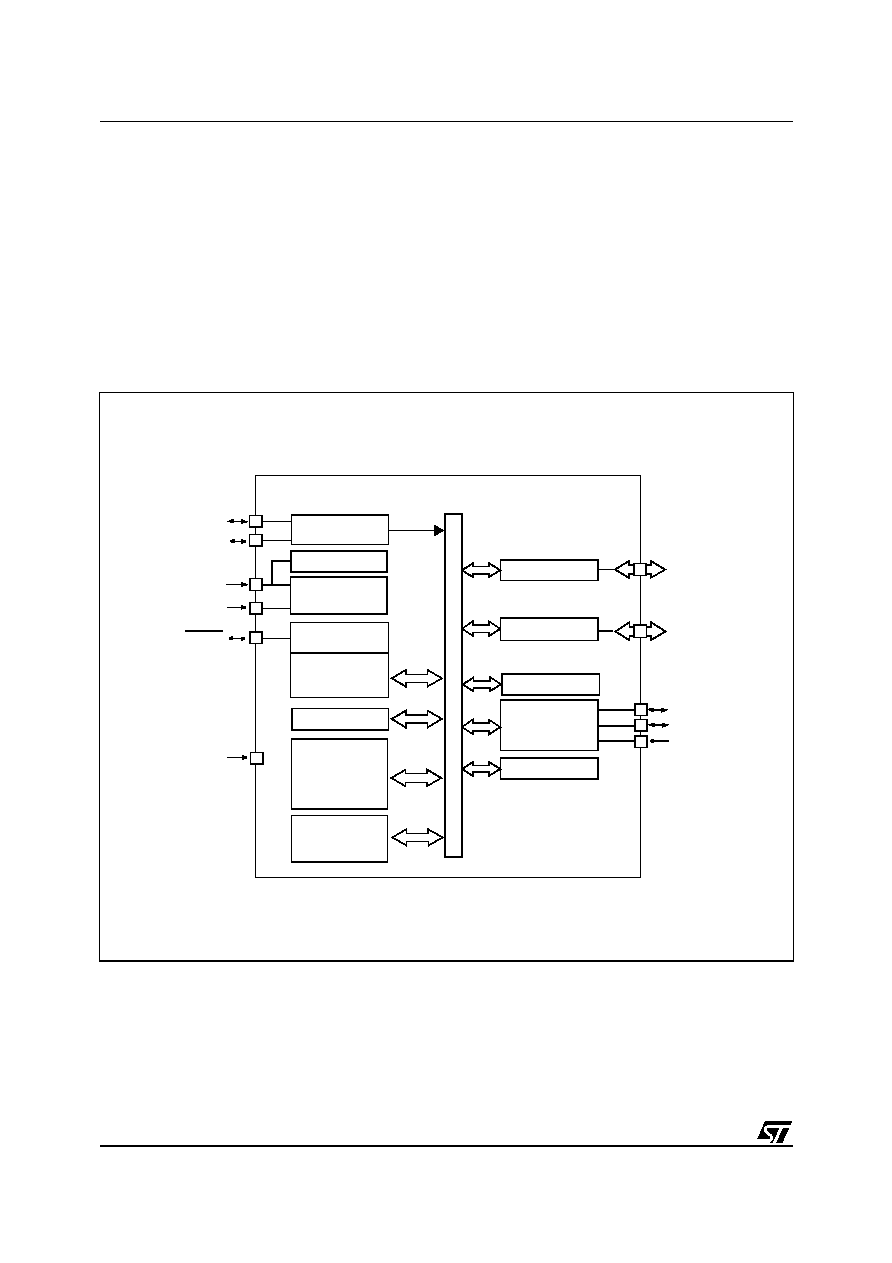

1 INTRODUCTION

The ST7261 devices are members of the ST7 mi-

crocontroller family designed for USB applications.

All devices are based on a common industry-

standard 8-bit core, featuring an enhanced instruc-

tion set.

The ST7261 devices are ROM versions. The

FLASH version is supported by the ST72F623F2.

Under software control, all devices can be placed

in WAIT, SLOW, or HALT mode, reducing power

consumption when the application is in idle or

standby state.

The enhanced instruction set and addressing

modes of the ST7 offer both power and flexibility to

software developers, enabling the design of highly

efficient and compact application code. In addition

to standard 8-bit data management, all ST7 micro-

controllers feature true bit manipulation, 8x8 un-

signed multiplication and indirect addressing

modes.

Figure 1. General Block Diagram

8-BIT CORE

ALU

A

DDRE

S

S

A

ND DA

T

A

B

U

S

OSCIN

OSCOUT

RESET

PORT B

USB SIE

PORT A

PB7:0

(8 bits)

OSCILLATOR

Internal

CLOCK

CONTROL

RAM

PA2:0

(3 bits)

V

SS

V

DD

POWER

SUPPLY

PROGRAM

(4 KBytes)

LVD

MEMORY

WATCHDOG

USBDP

USBDM

USBVCC

USB DMA

TIME BASE UNIT

V

PP

(256 Bytes)

1