Rev. 1.4

October 2000

1/152

This is preliminary information on a new product in development or undergoing evaluation. Details are subject to change without notice.

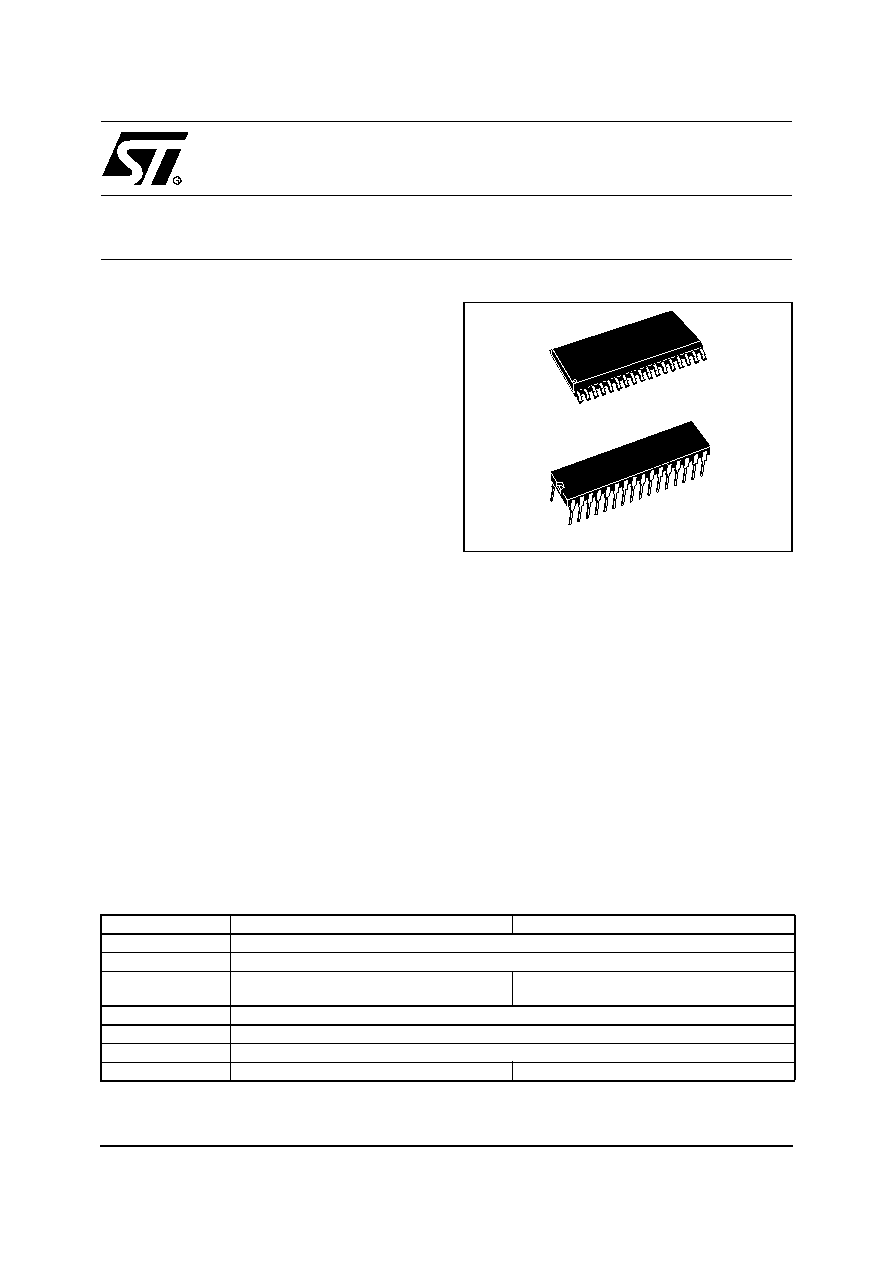

ST72C171

8-BIT MCU with 8K FLASH, ADC, WDG, SPI, SCI, TIMERS

SPGAs (Software Programmable Gain Amplifiers), OP-AMP

PRODUCT PREVIEW

s

Memories

≠ 8K of single voltage Flash Program memory

with read-out protection

≠ In-Situ Programming (Remote ISP)

s

Clock, Reset and Supply Management

≠ Enhanced Reset System

≠ Low voltage supervisor (LVD) with 3 program-

mable levels

≠ Low consumption resonator or RC oscillators

(internal or external) and by-pass for external

clock source, with safe control capabilities

≠ 3 Power Saving modes

s

22 I/O Ports

≠ 22 multifunctional bidirectional I/O lines:

≠ 16 interrupt inputs on 2 independent lines

≠ 8 lines configurable as analog inputs

≠ 20 alternate functions

≠ EMI filtering

s

2 Timers and Watchdog

≠ One 16-bit Timer with: 2 Input Captures, 2

Output Compares, external Clock input, PWM

and Pulse Generator modes

≠ One 8-bit Autoreload Timer (ART) with: 2

PWM output channels (internally connectable

to the SPGA inputs), 1 Input Capture, external

clock input

≠ Configurable watchdog (WDG)

s

2 Communications Interfaces

≠ Synchronous Serial Peripheral Interface (SPI)

≠ Serial Communications Interface (SCI)

s

3 Analog peripherals

≠ 2 Software Programmable Gain Operational

Amplifiers (SPGAs) with rail-to-rail input and

output, V

DD

independent (band gap) and pro-

grammable reference voltage (1/8 V

DD

reso-

lution), Offset compensation, DAC & on/off

switching capability

≠ 1 rail-to-rail input and output Op-Amp

≠ 8-bit A/D Converter with up to 11 channels (in-

cluding 3 internal channels connected to the

Op-Amp & SPGA outputs)

s

Instruction Set

≠ 8-bit data manipulation

≠ 63 basic Instructions

≠ 17 main addressing modes

≠ 8 x 8 unsigned multiply instruction

≠ True bit manipulation

s

Development Tools

≠ Full hardware/software development package

Device Summary

SO34

PSDIP32

Features

ST72C171K2M

ST72C171K2B

Flash - bytes

8K Single Voltage

RAM (stack) - bytes

256 (128)

Peripherals

2 SPGAs, 1 Op-Amp,

Watchdog, 3 Timers, SPI, SCI, ADC (11 chan.)

2 SPGAs,

Watchdog, 3 Timers, SPI, SCI, ADC (11 chan.)

Operating Supply

3.2 V to 5.5 V

CPU Frequency

Up to 8 MHz (with up to 16 MHz oscillator)

Temperature Range

- 40∞C to + 85∞C

Package

SO34 PSDIP32

1

Table of Contents

152

2/152

1

1 GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.2 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.3 MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2 FLASH PROGRAM MEMORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.2 MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.3 STRUCTURAL ORGANISATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.4 IN-SITU PROGRAMMING (ISP) MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.5 MEMORY READ-OUT PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3 CENTRAL PROCESSING UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.2 MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.3 CPU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4 SUPPLY, RESET AND CLOCK MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.1 MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.2 LOW VOLTAGE DETECTOR (LVD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4.3 CLOCK SECURITY SYSTEM (CSS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.4 CLOCK, RESET AND SUPPLY REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . 23

5 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.1 NON MASKABLE SOFTWARE INTERRUPT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.2 EXTERNAL INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.3 PERIPHERAL INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

6 POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.2 SLOW MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

6.3 WAIT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

6.4 HALT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

7 ON-CHIP PERIPHERALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

7.1 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

7.2 MISCELLANEOUS REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

7.3 OP-AMP MODULE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

7.4 WATCHDOG TIMER (WDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

7.5 16-BIT TIMER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

7.6 PWM AUTO-RELOAD TIMER (ART) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

7.7 SERIAL COMMUNICATIONS INTERFACE (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

7.8 SERIAL PERIPHERAL INTERFACE (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

7.9 8-BIT A/D CONVERTER (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

8 INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

8.1 ST7 ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

8.2 INSTRUCTION GROUPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table of Contents

3/152

9 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

9.1 PARAMETER CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

9.2 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

9.3 OPERATING CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

9.4 SUPPLY CURRENT CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

9.5 CLOCK AND TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

9.6 MEMORY CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

9.7 EMC CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

9.8 I/O PORT PIN CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

9.9 CONTROL PIN CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

9.10 TIMER PERIPHERAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

9.11 COMMUNICATION INTERFACE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . 136

9.12 8-BIT ADC CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

9.13 OP-AMP MODULE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

10 GENERAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

10.1 PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

10.2 THERMAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

10.3 SOLDERING AND GLUEABILITY INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

10.4 PACKAGE/SOCKET FOOTPRINT PROPOSAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

11 DEVICE CONFIGURATION AND ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . 147

11.1 OPTION BYTES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

11.2 DEVICE ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

11.3 DEVELOPMENT TOOLS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

11.4 ST7 APPLICATION NOTES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

11.5 TO GET MORE INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

12 SUMMARY OF CHANGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

ST72C171

4/152

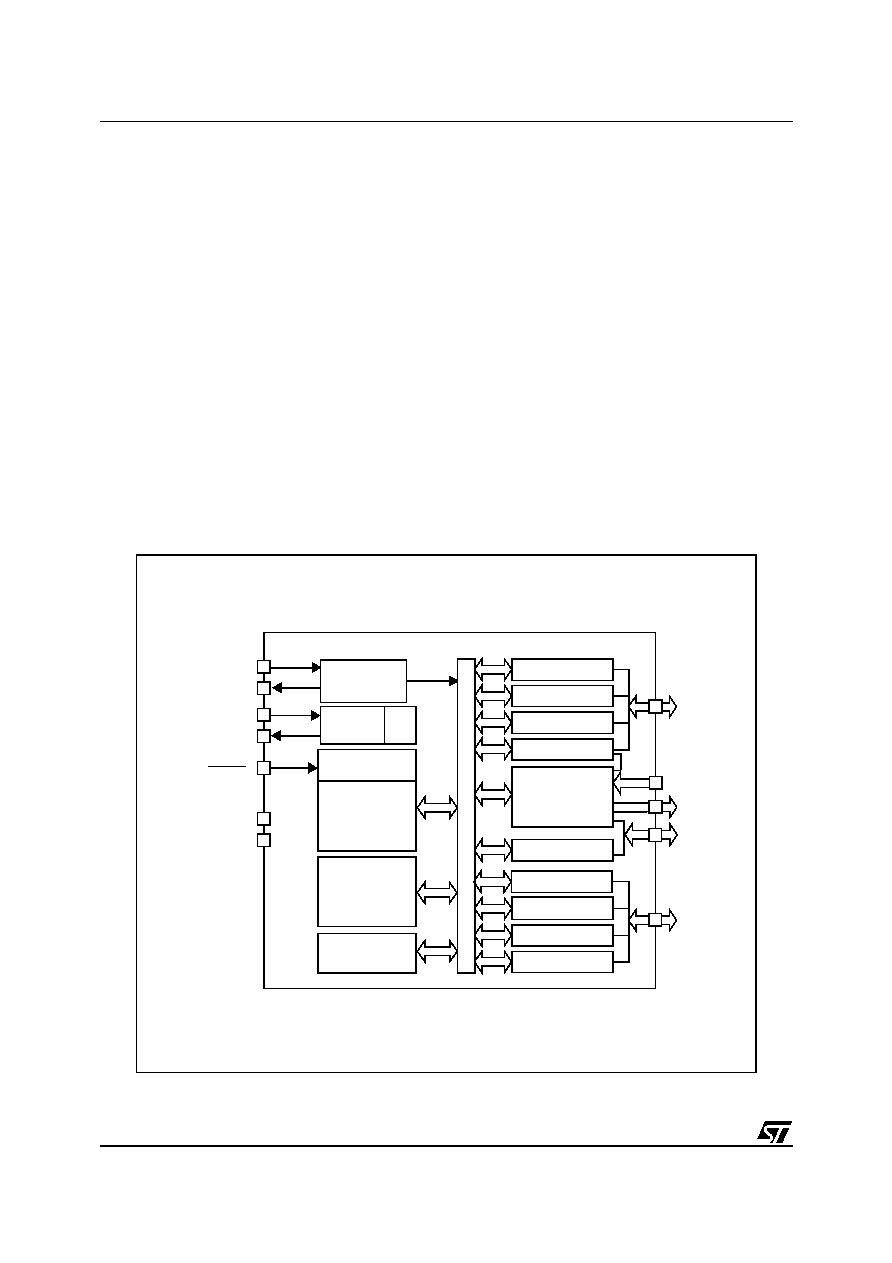

1 GENERAL DESCRIPTION

1.1 INTRODUCTION

The ST72C171 is a member of the ST7 family of

Microcontrollers. All devices are based on a com-

mon industry-standard 8-bit core, featuring an en-

hanced instruction set.

The ST72C171 features single-voltage FLASH

memory with byte-by-byte In-Situ Programming

(ISP) capability.

Under software control, the device can be placed

in WAIT, SLOW, or HALT mode, reducing power

consumption when the application is in idle or

standby state.

The enhanced instruction set and addressing

modes of the ST7 offer both power and flexibility to

software developers, enabling the design of highly

efficient and compact application code. In addition

to standard 8-bit data management, all ST7 micro-

controllers feature true bit manipulation, 8x8 un-

signed multiplication and indirect addressing

modes The device includes a low consumption

and fast start on-chip oscillator, CPU, Flash pro-

gram memory, RAM, 22 I/O lines and the following

on-chip peripherals: Analog-to-Digital converter

(ADC) with 8 multiplexed analog inputs, Op-Amp

module, synchronous SPI serial interface, asyn-

cronous serial interface (SCI), Watchdog timer, a

16-bit Timer featuring external Clock Input, Pulse

Generator capabilities, 2 Input Captures and 2

Output Compares, an 8-bit Timer featuring exter-

nal Clock Input, Pulse Generator Capabilities (2

channels), Autoreload and Input Capture.

The Op-Amp module adds on-chip analog fea-

tures to the MCU, that usually require using exter-

nal components.

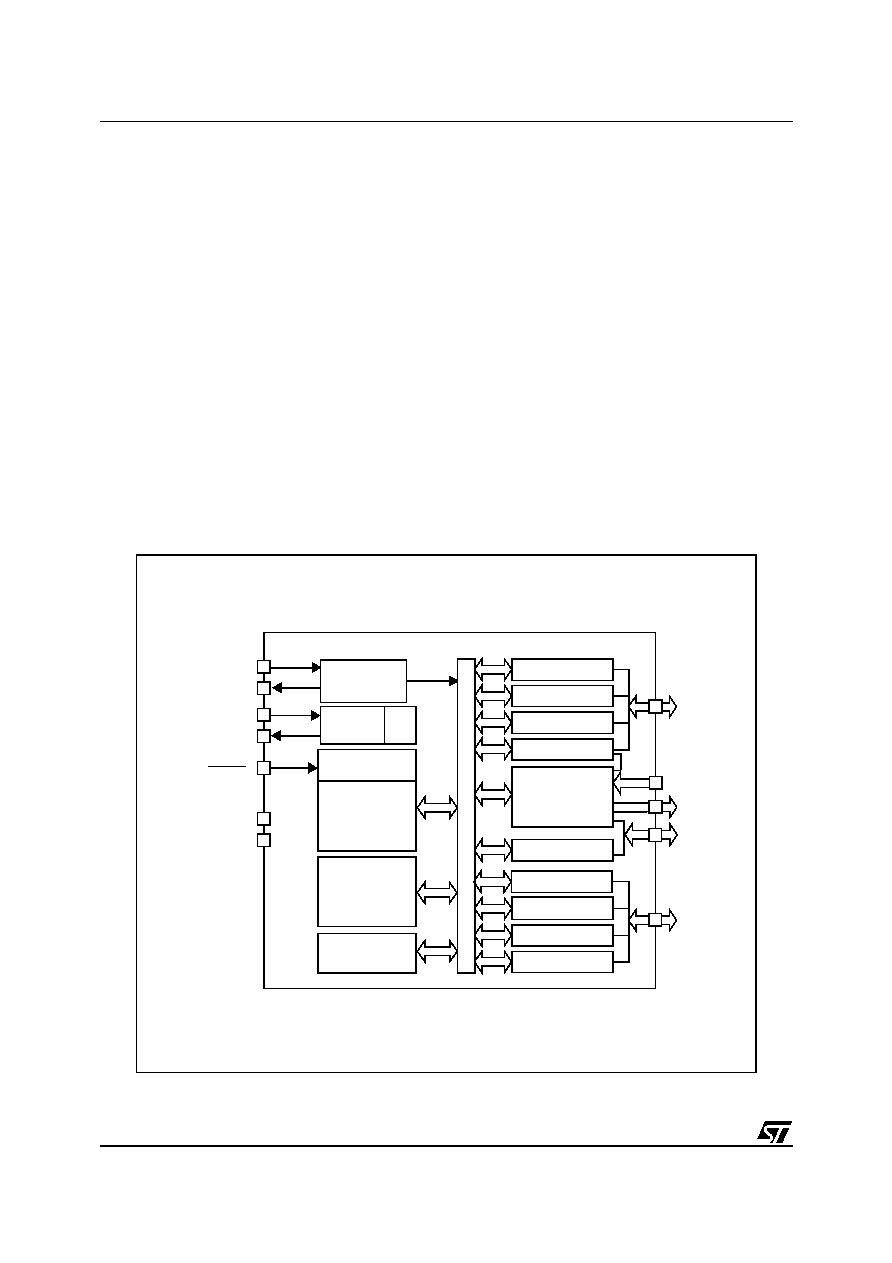

Figure 1. ST72C171 Block Diagram

A

DDRE

S

S

A

ND DA

T

A

B

U

S

OSCIN

OSCOUT

RESET

16-BIT TIMER

8-BIT ADC

PORT B

WATCHDOG

Internal

CLOCK

CONTROL

256b-RAM

PA[7:0]

V

SS

V

DD

POWER

SUPPLY

8K FLASH

PORT A

PWM/ART TIMER

SPI

PB[7:0]

LVD

SCI

MULTIOSC

+

CLOCK FILTER

OP-AMP

V

SSA

V

DDA

8-BIT CORE

ALU

PORT C

PC[5:0]

OA1OUT

OA2OUT

MEMORY

OA3OUT*

*only on 34-pin devices

OA3PIN*

ST72C171

5/152

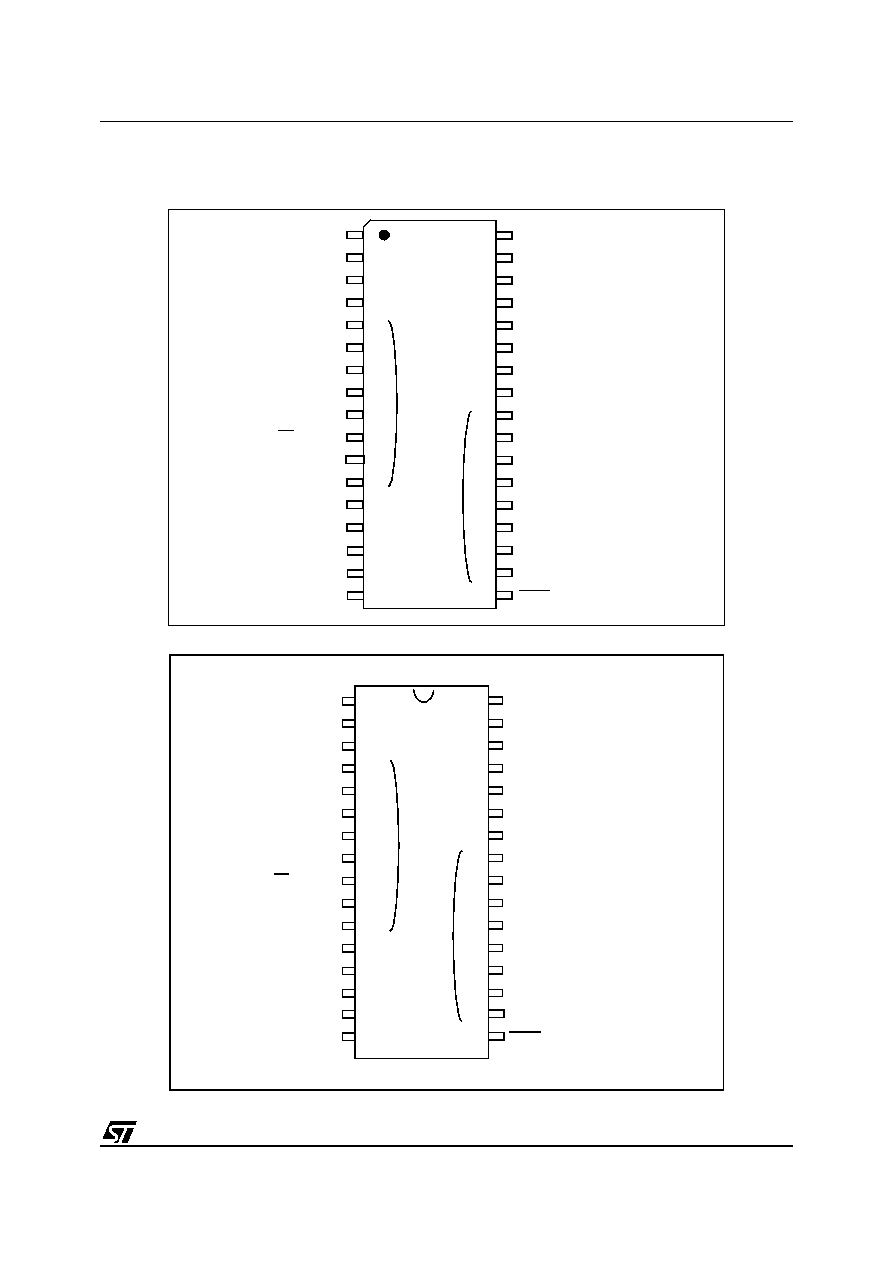

1.2 PIN DESCRIPTION

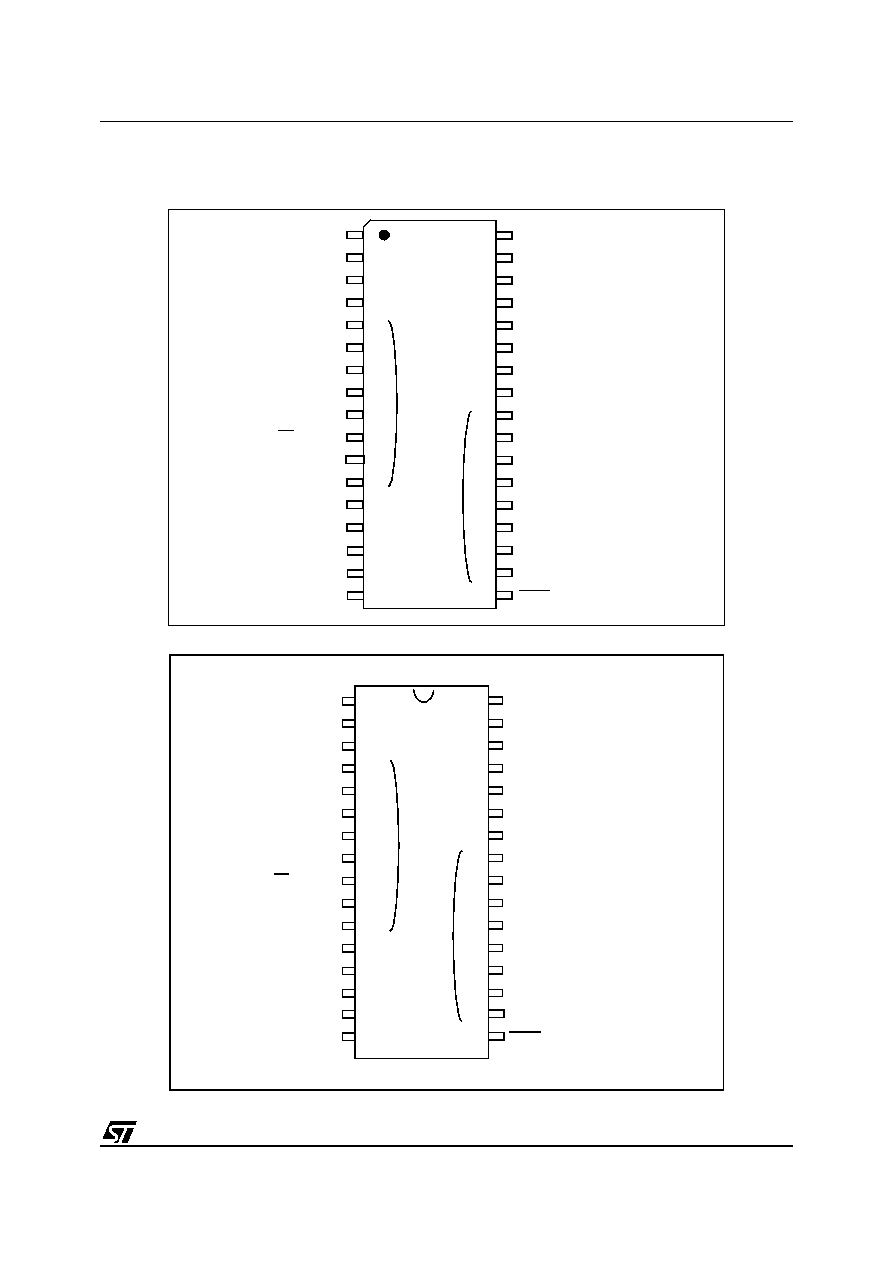

Figure 2. 34-Pin SO Package Pinout

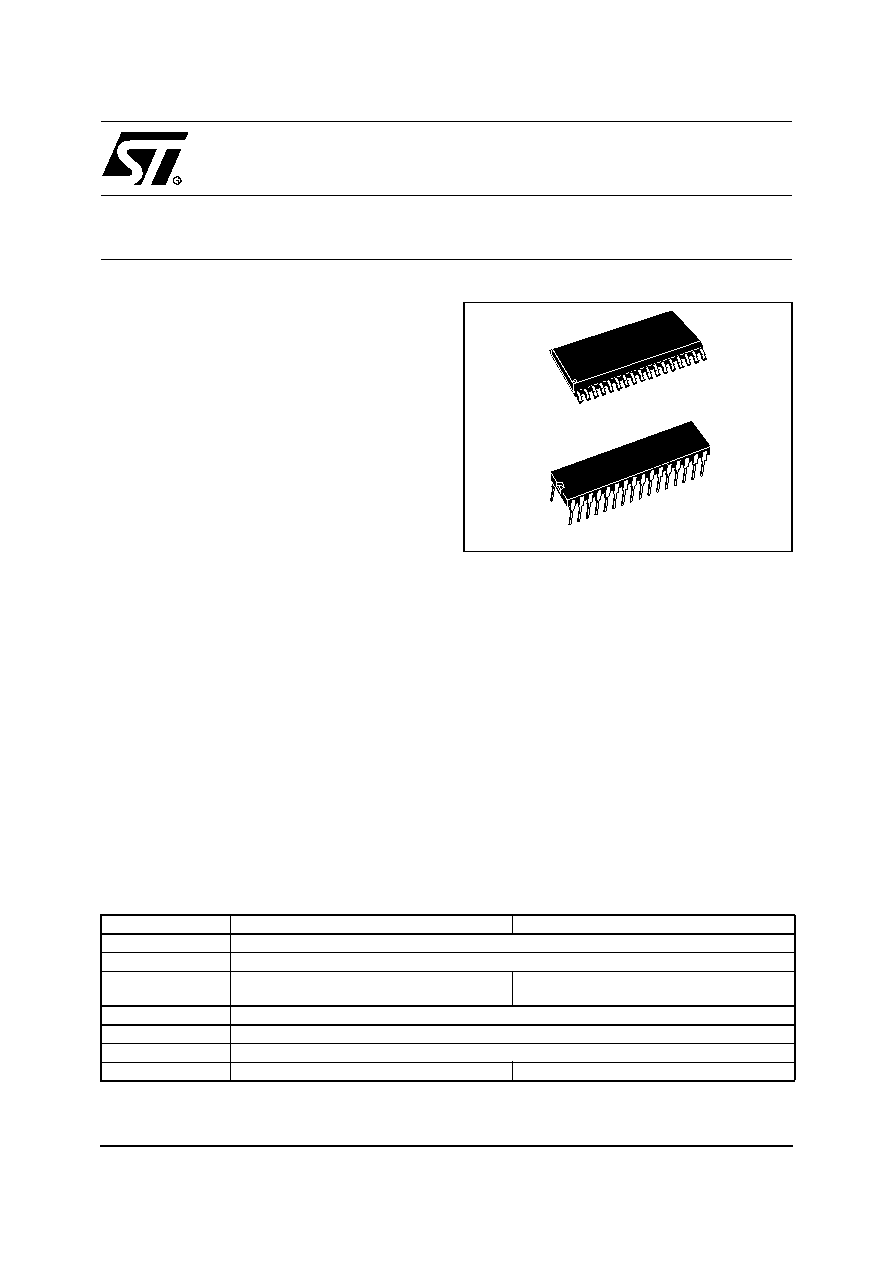

Figure 3. 32-Pin SDIP Package Pinout

PC2 / OA1PIN / PWM0R

PC3 / OA1NIN

OA1OUT

PC4 / MCO/ OA3NIN

V

DDA

V

SSA

OA3OUT

PC5/ PWM0

PA7 / AIN7 / PWM1

PA6 / AIN6 / ARTICP0

PA5 / AIN5

PA4 / AIN4 / OCMP1

PA3 / AIN3 / OCMP2

PA2 / AIN2 / ICAP1

PA1 / AIN1 / ICAP2

PA0 / AIN0

RESET

21

22

23

24

25

26

34

33

32

31

30

29

28

27

1

2

3

4

5

6

7

8

9

10

11

12

13

14

OA2OUT

PWM1R / OA2PIN / PC1

OA2NIN / PC0

OA3PIN

TDO / PB7

RDI / PB6

ISPDATA / MISO / PB5

MOSI /

(HS) PB4

ISPCLK / SCK /

(HS) PB3

SS /

(HS) PB2

ARTCLK /

(HS) PB1

EXTCLK /

(HS) PB0

V

DD

V

SS

OSC2

OSC1

ISPSEL

15

16

17

20

19

18

ei1

ei0

(HS) 20mA high sink capability

OA2OUT

PWM1R / OA2PIN / PC1

OA2NIN / PC0

TDO / PB7

RDI / PB6

ISPDATA / MISO / PB5

MOSI /

(HS) PB4

ISPCLK / SCK/

(HS) PB3

SS /

(HS) PB2

ARTCLK /

(HS) PB1

EXTCLK /

(HS) PB0

V

DD

V

SS

OSC2

OSC1

ISPSEL

PC2 / OA1PIN / PWM0R

PC3 / OA1NIN

OA1OUT

PC4 / MCO

V

DDA

V

SSA

PC5 / PWM0

PA7 / AIN7 / PWM1

PA6 / AIN6 /ARTICP0

PA5 / AIN5

PA4 / AIN4 / OCMP1

PA3 / AIN3 / OCMP2

PA2 / AIN2 / ICAP1

PA1 / AIN1 / ICAP2

PA0 / AIN0

RESET

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

ei1

ei0

(HS) 20mA high sink capability