November 1997

1/117

R

Rev. 1.0

ST7285C

8-BIT MCU FOR RDS WITH 48 K ROM, 3 K RAM, ADC,

TWO TIMERS, TWO SPIs, I

2

C AND SCI INTERFACES

s

4.5V to 5.5V Supply Operating Range

s

Operates at 8.664MHz Oscillator Frequency for

RDS compatibility

s

Fully Static operation

s

-40

∞

C

to

+

85

∞

C

Maximum

Operating

Temperature Range

s

Run, Wait, Slow, Halt and RAM Retention

modes

s

User ROM: 48 Kbytes

s

Data RAM: 3 Kbytes, including 128 byte stack

s

80 pin plastic package

s

62 multifunctional bidirectional I/O lines:

≠ Programmable Interrupt inputs on some I/Os

≠ 8 Analog inputs

≠ EMI filtering

s

Two 16-bit Timers, each featuring:

≠ 2 Input Captures

≠ 2 Output Compares

≠ External Clock input (on Timer A)

≠ PWM and Pulse Generator modes

s

RDS Radio Data System Filter, Demodulator

and GBS circuits

s

8-bit Analog-to-Digital converter with 8 channel

analog multiplexer

s

Digital Watchdog

s

Two SPI Serial Peripheral Interfaces

s

SCI Serial Communications Interface

s

Full I

2

C multiple Master/ Slave interface

s

2KHz Beep signal generator

s

Master Reset and Power-On Reset

s

8-bit Data Manipulation

s

63 Basic Instructions

s

17 main Addressing Modes

s

8 x 8 Unsigned Multiply Instruction

s

True Bit Manipulation

s

Complete Development Support on PC/DOS/

Windows

TM

Real-Time Emulator

s

Full Software Package (C-Compiler, Cross-

Assembler, Debugger)

PQFP80

1

2/117

Table of Contents

117

ST7285C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

1 GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

1.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

1.2 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

1.3 MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

2 CENTRAL PROCESSING UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

2.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

2.2 CPU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

3 CLOCKS, RESET, INTERRUPTS & POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . 15

3.1 CLOCK SYSTEM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

3.1.1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

3.1.2 Crystal Resonator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

3.1.3 Ceramic Resonator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1.4 External Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

3.2 MISCELLANEOUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.3 RESETS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.3.2 External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.3.3 Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.3.4 Power-on Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.4 WATCHDOG TIMER SYSTEM (WDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

3.4.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.4.3 Watchdog Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.5 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

3.6 POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3.6.1 Slow Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3.6.2 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3.6.3 Halt Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

4 ON-CHIP PERIPHERALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

4.1 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

4.1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

4.1.2 Generic I/O Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.1.3 I/O Port Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.2 SERIAL COMMUNICATIONS INTERFACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4.2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

4.2.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

4.2.3 Serial Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

4.2.4 Data Reception and Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4.2.5 Receiver Muting and Wake-up Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4.2.6 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.2.7 SCI Register Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.3 16-BIT TIMER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

4.3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

4.3.2 Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

3/117

Table of Contents

4.3.3 External Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

4.3.4 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

4.3.5 Output Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

4.3.6 Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

4.4 SERIAL PERIPHERAL INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

4.4.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

4.4.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.4.4 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

4.4.5 Master Out Slave In (MOSI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.4.6 Master In Slave Out (MISO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.4.7 Serial Peripheral Control Register (SPCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4.4.8 Serial Peripheral Status Register (SPSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

4.4.9 Serial Peripheral Data I/O Register (SPDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4.4.10Single Master And Multimaster Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4.5 I2C BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

4.5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

4.5.2 General Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

4.5.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.5.4 EPROM/ROM I C COMPATIBILITY APPLICATION NOTE. . . . . . . . . . . . . . . . . . . 56

4.5.5 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

4.5.6 I2C State Machine: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

4.6 A/D CONVERTER (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

4.6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

4.6.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.6.3 Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

4.7 RDS FILTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

4.7.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

4.7.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

4.8 RDS DEMODULATOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

4.8.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

4.8.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.9 RDS G.B.S . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

4.9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

4.9.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

4.9.3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

4.9.4 Acquisition of Group and Block Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.9.5 Application Tips . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

4.9.6 Block Synchronization Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.9.7 Error Correction software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5 SOFTWARE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

5.1 ST7 ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

5.2 ST7 ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.3 ST7 INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

6 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

6.1 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

6.2 POWER CONSIDERATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

4/117

Table of Contents

117

6.3 DC ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

6.4 AC ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

6.5 CONTROL TIMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

7 GENERAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

7.1 PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

ST72E85

ST72T85 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

1 GENERAL DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

1.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

1.2 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

1.3 MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

1.4 EPROM ERASURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

1.5 EPROM/ROM I C COMPATIBILITY APPLICATION NOTE. . . . . . . . . . . . . . . . . . . . . . . 106

2 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

2.1 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

2.2 POWER CONSIDERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

2.3 DC ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

2.4 AC ELECTRICAL CHARACTERISTICS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

2.5 CONTROL TIMING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

3 GENERAL INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

3.1 PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

5/117

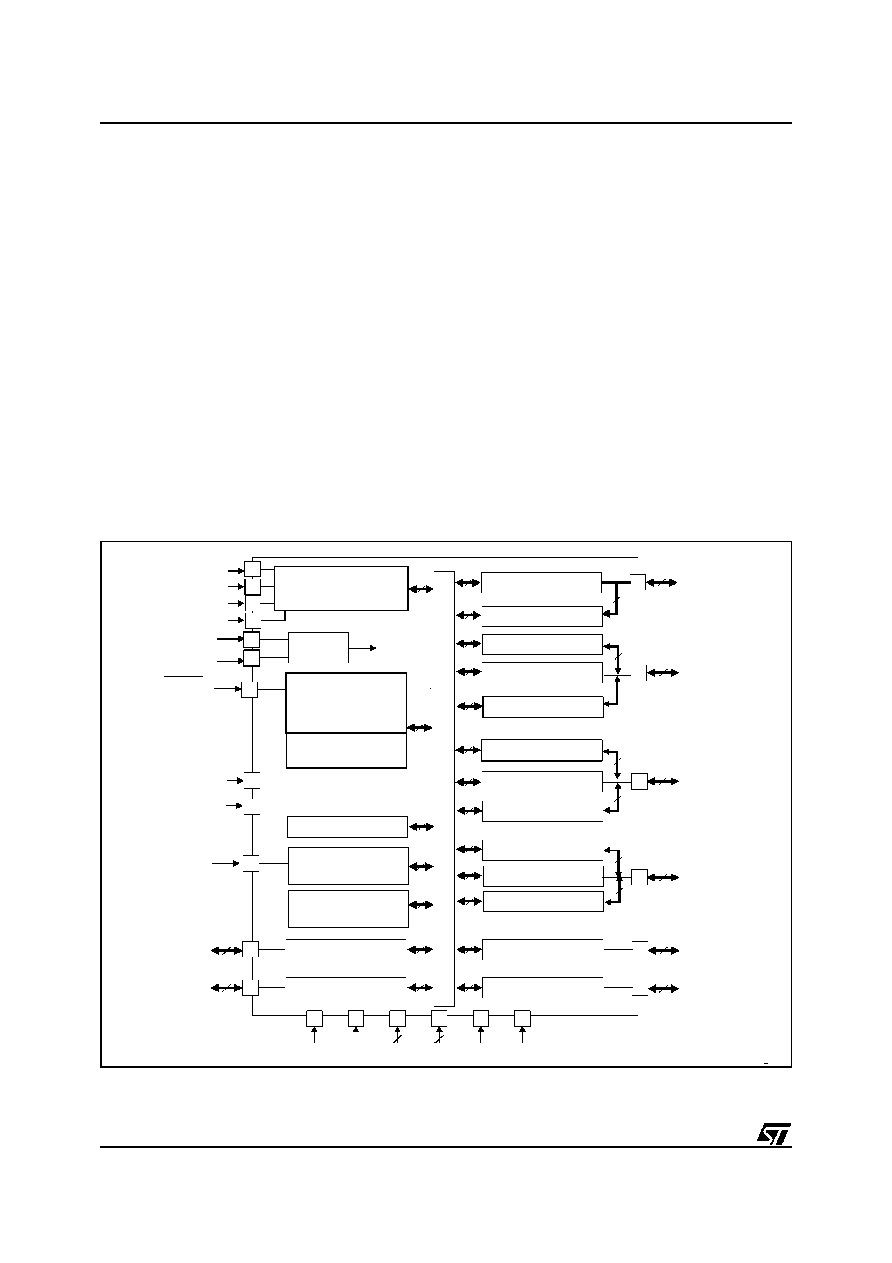

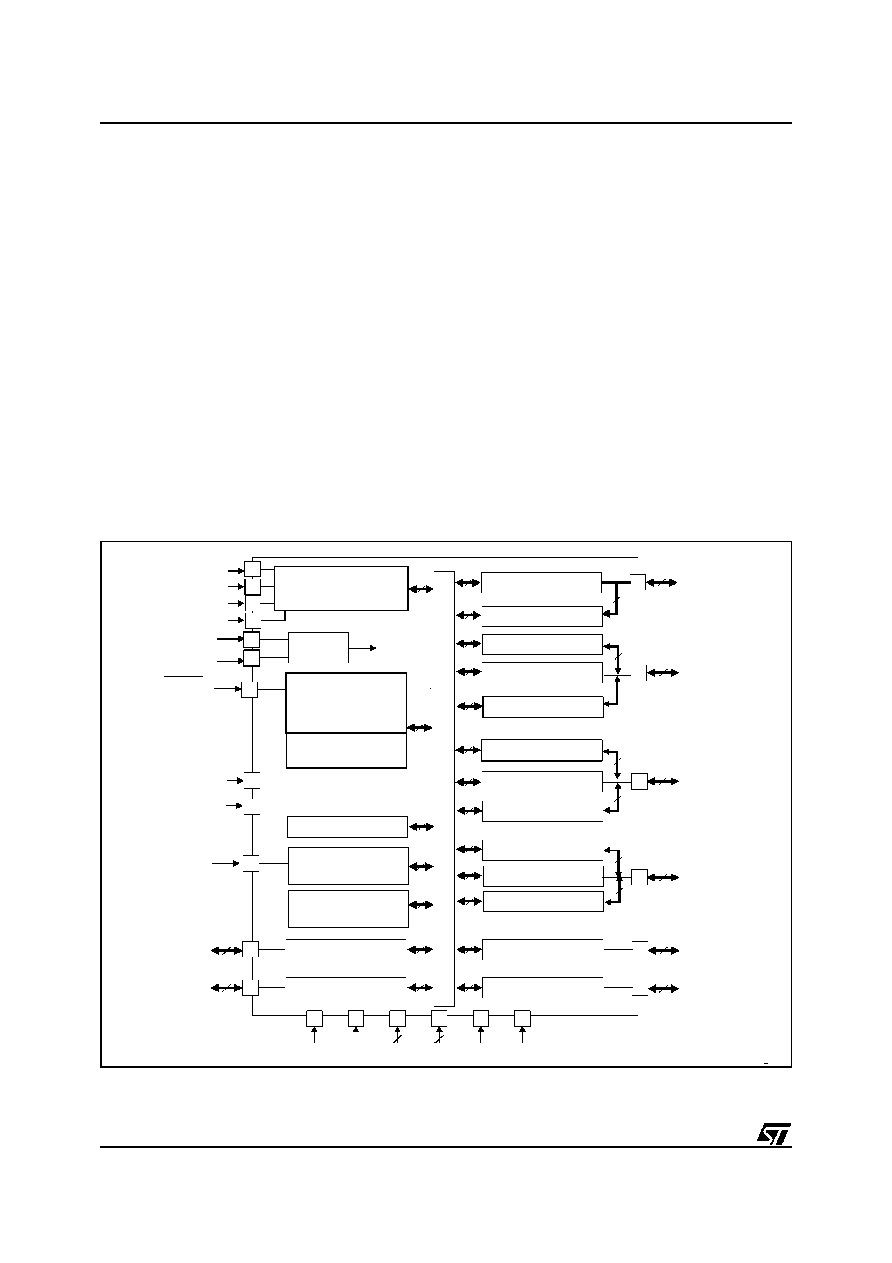

ST7285C

1 GENERAL DESCRIPTION

1.1 INTRODUCTION

The ST7285C HCMOS Microcontroller Unit is a

member of the ST7 family of Microcontrollers ded-

icated to car radio applications with RDS capabili-

ty. The device is based on an industry-standard 8-

bit core and features an enhanced instruction set.

The device is normally operated at an 8.664MHz

oscillator frequency for RDS compatibility but,

thanks to the fully static design, operation is possi-

ble down to DC, when RDS functionality is not re-

quired. Under software control, theST7285C may

be placed in either WAIT, SLOW or HALT modes,

thus reducing power consumption. The enhanced

instruction set and addressing modes afford real

programming potential. In addition to standard 8-

bit data management, the ST7285C features true

bit manipulation, 8x8 unsigned multiplication and

indirect addressing modes.

The device includes an on-chip oscillator, CPU,

ROM, RAM, 62 I/O lines and the following on-chip

peripherals: Analog-to-Digital converter (ADC),

two industry standard SPI serial interfaces, a Seri-

al Communications Interface, an I

2

C interface, a

digital Watchdog Timer, two independent 16-bit

Timers, one featuring an External Clock Input, and

both featuring Pulse Generator capabilities, 2 In-

put Captures and 2 Output Compares. RDS Filter,

Demodulator and GBS circuitry for car radio appli-

cations is also included.

NOTE: FOR THIS DEVICE, SGS-THOMSON

CAN ONLY RECEIVE MOTOROLA S19 FORMAT

FOR ROM CODES.

Figure 1. ST7285C Block Diagram

*On EPROM or OTP versions only.

Power on Reset

PA0 - PA7

Pin 65..72

PB0 - PB7

Pin 73..80

OSCin

OSCout

RESET

V

PP

/ TEST

OSC

8 -BIT CORE

ALU

VR01735P

Internal

CLOCK

ADDRESS

and

DATA

BUS

Timer A

PORT A

PORT B

A/D Converter

8

4

SPI B

PORT C

PC0 - PC7

Pin 5..12

SPI A

PORT D

I

2

C

SCI

8

RAM

3k

RDS

FILTER,DEMOD,GBS

8

8

8

Timer B

4

4

2

PD0 - PD7

Pin 13..20

2

PORT E

PE0 - PE7

Pin 25..32

8

PORT F

PF0 - PF7

Pin 33..40

8

PORT H

PORT G

PH0 - PH5

Pin 53..58

6

PG0 - PG7

Pin 45..52

8

ROM or EPROM*

48k

Watchdog

RDScomp

MPX

RDS fil

RDS ref

ARS

AINT

V

DD

V

SS

V

DDP

V

SSP

V

DDA

V

SSA

2

2