ƒÓÍÛÏÂÌÚýˆËˇ Ë ÓÔËÒýÌˡ www.docs.chipfind.ru

July 2005

1/167

Rev. 4.0

ST7LITE3

8-BIT MCU WITH SINGLE VOLTAGE FLASH, DATA EEPROM, ADC,

TIMERS, SPI, LINSCI

TM

Memories

≠ 8 Kbytes program memory: single voltage ex-

tended Flash (XFlash) Program memory with

read-out protection, In-Circuit Programming

and In-Application programming (ICP and

IAP), data retention: 20 years at 55∞C.

≠ 384 bytes RAM

≠ 256 bytes data EEPROM with read-out pro-

tection. 300K write/erase cycles guaranteed,

data retention: 20 years at 55∞C.

Clock, Reset and Supply Management

≠ Enhanced reset system

≠ Enhanced low voltage supervisor (LVD) for

main supply and an auxiliary voltage detector

(AVD) with interrupt capability for implement-

ing safe power-down procedures

≠ Clock sources: Internal RC1% oscillator, crys-

tal/ceramic resonator or external clock

≠ Optional x4 or x8 PLL for 4 or 8 MHz internal

clock

≠ Five Power Saving Modes: Halt, Active-Halt,

Wait and Slow, Auto Wake Up From Halt

I/O Ports

≠ Up to 15 multifunctional bidirectional I/O lines

≠ 7

high sink outputs

5 Timers

≠ Configurable Watchdog Timer

≠ Two 8-bit Lite Timers with prescaler,

1 realtime base and 1 input capture

≠ Two 12-bit Auto-reload Timers with 4 PWM

outputs, input capture and output compare

functions

2 Communication Interfaces

≠ Master/slave LINSCI

TM asynchronous serial

interface

≠ SPI synchronous serial interface

Interrupt Management

≠ 10 interrupt vectors plus TRAP and RESET

≠ 12 external interrupt lines (on 4 vectors)

A/D Converter

≠ 7 input channels

≠ 10-bit resolution

Instruction Set

8-bit data manipulation

≠ 63 basic instructions with illegal opcode

detection

≠ 17 main addressing modes

≠ 8 x 8 unsigned multiply instructions

Development Tools

≠ Full hardware/software development package

≠ DM (Debug module)

Device Summary

DIP20

SO20

Features

ST7LITE30

ST7LITE35

ST7LITE39

Program memory - bytes

8K

RAM (stack) - bytes

384 (128)

Data EEPROM - bytes

-

-

256

Peripherals

Lite Timer, Autoreload Timer, SPI, LINSCI, 10-bit ADC

Operating Supply

2.7V to 5.5 V

CPU Frequency

Up to 8Mhz

(w/ ext OSC up to 16MHz)

Up to 8Mhz (w/ ext OSC up to 16MHz

and int 1MHz RC 1% PLLx8/4MHz)

Operating Temperature

-40∞C to +85∞C

Packages

SO20 300", DIP20

1

Table of Contents

2/167

ST7LITE3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3 REGISTER & MEMORY MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4 FLASH PROGRAM MEMORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.1

INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.2

MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.3

PROGRAMMING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.4

ICC INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.5

MEMORY PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.6

RELATED DOCUMENTATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.7

REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5 DATA EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.1

INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.2

MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.3

MEMORY ACCESS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.4

POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.5

ACCESS ERROR HANDLING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.6

DATA EEPROM READ-OUT PROTECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.7

REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

6 CENTRAL PROCESSING UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

6.1

INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

6.2

MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

6.3

CPU REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

7 SUPPLY, RESET AND CLOCK MANAGEMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7.1

INTERNAL RC OSCILLATOR ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7.2

PHASE LOCKED LOOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7.3

REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

7.4

MULTI-OSCILLATOR (MO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

7.5

RESET SEQUENCE MANAGER (RSM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

7.6

SYSTEM INTEGRITY MANAGEMENT (SI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

8 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

8.1

NON MASKABLE SOFTWARE INTERRUPT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

8.2

EXTERNAL INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

8.3

PERIPHERAL INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

9 POWER SAVING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

9.1

INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

9.2

SLOW MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

9.3

WAIT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

9.4

HALT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

9.5

ACTIVE-HALT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2

Table of Contents

3/167

9.6

AUTO WAKE UP FROM HALT MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

10 I/O PORTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

10.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

10.2 FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

10.3 I/O PORT IMPLEMENTATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

10.4 UNUSED I/O PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

10.5 LOW POWER MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

10.6 INTERRUPTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

11 ON-CHIP PERIPHERALS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

11.1 WATCHDOG TIMER (WDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

11.2 DUAL 12-BIT AUTORELOAD TIMER 3 (AT3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

11.3 LITE TIMER 2 (LT2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

11.4 SERIAL PERIPHERAL INTERFACE (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

11.5 LINSCI SERIAL COMMUNICATION INTERFACE (LIN MASTER/SLAVE) . . . . . . . . . . 88

11.6 10-BIT A/D CONVERTER (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

12 INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

12.1 ST7 ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

12.2 INSTRUCTION GROUPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

13 ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

13.1 PARAMETER CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

13.2 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

13.3 OPERATING CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

13.4 SUPPLY CURRENT CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

13.5 CLOCK AND TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

13.6 MEMORY CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

13.7 EMC CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

13.8 I/O PORT PIN CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

13.9 CONTROL PIN CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

13.10 COMMUNICATION INTERFACE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . 151

13.11 10-BIT ADC CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

14 PACKAGE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

14.1 PACKAGE MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

14.2 THERMAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

14.3 SOLDERING AND GLUEABILITY INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

15 DEVICE CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

15.1 FLASH OPTION BYTES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

15.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE . . . . 160

15.3 DEVELOPMENT TOOLS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

16 KNOWN LIMITATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

16.1 CLEARING ACTIVE INTERRUPTS OUTSIDE INTERRUPT ROUTINE . . . . . . . . . . . . 163

16.2 LINSCI LIMITATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

17 REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

3

ST7LITE3

4/167

1 INTRODUCTION

The ST7LITE3 is a member of the ST7 microcon-

troller family. All ST7 devices are based on a com-

mon industry-standard 8-bit core, featuring an en-

hanced instruction set.

The ST7LITE3 features FLASH memory with

byte-by-byte In-Circuit Programming (ICP) and In-

Application Programming (IAP) capability.

Under software control, the ST7LITE3 device can

be placed in WAIT, SLOW, or HALT mode, reduc-

ing power consumption when the application is in

idle or standby state.

The enhanced instruction set and addressing

modes of the ST7 offer both power and flexibility to

software developers, enabling the design of highly

efficient and compact application code. In addition

to standard 8-bit data management, all ST7 micro-

controllers feature true bit manipulation, 8x8 un-

signed multiplication and indirect addressing

modes.

For easy reference, all parametric data are located

in

section 13 on page 129

.

The devices feature an on-chip Debug Module

(DM) to support in-circuit debugging (ICD). For a

description of the DM registers, refer to the ST7

ICC Protocol Reference Manual.

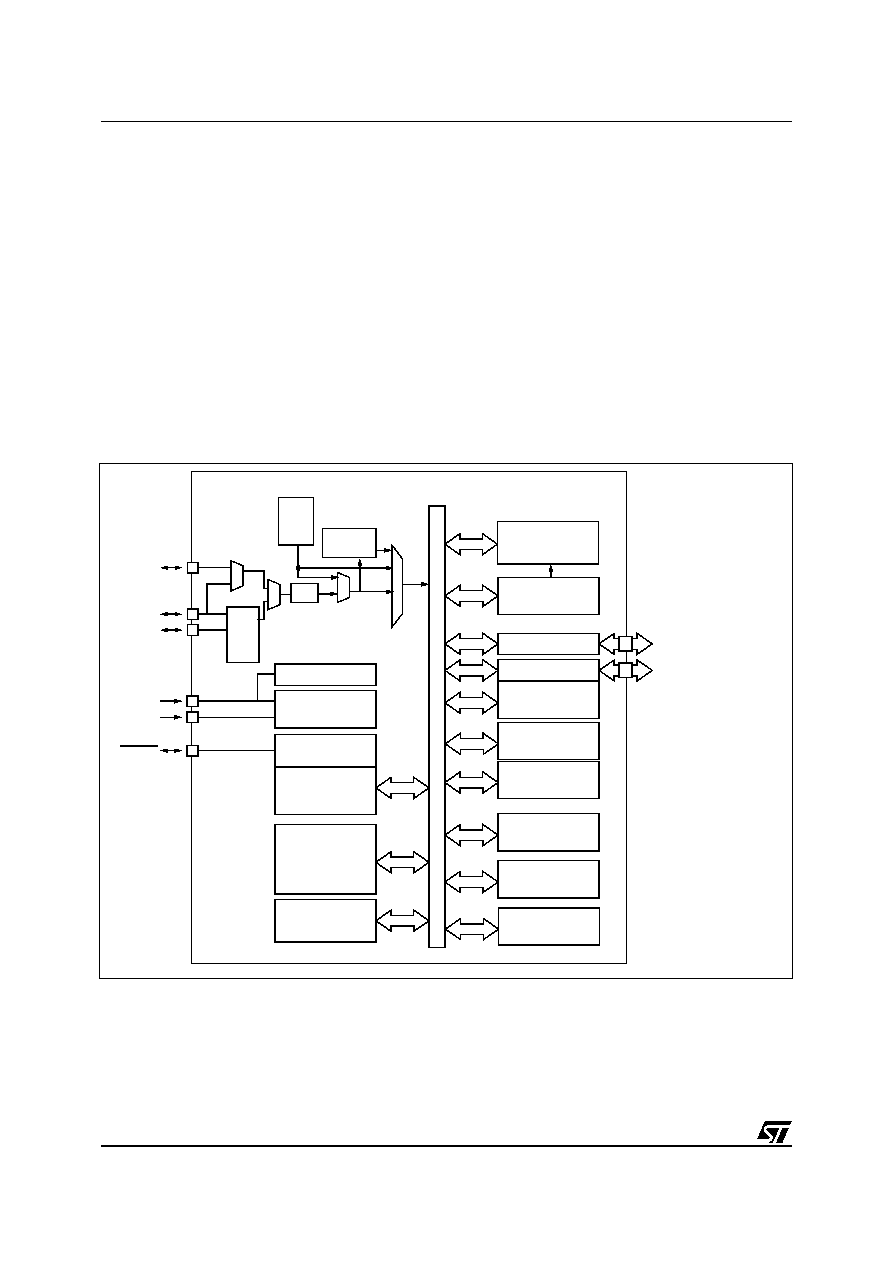

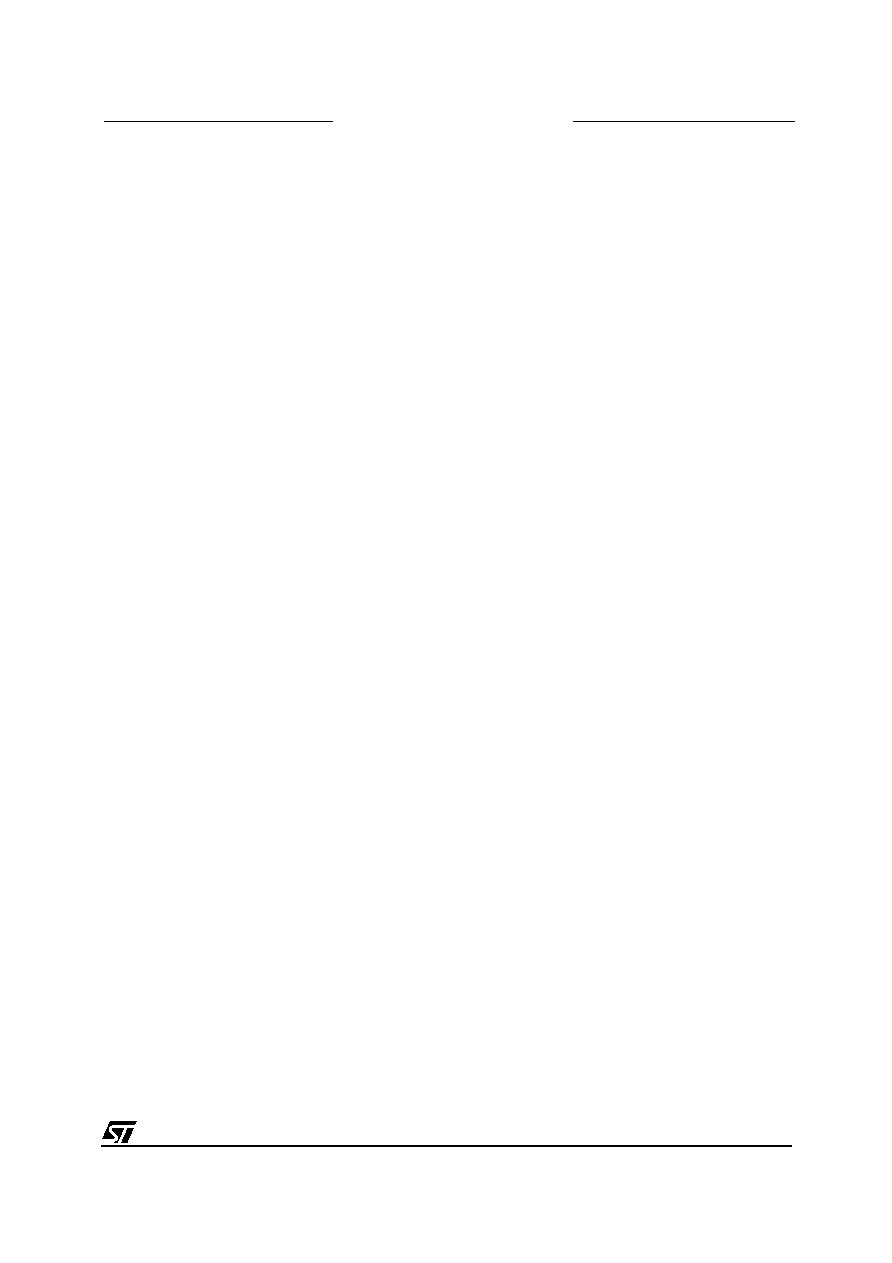

Figure 1. General Block Diagram

8-BIT CORE

ALU

ADDRESS AND DATA BUS

RESET

PORT A

CONTROL

RAM

(384 Bytes)

PA7:0

(8 bits)

V

SS

V

DD

POWER

SUPPLY

PROGRAM

(8K Bytes)

LVD

MEMORY

8-Bit

LITE TIMER 2

PORT B

SPI

PB6:0

(7 bits)

WDG

ADC

12-Bit

Auto-Reload

TIMER 2

LINSCI

Debug Module

OSC1

OSC2

Internal

CLOCK

PLL x 8

Ext.

1MHz

Int.

1MHz

1% RC

OSC

to

16MHz

CLKIN

/ 2

or PLL X4

DATA EEPROM

(

256 Bytes)

1

ST7LITE3

5/167

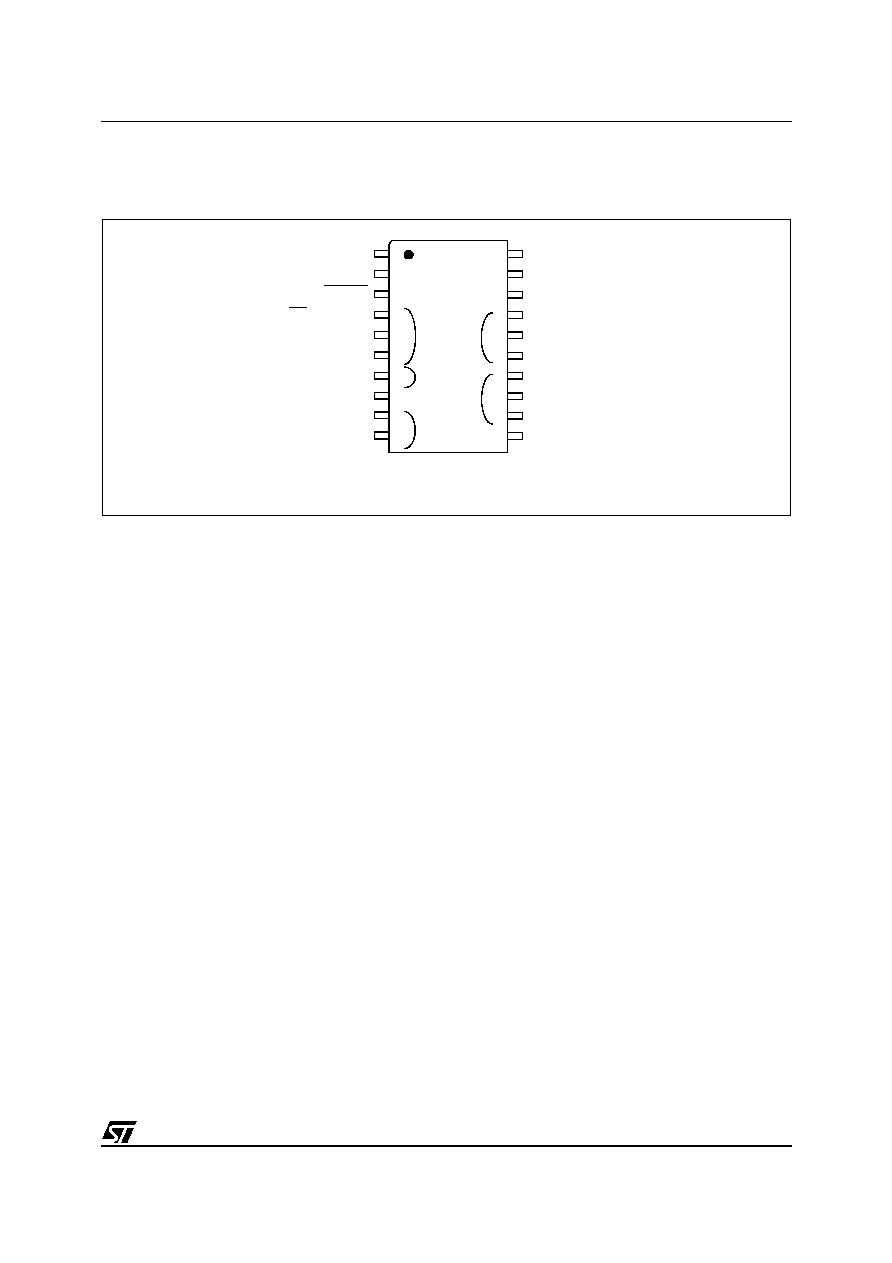

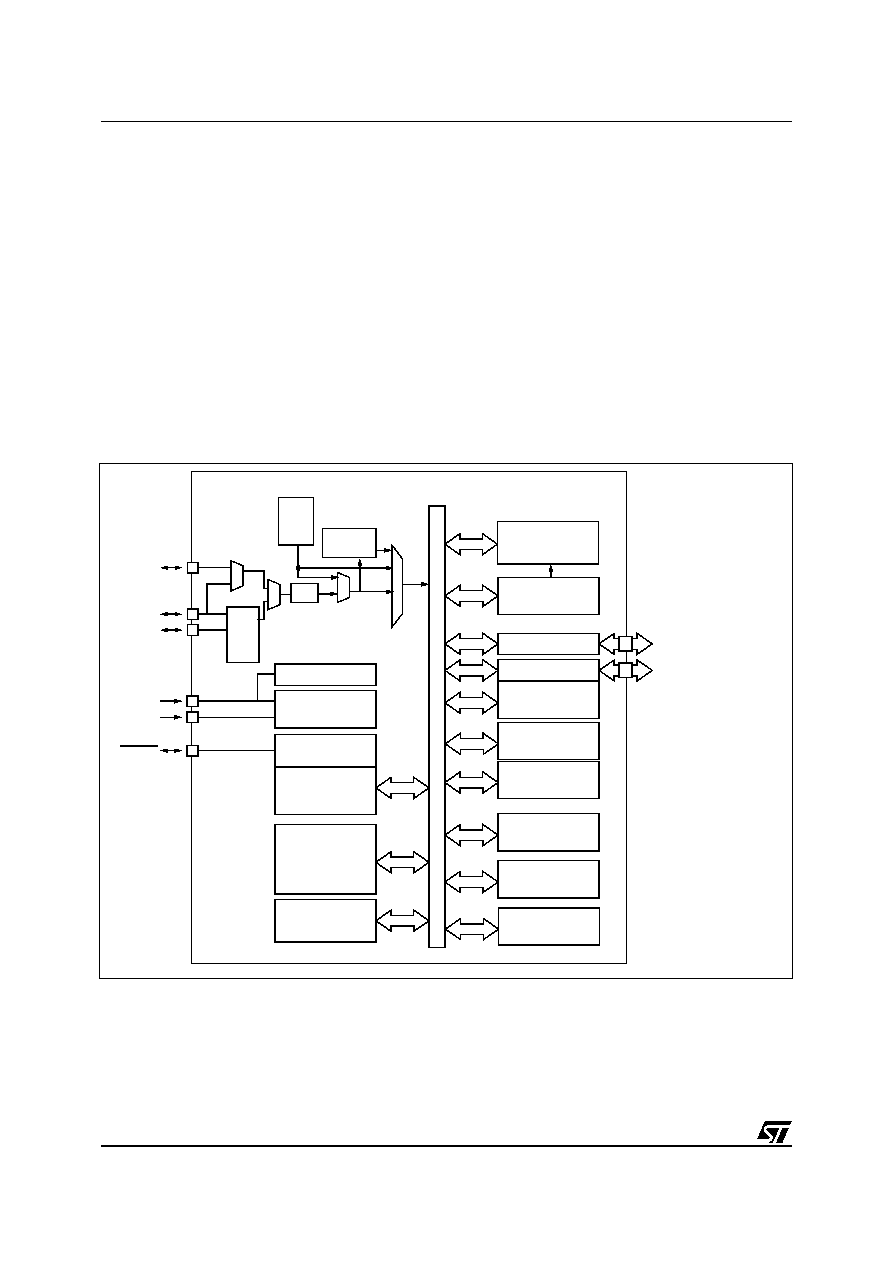

2 PIN DESCRIPTION

Figure 2. 20-Pin SO and DIP Package Pinout

20

19

18

17

16

15

14

13

1

2

3

4

5

6

7

8

V

SS

V

DD

AIN5/PB5

CLKIN/AIN4/PB4

MOSI/AIN3/PB3

MISO/AIN2/PB2

SCK/AIN1/PB1

SS/AIN0/PB0

OSC1/CLKIN

OSC2

PA5 (HS)/ATPWM3/ICCDATA

PA4 (HS)/ATPWM2

PA3 (HS)/ATPWM1

PA2 (HS)/ATPWM0

PA1 (HS)/ATIC

PA0 (HS)/LTIC

(HS) 20mA high sink capability

eix

associated external interrupt vector

12

11

9

10

RDI/AIN6/PB6

PA7 (HS)/TDO

PA6/MCO/ICCCLK/BREAK

RESET

ei3

ei2

ei0

ei1

ei2

1

Document Outline