| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: STG3000X | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

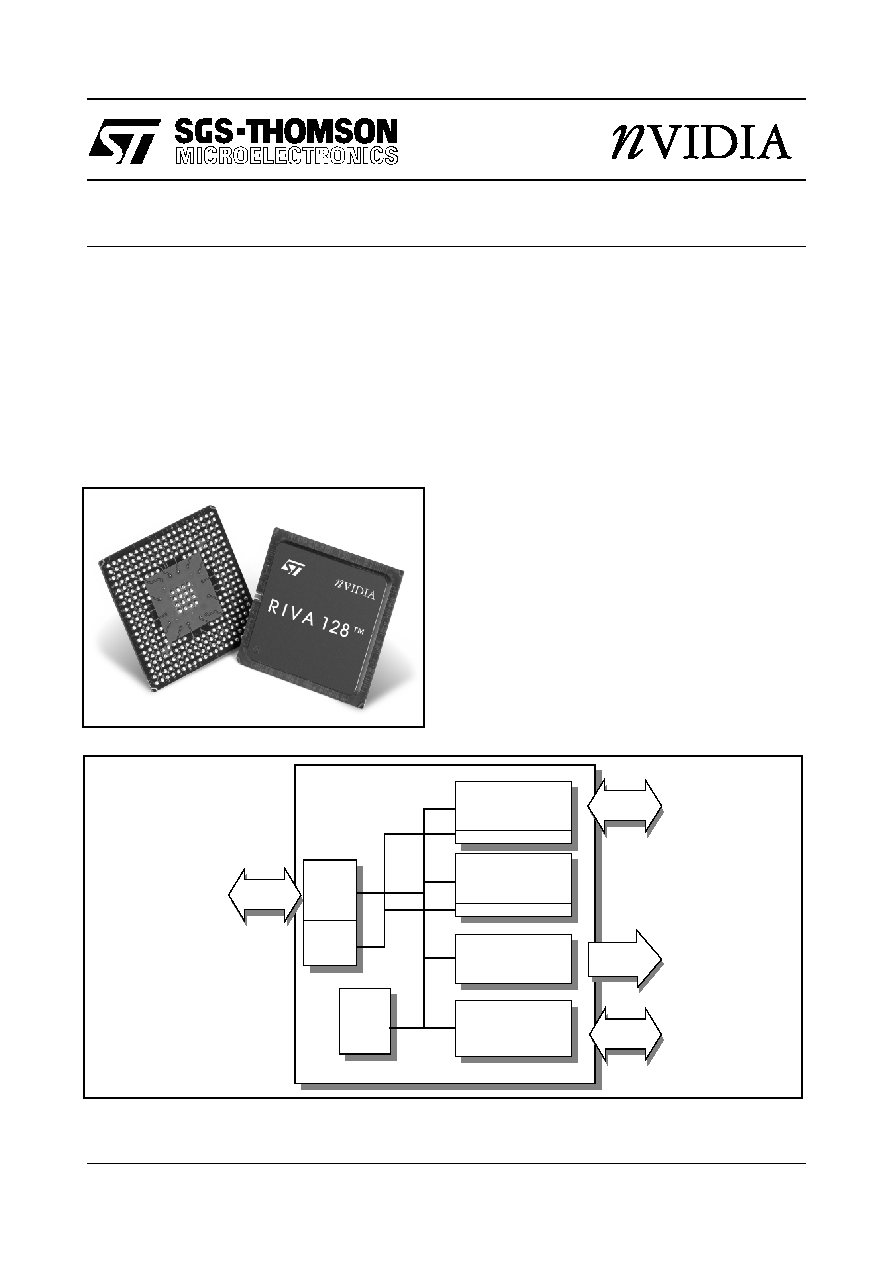

RIVA 128TM

128-BIT 3D MULTIMEDIA ACCELERATOR

Æ

TM

1/77

The information in this datasheet is subject to change

42 1687 01 (SGS-THOMSON)

October 1997

BLOCK DIAGRAM

Palette DAC

YUV - RGB,

Graphics Engine

128 bit 2D

Direct3D

SGRAM Interface

VGA

DMA Bus

I

n

t

e

r

nal

Bus

CCIR656

Video

PCI/AGP

128 bit

interface

Monitor/

TV

1.6 GByte/s

Internal Bus

Bandwidth

DMA Engine

Video Port

X & Y scaler

Host

Interface

FIFO/

DMA

Pusher

DMA Engine

DESCRIPTION

The RIVA 128TM is the first 128-bit 3D Multimedia

Accelerator to offer unparalleled 2D and 3D perfor-

mance, meeting all the requirements of the main-

stream PC graphics market and Microsoft's

PC'97. The RIVA 128 introduces the most ad-

vanced Direct3DTM acceleration solution and also

delivers leadership VGA, 2D and Video perfor-

mance, enabling a range of applications from 3D

games through to DVD, IntercastTM and video con-

ferencing.

KEY FEATURES

∑

Fast 32-bit VGA/SVGA

∑

High performance 128-bit 2D/GUI/DirectDraw

Acceleration

∑

Interactive, Photorealistic Direct3D Accelera-

tion with advanced effects

∑

Massive 1.6Gbytes/s, 100MHz 128-bit wide

frame buffer interface

∑

Video Acceleration for DirectDraw/DirectVideo,

MPEG-1/2 and Indeo

Æ

-

Planar 4:2:0 and packed 4:2:2 Color Space

Conversion

-

X and Y smooth up and down scaling

∑

230MHz Palette-DAC supporting up to

1600x1200@75Hz

∑

NTSC and PAL output with flicker-filter

∑

Multi-function Video Port and serial interface

∑

Bus mastering DMA 66MHz Accelerated

Graphics Port (AGP) 1.0 Interface

∑

Bus mastering DMA PCI 2.1 interface

∑

0.35 micron 5LM CMOS

∑

300 PBGA

RIVA 128

128-BIT 3D MULTIMEDIA ACCELERATOR

TABLE OF CONTENTS

2/77

1

REVISION HISTORY ......................................................................................................................

4

1

RIVA 128 300PBGA DEVICE PINOUT ..........................................................................................

5

2

PIN DESCRIPTIONS ......................................................................................................................

6

2.1

ACCELERATED GRAPHICS PORT (AGP) INTERFACE .....................................................

6

2.2

PCI 2.1 LOCAL BUS INTERFACE ........................................................................................

6

2.3

SGRAM FRAMEBUFFER INTERFACE ................................................................................

8

2.4

VIDEO PORT.........................................................................................................................

8

2.5

DEVICE ENABLE SIGNALS..................................................................................................

9

2.6

DISPLAY INTERFACE ..........................................................................................................

9

2.7

VIDEO DAC AND PLL ANALOG SIGNALS ..........................................................................

9

2.8

POWER SUPPLY ..................................................................................................................

9

2.9

TEST......................................................................................................................................

10

3

OVERVIEW OF THE RIVA 128 ......................................................................................................

11

3.1

BALANCED PC SYSTEM......................................................................................................

11

3.2

HOST INTERFACE ...............................................................................................................

11

3.3

2D ACCELERATION .............................................................................................................

12

3.4

3D ENGINE ...........................................................................................................................

12

3.5

VIDEO PROCESSOR............................................................................................................

12

3.6

VIDEO PORT.........................................................................................................................

13

3.7

DIRECT RGB OUTPUT TO LOW COST PAL/NTSC ENCODER .........................................

13

3.8

SUPPORT FOR STANDARDS..............................................................................................

13

3.9

RESOLUTIONS SUPPORTED..............................................................................................

13

3.10 CUSTOMER EVALUATION KIT............................................................................................

14

3.11 TURNKEY MANUFACTURING PACKAGE...........................................................................

14

4

ACCELERATED GRAPHICS PORT (AGP) INTERFACE .............................................................

15

4.1

RIVA 128 AGP INTERFACE .................................................................................................

16

4.2

AGP BUS TRANSACTIONS..................................................................................................

16

5

PCI 2.1 LOCAL BUS INTERFACE.................................................................................................

22

5.1

RIVA 128 PCI INTERFACE ...................................................................................................

22

5.2

PCI TIMING SPECIFICATION...............................................................................................

23

6

SGRAM FRAMEBUFFER INTERFACE.........................................................................................

29

6.1

SGRAM INITIALIZATION ......................................................................................................

31

6.2

SGRAM MODE REGISTER ..................................................................................................

31

6.3

LAYOUT OF FRAMEBUFFER CLOCK SIGNALS ................................................................

32

6.4

SGRAM INTERFACE TIMING SPECIFICATION ..................................................................

32

7

VIDEO PLAYBACK ARCHITECTURE...........................................................................................

37

7.1

VIDEO SCALER PIPELINE ...................................................................................................

38

8

VIDEO PORT ..................................................................................................................................

40

8.1

VIDEO INTERFACE PORT FEATURES ...............................................................................

40

8.2

BI-DIRECTIONAL MEDIA PORT POLLING COMMANDS USING MPC ..............................

41

8.3

TIMING DIAGRAMS ..............................................................................................................

42

8.4

656 MASTER MODE .............................................................................................................

46

8.5

VBI HANDLING IN THE VIDEO PORT .................................................................................

47

8.6

SCALING IN THE VIDEO PORT ...........................................................................................

47

9

BOOT ROM INTERFACE...............................................................................................................

48

128-BIT 3D MULTIMEDIA ACCELERATOR

RIVA 128

3/77

10

POWER-ON RESET CONFIGURATION........................................................................................

50

11

DISPLAY INTERFACE ...................................................................................................................

52

11.1 PALETTE-DAC ......................................................................................................................

52

11.2 PIXEL MODES SUPPORTED ...............................................................................................

52

11.3 HARDWARE CURSOR .........................................................................................................

53

11.4 I2C INTERFACE....................................................................................................................

54

11.5 ANALOG INTERFACE ..........................................................................................................

55

11.6 TV OUTPUT SUPPORT ........................................................................................................

56

12

IN-CIRCUIT BOARD TESTING ......................................................................................................

58

12.1 TEST MODES .......................................................................................................................

58

12.2 CHECKSUM TEST ................................................................................................................

58

13

ELECTRICAL SPECIFICATIONS ..................................................................................................

59

13.1 ABSOLUTE MAXIMUM RATINGS ........................................................................................

59

13.2 OPERATING CONDITIONS ..................................................................................................

59

13.3 DC SPECIFICATIONS...........................................................................................................

59

13.4 ELECTRICAL SPECIFICATIONS..........................................................................................

60

13.5 DAC CHARACTERISTICS ....................................................................................................

60

13.6 FREQUENCY SYNTHESIS CHARACTERISTICS................................................................

61

14

PACKAGE DIMENSION SPECIFICATION ....................................................................................

62

14.1 300 PIN BALL GRID ARRAY PACKAGE ..............................................................................

62

15

REFERENCES................................................................................................................................

63

16

ORDERING INFORMATION ..........................................................................................................

63

APPENDIX......................................................................................................................................

64

A

PCI CONFIGURATION REGISTERS .............................................................................................

64

A.1

REGISTER DESCRIPTIONS FOR PCI CONFIGURATION SPACE ....................................

64

128-BIT 3D MULTIMEDIA ACCELERATOR

RIVA 128

4/77

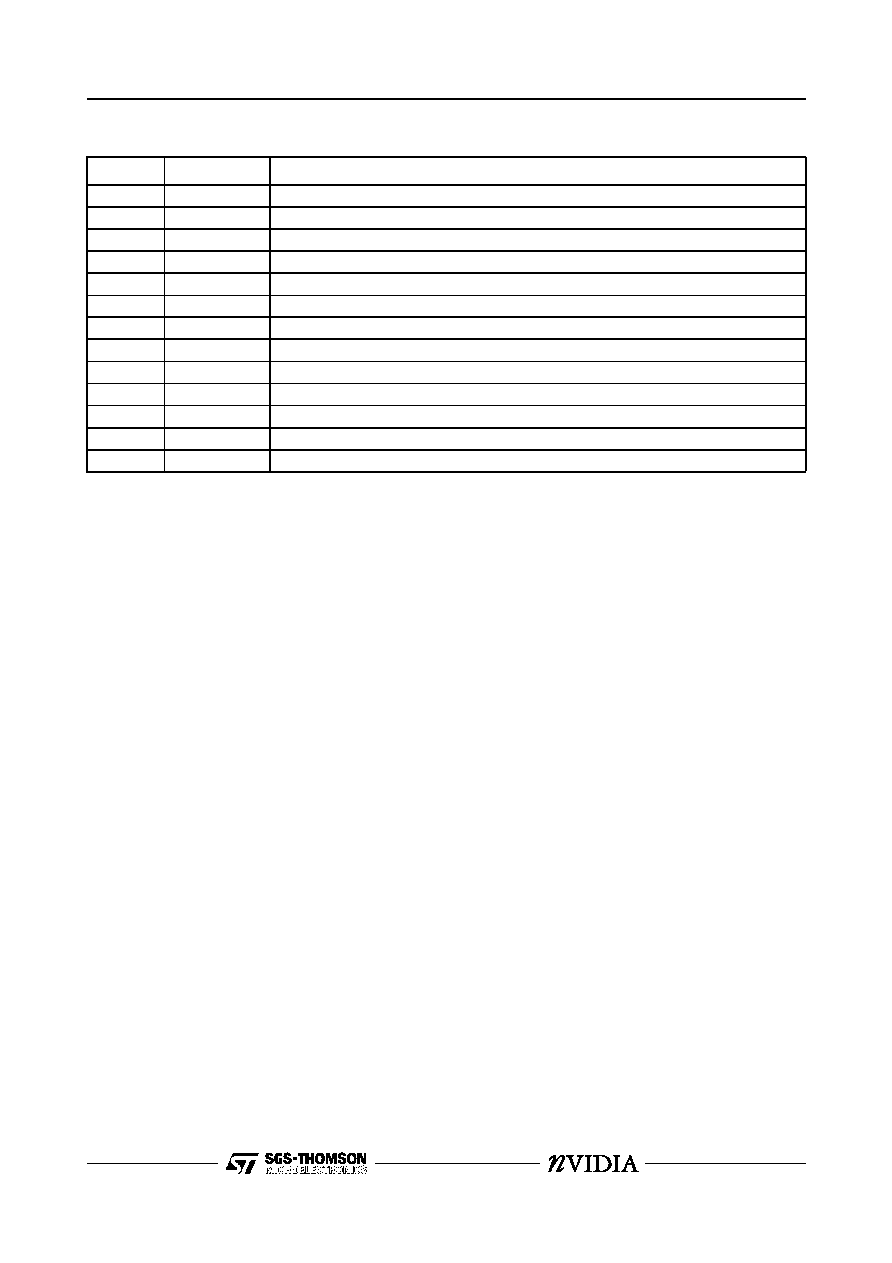

1

REVISION HISTORY

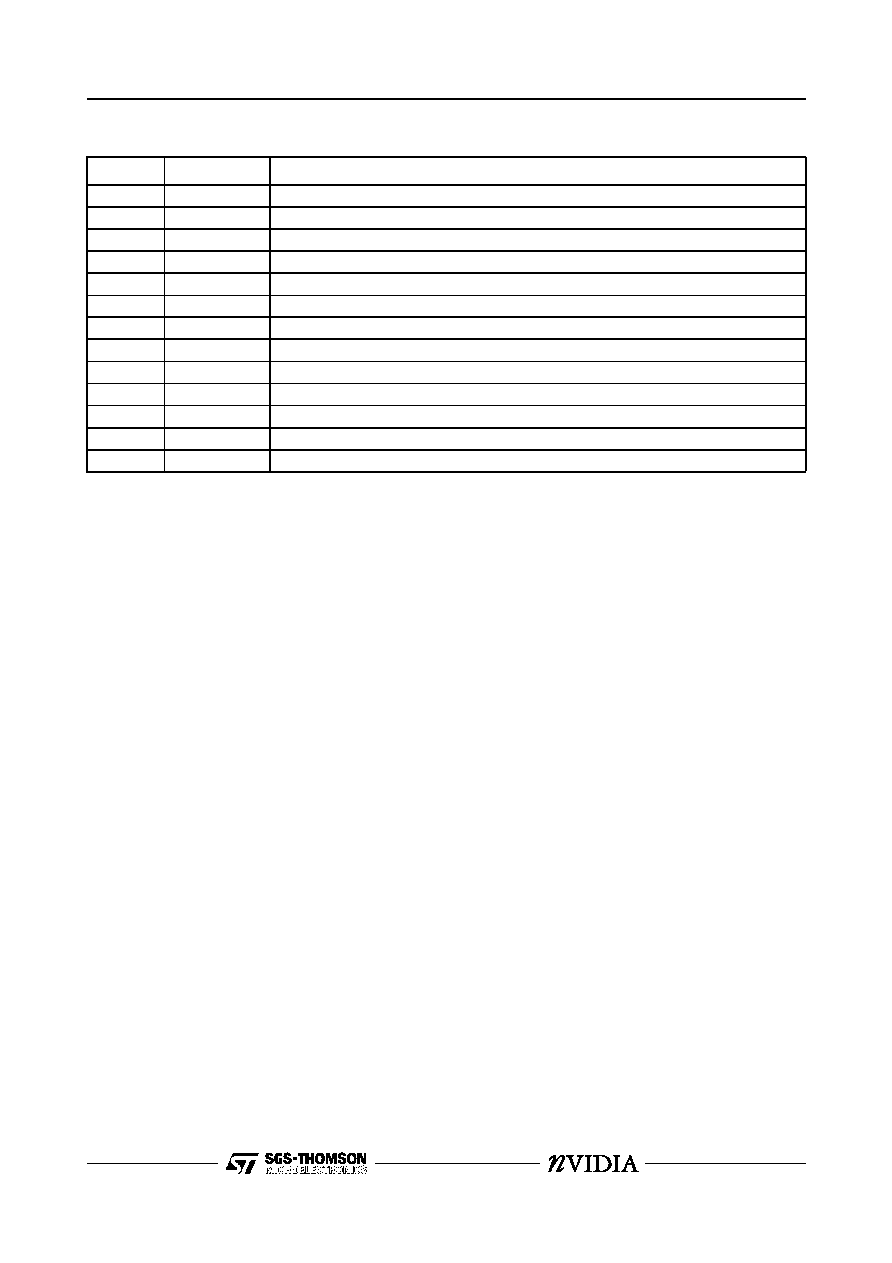

Date

Section, page

Description of change

15 Jul 97

6, page 28

Update of SGRAM framebuffer interface configuration diagrams.

28 Aug 97

13.5, page 59

Change of DAC specification from 206MHz to 230MHz max. operating frequency.

29 Aug 97

6.3, page 31

Update to recommendation for connection of FBCLK2 and FBCLKB pins.

4 Sep 97

10, page 49

Update to RAM Type Power-On Reset configuration bits.

15 Sep 97

13, page 58

Temperature specification TC now based on case, not ambient temperature.

15 Sep 97

13, page 58

Change to Power Supply voltage VDD specification.

17 Sep 97

1, page 5

Change to Video Port pin names.

17 Sep 97

2, page 6

Change to Video Port pin descriptions.

17 Sep 97

8, page 39

Updates to Video Port section.

18 Sep 97

11.6, page 55

Change to capacitor value in TV output implementation schematic.

18 Sep 97

13.3, page 58

Change to power dissipation specification.

25 Sep 97

4.2, page 16

Removal of AGP flow control description.

25 Sep 97

11.4, page 53

Updates to Serial Port description.

128-BIT 3D MULTIMEDIA ACCELERATOR

RIVA 128

5/77

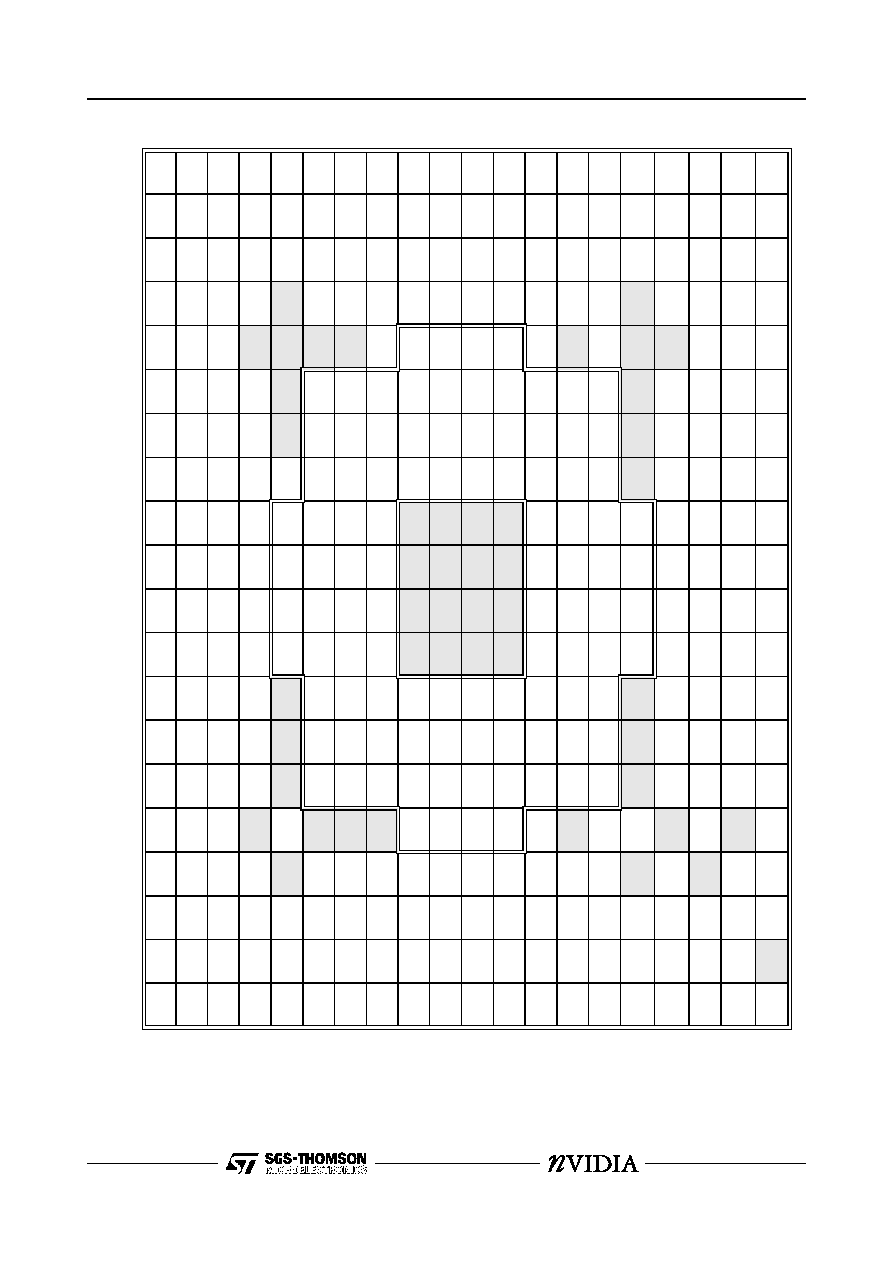

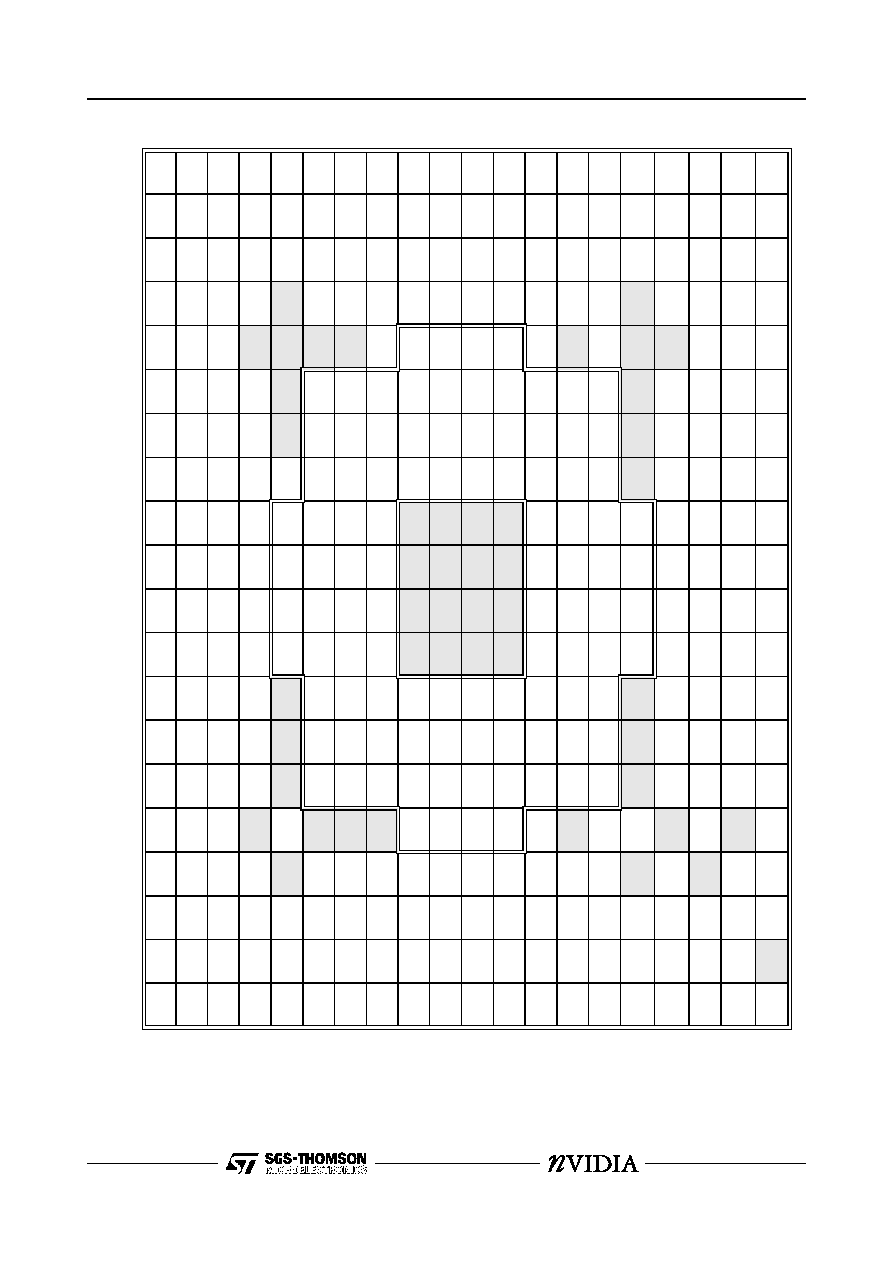

1

RIVA 128 300PBGA DEVICE PINOUT

NOTES

1

NIC = No Internal Connection. Do not connect to these pins.

2

VDD=3.3V

Signals denoted with an asterisk are defined for future expansion. See Pin Descriptions, Section 2, page 6 for details.

1234

56789

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

A

F

B

D

[

4]

F

B

D

[

6]

F

B

D

[

7

]

F

B

D

[

1

7

]

F

B

D

[

19]

F

B

D

[

21]

F

B

D

[

23

]

F

B

D

Q

M

[

2

]

F

B

A

[

0]

F

B

A

[

2

]

F

B

A

[

4]

F

B

A

[

6]

F

B

A

[

8]

F

B

D

Q

M

[

5]

F

B

D

[

41]

F

B

D

[

43]

F

B

D

[

45

]

F

B

D

[

4

7]

F

B

D

[

5

6

]

F

B

D

[

57]

B

F

B

D

[

3]

F

B

D

[

5]

F

B

D

[

16

]

F

B

D

[

1

8]

F

B

D

[

20]

F

B

D

[

22]

F

B

D

Q

M

[

0]

F

B

A

[

9]

F

B

A

[

1]

F

B

A

[

3

]

F

B

A

[

5]

F

B

A

[

7]

F

B

C

L

K

1

F

B

D

Q

M

[

7]

F

B

D

[

40]

F

B

D

[

42]

F

B

D

[

44

]

F

B

D

[

4

6]

F

B

D

[

5

8

]

F

B

D

[

59]

C

FB

D

[

1

]

FB

D

[

2

]

FB

D

[

2

8

]

F

B

D

[2

7

]

FB

D

[

2

6

]

FB

D

[

2

5

]

FB

D

[

1

5

]

F

B

D

[1

3

]

F

B

D

[

1

1

]

F

B

D

[9

]

F

B

D

Q

M

[1

]

F

B

W

E

#

FB

R

A

S

#

F

BA[

1

0

]

F

B

D

Q

M

[

4]

F

B

D

[

55]

F

B

D

[

54

]

F

B

D

[

5

3]

F

B

D

[

6

0

]

F

B

D

[

61]

D

FB

C

L

K

0

FB

D

[

0

]

FB

D

[

2

9

]

F

B

D

[3

0

]

VD

D

F

BD

[

2

4

]

F

B

D

[

1

4

]

F

BD

[

1

2

]

F

B

D

[

1

0

]

F

BD

[

8

]

F

BD

Q

M

[

3

]

F

BC

AS#

F

B

C

S

0

F

BC

S1

F

B

D

Q

M

[

6

]

V

D

D

F

B

D

[5

2

]

FB

D

[

5

1

]

F

B

D

[6

2

]

FB

D

[

6

3

]

E

SC

L

F

BC

L

K

2

F

BD

[

3

1

]

VD

D

N

I

C

VD

D

VD

D

VD

D

FB

C

K

E

VD

D

VD

D

VD

D

VD

D

F

BD

[

5

0

]

F

B

D

[

3

9

]

F

BD

[

3

8

]

F

M

P

_

A

D[

6

]

NI

C

S

DA

F

B

CL

K

F

B

VD

D

V

D

D

F

B

D

[4

8

]

FB

D

[

4

9

]

F

B

D

[3

7

]

FB

D

[

3

6

]

G

M

P

F

R

A

M

E

#

M

P

_A

D

[

7]

M

P

_A

D

[

5]

M

P

_A

D

[

4

]

MP

C

L

A

M

P

V

D

D

F

B

D

[3

5

]

FB

D

[

3

4

]

F

B

D

[3

3

]

FB

D

[

3

2

]

H

M

P

_A

D

[

2]

M

P

S

T

O

P

#

M

P

C

LK

M

P

_A

D

[

3

]

VD

D

N

I

C

F

B

D

Q

M

[1

2

]

FB

D

Q

M

[

1

4

]

F

B

D

Q

M

[1

5

]

FB

D

Q

M

[

1

3

]

J

F

B

D

Q

M

[

8]

M

P

D

T

A

C

K

#

M

P

_A

D

[

1]

M

P

_A

D

[

0

]

GN

D

GN

D

GN

D

G

N

D

F

B

D

[

118

]

F

B

D

[

1

1

9

]

F

B

D

[

1

05]

F

B

D

[

1

04]

K

FB

D

Q

M

[

9

]

FB

D

[

8

7

]

F

B

D

Q

M

[1

0

]

FB

D

Q

M

[

1

1

]

GN

D

GN

D

GN

D

G

N

D

F

B

D

[

116

]

F

B

D

[

1

1

7

]

F

B

D

[

1

07]

F

B

D

[

1

06]

L

FB

D

[

8

6

]

FB

D

[

8

5

]

F

B

D

[7

2

]

FB

D

[

7

3

]

GN

D

GN

D

GN

D

G

N

D

F

B

D

[

114

]

F

B

D

[

1

1

5

]

F

B

D

[

1

09]

F

B

D

[

1

08]

M

FB

D

[

8

4

]

FB

D

[

8

3

]

F

B

D

[7

4

]

FB

D

[

7

5

]

GN

D

GN

D

GN

D

G

N

D

F

B

D

[

112

]

F

B

D

[

1

1

3

]

F

B

D

[

1

11]

F

B

D

[

1

10]

N

FB

D

[

8

2

]

FB

D

[

8

1

]

F

B

D

[7

6

]

FB

D

[

7

7

]

N

IC

N

I

C

F

B

D

[

102

]

F

B

D

[

1

0

3

]

F

B

D

[

1

21]

F

B

D

[

1

20]

P

FB

D

[

8

0

]

FB

D

[

7

1

]

F

B

D

[7

8

]

FB

D

[

7

9

]

VD

D

V

D

D

F

B

D

[

100

]

F

B

D

[

1

0

1

]

F

B

D

[

1

23]

F

B

D

[

1

22]

R

FB

D

[

7

0

]

FB

D

[

6

9

]

F

B

D

[8

8

]

FB

D

[

8

9

]

N

IC

N

I

C

F

B

D

[9

8

]

FB

D

[

9

9

]

F

B

D

[1

2

5

]

F

B

D

[

1

2

4

]

T

FB

D

[

6

8

]

FB

D

[

6

7

]

F

B

D

[9

0

]

VD

D

N

I

C

H

O

ST

VD

D

H

O

ST

VD

D

H

O

ST

-

C

L

AM

P

H

O

ST

V

D

D

H

O

ST

-

C

L

AM

P

H

O

ST

VD

D

H

O

ST

-

CL

A

M

P

V

D

D

F

B

D

[

9

7]

F

B

D

[

1

27]

F

B

D

[

1

26]

U

FB

D

[

6

6

]

FB

D

[

6

5

]

F

B

D

[9

2

]

FB

D

[

9

1

]

H

O

ST

-

C

L

AM

P

XT

AL

O

U

T

P

C

I

R

S

T

#

AG

PST

[

1

]

P

C

I

AD

[

3

0

]

PC

I

A

D

[

2

6

]

P

C

I

C

BE#

[

3

]

P

C

I

AD

[

2

0

]

PC

I

A

D

[

1

6

]

P

C

I

T

R

D

Y

#

P

C

I

P

A

R

H

O

ST

VD

D

P

C

I

C

BE#

[

0

]

F

BD

[

9

6

]

VI

D

VSYN

C

V

I

D

H

SYN

C

V

F

B

D

[

64]

F

B

D

[

95

]

R

E

D

D

A

C

V

D

D

VR

EF

PC

I

I

N

T

A

#

P

C

I

G

N

T

#

A

G

P

P

I

P

E

#

PC

I

A

D

[

2

8

]

P

C

I

AD

[

2

4

]

PC

I

A

D

[

2

2

]

PC

I

A

D

[

1

8

]

PC

I

F

R

AM

E#

PC

I

S

T

O

P#

PC

I

A

D

[

1

5

]

P

C

I

AD

[

1

1

]

PC

I

A

D

[

6

]

PC

I

A

D

[

2

]

T

EST

M

O

D

ER

O

M

C

S

#

W

F

B

D

[

93]

F

B

D

[

94

]

B

LU

E

C

O

M

P

PL

L

V

D

D

PC

I

R

EQ

#

A

G

PST

[

2

]

P

C

I

AD

[

3

1

]

PC

I

A

D

[

2

7

]

AG

P

A

D

-

ST

B1

PC

I

A

D

[

2

1

]

PC

I

A

D

[

1

7

]

PC

I

I

R

D

Y

#

P

C

I

C

BE#

[

1

]

P

C

I

AD

[

1

3

]

PC

I

A

D

[

9

]

PC

I

A

D

[

4

]

PC

I

A

D

[

0

]

PC

I

A

D

[

7

]

PC

I

A

D

[

5

]

Y

G

R

EEN

G

N

D

R

SET

XT

AL

I

N

PC

I

C

L

K

A

G

PST

[

0

]

PC

I

I

D

SEL

/

A

G

PR

BF

#

PC

I

A

D

[

2

9

]

P

C

I

AD

[

2

5

]

PC

I

A

D

[

2

3

]

P

C

I

AD

[

1

9

]

PC

I

C

BE#

[

2

]

PC

I

-

D

EVSEL

#

PC

I

A

D

[

1

4

]

P

C

I

AD

[

1

2

]

PC

I

A

D

[

1

0

]

PC

I

A

D

[

8

]

AG

P

A

D

-

ST

B0

PC

I

A

D

[

3

]

PC

I

A

D

[

1

]