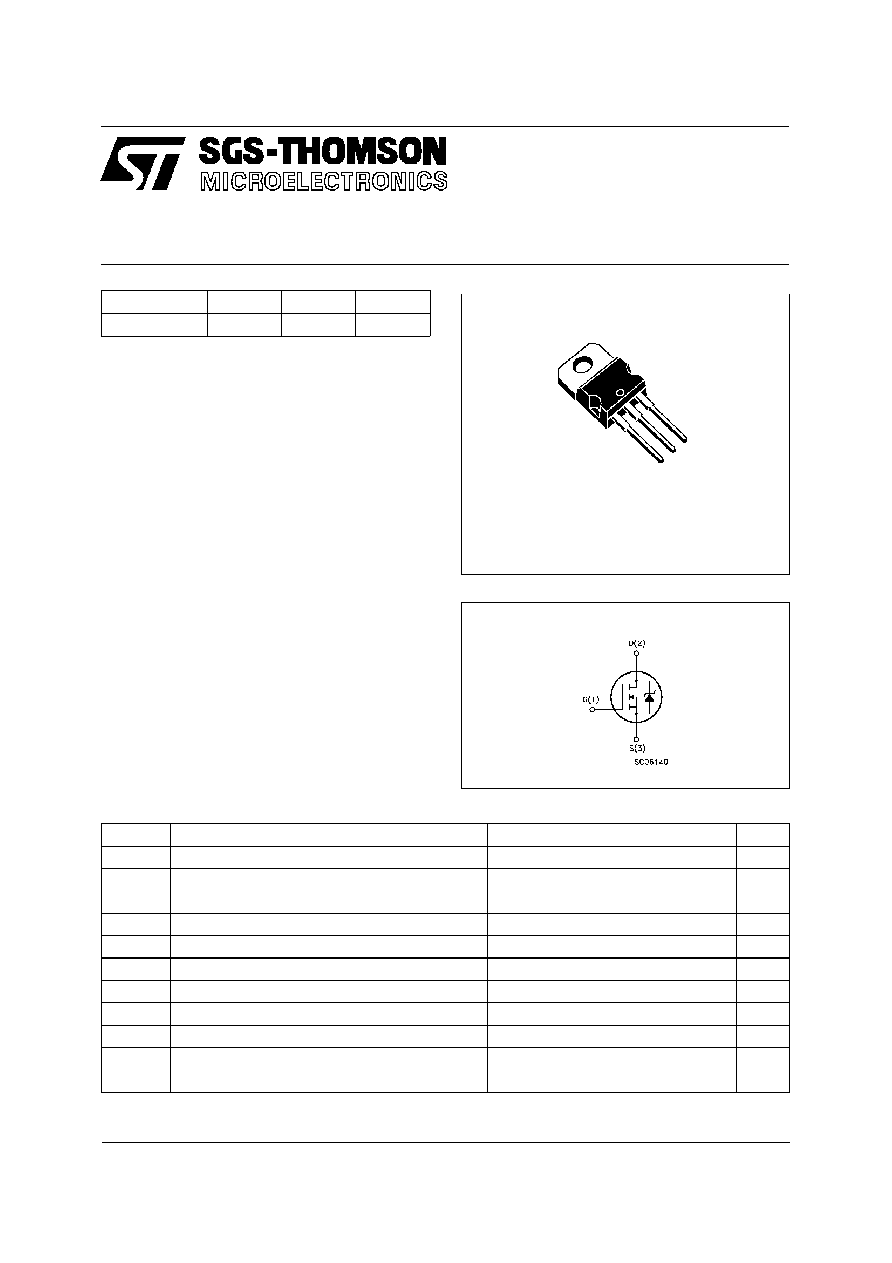

STP40N03L-20

N - CHANNEL ENHANCEMENT MODE

"ULTRA HIGH DENSITY" POWER MOS TRANSISTOR

PRELIMINARY DATA

s

TYPICAL R

DS(on)

= 0.016

s

AVALANCHE RUGGED TECHNOLOGY

s

100% AVALANCHE TESTED

s

HIGH CURRENT CAPABILITY

s

175

o

C OPERATING TEMPERATURE

s

HIGH dV/dt CAPABILITY

s

APPLICATION ORIENTED

CHARACTERIZATION

APPLICATIONS

s

HIGH CURRENT, HIGH SPEED SWITCHING

s

POWER MOTOR CONTROL

s

DC-DC & DC-AC CONVERTERS

s

SYNCRONOUS RECTIFICATION

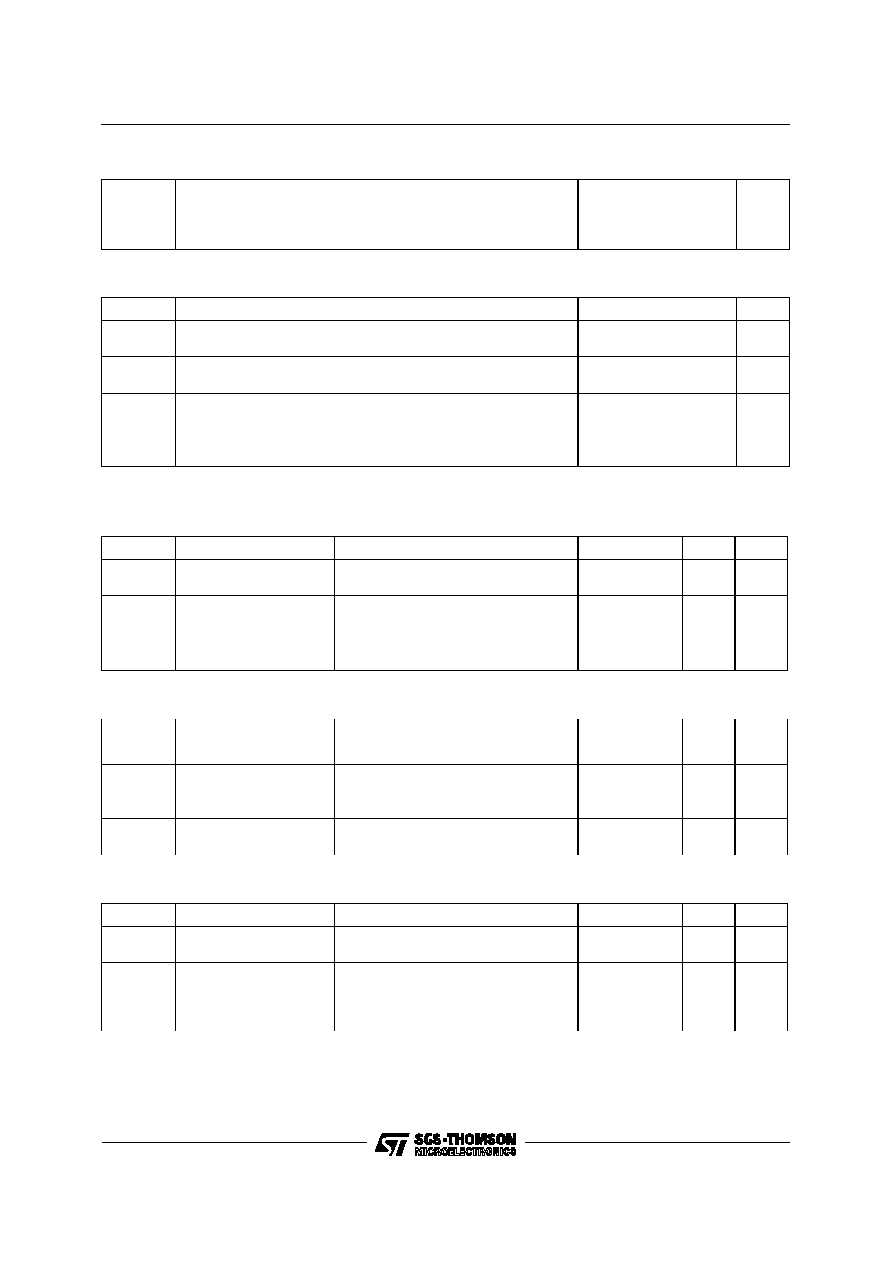

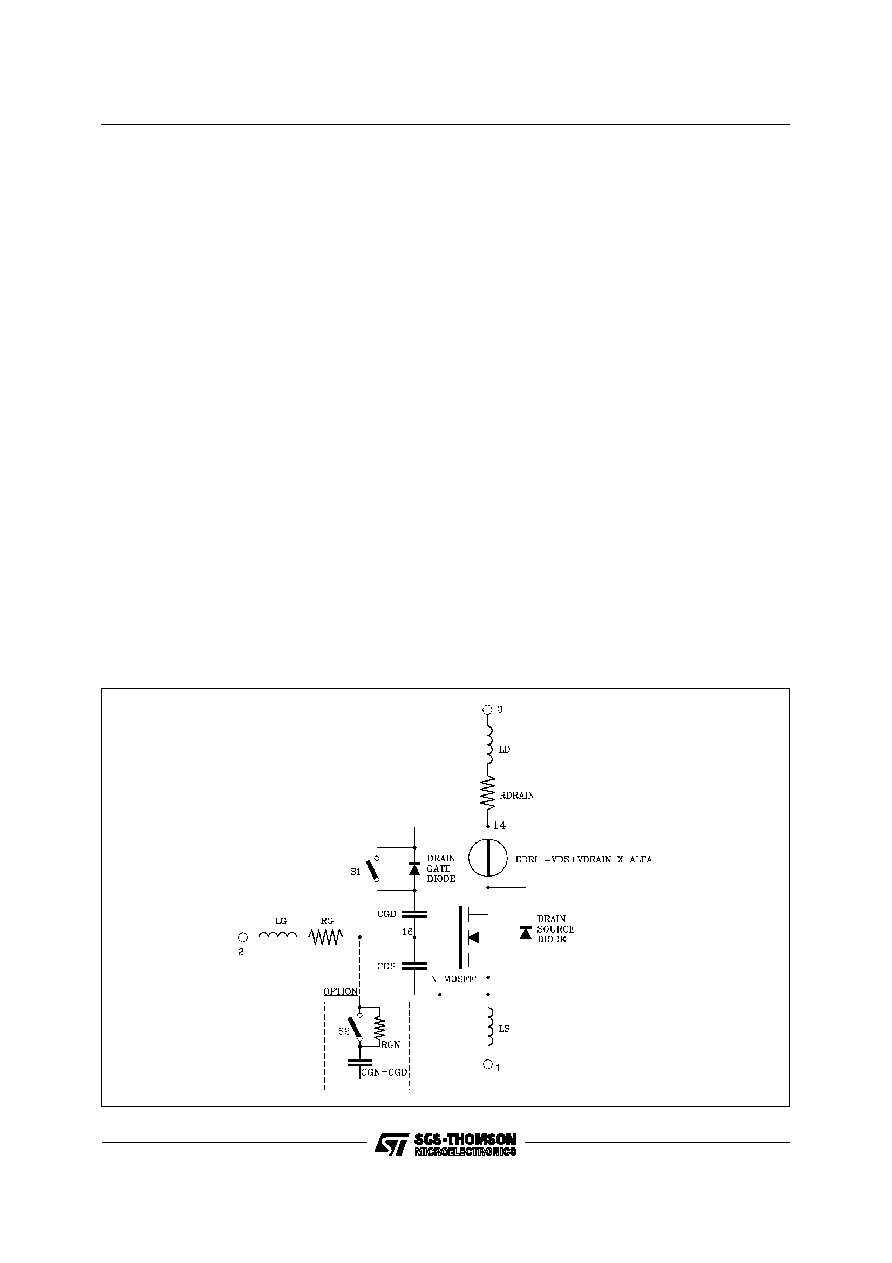

INTERNAL SCHEMATIC DIAGRAM

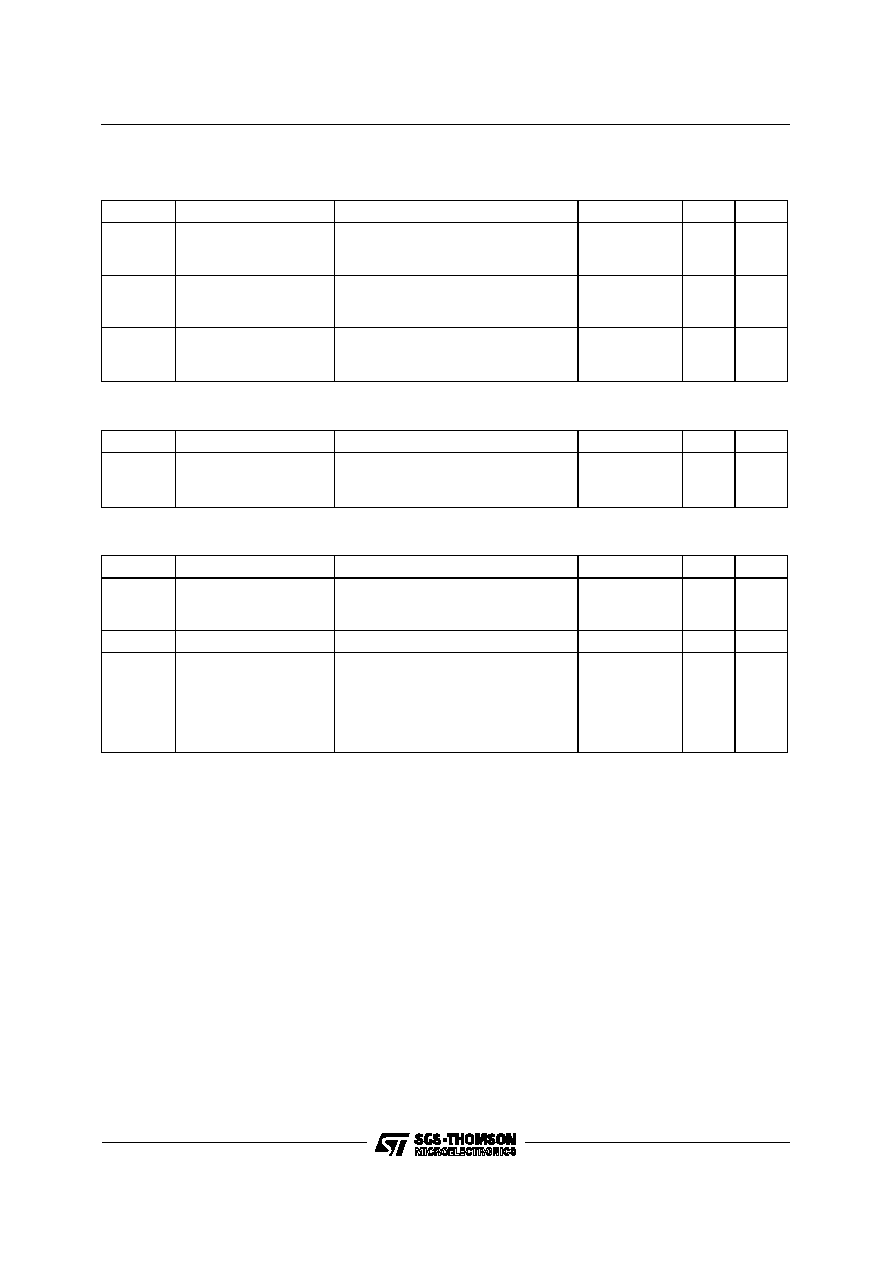

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Uni t

V

DS

Drain-source Voltage (V

GS

= 0)

30

V

V

DGR

Drain- gate Voltage (R

G S

= 20 k

)

30

V

V

GS

Gate-source Voltage

±

15

V

I

D

Drain Current (continuous) at T

c

= 25

o

C

40

A

I

D

Drain Current (continuous) at T

c

= 100

o

C

28

A

I

DM

(

∑

)

Drain Current (pulsed)

160

A

P

to t

Total Dissipat ion at T

c

= 25

o

C

90

W

Derating Fact or

0.6

W/

o

C

dV/dt(

1

)

Peak Diode Recovery voltage slope

6

V/ ns

T

st g

St orage Temperature

-65 to 175

o

C

T

j

Max. Operating Junction Temperat ure

175

o

C

(

∑

) Pulse width limited by safe operating area

TYPE

V

DSS

R

DS(on)

I

D

ST P40N03L-20

30 V

< 0.02

40 A

March 1996

1

2

3

TO-220

1/7

THERMAL DATA

R

t hj-ca se

R

t hj- amb

R

thc- si nk

T

l

Thermal Resistance Junction-case

Max

Thermal Resistance Junction-ambient

Max

Thermal Resistance Case-sink

Typ

Maximum Lead T emperature For Soldering Purpose

1.66

62.5

0.5

300

o

C/W

o

C/W

o

C/W

o

C

AVALANCHE CHARACTERISTICS

Symb ol

Parameter

Max Valu e

Uni t

I

AR

Avalanche Current , Repet itive or Not -Repetitive

(pulse widt h limited by T

j

max,

< 1%)

40

A

E

AS

Single Pulse Avalanche Energy

(starting T

j

= 25

o

C, I

D

= I

AR

, V

DD

= 25 V)

300

mJ

E

AR

Repetit ive Avalanche Energy

(pulse widt h limited by T

j

max,

< 1%)

75

mJ

I

AR

Avalanche Current , Repet itive or Not -Repetitive

(T

c

= 100

o

C, pulse width limited by T

j

max,

< 1%)

28

A

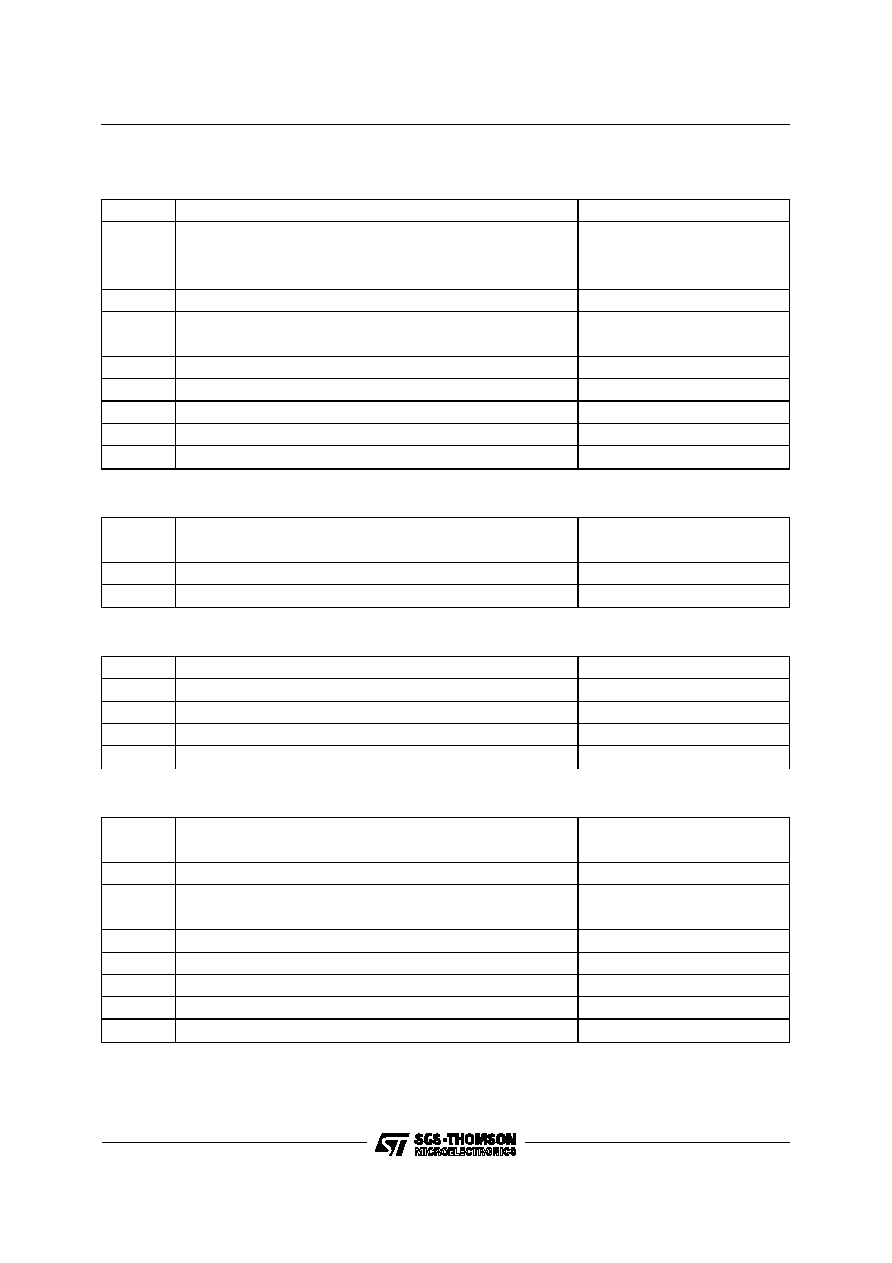

ELECTRICAL CHARACTERISTICS (T

case

= 25

o

C unless otherwise specified)

OFF

Symb ol

Parameter

Test Cond ition s

Mi n.

Typ .

Max.

Un it

V

(BR)DSS

Drain-source

Breakdown Volt age

I

D

= 250

µ

A

V

G S

= 0

30

V

I

DSS

Zero Gat e Voltage

Drain Current (V

GS

= 0)

V

DS

= Max Rating

V

DS

= Max Rating x 0. 8

T

c

= 125

o

C

250

1000

µ

A

µ

A

I

GSS

Gate-body Leakage

Current (V

DS

= 0)

V

G S

=

±

15 V

±

100

nA

ON (

)

Symb ol

Parameter

Test Cond ition s

Mi n.

Typ .

Max.

Un it

V

GS(th)

Gate T hreshold Voltage V

DS

= V

GS

I

D

= 250

µ

A

1

1.6

2

V

R

DS( on)

St atic Drain-source On

Resistance

V

G S

= 10V

I

D

= 20 A

V

G S

= 10V

I

D

= 20 A

T

c

= 100

o

C

V

G S

= 5V

I

D

= 20 A

0.016

0.019

0.02

0.04

0. 023

I

D(o n)

On Stat e Drain Current

V

DS

> I

D(on)

x R

DS(on) max

V

G S

= 10 V

40

A

DYNAMIC

Symb ol

Parameter

Test Cond ition s

Mi n.

Typ .

Max.

Un it

g

fs

(

)

Forward

Transconductance

V

DS

> I

D(on)

x R

DS(on) max

I

D

= 20 A

15

22

S

C

iss

C

oss

C

rss

Input Capacitance

Output Capacit ance

Reverse Transfer

Capacitance

V

DS

= 25 V

f = 1 MHz

V

GS

= 0

1800

450

180

2300

580

230

pF

pF

pF

STP40N03L-20

2/7

ELECTRICAL CHARACTERISTICS (continued)

SWITCHING ON

Symb ol

Parameter

Test Cond ition s

Mi n.

Typ .

Max.

Un it

t

d(on)

t

r

Turn-on T ime

Rise Time

V

DD

= 15 V

I

D

= 10 A

R

G

= 4.7

V

GS

= 5 V

(see t est circuit, figure 3)

20

80

30

100

ns

ns

(di/ dt)

on

Turn-on Current Slope

V

DD

= 24 V

I

D

= 20 A

R

G

= 50

V

GS

= 5 V

(see t est circuit, figure 5)

200

A/

µ

s

Q

g

Q

gs

Q

gd

Total Gat e Charge

Gate-Source Charge

Gate-Drain Charge

V

DD

= 24 V

I

D

= 20 A

V

G S

= 5 V

40

10

20

60

nC

nC

nC

SWITCHING OFF

Symb ol

Parameter

Test Cond ition s

Mi n.

Typ .

Max.

Un it

t

r(Vof f)

t

f

t

c

Of f-voltage Rise Time

Fall T ime

Cross-over T ime

V

DD

= 24 V

I

D

= 20 A

R

G

= 4.7

V

G S

= 5 V

(see t est circuit, figure 5)

42

45

76

55

60

100

ns

ns

ns

SOURCE DRAIN DIODE

Symb ol

Parameter

Test Cond ition s

Mi n.

Typ .

Max.

Un it

I

SD

I

SDM

(

∑

)

Source-drain Current

Source-drain Current

(pulsed)

40

160

A

A

V

SD

(

)

Forward O n Volt age

I

SD

= 40 A

V

GS

= 0

1.5

V

t

rr

Q

rr

I

RRM

Reverse Recovery

Time

Reverse Recovery

Charge

Reverse Recovery

Current

I

SD

= 20 A

di/ dt = 100 A/

µ

s

V

DD

= 24 V

T

j

= 150

o

C

(see t est circuit, figure 5)

65

0. 12

4

ns

µ

C

A

(

) Pulsed: Pulse duration = 300

µ

s, duty cycle 1.5 %

(

∑

) Pulse width limited by safe operating area

(

1

) I

SD

40 A, di/dt

300 A/

µ

s, V

DD

V

(BR)DSS

, T

j

T

JMAX

STP40N03L-20

3/7

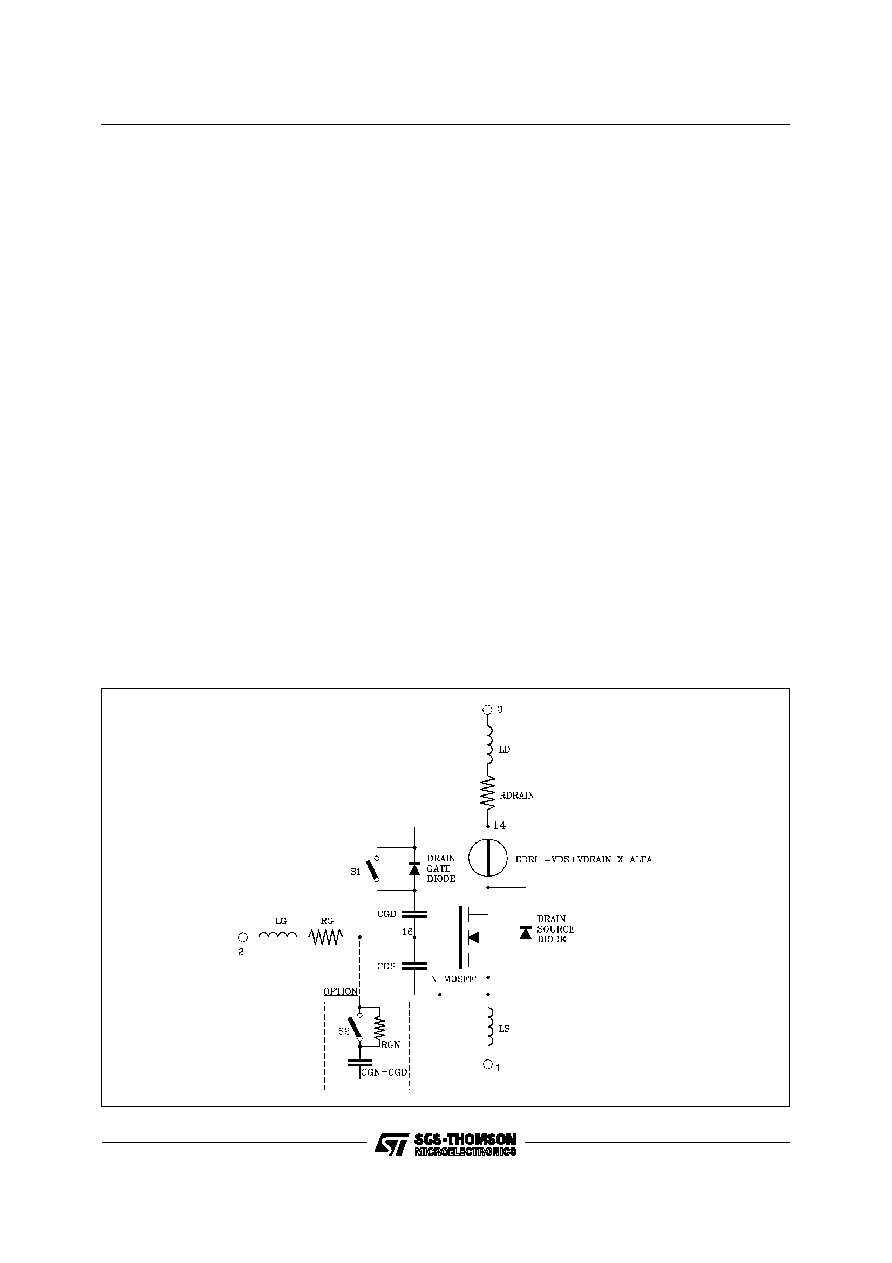

PSPICE PARAMETERS

SUBCIRCUIT COMPONENTS

Symb ol

Parameter

Valu e

Uni t

S1

(V14_16<0) (See Power Mosfet Model Subcircuit)

O N

S2

(V16_11<0) (See Power Mosfet Model Subcircuit)

O N

LD

Drain Induct ance

8

nH

LG

Gate I nductance

10

nH

LS

Source Inductance

10

nH

RDRAIN

Drain Resistance

1.9E

-2

RG ATE

Gate Resistance

1

CG D

Gate Drain Capacitance

3.92

nF

CGS

Gate Source Capacit ance

1. 9

nF

ALFA

Drift Coef icient

1E

-3

V

-1

RG N

Negative Bias Resistance

10

K

DIODE DRAIN GATE (Depletion Capacitance)

Symb ol

Parameter

Valu e

Uni t

CJO

Zero Bias p-n Capacitance

2. 7

nF

VJ

p-n Potential

0.35

V

M

p-n G rading Coef ficient

0.55

DIODE DRAIN SOURCE

Symb ol

Parameter

Valu e

Uni t

CJO

Zero Bias p-n Capacitance

10

nF

VJ

p-n Potential

0.35

V

M

p-n G rading Coef ficient

0.55

TT

Transit Time

20

nsec

N MOSFET

Symb ol

Parameter

Valu e

Uni t

L

Channel Lengt h

1

µ

Meter

W

Channel Width

1

µ

Meter

LEVEL

Model I ndex

3

TO X

Oxide Thickness

1

Met er

VT O

Zero Bias Threshold Voltage

3.25

V

U0

Surface Mobility

600

cm

2

/VS

THETA

Mobility Modulation

0.005

V

-1

Vmax

Maximum Drif t Velocit y

0

Meter/sec

KP

Trans Conductance Coefficient

15

Amp/V

2

For Transient Simulation Applicate U.I.C. (Use Initial Condition) Option

STP40N03L-20

4/7

PSPICE NETLIST OF THE SUBCIRCUIT

. SUBCKT STP40N03L-20 1 2 3

*VALUE OF THE PACKAG E INDUCTANCES

LS 1 11 10n

LG 2 12 10n

LD 3 13 7n

*RESISTA NCE O F T HE G AT E

POLYSILI CON

RG 12 16 1

*EPY AND DRIF T RESISTANCES

RD 13 14 1. 9e-02

EDRI 14 15 POLY(2) (13 14) (13 11) 0 0 0 0

1e-3

*CAPACITANCE G ATE SO URCE

CGS 16 11 1.90n

*OPT IO NAL FO R NEGAT IVE GATE BIAS

*S2 51 11 11 16 SWI TCH

*CGN 51 16 3.92n

*RGN 51 16 10k

*MILLER CAPACI TANCE

CGD 16 17 3.92n

* DEPLET ION CAPACIT ANCE

DGD 17 14 DGD

S1 17 14 16 14 SW ITCH

. MODEL DGD D +I S=

+CJO =2. 6n

+Vj=.1

+M=.6

. MODEL SWITCH VSW IT CH

+RON=1m

+ROF F=1MEG

+VON=0. 1

* OUTPUT CAPACITANCE AND BODY DRAI N DI ODE

DBD 11 14 DBD

. MODEL DBD D

+TT=20n

+CJO =7. 8n

+VJ=.1

+M=.6

* MO DEL OF THE MO SF ET

MMAI N 15 16 11 11 MMAI N L=1u W =1u

. MODEL MMAIN NMO S

+LEVEL=3

+TOX=1

+VTO =3. 25

+uo=600

+THETA=0.005

+VMAX=5e7

+KP=28

. ENDS

Power Mosfet Model Subcircuit

STP40N03L-20

5/7

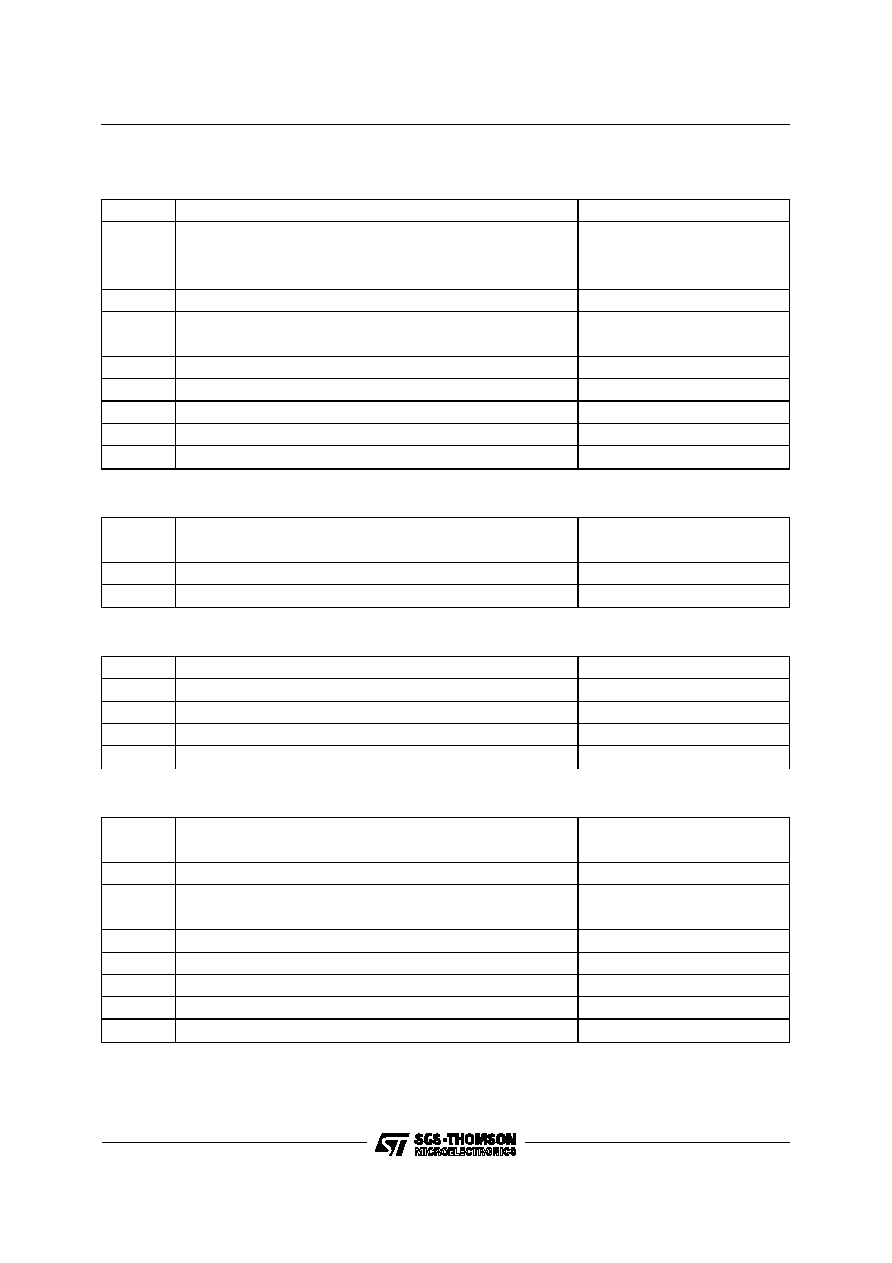

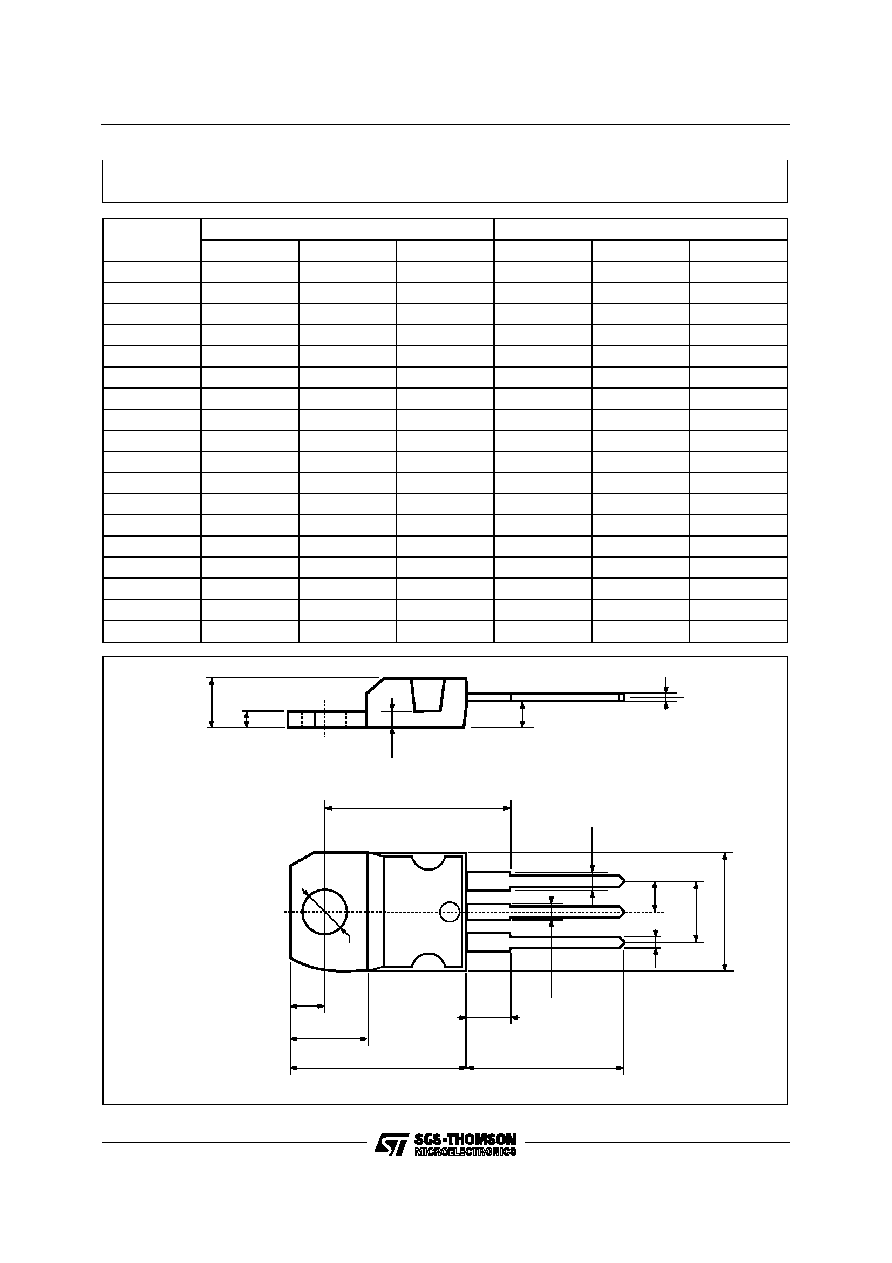

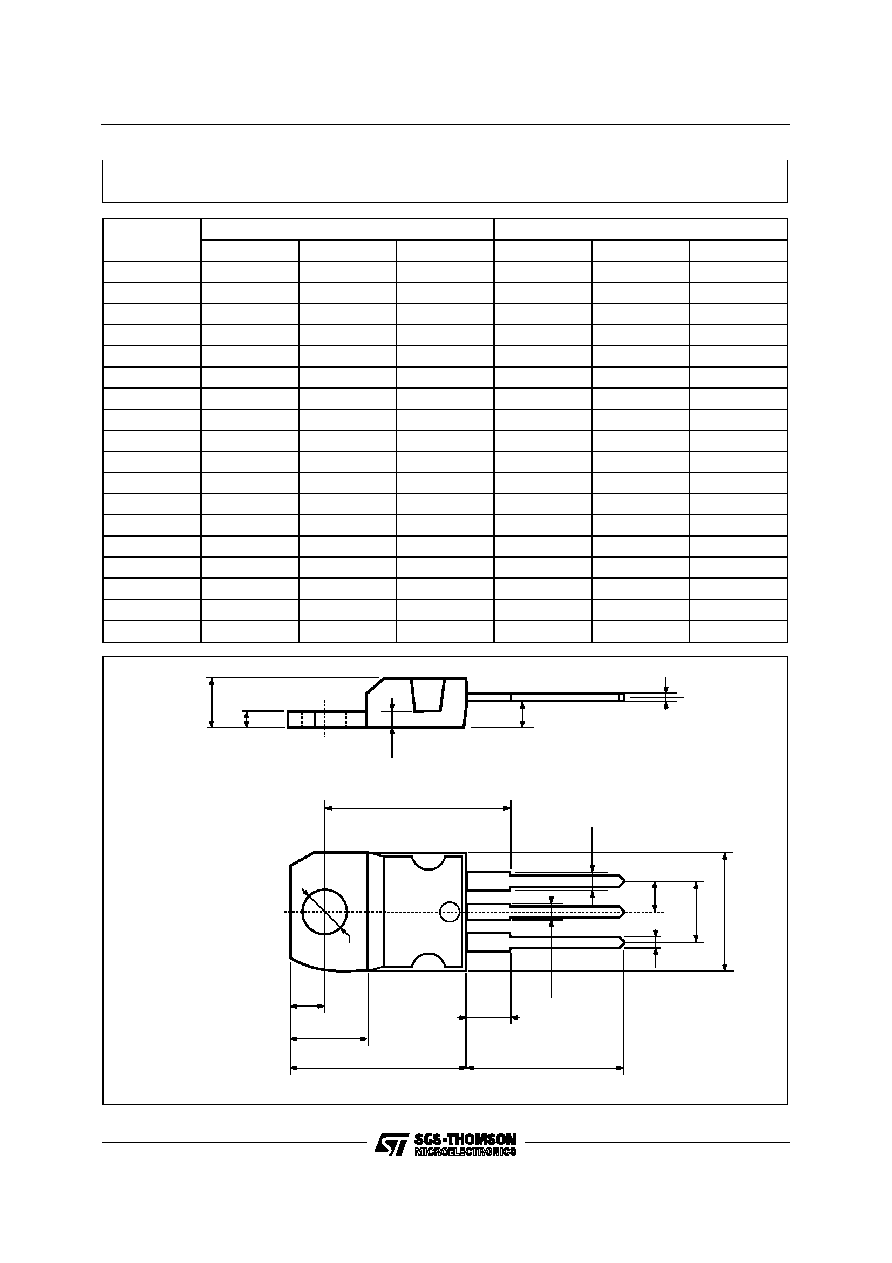

DIM.

mm

inch

MIN.

TYP.

MAX.

MIN.

TYP.

MAX.

A

4.40

4.60

0.173

0.181

C

1.23

1.32

0.048

0.051

D

2.40

2.72

0.094

0.107

D1

1.27

0.050

E

0.49

0.70

0.019

0.027

F

0.61

0.88

0.024

0.034

F1

1.14

1.70

0.044

0.067

F2

1.14

1.70

0.044

0.067

G

4.95

5.15

0.194

0.203

G1

2.4

2.7

0.094

0.106

H2

10.0

10.40

0.393

0.409

L2

16.4

0.645

L4

13.0

14.0

0.511

0.551

L5

2.65

2.95

0.104

0.116

L6

15.25

15.75

0.600

0.620

L7

6.2

6.6

0.244

0.260

L9

3.5

3.93

0.137

0.154

DIA.

3.75

3.85

0.147

0.151

L6

A

C

D

E

D1

F

G

L7

L2

Dia.

F1

L5

L4

H2

L9

F2

G1

TO-220 MECHANICAL DATA

P011C

STP40N03L-20

6/7

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsability for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. No

license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned

in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied.

SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express

written approval of SGS-THOMSON Microelectonics.

©

1995 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands -

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A

. . .

STP40N03L-20

7/7