| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: STPCI01 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

STPC

Æ

INDUSTRIAL

PC Compatible Embedded Microprocessor

1/69

11/2/02

Issue 2.4

ISA

I/F

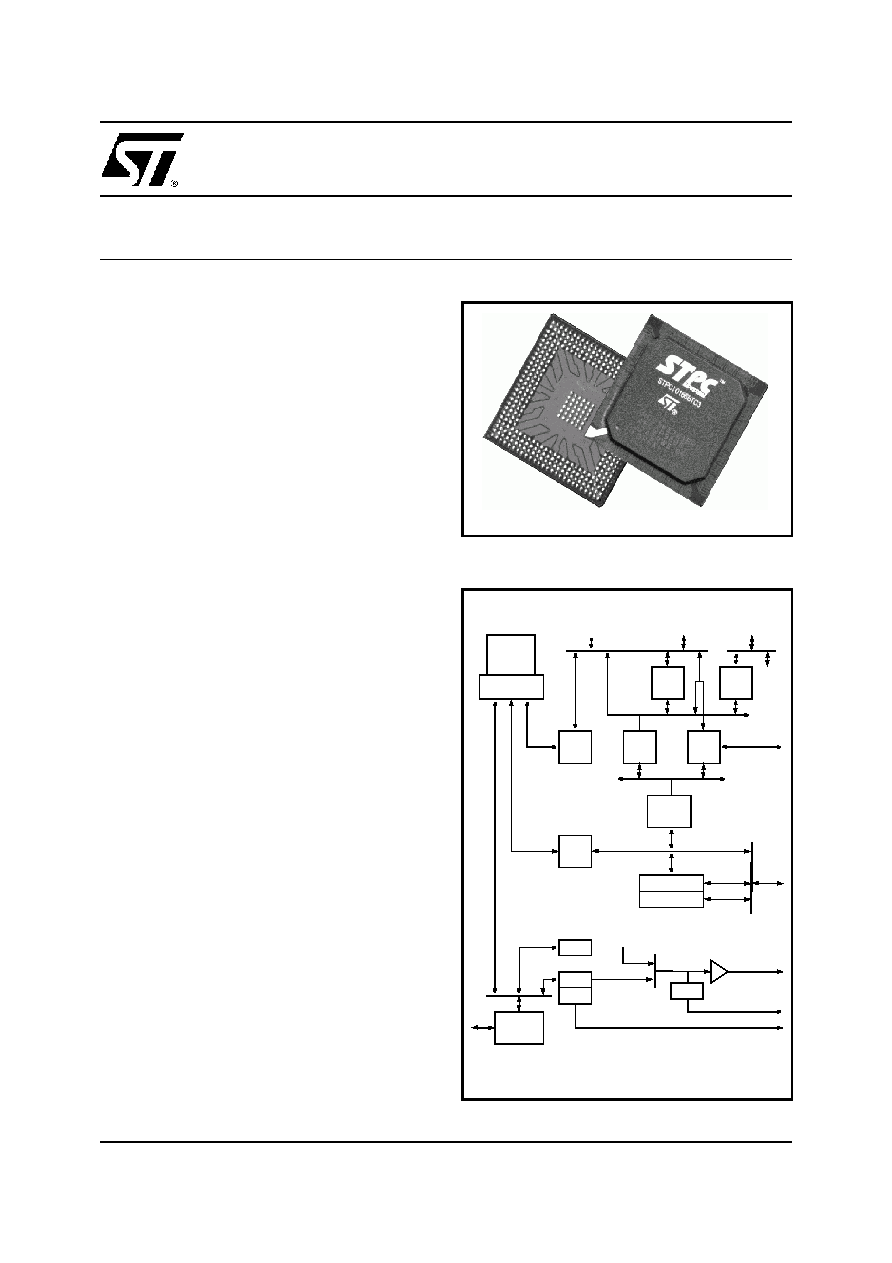

Figure 1. Logic Diagram

s

POWERFUL X86 PROCESSOR

s

64-BIT BUS ARCHITECTURE

s

64-BIT 66MHz DRAM CONTROLLER

s

SVGA GRAPHICS CONTROLLER

s

135MHz RAMDAC

s

UMA ARCHITECTURE

s

TFT DISPLAY CONTROLLER

s

PCI MASTER / SLAVE / ARBITER

s

LOCAL BUS INTERFACE

s

ISA (MASTER/SLAVE) INTERFACE

-INCLUDING THE IPC

s

PC-CARD INTERFACE

- PCMCIA

- CARDBUS

s

I/O FEATURES

- PC/AT+ KEYBOARD CONTROLLER

- PS/2 MOUSE CONTROLLER

- 2 SERIAL PORTS

- 1 PARALLEL PORT

s

IPC

- DMA CONTROLLER

- INTERRUPT CONTROLLER

- TIMER / COUNTERS

s

POWER MANAGEMENT

STPC INDUSTRIAL OVERVIEW

The STPC Industrial integrates a fully static x86

processor, fully compatible with standard fifth gen-

eration x86 processors, and combines it with pow-

erful chipset, graphics, TFT, PC-Card, Local Bus,

keyboard, mouse, serials and parallel interfaces to

provide a single Industrial oriented PC compatible

subsystem on a single device. The performance of

the device is comparable with the performance of

a typical P5 generation system.

The device is packaged in a 388 Plastic Ball Grid

Array (PBGA).

TFT

ext

x86

Core

Host I/F

Serial2

// Port

Serial1

Kbd

Mouse

DRAM

I/F

VGA

GE

PCI

m/s

Local

Bus I/F

PCMCIA

CARDBUS

PCI BUS

IPC

82C206

PCI

CONTROLLER

ISA BUS

CRTC

HW Cursor

Monitor

TFT Output

SYNC Output

TFT I/F

PBGA388

STPC INDUSTRIAL

2/69

Issue 2.4 - February 11, 2002

s

X86 Processor core

s

Fully static 32-bit 5-stage pipeline, x86

processor fully PC compatible.

s

Access up to 4GB of external memory.

s

8Kbyte unified instruction and data cache

with write back capability.

s

Parallel processing integral floating point unit,

with automatic power down.

s

Clock core speeds up to 100 MHz.

s

Fully static design for dynamic clock control.

s

Low power and system management modes.

s

Optimized design for 3.3V operation.

s

DRAM Controller

s

Integrated system memory and graphic frame

memory.

s

Supports up to 128-MByte system memory in

4 banks and down to as little as 2Mbytes.

s

Supports 4-MByte, 8-MByte, 16-MByte, and

32-MByte single-sided and double-sided

DRAM SIMMs.

s

Four quad-word write buffers for CPU to

DRAM and PCI to DRAM cycles.

s

Four quad-word read prefetch buffers for PCI

masters.

s

Supports Fast Page Mode & EDO DRAMs.

s

Programmable timing for DRAM parameters

including CAS pulse width, CAS pre-charge

time, and RAS to CAS delay.

s

60, 70, 80 & 100ns DRAM speeds.

s

Memory hole between 1 MByte & 8 MByte

supported for PCI/ISA busses.

s

Hidden refresh.

To check if your memory device is supported by

the STPC, please refer to

Table 6-24

in the

Programming Manual.

s

Graphics Controller

s

64-bit windows accelerator.

s

Complete backward compatibility to VGA and

SVGA standards.

s

Hardware acceleration for text (generalized

bit map expansion), bitblts, transparent blts

and fills.

s

Up to 64 x 64 bit graphics hardware cursor.

s

Up to 4MB long linear frame buffer.

s

8, 16, 24 and 32 bit pixels.

s

Drivers for Windows and other operating

systems.

s

CRT Controller

s

Integrated 135MHz triple RAMDAC allowing

for 1280 x 1024 x 75Hz display.

s

Requires external frequency synthesizer and

reference sources.

s

8, 16, 24 and 32-bit pixels.

s

Interlaced or non-interlaced output.

s

TFT Interface

s

Programmable panel size up to 1024 by 1024

pixels.

s

Support for 640 x 480, 800 x 600 & 1024 x

768 active matrix TFT flat panels with 9, 12,

18-bit interface.

s

Support 1 & 2 Pixels per Clock.

s

Programmable image positionning.

s

Programmable blank space insertion in text

mode.

s

Programmable horizontal and vertical image

expansion in graphic mode.

s

A fully programmable PWM (Pulse Width

Modulator) signals to adjust the flat panel

brightness and contrast.

s

Supports PanelLink

TM

high speed serial

transmitter externally for high resolution

panel interface.

s

PCI Controller

s

Fully compliant with PCI Version 2.1

specification.

s

Integrated PCI arbitration interface. Up to 3

masters can connect directly. External PAL

allows for greater than 3 masters.

s

Translation of PCI cycles to ISA bus.

s

Translation of ISA master initiated cycle to

PCI.

s

Support for burst read/write from PCI master.

s

0.33X and 0.5X CPU clock PCI clock.

s

Local Bus interface

s

66MHz, low latency bus.

s

Asynchronous / synchronous.

s

22-bit address and 16-bit data busses.

s

2 Programmable Flash EPROM Chip Select.

s

4 Programmable I/O Chip Select.

s

Separate memory and I/O address spaces.

s

Memory prefetch (improved performances).

STPC INDUSTRIAL

Issue 2.4 - February 11, 2002

3/69

s

ISA master/slave

s

Generation of the ISA clock from either

14.318MHz oscillator clock or system clock

s

Programmable extra wait state for ISA cycles

s

Supports I/O recovery time for back to back

I/O cycles.

s

Fast Gate A20 and Fast reset.

s

Supports the single ROM that C, D, or E.

blocks shares with F block BIOS ROM.

s

Supports flash ROM.

s

Supports ISA hidden refresh.

s

Buffered DMA & ISA master cycles to reduce

bandwidth utilization of the PCI and Host bus.

NSP compliant.

s

PC-Card interface

s

Support one PCMCIA 2.0 / JEIDA 4.1 68-pin

standard PC Card Socket.

s

Power Management support.

s

Support PCMCIA/ATA specifications.

s

Support I/O PC Card with pulse-mode

interrupts.

s

Provides an ExCA

TM

implementation to

PCMCIA 2.0 / JEIDA 4.1 standards.

s

DMA support.

s

Keyboard interface

s

Fully PC/AT& compatible

s

Mouse interface

s

Fully PS/2 compatible

s

Serial interface

s

16550A compatible

s

Programmable word length, stop bits, parity.

s

16-bit programmable baud rate generator.

s

Interrupt generator.

s

Loop-back mode.

s

8-bit scratch register.

s

Two 16-bit FIFOs.

s

Two DMA handshake lines.

s

Parallel port

s

Standard Centronics mode supported.

s

Nibble mode supported.

s

Integrated Peripheral Controller

s

Two 8237/AT compatible 7-channel DMA

controllers.

s

Two 8259/AT compatible interrupt Controller.

16 interrupt inputs - ISA and PCI.

s

Three 8254 compatible Timer/Counters.

s

Co-processor error support logic.

s

Power Management

s

Four power saving modes: On, Doze,

Standby, Suspend.

s

Programmable system activity detector

s

Supports SMM.

s

Supports IO trap & restart.

s

Independent peripheral time-out timer to

monitor hard disk, serial & parallel ports.

s

Supports APM

s

Supports RTC, interrupt and DMA wake ups

ExCA is a trademark of PCMCIA / JEIDA.

PanelLink is a trademark of SiliconImage, Inc

STPC INDUSTRIAL

4/69

Issue 2.4 - February 11, 2002

GENERAL DESCRIPTION

Issue 2.4 - February 11, 2002

5/69

1 GENERAL DESCRIPTION

At the heart of the STPC Industrial is an

advanced 64-bit processor block, dubbed the

5ST86. The 5ST86 includes a powerful x86

processor core along with a 64-bit DRAM

controller, advanced 64-bit accelerated graphics

and video controller, a high speed PCI local-bus

controller and Industry standard PC chip set

functions (Interrupt controller, DMA Controller,

Interval timer and ISA bus).

The STPC Industrial has in addition to the 5ST86

a TFT output, a Local Bus interface, PC Card and

super I/O features.

The STPC Industrial makes use of a tightly

coupled Unified Memory Architecture (UMA),

where the same memory array is used for CPU

main memory and graphics frame-buffer. This

means a reduction in total system memory for

system performances that are equal to that of a

comparable frame buffer and system memory

based system, and generally much better, due to

the higher memory bandwidth allowed by

attaching the graphics engine directly to the 64-bit

processor host interface running at the speed of

the processor bus rather than the traditional PCI

bus.

The 64-bit wide memory array provides the

system with 320MB/s peak bandwidth, double

that of an equivalent system using 32 bits. This

allows for higher resolution screens and greater

color depth. The processor bus runs at 66Mhz

further increasing "standard" bandwidth by at

least a factor of two.

The `standard' PC chipset functions (DMA,

interrupt controller, timers, power management

logic) are integrated together with the x86

processor core; additional functions such as

communication ports are accessed by the STPC

Industrial via an internal ISA bus.

The PCI bus is the main data communication link

to the STPC Industrial chip. The STPC Industrial

translates appropriate host bus I/O and Memory

cycles onto the PCI bus. It also supports the

generation of Configuration cycles on the PCI

bus. The STPC Industrial, as a PCI bus agent

(host bridge class), fully complies with PCI

specification 2.1. The chip-set also implements

the PCI mandatory header registers in Type 0 PCI

configuration space for easy porting of PCI aware

system BIOS. The device contains a PCI

arbitration function for three external PCI devices.

Graphics functions are controlled through the on-

chip SVGA controller and the monitor display is

produced through the 2D graphics display engine.

This Graphics Engine is tuned to work with the

host CPU to provide a balanced graphics system

with a low silicon area cost. It performs limited

graphics drawing operations which include

hardware acceleration of text, bitblts, transparent

blts and fills. The results of these operations

change the contents of the on-screen or off-

screen frame buffer areas of DRAM memory. The

frame buffer can occupy a space up to 4 Mbytes

anywhere in the physical main memory.

The maximum graphics resolution supported is

1280x1024 in 65536 colours at 75Hz refresh rate

and is VGA and SVGA compatible. Horizontal

timing fields are VGA compatible while the vertical

fields are extended by one bit to accommodate

above display resolution.

To generate the TFT output, the STPC Industrial

extracts the digital video stream before the

RAMDAC and reformats it to the TFT format. The

height and width of the flat panel are

programmable through configuration registers up

to a size of 1024 by 1024.

By default, lower resolution images cover only a

part of the larger TFT panel. The STPC Industrial

allows to expand the image vertically and

horizontally in text mode by inserting

programmable blank pixels. It allows expantion of

the image vertically and horizontally in graphics

mode by replicating pixels. The replication of J

times every K pixel is independently

programmable in the vertical and horizontal

directions.

PanelLink

TM

is a proprietary interconnect

protocol defined by Silicon Image, Inc. It consists

of a transmitter that takes parallel video/graphics

data from the host LCD graphics controller and

transmits it serially at high speed to the receiver

which controls the TFT panel. The TFT interface

is designed to support the connection of this

control signal to the PanelLink

TM

transmitter.

The STPC Industrial CARDBUS / PCMCIA

controller has been specifically designed to

provide the interface with PC-Cards which contain

additional memory or I/O and provides an

ExCA

TM

implementation to PCMCIA 2.0 / JEIDA

4.1 standards.

The power management control facilities include

socket power control, insertion/removal capability,

power saving with Windows inactivity, NCS

controlled Chip Power Down, together with further

controls for 3.3v suspend with Modem Ring

Resume Detection.