| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: STV9381 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

September 2003

1/8

Version 3.0

STV9381

CLASS-D VERTICAL DEFLECTION AMPLIFIER FOR TV AND

MONITOR APPLICATION

FEATURES

s

HIGH EFFICIENCY POWER AMPLIFIER

s

NO HEATSINK

s

SPLIT SUPPLY

s

INTERNAL FLYBACK GENERATOR

s

OUTPUT CURRENT UP TO 3 APP

s

SUITABLE FOR DC COUPLING

APPLICATION

s

FEW EXTERNAL COMPONENTS

s

PROTECTION AGAINST LOW Vcc

DESCRIPTION

Designed for monitors and TVs, the STV9381 is a

class-D vertical deflection booster assembled in

PDIP20 Package.

It operates with supplies up to +/- 18V, provides

up to 3 App output current to drive the yoke. The

internal flyback generator avoids the need for an

extra power supply.

PIN CONNECTION

PDIP20

(14+3+3)

ORDER CODE:

STV9381

20

19

18

17

16

15

14

13

12

11

1

2

3

4

5

6

7

8

9

10

-V

CC

-V

CC

-V

CC

-V

CC

-V

CC

-V

CC

-V

CC

POW

+ V

CC

POW

+V

CC

EAout

IN+

IN-

SGND

OUT

CFLY +

CFLY -

BOOT

VREG

FEEDCAP

FREQ

1

STV9381

2/8

1

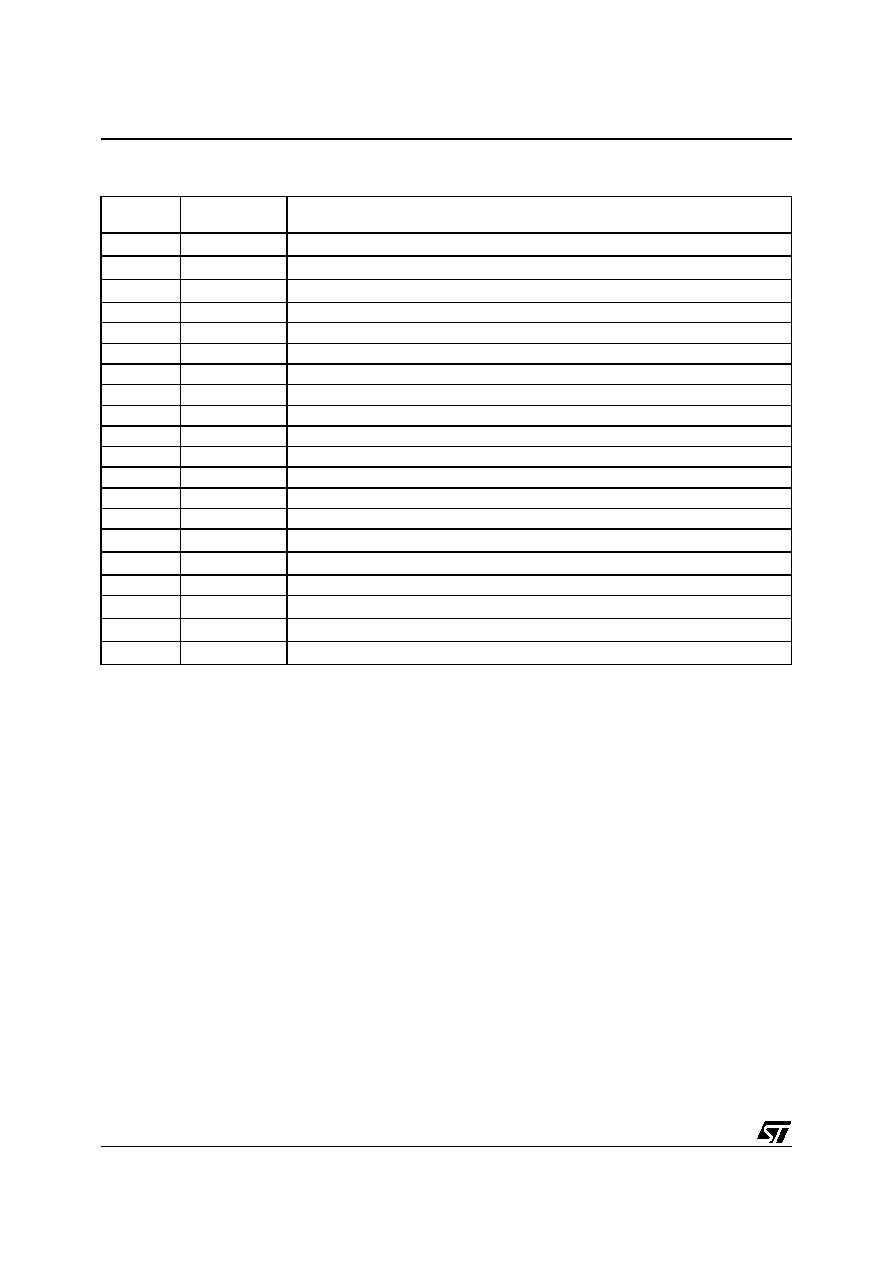

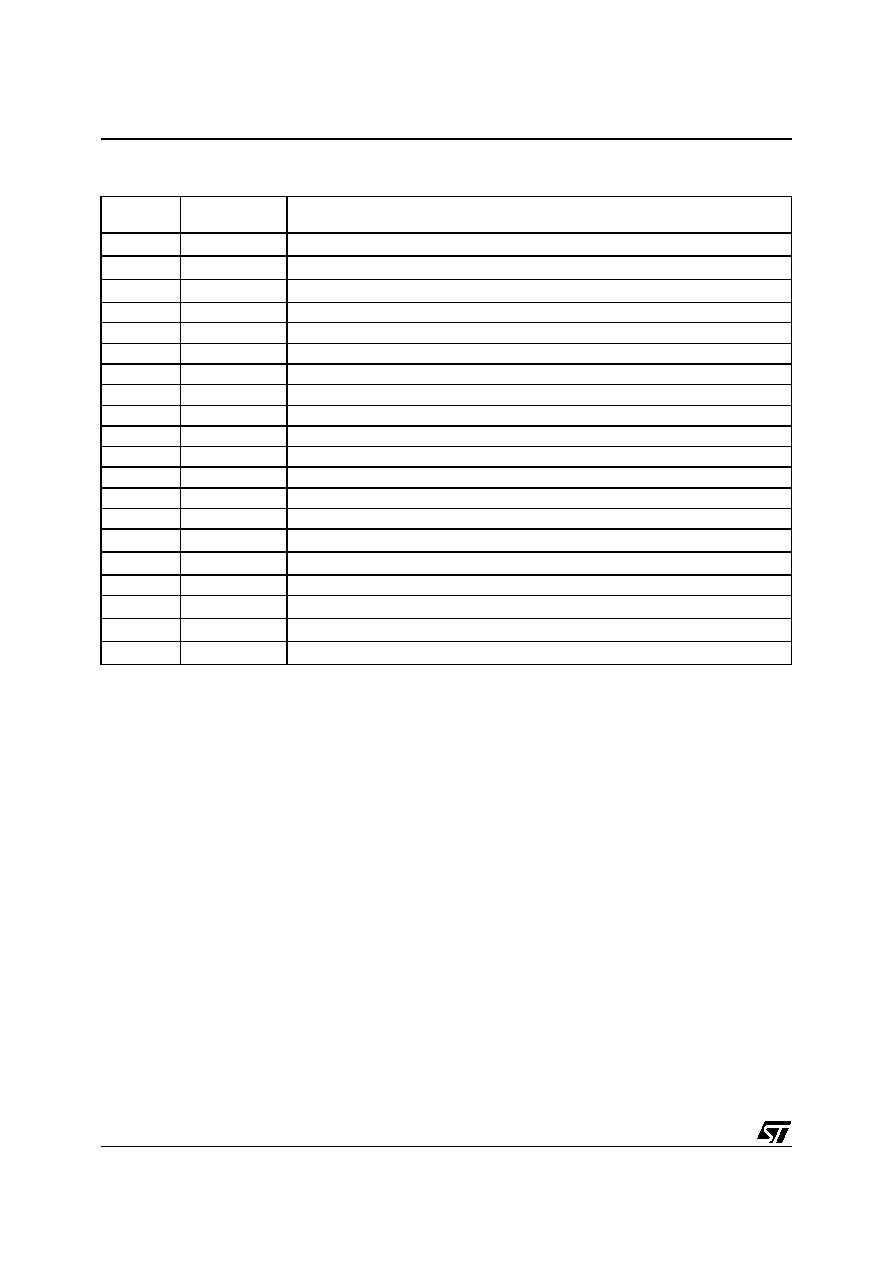

PIN FUNCTIONS

2

FUNCTIONAL DESCRIPTION

The STV9381 is a vertical deflection circuit operating in class D. The class D is a modulation method

where the output transistors work in switching mode at high frequency. The output signal is restored by fil-

tering the output square wave with an external LC filter. The major interest of this IC is the low power dis-

sipation comparatively to traditional amplifiers operating in class AB, eliminating the need of an heatsink.

Except for the output stage which uses the class D modulation, the circuit operation is similar to

the one

of a traditional linear vertical amplifier.

A reference signal (sawtooth) has to be applied to the circuit which can accept a differential or single end-

ed signal. This sawtooth is amplified and applied as a current to the deflection yoke. This current is meas-

ured by means of a low value resistor. The resulting voltage is used as a feed-back signal to guarantee the

conformity of the yoke current with the reference input signal.

The overvoltage necessary for a fast retrace is obtained with a chemical capacitor charged

at the power

supply voltage of the circuit. At the flyback moment this capacitor is connected in series with the output

stage power supply. This method, used for several years with the linear vertical boosters and called "in-

ternal flyback" or "flyback generator", avoids the need of an additional power supply, while reducing the

flyback duration.

The circuit uses a BCD process that combines Bipolar, CMOS and DMOS devices. DMOS transistors are

used in the output stage due to the absence of second breakdown.

Pin

Number

Name

Function

1

-V

CC

Negative supply

2

-V

CC

Negative supply

3

-V

CC

Negative supply

4

OUT

PWM Output

5

CFLY+

Flyback capacitor

6

CFLY-

Flyback capacitor

7

BOOT

Bootstrap capacitor

8

VREG

Internal voltage regulator

9

FEEDCAP

Feed-back integrating capacitor

10

FREQ

Frequency setting resistor

11

SGND

Signal Ground

12

IN-

Error amplifier inverting input

13

IN+

Error amplifier non-inverting input

14

EA out

Error amplifier output

15

+V

CC

Positive supply

16

+V

CC

POW

Positive Power supply

17

-VccPOW

Negative Power supply

18

-V

CC

Negative supply

19

-V

CC

Negative supply

20

-V

CC

Negative supply

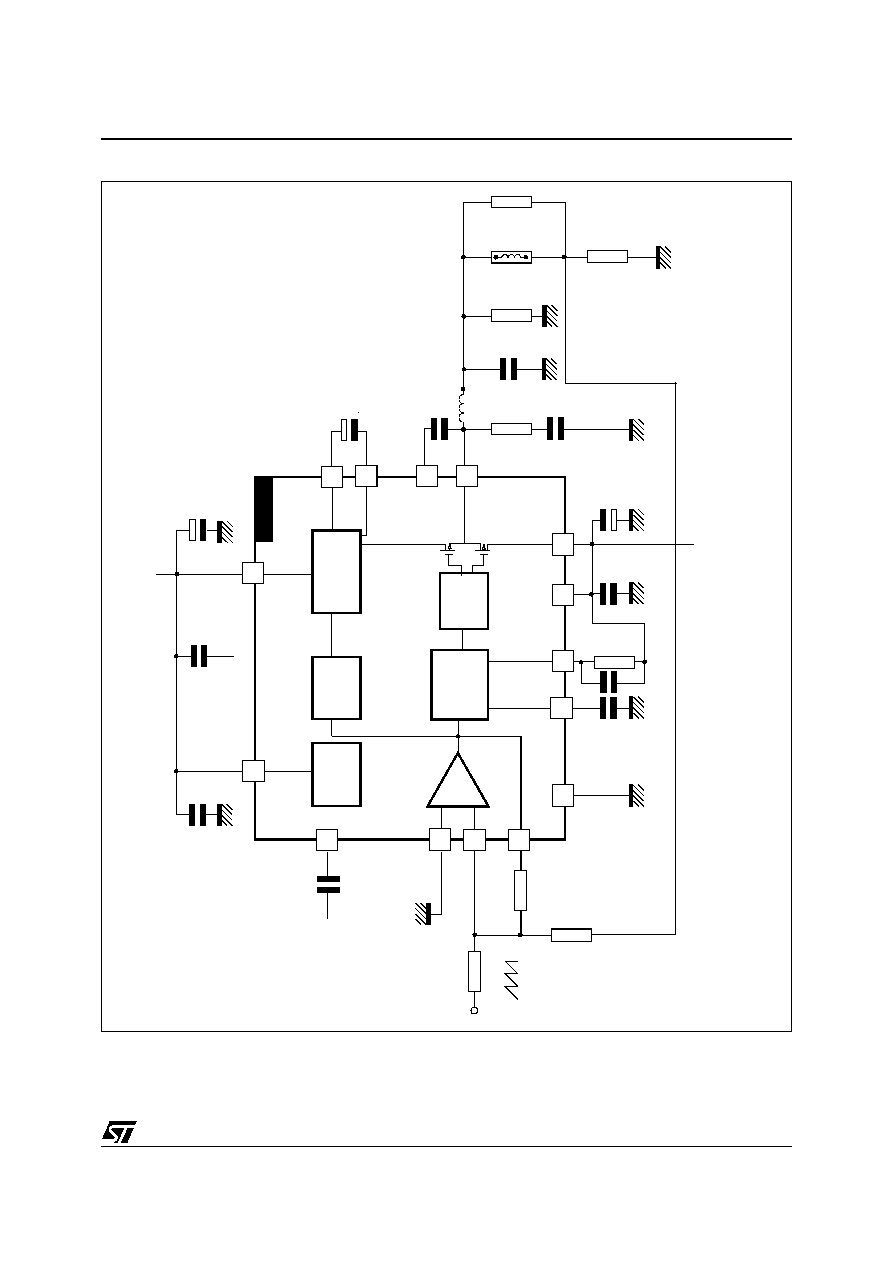

2

ST

V9381

3/

8

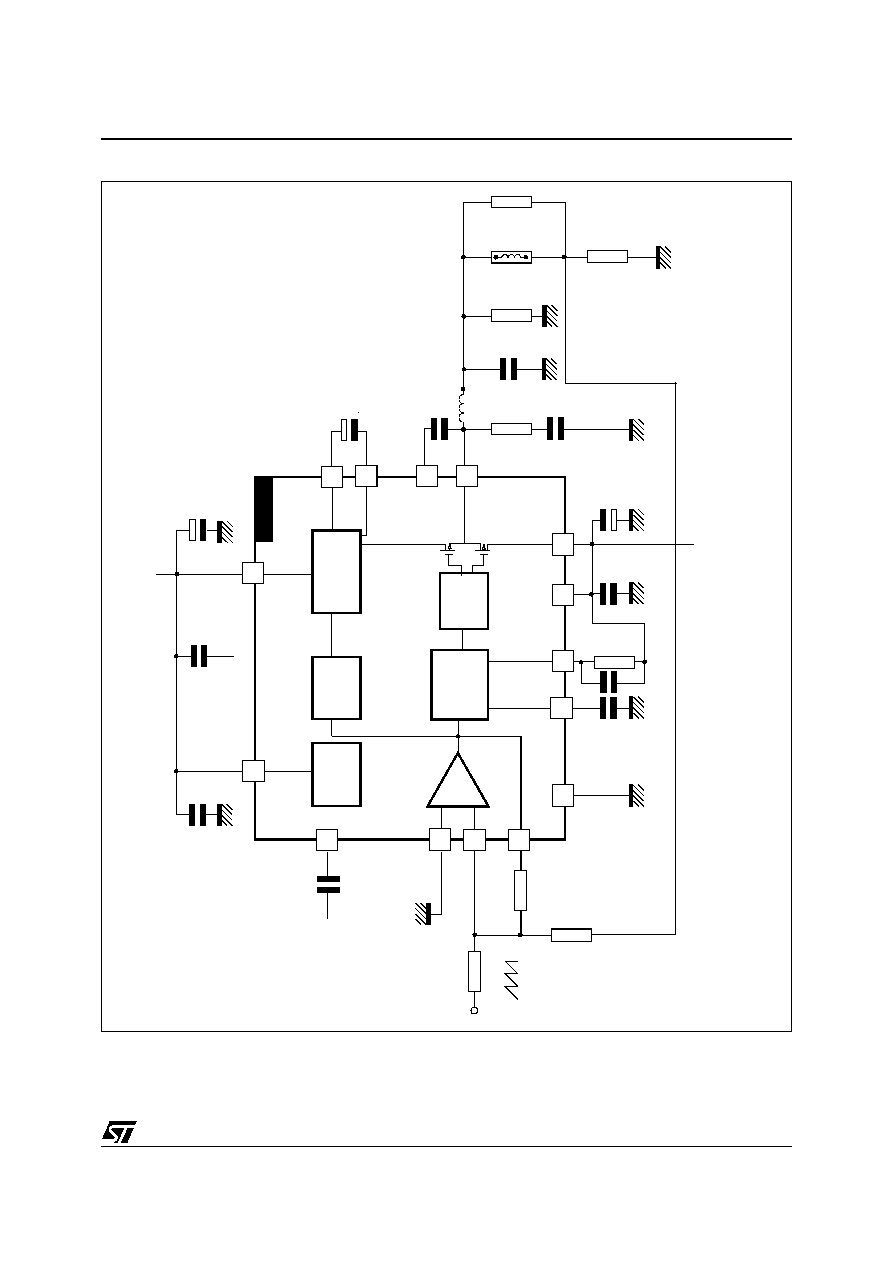

F

i

g

u

re

1.

T

e

s

t

an

d

ap

p

l

i

c

at

i

o

n

ci

r

c

u

i

t

Flyback

Flyback

Output

Modulator

+

_

drive

generator

detection

+VCC

+VCC power

CFLYBACK

CFLY+

100nF

VREG

IN+

IN -

1k

10k

EA out

-VCC power

-VCC

-VCC

BOOT

Cboot

470nF

10k

4.7nF

FREQ

FEEDCAP

SGND

Pins 1,2,3,18,19,20

OUT

0.5

Deflect.

Yoke*

CFLY-

+VCC

1mH

Input signal

1k

220nF

-VCC

100nF

100nF

1000

µ

F

1000

µ

F

STV9380

100

µ

F

14

11

9

17

560pF

150

200

15

16

8

STV9381

5

6

7

4

13

12

150

10

Vref

-VCC

470pF

* Deflection yoke characteristics: R = 5.5

, L = 7mH

100nF

Sense

resistor

f

vert

= 50Hz

2

STV9381

4/8

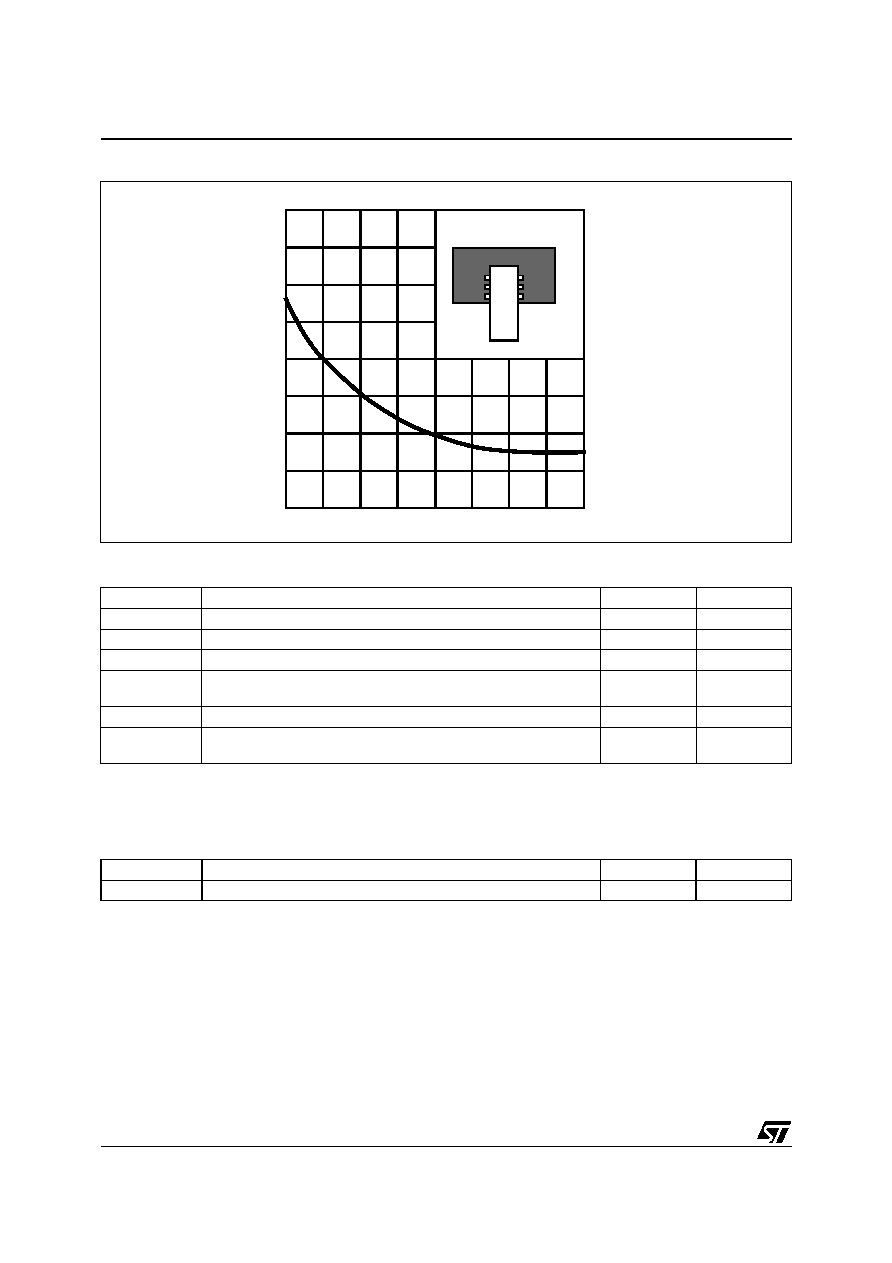

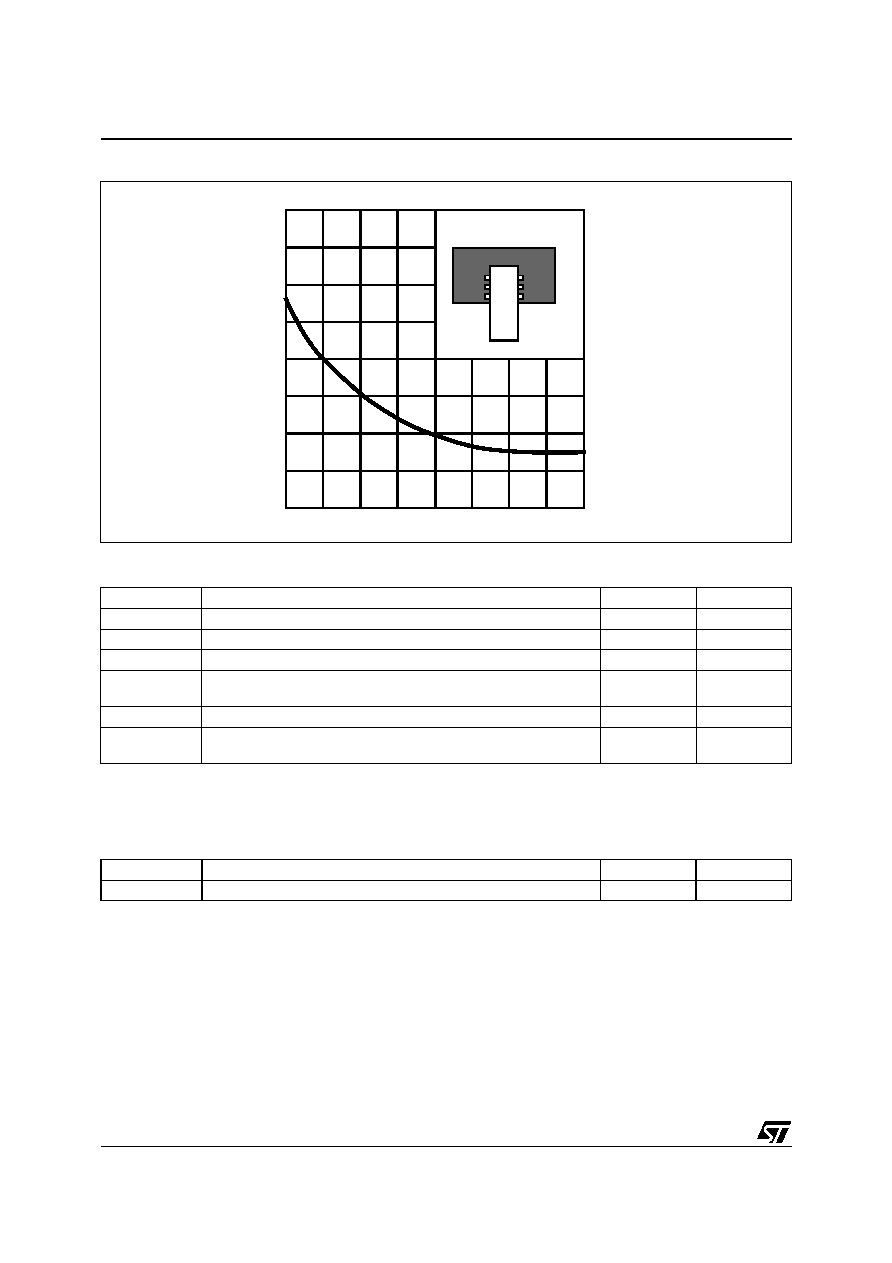

Figure 2. Rth with "on board" Square Heatsink vs. copper area

3

ABSOLUTE MAXIMUM RATINGS

Note: 1

During the flyback with Vcc=±18V, the maximum output voltage (pin 4) is close to 72V, with respect to -Vcc

(pins 1, 2, 3, 18, 19, 20).

4

THERMAL DATA

Pins 1, 2, 3, 18, 19, 20 are internally connected together and participate to heat evacuation.

Symbol

Parameter

Value

Unit

VCC

DC Supply Voltage

±20

V

T

stg

, T

j

Storage and Junction Temperature

-40 to +150

∞C

T

op

Operating Temperature Range

0 to +70

∞C

VESD

ESD Susceptibility - Human Body Model (100 pF discharge through

1.5 k

)

±2

kV

Iout

Output current

±2

A

Vout

Maximum output voltage (pin 4) with respect to -Vcc

(pins 1, 2, 3, 18, 19, 20) and during flyback (see

Note 1

)

80

V

Symbol

Parameter

Value

Unit

R

th j-amb

Thermal resistance Junction to ambient

70

∞C/W

0

4

8

12

Area(cm

2

)

40

50

60

70

R

thj-a

(∞C/W)

COPPER AREA 35

µ

m

THICKNESS

PC BOARD

2

STV9381

5/8

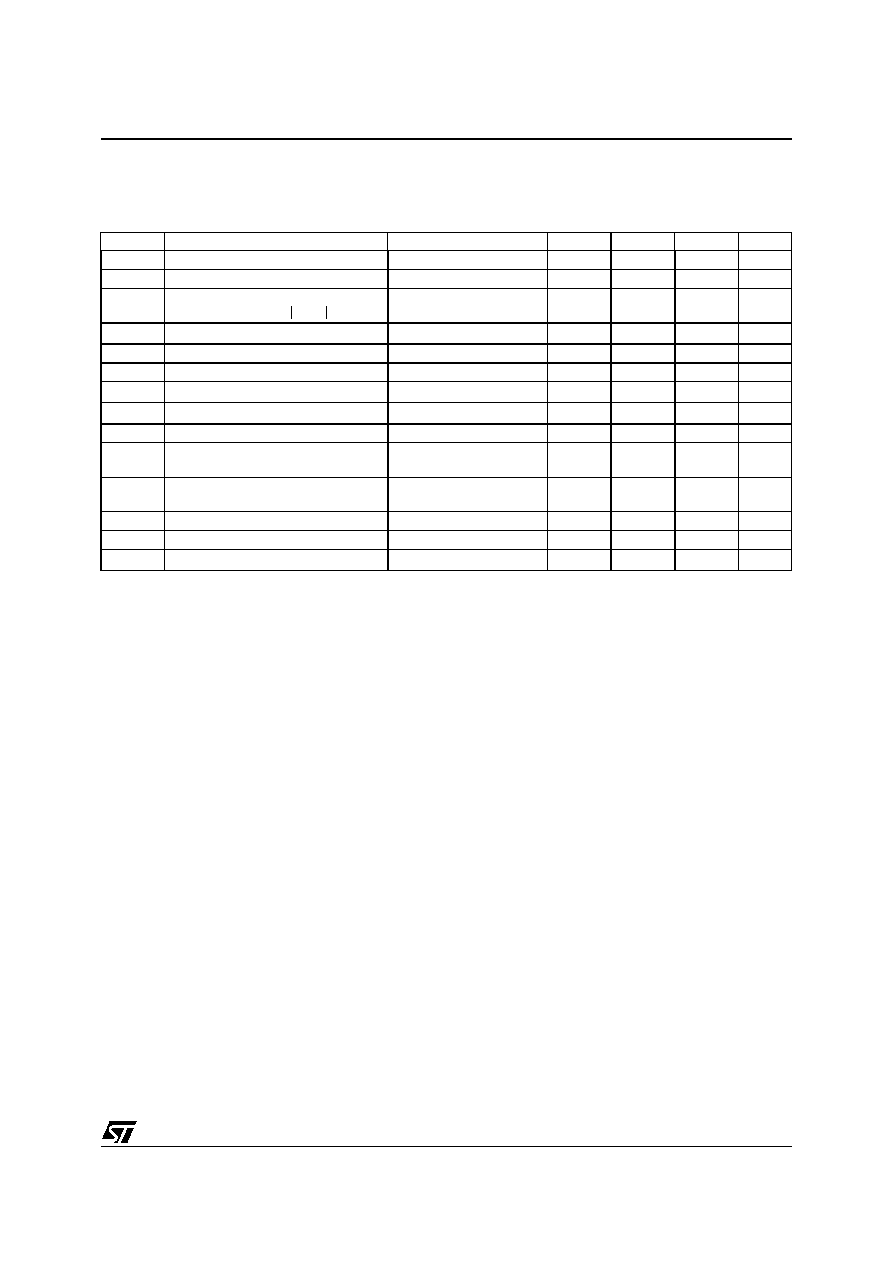

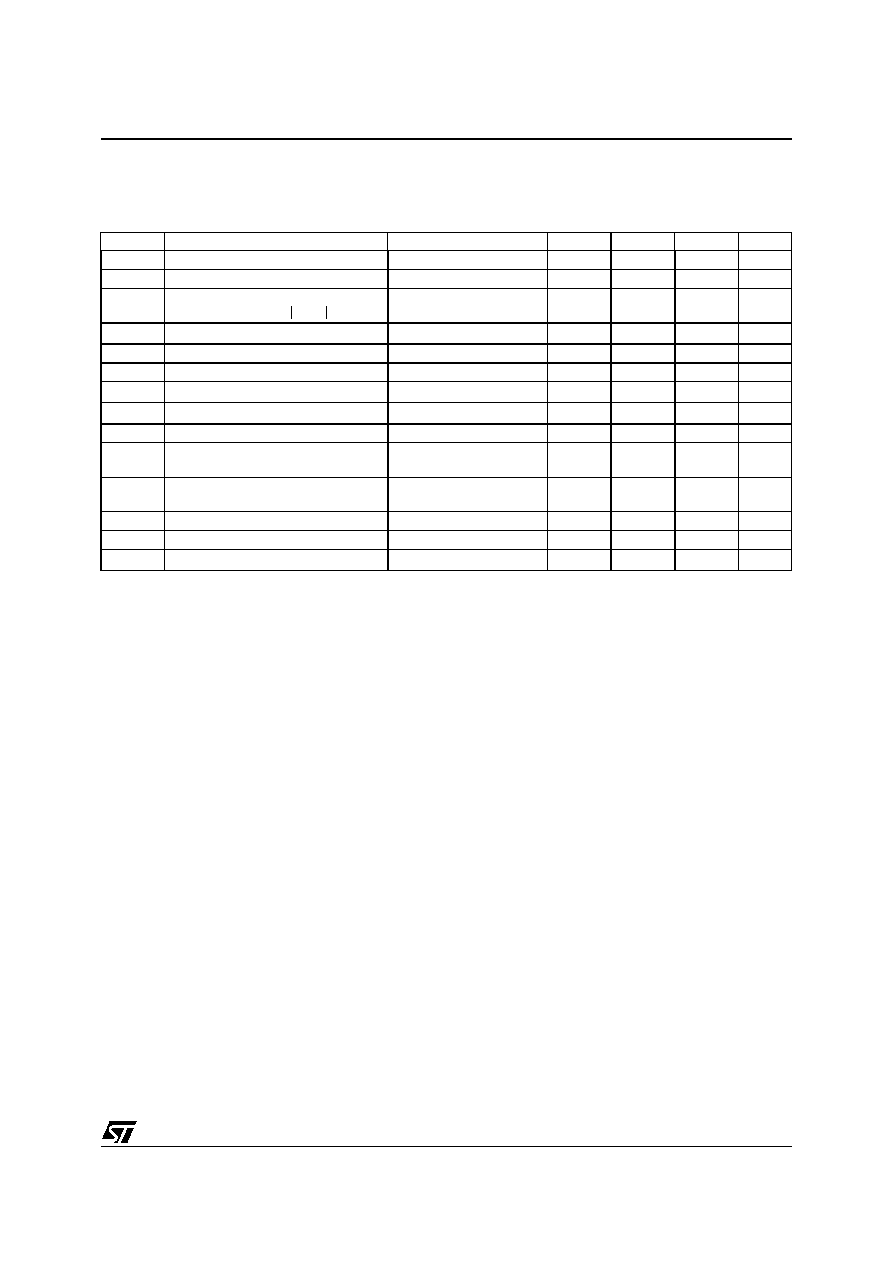

5

ELECTRICAL CHARACTERISTICS

(refer to

Figure 1 on page 3

)

Tamb = 25∞C unless otherwise specified, Vcc = ±12V, f

vert

=50Hz

Note: 2

Input voltage = 0, measured after the filter (e.g. accross the 470 nF filter capacitor)

Note: 3

Supply rejection of the positive or negative power supply. Vcc ripple

=1Vpp, f=100Hz, measured on the sense

resistor.

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Units

+Vcc

Positive supply range

+10

+18

V

-Vcc

Negative supply range

-18

-10

V

Vcc

Maximum recommended difference

between +Vcc and

±4

V

Vcc

start

Low Vcc detection

±6.5

V

Iq

Quiescent supply current

Input voltage = 0

14

mA

Iy

Maximum vertical yoke current

±1.5

A

I

13

, I

12

Amplifier Input bias current

-0.1

µ

A

V

OS

Output Offset voltage

Note 2

-50

+50

mV

SVR

Supply voltage rejection

Note 3

82

dB

Fly

thr

Flyback detection threshold

(positive slope)

V(14)

1.5

V

Fly

thf

Flyback detection threshold

(negative slope)

V(14)

0.5

V

Fsw

Switching frequency

R

freq

= 10k

120

140

160

kHz

Fsw - op

Switching frequency operative range

100

200

kHz

R

freq

Frequency controller resistor range

Pin 10

7

10

14

k

Vcc

≠

2