STV9410

CRT AND LCD SEMI-GRAPHIC DISPLAY PROCESSOR

April 1996

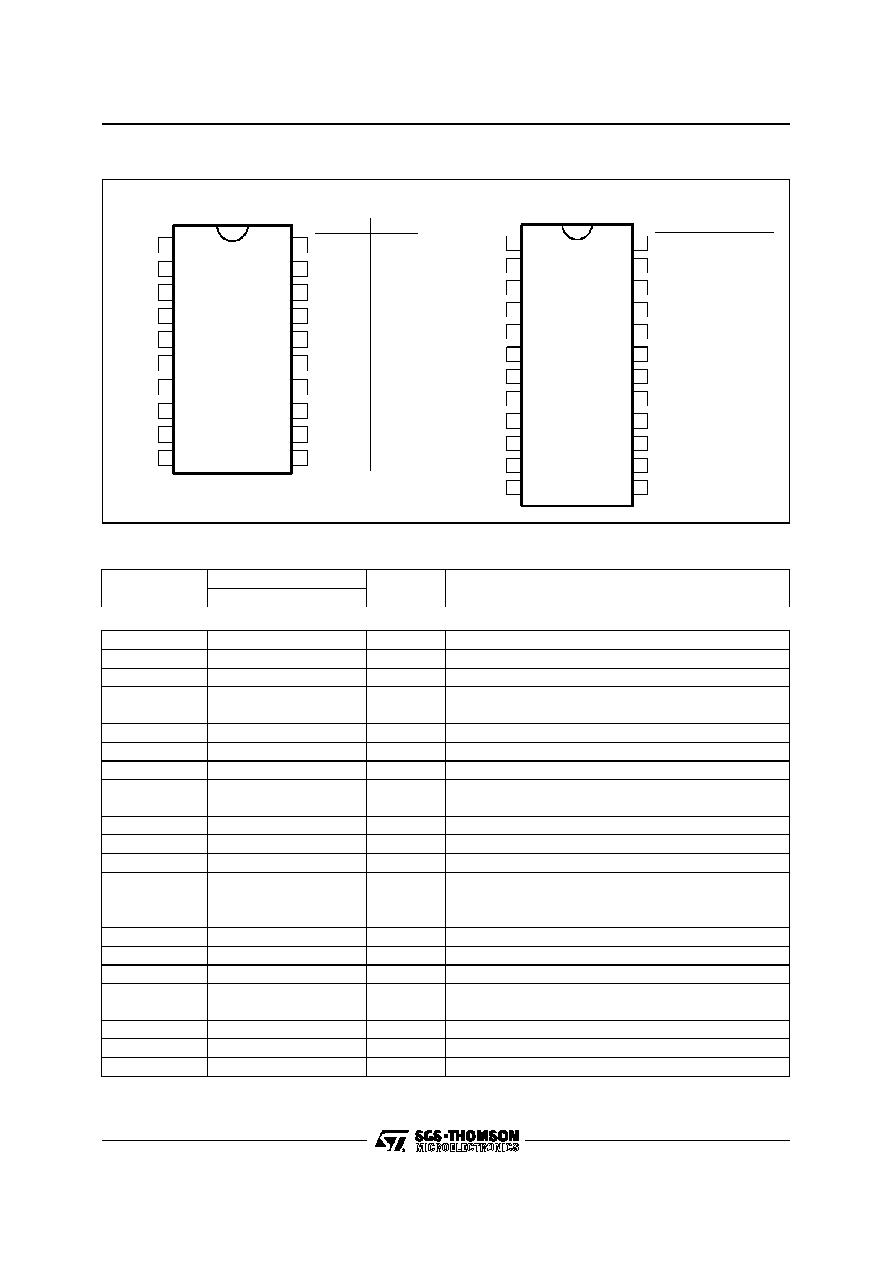

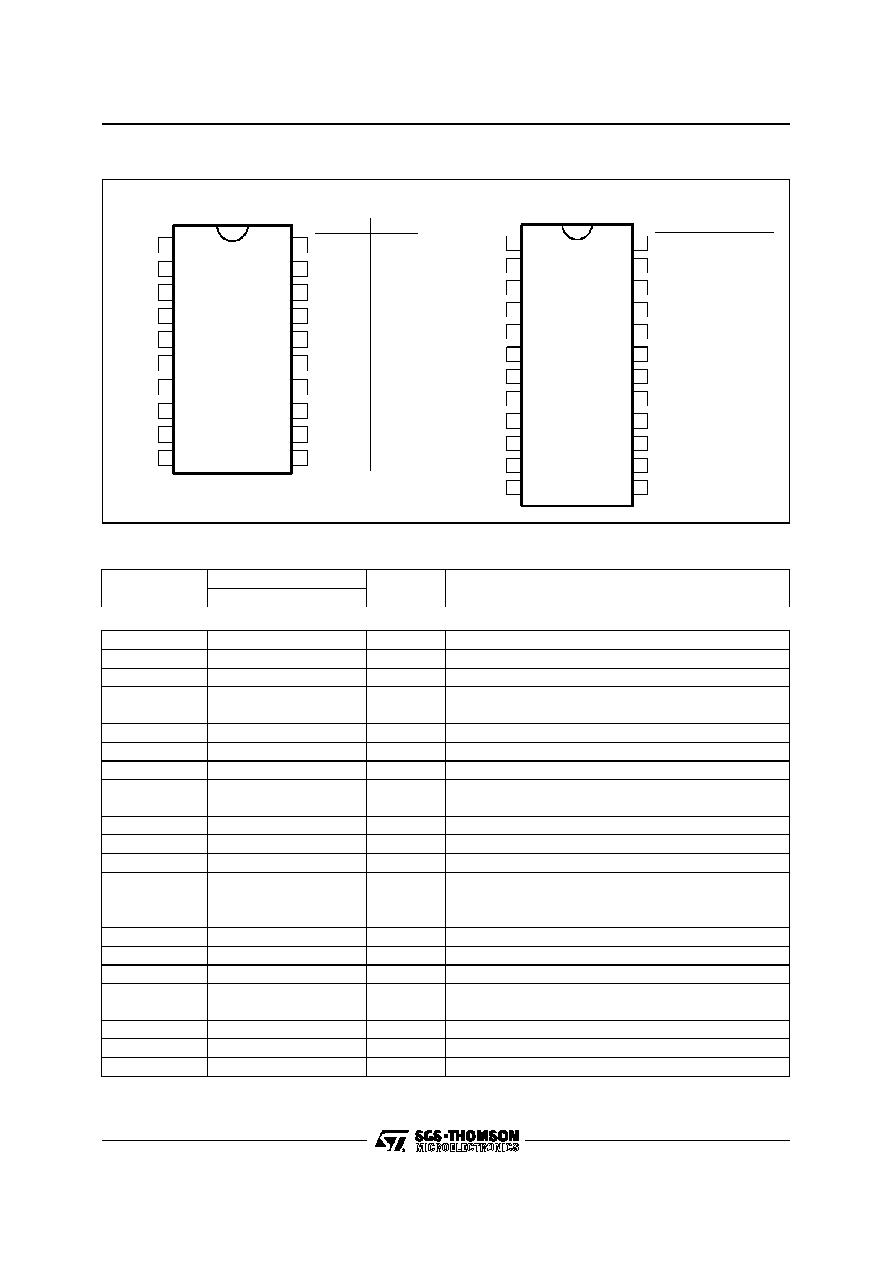

DIP20

(Plastic Package)

ORDER CODE : STV9410P

.

CMOS SINGLE CHIP CRT AND LCD DIS-

PLAY PROCESSOR

.

BUILT IN 6 KBYTE RAM

.

25 ROWS OR MORE OF 40 CHARACTERS

.

CRT MODE :

- ANALOG Y LUMINANCE OUTPUT OF 4-

BIT DAC

- R,G,B DIGITAL COLOR OUTPUTS

- FAST BLANKING OUTPUT FOR VIDEO

SWITCH COMMAND

- SYNCHRONIZATION INPUT AND OUTPUT

- MASTER AND SLAVE SYNCHRONIZATION

MODES

.

LCD MODE :

- 8 GREY LEVELS

- 4 BIT DATA WITH CLOCK OUTPUT

- 3 OUTPUTS FOR LCD DRIVERS SYN-

CHRONIZATION

- CONTRAST ANALOG COMMAND WITH

DAC OUTPUT

.

128

ALPHANUMERIC CODES AND 128

SEMI-GRAPHIC CODES IN INTERNAL ROM

.

PARALLEL ATTRIBUTES THANKS TO 2

BYTE CODES

.

128

ALPHANUMERIC

AND

96

SEMI-

GRAPHIC

USER

DEFINABLE

CODES

DOWN-LOADABLE IN RAM

.

3-WIRE ASYNCHRONOUS SERIAL MCU IN-

TERFACE

.

SQUARE WAVE OR LOGICAL PROGRAM-

MABLE OUTPUT

.

FULLY PROGRAMMABLE WITH 7 16-BIT

CONTROL REGISTERS

.

24-PIN SO OR 20-PIN DIP PACKAGES

DESCRIPTION

STV9410 controller is a VLSI CMOS Display Proc-

essor. Time base generator, display control & re-

fresh logic, interface for transparent MCU memory

access, ROM character sets, memory to store dis-

play data & page codes and control registers are

gathered on a single chip component packed in a

short 20 DIP or SO plastic package.

SO24

(Plastic Micropackage)

ORDER CODE : STV9410D

Using its 3-wire serial interface, working in both

read and write mode to program 7 control registers

and to access internal RAM, STV9410 is a highly

flexible processor.

The STV9410 provides the user an easy to use and

cost effective solution to display alphanumeric and

semigraphic Informationon CRT and LCD screens.

1/25

9410-01.EPS

-

9410-02.EPS

PIN CONNECTIONS

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

XTO

XTI

CKO

POR

NCS

SDA

SCK

V

REF

V

SSA

V

SS

V

DD

C

-

I

B

G

R

SYNC

V

SYNC

LOAD

FRAME

CRT

LCD

SYNC IN

CKD

Y

DF

D0

D1

D3

D2

V

EE

V

DD

DIP20

XTO

XTI

CKO

POR

NCS

SDA

SCK

V

REF

V

SSA

V

SS

V

DD

SYNC IN

C

-

I

B

G

R

SYNC

LOAD

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

24

23

22

21

11

12

RESERVED

RESERVED

RESERVED

RESERVED

V

FRAME

SYNC

CRT

LCD

CKD

Y

V

EE

D F

D0

D1

D3

D2

-

-

V

DD

SO24

PIN DESCRIPTION

Symbol

Pin n

o

I/O

Description

DIP20

SO24

CRT MODE

-

-

1

-

Reserved

XTO

1

2

O

Crystal oscillator output

XTI

2

3

I

Crystal oscillator or clock input

CKO

3

4

O

Clock output

POR

4

5

O

Programmable output port

NCS

5

6

I

Serial interface selection

SDA

6

7

I/O

Serial data input/output

SCK

7

8

I

Serial interface clock input

V

REF

8

9

I

Reset input and ref supply of Y DAC

V

SSA

9

10

S

Ref ground of Y DAC

V

SS

10

11

S

Ground

-

-

12

-

Reserved

-

-

13

-

Reserved

Y

11

14

O

Luminance output

R

12

15

O

Red output

G

13

16

O

Green output

B

14

17

O

Blue output

I

15

18

O

Fast blanking output

-

16

19

O

Reserved

C

SYNC

17

20

O

Composite synchro output

V

SYNC

18

21

O

Vertical synchro output

SYNC IN

19

22

I/O

Synchro input

V

DD

20

23

S

+5v power supply

-

-

24

-

Reserved

9410-01.TBL

STV9410

2/25

PIN DESCRIPTION (continued)

Symbol

Pin n

o

I/O

Description

DIP20

SO24

LCD MODE

-

-

1

-

Reserved

XTO

1

2

O

Crystal oscillator output

XTI

2

3

I

Crystal oscillator or clock input

CKO

3

4

O

Clock output

POR

4

5

O

Programmable output port

NCS

5

6

I

Serial interface selection

SDA

6

7

I/O

Serial data input/output

SCK

7

8

I

Serial interface clock input

V

REF

8

9

I

Reset input and ref supply of contrast adjustment

V

SSA

9

10

S

Ref ground of contrast adjustment

V

SS

10

11

S

Ground

-

-

12

-

Reserved

-

-

13

-

Reserved

V

EE

11

14

O

Constrast adjustment

D2

12

15

O

D2 Data output

D3

13

16

O

D3 Data output

D1

14

17

O

D1 Data output

D0

15

18

O

D0 Data output

DF

16

19

O

LCD polarity output

LOAD

17

20

O

Load output (line)

FRAME

18

21

O

Frame output

CKD

19

22

I/O

Data Clock

V

DD

20

23

S

+5v power supply

-

-

24

-

Reserved

9410-02.TBL

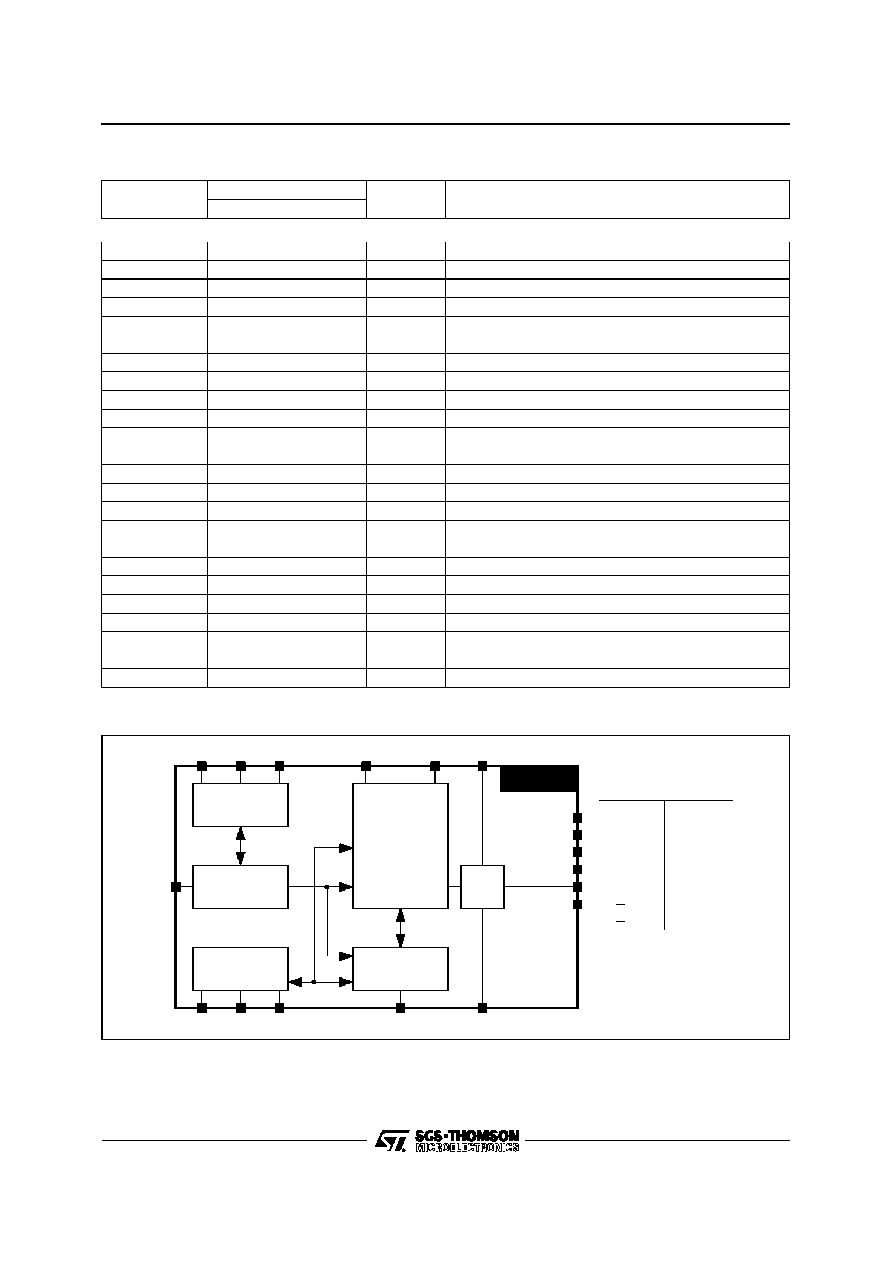

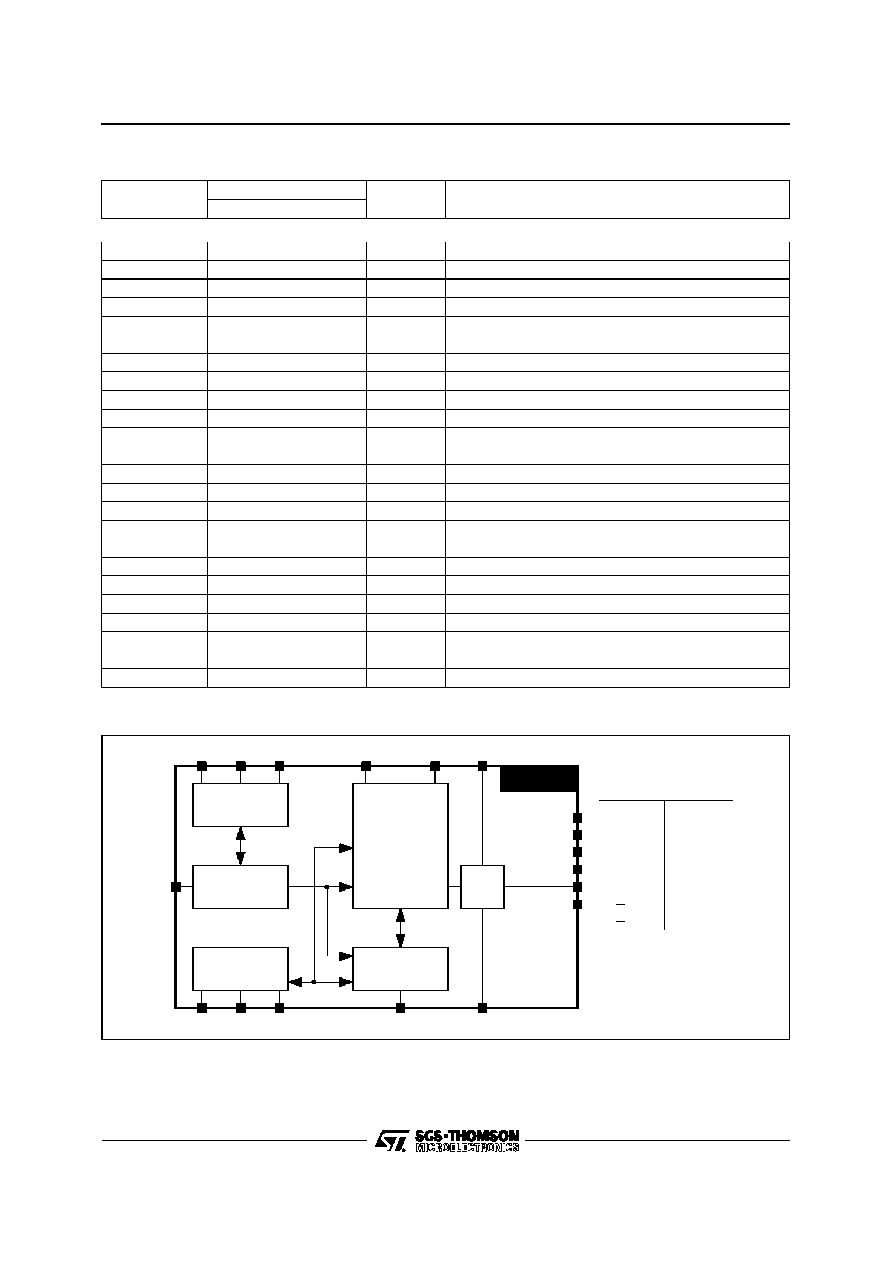

CLOCK

GENE RATOR

TIME BAS E

MCU

INTERFACE

CONTROL

P ROCES S ING

DISP LAY

LOGIC

6K BYTE

RAM

DAC

S YNC

IN

CRT

MODE

LCD

MODE

D2, D3 , D1

R, G, B

I

Y

LOAD

FRAME

D0

DF

PO R

CKO

XTI

XTO

NCS

S DA

S CK

CKD (SYNC IN)

V

DD

V

REF

V

S S

V

S SA

C

S YNC

V

SYNC

V

EE

S TV9410

9410-03.EPS

BLOCK DIAGRAM

STV9410

3/25

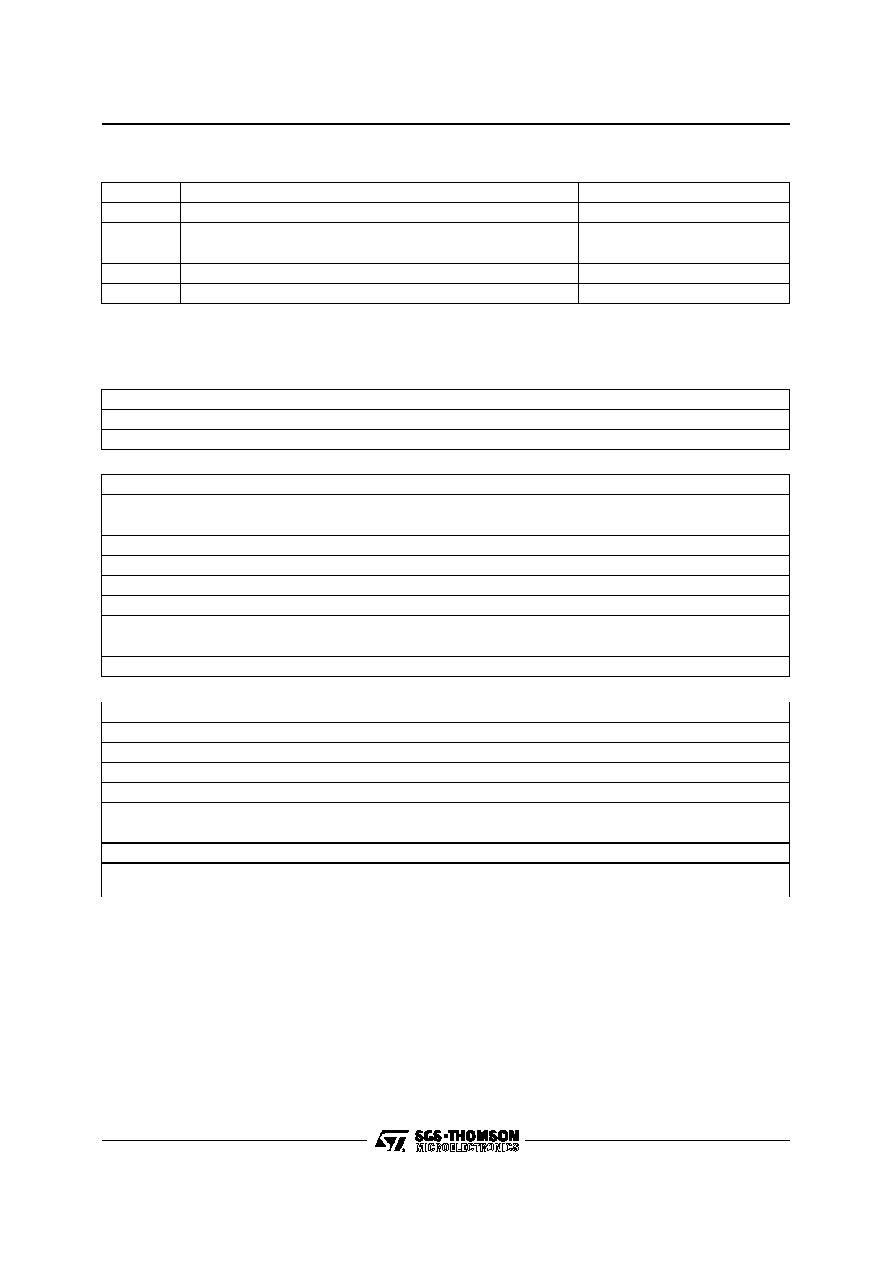

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Unit

V

DD

*

Supply Voltage

-0.3, +7.0

V

V

IN

*

Input Voltage

-0.3, +7.0

V

T

oper

Operating Temperature

0, +70

o

C

T

stg

Storage Temperature

-40, +125

o

C

P

to t

Power Dissipation

300

mW

9410-03.TBL

* with respect to V

SS

ELECTRICAL CHARACTERISTICS

(V

DD

= 5V, V

SS

= 0V, T

a

= 0 to + 70

o

C, fxtal = 8 to 10MHz, unless otherwise specified)

Symbol

Parameter

Min

Typ

Max

Unit

V

DD

Supply voltage

4.75

5.0

5.25

V

I

DD

Supply current *

-

-

50

mA

INPUTS

NCS, SDA, SCK, SYNC IN, XTI

V

IL

Input low voltage

0

-

0.8

V

V

IH

Input high voltage (except XTI)

2

-

V

DD

V

I

IL

Input leakage current (except XTI) (0 < V

IN

< V

DD

)

-10

-

+10

�

A

C

IN

Input capacitance (except XTI)

-

10

-

pF

V

REF

V

rh

Voltage reference of DAC

1.5

-

V

DD

V

V

rst

Reset level on V

REF

0

-

0.4

V

R

IN

V

REF

to V

SSA

internal resistance

0.4

-

1.0

k

V

SSA

Reference level of DAC

0

-

V

DD

V

OUTPUTS

SDA, C

SYNC

, V

SYNC

, R, G, B, I, SYNC IN, DF, XTO, CKO, POR

V

OL

Output low voltage (I

OL

= 1.6mA)

0

-

0.4

V

V

OH

Output high voltage (I

OH

= - 0.1mA )

0.8 V

DD

-

V

DD

V

Y

Output voltage (V

REF

=5V, V

SSA

=0, I

OUT

=0)

L

I

Integral linearity

-

-

0.25

V

L

D

Differential linearity

-

-

0.1

V

Z

OUT

Output impedance

-

-

0.5

k

T

p

Propagation time at V

OUT

90% of V

FINAL

,

C

L

=20pF, I

OUT

=0, V

REF

=5V, V

SSA

=0V

-

-

80

ns

* no load on outputs

9410-04.TBL

STV9410

4/25

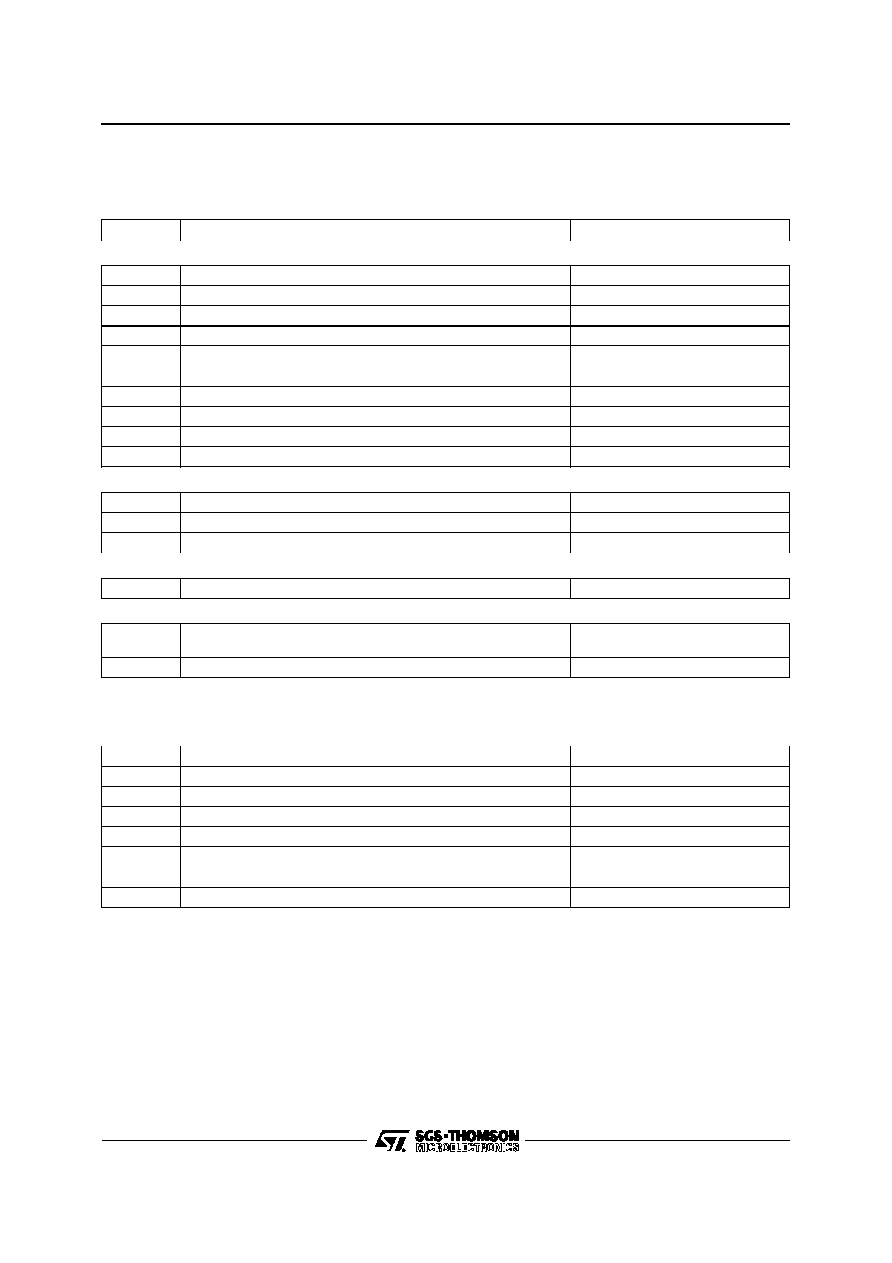

TIMINGS

(V

DD

= 5V

�

5%, V

SS

= 0V, T

a

= 0 to + 70

o

C, fxtal = 8 to 10MHz,

V

IL

= 0.8V, V

IH

= 2V, V

OL

= 0.4V, V

OH

= 2.4V, C

L

= 50pF, unless otherwise specified)

Symbol

Parameter

Min

Typ

Max

Unit

SERIAL INTERFACE NCS, SCK, SDA (Figure 1)

T

csl

NCS low to SCK falling edge

0

ns

T

sch

SCK pulse width high

80

ns

T

scl

SCK pulse width low

80

ns

f

SCK

Serial Clock Frequency

4

MHz

T

sds

Set up time of SDA on SCK rising edge

20

ns

T

sdh

Hold time of SDA after SCK rising edge

20

ns

T

sdv

Access time in read mode

50

ns

T

sdx

Hold data in read mode

0

ns

T

sdz

Serial interface disable time

50

ns

T

read

Delay before Valid Data

2

�

s

OSCILLATOR INPUT (XTI) (Figure 1)

T

wh

Clock high level

30

ns

T

wl

Clock low level

30

ns

F

clk

Clock frequency

8

10

MHz

RESET (V

REF

)

T

res

Reset Low level pulse

2

�

s

OUTPUT SIGNALS SDA, C

SYNC

, V

SYNC

, R, G, B, I, SYNC IN, DF, XTO, CKO, POR (Figure 2)

T

ph

,T

pl

Propagation time

C

L

= 30 pF

C

L

= 100 pF

50

100

ns

ns

T

skew

Skew between R, G, B, I signals

30

ns

(V

DD

= 5V

�

5%, V

SS

= 0V, T

a

= 0 to + 70

o

C, fxtal = 8 to 10MHz,

V

OL

= 0.2V

DD

, V

OH

= 0.8V

DD

, C

L

= 100pF, unless otherwise specified)

LCD INTERFACE D0, D1, D2, D3, CKD, LOAD, DF, FRAME (Figure 3)

t

CYC

CKD Shift Clock Period

4 x Pxtal

ns

t

CH

CKD Clock High

150

ns

t

CL

CKD Clock Low

150

ns

t

WLD

Load Pulse Width

150

ns

t

SU

Data Set-up Time

150

ns

t

DH

Data Hold Time

150

ns

t

DF

DF Delay from Load

100

ns

t

SUF

Frame Set-up before Load

150

ns

9410-05.TBL

STV9410

5/25