| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TDA7346D | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

TDA7346

DIGITAL CONTROLLED SURROUND SOUND MATRIX

1 STEREO INPUT

THREE INDEPENDENT SURROUND MODES

ARE AVAILABLE MOVIE, MUSIC AND SIMU-

LATED

- MUSIC: 4 SELECTABLE RESPONSES

- MOVIE AND SIMULATED:

256 SELECTABLE RESPONSES

TWO INDEPENDENT INPUT ATTENUATORS

IN 0.31dB FOR BALANCE FACILITY

ALL FUNCTIONS PROGRAMMABLE VIA SE-

RIAL BUS

DESCRIPTION

The TDA7346 reproduces surround sound by us-

ing phase shifters and a signal matrix. Control of

all the functions is accomplished by serial bus.

The AC signal setting is obtained by resistor net-

works and switches combined with operational

amplifiers.

February 1997

HP1

HP2

-

+

-

+

SUPPLY

RPS1

PS1

90Hz

MUSIC

EFFECT

CONTROL

I

2

C BUS

DECODER

LATCHES

Lout

DIG GND

SCL

VS

AGND

CREF

LP

D94AU122A

L-in

100K

100nF

LP1

RLP1

RHP1

5.6nF

680nF

-

+

R5

R6

+

SIM

MOVIE/

MUSIC

L-R

100nF

PS1

PS2

4KHz

4.7nF

PS2

PS3

400Hz

22nF

PS3

PS4

400Hz

22nF

PS4

RPS2

RPS3

RPS4

OFF

LPF

9KHz

MIXING

AMP

MIXING

AMP

PHASE SHIFTER

MOVIE/SIM

R-in

100nF

100K

C5

22

µ

F

1.2nF

SDA

ADDR

Rout

REAR

BLOCK DIAGRAM

ORDERING NUMBER: TDA7346 (DIP20)

TDA7346D (SO20)

SO20

DIP20

1/14

THERMAL DATA

Symbol

Description

Value

Unit

R

th j-pins

Thermal Resistance Junction-pins

Ma x.

85

∞

C/W

QUICK REFERENCE DATA

Symbol

Parameter

Min.

Typ.

Max.

Unit

V

S

Supply Voltage

7

9

10.2

V

V

CL

Max. input signal handling

2

Vrms

THD

Total Harmonic Distortion V = 1Vrms f = 1KHz

0.02

0.1

%

S/N

Signal to Noise Ratio V

out

= 1Vrms (mode = OFF)

106

dB

S

C

Channel Separation f = 1KHz

70

dB

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Unit

V

S

Operating Supply Voltage

10.5

V

T

amb

Operating Ambient Temperature

-40 to 85

∞

C

T

stg

Storage Temperature Range

-55 to +150

∞

C

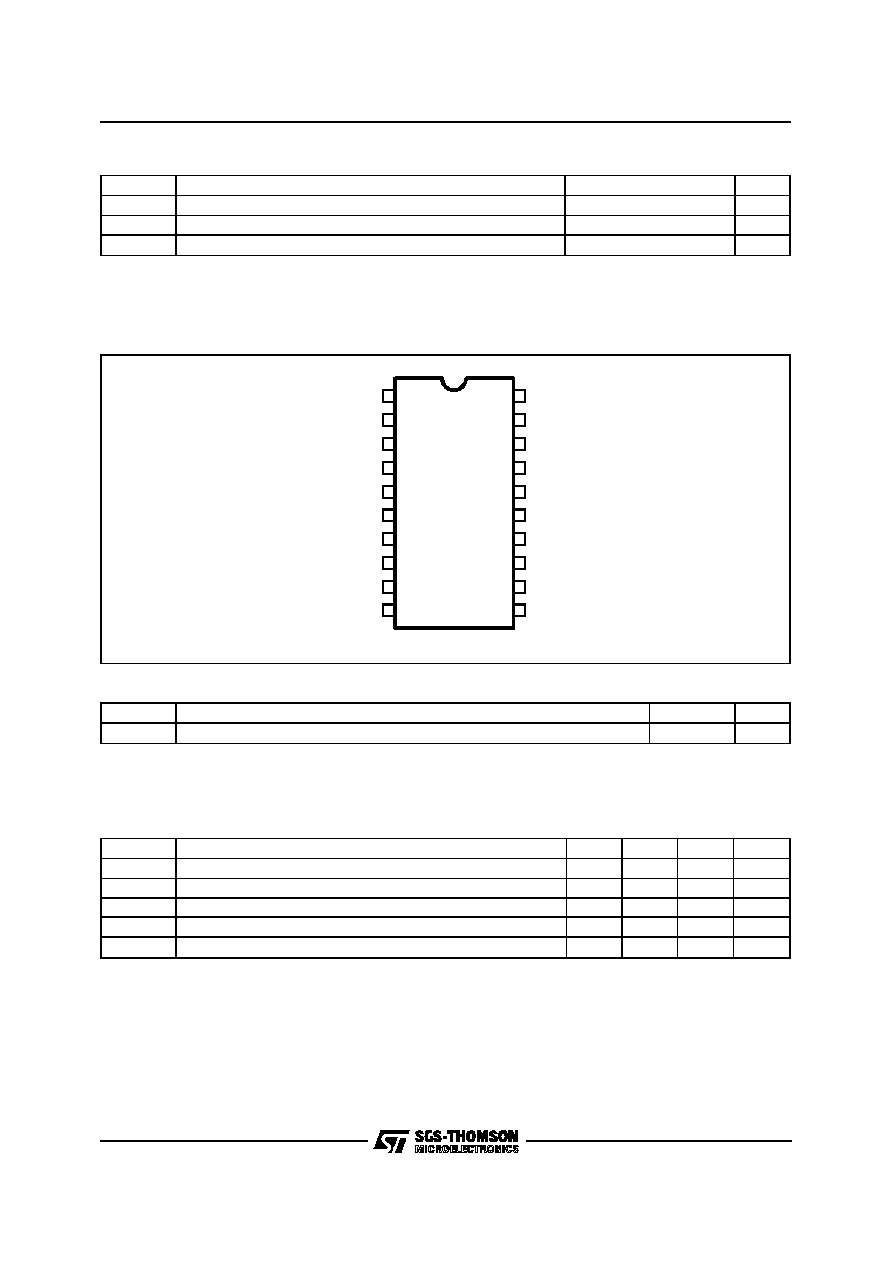

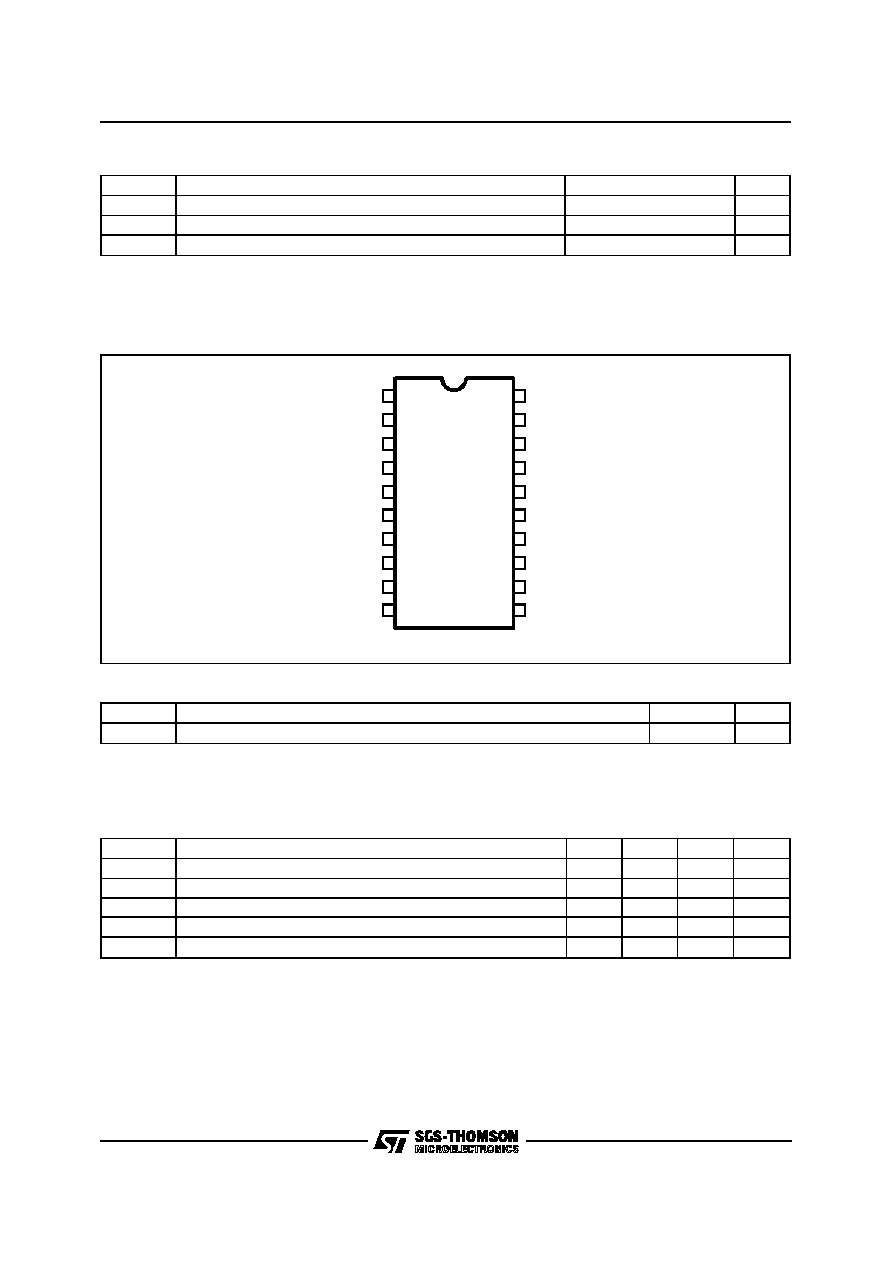

PS1

VS

CREF

L-in

LP

Lout

REAR

SDA

SCL

1

3

2

4

5

6

7

8

9

ADDR

Rout

PS4

R-in

PS3

HP2

HP1

LP1

PS2

20

19

18

17

16

14

15

13

12

D94AU128

DIG GND

10

AGND

11

PIN CONNECTION

TDA7346

2/14

ELECTRICAL CHARACTERISTICS (refer to the test circuit T

amb

= 25

∞

C, V

S

= 9V, R

L

= 10K

,

R

G

= 600

, all controls flat (G = 0),Effect Ctrl = -6dB, MODE = OFF; f = 1KHz

unless otherwise specified)

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

SUPPLY

V

S

Supply Voltage

7

9

10.2

V

I

S

Supply Current

10

mA

SVR

Ripple Rejection

L

CH

/ R

CH out

, Mode = OFF

60

80

dB

INPUT STAGE

R

II

Input Resistance

100

K

V

CL

Clipping Level

THD = 0.3%; Lin or Rin

2

2.5

Vrms

THD = 0.3%; Rin + Lin (2)

3.0

Vrms

C

RANGE

Control Range

20

dB

A

VMIN

Min. Attenuation

-1

0

1

dB

A

VMAX

Max. Attenuation

20

dB

A

STEP

Step Resolution

0.31

dB

V

DC

DC Steps

adjacent att. step

0

mV

EFFECT CONTROL

C

RANGE

Control Range

- 21

- 6

dB

S

STEP

Step Resolution

1

dB

680nF

C16

HP1

HP2

L-in

0.1

µ

F

C17

Lout

Rout

AGND

DIG GND

SCL

ADDR

LP1

1.2nF

C6

LP

REAR

R-in

0.1

µ

F

C7

5.6nF

C15

TDA7346

SDA

PS1

100nF

C14

PS2

4.7nF

C13

CREF

22

µ

F

C3

PS3

22nF

C4

PS4

22nF

C5

100nF

C2

10

µ

F C1

VS

D93AU040C

6

7

9

8

5

16

19

1

20

3

12

10

11

13

14

15

2

4

17

18

TEST CIRCUIT

TDA7346

3/14

ELECTRICAL CHARACTERISTICS (continued)

SURROUND SOUND MATRIX

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

G

OFF

In-phase Gain (OFF)

Mode OFF, Input signal of

1kHz, 1.4 V

p-p

, R

in

R

out

L

in

L

out

-1.5

0

1.5

dB

D

GOFF

LR In-phase Gain Difference

(OFF)

Mode OFF, Input signal of

1kHz, 1.4 V

p-p

(R

in

R

out

), (L

in

L

out

)

-1.5

0

1.5

dB

G

MOV1

In-phase Gain (Movie 1)

RPS1, RPS2, RPS3, RPS4 =

POR Preset

Movie mode, Effect Ctrl = -6dB

Input signal of 1kHz, 1.4 V

p-p

R

in

R

out

, L

in

L

out

7

dB

G

MOV2

In-phase Gain (Movie 2)

RPS1, RPS2, RPS3, RPS4 =

POR Preset

Movie mode, Effect Ctrl = -6dB

Input signal of 1kHz, 1.4 V

p-p

R

in

R

out

, L

in

L

out

8

dB

D

GMOV

LR In-phase Gain Difference

(Movie)

Movie mode, Effect Ctrl = -6dB

Input signal of 1kHz, 1.4 V

p-p

(R

in

R

out

) ≠ (L

in

L

out

)

0

dB

G

MUS1

In-phase Gain (Music 1)

RPS1 = POR PRESET

Music mode, Effect Ctrl = -6dB

Input signal of 1kHz, 1.4 V

p-p

(R

in

R

out

) ≠ (L

in

L

out

)

6

dB

G

MUS2

In-phase Gain (Music 2)

RPS1 = POR PRESET

Music mode, Effect Ctrl = -6dB

Input signal of 1kHz, 1.4 V

p-p

R

in

R

out

, L

in

L

out

7.5

dB

D

GMUS

LR In-phase Gain Difference

(Music)

Music mode, Effect Ctrl = -6dB

Input signal of 1kHz, 1.4 V

p-p

(R

in

R

out

) ≠ (L

in

L

out

)

0

dB

L

MON1

Simulated L Output 1

RPS1, RPS2, RPS3, RPS4 =

POR Preset

Simulated Mode, Effect Ctrl = -6dB

Input signal of 250Hz,

1.4 V

p-p

, R

in

and L

in

L

out

4.5

dB

L

MON2

Simulated L Output 2

RPS1, RPS2, RPS3, RPS4 =

POR Preset

Simulated Mode, Effect Ctrl = -6dB

Input signal of 1kHz,

1.4 V

p-p

, R

in

and L

in

L

out

≠ 4.0

dB

L

MON3

Simulated L Output 3

RPS1, RPS2, RPS3, RPS4 =

POR Preset

Simulated Mode, Effect Ctrl = -

6dB

Input signal of 3.6kHz,

1.4 V

p-p

, R

in

and L

in

L

out

7.0

dB

R

MON1

Simulated R Output 1

RPS1, RPS2, RPS3, RPS4 =

POR Preset

Simulated Mode, Effect Ctrl = -6dB

Input signal of 250Hz,

1.4 V

p-p

, R

in

and L

in

R

out

≠ 4.5

dB

R

MON2

Simulated R Output 2

RPS1, RPS2, RPS3, RPS4 =

POR Preset

Simulated Mode, Effect Ctrl = -6dB

Input signal of 1kHz,

1.4 V

p-p

, R

in

and L

in

R

out

3.8

dB

R

MON3

Simulated R Output 3

RPS1, RPS2, RPS3, RPS4 =

POR Preset

Simulated Mode, Effect Ctrl = -6dB

Input signal of 3.6kHz,

1.4 V

p-p

, R

in

and L

in

R

out

≠ 20

dB

R

LP1

Low Pass Filter Resistance

10

K

R

PS1

Phase Shifter 1 Resistance

at POR

17.95

k

R

PS2

Phase Shifter 2 Resistance

at POR

8.465

K

R

PS3

Phase Shifter 3 Resistance

at POR

18.050

K

R

PS2

Phase Shifter 4 Resistance

at POR

18.050

K

R

HPI

High Pass Filter Resistance

60

K

R

LPF

LP Pin Impedance

10

K

TDA7346

4/14

ELECTRICAL CHARACTERISTICS (continued)

Symbol

Parameter

Test Condition

Min.

Typ.

Max.

Unit

AUDIO OUTPUTS

V

OCL

Clipping Level

d = 0.3%

2

2.5

Vrms

R

OUT

Output resistance

100

200

300

V

OUT

DC Voltage Level

3.5

3.8

4.1

V

GENERAL

N

O(OFF)

Output Noise (OFF)

B

W

= 20Hz to 20KHz

R

out

and L

out

measurement

8

µ

Vrms

N

O(MOV)

Output Noise (Movie)

Mode =Movie ,

B

W

= 20Hz to 20KHz

R

out

and L

out

measurement

30

µ

Vrms

N

O(MUS)

Output Noise (Music)

Mode = Music ,

B

W

= 20Hz to 20KHz,

R

out

and L

out

measurement

30

µ

Vrms

N

O(MON)

Output Noise (Simulated)

Mode = Simulated,

B

W

= 20Hz to 20KHz

R

out

and L

out

measurement

30

µ

Vrms

d

Distorsion

Av = 0 ; V

in

= 1Vrms

0.02

0.1

%

S

C

Channel Separation

70

dB

BUS INPUTS

V

IL

Input Low Voltage

1

V

V

IH

Input High Voltage

3

V

I

IN

Input Current

-5

+5

µ

A

V

O

Output Voltage SDA

Acknowledge

I

O

= 1.6mA

0.4

0.8

V

Note:

(1) Bass and Treble response: The center frequency and the resonance quality can be choosen by

the external circuitry. A standard first order bass response can be realized by a standard feedback network.

(2) The peak voltage of the two input signals must be less then

V

S

2

:

(Lin + Rin)

peak

∑

A

Vin

<

V

S

2

TDA7346

5/14

I

2

C BUS INTERFACE

Data transmission from microprocessor to the

TDA7346 and viceversa takes place through the

2 wires I

2

C BUS interface, consisting of the two

lines SDA and SCL (pull-up resistors to positive

supply voltage must be connected).

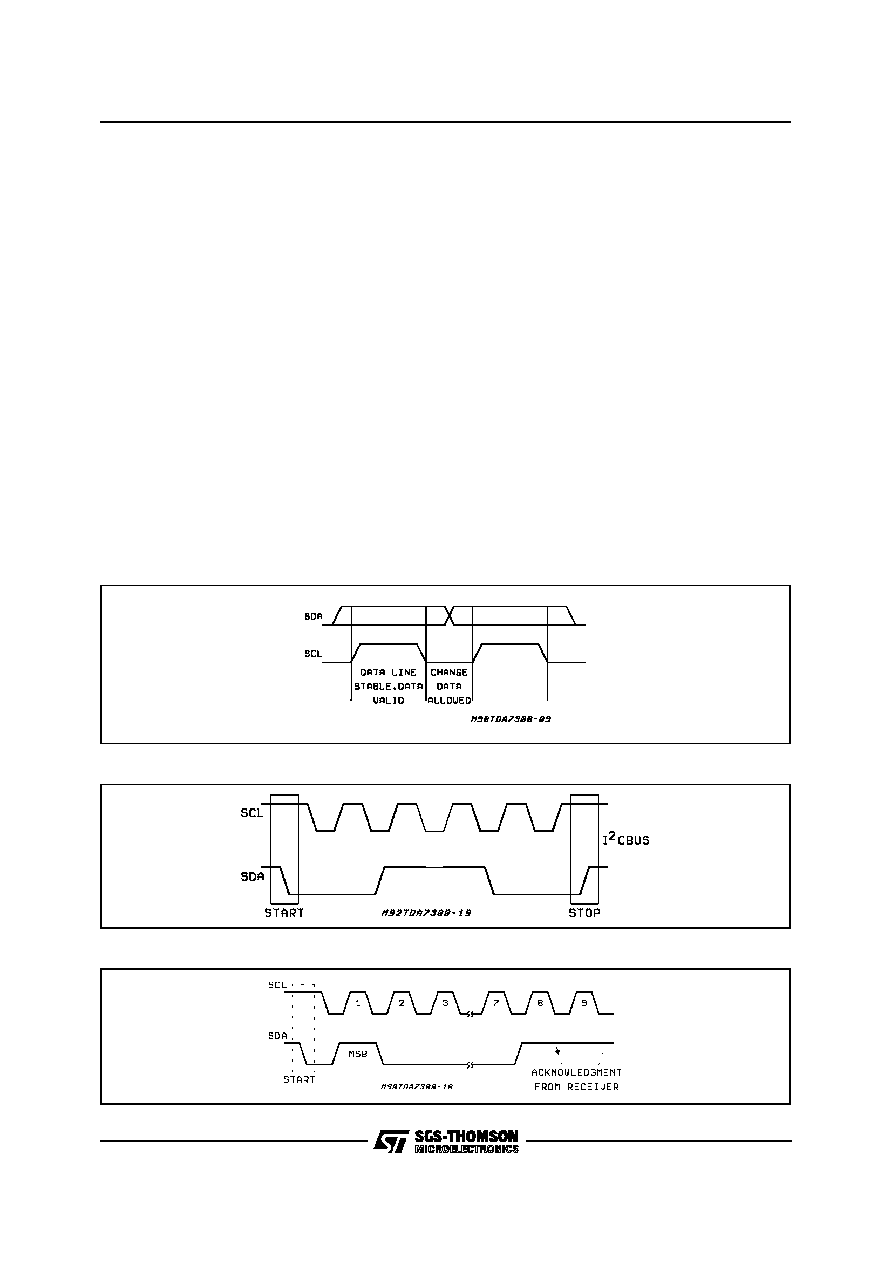

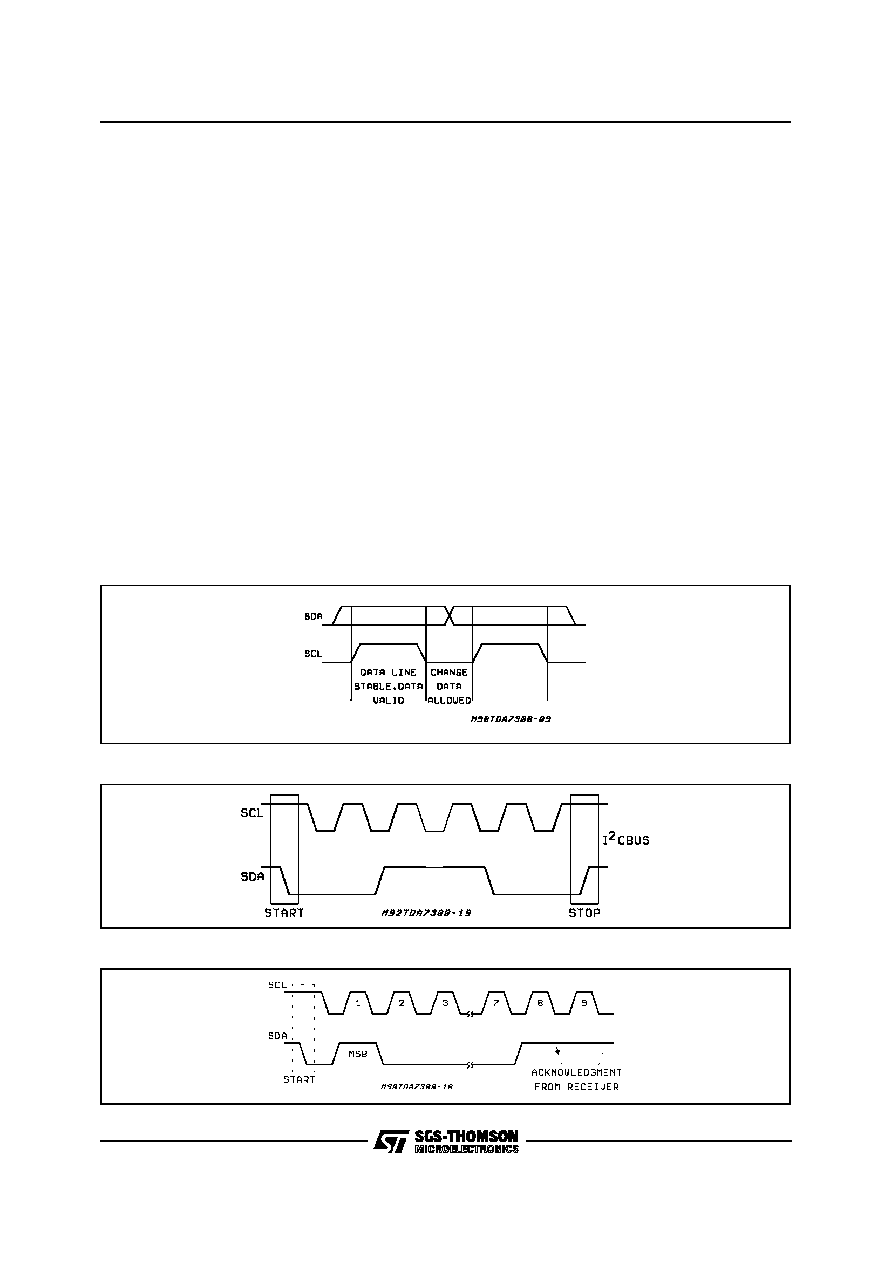

Data Validity

As shown in fig. 3, the data on the SDA line must

be stable during the high period of the clock. The

HIGH and LOW state of the data line can only

change when the clock signal on the SCL line is

LOW.

Start and Stop Conditions

As shown in fig.4 a start condition is a HIGH to

LOW transition of the SDA line while SCL is

HIGH. The stop condition is a LOW to HIGH tran-

sition of the SDA line while SCL is HIGH.

Byte Format

Every byte transferred on the SDA line must con-

tain 8 bits. Each byte must be followed by an ac-

knowledge bit. The MSB is transferred first.

Acknowledge

The master (

µ

P) puts a resistive HIGH level on the

SDA line during the acknowledge clock pulse (see

fig. 5). The peripheral (audioprocessor) that ac-

knowledges has to pull-down (LOW) the SDA line

during the acknowledge clock pulse, so that the

SDA line is stable LOW during this clock pulse.

The audioprocessor which has been addressed

has to generate an acknowledge after the recep-

tion of each byte, otherwise the SDA line remains

at the HIGH level during the ninth clock pulse

time. In this case the master transmitter can gen-

erate the STOP information in order to abort the

transfer.

Transmission without Acknowledge

Avoiding to detect the acknowledge of the audio-

processor, the

µ

P can use a simpler transmission:

simply it waits one clock without checking the

slave acknowledging, and sends the new data.

This approach of course is less protected from

misworking and decreases the noise immunity.

Figure 3: Data Validity on the I

2

CBUS

Figure 4: Timing Diagram of I

2

CBUS

Figure 5: Acknowledge on the I

2

CBUS

TDA7346

6/14

A

CHIP ADDRESS

0

DC (HEX)

1

DE (HEX)

SOFTWARE SPECIFICATION

Interface Protocol

The interface protocol comprises:

A start condition (s)

A chip address byte, containing the TDA7346

address (the 8th bit of the byte must be 0). The

TDA7346 must always acknowledge at the end

of each transmitted byte.

A sequence of data (N bytes + achnowledge).

A stop condition (P)

TDA7346 ADDRESS

MSB

first byte

LSB

MSB

LSB

MSB

LSB

S

1

1

0

1

1

1

A

0

ACK

DATA

ACK

DATA

ACK

P

Data Transferred (N-bytes + Acknowledge)

ACK = Acknowledge

S = Start

P = Stop

MAX CLOCK SPEED 100kbits/s

SOFTWARE SPECIFICATION

Chip address

1

MSB

1

0

1

1

1

A

0

LSB

A = Logic level on pin ADDR

A = 1 if ADDR pin = open

A = 0 if ADDR pin = connected to ground

MSB

LSB

SUBADDRESS

0

0

A5

A4

A3

A2

A1

A0

INPUT ATTENUATION R

0

1

A5

A4

A3

A2

A1

A0

INPUT ATTENUATION L

1

M1

M0

SURROUND MODES

1

0

0

SIMULATED MODE

1

0

1

MUSIC MODE

1

1

0

MOVIE MODE

1

1

1

1

1

1

1

1

OFF MODE

1

M1

M0

1

B3

B2

B1

B0

EFFECT CONTROL

1

M1

M0

0

0

0

C1

C0

PHASE SHIFTER 4 CONTROL

1

M1

M0

0

0

1

C1

C0

PHASE SHIFTER 3 CONTROL

1

M1

M0

0

1

0

D1

D0

PHASE SHIFTER 2 CONTROL

1

M1

M0

0

1

1

E1

E0

PHASE SHIFTER 1 CONTROL

Software Specification

TDA7346

7/14

INPUT ATTENUATION

MSB

LSB

0.3125 dB STEPS

I

A5

A4

A3

A2

A1

A0

0

0

0

0

0

0

0

0

1

-0.3125

0

0

1

0

-0.625

0

0

1

1

-0.9375

0

1

0

0

-1.25

0

1

0

1

-1.5625

0

1

1

0

-1.875

0

1

1

1

-2.1875

2.5 dB STEPS

0

0

0

0

0

0

0

0

1

-2.5

0

0

1

0

-5

0

0

1

1

-7.5

0

1

0

0

-10

0

1

0

1

-12.5

0

1

1

0

-15

0

1

1

1

-17.5

I = 0 Attenuation Input R

I = 1 Attenuation Input L

Example: to program an R input attenuation equal to -11.25 you have to send 00100100

EFFECT CONTROL (-6 / -21dB)

MSB

LSB

1dB STEPS

B3

B2

B1

B0

1

M1

M0

1

0

0

0

0

-6

1

M1

M0

1

0

0

0

1

-7

1

M1

M0

1

0

0

1

0

-8

1

M1

M0

1

0

0

1

1

-9

1

M1

M0

1

0

1

0

0

-10

1

M1

M0

1

0

1

0

1

-11

1

M1

M0

1

0

1

1

0

-12

1

M1

M0

1

0

1

1

1

-13

1

M1

M0

1

1

0

0

0

-14

1

M1

M0

1

1

0

0

1

-15

1

M1

M0

1

1

0

1

0

-16

1

M1

M0

1

1

0

1

1

-17

1

M1

M0

1

1

1

0

0

-18

1

M1

M0

1

1

1

0

1

-19

1

M1

M0

1

1

1

1

0

-20

1

M1

M0

1

1

1

1

1

-21

TDA7346

8/14

PHASE SHIFTER 3, 4

MSB

LSB

RESISTOR VALUE (K

)

C1

C0

1

M1

M0

0

0

F

0

0

12.060

1

M1

M0

0

0

F

0

1

14.450

1

M1

M0

0

0

F

1

0

18.050

1

M1

M0

0

0

F

1

1

39.100

F = 0 Phase Shifter 4

F = 1 Phase Shifter 3

PHASE SHIFTER 2

MSB

LSB

RESISTOR VALUE (K

)

D1

D0

1

M1

M0

0

1

0

0

0

5.640

1

M1

M0

0

1

0

0

1

6.770

1

M1

M0

0

1

0

1

0

8.465

1

M1

M0

0

1

0

1

1

18.300

PHASE SHIFTER 1

MSB

LSB

RESISTOR VALUE (K

)

E1

E0

1

M1

M0

0

1

1

0

0

11.745

1

M1

M0

0

1

1

0

1

14.150

1

M1

M0

0

1

1

1

0

17.950

1

M1

M0

0

1

1

1

1

37.625

Example: to program MOVIE MODE with EFFECT control = -7dB with PHASE SHIFTER resistor =

11.745K

, PHASE SHIFTER 2 resistor = 6.77K

,

PHASE SHIFTER 3 resistor = 12.06K

,

PHASE

SHIFTER 4 resistor = 18.05K

,

you have to send in sequence 5 bytes:

11010001

11001100

11001001

11000100

11000010

POWER ON RESET

INPUT ATTENUATION

-19.375dB

EFFECT CONTROL

-20dB

SURROUND MODE

OFF MODE

PHASE SHIFTER 1 RESISTOR VALUE

17.950 K

PHASE SHIFTER 2 RESISTOR VALUE

8.465 K

PHASE SHIFTER 3, 4 RESISTOR VALUE

18.050 K

TDA7346

9/14

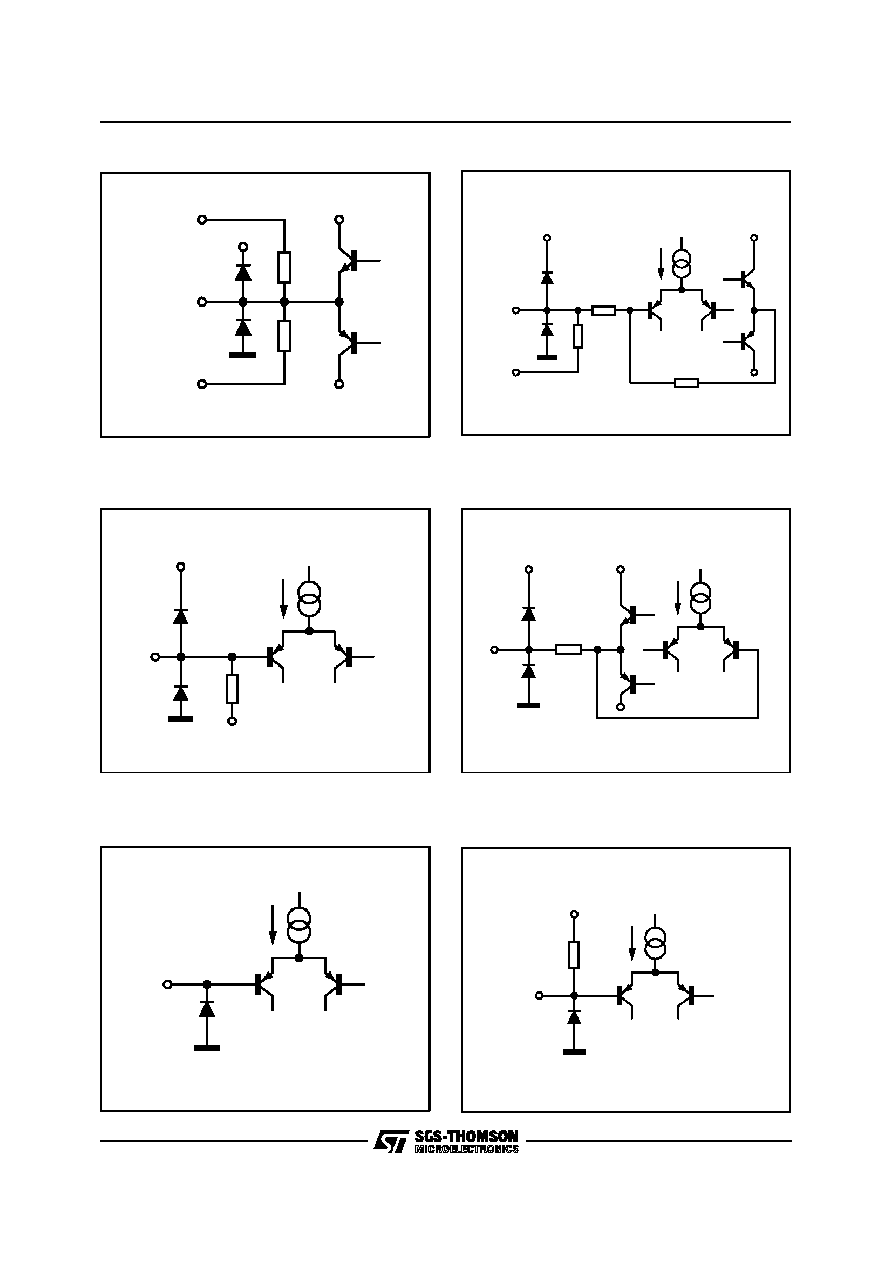

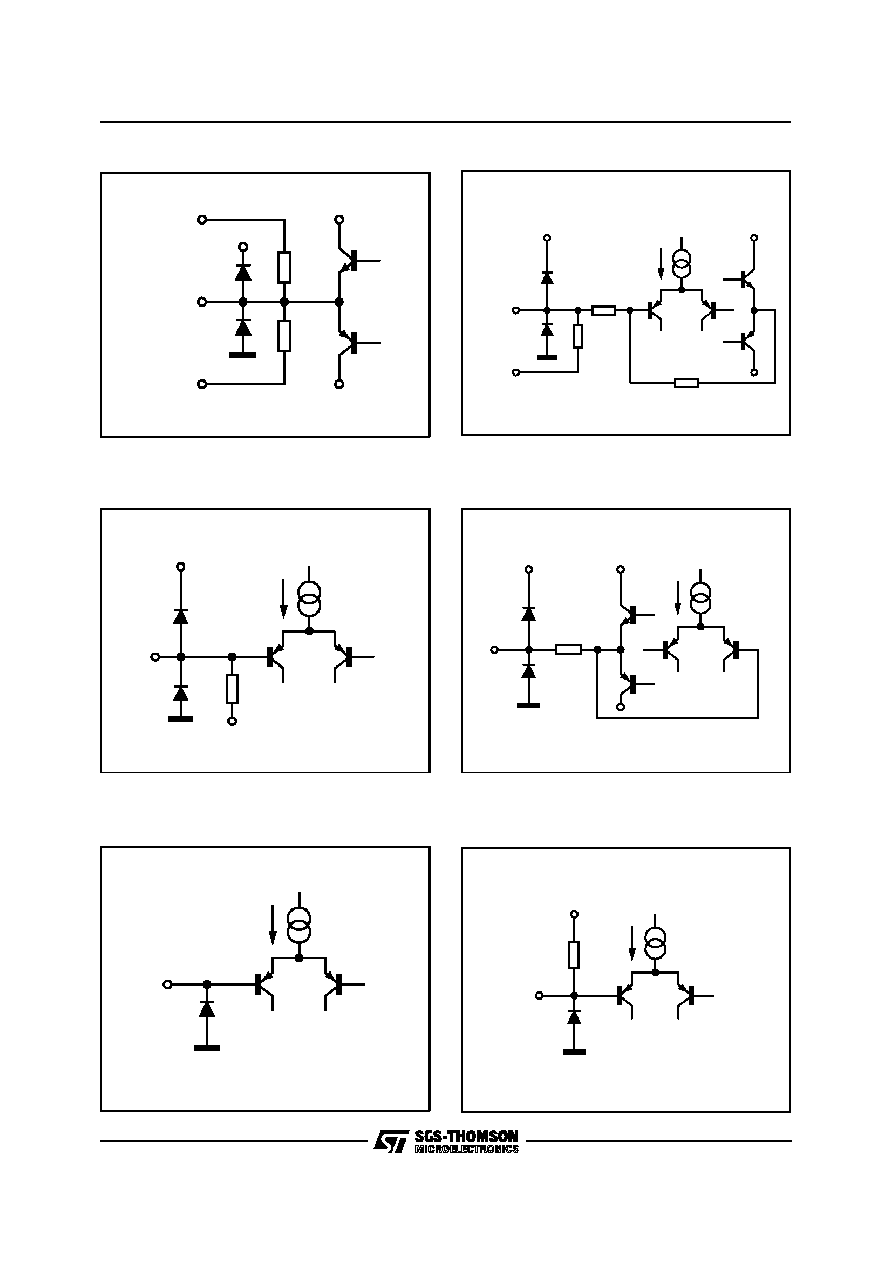

100

V

S

D94AU204

20

µ

A

PIN: L

OUT

, R

OUT

, REAR

20

µ

A

V

S

100K

Vref

D94AU123

PIN: L

in

, R

in

D94AU212

20

µ

A

V

S

100K

PIN: ADDR

D94AU205

20

µ

A

PIN: SCL, SDA

5.5K

60K

V

S

HP1

D94AU199

20

µ

A

5.5K

PIN: HP2

10K

60K

GND

V

S

LP1

HP2

D94AU198

PIN: HP1

TDA7346

10/14

20

µ

A

V

S

8.465K

D94AU125

PS2A

PIN: PS2

20K

V

S

D94AU208

20

µ

A

20K

PIN: C

REF

10K

V

S

D94AU211

20

µ

A

HP1

PIN: LP1

20

µ

A

V

S

17.95K

D94AU126

PS1A

PIN: PS1

10K

V

S

D94AU206

20

µ

A

PIN: LP

20

µ

A

V

S

18.050K

PS3A

D94AU124

PS4A

PIN: PS3, PS2

TDA7346

11/14

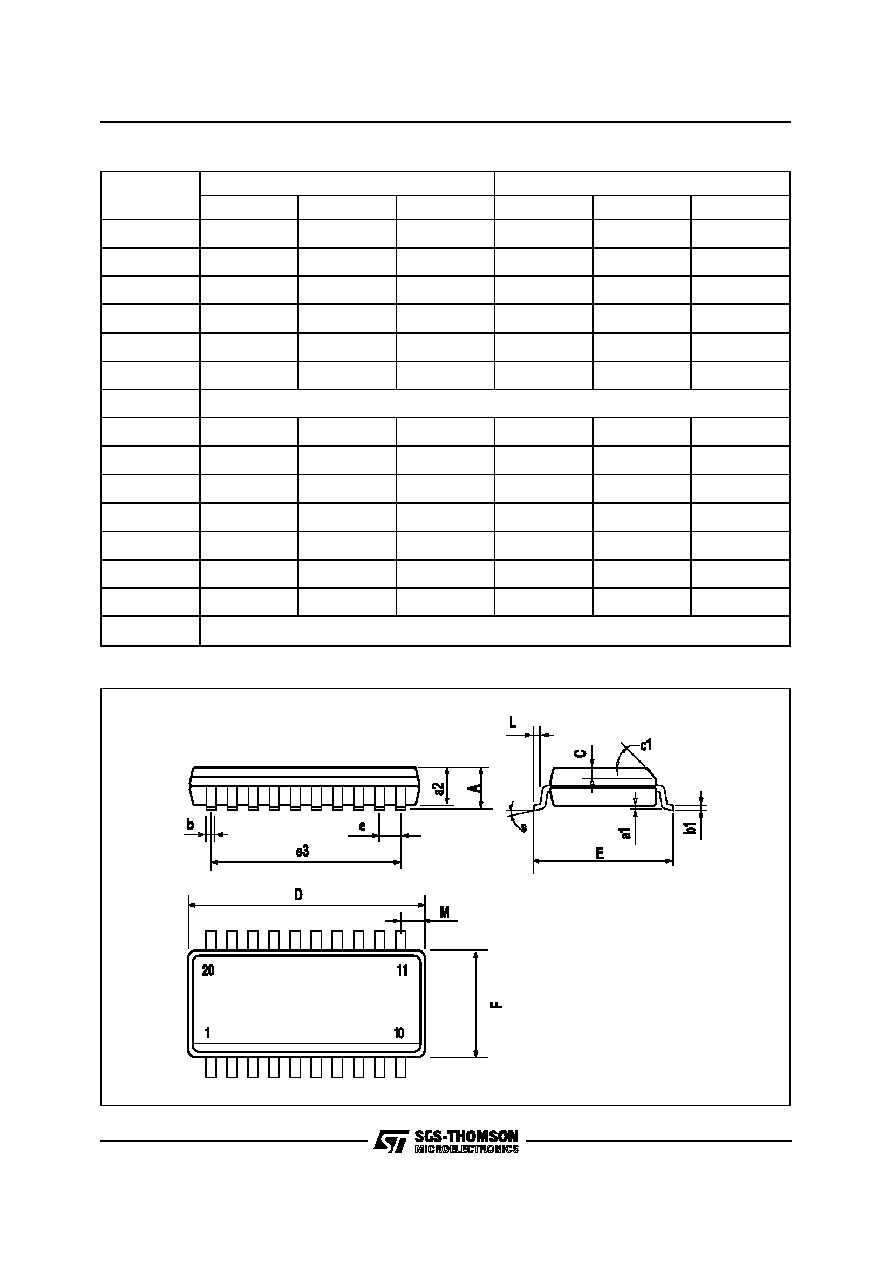

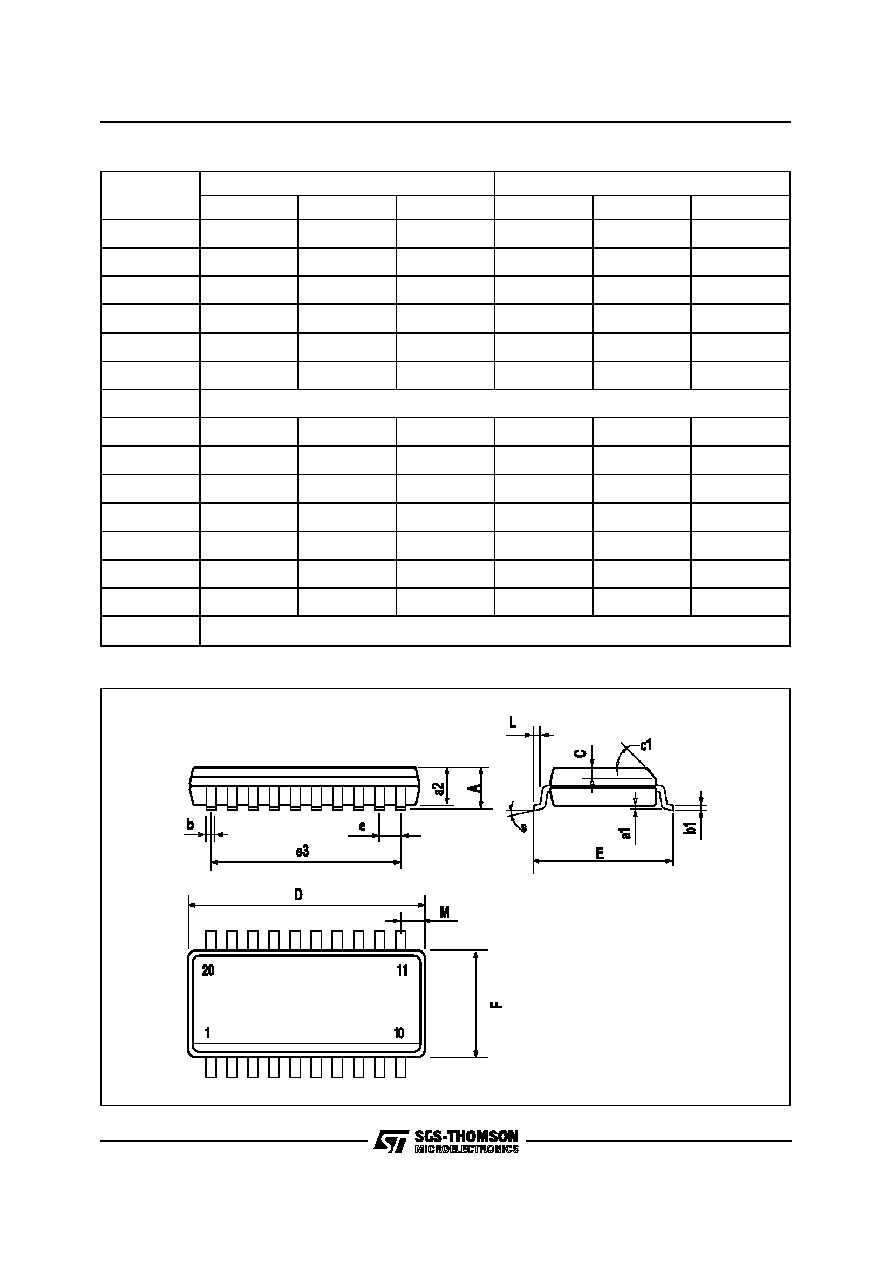

SO20 PACKAGE MECHANICAL DATA

DIM.

mm

inch

MIN.

TYP.

MAX.

MIN.

TYP.

MAX.

A

2.65

0.104

a1

0.1

0.3

0.004

0.012

a2

2.45

0.096

b

0.35

0.49

0.014

0.019

b1

0.23

0.32

0.009

0.013

C

0.5

0.020

c1

45

∞

(typ.)

D

12.6

13.0

0.496

0.512

E

10

10.65

0.394

0.419

e

1.27

0.050

e3

11.43

0.450

F

7.4

7.6

0.291

0.299

L

0.5

1.27

0.020

0.050

M

0.75

0.030

S

8

∞

(max.)

TDA7346

12/14

DIM.

mm

inch

MIN.

TYP.

MAX.

MIN.

TYP.

MAX.

a1

0.254

0.010

B

1.39

1.65

0.055

0.065

b

0.45

0.018

b1

0.25

0.010

D

25.4

1.000

E

8.5

0.335

e

2.54

0.100

e3

22.86

0.900

F

7.1

0.280

I

3.93

0.155

L

3.3

0.130

Z

1.34

0.053

DIP20 PACKAGE MECHANICAL DATA

TDA7346

13/14

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specification mentioned

in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-

THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express

written approval of SGS-THOMSON Microelectronics.

©

1997 SGS-THOMSON Microelectronics ≠ Printed in Italy ≠ All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands -

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

TDA7346

14/14