September 2003

1/10

TEA6422

BUS-CONTROLLED AUDIO MATRIX

s

6 Stereo Inputs

s

3 Stereo Ouputs

s

Gain Control 0 dB/Mute for each Output

s

Cascadable (2 different addresses)

s

Serial Bus Controlled

s

Very Low Noise

s

Very Low Distorsion

s

Fully ESD Protected

s

Wide Audio Dynamic Range ( 3 V

RMS

)

DESCRIPTION

The TEA6422 switches 6 stereo audio inputs on 3

stereo outputs.

All the switching possibilities are changed through

the I

2

C BUS.

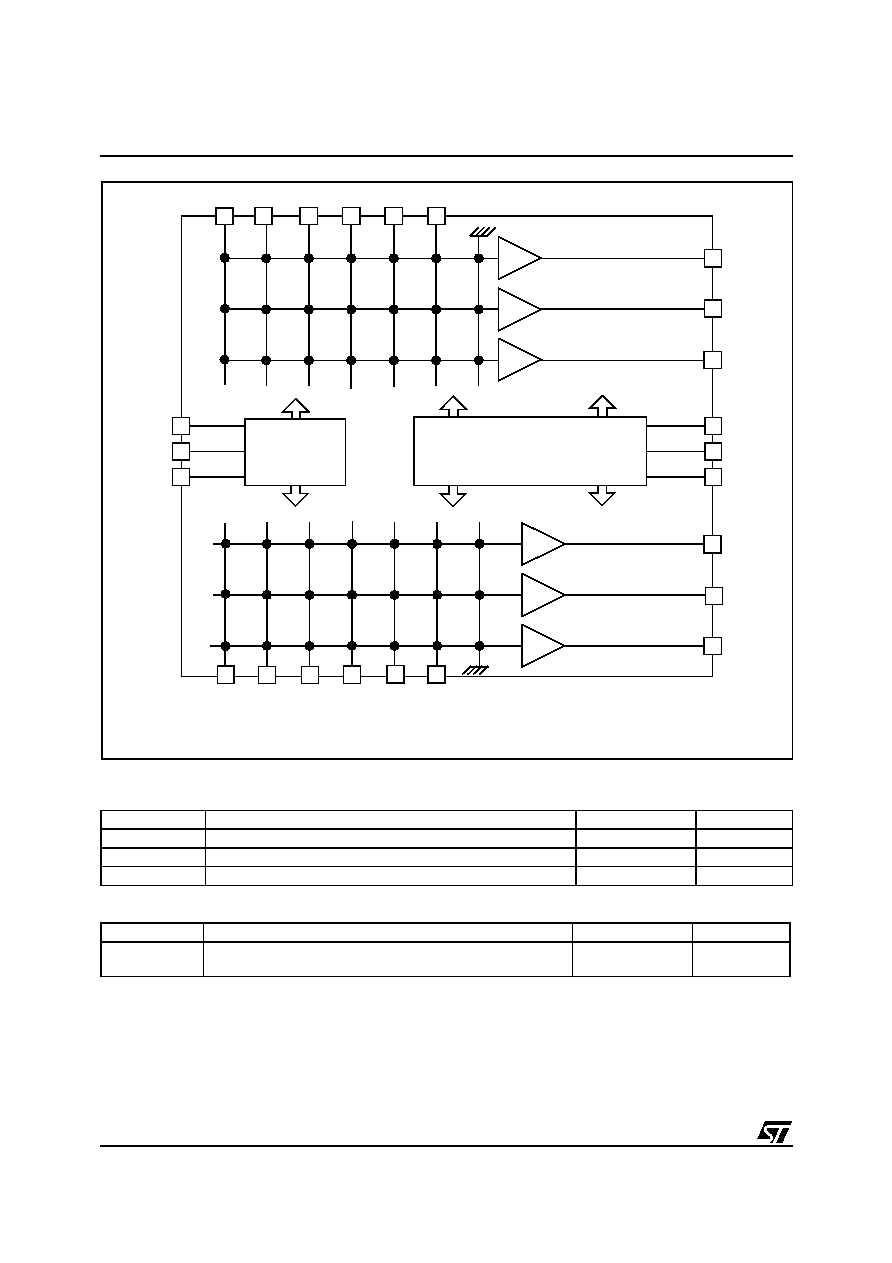

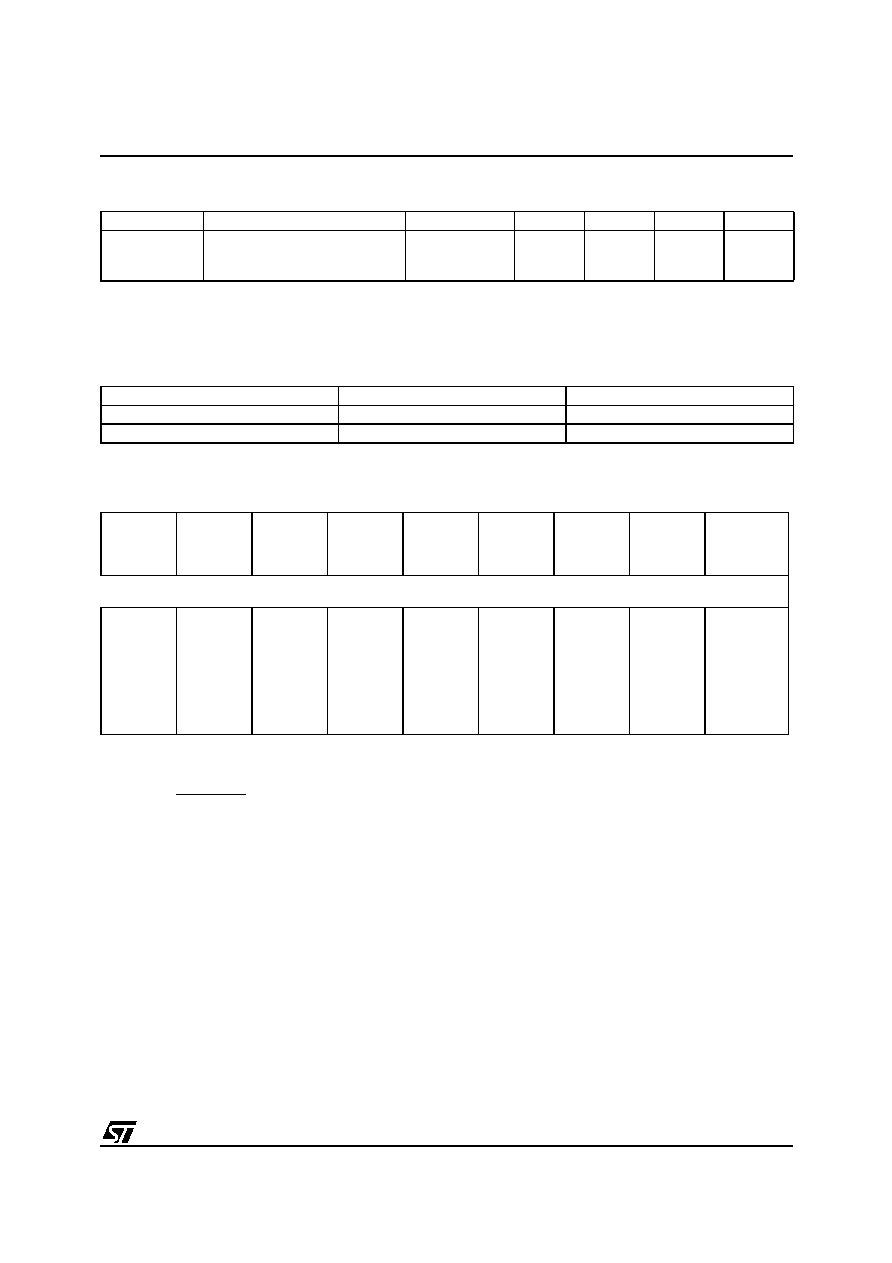

Figure 1. PIN CONNECTIONS

SHRINK DIP24

(Shrink Plastic Package)

ORDER CODE: TEA6422

SO28

(Plastic Monopackage)

ORDER CODE: TEA6422D

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

24

23

22

21

11

12

GND

CAPACITANCE

L1

L2

L3

L4

L5

LOUT1

ROUT1

SDA

SCL

ADDR

R1

R2

R3

R4

R5

V

S

L6

LOUT2

R6

ROUT3

LOUT3

ROUT2

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

24

23

22

21

11

12

25

13

14

28

27

26

SDA

SCL

ADDR

R1

R2

R3

NC

NC

R4

R5

R6

ROUT3

LOUT3

ROUT2

LOUT2

ROUT1

LOUT1

L6

L5

L4

NC

NC

L3

L2

L1

GND

CAPACITANCE

V

S

SDIP24

SO28

1

TEA6422

3/10

ELECTRICAL CHARACTERISTICS

T

A

= 25

o

C, V

S

= 9 V, R

L

= 10 k

, R

G

= 600

, f = 1 kHz (unless otherwise specified)

Symbol

Parameter

Test Conditions

Min.

Typ.

Max.

Unit

SUPPLY

V

S

Supply Voltage

8

10

11

V

I

S

Supply Current

3

8

mA

SVR

Ripple Rejection

V

IN

= 500mV

RMS

, f = 1kHz

70

80

dB

MATRIX

V

IN

Input DC Level

V

CC

/2

V

R

I

Input Resistance

30

50

100

k

C

S

Channel Separation

V

IN

= 2V

RMS

, f = 1kHz

80

90

dB

OUTPUT BUFFER

V

OUT

Output DC Level

V

CC

/2

V

R

OUT

Output Resistance

50

100

e

NI

Input Noise

BW = 20 - 20kHz, flat

3

�V

S/N

Signal to Noise Ratio

V

IN

= V

OUT

= 1V

RMS

110

dB

G

Gain

-1

0

+ 1

dB

d

Distortion

V

IN

= V

OUT

= 1V

RMS

0.01

0.05

%

V

CL

Clipping Level

d = 0.3 %, V

S

= 10 V

2.8

3

V

RMS

R

L

Output Load Resistance

2

k

1

TEA6422

4/10

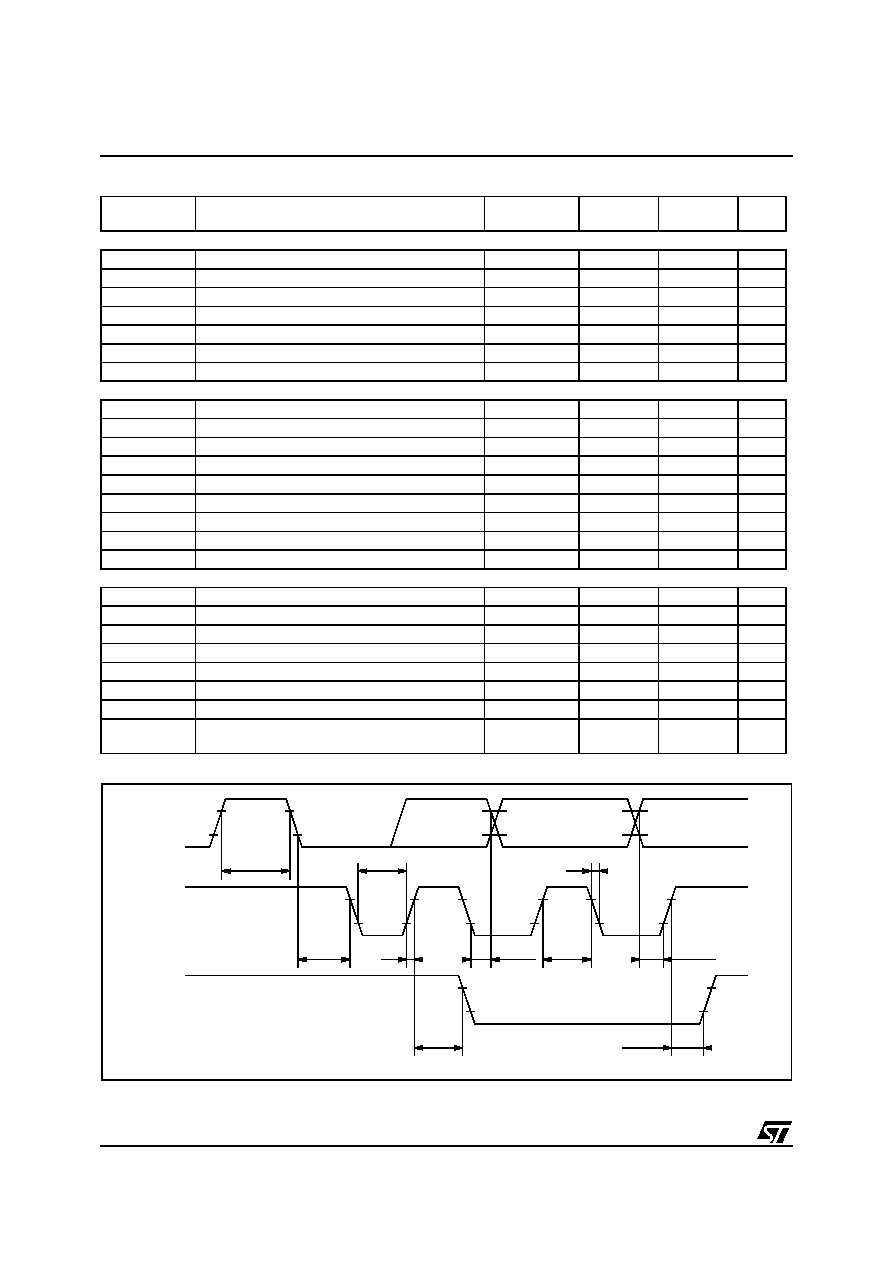

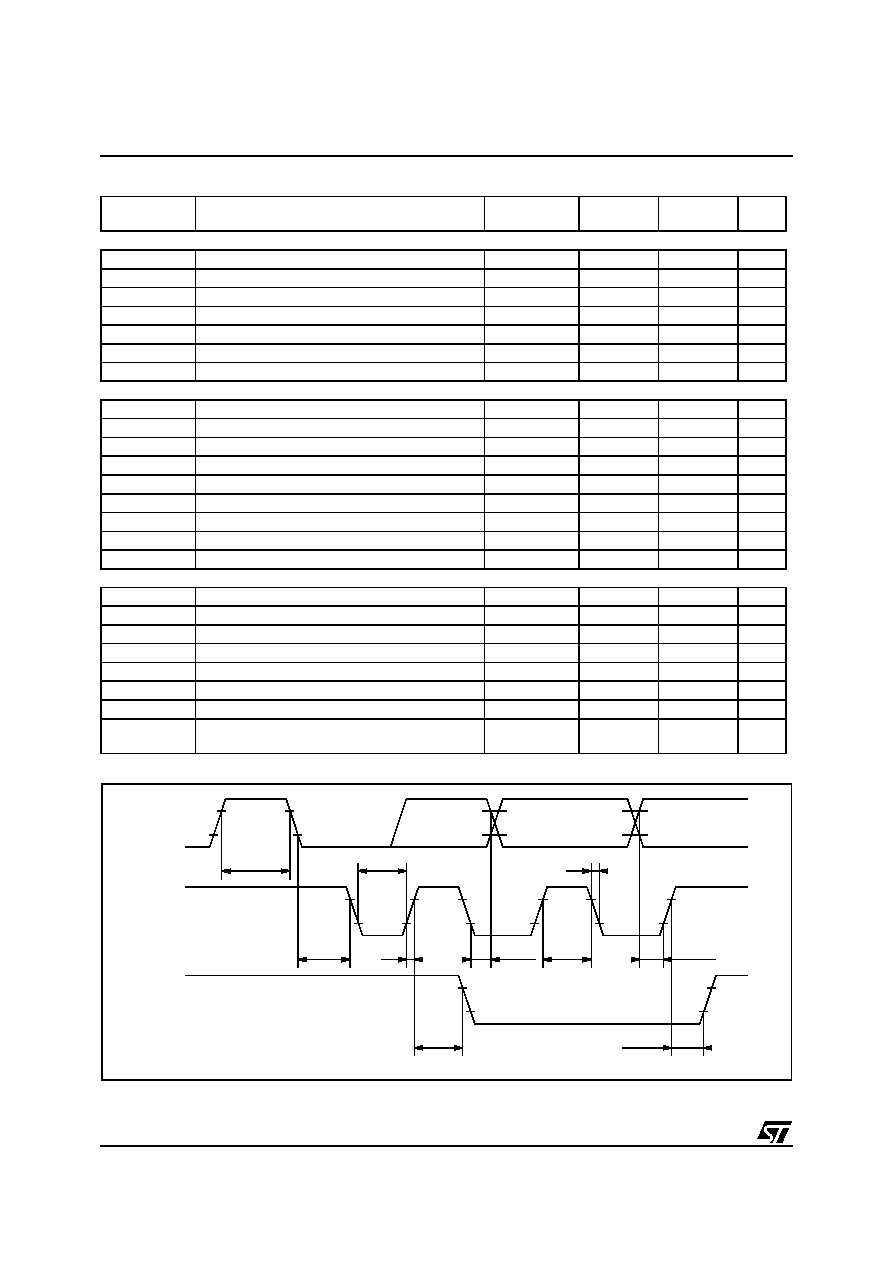

Figure 2. I�C Bus Timing

I

2

C BUS CHARACTERISTICS

Symbol

Parameter

Test

Conditions

Min.

Max.

Unit

SCL

V

IL

Low Level Input Voltage

- 0.3

+ 1.5

V

V

IH

High Level Input Voltage

3.0

V

CC

+ 0.5

V

I

LI

Input Leakage Current

V

I

= 0 to V

CC

- 10

+ 10

�A

f

SCL

Clock Frequency

0

100

kHz

t

R

Input Rise Time

1.5V to 3V

1000

ns

t

F

Input Fall Time

3V to 1.5V

300

ns

C

I

Input Capacitance

10

pF

SDA

V

IL

Low Level Input Voltage

- 0.3

+ 1.5

V

V

IH

High Level Input Voltage

3.0

V

CC

+ 0.5

V

I

LI

Input Leakage Current

V

I

= 0 to V

CC

- 10

+ 10

�A

C

I

Input Capacitance

10

pF

t

R

Input Rise Time

1.5V to 3V

1000

ns

t

F

Input Fall Time

3V to 1.5V

300

ns

V

OL

Low Level Output Voltage

I

OL

= 3mA

0.4

V

t

F

Output Fall Time

3V to 1.5V

250

ns

C

L

Load Capacitance

400

pF

TIMING

t

LOW

Clock Low Period

4.7

�s

t

HIGH

Clock High Period

4.0

�s

t

SU

, DAT

Data Set-up Time

250

ns

t

HD

, DAT

Data Hold Time

0

340

ns

t

SU

, STO

Set-up Time from Clock High to Stop

4.0

�s

t

BUF

Start Set-up Time following a Stop

4.7

�s

t

HD

, STA

Start Hold Time

4.0

�s

t

SU

, STA

Start Set-up Time following Clock Low-to High

Transition

4.7

�s

(start, stop)

t

BUF

t

LOW

t

HIGH

t

f

t

r

t

HD,STA

t

HD,DAT

t

SU,DAT

t

SU,STA

t

SU,STO

SDA

SCL

SDA

1

TEA6422

5/10

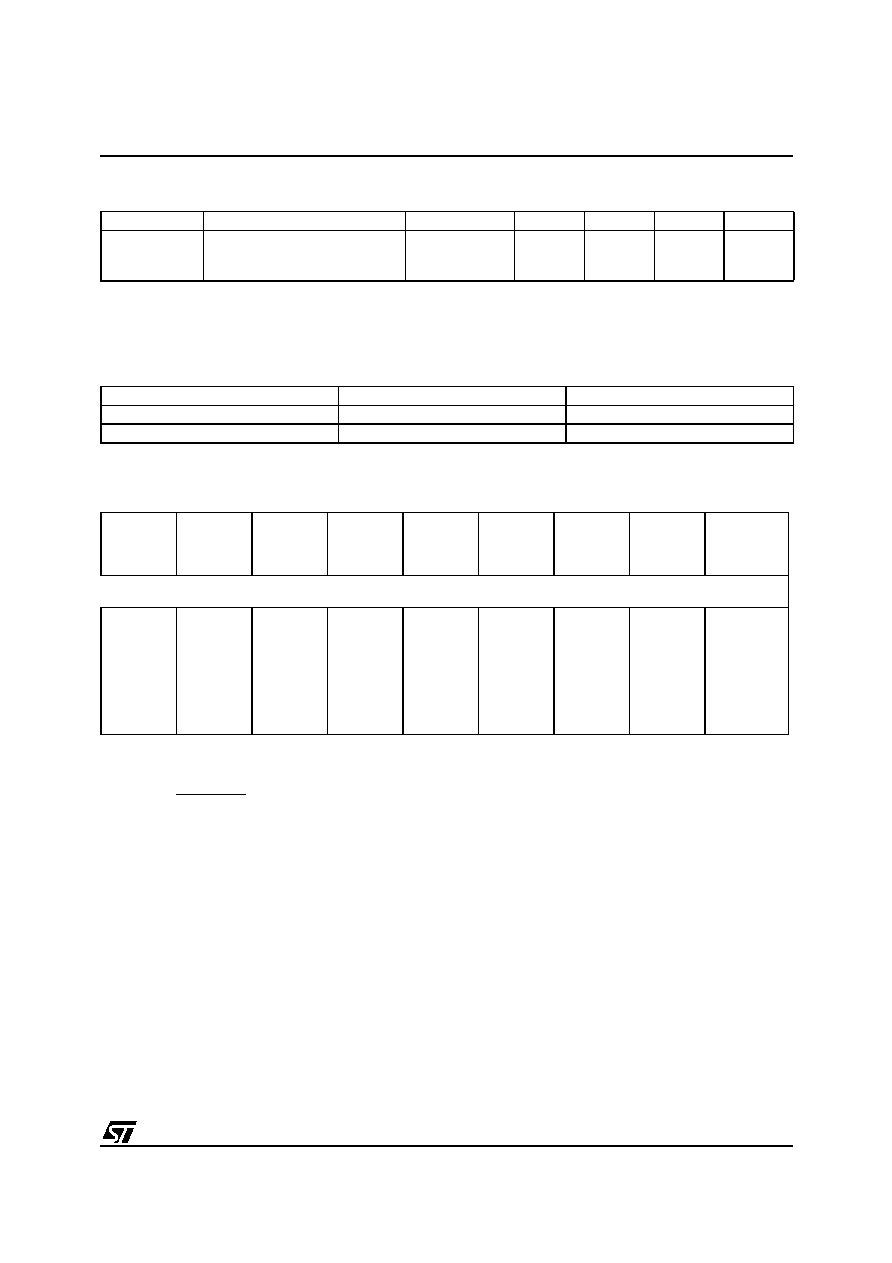

POWER ON RESET

After power-on reset all outputs are in mute mode

SOFTWARE SPECIFICATION

1. Chip address

2. Data bytes

X = don't care - MSB is transmitted first

Example : 010XX100 connects output 3 with input 5.

Symbol

Parameter

Conditions

Min.

Typ.

Max.

Unit

Reset

Start of Reset

End of Reset

Incr. V

CC

Decr. V

CC

Incr. V

CC

4.5

2.5

4.2

V

V

V

Address

HEX

ADDR

1001 1000

98

0

1001 1010

9A

1

Output select

X

0

0

1

0

1

0

X

X

I

2

I

1

I

0

Output 1

Output 2

Output 3

Input select

X

Q

1

Q0

X

X

0

0

0

0

1

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

Input 1

Input 2

Input 3

Input 4

Input 5

Input 6

Mute

1