| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: UC3844A | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1/16

UC284XA

UC384XA

May 2004

1

FEATURES

TRIMMED OSCILLATOR DISCHARGE

CURRENT

CURRENT MODE OPERATION TO 500kHz

AUTOMATIC FEED FORWARD

COMPENSATION

LATCHING PWM FOR CYCLE-BY-CYCLE

CURRENT LIMITING

INTERNALLY TRIMMED REFERENCE WITH

UNDERVOLTAGE LOCKOUT

HIGH CURRENT TOTEM POLE OUTPUT

UNDERVOLTAGE LOCKOUT WITH

HYSTERESIS

LOW START-UP CURRENT (< 0.5mA)

DOUBLE PULSE SUPPRESSION

2

DESCRIPTION

The UC384xA family of control ICs provides the

necessary features to implement off-line or DC to

DC fixed frequency current mode control schemes

with a minimal external parts count. Internally im-

plemented circuits include a trimmed oscillator for

precise DUTY CYCLE CONTROL under voltage

lockout featuring start-up current less than 0.5mA,

a precision reference trimmed for accuracy at the

error amp input, logic to insure latched operation,

a PWM comparator which also provides current

limit control, and a totem pole output stage de-

signed to source or sink high peak current. The

output stage, suitable for driving N-Channel MOS-

FETs, is low in the off-state.

Differences between members of this family are

the under-voltage lockout thresholds and maxi-

mum duty cycle ranges. The UC3842A and

UC3844A have UVLO thresholds of 16V (on) and

10V (off), ideally suited off-line applications The

corresponding thresholds for the UC3843A and

UC3845A are 8.5 V and 7.9V. The UC3842A and

UC3843A can operate to duty cycles approaching

100%. A range of the zero to < 50 % is obtained by

the UC3844A and UC3845A by the addition of an

internal toggle flip flop which blanks the output off

every other clock cycle.

NOT FOR NEW DESIGN

HIGH PERFORMANCE CURRENT MODE PWM CONTROLLER

Figure 2. Block Diagram (toggle flip flop used only in UC3844A and UC3845A)

UVLO

S/R

5V

REF

34V

INTERNAL

BIAS

VREF GOOD

LOGIC

2.50V

T

S

R

OSC

R

1V

CURRENT

SENSE

COMPARATOR

2R

+

-

PWM

LATCH

7

5

4

2

1

3

8

6

ERROR AMP.

Vi

GROUND

RT/CT

VFB

COMP

CURRENT

SENSE

VREF

5V 50mA

OUTPUT

D95IN331

REV. 5

Figure 1. Package

Table 1. Order Codes

Part Number

Package

UC2842AD1; UC3842AD1;

UC2843AD1; UC3843AD1;

UC2844AD1; UC3844AD1;

UC2845AD1; UC3845AD1

SO-8

UC2842AN; UC3842AN;

UC2843AN; UC3843AN;

UC2844AN; UC3844AN;

UC2845AN; UC3845AN

DIP-8

SO-8

DIP-8

UC384XA - UC284XA

2/16

Table 2. Absolute Maximum Ratings

* All voltages are with respect to pin 5, all currents are positive into the specified terminal.

Figure 3. DIP-8/SO-8 Pin Connection (Top view)

Table 3. Pin Description

Symbol

Parameter

Value

Unit

V

i

Supply Voltage (low impedance source)

30

V

V

i

Supply Voltage (Ii < 30mA)

Self Limiting

I

O

Output Current

±

1

A

E

O

Output Energy (capacitive load)

5

µ

J

Analog Inputs (pins 2, 3)

≠ 0.3 to 5.5

V

Error Amplifier Output Sink Current

10

mA

P

tot

Power Dissipation at T

amb

25 ∞C (DIP-8)

1.25

W

P

tot

Power Dissipation at T

amb

25

∞

C (SO-8)

800

mW

T

stg

Storage Temperature Range

≠ 65 to 150

∞

C

T

J

Junction Operating Temperature

≠ 40 to 150

∞C

T

L

Lead Temperature (soldering 10s)

300

∞

C

N∞

Pin

Function

1

COMP

This pin is the Error Amplifier output and is made available for loop compensation.

2

V

FB

This is the inverting input of the Error Amplifier. It is normally connected to the switching power

supply output through a resistor divider.

3

I

SENSE

A voltage proportional to inductor current is connected to this input. The PWM uses this

information to terminate the output switch conduction.

4

R

T

/C

T

The oscillator frequency and maximum Output duty cycle are programmed by connecting

resistor R

T

to V

ref

and cpacitor C

T

to ground. Operation to 500kHz is possible.

5

GROUND

This pin is the combined control circuitry and power ground.

6

OUTPUT

This output directly drives the gate of a power MOSFET. Peak currents up to 1A are sourced

and sunk by this pin.

7

V

CC

This pin is the positive supply of the control IC.

8

V

ref

This is the reference output. It provides charging current for capacitor C

T

through resistor R

T

.

COMP

V

FB

I

SENSE

R

T

/C

T

GROUND

OUTPUT

Vi

V

REF

1

3

2

4

6

5

7

8

D95IN332

3/16

UC384XA - UC284XA

Table 4. Thermal Data

Symbol

Parameter

DIP-8

SO-8

Unit

R

th j-amb

Thermal Resistance Junction-ambient

Max.

100

150

∞C/W

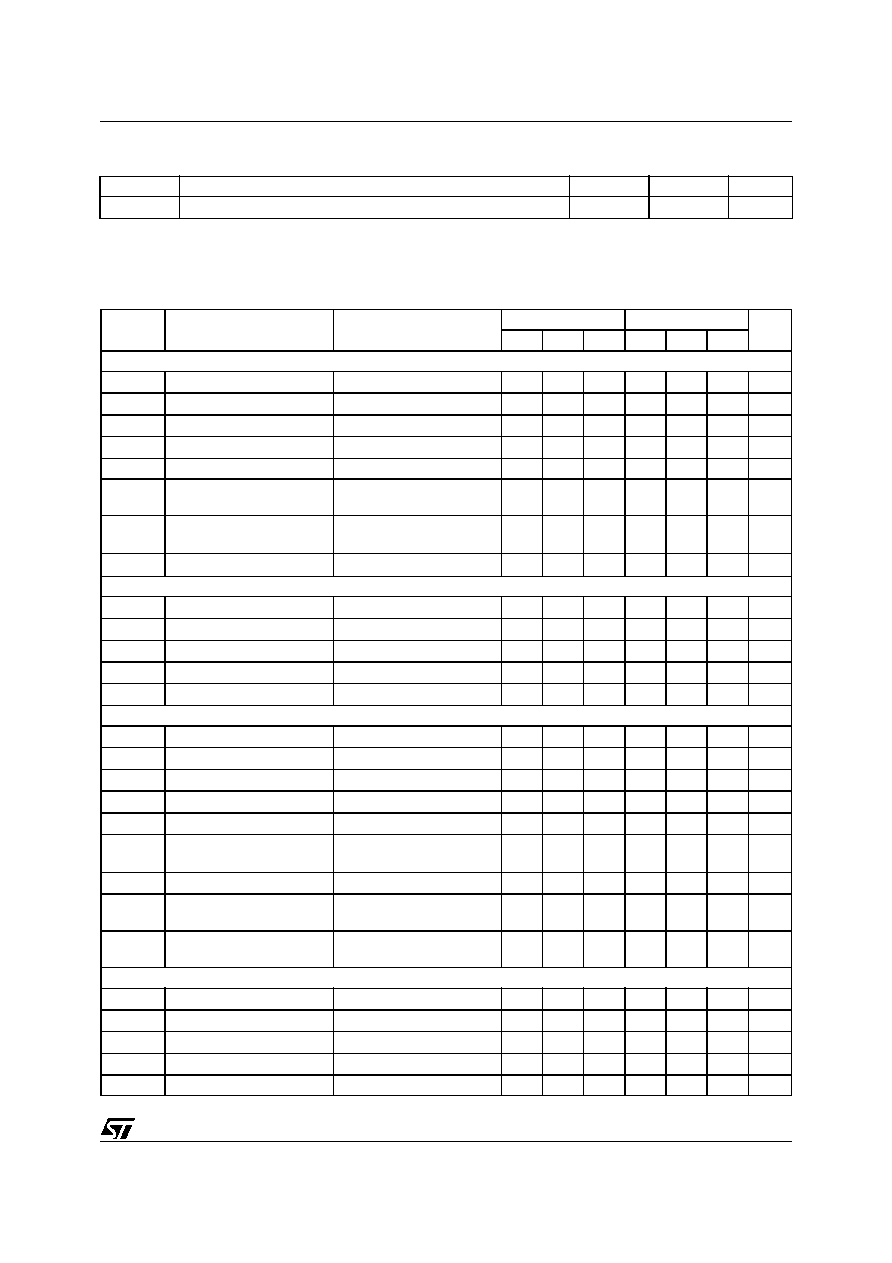

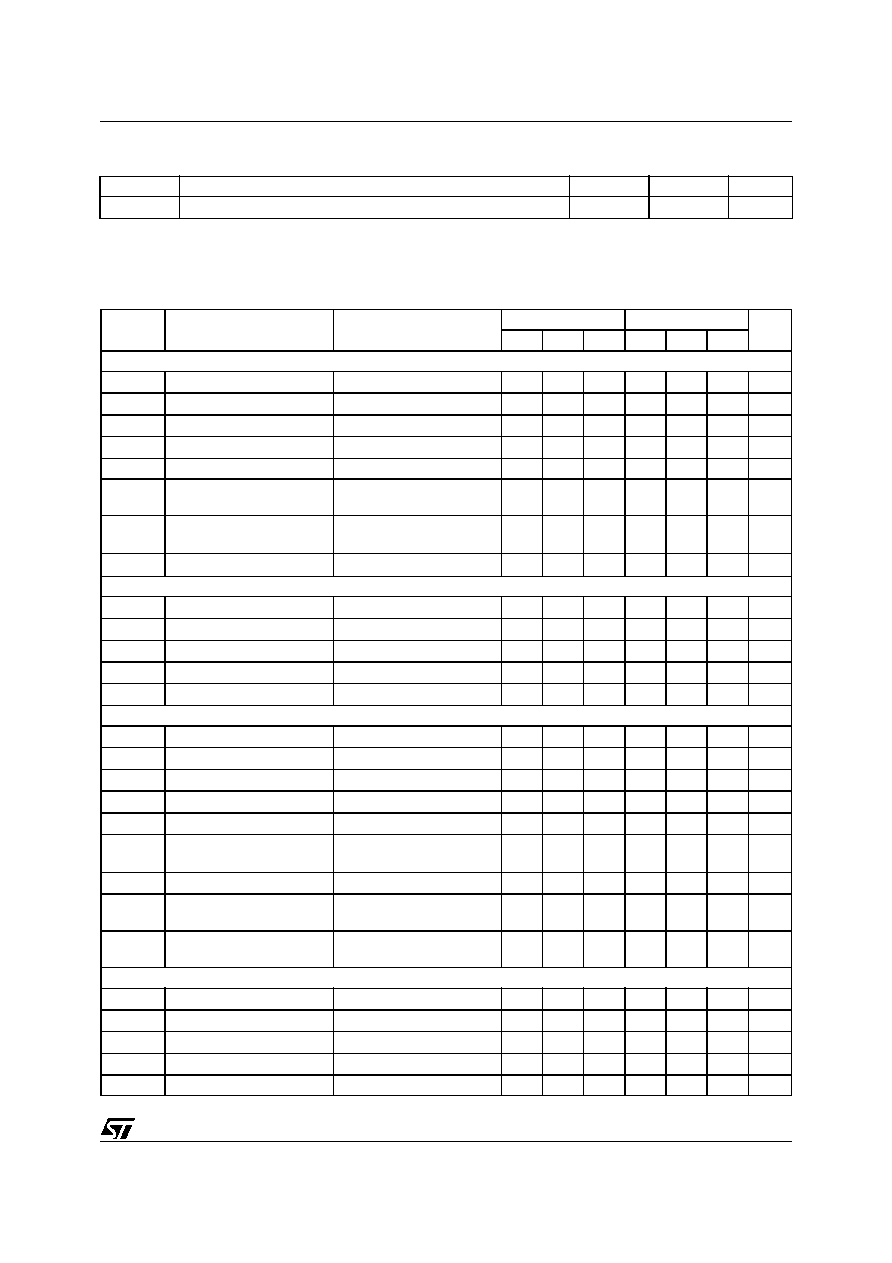

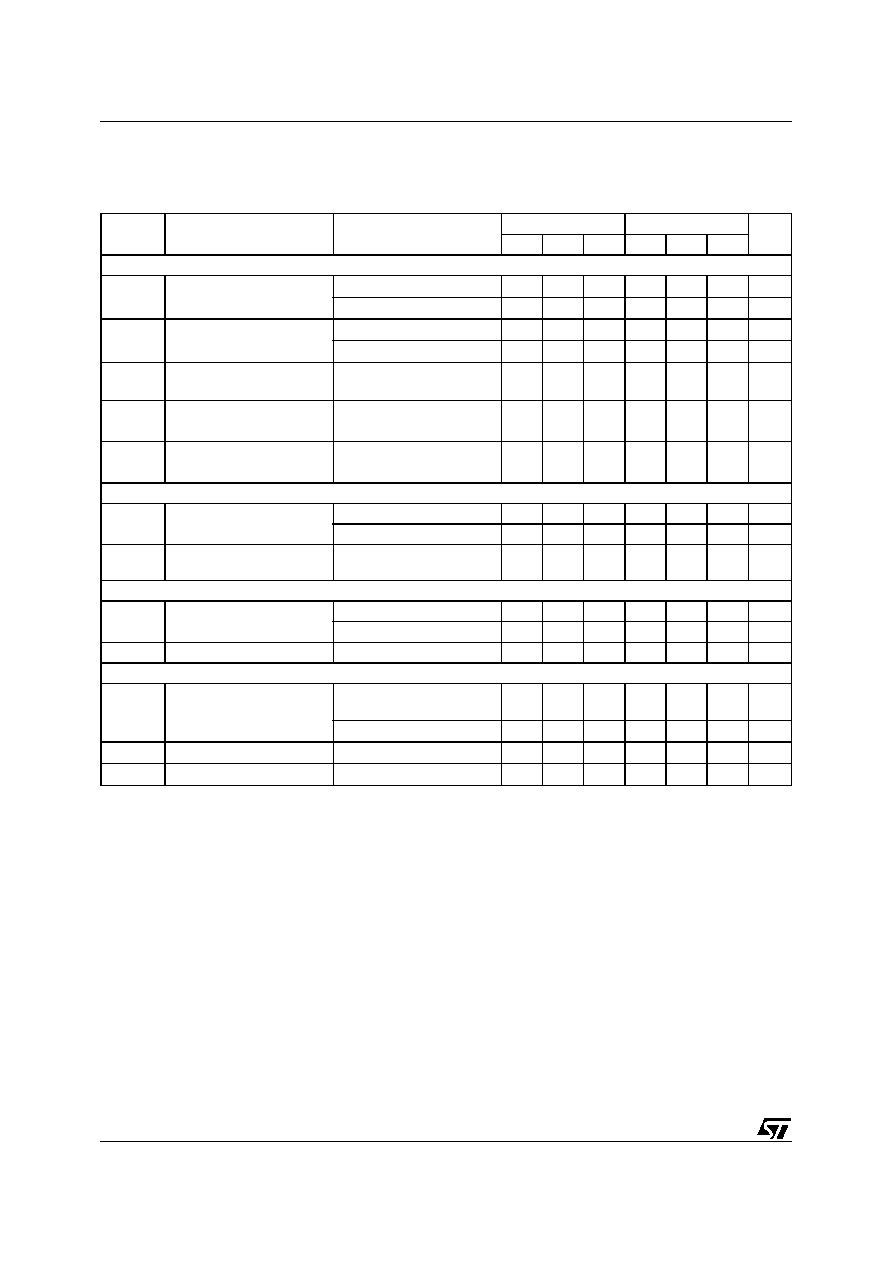

Table 5. Electrical Characteristcs

( [note 1] Unless otherwise stated, these specifications apply for -25 < T

amb

< 85∞C for UC284XA;

0 < T

amb

< 70∞C for UC384XA; V

i

= 15V (note 5); R

T

= 10K; C

T

= 3.3nF)

Symbol

Parameter

Test Condition

UC284XA

UC384XA

Unit

Min. Typ.

Max.

Min. Typ.

Max.

REFERENCE SECTION

V

REF

Output Voltage

T

j

= 25∞C I

o

= 1mA

4.95

5.00

5.05

4.90

5.00

5.10

V

V

REF

Line Regulation

12V

V

i

25V

2

20

2

20

mV

V

REF

Load Regulation

1

I

o

20mA

3

25

3

25

mV

V

REF

/

T

Temperature Stability

(Note 2)

0.2

0.2

mV/∞C

Total Output Variation

Line, Load, Temperature

4.9

5.1

4.82

5.18

V

e

N

Output Noise Voltage

10Hz

f

10KHz

T

j

= 25∞C (note 2)

50

50

µ

V

Long Term Stability

T

amb

= 125

∞

C,

1000Hrs

(note 2)

5

25

5

25

mV

I

SC

Output Short Circuit

-30

-100

-180

-30

-100

-180

mA

OSCILLATOR SECTION

f

OSC

Frequency

T

j

= 25∞C

47

52

57

47

52

57

KHz

f

OSC

/

V

Frequency Change with Volt.

V

CC

= 12V to 25V

≠

0.2

1

≠

0.2

1

%

V

REF

/

T

Frequency Change with Temp.

T

A

= T

low

to T

high

≠

5

≠

≠

5

≠

%

V

OSC

Oscillator Voltage Swing

(peak to peak)

≠

1.6

≠

≠

1.6

≠

V

I

dischg

Discharge Current (V

OSC

=2V)

T

J

= 25∞C

7.8

8.3

8.8

7.8

8.3

8.8

mA

ERROR AMP SECTION

V

2

Input Voltage

V

PIN1

= 2.5V

2.45

2.50

2.55

2.42

2.50

2.58

V

I

b

Input Bias Current

V

FB

= 5V

-0.1

-1

-0.1

-2

µ

A

A

VOL

2V

V

o

4V

65

90

65

90

dB

BW

Unity Gain Bandwidth

T

J

= 25∞C

0.7

1

0.7

1

MHz

PSRR

Power Supply Rejec. Ratio

12V

V

i

25V

60

70

60

70

dB

I

o

Output Sink Current

V

PIN2

= 2.7V

V

PIN1

= 1.1V

2

12

2

12

mA

I

o

Output Source Current

V

PIN2

= 2.3V V

PIN1

= 5V

-0.5

-1

-0.5

-1

mA

V

OUT

High

V

PIN2

= 2.3V;R

L

= 15K

to

Ground

5

6.2

5

6.2

V

V

OUT

Low

V

PIN2

= 2.7V;R

L

= 15K

to

Pin 8

0.8

1.1

0.8

1.1

V

CURRENT SENSE SECTION

G

V

Gain

(note 3 & 4)

2.85

3

3.15

2.85

3

3.15

V/V

V

3

Maximum Input Signal

V

PIN1

= 5V (note 3)

0.9

1

1.1

0.9

1

1.1

V

SVR

Supply Voltage Rejection

12

V

i

25V (note 3)

70

70

dB

I

b

Input Bias Current

-2

-10

-2

-10

µ

A

Delay to Output

150

300

150

300

ns

UC384XA - UC284XA

4/16

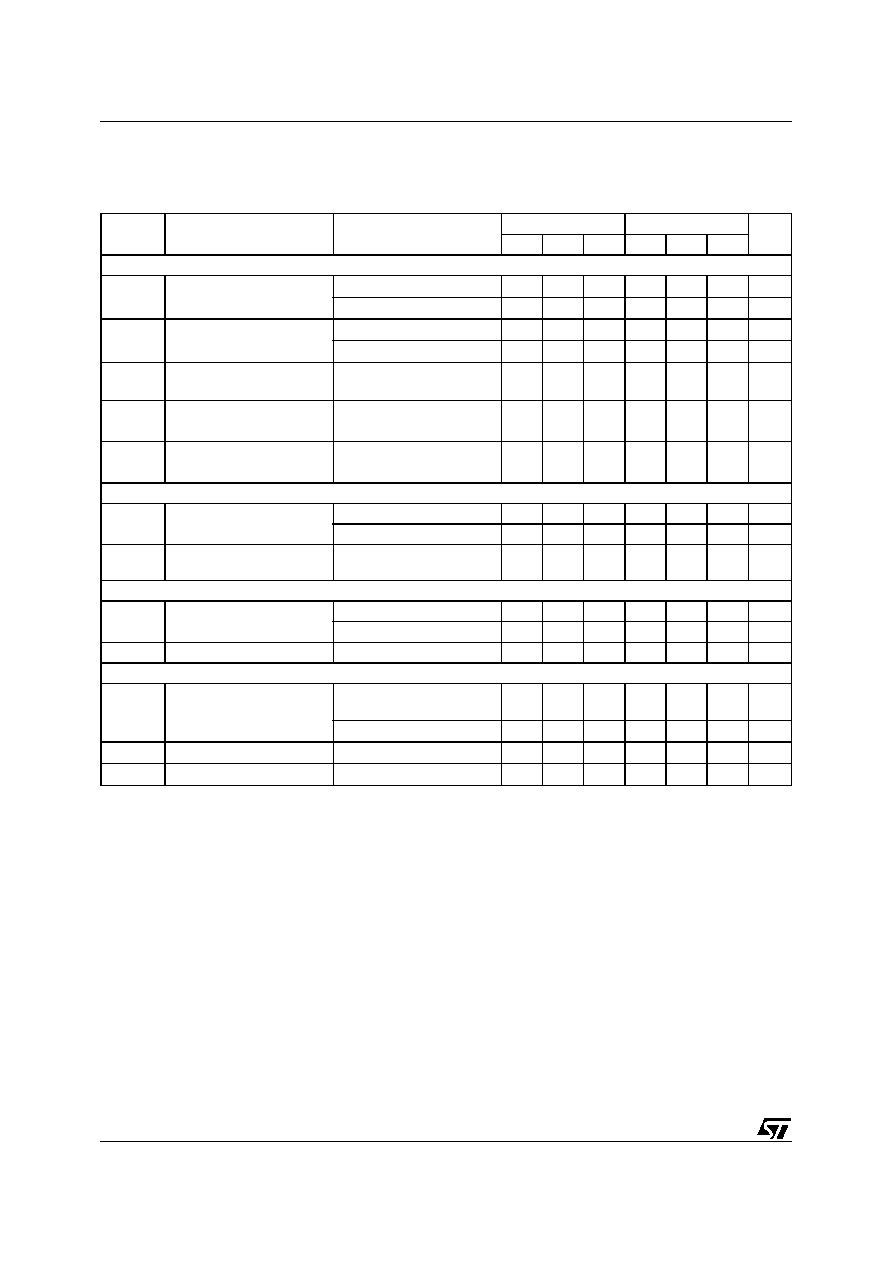

Notes: 1. Max package power dissipation limits must be respected; low duty cycle pulse techniques are used during test maintain T

j

as close

to T

amb

as possible.

2. These parameters, although guaranteed, are not 100% tested in production.

3. Parameter measured at trip point of latch with V

PIN2

= 0.

4. Gain defined as : A =

V

PIN1

/

V

PIN3

; 0

V

PIN3

0.8V

5. Adjust V

i

above the start threshold before setting at 15 V.

OUTPUT SECTION

V

OL

Output Low Level

I

SINK

= 20mA

0.1

0.4

0.1

0.4

V

I

SINK

= 200mA

1.6

2.2

1.6

2.2

V

V

OH

Output High Level

I

SOURCE

= 20mA

13

13.5

13

13.5

V

I

SOURCE

= 200mA

12

13.5

12

13.5

V

V

OLS

UVLO Saturation

V

CC

= 6V; I

SINK

= 1mA

0.7

1.2

0.7

1.2

V

t

r

Rise Time

T

j

= 25∞C

C

L

= 1nF

(2)

50

150

50

150

ns

t

f

Fall Time

T

j

= 25∞C

C

L

= 1nF

(2)

50

150

50

150

ns

UNDER-VOLTAGE LOCKOUT SECTION

Start Threshold

X842A/4A

15

16

17

14.5

16

17.5

V

X843A/5A

7.8

8.4

9.0

7.8

8.4

9.0

V

Min Operating Voltage

After Turn-on

X842A/4A

9

10

11

8.5

10

11.5

V

PWM SECTION

Maximum Duty Cycle

X842A/3A

94

96

100

94

96

100

%

X844A/5A

47

48

50

47

48

50

%

Minimum Duty Cycle

0

0

%

TOTAL STANDBY CURRENT

I

st

Start-up Current

V

i

= 6.5V for UCX843A/

45A

0.3

0.5

0.3

0.5

mA

V

i

= 14V for UCX842A/44A

0.3

0.5

0.3

0.5

mA

I

i

Operating Supply Current

V

PIN2

= V

PIN3

= 0V

12

17

12

17

mA

V

iz

Zener Voltage

I

i

= 25mA

30

36

30

36

V

Table 5. Electrical Characteristcs (continued)

( [note 1] Unless otherwise stated, these specifications apply for -25 < T

amb

< 85∞C for UC284XA;

0 < T

amb

< 70∞C for UC384XA; V

i

= 15V (note 5); R

T

= 10K; C

T

= 3.3nF)

Symbol

Parameter

Test Condition

UC284XA

UC384XA

Unit

Min. Typ.

Max.

Min. Typ.

Max.

5/16

UC384XA - UC284XA

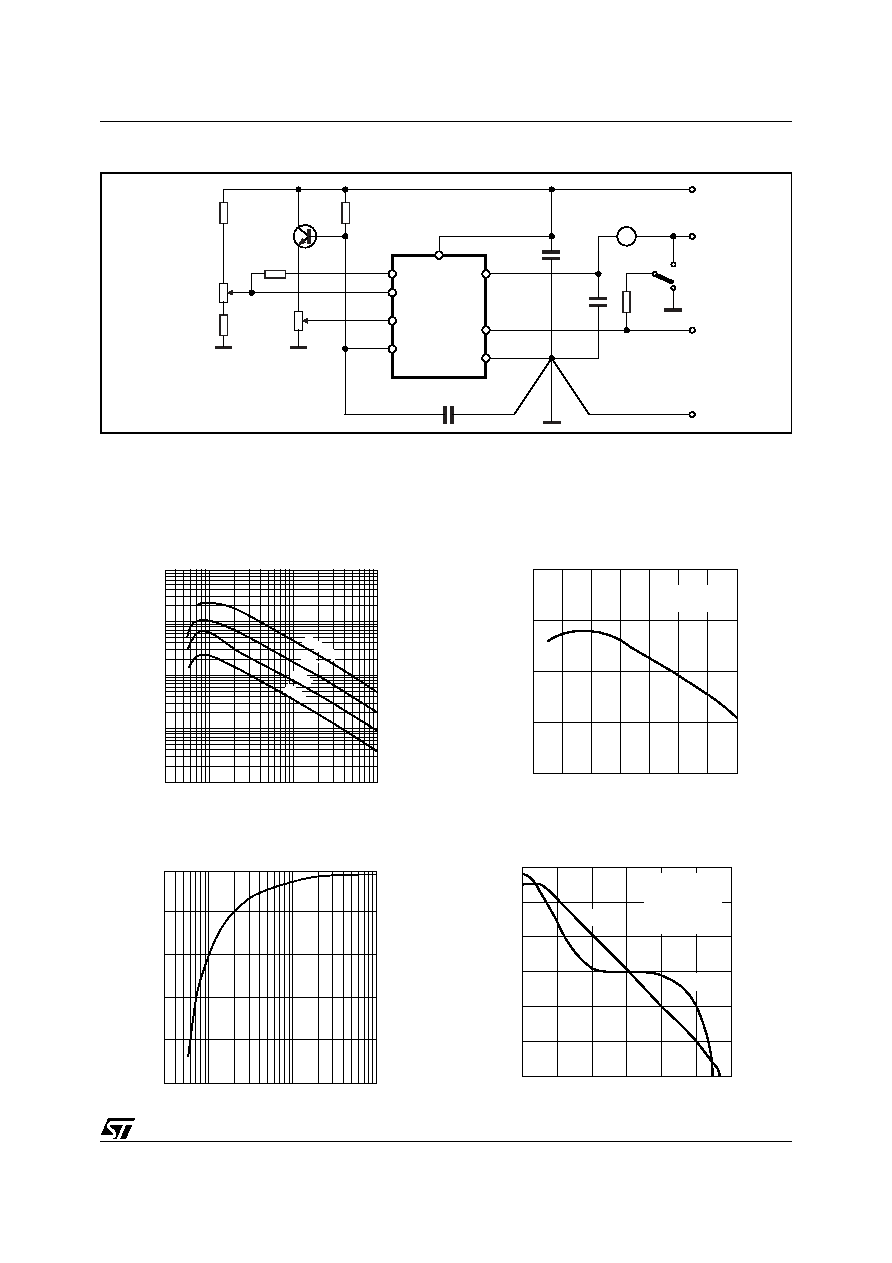

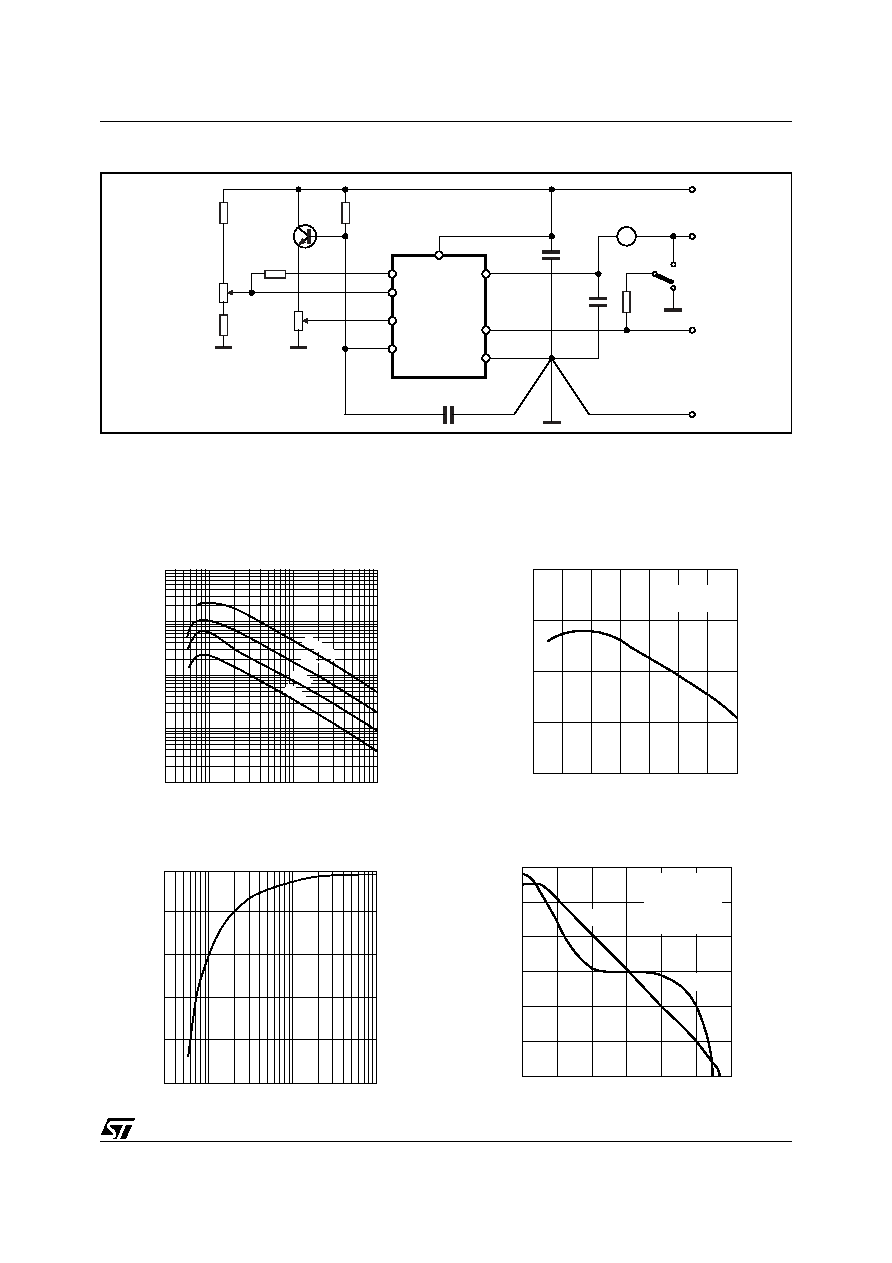

Figure 4. Open Loop Test Circuit.

High peak currents associated with capacitive loads necessitate careful grounding techniques. Timing and

bypass capacitors should be connected close to pin 5 in a single point ground. The transistor and 5 K

potentiometer are used to sample the oscillator waveform and apply an adjustable ramp to pin 3.

R

T

A

2N2222

4.7K

1K

ERROR AMP.

ADJUST

4.7K

5K

I

SENSE

ADJUST

100K

COMP

V

FB

I

SENSE

R

T

/C

T

1

2

3

4

C

T

7

6

5

8

V

REF

V

i

OUTPUT

GROUND

0.1

µ

F

0.1

µ

F

V

REF

V

i

OUTPUT

GROUND

1W

1K

D95IN343

Figure 5. Oscillator Frequency vs Timing

Resistance

Figure 6. Maximum Duty Cycle vs Timing

Resistor

Figure 7. Oscillator Discharge Current vs.

Temperature.

Figure 8. Error Amp Open-Loop Gain and

Phase vs. Frequency.

300

1K

3K

10K

30K

R

T

(

)

1K

10K

100K

1M

f

o

(Hz)

D96IN362

CT=470pF

1nF

2.2nF

4.7nF

300

1K

3K

10K

30K

R

T

(

)

0

20

40

60

f

o

(Hz)

D96IN363

80

-55

-25

0

25

50

75

100 T

A

(∞C)

7.0

7.5

8.0

8.5

I

dischg

(mA)

D95IN335

V

i

=15V

V

OSC

=2V

10

100

1K

10K

100K

1M

f(Hz)

-20

0

20

40

60

80

(dB)

180

150

120

90

60

30

D95IN337

V

i

=15V

V

O

=2V to 4V

R

L

=100K

T

A

=25∞C

Gain

Phase