PRODUCT SELECTION GUIDE

PARAMETER

WS57C71C-45

WS57C71C-55

WS57C71C-70

Address Access Time (Max)

45 ns

55 ns

70 ns

CS to Output Valid Time (Max)

20 ns

20 ns

30 ns

WS57C71C

4-13

MILITARY HIGH SPEED 32K x 8 CMOS PROM/RPROM

KEY FEATURES

∑

Ultra-Fast Access Time

∑

Immune to Latch-UP

-- 45 ns

-- Up to 200 mA

∑

Low Power Consumption

∑

ESD Protection Exceeds 2000V

∑

Fast Programming

∑

Available in 300 and 600 Mil DIP

and CLLCC

GENERAL DESCRIPTION

The WS57C71C is a High Performance 256K UV Erasable Electrically Re-Programmable Read Only Memory

(RPROM). It is manufactured in an advanced CMOS technology and utilizes WSI's patented self-aligned split gate

EPROM cell.

The industry standard PROM pin configuration of the WS57C71C provides an easy upgrade path from a 16K x 8

device.

This RPROM is capable of operating at speeds as fast as 35 ns address access time, which enables it to be used

directly with today's fast microprocessors and DSP processors without introducing any wait states. All inputs and

outputs are TTL compatible. The WS57C71C is a low power device even when operated at its fastest speed. The

DIP version is packaged in a 300 mil wide DIP package saving board space for the user.

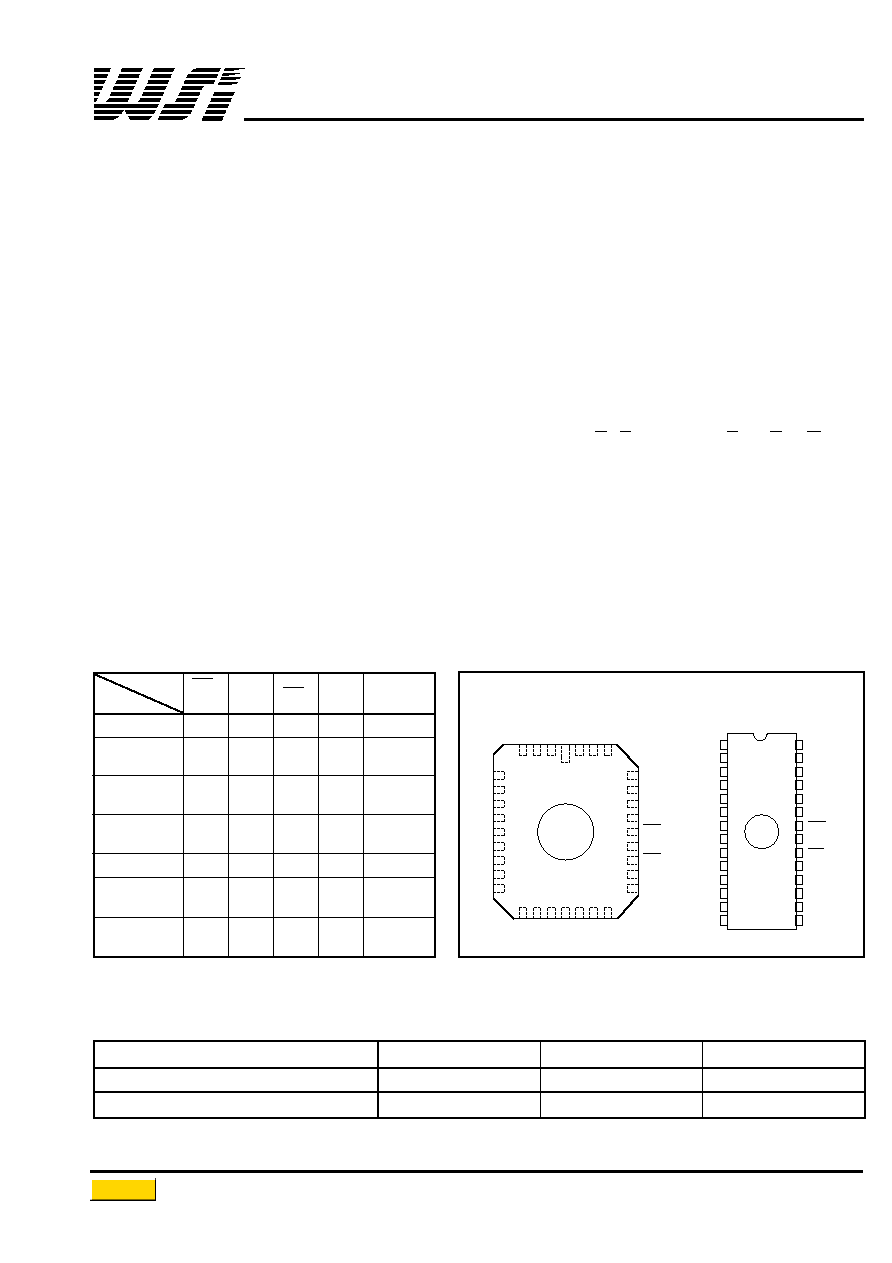

MODE

PINS

CS1/

CS2

CS3

VCC

OUTPUTS

VPP

Read

VIL

VIH

VIL

VCC

DOUT

Output

Disable

VIH

X

X

VCC

High Z

Output

X

VIL

X

VCC

High Z

Disable

Output

X

X

VIH

VCC

High Z

Disable

Program

VPP

X

VIH

VCC

DIN

Program

Verify

VIL

VIH

VIL

VCC

DOUT

Program

Inhibit

VPP

X

VIL

VCC

HIGH Z

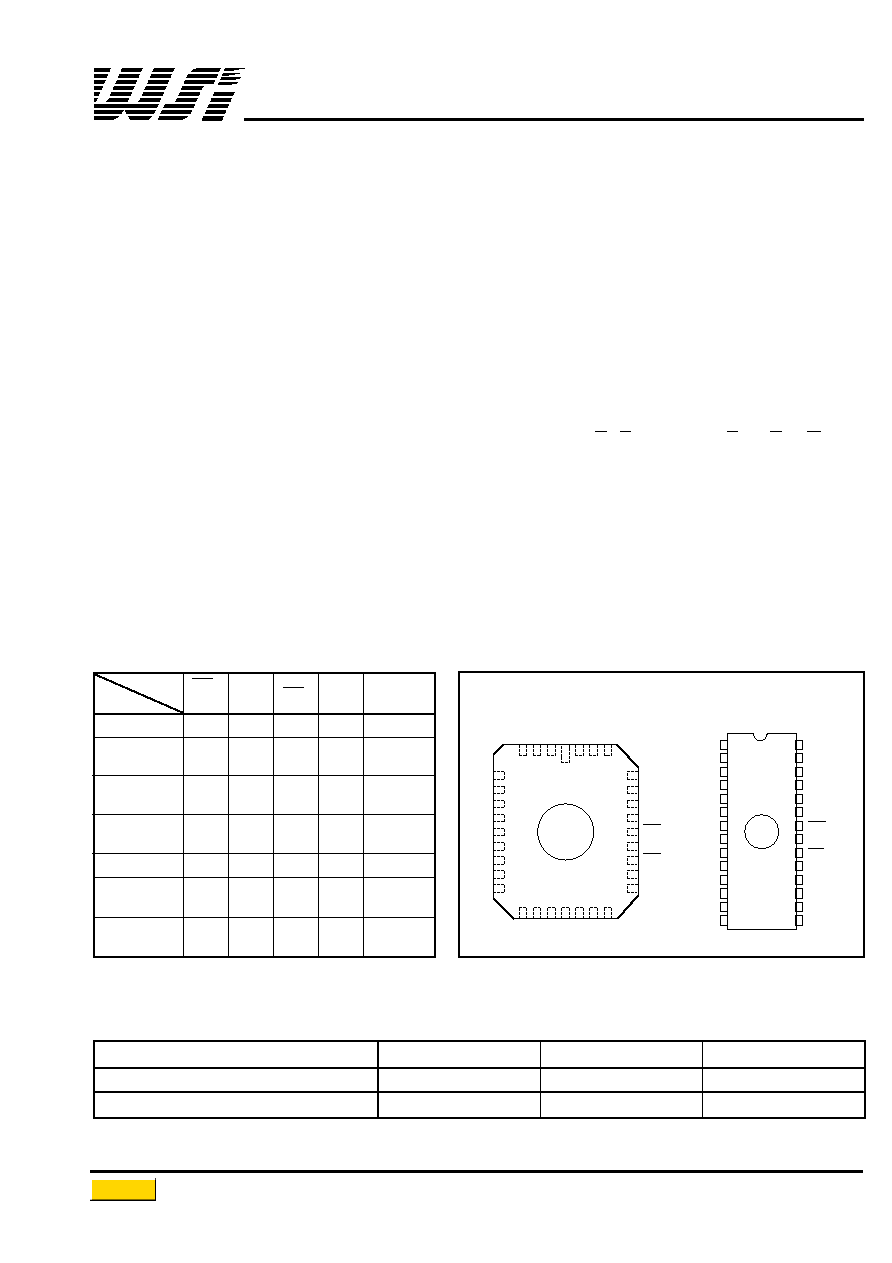

V

CC

A10

A11

A12

A13

A14

CS3

CS2

CS1/VPP

O

7

O

6

O

5

O

4

O

3

A

9

A

8

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

O

0

O

1

O

2

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

A

12

A

13

A

14

NC

CS3

CS2

CS1/VPP

O

7

O

6

A

6

A

5

A

4

A

3

A

2

A

1

A

0

NC

O

0

A

7

A

8

A

9

NC

V

CC

A

10

A

11

O

1

O

2

NC O

3

O

4

O

5

1

4 3

2

32 31 30

29

28

27

26

25

24

23

22

21

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20

GND

TOP VIEW

Chip Carrier

CERDIP

MODE SELECTION

PIN CONFIGURATION

Return to Main Menu

WS57C71C

4-14

ORDERING INFORMATION

OPERATING WSI

PART NUMBER

TEMPERATURE MANUFACTURING

RANGE

PROCEDURE

WS57C71C-45TMB

45

28 Pin CERDIP, 0.3"

T2

Military

MIL-STD-883C

WS57C71C-55CMB

55

32 Pad CLLCC

C2

Military

MIL-STD-883C

WS57C71C-55DMB

55

28 Pin CERDIP, 0.6"

D2

Military

MIL-STD-883C

WS57C71C-55TMB

55

28 Pin CERDIP, 0.3"

T2

Military

MIL-STD-883C

WS57C71C-70TMB

70

28 Pin CERDIP, 0.3"

T2

Military

MIL-STD-883C

SPEED

PACKAGE PACKAGE

(ns)

TYPE

DRAWING

PROGRAMMING/ALGORITHMS/ERASURE/PROGRAMMERS

REFER TO

PAGE 5-1

The WS57C71C is programmed using Algorithm D shown on page 5-9.

NOTE: 9. The actual part marking will not include the initials "WS."

For complete data sheet and electrical specifications see page 2-55.

Return to Main Menu